# High Frequency Integrated MOS Filters

C. Peterson

International Microelectronic Products

San Jose, CA 95134

Abstract- Several techniques exist for implementing integrated MOS filters. These techniques fit into the general categories of sampled and tuned continuous-time filters. Advantages and limitations of each approach are discussed. This paper focuses primarily on the high frequency capabilities of MOS integrated filters.

#### 1 Introduction

The use of MOS in the design of analog integrated circuits continues to grow. Competitive pressures drive system designers towards system-level integration. System-level integration typically requires interface to the analog world. Often, this type of integration consists predominantly of digital circuitry, thus the efficiency of the digital in cost and power is key. MOS remains the most efficient integrated circuit technology for mixed-signal integration. The scaling of MOS process feature sizes combined with innovation in circuit design techniques have also opened new high bandwidth opportunities for MOS mixed-signal circuits.

There is a trend to replace complex analog signal processing with digital signal processing (DSP). The use of over-sampled converters minimizes the requirements for pre-and post filtering. In spite of this trend, there are many applications where DSP is impractical and where signal conditioning in the analog domain is necessary, particularly at high frequencies. Applications for high frequency filters are in data communications and the read channel of tape, disk and optical storage devices where filters bandlimit the data signal and perform amplitude and phase equalization. Other examples include filtering of radio and video signals. Integrated filters offer obvious advantages in reducing PC board space and eliminating trimming or the requirement for tight passive component tolerances. Also, integrated filters offer advantages over passive filters when it is necessary for the filter characteristics to be programmable. This paper will review techniques for building integrated CMOS filters with a focus toward high frequencies.

Since tolerances of resistors and capacitors available in integrated circuit technologies are typically too large for most applications, circuit design techniques have been developed to take advantage of the tracking of components on a single die. There are two general types of approaches. The first utilizes discrete time sampling and the second approach is continuous-time and utilizes a tuning scheme to compensate for process variation. These two general approaches will be discussed in more detail.

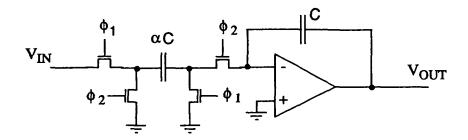

Figure 1: Switched-Capacitor Integrator

## 2 Sampled Filters

In sampled filters a delay element is implemented by storing charge on a capacitor. In a switched capacitor filter, signals are summed by charge sharing between weighted capacitors. Pole and zero frequencies are set by ratios of capacitors and the clocking rate. An example of a switched-capacitor integrator is shown in Figure 1. The output of the integrator has a transfer function given by:

$$H(z) = \frac{V_{out}(z)}{V_{IN}(z)} = \frac{\alpha z^{-1}}{1 - Z^{-1}}$$

(1)

Switched-capacitor technology is now a mature design technique that has been used extensively in audio band communication circuits over the last 10-15 years. This design technique has matured such that sophisticated tools have been developed to automate the design of switched-capacitor filters. Switched-capacitor filters require a floating linear capacitor which adds processing steps that are not needed for standard digital circuits. This may not be a significant burden if the majority of a chip is analog, however more and more mixed-signal designs are dominated by digital.

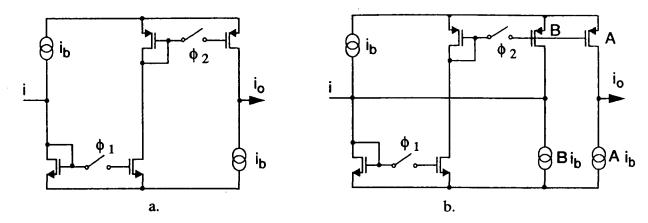

A new alternative to switched-capacitor filters are switched-current filters [1],[2]. This technique represents signals as sampled currents rather than sampled charge. Signals are simply summed by connecting current mirror outputs together. The delay element is made of a current mirror in which the voltage on the gate of the output transistor is sampled. Figure 2a shows a simple delay element. Figure 2b shows how the delay element can be modified into a switched-current integrator. The output of the integrator has a transfer function given by:

$$H(z) = \frac{io(z)}{i(z)} = \frac{Az^{-1}}{1 - Bz^{-1}}$$

(2)

These circuits can also be extended to a fully differential topology. Cascades may be added to improve accuracy of the current mirrors. Poles and zeros are set by the ratio of current mirrors and the sampling rate. This technique offers several advantages. First, the holding capacitor need not be linear; gate capacitance works well. Second, amplifiers are

Figure 2: a. Switched-Current Delay Cell, b. Switched-Current Integrator

not needed. This is an obvious advantage for power efficiency and for bandwidth. Third, signals are represented as currents rather than voltages. This allows signal nodes to be low impedance, which maximizes the frequency of parasitic poles. Also, current-mode circuits offer a signal-to-noise advantage, particularly as supply voltages are scaled down.

Sampled-data filter performance is limited by the non-ideal characteristics of its components. In the case of switched-capacitor filters, performance is limited by capacitor matching, charge injection, opamp gain and bandwidth and noise from switches and opamps. Switched-current filter performance is limited by matching of transistors, output impedance of the current mirrors, charge injection on the hold capacitor and noise contributions of the switch and mirror transistors. In both switched-capacitor and switched-current filters, broadband noise is sampled and aliased back into the base band.

Switched-capacitor filters have been demonstrated up to 10.7 MHz pole frequencies [3], but practical limits for this technology today are considered to be around 200 KHz pole frequencies. Sampling rates are typically greater than 10 times the pole frequency. Otherwise, the anti-aliasing filter becomes complex enough to render the switched-capacitor filter approach impractical. A common rule-of-thumb is to make the opamp gain bandwidth at least 5 times the sample rate. This would indicate that the opamp bandwidth should be at least 50 times the pole frequency. The achievable opamp bandwidth depends upon its capacitive load up to the point where the opamp's own output capacitance greatly exceeds the load it is driving. In a single-stage opamp the gain-bandwidth is determined by the output pole and in the case of a two-stage opamp the output pole must be greater than the gain-bandwidth to achieve reasonable phase margin. For a  $1\mu$ m process an opamp tops out at 100 MHz into a 5pF load, not to mention that it is burning about 5mA of current and only has about 40 dB of low frequency gain.

Techniques for high frequency switched-current filters are not fully developed yet. The inherent limit would appear to be the sample rate that would allow the sample and hold to settle out sufficiently. Trade-offs have to be made between charge injection error and settling time in sizing the switch and hold capacitor. This issue is common with switched-

capacitor filters, however, switched-current filters are not limited by the bandwidth of an opamp. This approach certainly has interesting advantages and deserves more attention.

#### 3 Continuous-Time Filters

Tuned continuous-time filters have been reported over the last several years. However, they are now starting to receive serious attention in industry. Continuous filters have several key advantages over their sampled counterpart: they do not suffer from a aliasing of broadband noise, they do not require anti-aliasing filters, and they are more suitable for high frequency applications since they do not need to be sampled at 10 or more times the signal band.

There are several ways to implement integrated continuous-time filters. Thin-film resistors can be trimmed by lasers, however this requires an undesirable complexity and increase in production costs. One novel approach published uses thin-film resistors to build a classic active R-C filter. All integrator capacitors are identically digitally programmable and tuned during an initialization sequence under the control of the host processor, thus compensating for the process variation of the capacitors and resistors [6].

Another technique utilizes MOS transistors operated in their linear region to implement a classic active R-C filter. Typically the filter is operated in a fully differential mode to cancel out non-linearities in the MOS resistor (MOS-R). To maintain reasonable linearity the signal swing is kept small, especially if only a 5V supply is utilized. The control voltage for the MOS-R transistors is derived from a phase-locked loop (PLL) using a reference filter locked to a stable reference clock.

To build high bandwidth active R-C filters, high bandwidth opamps are needed. A good rule-of-thumb is to make the unity-gain-bandwidth of the opamp over 50 times larger than the signal bandwidth of the filter. This places a practical limit for MOS active R-C filter today to under 2MHz.

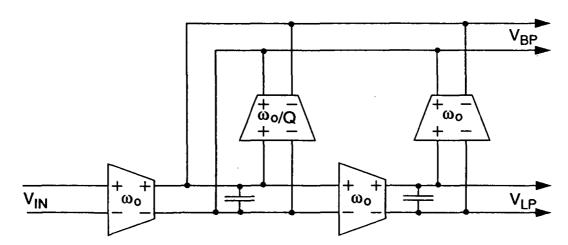

Another approach growing in popularity is that of transconductance-C filters. This technique has the advantage that the unity-gain-bandwidth of the amplifier is the desired filter pole frequency. Signals are summed by connecting transconductance amplifiers, or OTA, outputs together. Figure 3 shows a typical transconductance-C biquad. Optimum high frequency operation can be achieved if all the nodes in the filter that the signal is represented as a voltage are integrator nodes. Thus no high frequency amplifiers are needed. This greatly reduces the amplifier current or increases the filter bandwidth that can be achieved when compared with an active R-C approach.

Since the transconductance of the OTA is affected by process and temperature it can be tuned similar to the MOS-R filter by a tuning PLL. The transconductance can be tuned by adjusting the bias current of the input devices. Large variations in bias current will however degrade the allowable signal swing for good linearity. Other techniques for coarse tuning may be utilized, such as changing the integration capacitor or current gain of the OTA output stage to reduce the tuning range for the bias current. Techniques exist to linearize the input range of an OTA, however they all limit the ability to tune the OTA

Figure 3: Transcinductive-C biquad

transconductance by changing the bias current [7], [8]. For a non-linearized OTA, the linear input signal range is a function of the excess bias voltage of the input transistors, which is set by the transistor's dimensions and bias current.

Unfortunately, there exist internal poles in an OTA that cause excess phase shift in the integrators that distort the frequency response of the filter. These poles are typically far beyond the pole frequency, but not far enough to neglect. Techniques have been published to compensate for this phase loss by adding in an equivalent phase shift of the opposite sign [9]. For optimal cancellation of excess phase, the compensating circuit can be tuned by a vector-locked-loop (VLL) [10,11]. Tuning can be accomplished by using a separate reference filter or a filter may be switched out of the signal path and used in a calibration mode.

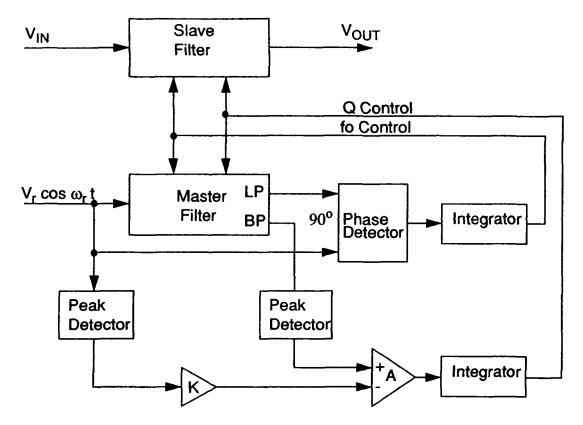

Figure 4 shows an example of a vector-locked tuning loop. In this architecture two tuning loops exist, a phase-locked loop for frequency control and a magnitude-locked-loop for Q control. In the frequency control loop the lowpass output of the master biquad filter is compared to the reference signal on its input. The output of the phase detector is integrated and used to tune the reference filter along with the slave or main signal filter. The loop locks the pole frequency of the reference biquad to the reference clock frequency by detecting a 90 degree phase shift through the biquad. Since the Q of a biquad filter is extremely sensitive to excess phase shift in its integrators, a magnitude locking-loop for Q-control may be used. This can be implemented by integrating the difference between the RMS or peak signal from the input of the reference filter with its bandpass output. This adjusts the excess phase of the integrator such that the correct gain is maintained at its pole frequency. A more sophisticated technique has been proposed that derives the autocorrection and crosscorrelation functions of the filter input and output signals [12]. This approach allows the same filter to be used simultaneously to process signals while it is being used for tuning, thus eliminating any mismatch error between the master and

Figure 4: Vector-locked tuning loop

slave filter.

Design of high frequency circuits require accurate modeling of parasitic capacitances and resistances. A challenge that must be faced during the design of high frequency filters is that of the distributed R-C of the MOSFET channel. Current SPICE like simulation models ignore this limitation [13]. One solution involves modeling individual transistors as multiple devices in series.

Experimental MOS transconductance-C filters have been published that have achieved bandwidths up to 90MHz. An example of a commercial application of this technology, is an automatically tuned, programmable filter that has been developed for the read-channel of the disk drives at IMP. This product includes a programmable second-order allpass and a 6th-order Bessel lowpass with programmable pulse-sliming zeros. The filter is digitally programmed through a serial interface. The frequency response can be shifted by changing the clock reference. Pole frequencies may be set up to 30MHz.

### 4 Conclusion

Pre- and post filtering requirements of sampled filters and high sample rates render sampled filters undesirable for high frequency applications. Opamp based continuous-time filters are constrained by the requirement for stable opamps with bandwidths substantially beyond the filter's pole frequencies. Of the techniques described in this paper, superior high

frequency performance can be achieved by continuous-time transconductance-C filters. Automatic tuning allows for the compensation of process variations and effects of non-ideal integrators. Transconductance-C filters should have as big of an impact on high-frequency filter applications as switched-capacitor filters have had in audio-band communication circuits.

#### References

- [1] John. B. Hughes, "Analogue IC Design: The Current Mode Approach," IEEE 1990, pp. 415-450.

- [2] John B. Hughes, et al, "Switched Currents- A New Technique For Analog Sampled-Data Signal Processing," IEEE International Symposium on Circuits and Systems Proceedings, pp. 1584-1587, 1989.

- [3] Bang-Sup Song, "A 10.7MHz Switched-Capacitor Bandpass Filter," IEEE J. of Solid State Circuits, Vol. 24, pp. 320-324, April 1989.

- [4] F. Op't Eynde, et al, "A 150MHz OTA In 3 Micron CMOS Silicon Technology," IEEE International Symposium on Circuits and Systems Proceedings, pp. 86-89, 1989.

- [5] Germano Nicollini, et al, "High Frequency Fully Differential Filter Using Operational Amplifiers Without Common-mode Feedback," IEEE J. of Solid State Circuits, Vol. 24, No. 3, pp. 803-813, June 1989.

- [6] John P. Roesgen et al, "An Analog Front End Chip For V.32 Modems," IEEE Custom Integrated Circuits Conference, pp.16.1.1-16.1.5, 1989.

- [7] F. Krummenacher, "Design Considerations In High Frequency CMOS Transconductance Amplifier Capacitor (TAC) Filters," IEEE International Symposium on Circuits and Systems Proceedings, pp. 100-105, 1989.

- [8] Peter M. VanPeteghem, et al, "Design of a Very-Linear CMOS Transconductance Input Stage for Continuous-Time Filters," IEEE J. of Solid State Circuits, Vol. 25, No. 2, pp. 497-500, April 1990.

- [9] Tsutomu Wakimoto, et al, "A Low-Power Wide-Band Amplifier Using a new Parasitic Capacitance Technique,", IEEE International Symposium on Circuits and Systems Proceedings, pp. 106-109, 1989.

- [10] Rolf Schaumann, "The Problem of On-Chip Automatic Tuning In Continuous-Time Integrated Filters," IEEE International Symposium on Circuits and Systems Proceedings, pp. 106-109, 1989.

- [11] Rolf Schaumann, Design of Analog Filters, Prentice Hall, 1990, pp.419-446.

- [12] Todd L. Brooks, et al, "Simultaneous Tuning and Signal Processing in Integrated Continuous-Time Filters: The Correlated Tuning Loop," IEEE International Symposium on Circuits and Systems Proceedings, pp. 651-654, 1989.

- [13] Haideh Khorramabadi, et al, "High-Frequency CMOS Continuous-Time Filters," IEEE J. of Solid State Circuits, Vol. SC-19, No. 6, pp. 939-948, Dec 1984.