## Three-Function Logic Gate Controlled by Analog Voltage

A different logic function is selected by changing a single voltage.

NASA's Jet Propulsion Laboratory, Pasadena, California

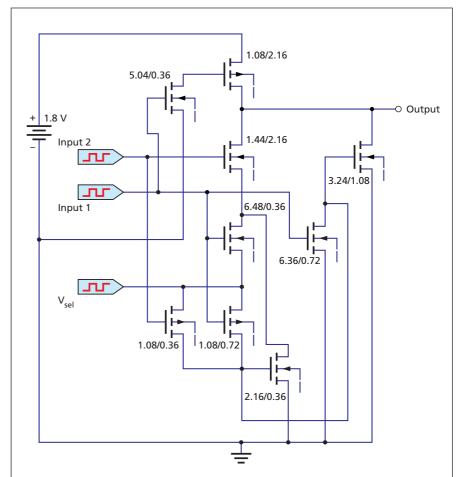

The figure is a schematic diagram of a complementary metal oxide/semiconductor (CMOS) electronic circuit that performs one of three different logic functions, depending on the level of an externally applied control voltage,  $V_{\rm sel}$ . Specifically, the circuit acts as

- A NAND gate at  $V_{sel} = 0.0$  V,

- A wire (the output equals one of the inputs) at  $V_{sel} = 1.0$  V, or

- An AND gate at  $V_{\text{sel}} = -1.8$  V.

[The nominal power-supply potential  $(V_{DD})$  and logic "1" potential of this circuit is 1.8 V.]

Like other multifunctional circuits described in several prior NASA Tech Briefs articles, this circuit was synthesized following an automated evolutionary approach that is so named because it is modeled partly after the repetitive trial-and-error process of biological evolution. An evolved circuit can be tested by computational simulation and/or tested in real hardware, and the results of the test can provide guidance for refining the design through further iteration. The evolutionary synthesis of electronic circuits can now be implemented by means of a software package - Genetic Algorithms for Circuit Synthesis (GACS) that was developed specifically for this purpose. GACS was used to synthesize the present trifunctional circuit.

As in the cases of other multifunctional circuits described in several prior *NASA Tech Briefs* articles, the multiple functionality of this circuit, the use of a single control voltage to select the function, and the automated evolutionary approach to synthesis all contribute synergistically to a combination of features that are potentially advantageous for the further development of robust, multiple-function logic circuits, including, especially, field-programmable gate arrays (FPGAs). These advantages include the following:

This circuit contains only 9 transistors

about half the number of transistors

that would be needed to obtain equivalent NAND/wire/AND functionality by

use of components from a standard dig ital design library.

This **CMOS Circuit Performs as One of Three Logic Gates**, depending on  $V_{sel}$ . The first and second number next to each transistor symbol are the width and length, respectively, of the transistor in microns. The CMOS substrate connections are  $V_{DD}$  (PMOS) and ground (NMOS).

• If multifunctional gates like this circuit were used in the place of the configurable logic blocks of present commercial FPGAs, it would be possible to change the functions of the resulting digital systems within shorter times. For example, by changing a single control voltage, one could change the function of thousands of FPGA cells within nanoseconds. In contrast, typically, the reconfiguration in a conventional FPGA by use of bits downloaded from look-up tables via a digital bus takes microseconds.

This work was done by Ricardo Zebulum and Adrian Stoica of Caltech for NASA's Jet **Propulsion Laboratory**. Further information is contained in a TSP (see page 1).

In accordance with Public Law 96-517, the contractor has elected to retain title to this invention. Inquiries concerning rights for its commercial use should be addressed to:

Innovative Technology Assets Management JPL

Mail Stop 202-233 4800 Oak Grove Drive Pasadena, CA 91109-8099 (818) 354-2240

E-mail: iaoffice@jpl.nasa.gov

Refer to NPO-40919, volume and number of this NASA Tech Briefs issue, and the page number.