the fabrication processes follow a standard sequence until just before the fabrication of the microscopic wires.

Then, by use of a thermal SiO-deposition technique, the electrodes and the substrate surface areas in the gaps between them are covered with SiO. Next, the SiO is electron-beam patterned, then reactive-ion etched to form channels having specified widths (typically about 1 µm or less) that define the widths of the wires to be formed. Drops of an electroplating solution are placed on the substrate in the regions containing the channels thus

formed, then the wires are electrodeposited from the solution onto the exposed portions of the electrodes and into the channels. The electrodeposition is a room-temperature, atmospheric-pressure process. The figure shows an example of palladium wires that were electrodeposited into 1-mm-wide channels between gold electrodes.

This work was done by Minhee Yun, Nosang Myung, and Richard Vasquez of Caltech for NASA's Jet Propulsion Laboratory. Further information is contained in a TSP (see page 1).

In accordance with Public Law 96-517, the contractor has elected to retain title to this invention. Inquiries concerning rights for its commercial use should be addressed to:

Innovative Technology Assets Management

Mail Stop 202-233

4800 Oak Grove Drive Pasadena, CA 91109-8099

(818) 354-2240

E-mail: iaoffice@jpl.nasa.gov

Refer to NPO-40221, volume and number of this NASA Tech Briefs issue, and the page

## Improved Method of Manufacturing SiC Devices

Several improvements promise to make manufacture of SiC devices more economical.

John H. Glenn Research Center, Cleveland, Ohio

The phrase, "common-layered architecture for semiconductor silicon carbide" ("CLASSiC") denotes a method of batch fabrication of microelectromechanical and semiconductor devices from bulk silicon carbide. CLASSiC is the latest in a series of related methods developed in recent years in continuing efforts to standardize SiC-fabrication

processes. CLASSiC encompasses both institutional and technological innovations that can be exploited separately or in combination to make the manufacture of SiC devices more economical. Examples of such devices are piezoresistive pressure sensors, strain gauges, vibration sensors, and turbulence-intensity sensors for use in harsh environments (e.g., high-temperature, high-pressure, corrosive atmospheres).

The institutional innovation is to manufacture devices for different customers (individuals, companies, and/or other entities) simultaneously in the same batch. This innovation is based on utilization of the capability for fabrication, on the same substrate, of multiple

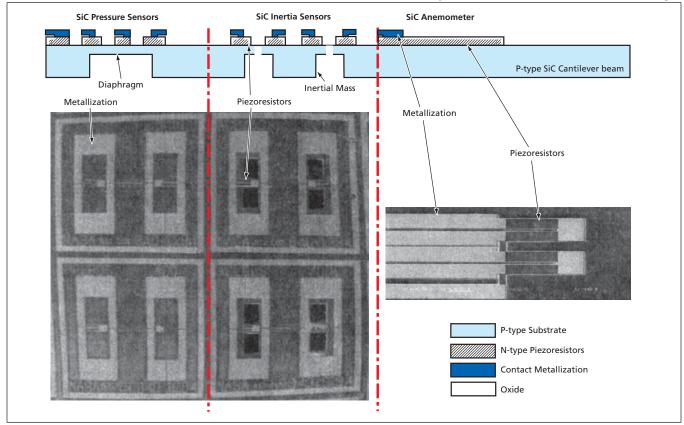

Two Pressure Sensors, Two Accelerometers, and an Anemometer were fabricated on the same SiC substrate to demonstrate the capability for simultaneous batch fabrication of devices that perform different functions. Cross-sectional views of devices are also shown.

SiC devices having different functionalities (see figure). Multiple customers can purchase shares of the area on the same substrate, each customer's share being apportioned according to the customer's production-volume requirement. This makes it possible for multiple customers to share costs in a common foundry, so that the capital equipment cost per customer in the inherently low-volume SiC-product market can be reduced significantly.

One of the technological innovations is a five-mask process that is based on an established set of process design rules. The rules provide for standardization of the fabrication process, yet are flexible enough to enable multiple customers to lay out masks for their portions of the SiC substrate to provide for simultaneous batch fabrication of their various devices. In a related prior method, denoted multi-user fabrication in silicon carbide (MUSiC), the fabrication process is based largely on surface micromachining of poly SiC. However, in MUSiC one cannot exploit the superior sensing, thermomechanical, and electrical properties of single-crystal 6H-SiC or 4H-SiC. As a complement to MUSiC, the CLASSiC five-mask process can be utilized to fabricate multiple devices in bulk single-crystal SiC of any polytype. The five-mask process makes fabrication less complex because it eliminates the need for large-area deposition and removal of sacrificial material.

Other innovations in CLASSiC pertain to selective etching of indium tin oxide and aluminum in connection with multilayer metallization. One major characteristic of bulk micromachined microelectromechanical devices is the presence of three-dimensional (3D) structures. Any 3D recesses that already exist at a given step in a fabrication process usually make it difficult to apply a planar coat of photoresist for metallization and other subsequent process steps. To overcome this difficulty, the CLASSiC process includes a reversal of part of the conventional flow: Metallization is performed before the recesses are etched.

The metallization is followed by the deposition and lift-off of aluminum

and indium tin oxide etch masks on the entire planar SiC substrate surface except where the recesses are to be created. After etching of the recesses, the aluminum and indium tin oxide etch masks are selectively etched to leave a stack of underlying metals (example, titanium, tantalum silicide, and platinum). Thus, the aluminum and indium tin oxide serve as protective layers for the metallization while also functioning as etch masks during deep reactive-ion etching to create the desired 3D structures. After removal of the aluminum and indium tin oxide, wires can be bonded onto the top platinum layer to provide for transition of electrical signals to/from the device.

This work was done by Robert S. Okojie of Glenn Research Center. Further information is contained in a TSP (see page 1).

Inquiries concerning rights for the commercial use of this invention should be addressed to NASA Glenn Research Center, Innovative Partnerships Office, Attn: Steve Fedor, Mail Stop 4–8, 21000 Brookpark Road, Cleveland, Ohio 44135. Refer to LEW-17170.

NASA Tech Briefs, June 2005