NASA/CR-2014-218244

# Formal Methods Case Studies for DO-333

Darren Cofer and Steven P. Miller Rockwell Collins, Inc., Cedar Rapids, Iowa

#### NASA STI Program . . . in Profile

Since its founding, NASA has been dedicated to the advancement of aeronautics and space science. The NASA scientific and technical information (STI) program plays a key part in helping NASA maintain this important role.

The NASA STI program operates under the auspices of the Agency Chief Information Officer. It collects, organizes, provides for archiving, and disseminates NASA's STI. The NASA STI program provides access to the NASA Aeronautics and Space Database and its public interface, the NASA Technical Report Server, thus providing one of the largest collections of aeronautical and space science STI in the world. Results are published in both non-NASA channels and by NASA in the NASA STI Report Series, which includes the following report types:

- TECHNICAL PUBLICATION. Reports of completed research or a major significant phase of research that present the results of NASA Programs and include extensive data or theoretical analysis. Includes compilations of significant scientific and technical data and information deemed to be of continuing reference value. NASA counterpart of peerreviewed formal professional papers, but having less stringent limitations on manuscript length and extent of graphic presentations.

- TECHNICAL MEMORANDUM. Scientific and technical findings that are preliminary or of specialized interest, e.g., quick release reports, working papers, and bibliographies that contain minimal annotation. Does not contain extensive analysis.

- CONTRACTOR REPORT. Scientific and technical findings by NASA-sponsored contractors and grantees.

- CONFERENCE PUBLICATION. Collected papers from scientific and technical conferences, symposia, seminars, or other meetings sponsored or cosponsored by NASA.

- SPECIAL PUBLICATION. Scientific, technical, or historical information from NASA programs, projects, and missions, often concerned with subjects having substantial public interest.

- TECHNICAL TRANSLATION. English-language translations of foreign scientific and technical material pertinent to NASA's mission.

Specialized services also include organizing and publishing research results, distributing specialized research announcements and feeds, providing information desk and personal search support, and enabling data exchange services.

For more information about the NASA STI program, see the following:

- Access the NASA STI program home page at <u>http://www.sti.nasa.gov</u>

- E-mail your question to <u>help@sti.nasa.gov</u>

- Fax your question to the NASA STI Information Desk at 443-757-5803

- Phone the NASA STI Information Desk at 443-757-5802

- Write to: STI Information Desk NASA Center for AeroSpace Information 7115 Standard Drive Hanover, MD 21076-1320

NASA/CR-2014-218244

# Formal Methods Case Studies for DO-333

Darren Cofer and Steven P. Miller Rockwell Collins, Inc., Cedar Rapids, Iowa

National Aeronautics and Space Administration

Langley Research Center Hampton, Virginia 23681-2199 Prepared for Langley Research Center under Contract NNL06AA04B

April 2014

The use of trademarks or names of manufacturers in this report is for accurate reporting and does not constitute an official endorsement, either expressed or implied, of such products or manufacturers by the National Aeronautics and Space Administration.

Available from:

NASA Center for AeroSpace Information 7115 Standard Drive Hanover, MD 21076-1320 443-757-5802

## **Table of Contents**

| Acknow   | ledgements                                                  | . 11 |

|----------|-------------------------------------------------------------|------|

| Abstract |                                                             | . 12 |

| 1        | Introduction                                                | . 13 |

| 2        | Example: Dual-Channel Flight Guidance System                | . 17 |

| 3        | Case Study: Theorem Proving                                 | . 21 |

| 3.1      | Overview of FGS System                                      | . 21 |

| 3.2      | Software Verification Plan                                  | . 23 |

| 3.2.1    | Formal Specification and Verification Tools                 | . 23 |

| 3.2.2    | Life Cycle Data Items                                       | . 23 |

| 3.2.3    | Objectives to Be Satisfied                                  | . 24 |

| 3.2.4    | Tool Qualification Issues                                   | . 28 |

| 3.3      | The Synchronous Pilot Flying Example                        | . 31 |

| 3.3.1    | High-Level Requirements for the Synchronous Bus             | . 31 |

| 3.3.2    | Low-Level Requirements for the Synchronous Bus              | . 35 |

| 3.3.3    | High-level Requirements for the Synchronous FGS Side        | . 37 |

| 3.3.4    | Low-level Requirements for the Synchronous FGS Side         | . 41 |

| 3.3.5    | PVS Specification of the Synchronous Pilot Flying System    | . 45 |

| 3.3.6    | Formal Verification of the Synchronous Pilot Flying Example | . 48 |

| 3.4      | The Asynchronous Pilot Flying Example                       | . 58 |

| 3.4.1    | Specification of the Asynchronous Bus Messages              | . 59 |

| 3.4.2    | High-Level Requirements for the Asynchronous Bus            | . 59 |

| 3.4.3    | Low-Level Requirements for the Asynchronous Bus             | . 60 |

| 3.4.4    | High-Level Requirements for the Asynchronous FGS Side       | . 62 |

| 3.4.5 | Low-Level Requirements for the Asynchronous FGS Side         |  |

|-------|--------------------------------------------------------------|--|

| 3.4.6 | PVS Specification of the Asynchronous Pilot Flying Example   |  |

| 3.4.7 | Formal Verification of the Asynchronous Pilot Flying Example |  |

| 3.5   | The Synchronous Pilot Flying Example in HOL                  |  |

| 3.5.1 | Specification in HOL4 using a Next-State Approach            |  |

| 3.5.2 | Formal Verification of the Next-State Approach in HOL4       |  |

| 3.5.3 | Specification in HOL4 using a Streams Approach               |  |

| 3.5.4 | Formal Verification of the Streams Approach in HOL4          |  |

| 4     | Case Study: Model Checking                                   |  |

| 4.1   | Mode Logic Overview                                          |  |

| 4.2   | Software Verification Plan                                   |  |

| 4.2.1 | Formal Specification and Verification Tools                  |  |

| 4.2.2 | Life Cycle Data Items                                        |  |

| 4.2.3 | Objectives to Be Satisfied                                   |  |

| 4.2.4 | Tool Qualification Issues                                    |  |

| 4.3   | Specification of the Mode Logic                              |  |

| 4.3.1 | Flight Modes                                                 |  |

| 4.3.2 | Event Processing                                             |  |

| 4.4   | Formal Verification of the Mode Logic                        |  |

| 4.4.1 | Heuristics for Writing Formal Properties                     |  |

| 4.4.2 | Verification of the Mode Logic Using the Kind Model Checker  |  |

| 4.4.3 | Verification of the Mode Logic Using MATLAB Design Verifier  |  |

| 5     | Case Study: Abstract Interpretation                          |  |

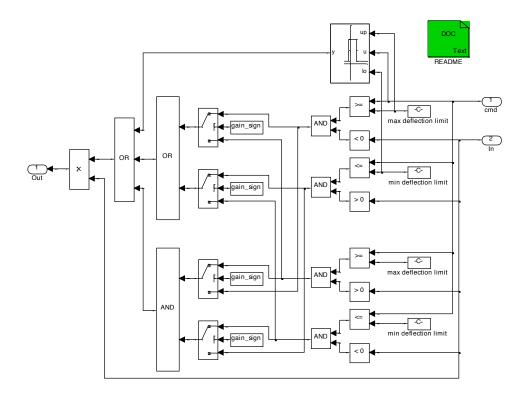

| 5.1   | Overview of the Heading Control Model                        |  |

| 5.1.1    | Head   | ing Control Model and Code                                | 158 |

|----------|--------|-----------------------------------------------------------|-----|

| 5.1.2    | Prope  | erties to Be Checked                                      | 161 |

| 5.2      | Softw  | vare Verification Plan                                    | 162 |

| 5.2.1    | Life ( | Cycle Data Items                                          | 164 |

| 5.2.2    | Objec  | ctives to Be Satisfied                                    | 164 |

| 5.2.3    | Tool   | Qualification Issues                                      | 167 |

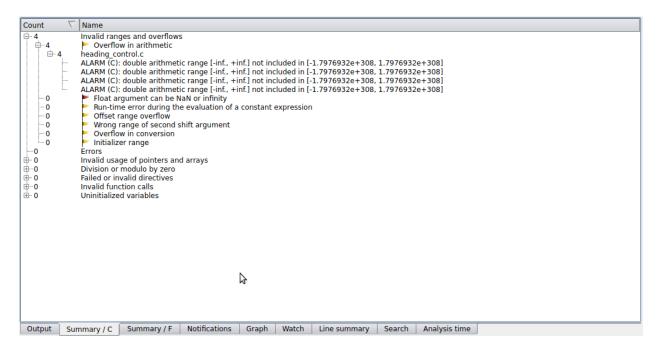

| 5.3      | Analy  | sis of the Heading Control Law Source Code with Astrée    | 167 |

| 5.4      | Analy  | sis of the Heading Control Law Source Code with Polyspace | 169 |

| 6        | Conc   | lusion                                                    | 172 |

| 7        | Refer  | ences                                                     | 173 |

| Appendix | кA     | Acronyms                                                  | 175 |

| Appendix | ĸВ     | Mode Logic Properties                                     | 177 |

| Appendix | с С    | Mode Logic Error Log                                      | 198 |

## Figures

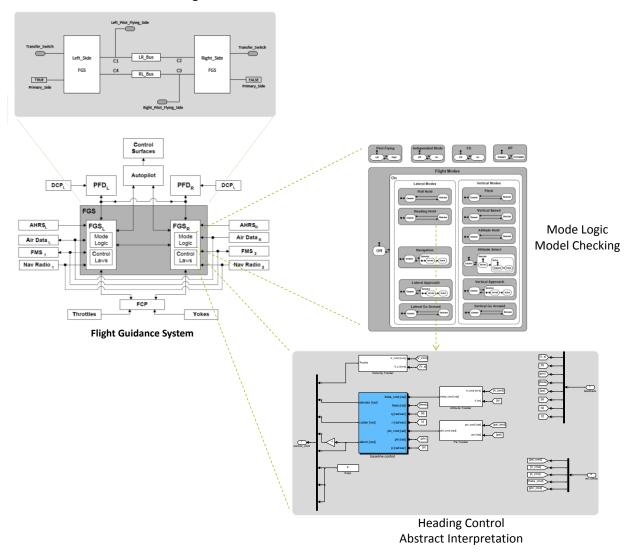

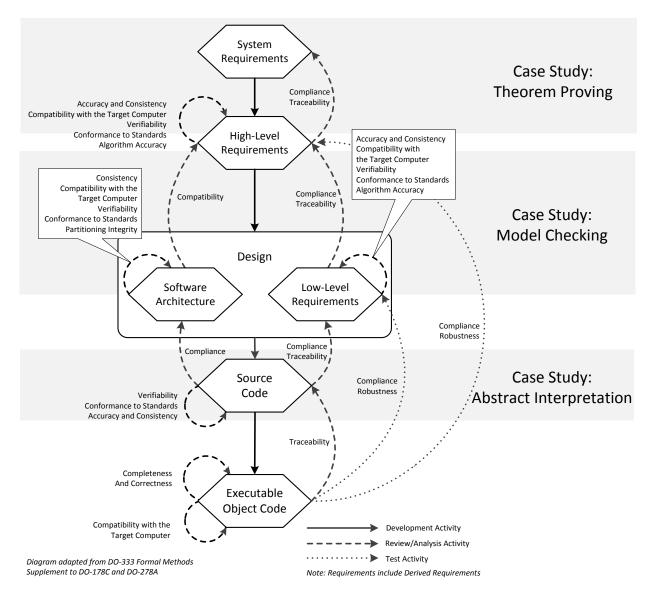

| Figure 1 – Relationship of Elements of the Dual-channel FGS Example            | 14 |

|--------------------------------------------------------------------------------|----|

| Figure 2 – Relationship of Case Studies to DO-178C Objectives                  | 15 |

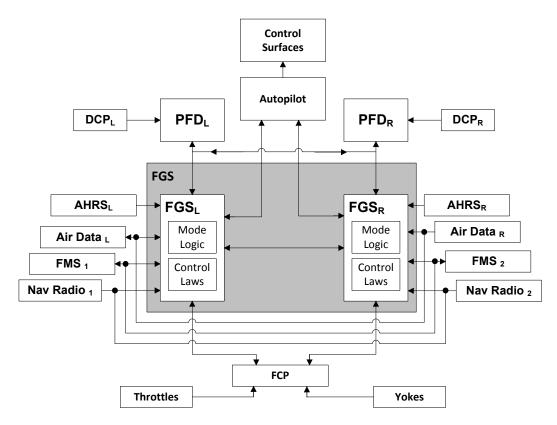

| Figure 3 – Overview of the Flight Guidance System                              | 17 |

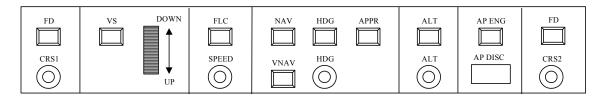

| Figure 4 – Flight Control Panel                                                | 18 |

| Figure 5 – Primary Flight Display                                              | 19 |

| Figure 6 – FGS System Function                                                 |    |

| Figure 7 – Synchronous Pilot Flying System                                     | 31 |

| Figure 8 – High-Level Requirements for the Synchronous Bus                     | 32 |

| Figure 9 – Low-Level Requirements for the Synchronous Bus                      | 35 |

| Figure 10 – Theory Interpretation for Synchronous Bus                          | 36 |

| Figure 11 – TCCs Generated from Theory Interpretation for the Synchronous Bus  | 37 |

| Figure 12 – Synchronous Pilot Flying Side Logic                                | 38 |

| Figure 13 – High-Level Requirements for the Synchronous Side (Part 1)          | 39 |

| Figure 14 – High-Level Requirements for the Synchronous Side (Part 2)          | 40 |

| Figure 15 – Low-Level Requirements for the Synchronous Side (Part 1)           | 42 |

| Figure 16 – Low-Level Requirements for the Synchronous Side (Part 2)           | 43 |

| Figure 17 – Theory Interpretation for the Synchronous Side                     | 44 |

| Figure 18 – PVS Specification of the Synchronous Pilot Flying System (Part 1)  | 45 |

| Figure 19 – PVS Specification of the Synchronous Pilot Flying System (Part 2)  | 46 |

| Figure 20 – Incorrect Statement of Synchronous Requirement R1 in PVS           | 48 |

| Figure 21 – Synchronous Pilot Flying System Requirements (Part 1)              | 49 |

| Figure 22 – Correct Statement of Requirement R1 in PVS                         | 50 |

| Figure 23 – PVS Proof of Synchronous Reachable States Valid Theorem            | 51 |

| Figure 24 – Inductive Sequent for Reachable States                             | 51 |

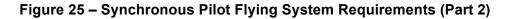

| Figure 25 – Synchronous Pilot Flying System Requirements (Part 2)              | 52 |

| Figure 26 – PVS Proof of Requirement R1 for Synchronous Pilot Flying System    | 53 |

| Figure 27 – PVS Specification of the Pilot Flying System Requirements (Part 3) | 54 |

| Figure 28 – PVS Proof of Requirement R3a/b for Synchronous Pilot Flying System | 55 |

| Figure 29 – Pilot Flying System Requirements 2                                 | 56 |

| Figure 30 – PVS Proof of Switching Transient                                   | 57 |

|                                                                                |    |

| Figure 31 – Asynchronous Pilot Flying System                                    |    |

|---------------------------------------------------------------------------------|----|

| Figure 32 – PVS Specification of a Bus Message                                  | 59 |

| Figure 33 – High-Level Requirements for the Asynchronous Bus                    | 60 |

| Figure 34 – Low-Level Requirements for the Asynchronous Bus                     | 61 |

| Figure 35 – Theory Interpretation for Asynchronous Bus                          |    |

| Figure 36 – Asynchronous Pilot Flying Side Logic                                | 63 |

| Figure 37 – High-Level Requirements for the Asynchronous Side (Part 1)          | 64 |

| Figure 38 – High-Level Requirements for the Asynchronous Side (Part 2)          | 65 |

| Figure 39 – High-Level Requirements for the Asynchronous Side (Part 3)          |    |

| Figure 40 – High-Level Requirements for the Asynchronous Side (Part 4)          | 67 |

| Figure 41 – Low-Level Requirements for the Asynchronous Side (Part 1)           | 68 |

| Figure 42 – Low-Level Requirements for the Asynchronous Side (Part 2)           | 69 |

| Figure 43 – Theory Interpretation for the Asynchronous Side                     |    |

| Figure 44 – PVS Specification of the Asynchronous Pilot Flying Example – Part 1 |    |

| Figure 45 – PVS Specification of the Asynchronous Pilot Flying Example – Part 2 |    |

| Figure 46 – Asynchronous Pilot Flying System Requirements (Part 1)              |    |

| Figure 47 – Asynchronous Pilot Flying System Requirements (Part 2)              | 75 |

| Figure 48 – Asynchronous Pilot Flying System Requirements (Part 3)              |    |

| Figure 49 – Lemmas Added to Side_HLR to Support Theorem Proving                 |    |

| Figure 50 – Grind-use-grind PVS Proof Strategy                                  |    |

| Figure 51 – PVS Proof of Asynchronous Reachable States Valid Theorem            |    |

| Figure 52 – Asynchronous Pilot Flying System Requirements (Part 4)              | 80 |

| Figure 53 – Incorrect Statement of Asynchronous Requirement R3                  | 80 |

| Figure 54 – Asynchronous Pilot Flying System Requirements (Part 5)              | 81 |

| Figure 55 – Incorrect Statement of Asynchronous Requirement R5                  | 82 |

| Figure 56 – Asynchronous Pilot Flying System Requirements (Part 6)              | 83 |

| Figure 57 – Rise and Data Type Definitions                                      | 85 |

| Figure 58 – Initial State Definitions                                           |    |

| Figure 59 – Next State Definitions                                              |    |

| Figure 60 – Valid State Definition                                              |    |

| Figure 61 – Custom Simplification Set sys ss                                    |    |

| Figure 62 – HOL4 Proof that all Reachable States are Valid    |  |

|---------------------------------------------------------------|--|

| Figure 63 – HOL4 Proof that All Valid States Satisfy R1       |  |

| Figure 64 – HOL4 Proof that All Valid States Satisfy R1       |  |

| Figure 65 – Bus Specification with Streams Approach           |  |

| Figure 66 – Two-Delay Bus Specification with Streams Approach |  |

| Figure 67 – 'Rise' Definition with Streams Approach           |  |

| Figure 68 – Alternate 'Rise' Definition with Streams Approach |  |

| Figure 69 – System Specification with Streams Approach        |  |

| Figure 70 – Side Specification with Streams Approach          |  |

| Figure 71 – Final Bus Specification for Streams Approach      |  |

| Figure 72 – Statement of R4 Property                          |  |

| Figure 73 – Statement of R1 Property                          |  |

| Figure 74 – Proof of R4 Property for Streams Approach         |  |

| Figure 75 – Proof of R1 Property for Streams Approach         |  |

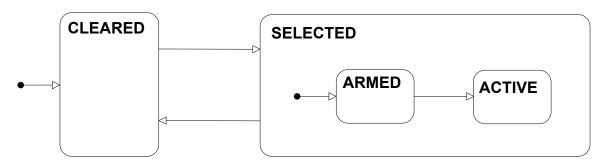

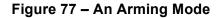

| Figure 76 – A Non-Arming Mode                                 |  |

| Figure 77 – An Arming Mode                                    |  |

| Figure 78 – A Capture/Track Mode                              |  |

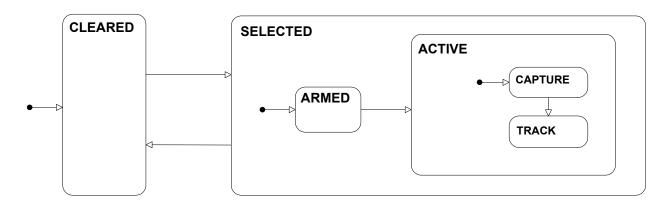

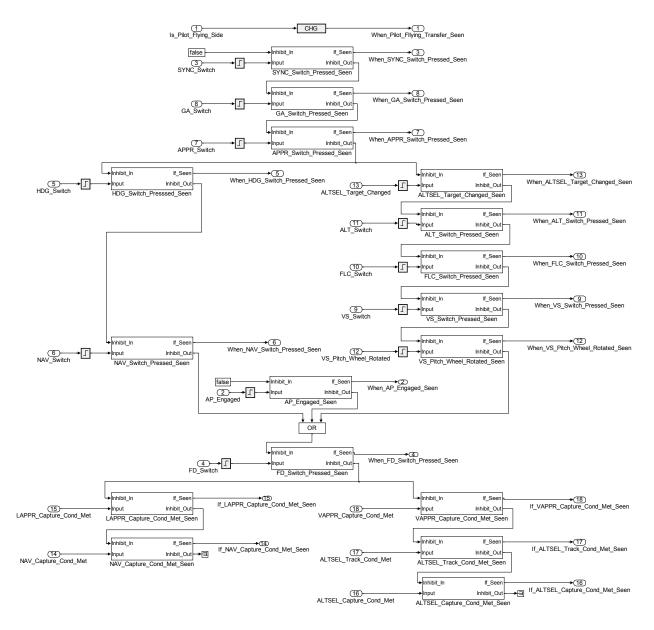

| Figure 79 – Mode Logic Top Level                              |  |

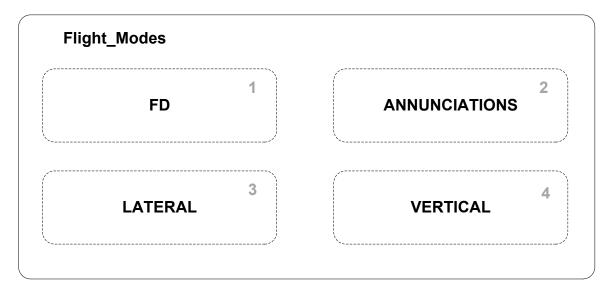

| Figure 80 – Flight Modes Subsystem                            |  |

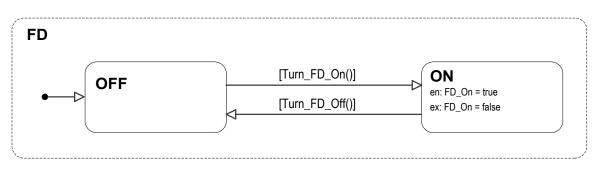

| Figure 81 – FD Mode Logic                                     |  |

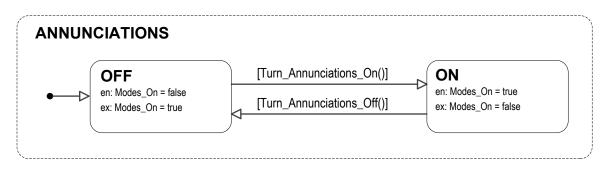

| Figure 82 – ANNUNCIATIONS Mode Logic                          |  |

| Figure 83 – LATERAL Modes                                     |  |

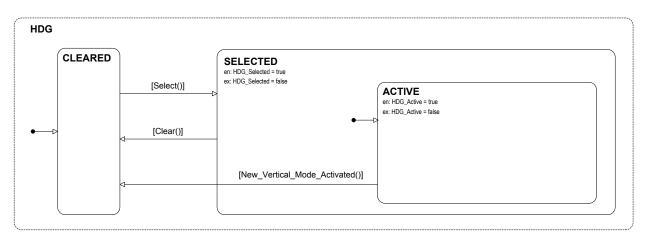

| Figure 84 – Heading Select (HDG) Mode                         |  |

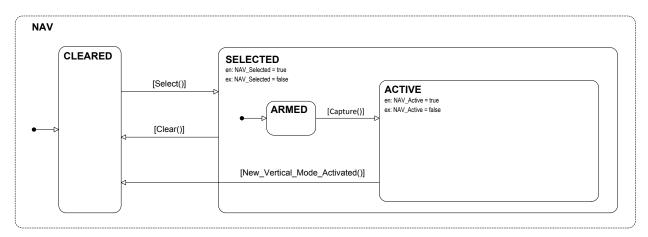

| Figure 85 – Lateral Navigation (NAV) Mode                     |  |

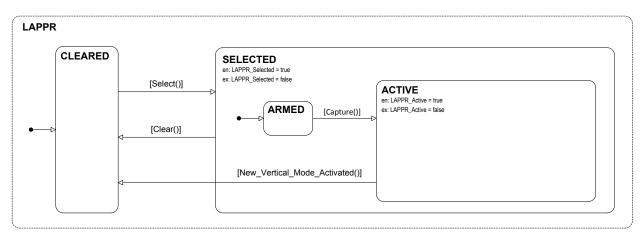

| Figure 86 – Lateral Approach (LAPPR) Mode                     |  |

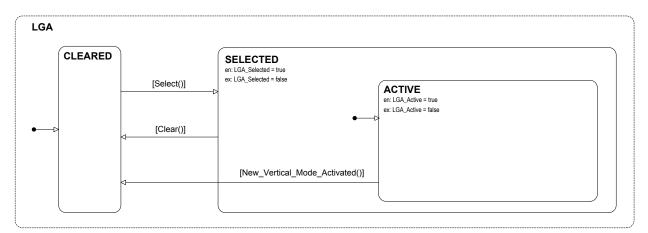

| Figure 87 – Lateral Go Around (LGA) Mode                      |  |

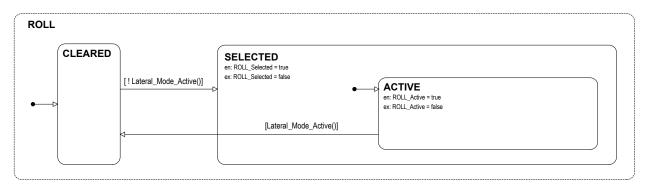

| Figure 88 – Roll Hold (ROLL)                                  |  |

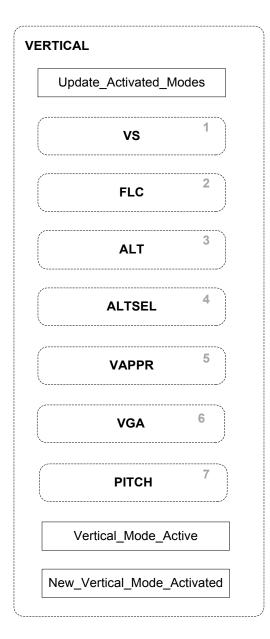

| Figure 89 – VERTICAL Modes                                    |  |

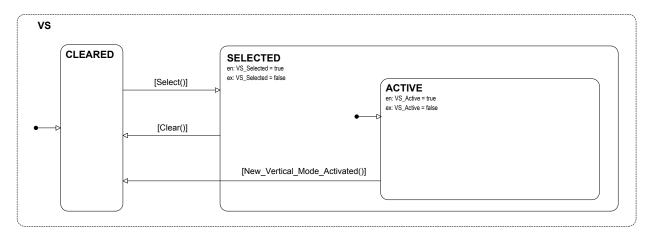

| Figure 90 – Vertical Speed (VS) Mode                          |  |

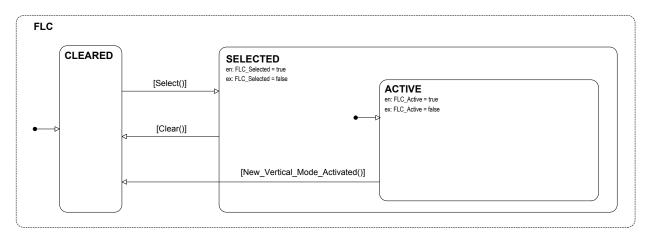

| Figure 91 – Flight Level Change (FLC) Mode                    |  |

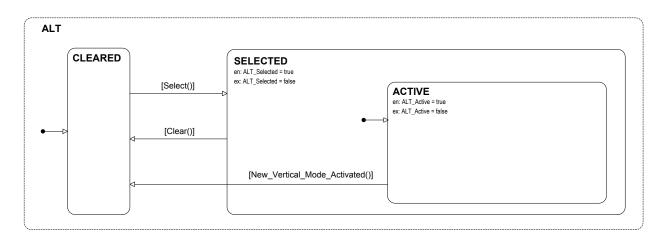

| Figure 92 – Altitude Hold (ALT) Mode                          |  |

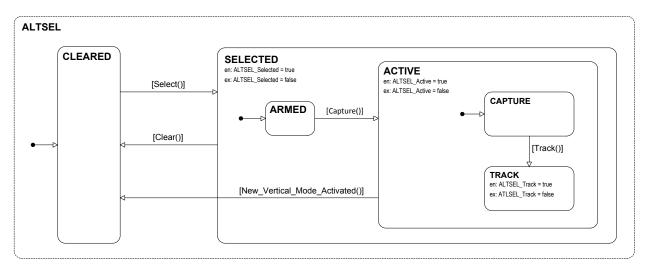

| Figure 93 – Altitude Select (ALTSEL) Mode                                     | . 126 |

|-------------------------------------------------------------------------------|-------|

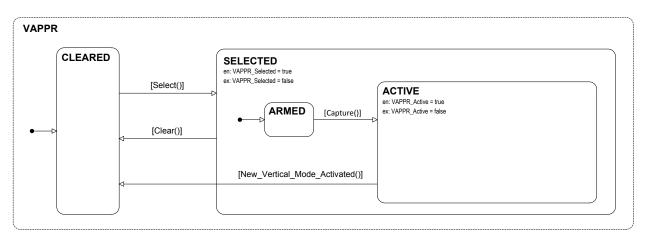

| Figure 94 – Vertical Approach (VAPPR) Mode                                    | . 128 |

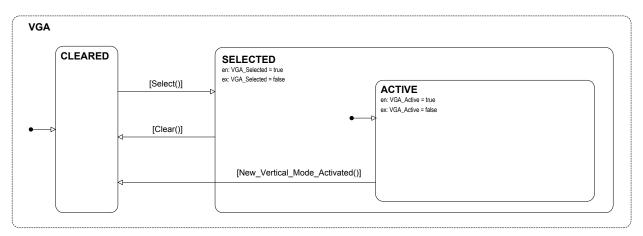

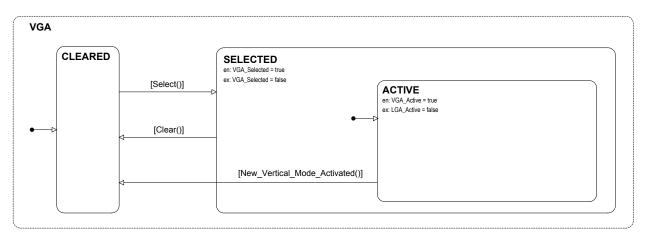

| Figure 95 – Vertical Go Around (VGA) Mode                                     | . 130 |

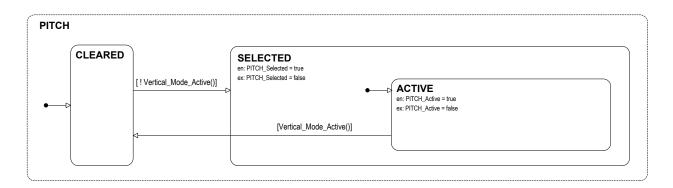

| Figure 96 – Pitch Hold (PITCH) Mode                                           | . 132 |

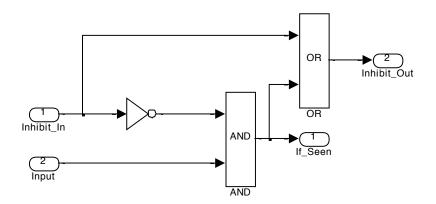

| Figure 97 – Event Processing                                                  | . 133 |

| Figure 98 – Seen Logic                                                        | . 134 |

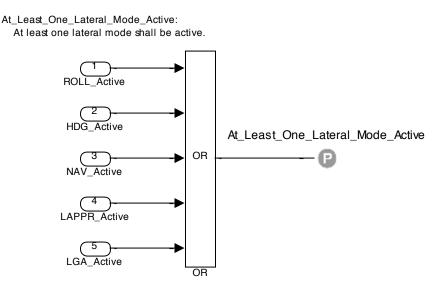

| Figure 99 – At Least One Lateral Mode Active (Lustre)                         | . 138 |

| Figure 100 – Weaker Version of at Least One Lateral Mode Active (Lustre)      | . 139 |

| Figure 101 – At Most One Lateral Mode Active (Lustre)                         | . 140 |

| Figure 102 – VAPPR Active Only If LAPPR Active (Lustre)                       | . 141 |

| Figure 103 – LGA Active If and Only If VGA Active (Lustre)                    | . 141 |

| Figure 104 – Overspeed Implies FLC, ALT, ALTSEL, or PITCH Active (Lustre)     | . 142 |

| Figure 105 – Overspeed and PITCH Transitory (Lustre)                          | . 142 |

| Figure 106 – HDG Switch Pressed Selects HDG (Lustre)                          | . 143 |

| Figure 107 – Definition of RISING (Lustre)                                    | . 143 |

| Figure 108 – HDG Switch Pressed Selects HDG Using Internal Variables (Lustre) | . 144 |

| Figure 109 – No Higher Event Than HDG Switch Pressed (Lustre)                 | . 145 |

| Figure 110 – Functional Requirements for Clearing HDG Mode (Lustre)           | . 145 |

| Figure 111 – Initial Functional Requirements for Activating NAV Mode (Lustre) | . 146 |

| Figure 112 – Correct Functional Requirements for Activating NAV Mode (Lustre) | . 146 |

| Figure 113 – VGA Clear Error                                                  | . 147 |

| Figure 114 –Counterexample for Clearing VGA Error                             | . 148 |

| Figure 115 – Counterexample for FLC Select Error                              | . 150 |

| Figure 116 – ALTSEL Select Error (Lustre)                                     | . 151 |

| Figure 117 – Counterexample for ALTSEL Select Error                           | . 152 |

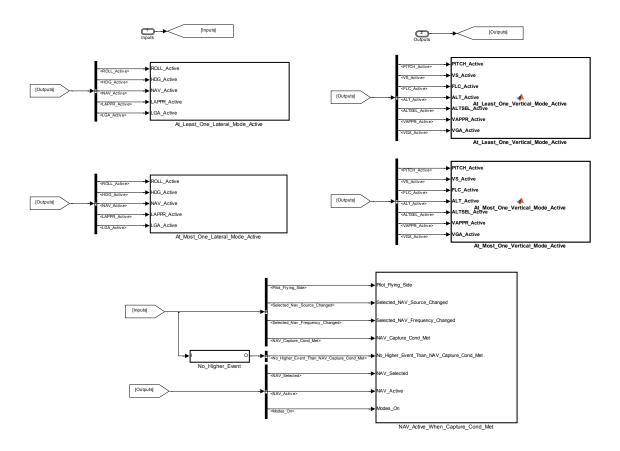

| Figure 118 – At Least One Lateral Mode Active (Design Verifier)               | . 153 |

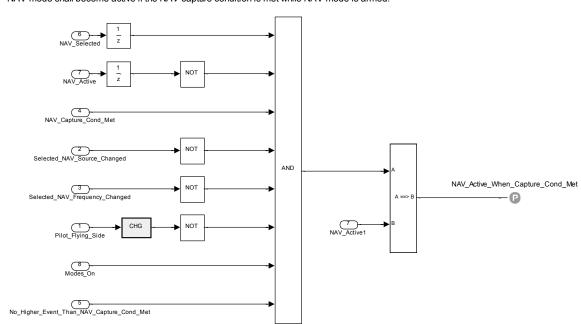

| Figure 119 – NAV Active When Capture Cond Met (Design Verifier)               | . 154 |

| Figure 120 – At Least One Vertical Mode Active (Design Verifier)              | . 154 |

| Figure 121 – Properties Subsystem (Design Verifier)                           | . 155 |

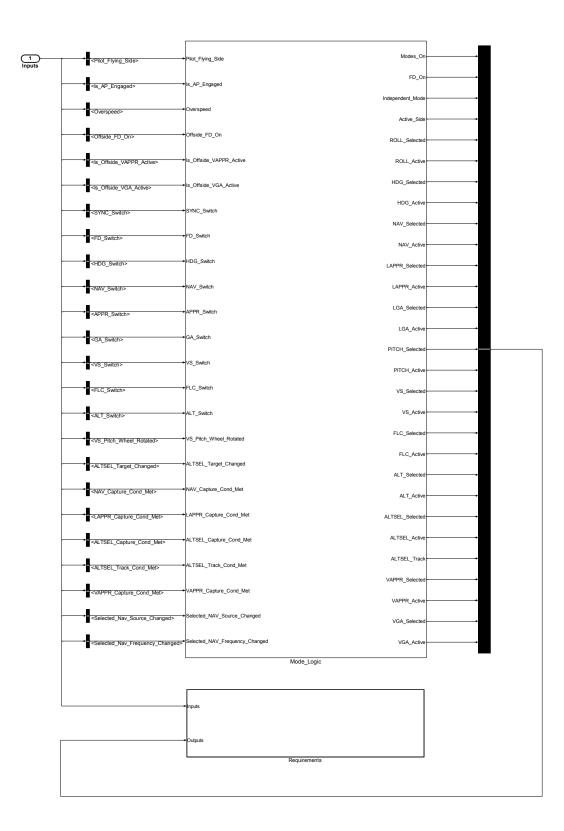

| Figure 122 – Top-Most Model (Design Verifier)                                 | . 157 |

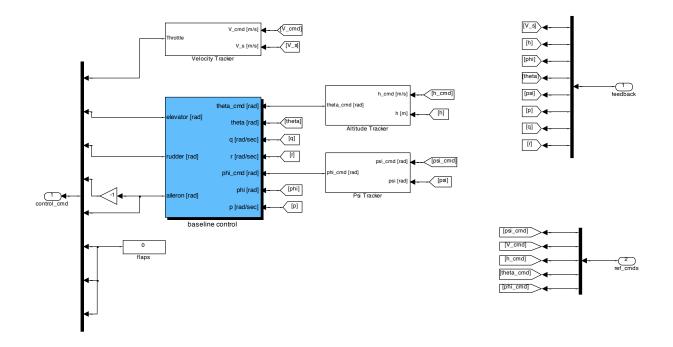

| Figure 123 – Heading Control Law Model                                        | . 159 |

| Figure 124 – Fragment of Autogenerated C Code for Heading Control Model | . 160 |

|-------------------------------------------------------------------------|-------|

| Figure 125 – Astrée Analysis Results                                    | . 168 |

| Figure 126 – Astrée Directives to Define Partitions                     | . 169 |

| Figure 127 – Anti-Windup Logic                                          | . 170 |

## Tables

| Table 1 – Summary of Objectives Satisfied by Theorem Proving |  |

|--------------------------------------------------------------|--|

| Table 2 – Summary of Objectives Satisfied by Model Checking  |  |

| Table 3 – Turn FD On                                         |  |

| Table 4 – Lateral Mode Manually Selected                     |  |

| Table 5 – Vertical Mode Manually Selected                    |  |

| Table 6 – Turn FD Off                                        |  |

| Table 7 – Turn Annunciations On                              |  |

| Table 8 – Turn Annunciations Off                             |  |

| Table 9 – New Lateral Mode Activated                         |  |

| Table 10 – HDG Select                                        |  |

| Table 11 – HDG Clear                                         |  |

| Table 12 – HDG Will Be Activated                             |  |

| Table 13 – NAV Select                                        |  |

| Table 14 – NAV Capture                                       |  |

| Table 15 – NAV Clear                                         |  |

| Table 16 – NAV Will Be Activated                             |  |

| Table 17 – LAPPR Select                                      |  |

| Table 18 – LAPPR Capture                                     |  |

| Table 19 – LAPPR Clear                                       |  |

| Table 20 – LAPPR Will Be Activated                           |  |

| Table 21 – LGA Select                                        |  |

| Table 22 – LGA Clear                                         |  |

| Table 23 – LGA Will Be Activated                             |  |

| Table 24 – Lateral Mode Active                               |  |

| Table 25 – New Vertical Mode Activated                       |  |

| Table 26 – VS Select                                         |  |

| Table 27 – VS Clear                                          |  |

| Table 28 – VS Will Be Activated                              |  |

| Table 29 – FLC Select                                        |  |

| Table 30 – FLC Clear                                         |  |

| Table 31 – FLC Will Be Activated                                      |     |

|-----------------------------------------------------------------------|-----|

| Table 32 – ALT Select                                                 | 125 |

| Table 33 – ALT Clear                                                  | 126 |

| Table 34 – ALT Will Be Activated                                      | 126 |

| Table 35 – ALTSEL Select                                              | 127 |

| Table 36 – ALTSEL Capture                                             | 127 |

| Table 37 – ALTSEL Track                                               | 127 |

| Table 38 – ALTSEL Clear                                               | 128 |

| Table 39 – ALTSEL Will Be Activated                                   | 128 |

| Table 40 – VAPPR Select                                               | 129 |

| Table 41 – VAPPR Capture                                              | 129 |

| Table 42 – VAPPR Clear                                                | 129 |

| Table 43 – VAPPR Will Be Activated                                    |     |

| Table 44 – VGA Select                                                 |     |

| Table 45 – VGA Clear                                                  |     |

| Table 46 – LGA Will Be Activated                                      |     |

| Table 47 – Vertical Mode Active                                       |     |

| Table 48 – FLC Select Error                                           | 149 |

| Table 49 – Summary of Objectives Satisfied by Abstract Interpretation |     |

| Table 50 – Initial Polyspace Analysis Results                         |     |

| Table 51 – Unproven Runtime Checks                                    | 171 |

| Table 52 – Coding Rules Analysis                                      | 171 |

## Acknowledgements

Several individuals contributed to the case studies described in this report. Darren Cofer of Rockwell Collins provided general oversight and developed the sections on meeting DO-333 objectives and tool qualification. Steven P. Miller and Jennifer Davis of Rockwell Collins developed the Pilot Flying theorem proving case study based on PVS with assistance from Konrad Slind, also of Rockwell Collins. Jennifer Davis and Konrad Slind provided the HOL4 version of the Pilot Flying case study. Cesar Munoz of the NASA Langley Research Center provided valuable input regarding tool qualification and soundness for the PVS theorem prover. Sam Owre of SRI International and Mike Whalen of the University of Minnesota provided assistance on the use of PVS.

Steven P. Miller developed the Mode Logic model checking case study based on MATLAB Simulink/Stateflow® and the Kind and MATLAB Design Verifier<sup>TM</sup> model checkers with assistance from Andrew Gacek and Daren Cofer of Rockwell Collins. Cesare Tinelli of the University of Iowa provided valuable input regarding tool qualification and soundness for the Kind model checker.

Michael Dierkes of Rockwell Collins France developed the Heading Control abstract interpretation case study based on Astrée. Sidhartha Battacharyya of Rockwell Collins developed the Polyspace® version of the same case study. Gary Balas of the University of Minnesota provided the Heading Control flight control law.

## Abstract

*RTCA DO-333, Formal Methods Supplement to DO-178C and DO-278A* provides guidance for software developers wishing to use formal methods in the certification of airborne systems and air traffic management systems. The supplement identifies the modifications and additions to DO-178C and DO-278A objectives, activities, and software life cycle data that should be addressed when formal methods are used as part of the software development process. This report presents three case studies describing the use of different classes of formal methods to satisfy certification objectives for a common avionics example – a dual-channel Flight Guidance System. The three case studies illustrate the use of theorem proving, model checking, and abstract interpretation. The material presented is not intended to represent a complete certification effort. Rather, the purpose is to illustrate how formal methods can be used in a realistic avionics software development project, with a focus on the evidence produced that could be used to satisfy the verification objectives found in Section 6 of DO-178C.

## **1** Introduction

*RTCA DO-333, Formal Methods Supplement to DO-178C and DO-278A* [35] provides guidance for software developers wishing to use formal methods in the certification of airborne systems and air traffic management systems. The supplement identifies the modifications and additions to DO-178C [33] objectives, activities, and software life cycle data that should be addressed when formal methods are used as part of the software development process. This includes artifacts that would be expressed using some formal notation and the verification evidence that could be derived from them.

This report presents three case studies describing the use of different classes of formal methods to satisfy DO-178C certification objectives. The material presented is not intended to represent a complete certification effort. Rather, the purpose is to illustrate how formal methods can be used in a realistic avionics software development project, with a focus on the evidence produced that could be used to satisfy the verification objectives found in Section 6 of DO-178C.

The case studies examine different aspects of a common avionics example – a dual-channel Flight Guidance System (FGS) shown in Figure 1. While not intended as a complete example, it is representative of the issues encountered in actual avionics development projects and includes design artifacts specified using PVS, MATLAB Simulink/Stateflow®, and C source code. These files are available for download and use without restriction from the same site where this report is posted. A description of this example is provided in Section 2.

The three case studies illustrate the use of theorem proving, model checking, and abstract interpretation. Each of these techniques has strengths and weaknesses, and each could be applied to different life cycle data items and different objectives than those described here. The purpose here is to illustrate a reasonable application of each of these techniques for satisfying certification objectives.

DO-333 provides general guidance that is applicable to the overall verification process when formal methods are used. This includes requirements for the use of formal notations with unambiguous, mathematically defined syntax and semantics, soundness of the formal analysis methods used, and justification of all assumptions used in each formal analysis. Specific guidance is provided to describe how formal methods can be applied within each of the verification activities and objectives defined in DO-178C. This is illustrated in Figure 2 for

Level A software, the highest criticality level defined in DO-178C. These include compliance with requirements, accuracy and consistency of requirements, compatibility with the target computer, verifiability of requirements, conformance to standards, traceability between life cycle data items, and algorithmic correctness. Some of the objectives do not need to be satisfied for the less critical Level C or Level D software.

Pilot Flying Theorem Proving

Figure 1 – Relationship of Elements of the Dual-channel FGS Example

As shown in Figure 2, theorem proving was applied to the verification of the High-Level Requirements, model-checking was applied to verification of the Low-Level Requirements and Software Architecture, and abstract interpretation was applied to verification of the Source Code.

Figure 2 – Relationship of Case Studies to DO-178C Objectives

Theorem proving was applied to the verification of the High-Level Requirements for the synchronization of the two channels of the FGS, focusing on the objectives of DO-333 Table FM.A-3. Theorem proving is generally considered the most powerful and versatile class of formal methods, but it is also the least automated, and usually requires the significant expertise and user training. This case study is described in Section 3.

Model checking was applied to the verification of the Low-Level Requirements for the mode logic of a single FGS channel, focusing on the objectives of DO-333 Table FM.A-4. Current model checking tools are very powerful and provide much more automation than theorem provers. In general, less user expertise is required, but the user must be able to specify requirements to be analyzed in a formal language. These tools are relatively mature and (in our opinion) the benefits of using formal methods are greatest at this level. This case study is described in Section 4.

Abstract interpretation was applied to the Source Code implementing one of the control laws of the FGS, focusing on the objectives of DO-333 Table FM.A-5. Abstract interpretation is the most automated of the three techniques, at least as used in currently available commercial tools, and typically require the least expertise from users. Part of this is due to the use of abstract interpretation to check non-functional requirements, eliminating the need to formally specify requirements. We should note, however, that more powerful versions of abstract interpretation tools exist which require much more expertise to specify and check user-defined abstract domains. This case study is described in Section 5.

Each case study includes:

- A general description of the portion of the example system to be verified

- A description of the verification approach used, including the life cycle data items produced and the tools used, roughly corresponding to some of the information that should be included in a Software Verification Plan

- The objectives to be satisfied and the evidence produced

- Tool qualification issues relevant for the formal methods tools used

- A detailed description of the verification effort that was performed

As a result of the tools and objectives we have chosen for these case studies, there are some parts of DO-333 that are not covered. In particular, we do not address the verification of Executable Object Code (Table FM.A-6 objectives), nor do we address the replacement of coverage testing by formal analysis (Table FM.A-7 objectives).

## 2 Example: Dual-Channel Flight Guidance System

We will illustrate the use of formal methods to satisfy DO-178C objectives with three case studies built around a common avionics example, a dual-channel Flight Guidance System (FGS). In this chapter, we provide a high level description of the FGS and how it interacts with the other avionics systems and with the flight crew.

An FGS is a component of the overall Flight Control System (FCS). It compares the measured state of an aircraft (position, speed, and attitude) to the desired state and generates pitch and roll guidance commands to minimize the difference between the measured and desired state. An overview of an FCS that emphasizes the role of the FGS is shown in Figure 3.

Figure 3 – Overview of the Flight Guidance System

As shown in Figure 3 the FGS subsystem accepts input about the aircraft's state from the Attitude Heading Reference System (AHRS), the Air Data System (ADS), the Flight Management System (FMS), and the Navigation Radios. Using this information, it computes pitch and roll guidance commands that are provided to the autopilot (AP). When engaged, the

AP translates these commands into movement of the aircraft's control surfaces necessary to achieve the commanded changes about the lateral and vertical axes.

The flight crew interacts with the FGS primarily through the Flight Control Panel (FCP), shown in Figure 4. The FCP includes switches for turning the Flight Director (FD) on and off, switches for selecting the different flight modes such as vertical speed (VS), lateral navigation (NAV), heading select (HDG), altitude hold (ALT), and approach (APPR), the Vertical Speed/Pitch Wheel, and the AP disconnect bar. The FCP also supplies feedback to the crew, indicating selected modes by lighting lamps on either side of a selected mode's button.

#### Figure 4 – Flight Control Panel

A few key controls, such as the Go Around button, the AP Disengage switch, and the SYNC switch are provided on the control yokes and throttles and routed through the FCP to the FGS. Navigation sources are selected through the Display Control Panel (DCP), with the selected navigation source routed through the PFD to the FGS.

As shown in Figure 3, the FGS has two physical sides, or channels, one on the left side and one on the right side of the aircraft. These provide redundant implementations that communicate with each other over a cross-channel bus. Each channel of the FGS can be further broken down into the mode logic and the flight control laws. The flight control laws accept information about the aircraft's current and desired state and compute the pitch and roll guidance commands. A flight control law is active if its guidance commands are being used to control the aircraft or to provide visual cues to the flight crew. A flight control law that is operational but that is not yet active is armed. The mode logic determines which lateral and vertical modes of operation are active (e.g. controlling the aircraft or providing visual guidance cues to the flight crew) and armed (e.g. operational but not yet active) at any given time. These in turn determine which flight control laws are active and armed. These are annunciated, or displayed, on the Primary Flight Displays (PFD) along with a graphical depiction of the flight guidance commands generated by the FGS.

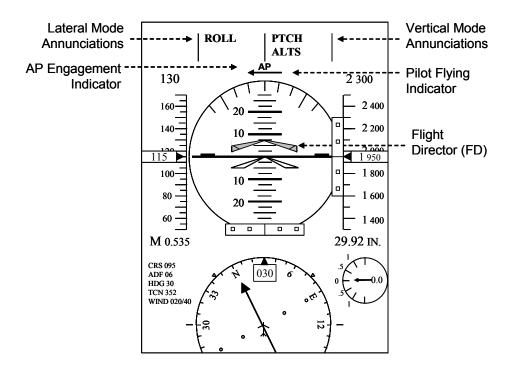

A simplified image of a Primary Flight Display (PFD) is shown in Figure 5. The PFDs display essential information about the aircraft, such as airspeed, vertical speed, attitude, the horizon, and heading. The active lateral and vertical modes are displayed (annunciated) at the top of the display. The annunciations in Figure 5 indicate that the current active lateral mode is Roll Hold (ROLL), the active vertical mode is Pitch Hold (PITCH), and that the Altitude Select (ALTSEL) mode is armed.

Figure 5 – Primary Flight Display

The large sphere in the center of the PFD is the attitude indicator. The horizontal line across its middle is the artificial horizon. The current pitch and roll of the aircraft is indicated by a white wedge representing the aircraft in the middle of the attitude indicator. Figure 5 depicts an aircraft in level flight with zero degrees of roll and zero degrees of pitch.

The graphical presentation of the pitch and roll guidance commands on the PFD are referred to as the Flight Director  $(FD)^1$ . The pitch and roll guidance commands are shown as a grey wedge in the sky/ground ball. When the AP is not engaged, these are interpreted as guidance to the pilot. When the AP is engaged, these indicate the direction the aircraft is being steered by the

<sup>&</sup>lt;sup>1</sup> The term Flight Director is also commonly used to refer to the logic that computes the pitch and roll guidance commands.

AP. Engagement of the AP is indicated by the letters AP displayed directly under the mode annunciations. Figure 5 depicts an aircraft in which the AP is engaged and the FD is commanding the pilot to pitch up 7.5 degrees.

In most flight modes, the FGS operates in *dependent* mode where only one FGS channel is *active* and provides guidance to the FD and the AP. The other side serves as a hot spare and sets its modes to match those of the active side. This is indicated by the Pilot Flying indicator displayed directly below the mode annunciations which points to the pilot flying (active) side. In some of the more critical modes such as Approach, Takeoff, and Go Around, the FGS operates in *independent* mode where both channels are active and independently computing guidance commands that must agree for the AP to be engaged.

## 3 Case Study: Theorem Proving

This section illustrates the use of theorem proving to verify important system properties of the dual-channel FGS. We demonstrate the use of two different interactive theorem proving tools: PVS and HOL4. The majority of the case study is carried out using PVS, and then repeated (on a part of the example) using HOL4 to illustrate the differences in the approaches.

The rest of this section is organized as follows. Section 3.1 provides an overview of the FGS system and the functionality that we will be verifying in this case study. Section 3.2 describes the software verification plan, identifying the life-cycle data items to be produced, the DO-178C objectives to be satisfied, and tool qualification issues. Section 3.3 describes the synchronous example, including how the components are specified in PVS, how the entire system is composed from the components, and how the system requirements are verified. Section 3.4 extends the synchronous example to the asynchronous case by introducing independent clocks for each component and repeats the verification. Finally, Section 3.5 presents an alternative specification and verification of the synchronous example using HOL4.

## 3.1 Overview of FGS System

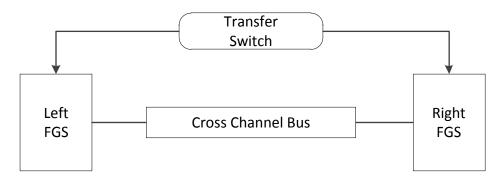

The overall FGS system has two physical sides, or channels, one on the left side and one on the right side of the aircraft. These provide redundant implementations that communicate with each other over a cross-channel bus as shown in Figure 6.

Figure 6 – FGS System Function

Most of the time, the FGS operates in *dependent* mode where only one FGS channel is *active* and provides guidance to the FD and the AP. In this mode, the flight crew can choose whether the left or the right FGS is the active or *pilot flying* side by pressing the Transfer Switch located

above the FCP. The other side serves as a hot spare and sets its modes to agree with those of the active side. In some of the more critical modes such as Approach, Takeoff, and Go Around, the FGS operates in *independent* mode where both channels are active and independently compute guidance commands that must agree for the AP to be engaged, regardless of which side is the current pilot flying side.

In this example, there are five system level requirements related to the synchronization of the pilot flying side. Stated informally, these are:

- R1. At least one side shall be the pilot flying side.

- R2. At most one side shall be the pilot flying side.

- R3. Pressing the Transfer Switch shall always change the pilot flying side.

- R4. The system shall start with the Primary Side as the pilot flying side.

- R5. The system shall not change the pilot flying side unless the Transfer Switch is pressed.

Note that these requirements are system-level requirements that encompass the two sides of the FGS and the cross-channel bus between them.

The overview of Figure 6 provides no indication whether the two FGS execute synchronously or asynchronously. In some designs, such as in a Time-Triggered Architecture (TTA), all components are driven off of a single master clock and execute synchronously. In other architectures, such as Avionics Full-Duplex Switched Ethernet (AFDX), each component is driven by its own local clock and the components execute asynchronously relative to each other.

In this case study we first develop a synchronous design in which all components are driven from single master clock. We develop a set of high-level requirements for each FGS side and the cross-channel bus that are completely free of design detail. Using theorem proving, we show that these high-level requirements are consistent (i.e. do not contradict each other) by proving that there is at least one concrete implementation that satisfies the high-level component requirements. We then show that the system architecture and the high-level requirements are satisfied by the synchronous design instantiated with any components that satisfy the high-level component requirements. We then extend this example to the more complex asynchronous case by introducing independent clocks for each component.

### 3.2 Software Verification Plan

In this case study, we will use theorem proving to verify the outputs of the software requirements process (DO-178C Section 5.1) focusing on the objectives of Table A-3 in DO-178C and Table FM.A-3 in DO-333. The purpose of these verification activities is to detect any errors that may have been introduced during the software requirements process. Specifically, this case study will verify the high-level software requirements for the synchronization of the pilot flying side of the FGS and show that the system architecture, the high-level software requirements, and the high-level hardware requirements comply with the system requirements.

### 3.2.1 Formal Specification and Verification Tools

The PVS formal specification language will be used to specify the system architecture, system requirements, high-level software and hardware requirements of the system components, and candidate low-level software and hardware requirements of the system components. Verification of all formal properties will be performed using the PVS theorem proving system.

#### 3.2.2 Life Cycle Data Items

Life cycle data items are provided for both the synchronous and asynchronous examples using the PVS formal specification language. To facilitate comparison of the two examples, the same names are used for comparable data items in each example.

- **System Architecture** The system architecture is captured in the PVS theory *Pilot\_Flying\_System*. This theory describes how the system components interact in the overall system.

- **System Requirements** The system requirements are stated formally as theorems in the PVS theory *Pilot\_Flying\_System\_Requirements*. Machine checked proofs are developed in PVS to prove that these requirements are satisfied by the system architecture and the high-level requirements for the system components.

- **High-Level Software Requirements** The high-level software requirements are specified for each FGS side in the *Side\_HLR* theory. This theory uses axioms and uninterpreted types, constants, and functions to eliminate design detail from the requirements. The axioms are proven consistent by demonstrating that at least one concrete implementation exists that satisfies the axioms.

- Low-Level Software Requirements Candidate low-level requirements are specified for an FGS side in the *Side\_LLR* theory. This theory uses interpreted types, constants, and functions to define a specification that is consistent-by-construction. The *Side\_Interpretation* theory is used to prove that the low-level requirements comply with (i.e. implement) the high-level requirements, proving that the high-level requirements are consistent.

- **High-Level Hardware Requirements** The high-level hardware requirements are specified for the cross-channel bus in the *Bus\_HLR* theory. This theory uses axioms and uninterpreted types, constants, and functions to eliminate all design detail from the requirements. The axioms are proven consistent by demonstrating that at least one concrete implementation exists that satisfies the axioms.

- Low-Level Hardware Requirements Candidate low-level requirements are specified for the crosschannel bus in the *Bus\_LLR* theory. This theory uses interpreted types, constants, and functions to define a specification that is consistent-by-construction. The *Bus\_Interpretation* theory is used to prove that the low-level requirements comply with (i.e. implement) the high-level requirements, proving that the high-level requirements are consistent.

The low-level requirements for each FGS side and the cross-channel bus exist primarily to prove that the high-level requirements are consistent. While they could be used as the actual low-level requirements for a development, a more likely scenario is that more detailed low-level requirements would be developed and proven to comply with (i.e. implement) the high-level requirements. So long as the more detailed requirements maintain the same interface and are proven to satisfy the high-level requirements, they can be substituted for the low-level requirements without invalidating the verification of the system requirements.

#### 3.2.3 Objectives to Be Satisfied

The DO-178C and DO-333 objectives to be satisfied through theorem proving are summarized in Table 1. Columns A through D in the table indicate for each DO-178C software level whether that objective must be satisfied, and if the objective has been fully or partially satisfied in the case study using formal methods. A more detailed discussion of how each objective is satisfied

is provided in this section. The discussion here is focused on the PVS version of the specification.

| Objective | Description                                                            | Α | В | С | D | Notes                                                                                                                                                                   |

|-----------|------------------------------------------------------------------------|---|---|---|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A-3.1     | High-level requirements<br>comply with system<br>requirements.         | • | • |   | • | Established by proof the system requirements are implemented by the high-level requirements and the system architecture.                                                |

| A-3.2     | High-level requirements are accurate and consistent.                   | • | • | - | • | Accuracy is established by formalization of the high-<br>level requirements. Consistency is established by<br>proving the absence of logical conflicts.                 |

| A-3.3     | High-level requirements are<br>compatible with target<br>computer.     |   |   |   |   | Not addressed                                                                                                                                                           |

| A-3.4     | High-level requirements are verifiable.                                |   |   |   |   | Established by formalizing the requirements and completion of the proof.                                                                                                |

| A-3.5     | High-level requirements conform to standards.                          |   |   |   |   | Partially established by specifying the high-level requirements as formal properties.                                                                                   |

| A-3.6     | High-level requirements are traceable to system requirements.          | • | • | - | • | Established by verification of the system requirements,<br>and by demonstrating the necessity of each high-level<br>requirement for satisfying some system requirement. |

| A-3.7     | Algorithms are accurate.                                               | • | • | • |   | Correctness of the pilot flying selection logic is established by proof.                                                                                                |

| FM.A-3.8  | Formal analysis cases and procedures are correct.                      | • | • | • |   | Established by review.                                                                                                                                                  |

| FM.A-3.9  | Formal analysis results are<br>correct and discrepancies<br>explained. | • | • |   |   | Established by review.                                                                                                                                                  |

| FM.A-3.10 | Requirements formalization is correct.                                 |   |   |   |   | Established by review.                                                                                                                                                  |

| FM.A-3.11 | Formal method is correctly defined, justified, and appropriate.        |   |   |   |   | Established by review.                                                                                                                                                  |

Table 1 – Summary of Objectives Satisfied by Theorem Proving

■ Full credit claimed □ Partial credit claimed

Satisfaction of objective is at applicant's discretion

**Objective A-3.1 – High-level requirements comply with system requirements.** This objective is demonstrated by proving with the PVS theorem prover that the system level requirements specified as theorems in theory *Pilot\_Flying\_System\_Requirements* are implemented by the system architecture defined in theory *Pilot\_Flying\_System*, the high-level software requirements specified as axioms in theory *Side\_HLR* and the high-level hardware requirements specified as axioms in theory *Bus\_HLR*.

**Objective A-3.2 High-level requirements are accurate and consistent.** Accuracy is demonstrated by formalizing the high-level software requirements as axioms in the PVS theory *Side\_HLR*.

Consistency is demonstrated by proving that the concrete implementation defined in *Side\_LLR* implements the axioms of *Side\_HLR*. This is done by mapping in theory *Side\_Interpretation* each uninterpreted type, constant, and function in *Side\_HLR* to its interpreted counterpart in *Side\_LLR* and proving that the axioms of *Side\_HLR* are implemented by *Side\_LLR*.

**Objective A-3.4 High-level requirements are verifiable.** This objective is demonstrated by formalizing the high-level software requirements as axioms in the PVS theory *Side\_HLR* and proving that axioms are satisfied by the concrete implementation defined in *Side\_LLR*.

**Objective A-3.5 High-level requirements conform to standards.** This objective is partially demonstrated by formalizing the high-level software requirements as axioms in the PVS theory *Side\_HLR*, establishing that the requirements conform to the PVS specification language. Additional standards, such as naming standards or the presence of comments providing rationale for the requirement, are verified by review.

**Objective A-3.6 High-level requirements are traceable to system requirements.** This objective is demonstrated by the proof that the high-level requirements comply with the system requirements (objective A-3.1) and by commenting out the high-level requirements one at a time and showing that the proof of the system requirements fail without each high-level requirement.

**Objective A-3.7 Algorithms are accurate.** This objective is demonstrated by proving that the system-level requirements specified in theory *Pilot\_Flying\_System\_Requirements* are implemented by the system architecture specified in the theory *Pilot\_Flying\_System* when instantiated with the high-level requirements specified in theory *Side\_HLR* and *Bus\_HLR*.

**Objective FM.A-3.8 Formal analysis cases and procedures are correct.** This objective is met through review to ensure that the analyses and procedures satisfy the objectives A-3.1 through A-3.7 for which credit is claimed. The soundness of the proofs is ensured by the PVS verification system once the consistency of all axioms is verified and all types are shown to be non-empty. The remaining reviews consist of validating any assumptions. This includes:

- Confirming that the resolution of cyclic dependencies in the theory *Pilot\_Flying\_System* is correct and can be implemented.

- Confirming that the addition of asynchronous clocks conservatively models the behavior of the asynchronous system.

• Confirming that assumption that the Transfer Switch is observed by both sides in the same step is acceptable.

**Objective FM.A-3.9 Formal analysis results are correct and discrepancies explained.** This objective is met through review to ensure that all theorems or lemmas are proven. The PVS verification system will identify any proofs that cannot be completed or that depend on a proof that cannot be completed. Many of the properties had to be revised before they could be proved. Typically, these were due to omissions in the original requirements or oversights introduced by the informality of textual requirements. For example, the requirement R2 "*At most one side shall be the pilot flying side*" had to be changed to "*At most one side shall be the pilot flying side except while the system is switching sides.*" Each such discrepancy was explained and fed back into the safety assessment process for review.

**Objective FM.A-3.10 Requirements formalization is correct.** This objective is met through review to ensure that the formal statement of a requirement is a conservative representation of the informal requirement.

**Objective FM.A-3.11 Formal method is correctly defined, justified, and appropriate.** This objective is met through a review to ensure:

- a. All notations used for formal analysis are verified to have precise, unambiguous, mathematically defined syntax and semantics. Only the PVS language was used which provides a formal syntax and semantics.

- b. The soundness of each formal analysis method is normally demonstrated by citing research papers that discuss the soundness of the method(s) implemented in a given tool. In the case of PVS, it may be necessary to restrict the use of certain proof strategies for which evidence of soundness is not available. At a minimum, it must be shown that all axioms are consistent and all types are non-empty. Soundness of both PVS and HOL4 is discussed further in the next section in the context of tool qualification.

- c. Assumptions related to each formal analysis are described and justified. The one assumption described above that both sides observe the Transfer Switch in the same step is shown to be acceptable since only the *pilot not flying* side listens for the Transfer Switch. Since this example contains only Boolean and enumerated types and no other

relationships are assumed about its inputs, no assumptions related to the formal analysis (e.g., approximating floating-point numbers as reals) were necessary.

### 3.2.4 Tool Qualification Issues

Tool qualification is the process necessary to obtain certification credit for the use of a software tool within the context of a specific airborne system. It is likely that any formal methods tool used for verification as described in DO-333 will require qualification.

According to DO-178C, qualification of a tool is needed when:

- 1. DO-178C processes are eliminated, reduced, or automated through the use of the tool, and

- 2. The output of the tool is used without being verified.

The purpose of qualification is to ensure that the tool provides confidence at least equivalent to that of the process which is eliminated, reduced, or automated.

DO-178C specifies that tool qualification should be performed in accordance with *DO-330*, *Software Tool Qualification Considerations* [34]. DO-330 specifies five different Tool Qualification Levels (TQLs) that define what activities must be performed to qualify a particular software tool. DO-178C, in turn defines three criteria to determine to determine which TQL should apply to a particular tool in a given context.

Criteria 1: A tool whose output is part of the airborne software and thus could insert an error.

**Criteria 2:** A tool that automates verification processes and thus could fail to detect an error, *and* whose output is used to justify the elimination or reduction of either verification processes *other than* those automated by the tool, or development processes that could have an impact on the airborne software.

**Criteria 3:** A tool that, within the scope of its intended use, could fail to detect an error (in other words, a tool that automates verification processes).

Once the criteria are applied, DO-178C provides a table in section 12.2.2 to map software level and qualification criteria to the required TQL. For the certification objectives and tool use that we are considering in this case study, Criteria 3 applies. This means that for all airborne

software levels the theorem provers would need to be qualified to TQL-5 (if their results are not independently checked).

Depending on the tool, qualification of a theorem prover may be a difficult task. Even at the lowest qualification level (TQL-5) there are a number of development artifacts that must be produced as part of the qualification process. The largest part of the effort is focused on defining operational requirements for the tool (what the tool claims to do – the processes eliminated, reduced, or automated), and then developing a comprehensive test suite to show that those requirements are satisfied over an appropriate range of tool inputs.

An alternative approach is to avoid the need to qualify the theorem prover itself by providing an independent check of the proof it produces. This may be more or less feasible depending on the nature of the proof artifacts generated by a particular theorem prover.

The PVS proof engine is built from a small set of primitive inference steps. Most of the inference steps are small, but a few involve deep combinations of decision procedures and rewriting. Larger proof strategies can be defined using the primitive ones. Several external proof tools for Binary Decision Diagram (BDD)-based simplification and model checking, monadic second-order reasoning, nonlinear arithmetic, and predicate abstraction have been added to PVS.

PVS is based on a classical strongly-typed higher-order logic and the theorem prover itself is a based on a sequent calculus for this logic. Standard references for the PVS language are [29], [30], [31] and [32]. However, not all aspects of the language are described. For example, the formal semantics of recursive functions and their termination is not described. This would likely present some challenges to qualification and the requirement to demonstrate soundness of the analysis method.

Unlike Isabelle/HOL or Coq, PVS does not normally emit a proof that could be checked by a separate (qualified) proof checking tool, though this option is available. We have expanded one of our proofs down to the primitive proof rules to demonstrate that this is feasible. Depending upon the nature of the proof rules used, this expansion could in principle be independently checked by a separate tool. However, we are not aware of this having been done in practice and development of an appropriate independent checker for PVS is still a research topic.

Extant implementations of HOL follow the so-called "LCF approach" to designing theorem provers. This methodology implements the logic by a small trusted kernel, which encapsulates just the primitive inference rules, axioms, and definition mechanisms of the logic. The logic kernel is an abstract data type, having the property that the only way a theorem can be obtained is ultimately by making primitive inference steps, which are very close in granularity to those in the mathematical definition of the logic. For example, the introduction and elimination rules for the logical connectives constitute the bulk of the implementation of the HOL4 kernel, and these are very simple to implement. In contrast, basic inference steps in systems like PVS tend to be much larger, amounting to invocation of complex combinations of simplifiers and powerful decision procedures.

As a consequence, it is straightforward to instrument HOL kernels so that they produce formal proofs. This has been done in a variety of research projects [28], [15]. Programs that check the correctness of such proofs are small and relatively easy to verify.

Another approach to theorem prover correctness is to verify the kernel once and for all. This has been done for the implementations of the primitive inferences of HOL Light, with respect to an abstract, set-theoretic specification of the logic.

A more extensive overview of the issues for PVS and HOL4, as well as other popular theorem proving environments, can be found in the summary document for the "Trusted Extensions of Interactive Theorem Provers" workshop [36].

## 3.3 The Synchronous Pilot Flying Example

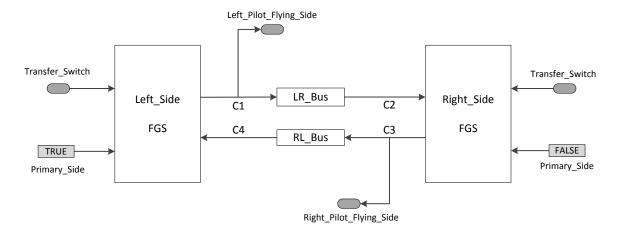

The synchronous Pilot Flying example consists of four main components, the *Left\_Side* FGS, the *Right Side* FGS, an *LR Bus* and an *RL Bus* connecting the two sides as shown in Figure 7.

Figure 7 – Synchronous Pilot Flying System

All four components are assumed to be driven by the same master clock and to execute synchronously. Each FGS produces a *Pilot\_Flying\_Side* Boolean output indicating if it believes itself to be the current pilot flying side. The two buses pass the value produced by one side to the other side, introducing a one-step delay in the process. Each FGS accepts as inputs a Boolean value representing the current value of the *Transfer\_Switch*<sup>2</sup> and the *Pilot\_Flying\_Side* value passed across the bus from the other side. Each FGS also accepts a single Boolean constant indicating if it is the *Primary\_Side* that is to be the initial pilot flying side. The constant for the *Left\_Side* is set to true to make it the initial pilot flying side while the input to the *Right\_Side* is set to false. The intermediate connections C1, C2, C3, and C4 are also labeled on the diagram to facilitate discussion of the formal specification and the proofs.

### 3.3.1 High-Level Requirements for the Synchronous Bus

Each bus in the synchronous Pilot Flying example transfers its input to its output with a one-step delay. The PVS theory specifying this behavior is shown in Figure 8.

$<sup>^{2}</sup>$  Note that there is an implied assumption in this model that the *Transfer Switch* arrives at both sides on the same step. The subsequent discussion shows that this assumption can be safely made since only the pilot not flying side listens for the *Transfer Switch* and no more than one side is ever *the pilot not flying side*.

```

Bus HLR[Init: bool]: THEORY

BEGIN

% State defined as an uninterpreted, non-empty type

8-

State: TYPE+

Initial State: State

% Next state defined as an uninterpreted function

8-

next state: [State, bool -> State]

% Output of the bus

output: [State -> bool]

% High level requirements

HLR1: AXIOM

output(Initial_State) = Init

HLR2: AXIOM

forall (s: State, i: bool) :

output(next_state(s, i)) = i

END Bus HLR

```

#### Figure 8 – High-Level Requirements for the Synchronous Bus

Since the bus introduces a one-step delay in conveying its inputs to its outputs, the initial output value of the bus must be specified. This is done by parameterizing the theory with the *Init* Boolean value. To be able to compose all the components of the Pilot Flying System in a consistent fashion, we adopt the convention of defining a *State* type for each component representing its internal state. Since we want the high-level requirements to be as free of design decisions as possible, we define the type *State* for the synchronous bus to be an uninterpreted type that provides no information about how the state is implemented. Since an empty type can lead to an unsound proof system, we do specify that the type must have at least one value by defining it to PVS as a TYPE+. We also define an uninterpreted constant *Initial\_State* to be an element of this type. As its name implies, *Initial\_State* will represent the initial state of the bus at start-up.

While the type of the internal state of a component can be defined in PVS, PVS does not provide a mechanism for persisting state as might be done in an object-oriented system. Instead, the current state is passed in as an argument of each function that manipulates it. We adopt the convention of defining for each component a *next\_state* function that compute the component's next state from its current state and its inputs and an *output* function that returns the outputs of the component from its current state. For the synchronous bus, the *next\_state* function takes a state *s* of the bus and a Boolean *input*, and returns the next internal state of the bus. The *output* function takes a state *s* and returns a Boolean value.

The high-level requirements for the synchronous bus are specified as two PVS axioms. The first requirement, HLR1, simply states that the *output* of the *Initial\_State* is the Boolean value *Init* specified as the theory parameter. The second requirement, HLR2, states that the output of the *next\_state* of any state *s* and any input *i* is *i*.

These axioms were defined through use of a well-known heuristic for writing axiomatic, or declarative, specifications. We first identify all *constructors* that generate new values of the type *State* and all *extractors* that extract values from elements of the type *State*. For the synchronous bus, the constructors are *Initial\_State* and *next\_state* and the only extractor is *output*. We then write one or more axioms that describe the result of applying each extractor to each constructor. For the synchronous bus, this results in the two axioms shown in Figure 8.

Writing requirements as axioms allows us to specify the required behavior of a component without committing to a specific design or implementation. Note that these axioms only specify the functionality of a component. In particular, we have not stated whether they are system, software, or hardware requirements. They could be viewed as the high-level functional system requirements for the bus. If the bus is to be implemented primarily in software, they could also be used as the high-level functional software requirements. If the bus is to be implemented primarily in hardware, they could be used as the high-level functional hardware requirements. Such axiomatic or declarative specifications are formal versions of the informal "shall" statements typically written in requirements documents. In fact, they share two common concerns with such requirements, *completeness* and *consistency*.

Completeness refers to whether the axioms (requirements) fully specify what needs to be built. We address this issue in two ways. First, we used the heuristic described earlier to define the effect of each extractor on each constructor, giving us a systematic way of developing the axioms. More importantly, we prove in Section 3.3.6 that the requirements for the overall Pilot Flying system will be satisfied using any bus that satisfies these axioms, showing that the axioms are sufficiently complete to ensure the required system behavior.

Consistency refers to whether the axioms contradict each other. In an informal development process, inconsistent requirements are typically discovered during development when it becomes apparent that the specified system cannot be built. In the same way, inconsistent axioms cannot be implemented. Even worse, inconsistent axioms introduce unsoundness into a proof system allowing false theorems to be proven. For this reason, whenever axioms are used in a specification, it is important to prove that they are consistent. The standard way of doing this is to demonstrate that an implementation exists that satisfies all the axioms. In the next section, we define a set of low-level requirements for the bus that are consistent by construction and prove that the implementation satisfies the high-level axioms.

# 3.3.2 Low-Level Requirements for the Synchronous Bus

A PVS theory for an implementation of the synchronous bus is shown in Figure 9.

```

Bus_LLR[Init:bool]: THEORY

BEGIN

%

Define the bus state and initial state

%

State: TYPE = bool

Initial_State: State = Init

%

%

next_state function

%

next_state(s: State, i: bool): State = i

%

%

Output of the bus

%

output(s: State): bool = s

END Bus_LLR

```

## Figure 9 – Low-Level Requirements for the Synchronous Bus

As with the high-level requirements, the theory is parameterized with the initial output value of the bus. We also introduce a type *State* and a constant *Initial\_State* of that type. However, this time we give each of these a concrete interpretation. We define the *State* of the bus to be of type Boolean and we assign the theory parameter *Init* to be the value of *Initial\_State*. We also provide a concrete interpretation for each function. We define the *next\_state* function to return the value of its input *i* and we define the *output* of the bus to be its current state *s*.

Note that this specification does not include any axioms. It is constructed using only the base types of PVS and functions. The PVS type system will ensure that such a *constructive* specification is consistent by generating type-correctness conditions (TCCs) that must be proven using the PVS theorem prover.

This specification is notable in that is actually shorter than the high-level bus requirements. However, it is also more concrete in that it makes the design decision to represent the state of the channel as a single Boolean variable. We could have also chosen to implement the bus using an integer rather than a Boolean or using a queue of size one providing the constructor and extractor functions were defined appropriately. So long as an implementation provides the same types, constants, and functions and satisfies the two axioms of the high-level requirements of Figure 8, it would be an acceptable implementation of the synchronous bus.

To prove that the low-level bus requirements of Figure 9 implement, or comply with, the highlevel bus requirements of Figure 8, we use the theory interpretation capability of PVS. This is shown in Figure 10. The *Bus\_Interpretation* theory first imports the *Bus\_LLR* theory using the same Boolean theory parameter, *Init*. It then imports the *Bus\_HLR* theory, but provides an interpretation for each uninterpreted type, constant, and function based on the *Bus\_LLR* specification. For example, it defines the *State* type of the *Bus\_HLR* theory to be the *State* type of the *Bus\_LLR* theory. In fact, it defines each uninterpreted type, constant and function in *Bus\_HLR* to be the corresponding type, constant, or function in *Bus\_LLR*. When this theory is typechecked using PVS, it generates the two TCCs shown in Figure 11.

```

Bus Interpretation[Init : bool] : THEORY

BEGIN

8.

% Import low-level requirements (LLR) for a bus

IMPORTING Bus_LLR[Init]

% Import high-level (HLR) requirements for a bus and

% define the LLR as an interpretation of the HLR

IMPORTING Bus_HLR[Init] {{

State

:= Bus_LLR.State,

Initial State := Bus LLR.Initial State,

next state := Bus LLR.next state,

:= Bus LLR.output

output

}}

END Bus Interpretation

```

### Figure 10 – Theory Interpretation for Synchronous Bus

A careful examination of these TCCs reveals that they are the axioms of the *Bus\_HLR* theory instantiated with the types, constants, and functions defined in the *Bus\_LLR* theory. These TCCs can easily be proved using the *typecheck-prove* (M-x tcp) command of PVS, proving that the *Bus\_LLR* theory implements the axioms of the *Bus\_HLR* theory.

```

% Mapped-axiom TCC generated (at line 14, column 12) for

% Bus HLR[Init]

{{ State := Bus_LLR.State,

옹

Initial State := Bus LLR.Initial State,

옹

웅

next state := Bus LLR.next state,

å

output := Bus LLR.output }}

% proved - complete

IMP Bus HLR HLR1 TCC1: OBLIGATION

Bus LLR[Init].output(Bus LLR[Init].Initial State) = Init;

% Mapped-axiom TCC generated (at line 14, column 12) for

% Bus_HLR[Init]

{{ State := Bus LLR.State,

å

Initial State := Bus LLR.Initial State,

8

웅

next state := Bus LLR.next state,

옹

output := Bus LLR.output }}

% proved - complete

IMP Bus HLR HLR2 TCC1: OBLIGATION

FORALL (s: State[Init], i: bool):

Bus LLR[Init].output(Bus LLR[Init].next state(s, i)) = i;

```

### Figure 11 – TCCs Generated from Theory Interpretation for the Synchronous Bus

In this way, we have shown that at least one concrete implementation of the *Bus\_HLR* theory exists and that the axioms of the *Bus\_HLR* are consistent, allowing us to safely use it as the high-level functional requirements for the synchronous bus. The *Bus\_LLR* theory can be used as the low-level requirements for the bus or a more detailed set of low-level requirements can be developed and proven to implement the high-level requirements.

## 3.3.3 High-level Requirements for the Synchronous FGS Side

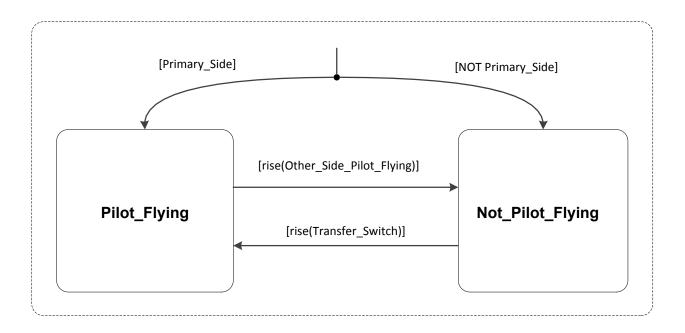

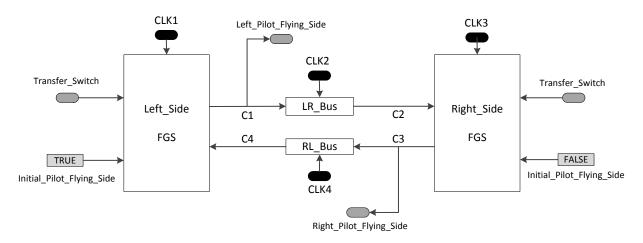

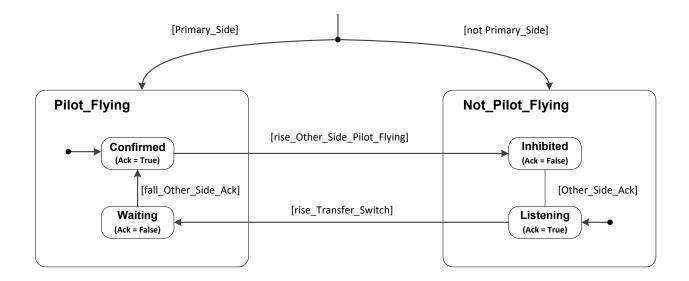

In this section we develop the high-level requirements for the synchronous FGS side just as we did for the synchronous bus. For the synchronous system, each side executes the simple state machine shown in Figure 12 to determine which side is the current pilot flying side.

Figure 12 – Synchronous Pilot Flying Side Logic

If a side believes itself to be the *Not\_Pilot\_Flying* side, it will become the *Pilot\_Flying* side when it sees the *Transfer\_Switch* pressed (i.e. a rising edge). If a side is the *Pilot\_Flying* side, it will become the *Not\_Pilot\_Flying* side when it sees the other side become the pilot flying side. Thus, it is always the *Not\_Pilot\_Flying* side that responds to the Transfer Switch, and the current *Pilot\_Flying* side always yields when it sees the other side become the *Pilot\_Flying* side. The PVS specification of the high-level requirements for a synchronous FGS side is shown in Figure 13 and Figure 14.

The theory is parameterized with whether this side is the *Primary\_Side*. Just as with the bus, we introduce an uninterpreted *State* type, an uninterpreted *Initial\_State* constant and an uninterpreted *next\_state* function. Since each side needs to be able to observe a rising edge of the *Transfer\_Switch* and of the other side's *Pilot\_Flying* value, each side saves the previous value of the *Transfer\_Switch* and the other side's *Pilot\_Flying* value passed across the bus.

```

Side HLR[Primary Side : bool] : THEORY

BEGIN

% State defined as an uninterpreted, non-empty type

8-

State: TYPE+

Initial State: State

% Next state defined as an uninterpreted function

8-

next state: [State, bool, bool -> State]

% Extractor functions for this side

8-

pre TS : [State -> bool]

pre OSPF : [State -> bool]

% Pilot flying output for this side

pilot flying : [State -> bool]

% Auxiliary definitions for stating axioms

8

rise ospf(s:State, ospf:bool) : bool = NOT pre OSPF(s) AND ospf

rise ts (s:State, ts :bool) : bool = NOT pre_TS (s) AND ts

```