# VLBI Digital-Backend Intercomparison Test Report

Alan Whitney, Christopher Beaudoin, Roger Cappallo, Arthur Niell, Bill Petrachenko, Chester A. Ruszczyk, Mike Titus

#### Abstract

Issues related to digital-backend (DBE) systems can be difficult to evaluate in either local tests or actual VLBI experiments. The 2nd DBE intercomparison workshop at Haystack Observatory on 25-26 October 2012 provided a forum to explicitly address validation and interoperability issues among independent global developers of DBE equipment. This special report discusses the workshop. It identifies DBE systems that were tested at the workshop, describes the test objectives and procedures, and reports and discusses the results of the testing.

### 1. Introduction

As VLBI expands the scope of digital signal-processing in VLBI systems, it is important that each sub-system be validated for proper function and interoperability. While every VLBI developer strives to ensure that these criteria are met, it is often only by comparison that problems can be uncovered. One area of particular interest is digital-backend (DBE) systems, where some issues are difficult to evaluate in either local tests or actual VLBI experiments. The 2nd DBE intercomparison workshop at Haystack Observatory on 25-26 October 2012 provided a forum to explicitly address validation and interoperability issues among independent global developers of DBE equipment, and it built on the work of the first such workshop held at Haystack Observatory in May 2009. The 2012 workshop took advantage of the completion of a new Instrumentation Lab at Haystack Observatory that provided the space and signal connections needed to efficiently support the comparison exercise.

#### 2. The DBE Systems

Five systems were assembled at Haystack for testing<sup>1</sup>:

- 1. The European 'DBBC' system, configured as a polyphase filter bank (PFB) converter<sup>2</sup>, hereafter referred to as 'DBBC-PFB'.

- 2. The Chinese VLBI Data Acquisition System (CDAS) configured as 16 tunable DDCs, hereafter referred to as 'CDAS-DDC'.

- 3. The CDAS with polyphase filter-bank signal processing, hereafter referred to as 'CDAS-PFB'. The CDAS-PFB is a separate hardware unit from the CDAS-DDC.

- 4. The Japanese 'ADS3000+' system configured with 16 tunable DDC processors.

<sup>&</sup>lt;sup>1</sup>The DBBC was accompanied by Gino Tuccari of INAF/IRA and Michael Wunderlich of MPIfR. The CDAS units were designed by Drs. Hong Xiaoyu, Zhang Xiuzhong, Wei Wenrun, Xiang Ying, Li Bin, Shu Fengchun, Zhu Renjie, Zhao Rongbing, Ling Quanbao, Wu Yajun, Wang Jinqing, Xue Zhuhe, Luo Jintao (all SHAO), and Chen Lan (now at Shanghai Institute of Technology). The ADS3000+ was accompanied by Hiroshi Takeuchi of JAXA and Kazuhiro Takefuji of National Institute of Information and Communications Technology. The RDBE-H was overseen by Haystack staff Chester Ruszczyk, Russ McWhirter, and Arthur Niell.

$<sup>^{2}</sup>$ The DBBC system can also be configured in a DDC configuration, which was successfully tested at the 2009 DBE intercomparison workshop but was not tested at this workshop.

5. The Haystack 'RDBE-H' PFB system, with hardware designed by UCBerkeley and NRAO-Socorro, and with firmware from Haystack and NRAO. The RDBE was configured with FPGA code version 1.4.

A detailed comparison of the systems under test, based on information gathered by Bill Petrachenko, is found in Table 1.

# 3. Test Objectives

The test objective was to ensure, as much as possible, that all DBE units were operating properly, including both functional and interoperability criteria. This was done by providing all units with a common frequency reference, 1pps timing signal, and broadband noise source spanning approximately 100 MHz to 2 GHz. For some testing, embedded test tones at IF frequencies 575 MHz and 961 MHz were added to the broadband noise source. The testing was divided into three specific phases:

- 1. Verification of compatibility with laboratory interfaces, command and control functionality, and digital-output format compatibility.

- 2. Single baseline cross-correlation test of each unit paired with RDBE-H unit; all station autocorrelations.

- 3. Simultaneous four-station zero-baseline cross-correlation of all six possible station pairs; all station auto-correlations.

## 4. Test Procedures

# 4.1. DBE Unit Setup First Day (Day 299)

Initial setup included basic testing of the compatibility of lab interfaces with equipment under test, including test recordings and verifications of recorded format, etc. Nearly the full first day of testing was devoted to this type of activity, but it resulted in the successful interfacing of all the units and successful basic operation of all units.

Prior to any testing, the units under test were set up as follows:

- 1. All units were supplied with a common 5 or 10 MHz reference frequency, as required.

- 2. All units were synchronized to a common TTL 1pps timing reference.

- 3. All units were set to identical UT times, as required.

- 4. IF levels were set appropriately by adjusting the amplification or attenuation to each unit under test.

- 5. Temporary test tones at 575 MHz and 961 MHz were injected into the IF as test markers (which were subsequently turned off after it was determined that the marker frequencies were appearing in the expected output channels via auto-correlation processing).

- 6. The CDAS-PFB and CDAS-DDC units were each connected to a Mark 5B+ with a VSI-H interface operating at a 64 MHz clock rate.

- 7. The RDBE-H produced 10GigE data in Mark 5B data format and was connected to a Mark 5C.

- 8. The DBBC produced Mark 5B data format over either a VSI-H interface to a Mark 5B+ recorder or a 10GigE interface (via Fila10G card) to a Mark 5C.

- 9. The ADS3000+ was connected to a K5 recorder and recorded in K5 format. The data were software-converted to Mark 5B format prior to correlation.

Each DBE unit under test included at its input a 512-to-1024 MHz anti-aliasing filter to place the recorded signal in the second Nyquist zone of the DBEs. The sampling clock for all units was 1024 MHz.

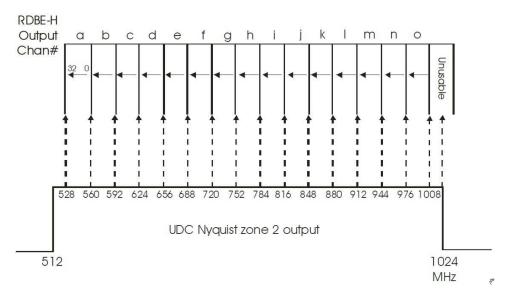

Figure 1. Relationship between input IF and digital output channels for PFB units.

### 4.2. Pairwise Zero-baseline Cross-correlation Tests - First Day

Following successful setup, auto-correlation and single-baseline cross-correlation tests were conducted with each unit using the RDBE-H as a reference unit. (The DBBC was tested separately with both VSI-H and Fila10G output formats.) The DBEs using a polyphase filter bank, namely RDBE, DBBC and CDAS-PFB, were configured to produce 15 useful 32 MHz baseband channels, each of which was lower sideband (LSB) with respect to the input IF (i.e. sky frequency increases in opposite direction to the IF). The frequencies that appear at DC for the 15 good channels were 1008,..., 528 MHz in steps of 32 MHz (see Figure 1). The PFB algorithm causes the 0th channel to be unusable, as indicated in Figure 1. The DBEs with flexible LOs, namely CDAS-DDC and ADS3000+ were set up with compatible channels.

For each pairwise test,  $\sim 30$  seconds of data were recorded, followed by e-transfer to standard Linux files, followed by auto-correlation and cross-correlation processing on the Haystack DiFX correlator. For each station pair, auto-correlation spectra were created for each station, as well as the zero-baseline cross-correlation results.

## 4.3. Four-station Zero-baseline Cross-correlation Tests - Second Day (Day 300)

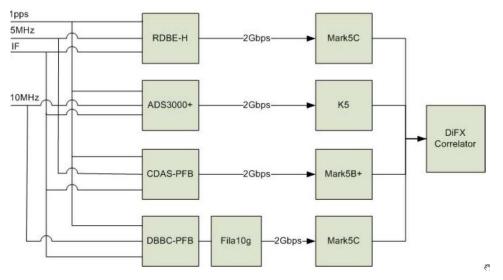

A four-station zero-baseline cross-correlation test captured simultaneous data using the common broadband IF noise source to all systems under test. The setup is shown in Figure 2, where the broadband noise input is labeled 'IF' and Nyquist zone 2 filters are assumed to be internal to the individual DBE units.

Figure 2. Setup for the zero-baseline inter-comparison test.

As before, 30 seconds of data were recorded from all four units simultaneously (with the DBBC unit operating in DDC mode with 10GigE output). No test tones were injected into the IF. The data were again e-transferred to standard Linux files, and the six cross-correlation pairs were processed on the DiFX correlator.

# 5. Results and Discussion

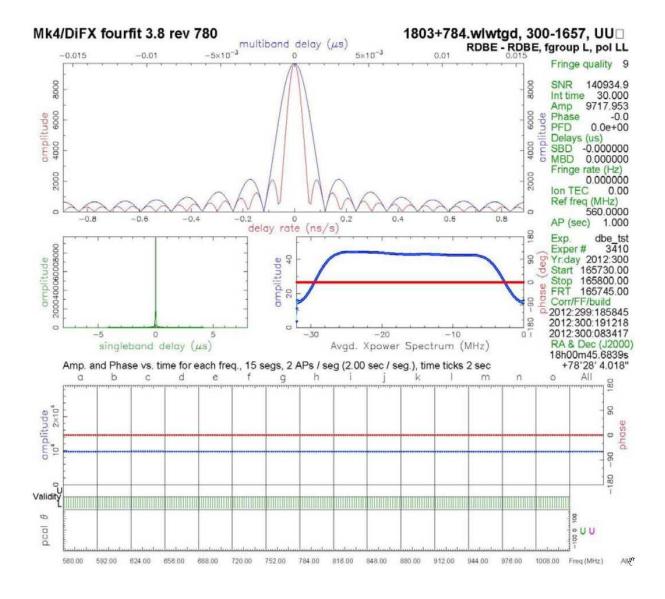

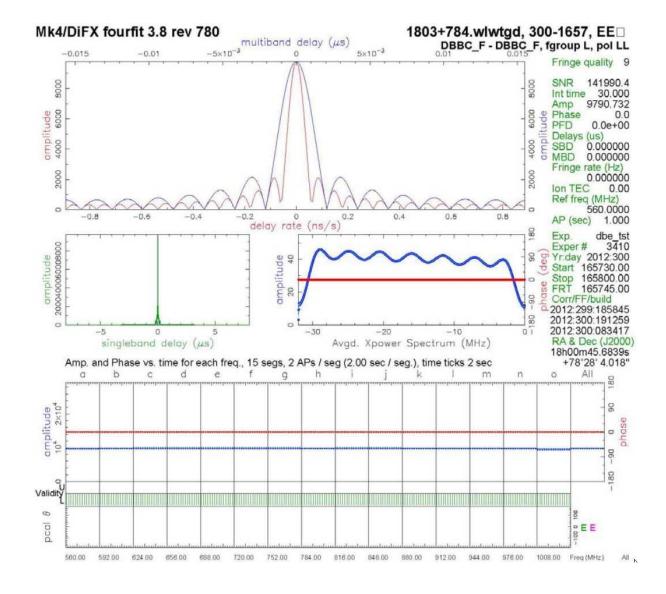

## 5.1. Auto-correlation Results (Figures 3 through 7)

All auto-correlation scans shown were with all test tones turned off.

Auto-correlation results shown for RDBE-H, ADS3000+ and DBBC are from Day 300 (scan 300-1657). Auto-correlation results for CDAS-DDC and CDAS-PFB are from Day  $299^3$

The only significant difference between the auto-correlation results of the four units under test are the amplitude and spacing of ripples in the auto-correlation spectra, as well as the sharpness of the cutoffs at the top and bottom of the bands. These differences should not present any

<sup>&</sup>lt;sup>3</sup>The CDAS-DDC was not active on Day 300. Auto-correlation results for RDBE-H, ADS3000+, and DBBC-PFB units are from the four-station scan 300-1657; auto-correlation results for CDAS-PFB for scan 300-1657 (not shown) contain a number of anomalous 'birdies' (though these 'birdies', as expected, do not propagate to the associated zero-baseline cross-correlation spectra). The cause of the 'birdies' is not known, but they were not present in the CDAS-PFB Day 299 data and may not be intrinsic to the CDAS-PFB. Hence we have elected to show the Day 299 auto-correlation for the CDAS-PFB unit. Further testing will be required to investigate the cause of these 'birdies' in the CDAS-PFB spectra for scan 300-1657.

problems for geodetic-VLBI operation or analysis, and can, in any case, be calibrated and removed if necessary.

The only problems in the set of auto-correlation of Figures 3 through 7 are in the CDAS-DDC spectra (Figure 7) that show a 'birdie' at mid-point in the auto-correlation spectra and a drop in amplitude of channel h (which covers IF frequency range 752-784; see Figure 1); separate processing of each 32 MHz output channel shows the 'birdie' to be only in channel h, which causes the apparent spectra amplitude to drop. We speculate that this problem may be due to a rounding bias in an interpolation step in the processing of that channel, but further testing is necessary to fully understand this problem.

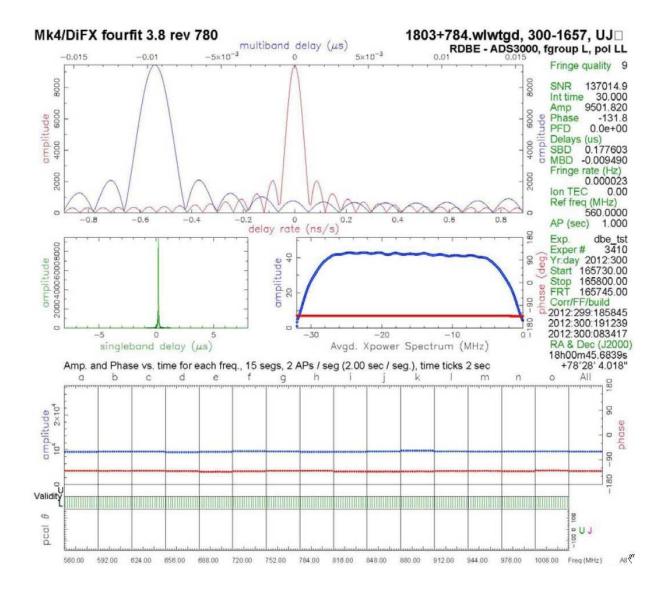

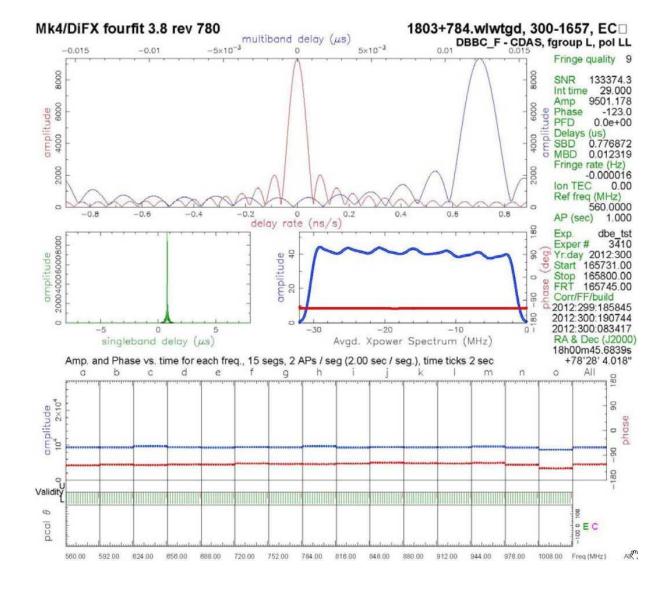

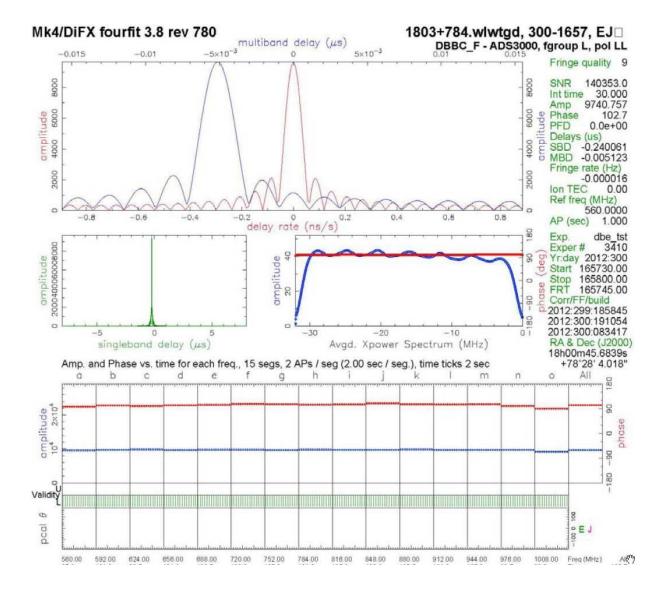

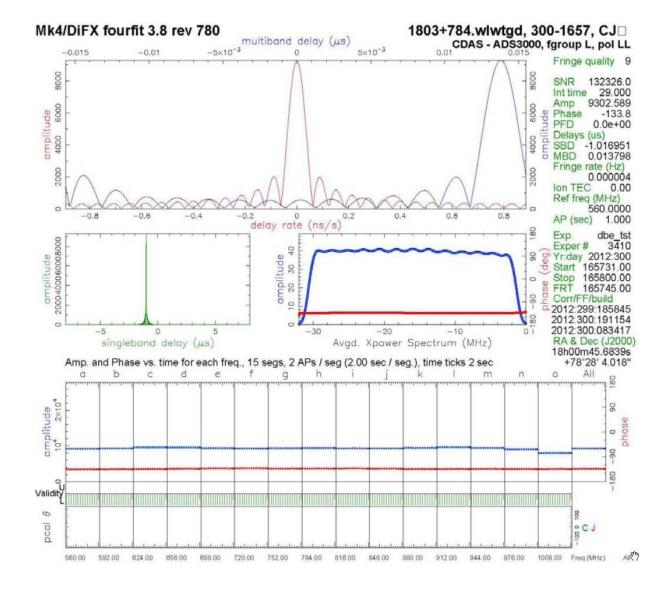

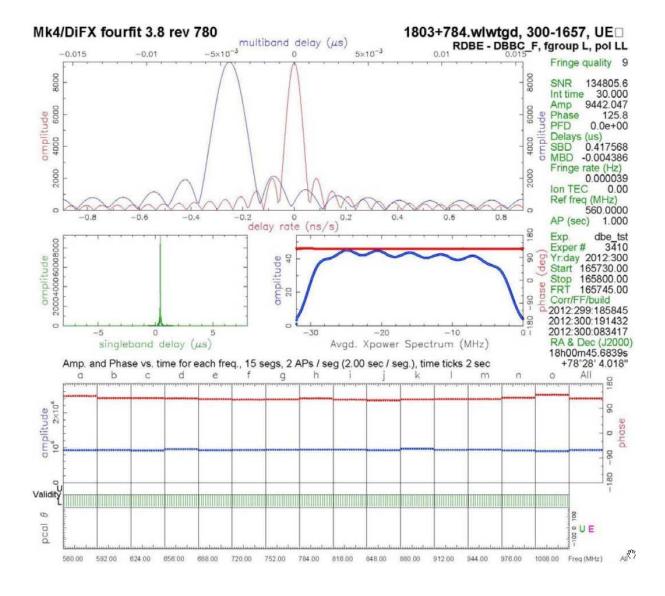

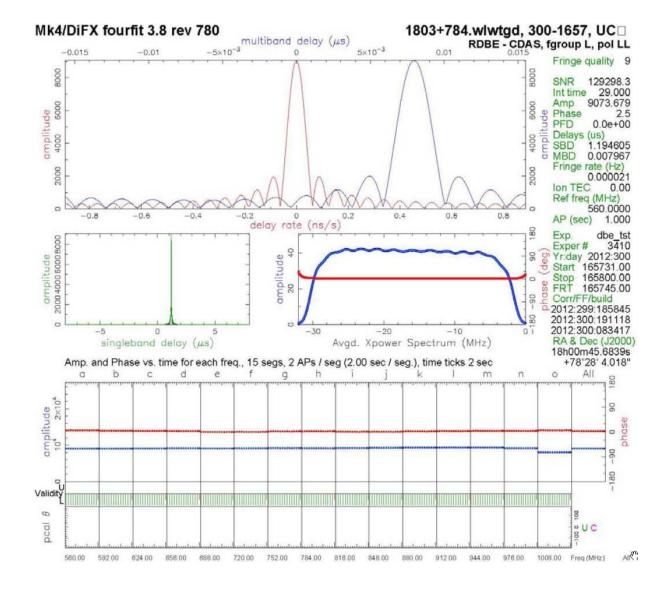

### 5.2. Cross-correlation Results (Figures 8 through 14)

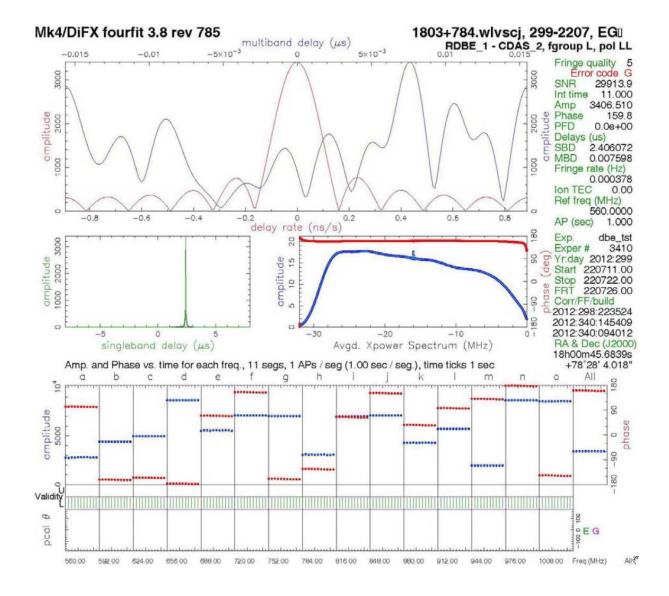

All zero-baseline cross-correlation results look quite nominal except for the Day 299 singlebaseline result from the RDBE to CDAS-DDC (Figure 8), for which both correlation amplitudes and phases differ widely from channel to channel. Further investigation of this result has been inconclusive; post-correlation processing of single channels shows similarly low cross-correlation amplitudes as well as channel-to-channel delay differences spanning a range of almost 30 nsec, whereas equivalent delay differences among all other units (Figures 10-14) are all under ~2 nsec. It is possible that the RDBE unit was malfunctioning on the day of the test, but we have no way to test this with only the single baseline of available data, and the RDBE unit behaved well on the second day of testing. At this point, we can only suggest that perhaps some sort of sampler jitter or digital-oscillator phase jitter in the CDAS-DDC may be responsible for the low correlation amplitudes, and varying internal signal path lengths may be responsible for the observed channel-to-channel delays; further testing is necessary. On the other hand, the CDAS-PFB unit, cross-correlated against DBBC-DDC, ADS3000+, and RDBE-H (as shown in Figures 10, 12 and 14, respectively) on Day 300 performed well despite observed 'birdies' in the CDAS-PFB data in scan3.

### 6. Summary

After several weeks of preparation and two long days of testing, including correcting various misunderstandings, fixing some hardware, and overcoming some internal networking problems, the testing was quite successful. Only one unit was found to have apparent significant problems, and another to have possible, more minor issues, and we hope that the results of this testing will help to understand and fix these problems, allowing more confidence of proper results as these DBEs move into routine VLBI observations.

This report is also available on-line at:

http://www.haystack.mit.edu/workshop/ivtw/2012.12.17\_DBE\_testing\_memo\_final.pdf

### Acknowledgements

We thank everyone who participated. We hope that this exercise was useful for all of the participants, and we at Haystack were happy to be able to help support this effort.

Figure 3. Auto-correlation results for RDBE-H version 1.4 (PFB algorithm).

Figure 4. Auto-correlation results for DBBC-PFB w/Fila10G.

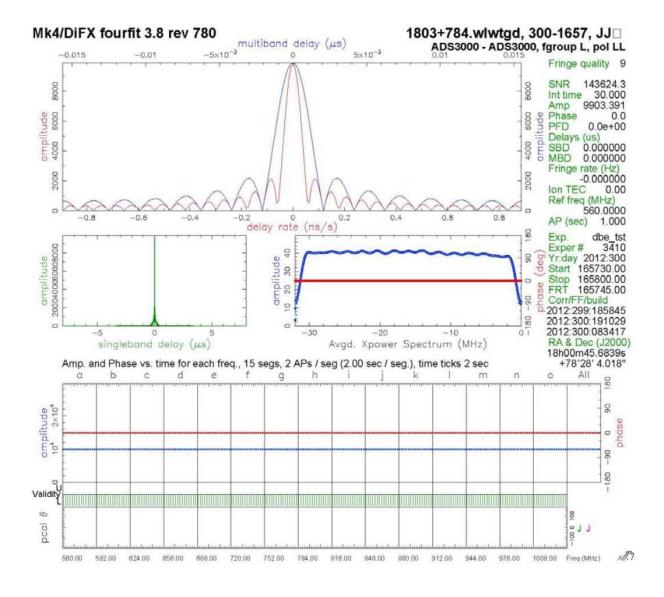

Figure 5. Auto-correlation results for ADS3000+ (DDC algorithm).

Figure 6. Auto-correlation results for CDAS-PFB.

Figure 7. Auto-correlation results for CDAS-DDC.

Figure 8. Zero-baseline cross-correlation results between RDBE-H and CDAS-DDC.

Figure 9. Zero-baseline cross-correlation results between RDBE-H and ADS3000+

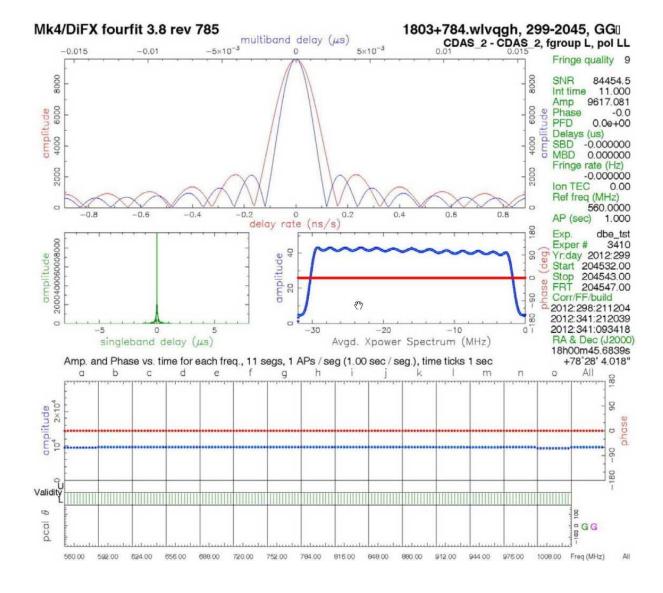

Figure 10. Zero-baseline cross-correlation results between DBBC-PFB w/Fila10G and CDAS-PFB

Figure 11. Zero-baseline cross-correlation results between DBBC-PFB w/Fila10G and ADS3000+.

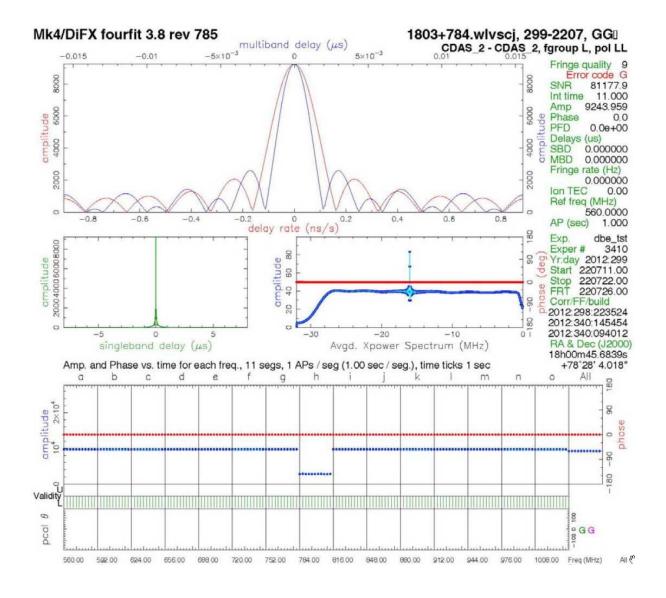

Figure 12. Zero-baseline cross-correlation results between CDAS-PFB and ADS3000+.

Figure 13. Zero-baseline cross-correlation results between RDBE-H and DBBC-PFB w/Fila10G.

Figure 14. Zero-baseline cross-correlation results between RDBE-H and CDAS-PFB.

Table 1. DBE Feature Comparison.

| Feature                         | RDBE-H            | DBBC2010-8H8C          | CDAS                           | ADS3000+              |

|---------------------------------|-------------------|------------------------|--------------------------------|-----------------------|

| FPGA code version tested        | 1.4               | 14                     | 1.0(PFB)/2.0(DDC)              | 10.06                 |

| IF's/Unit                       | 2                 | 8                      | 4                              | 4                     |

| Ref Freq (MHz)                  | 5                 | 10                     | 5                              | 10                    |

| Sampler resolution(bits)        | 8                 | 10 at ADC              | 8                              | 10  at ADC/8  at FPGA |

| Input Gain Set                  | Internal          | Internal               | Internal                       | Select 4 bits         |

| Sampler BW (MHz)                | 0-1536            | 0-3500                 | 50 -1024                       | 0-2500 (-3dB@1800)    |

| Input BW (MHz)                  | 512               | 1024                   | 512                            | $4 \times 512$        |

|                                 |                   |                        |                                | $2 \times 1024$       |

|                                 |                   |                        |                                | $1 \times 2048$       |

| PFB - Channel BW (MHz)          | 32                | 32/64                  | 32                             | -                     |

| PFB - Max # channels per IF     | 15 usable         | 31/15 usable           | 15 usable                      | -                     |

| PFB - Channel selection         | Flexible (16 max) | Flexible               | No (but planned)               | -                     |

| DDC - Channel BW (MHz)          | -                 | 1/2/4/8/16             | 1/2/4/8/16/32                  | 4/8/16/32             |

| DDC - # per unit                | -                 | 32 UL                  | 16                             | 16                    |

| DDC - Frequency resolution      | -                 | $10^4 (1e6/2^{20}) Hz$ | 10kHz                          | 1Hz                   |

| Requantization threshold (bits) | 2                 | 1, 2 or 4              | 1, 2 or 4                      | 2 or 4                |

| Real / Complex Data Output      | Yes / No          | Yes / Yes              | Yes / No                       | Yes / Yes             |

| Pcal / Total Pwr                | No/Yes            | Yes/Yes                | Yes/Yes                        | No/No                 |

| Data Rate/Unit (Gbps)           | 2                 | 32                     | 2                              | 2                     |

| Output Layer                    | 10GigE            | 10GigE/VSI-H           | VSI-H                          | VSI-H                 |

| Availability                    | Commercial        | Commercial             | Small number                   | Commercial            |

| Availability Date               | Now               | Now                    | Now                            | Now                   |

| Upgradable                      | Yes               | Yes                    | No                             | No                    |

| Cost/Unit                       | US\$18K           | 98.6K euros            | US\$50K (DDC)<br>US\$10K (PFB) | US\$40K               |