# **AEC-NASA TECH BRIEF**

AEC-NASA Tech Briefs describe innovations resulting from the research and development program of the U.S. AEC or from AEC-NASA interagency efforts. They are issued to encourage commercial application. Tech Briefs are published by NASA and may be purchased, at 15 cents each, from the Clearinghouse for Federal Scientific and Technical Information, Springfield, Virginia 22151.

# Nixie Tube Display Unit Employs Time-Shared Logic

## The problem:

To achieve input switching simplication of a Nixie tube display system. In conventional readout devices, Nixie display tubes are connected so all anodes of all tubes are continuously energized. Events are channeled to the particular Nixie display unit for portrayal. This method requires that each Nixie unit have all of its cathodes individually wired to the event generator, resulting in cluttered circuitry.

#### The solution:

Wire the cathodes of the display tubes in parallel. Use time-shared logic to energize the appropriate anode and inhibit all unnecessary cathodes.

# How it's done:

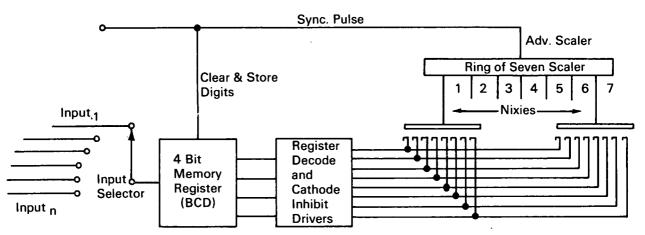

The system consists of an anode scaler ring, a 4-bit memory register, a master pulse generator, and cathode inhibit circuits. All of the corresponding numeric cathodes of seven display tubes are connected in parallel. The anodes are connected to a seven scaler ring which turns each anode on for 140 microseconds, stepping each anode through the ring and repeating the sequence indefinitely. A scaler output consists of an endlessly repeating train of 28 serial bits (7 digits  $\times$  4 bits per digit). The cathodes are returned to ground through a circuit which can inhibit any unneeded element as determined by the digit stored in a 4-bit memory register. A synchronization pulse from the master pulse generator causes the memory register to store and clear the digits in phase with the advance of the anode scaler. This arrangement makes it possible to display seven decades of data by serially reading the individual digits into the memory register and synchronizing the anode scaler advance to correspond to the digit being read.

## Notes:

1. The resulting display repetition rate of approximately 1000 cps completely eliminates visible flicker, while the intensity appears comparable to normal operation. The device provides substantial component savings over full-time parallel systems, while achieving input-switching simplification.

(continued overleaf)

This document was prepared under the sponsorship of the Atomic Energy Commission and/or the National Aeronautics and Space Administration. Neither the United States Government nor any person acting on behalf of the United States Government assumes any liability resulting from the use of the information contained in this document, or warrants that the use of any information, apparatus, method, or process disclosed in this document may not infringe privately owned rights.

- 2. The device has been operating for 2<sup>1</sup>/<sub>2</sub> years and has required no maintenance.

- 3. Inquiries concerning this innovation may be directed to:

Office of Industrial Cooperation Argonne National Laboratory 9700 S. Cass Avenue Argonne, Illinois 60439 Reference: B66-10512

#### Patent status:

Inquiries about obtaining rights for commercial use of this innovation may be made to:

Mr. George H. Lee, Chief Chicago Patent Group U.S. Atomic Energy Commission Chicago Operations Office 9800 S. Cass Avenue Argonne, Illinois 60439

Source: J. Gray Chemistry Division (ARG-117)

Category 01