| T5-2110/319                               | Copy No.     |

|-------------------------------------------|--------------|

|                                           | 4 months and |

| STUDY FOR A<br>FAILURE WARNING<br>PCM SYS | AND ANALYSIS |

| FINAL RE                                  | PORT         |

| 15 Novemb                                 | <b>1965</b>  |

Approved by

*fC-fay* E. R. Buxton

E. R. Buxton Chief Engineer Minuteman Engineering

# CONTENTS

- chine she she in an anno 1911 - All malanta shifti so sa

ĺ

|     |        |                                              | Page |

|-----|--------|----------------------------------------------|------|

| I.  | Introd | luction •••••••••••••••••••••••••••••••••••• | 1    |

| II. | Sumr   | mary • • • • • • • • • • • • • • • • • • •   | 3    |

|     | Α.     | Failure Warning Capability                   | 3    |

|     | в.     | Data Recording Capability                    | 3    |

|     | с.     | Limit Calculation                            | 3    |

|     | D.     | Dangerous Trend Detection                    | 3    |

|     | E.     | Pilot Options                                | 3    |

|     | F.     | PCM Flexibility                              | 4    |

|     | G.     | AWARE Adaptability                           | 4    |

| ш.  | Cond   | clusions and Recommendations                 | 5    |

| IV. | AWA    | ARE System Description                       | 6    |

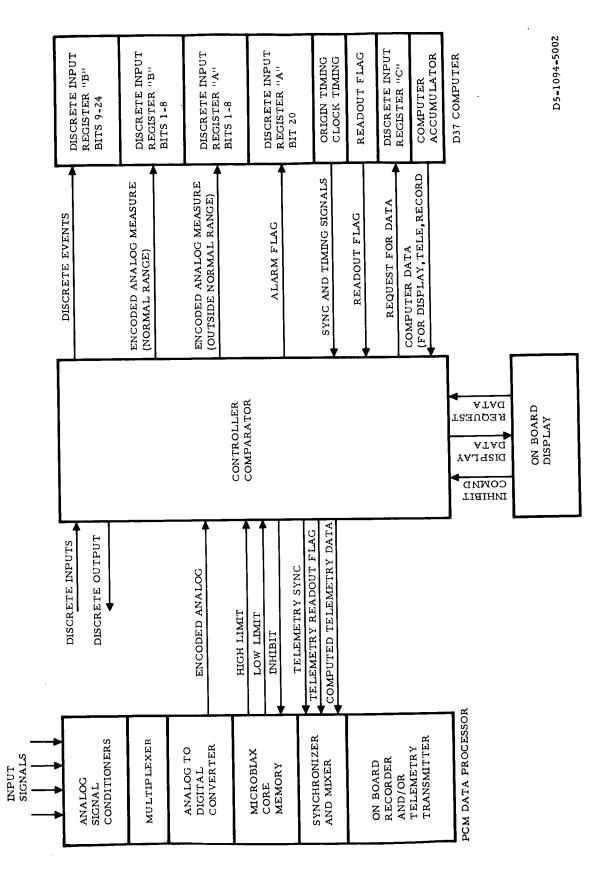

|     | А.     | Computer                                     | 6    |

|     | в.     | AWARE Display                                | 6    |

|     | с.     | AWARE Control Panel                          | 10   |

|     | D.     | PCM System                                   | 10   |

|     | E.     | Ground Checkout of the AWARE System          | 14   |

| v.  | Gene   | ral Discussion                               | 18   |

|     | А.     | Computer Considerations                      | 18   |

|     | в.     | PCM Telemetry Considerations                 | 18   |

|     | с.     | System Considerations                        | 19   |

|     | D.     | AWARE Computer Programming                   |      |

|     |        | Considerations                               | 20   |

| VI. | AWA    | ARE PCM Detailed Description                 | 36   |

|     | Α.     | PCM Circuit Design                           | 36   |

|     | в.     | D26 Detailed Description                     | 50   |

| VII | . Alt  | ernate AWARE System                          | 71   |

iii

# ILLUSTRATIONS

# Figure

# Page

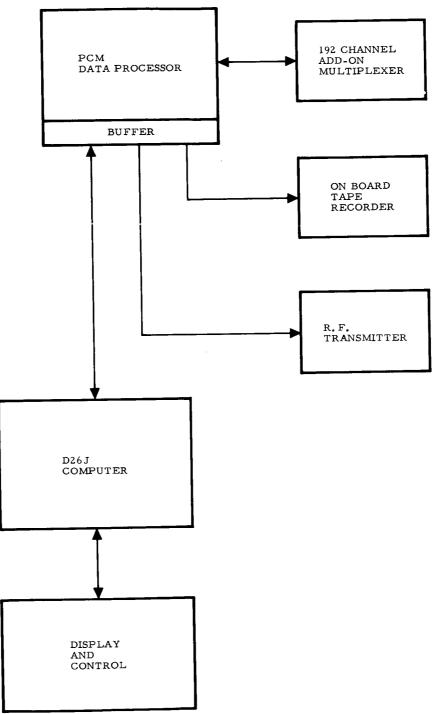

| 1.  | AWARE System                                                 | 7  |

|-----|--------------------------------------------------------------|----|

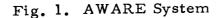

| 2.  | D26J Integrated Circuits and Multilayer Boards               | 8  |

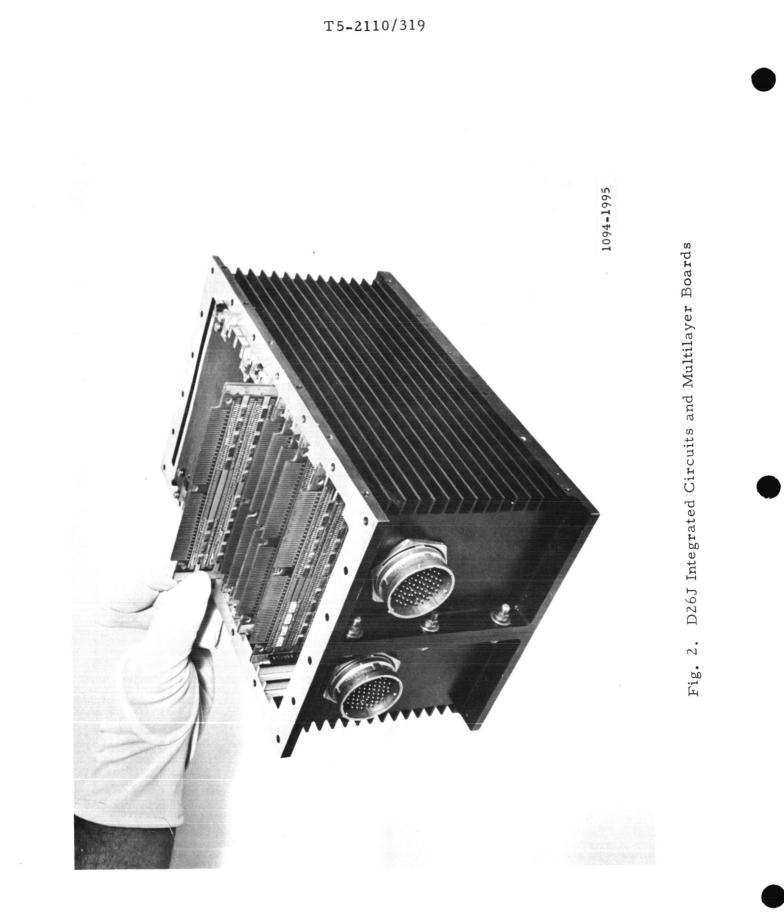

| 3.  | AWARE Display Panel                                          | 9  |

| 4.  | AWARE Control Panel                                          | 11 |

| 5.  | PCM Data Processor                                           | 12 |

| 6.  | Add-On Multiplexer (192-Channel)                             | 13 |

| 7.  | AWARE PCM Telemeter                                          | 15 |

| 8.  | AWARE System/Test Set Interface                              | 16 |

| 9.  | Program Execution Section Diagram                            | 27 |

| 10. | Constants Block Memory Allocation                            | 28 |

| 11. | Memory and Time Estimates versus System                      |    |

|     | Size                                                         | 30 |

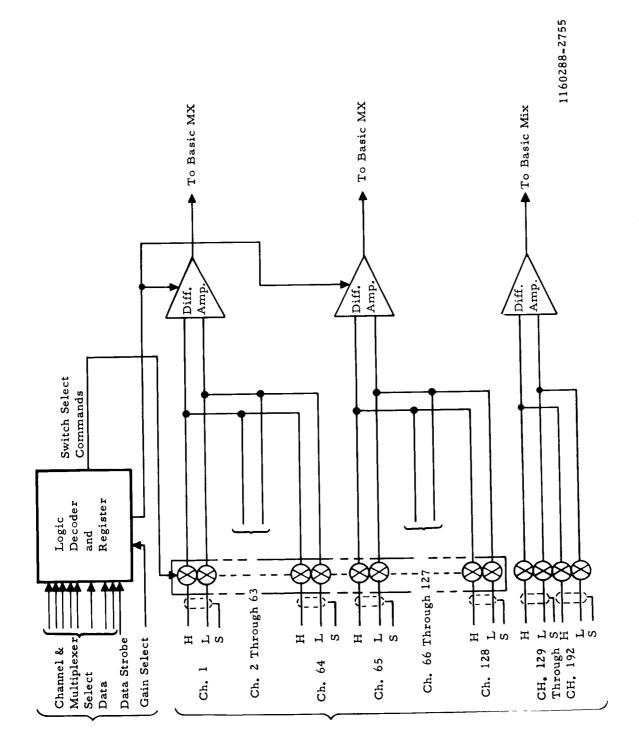

| 12. | Basic Analog Multiplexer                                     | 40 |

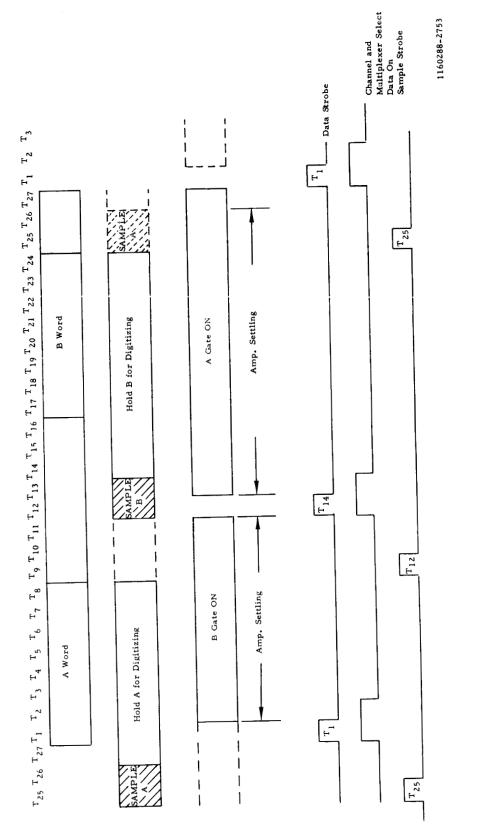

| 13. | Multiplexer Timing and Sequencing Diagram                    | 41 |

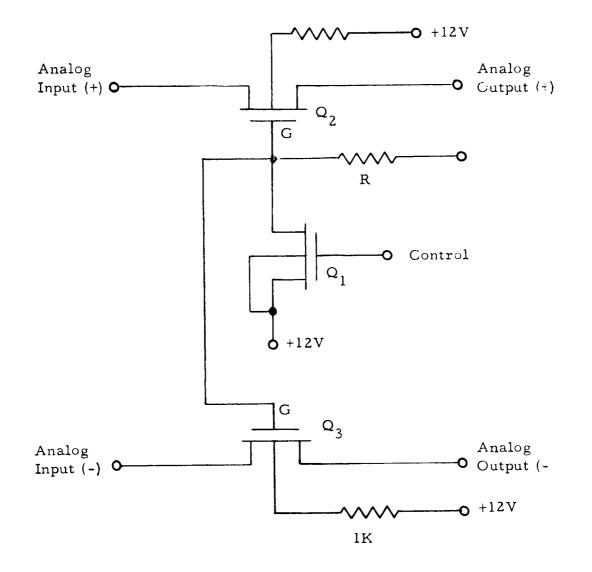

| 14. | Double Pole, Single Throw FET Switch                         | 46 |

| 15. | Add-On Analog Multiplexer                                    | 48 |

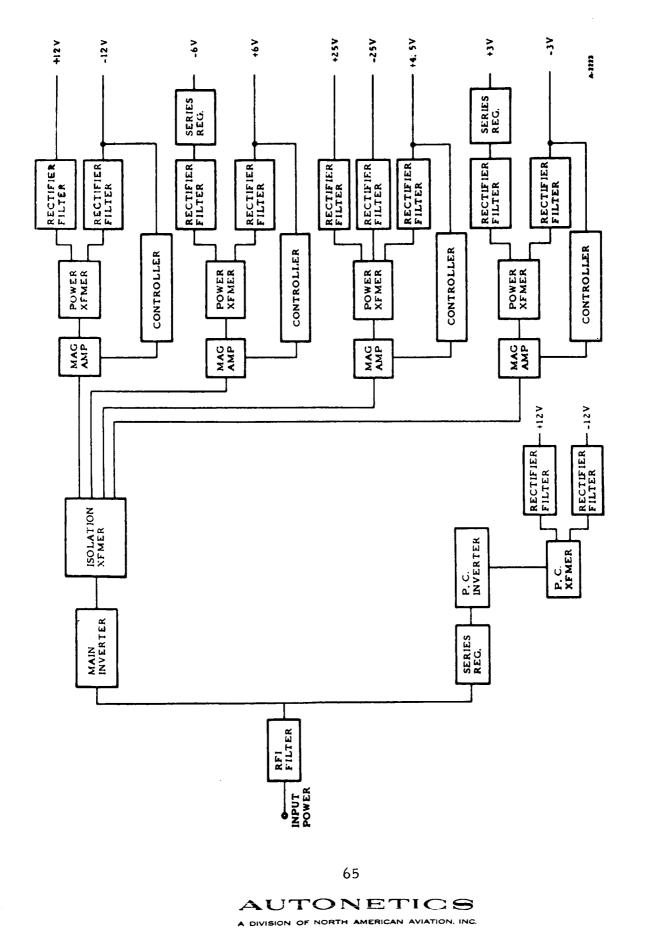

| 16. | D26J Power Supply                                            | 65 |

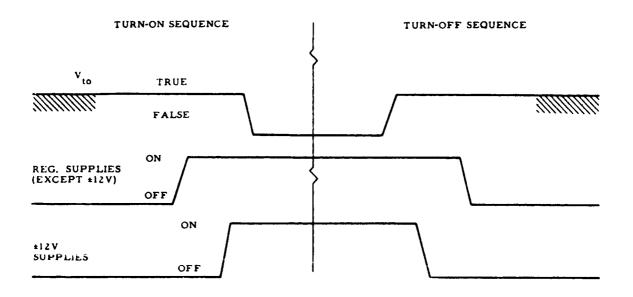

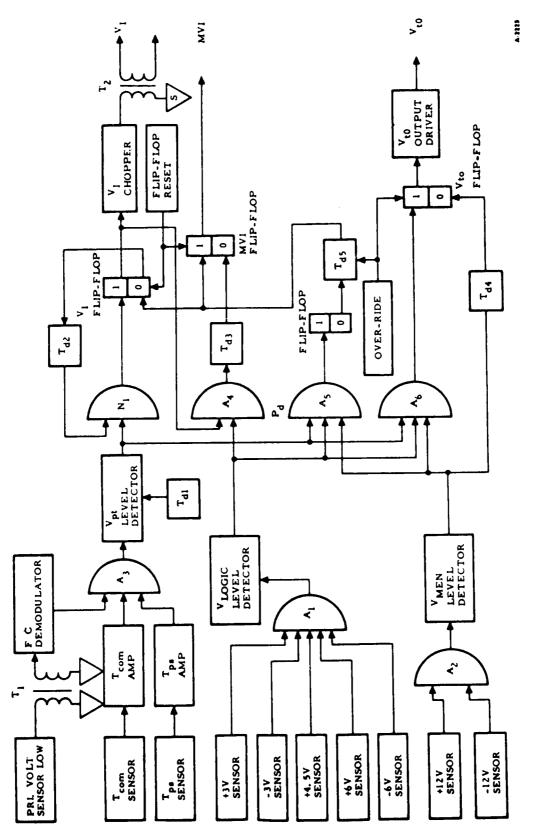

| 17. | Timing Sequence                                              | 67 |

| 18. | Block Diagram D26J Power Control                             | 68 |

| 19. | Alternate AWARE System • • • • • • • • • • • • • • • • • • • | 72 |

iv

-

# TABLES

| Number |                                 | Page       |

|--------|---------------------------------|------------|

| 1.     | D26J Instruction List           | <b>2</b> 3 |

| 2.     | Summary of Amplifier Capability | 44         |

| 3.     | Typical Operation Times         | 50         |

| 4.     | Characteristics of the D26J     | 51         |

| 5.     | Typical D26J Configurations     | 56         |

| 6.     | D26J Command List               | 61         |

| 7.     | Power Control Functions         | 66         |

a second and the second of the second

v

A DIVISION OF NORTH AMERICAN AVIATION INC.

## I. INTRODUCTION

This is the final report of a study conducted by the Autonetics Division of North American Aviation for the NASA Flight Research Center, Edwards, California.

The purpose of the study was to determine the feasibility of mechanizing a flight failure warning system. NASA visualized an airborne digital computer and a PCM data system functioning together to provide failure warning data to a pilots display panel. NASA also intended that the combined computer/PCM system be capable of gathering flight test data for analysis by ground based personnel.

The study has concluded that the NASA failure warning concept is both feasible and practical. Consequently, Autonetics devised the AWARE system (Automatic Warning and Recording Equipment) to illustrate the feasibility of mechanizing such a system.

The AWARE computer/PCM System monitors flight safety parameters and warns the pilot if any operating limit is exceeded. The pilots panel identifies the overlimit parameter and indicates the actual value along with the upper and lower operating limits.

The AWARE system also warns the pilot of any dangerous trends so that he can anticipate overlimit operation and take appropriate preventive action.

In addition, the pilot can select any parameter for display by momentarily depressing the "SCAN" switch and then depressing the "HOLD" switch when the desired parameter appears. Subsequently, the selected parameter will remain on the display and be periodically updated until the pilot selects another parameter or until the computer issues a failure warning. Once the pilot acknowledges a failure warning he can override that particular warning by mementarily depressing the "INHIBIT" switch. The inhibited parameter can be reselected at anytime.

The mechanication of the AWARE system takes full advantage of current advanced integrated circuits and thin film technology. The system uses the same type of integrated circuits and multilayer boards that were developed by Autonetics for the highly reliable Minuteman D37 computer.

The primary purpose of this system is to aid the pilot by warning him of potentially dangerous conditions. Once this warning function is performed, the system serves as a source of additional data for analysis by the pilot and the flight engineer. In this way, the AWARE system takes full advantage of sophisticated electronic data processing without loosing the advantages of human reasoning and human judgment which is absolutely necessary when evaluating flight performance of manned vehicles.

AUTONETICS

# II. SUMMARY

The Autonetics AWARE system fulfills the flight failure warning requirements specified in the NASA Statement of Work NAS4-882. Significant features of the AWARE system include:

# A. FAILURE WARNING CAPABILITY

Up to 256 parameters are monitored and compared to normal operating limits. If any parameter exceeds its normal operating range an appropriate failure warning is displayed on the pilots panel and an audio pulse is injected into his headset.

#### B. DATA RECORDING CAPABILITY

Up to 256 measurements can be recorded in PCM format on an airborne tape recorder or the data can be relayed via a PCM telemetry transmitter to ground based recorders.

#### C. LIMIT CALCULATION

Operating limits may be loaded directly into the computer memory or the computer can calculate the appropriate limits based upon flight conditions and programmed instructions.

#### D. DANGEROUS TREND DETECTION

The AWARE system can detect and warn the pilot if any parameter approaches an operating limit at an excessive rate so that the pilot can take preventive action.

E. PILOT OPTIONS

The pilot can call-up any measurement for display in alpha numeric terms and in engineering units.

The pilot can introduce new limits into the computer or he can inhibit any measurement at will.

#### F. PCM FLEXIBILITY

The AWARE PCM system is extremely flexible. This flexibility is made possible by including a core storage memory in the PCM system itself. The multiplexer program, word format and frame synchronization codes can be stored in the PCM core memory. Thus, many of the traditional PCM hardware modifications can now be accomplished by software change, namely, a PCM program tape can be loaded into the PCM core memory.

In addition, an adjustable PCM output buffer allows the PCM system to supply narrow bandwidth data to on-board tape recorders while supplying wide bandwidth data to the computer. In this way, the AWARE system can help conserve the on-board tape supply by operating at narrow bandwidth and low tape recorder speed during static conditions. Conversely, the PCM system can operate at wide bandwidth, high tape speeds during dynamic test conditions.

# G. AWARE ADAPTABILITY

The AWARE telemetry system communicates with the airborne computer through an asynchronous buffer unit which allows the telemetry system and the computer to operate at different clock frequencies. Therefore, the AWARE PCM system could be used to expand the input/output capacity of airborne digital computers already in use.

Another application of the entire AWARE system, including computer, is in the data compression field. Many sensors can be monitored at high sampling rates and the computer can be programmed to eliminate redundant samples. In some cases data bandwidth can be reduced significantly.

# III. CONCLUSIONS AND RECOMMENDATIONS

The AWARE system was specifically devised to fulfill the failure warning requirements of the subject NASA contract. Since the essential functional building blocks are readily available, it is recommended that an experimental or prototype AWARE system should be assembled to further demonstrate the feasibility of mechanizing such a system.

A DIVISION OF NORTH AMERICAN AVIATION, INC.

#### IV. AWARE SYSTEM DESCRIPTION

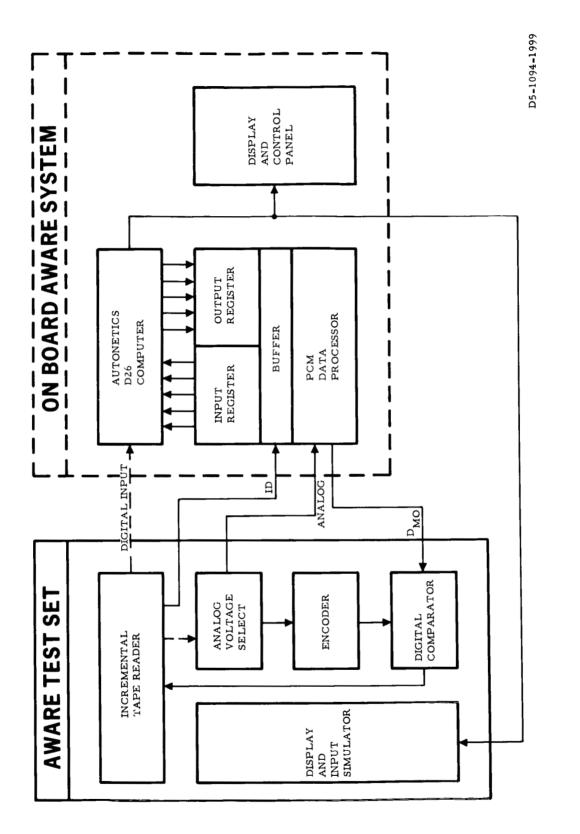

The AWARE system consists of a digital computer, a PCM data system, a display panel, and a tape recorder or radio transmitter. A simplified block diagram is shown in Fig. 1.

## A. COMPUTER

The digital computer selected for this system is the Autonetics D26J microminature digital computer. The D26J is ideally suited for the AWARE system since it is a reliable general purpose computer with a random access memory and parallel word transfer capability. The core memory is expandable to over 16,000 words if required.

The D26J integrated circuits and multilayer boards (Fig. 2) have proven reliability since they are identical to those used in the highly reliable Minuteman D37 computer. In addition, the D26J has successfully completed flight tests at Holloman Air Force Base. Additional detailed description of the D26J is contained in later sections of this report.

#### B. AWARE DISPLAY

1. Data Call-Up

The pilot may request any measurement for display by depressing the appropriate system "SCAN" switch on the display panel (Fig. 3). When the desired parameter appears on the display, the pilot depresses the "HOLD" switch. This selected parameter, along with it's upper and lower limits, will remain on the display and be continually updated until the pilot selects another parameter or until the computer issues a warning alarm pertaining to the system being monitored. Even then, the pilot can override the warning by depressing the "INHIBIT" switch and then select the original parameter again.

2. Confidence Tests and System Self Test

The validity of any sudden warning of impending failure will naturally be questioned by most flight test pilots. Therefore, methods of verifying dangerous conditions must be available to the pilot.

D5-1094-1994

----

- - -

A DIVISION OF NORTH AMERICAN AVIATION. INC.

AUTONETICS A DIVISION OF NORTH AMERICAN AVIATION, INC.

The AWARE system allows the pilot to verify proper system operation by three different means. (1) The computer completes a self test of the entire AWARE system once each frame and illuminates a green "SELF TEST" light continuously if all the self test criteria are fulfilled. (2) A green "ALL SYSTEMS NORMAL" light is illuminated when there are no measurements exceeding their respective operating limits and (3) the pilot can initiate a special system test by depressing a "CONFIDENCE TEST" switch which in turn illuminates a green "CONFIDENCE TEST" light.

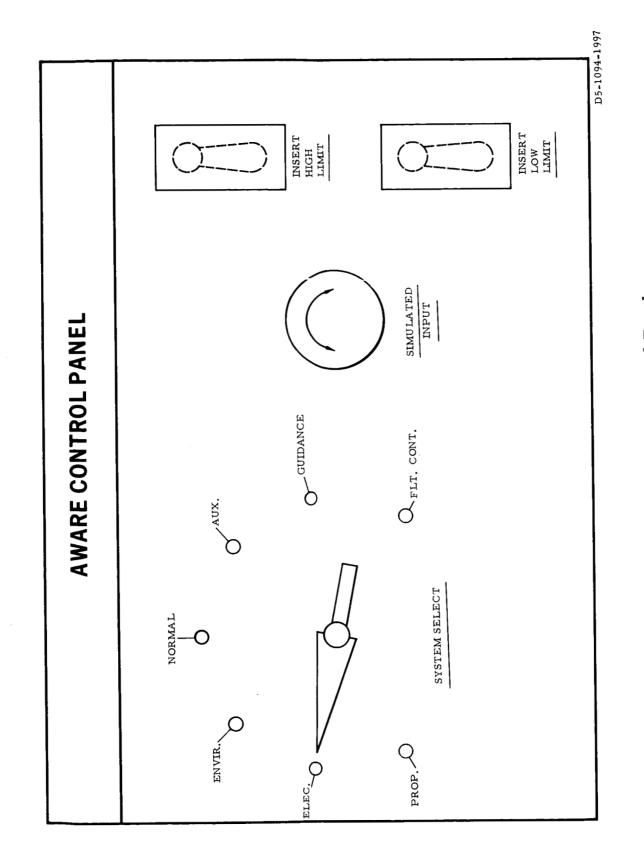

#### C. AWARE CONTROL PANEL

The AWARE control panel (Fig. 4), in conjunction with the display, allows the operator to induce a simulated input into any channel of the AWARE system. Actually, the simulated input is routed through one single multiplexer gate, through the A/D converter and then into the computer. However, the computer analyzes the input signal as though it were the actual channel being requested by the pilots panel. The simulated input is converted to engineering units and displayed on the panel as an actual measurement.

This simulated input capability can be used in two ways. First, it allows the pilot to check the AWARE system, by simulating abnormally high or low measurements to ascertain that the warning system will actually generate a warning if an out of limits condition ever existed. Secondly, it allows the operator to insert the simulated value into the computer as a new fixed limit.

This control panel could be installed in the aircraft accessible to the pilot or it could be part of the ground test console whichever the customer desired.

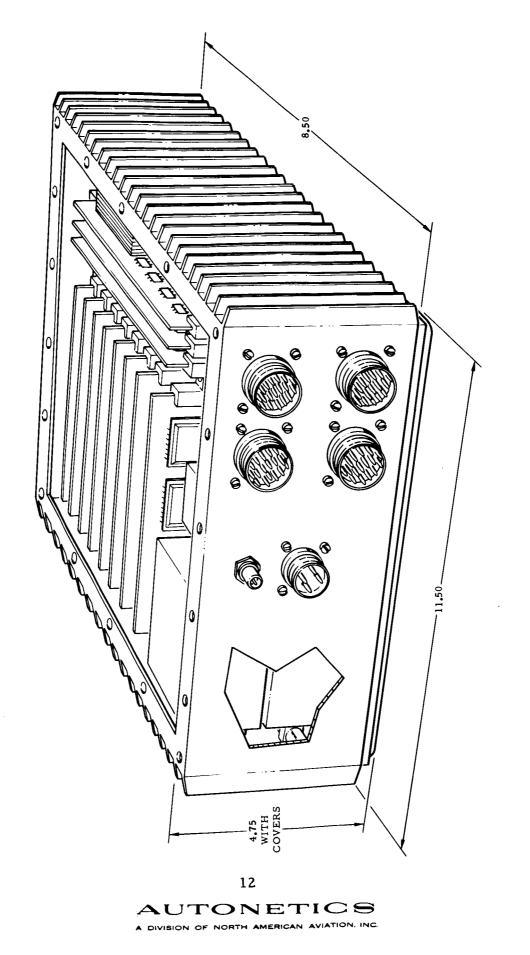

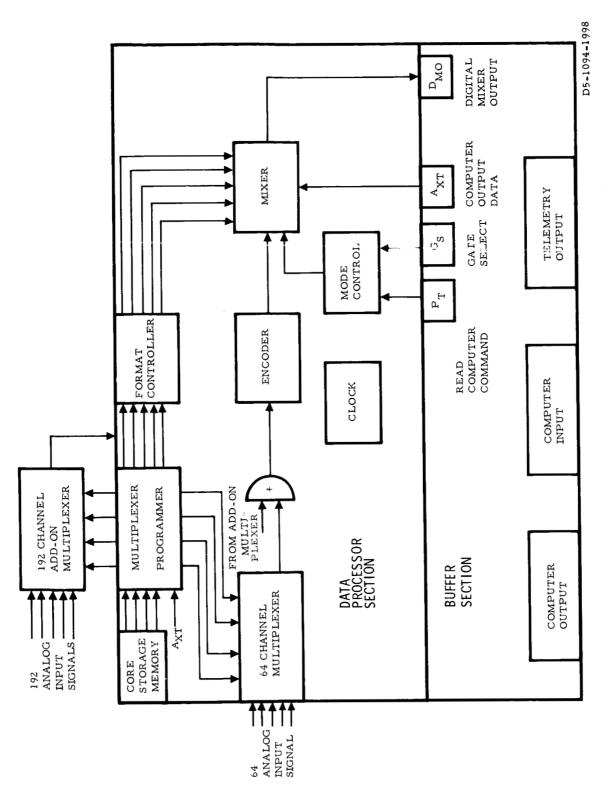

#### D. PCM SYSTEM

The AWARE PCM Data Processor system shown in Fig. 5 is capable of performing the usual PCM functions of multiplexing and encoding analog information but it also includes some special features which make it particularly useful in the AWARE system.

These special features include:

- 1. A core storage memory is a part of the basic PCM system.

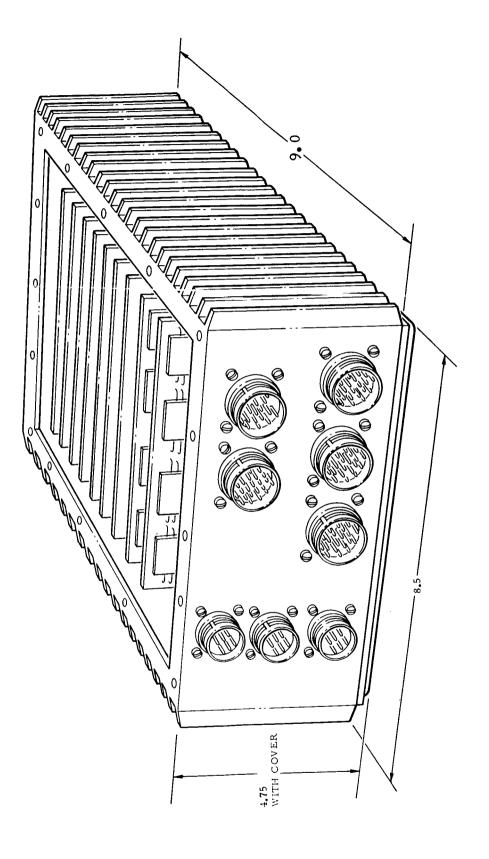

- 2. An internal 64 channel multiplexer is included plus a 192 channel add-on multiplexer (Fig. 6).

Fig. 4. AWARE Control Panel

11 AUTONETICS

!

Fig. 5. PCM Data Processor

Fig. 6. Add-On Multiplexer (192-Channel)

1160288-2748

13 AUTONETICS

A DIVISION OF NORTH AMERICAN AVIATION. INC.

- - - -

T5-2110/319

- 3. Both multiplexers are capable of low and high level multiplexing.

- 4. The multiplexer program is stored in the core memory to designate sampling rate and signal level (low or high level switching).

- 5. The telemetry output format is controlled by the program loaded into the core memory.

- 6. A buffer section is included which allows the PCM system to operate asynchronously with various computers.

- 7. The buffer section also provides for telemetry data bandwidth control by varying the telemetry buffer output frequency. The AWARE PCM telemetry is shown in Fig. 7.

- 8. The multiplexer gates can be selected either by core storage sequencing or by computer initiated data requests.

## E. GROUND CHECKOUT OF THE AWARE SYSTEM

Analog stimulation signals and digital sequencing commands are provided to the system from a test set consisting of an incremental tape recorder, a digital to analog converter and a digital comparator (Fig. 8). In essence, the test set performs an automated end-to-end test of the AWARE system exclusive of the display panel which, of course, must be monitored visually. The analog stimulation signal is routed through one gate of the multiplexer and the digital parameter identification signal is routed into the computer input register once each frame upon command from the computer. Subsequently, the AWARE system processes the stimulation signal as if it were a "call up" from the on board display. Thus, the on board and test set displays are driven to the parameter commanded by the tape reader and the analog voltage supplied is encoded and displayed as an actual measured value in engineering units after processing by the computer. The analog voltage from the test set is programmed so that first it is within limits, next its value exceeds the high limit, and finally, it's value is below the low limit. This, in turn, gives the expected normal, high warning, and low warning indications on both the on board and test set displays. Simultaneously, the system provides a unique computer word back to the telemetry along with digital data equivalent to the original analog voltage supplied by the test set. This, in turn, requires that the telemetry recognize the unique computer word, thus

# Fig. 7. AWARE PCM Telemeter

15

# AUTONETICS

A DIVISION OF NORTH AMERICAN AVIATION, INC.

T5-2110/319

ł

Fig. 8. AWARE System/Test Set Interface

16

AUTONETICS

T5-2110/319

ļ

I

İ

1

commanding transmittal out to the test set. At this point, the digital comparator compares transmitted telemetry data with encoded test set input data and thus checks the telemetry link. If the comparison is proper, the incremental tape reader is stimulated to the next parameter. This process is repeated until all parameters are checked unless comparisons indicate a malfunction. In this case the test set commands a halt, indicating which channel of data is erroneous and appropriate maintenance procedures can be initiated such as using computer diagnostic tapes to isolate the malfunction to the faulty module.

#### V. GENERAL DISCUSSION

The primary goal of this study was to provide a practical method of warning the flight test pilot of potentially dangerous conditions so that he might take preventive or corrective measures he considers necessary. A secondary goal was to provide ground based flight test engineers with adequate quantitative data for effective flight performance analysis.

#### A. COMPUTER CONSIDERATIONS

The ideal flight failure warning system, from a computer utilization viewpoint, would use the PCM telemetry as a synchronized input/ output device with random access and parallel word transfer capability. Such a system could possibly be mechanized. In this configuration the computer could issue a data selection command at any time and the telemetry would respond instantaneously with the encoded value of the requested analog measurement. The computer could then analyze the requested measurement to determine if it was within normal operating range. If the data did not exceed normal limits then the computer could command another measurement immediately. If the normal limits are exceeded, then a warning message could be relayed to the pilots panel and the telemetry system could be commanded to record or transmit similar warning data. If all measurements remain within normal operating range then no data would be displayed on the pilots panel and no data could be flagged to telemetry.

Although this system might be acceptable for many applications it probably would not be completely adequate for use in most flight test aircraft because it doesn't provide adequate test data for flight performance analysis purposes.

# **B. PCM TELEMETRY CONSIDERATIONS**

The on-board computer can be an extremely valuable aid to the pilot and to the flight test engineer. However, one of the primary missions of flight test aircraft is to gather quantitative flight test data to evaluate aircraft performance characteristics. Also, when an unexpected malfunction occurs, accurate quantitative data must be available for analysis. This analysis is necessary to determine what action is necessary to prevent failure recurrence. Consequently, there are definite test data requirements for nearly all flight test aircraft.

AUTONETICS

The ideal flight failure warning system (from a PCM telemetry utilization viewpoint) would use the PCM telemetry system as a sequential input/output device with serial data transfer to the computer and recorders or transmitter. The PCM data bandwidth would be narrow to be compatible with low frequency tape recorders and narrow bandwidth transmitters.

Although this PCM centered failure warning system could be easily mechanized, it would not be acceptable because of the severe computer programming limitations it imposes. The computer must accept the data whenever the PCM system supplies it and, since PCM data samples must be sequential with uniform spacing between samples, the computer program would be extremely inflexible.

## C, SYSTEM CONSIDERATIONS

It is clear that an effective failure analysis system must incude a computer with parallel word transfer and random access memory. Likewise, the PCM system must be capable of sequentially sampling test data at a uniform rate and symmetical sampling pattern.

Therefore, it appears that the best method of mechanizing a combined computer/PCM system must involve an unusual time sharing arrangement. Normally, a computer must perform several functions and it is common practice to time share a computer with several input/ output devices. However, in this case, the telemetry must perform two functions. It must act as a computer input/output device and it must feed sequential uniformly spaced samples of test data to telemetry tape recorders or telemetry transmitters. In essence then, the PCM system must be time shared between its computer input/output functions and its conventional telemetry functions.

Fortunately, telemetry multiplexers and encoders are capable of high speed operation so that it is practical to time share them. For example, it is feasible to operate a basic PCM system at 300 kilopulses per sec and by time sharing, supply 150 kilopulse data to the computer and 150 kilopulse data to the telemetry recorder. Of course, it is necessary to include buffer registers in the PCM package to allow for this time sharing operation. These buffers require little space though, since they can be mechanized with microminiature integrated circuits.

Consequently, it is feasible to mechanize a failure warning system using an airborne digital computer and a PCM system and still retain the operational capabilities of both pieces of equipment. The Autonetics AWARE system (Automatic Warning and Recording Equipment) is an example of such a system.

# D. AWARE COMPUTER PROGRAMMING CONSIDERATIONS

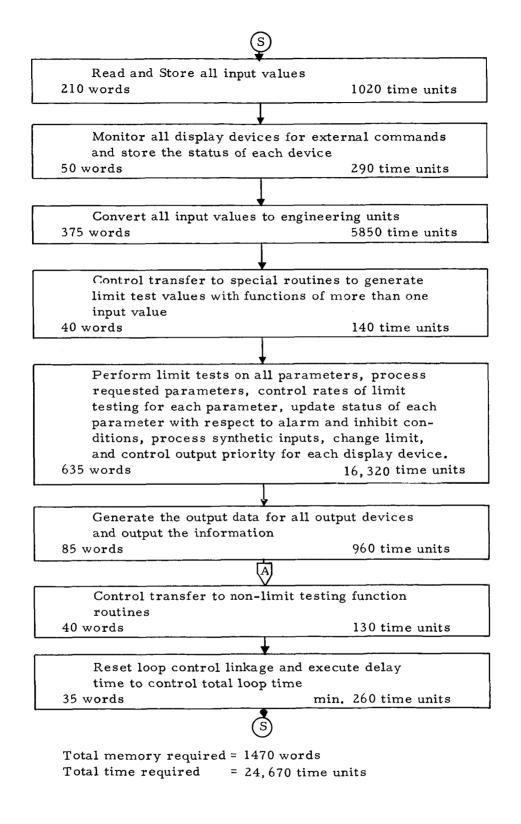

While it was not within the scope of the study to develop and write a digital computer program to accomplish the Early Warning Task, it was necessary to develop a general program philosophy in order to arrive at reasonable estimates for storage and timing requirements. The information presented in the following paragraphs of this section describe the program in general terms and list the basis for the associated memory and timing estimates.

## 1. D26J Functional Description

The following information describes the programming and program execution characteristics of the D26J computer.

Type: General Purpose. Internally stored

Clock Rate: 500 kilopulses/sec

Time Unit: 2 usec

Memory Type: Random Access Core

Memory Sizes: 1024, 4096, 8192, 16, 384 words

Memory System: Binary with two's complement negative values.

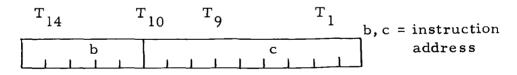

Instruction Word Length: 16 bits

Data Word Length: 15 bits plus sign

Input-Output: as required by customer with respect to the number and types of external communication required. The minimum requirement for the failure warning task is one full word of input and one full word of output.

Address Modification: Accomplished in 512 word blocks by means of a program controllable bank register.

Instruction List: See Table 1

Instruction Execution Times: See Table 1

2. Memory and Time Estimates for Individual Functions

The following data was developed using the D26J 2 usec time unit.

| Function                           | Memory Required<br>(Words) | Time<br>(ms) |  |

|------------------------------------|----------------------------|--------------|--|

| Execution Section                  | 1470                       | 49.340       |  |

| Constants Block                    | 500                        |              |  |

| MACH from Pressure<br>Measurements | 90                         | 2.240        |  |

AUTONETICS

A DIVISION OF NORTH AMERICAN AVIATION, INC.

| Function                         | Memory Required<br>(Words) | Time<br>(ms) |

|----------------------------------|----------------------------|--------------|

| Flare Computer Computations      | s 2500                     | 200.000      |

| True Airspeed                    | 145                        | 1.686        |

| Angle of Attack and Side Slip    | 190                        | 3.940        |

| Atmospheric Density              | 25                         | 0.330        |

| Actual Versus Planned<br>Profile | 2050                       | 0.380        |

3. Program Purposes

The primary purpose of the digital computer program is to periodically read values for a predetermined number of vehicle environmental and state parameters, compute values which are functions of one or more of the input values, test the computed values against pre-set limits by one of three methods and, if the test is failed, generate and output sufficient data to identify the failed parameter or system, and display the limits used in the test, the value which failed the test, the type of engineering units in which the data is displayed and turn on an alarm light/signal device.

The three limit test methods are: (1) direct comparison of the converted input value with high and low limits, (2) comparison of the rate of change of the converted input value with high and low limits and, (3) comparison of a proportional rate of change of the converted input value to high and low limits.

A secondary purpose of the program is to accept manually controlled parameter identifications and instructions to: (1) compel the generation and display of outputs similar to the above, (2) inhibit the display even when a test is failed, (3) sequence through a set of parameters at a preset rate, generating and emitting the required data, (4) read and process a synthetic value as if it were the actual input value and (5) change one of the limits used in the test to an indicated value.

Other purposes of the program are to perform as many computations other than the above as time and computer storage space will allow.

1

į.

i

1

1

# Table 1. D26J Instruction List

| MNEMONIC | Code <sub>8</sub> | Bits<br>2 1 | Name                            | Execution<br>Time (us) |

|----------|-------------------|-------------|---------------------------------|------------------------|

| ADD      | 34                |             | Add                             | 12                     |

| AND      | 66                | 01          | Logical AND                     | 12                     |

| DIV      | 70                | 01          | Divide                          | 108                    |

| DPAD     | 74                |             | Double Precision Add            | 18                     |

| DPLD     | 76                |             | Double Precision Load           | 18                     |

| DPST     | 72                |             | Double Precision Store          | 18                     |

| DPSU     | 64                |             | Double Precision                | 18                     |

|          |                   |             | Subtract                        |                        |

| HPR      | 04                |             | Halt and Proceed                | 6                      |

| LDB      | 10                |             | Load Bank Register              | 6                      |

| LDL      | 36                |             | Load L                          | 12                     |

| LDU      | 26                |             | Load U                          | 12                     |

| MPY      | 60                |             | Multiply                        | 54                     |

| RIL      | 30                | 0           | Read Input to L                 | 12                     |

| RIU      | 30                | 1           | Read Input to U                 | 12                     |

| SAL      | 50                |             | Shift A Left n Bits             | 6 + 2 n                |

| SAR      | 40                |             | Shift A Right n Bits            | 6 + 2 n                |

| SLR      | 44                |             | Shift L Right n Bits            | 6 + 2 n                |

| SøL      | 00                |             | Set Output Lines                | 6                      |

| SSS      | 62                |             | Store Spread Sign               | 18                     |

| STB      | 42                |             | Store Bank Register             | 12                     |

| STL      | 32                |             | Store L                         | 12                     |

| STU      | 22                |             | Store U                         | 12                     |

| SUB      | 24                |             | Subtract                        | 12                     |

| TML      | 02                |             | Transfer on Minus L             | 6                      |

| TMU      | 16                |             | Transfer on Minus U             | 6                      |

| TRA      | 56                |             | Indirect Transfer               | 12                     |

| TRB      | 06                |             | Transfer in Bank                | 6                      |

| TSR      | 52                |             | Indirect Transfer and<br>Return | 18                     |

| TZL      | 12                |             | Transfer if ZERO L              | 6                      |

| WøL      | 20                | 0           | Write Output from L             | 12                     |

| WøU      | 20                | 1           | Write Output from U             | 12                     |

| XUL      | 66                | 1 0         | Exchange U&L                    | 18                     |

AUTONETICS

#### 4. Definitive Assumptions

The following assumptions were used to define program requirements in addition to those imposed by the stated purposes of the program:

- a. Computer Configuration

- 1. Random access storage

- 2. Single address command structure

- 3. Fixed execution times for all instructions

- 4. At least one full word of input

- 5. At least one full word of output

- b. Program Flexibility

Except for those functions which require a solution to unique analytical expressions or which are non-limit testing computations the program will have the following capabilities (as allowed by the available storage) without requiring any changes to the main program or subroutines:

- 1. Input any number of data values in any order.

- 2. Generate and test any number of computer values at individually assigned rates.

- 3. Accept information from and generate output data for any number of display devices of various types.

- 4. Modification of the program after being loaded will allow the substitution, deletion, or limit and scaling constant changes for any input or output parameter without disturbing the main program functions or timing.

- c. Input Format

All input data for all parameters will be conditioned to have a magnitude between fixed limits and will be binary integers.

24 AUTONETICS A DIVISION OF NORTH AMERICAN AVIATION. INC. d. Output Formats

All output data will consist of one of the following:

- 1. Parameter Identification at least 16 six-bit binary code alphameric characters.

- 2. Limits and Values four 4-bit binary code decimal characters.

- 3. Telemetry Data a parameter identification code plus the input value in conditioned units in one word.

- 4. Display Device Controls a full word with specific portions having control over unique device functions.

- 5. Manually Generated Commands a full word with specific portions allocated to unique instructions and parameter identifications.

#### 5. Program Structure

a. Discussion

The following, which consists of a description of a program structure or memory allocation scheme, was developed for the purposes of estimating memory and timing requirements for a program which would satisfy the conditions imposed by the program purposes stated in Par. 3 and the assumptions listed in Par. 4 The inclusion of this program in the report does not imply that it is the only method of satisfying the imposed conditions. It is, however, a reasonable and sufficient method of meeting the conditions. The memory and timing requirements which were computed for it are not grossly different from those which would be computed for any other programming scheme which satisfies the conditions.

All of the main parts of the program and its subroutines were partially or completely coded using the instructions for a computer satisfying the requirements stated in Exhibit A of Contract NAS4-883 and the assumed conditions stated in Par. 4.a. (Autonetics D26J). The memory and timing data were obtained by analyzing the coded information and by estimating minor linkage and control functions. All timing information is in terms of computer clock rate (bit rate).

The basic program structure consists of an Execution Section which contains all of the executable sequences (except for those parameters which require a unique solution) and the remainder of the memory contains all of the input/output dependent constants in modular blocks and the unique program sequences.

b. Execution Section

This section accomplishes all of the normal computations, limit testing, control and input-output functions of the program. Its size is independent of the number of parameters being processed either for input or output. It is in the form of a program loop which repeats at a fixed, predictable rate dependent on the number of Constants Blocks being processed. The Execution Section is described in functional form in Fig. 9. The number of words of storage for each function is shown and the time required to process each modular block of constants is noted.

c. Constants Block

Each Constants Block contains the definition, status and numerical constant words for 16 input parameters, 16 output parameters, 4 display devices, 2 special limit test function controls and 2 special nonlimit test function controls. These ratios were determined by (1) analyzing the types and number of input and output parameters, the display device capabilities and the special function requirements and, (2) making the program have the capability of operating in systems of various sizes as determined by the number of input and output parameters required. A format for a Constants Block is shown in Fig. 10 with memory word requirements.

d. Program Dependent System Size Capabilities

The following information indicates the range of system sizes which can be accommodated by the varying number of Constants Blocks in the memory. The Execution Section will process up to 16 constants blocks without a programmed change.

- 16 to 256 input and output parameters in increments of 16 parameters.

- 2. 4 to 64 display devices in increments of 4 devices. Each device can have from 1 to 32 parameters assigned to it for display and control.

AUTONETICS

Linear Interpolation tables for converting input values to engineering units (10 words/input parameter x 16 parameters = 160 words)

Raw Input Data Storage

(1 word/parameter x 16 parameters = 16 words)

Converted Input Data Storage

(1 word/parameter x 16 paramters = 16 words)

Output parameter constants storage two limits and one constant

(3 words/parameter x 16 parameters = 48 words)

Output parameter control, Identification and Status Storage (8/parameter x 16 parameters = 128 words)

Alphameric Identification and Descriptive Storage (5 words/parameter x 16 parameters = 80 words)

Display Device Control, Identification and Status Storage (6 words/device x 4 devices = 24 words)

Special Limit Test Function Transfer Controls (4 per function x 2 functions = 8 words)

Special Non Limit Test Function Transfer Controls (4 per function x 2 functions = 8 words)

Total memory required = 488 words

Fig. 10. Constants Block Memory Allocation

- 3. 2 to 32 special limit test function routines in increments of 2 routines.

- 4. 2 to 32 special non-limit test function routines in increments of 2 routines.

- e. Memory Time Estimates versus System Size

The following information shown in Fig. 11 represents minimum requirements in that no special functions have been included. The memory and time requirements for special functions are dependent on the complexity of the individual functions and the memory and time requirements would be in addition to the indicated minimum requirements.

f. Special Limit Test Functions Memory and Time Estimates

The following functions are presented to indicate the types of computations which could be performed using one or more input parameters for the purpose of testing the computed result against stored limits. The estimates were predicated on having particular noted types of input data available and the complexity of the analytical expression for generating the required parameter value.

1. MACH from Pressure Measurements

Given: a.

$$p_d$$

, dynamic pressure (lb/ft<sup>2</sup>)

b.  $p_s$ , static pressure (lb/ft<sup>2</sup>)

c. MACH =  $\sqrt{5}\sqrt{\left(\frac{p_s}{p_d + p_s}\right)^{.286}}$  - 1

Memory required = 90 words

Time required = 1120 time units

2. Flare Computer Equations

Memory required = 2500 words

Time required = 100,000 time units

Note: The above was derived from information contained in EM-0363-113 prepared by Autonetics for Contract NAS2-1201.

29

AUTONETICS

A DIVISION OF NORTH AMERICAN AVIATION, INC.

τ.

| Number of<br>Constants<br>Blocks | Number of<br>Input/Output<br>Parameters | Number of<br>Display<br>Devices | Number of<br>Special Limit<br>Test Functions | Number of<br>Other<br>Functions | Memory<br>Words<br>Required | Time<br>(1000 units) |

|----------------------------------|-----------------------------------------|---------------------------------|----------------------------------------------|---------------------------------|-----------------------------|----------------------|

| 1                                | 16                                      | 4                               | 2                                            | 2                               | 2000                        | 25                   |

| 2                                | 32                                      | 8                               | 4                                            | 4                               | 2500                        | 50                   |

| 3                                | 48                                      | 12                              | 6                                            | 6                               | 3000                        | 75                   |

| 4                                | 64                                      | 16                              | 8                                            | 8                               | 3500                        | 100                  |

| 5                                | 80                                      | 20                              | 10                                           | 10                              | 4000                        | 125                  |

| 6                                | 96                                      | 24                              | 12                                           | 12                              | 4500                        | 150                  |

| 7                                | 112                                     | 28                              | 14                                           | 14                              | 5000                        | 175                  |

| 8                                | 128                                     | 32                              | 16                                           | 16                              | 5500                        | 200                  |

| 9                                | 144                                     | 36                              | 18                                           | 18                              | 6000                        | 225                  |

| 10                               | 160                                     | 40                              | 20                                           | 20                              | 6500                        | 250                  |

| 11                               | 176                                     | 44                              | 22                                           | 22                              | 7000                        | 275                  |

| 12                               | 192                                     | 48                              | 24                                           | 24                              | 7500                        | 300                  |

| 13                               | 208                                     | 52                              | 26                                           | 26                              | 8000                        | 325                  |

| 14                               | 224                                     | 56                              | 28                                           | 28                              | 8500                        | 350                  |

| 15                               | 240                                     | 60                              | 30                                           | 30                              | 9000                        | 375                  |

| 16                               | 256                                     | 64                              | 32                                           | 32                              | 9500                        | 400                  |

|                                  |                                         | l                               |                                              |                                 |                             |                      |

Fig. 11. Memory and Time Estimates versus System Size

30

AUTONETICS

# 3. True Airspeed

Given: a. V,, indicated airspeed

- b. A, altitude

- c. a 50 point table of density versus altitude

- d. Va, actual airspeed =  $\left(\frac{P_o}{P_a}\right)^{1/2}$  V<sub>i</sub>

where p = standard air density

$p_{2}$  = density of altitude A

Memory required = 145 words

Time required = 843 time units

4. Angle of Attack and Side Slip

Given: a. Vehicle orientation: heading, inclination and roll

b. Vehicle Velocity Vector: dx, dy and dz in a known inertial reference system.

Memory required = 190 words

Time required = 1970 time units

g. Special Non-Limit Test Functions Memory and Time Estimates

The following functions are presented to indicate the types of computation which could be performed for purposes other than warning analysis.

1. Atmospheric Density

Given: a.  $p_s$ , static pressure (lb/ft<sup>2</sup>) b. T, Temperature in F c. R, gas constant d. p, atmospheric density =  $\frac{P_s}{(T+540)R}$

AUTONETICS

Memory required = 25

Time required = 330 time units

2. Actual Versus Planned Profile Computations

Given: a. a 1000 point table of time versus planned profile, (A<sub>i</sub>)

- b. actual heighth value in a known inertial reference system, (a)

- c. at any time (t) output the planned heighth  $(A_t)$ , the actual heighth (a) and the error,  $\Delta a = A_t - a$

Memory required = 2050 words

Time required = 190 time units

h. Change Capabilities

The descriptions of the methods of changing the program are presented in three classes; (1) changes prior to program loading, (2) changes while the computer is connected to the ground control panel and (3) changes immediately prior to or during the mission.

- 1. Changes prior to loading all changes for this category require changes in the loading tape, either the generation of a new program tape or portions of the program tape.

- 2. Changes while the computer is connected to the ground control panels - Any input or output parameter can be deleted, modified or substituted by manually entering a constant or constants into known locations in the appropriate Constants Block. Any special function can be deleted or modified by entering a constant or constants into known locations in the appropriate Constants Block. It is possible to substitute a new special function sequence for an existing one either manually or by a special tape, however, for all but very simple functions, this technique is impractical.

- 3. Changes immediately prior to or during the mission No parameters may be added or substituted at this time. Parameters can be inhibited to prevent display, if they are assigned to a manually controllable display panel.

#### 6. Timing and Functional Capability Versus Memory Size

The functional configurations described in this section are presented to demonstrate the types of applications which can be installed in the system and the flexibility of functional formats that can be accomplished without changing the main program. The total time indicated for each case represents the minimum cycle or iteration time interval for the configuration. This time interval can be increased to any desired value by storing an appropriate value in a constant location which is used by a Loop Control Delay Timer.

The numbers of input parameters, output parameters special functions and display devices for each of the configurations are specifically for the configuration and do not represent the limits for the associated memory size. The total possible number of each of these items which can be controlled is a function of the number of Constants Blocks in the configuration. Each Constants Block can control 16 input parameters, 16 output parameters, 4 display devices, 2 special limit test functions and 2 special non limit test functions.

- a. Capability with a 4096 Word Memory

- 1. Typical Configuration

64 input parameters, 64 output parameters, 3 special limit test functions, 1 special non limit test function and up to 16 display devices

| Function                                         | Memory Words | Time<br>(ms) |

|--------------------------------------------------|--------------|--------------|

| Control 4 constants blocks at<br>49.340 ms/block | 3470         | 197.4        |

| Angle of Attack and Sideslip                     | 190          | 3.9          |

| MACH from Pressure Measure                       | ments 90     | 22           |

| True Airspeed                                    | 145          | 1.7          |

| Atmospheric                                      | 25           | 0.3          |

| Unused Words                                     | 176          |              |

| Totals                                           | 4096         | 205.5        |

## 2. Configuration with no Special Functions

80 Input Parameters, 80 Output Parameters and control of up to 20 Display Devices

| Function                                      |        | Memory Words | Time<br>(ms) |  |

|-----------------------------------------------|--------|--------------|--------------|--|

| Control 5 Constants/Blo<br>at 49.340 ms/Block | cks    | 3970         | 246.7        |  |

| Unused Words                                  |        | 126          |              |  |

|                                               | ſotals | 4096         | 246.7        |  |

#### b. Capability with an 8192 Word Memory

1. Typical Configuration

128 input parameters, 128 output parameters, 4 special limit test functions, 1 non-limit test function and control of up to 32 display devices

| <b>Function</b>                                  | Memory Words | Time<br>(ms) |

|--------------------------------------------------|--------------|--------------|

| Control 8 Constants Blocks<br>at 49.340 ms/Block | 5470         | 394.7        |

| MACH from Pressure Measuremen                    | ts 90        | 2.2          |

| True Airspeed                                    | 145          | 1.7          |

| Angle of Attack and Sideslip                     | 190          | 3.9          |

| Atmospheric Density                              | 25           | 0.3          |

| Actual Versus Planned Mission<br>Profile         | 2050         | 0.4          |

| Unused Words                                     | 222          |              |

| Totals                                           | 8192         | 403.2        |

## 2. Configuration with Flare Computer Computations

128 input parameters, 128 output parameters, 1 special limit test function, flare computer computations and control of up to 32 display devices

| Function                                        | Memory Words | Time<br>(ms)   |

|-------------------------------------------------|--------------|----------------|

| Control 8 Constants Block<br>at 49.340 ms/Block | 5470         | 394 <b>.</b> 7 |

| Flare Computer Computations                     | 2500         | 200.0          |

| Angle of Attack and Side Slip                   | 190          | 3.9            |

| Unused Words                                    | 32           |                |

| Totals                                          | 8192         | 598.6          |

## 3. Configuration with No Special Functions

The following configuration will allow 208 input parameters, 208 output parameters and control of 52 display devices.

| Function                                          | Memory Words | Time<br>(ms) |

|---------------------------------------------------|--------------|--------------|

| Control 13 Constants Blocks<br>at 49.340 ms/Block | 7970         | 661.4        |

| Unused Words                                      | 222          |              |

| Total                                             | s 8192       | 661.4        |

#### VI. AWARE PCM DETAILED DESCRIPTION

#### A. PCM CIRCUIT DESIGN

A conservative design approach was taken on the application of microcircuit technology. Proven analytical techniques were used to determine the optimum method of mechanizing each circuit function. The result of these analyses indicate that a combination of hybrid thin film circuits, discrete components, and integrated circuits would provide a minimum sized package.

The physical description is as follows:

1. Basic PCM Data Processor

The physical characteristics are:

| Size    | $8-1/2 \ge 11-1/2 \ge 4-3/4$ in.              |

|---------|-----------------------------------------------|

| Weight  | 17 lb                                         |

| Power   | 58 w at 28 vdc                                |

| Cooling | None required between 50 and 85 F ambient air |

2. Add-On 128-Channel Multiplexer

The physical characteristics are:

| Size    | $8-1/2 \ge 8-1/2 \ge 4-3/4$ in.               |

|---------|-----------------------------------------------|

| Weight  | 12 lb                                         |

| Power   | 26 w at 28 vdc                                |

| Cooling | None required between 50 and 85 F ambient air |

The Basic PCM System and the Add-On 192-Channel Multiplexer are packaged as shown in Fig. 5 and 6. The packages are made from cast aluminum. The packaging design incorporates in its design provisions for RFI integrity. In addition, the packaging design will have thermal characteristics which will allow continuous operation of the units in an ambient environment between 50 and 85 F.

#### 1. ADC Operation

During the telemeter analog and analog frame sync words, the ADC converts multiplexed analog voltage samples into a digital representation. For the telemeter analog word, the digital representation is serially stored in an 8-flip-flop encoding register. Each bit of this stored digital information is telemetered to the ground station one bit time after it is generated.

The philosophy in the design of the ADC is to generate and present to a comparator an analog voltage which converges toward the level of the analog input signal with each successive bit time. The generated analog voltage is obtained by a resistive ladder network which is controlled by the 8-flip-flop encoding register. The encoding process may be called one of "successive approximation." The analog equivalent of the binary register is successively compared with the input signal until agreement (within the accuracy of the comparator) occurs. During telemeter analog words, the analog data is encoded to 8 bits, accurate to the least significant bit (20 mv). During word 0, the analog data is encoded to 9 bits which is accurate to 10 mv. During the encoding of a telemeter analog word, the serial readout of the flip-flop encoding register is feasible because the flip-flops are required to contribute to the ladder network in a sequential order. In order to readout at the first bit time of a telemeter analog word, encoding must commence during the last bit time of the previous word which may be either a telemeter analog word, computer word, or analog frame sync word.

2. Drift Correction - Encoding During the Analog Frame Sync Word

During segment "A", word 0 of each analog frame sync word, the ADC is calibrated to a precision ground level. The ground level is programmed from the multiplexer to the input of the ADC and encoding of this signal follows a process similar to that explained in the previous discussion. However, in the encoding of the precision

ground level, an additional flip-flop is added to the 8-flip-flop encoding register and the ADC is increased to 9-bit resolution. Since an additional flip-flop has been added to the encoding register, the encoding process must be prolonged for one extra bit time as compared to encoding during an analog word. After the ground signal has been encoded, the three least significant flip-flops of the encoding register are copied by three drift correction flip-flops. The drift correction flip-flops then remain frozen throughout an analog frame until the ADC is calibrated again at the next word 0.

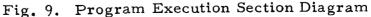

#### 3. Basic Multiplexer

The basic multiplexer is a precision high-speed, 64-channel analog multiplexer providing random channel selection, high common mode rejection, programmable gain selection, and sample-and-hold capability. The basic multiplexer will be an integral part of the basic PCM Digital Data Processor and will operate separately or in conjunction with the Add-on 192-channel multiplexer.

The multiplexer will be capable of multiplexing 0 to 50 mv and 0 to 5 v analog signals and providing a gain of 100 or unity, respectively, as programmed by the DDP. The overall accuracy of the multiplexer subsystem including the sample and hold circuit will be 0.5 percent of full scale for the 0 to 5 v channels and 0.6 percent of full scale for the 0 to 50 mv scales. The input impedance to the multiplexer will be greater than 500 k for the closed condition of the multiplexer switch, and greater than 1 megohm for the open condition of the multiplexer switch. The feedback current to the data source for a 0 to 50 mv channel will not exceed 300 nanoamperes and for the 0 to 5 v channels will not exceed 1 microampere. Under command of the DDP, the multiplexer will select the analog input channel and provide a 0 to 5 v PAM output to the ADC at a data rate of 25,600 words per second.

The multiplexer unit shall be capable of rejecting dc common mode potentials over the range of a minus 10 to a plus 10 v with a common mode rejection ratio of 5000:1 on 5 v channels, and 20,000:1 on 50 mv channels.

The multiplexer unit shall be capable of rejecting ac common mode potentials of 200 mv. The 5-v channel ac common mode rejection ratio is 5000:1 at dc decreasing linearly with increasing frequency to 2000:1 at 10 kc. The 50 mv channel ac common mode rejection ratio

is 20,000:1 at dc decreasing linearly with increasing frequency to 2000:1 at 10 kc. The multiplexer will provide this common mode rejection capability for data source impedances of up to 1000 ohms resistive or 5000 ohms shunted by 0.5 uf to 150 uf. To aid achievement of this common mode rejection capability, the multiplexer will contain its own dc-to-dc converter power supplies.

A block diagram of the basic multiplexer is shown in Fig. 12. The operation of the multiplexer is explained in the following paragraphs, with the aid of the timing and sequencing diagram, Fig. 13.

#### 4. Programming and Configuration Control

The loading of the multiplexer program into the DDP multiplexer programmer is accomplished from the ground test equipment utilizing a conventional tape reader and associated loading electronics. The mechanisms associated with transferring the information from the program punched tape into the core memory is basic memory loading technology. The configuration control, and programming of the multiplexer program tapes will be discussed to illustrate the programming flexibility attainable while still maintaining strict configuration control of the multiplexer programs.

The task of programming may either be accomplished by a computer or manually. In either case the basic considerations of the number of channels available, required sampling rates, and maximum total number of samples per second must be observed.

Upon obtaining the desired program the programming information is transferred to punched tape. The tape may be punched and verified by a computer. Configuration control of the punched tape may be maintained similar to Instrumentation Control Drawings, or Airborne Computer programming tapes.

#### 5. Multiplexer Timing

The timing as it relates to the multiplexer, for one 27-bit data word, will be discussed to provide details on the sequencing. At the leading edge of bit time  $T_1$ , all multiplexer gates will be disabled by the Data Strobe Signal. The six channel select lines and two multiplexer select lines for the next channel to be selected will be true from the DDP during the multiplexer select data-on-time as shown in Fig. 13, and will be clocked into the multiplexer register on the

Fig. 12. Basic Analog Multiplexer

ł

Fig. 13. Multiplexer Timing and Sequencing Diagram

lagging edge of the Data Strobe. The multiplexer differential amplifier will settle out in the "B" gate on-time, and will be sampled by the sample-and-hold during bit times 12 and 13 for approximately 5 usec. The "B" word will be digitized during bit time  $T_{16}$  through  $T_{23}$ . The The Data Strobe will disable the multiplexer switches on the leading edge of  $T_{14}$  and clock in the "A" gate select information on the lagging edge of  $T_{14}$ . The multiplexer differential amplifier will settle out during the subsequent 12-bit times and will be sampled by the sampleand-hold circuit starting on the leading edge of  $T_{25}$  for approximately 5 usec. The "A" word will be digitized during bit times  $T_{27}$  through  $T_7$  ( $T_8$  during word 0) of the subsequent word. This sequence will be repeated for each data word.

The basic multiplexer will consist of the following four functional blocks:

- 1. Logic decoder and register

- 2. 64-channel differential input solid state switching circuit

- 3. A precision wideband differential amplifier

- 4. A high speed sample-and-hold circuit

- a. Logic Decoder and Register

The Logic Decoder interfaces with the DDP (Multiplexer Programmer) and decodes the programmer signals for sequencing the multiplexer system. The control lines from the DDP consist of 11 signals. These signals are:

- 1. Six channel select signals: providing random selection of any one of the 64 analog input channels.

- 2. Two multiplexer select signals: providing selection of either the basic or one of the inputs from the three 64channel groups of the add-on multiplexer.

- 3. One gain select signal: providing the appropriate gain selection for a 0 50 mv or 0 to 5 v channel.

- 4. One data strobe signal to disable the analog switches during the decoder register transition period.

- 5. One sample strobe signal to control the sample-and-hold circuit.

The Logic Decoder is transformer coupled to the DDP control lines and floating to provide necessary isolation for common mode rejection requirements.

#### b. Differential Input Switching Circuit

The switching circuits will be constructed using hybrid thin film techniques employing discrete field-effect transistors (FET's) as the cwitching elements for the differential input channels. The hybrid thin film circuits will be enclosed in metal cans to provide electrostatic shielding of the low level input signals.

The discrete FET's were selected in preference to the integrated FET switches because they are field-proven to provide highest performance, reliability, versatility and ease of fault location.

The field-effect transistor is ideally suited for switching applications caused by the following desirable characteristics:

- 1. Low "ON" offset voltage

- 2. Low "OFF" leakage current

- 3. High "OFF" resistance

The basic limitations of the FET as a switching element is the variation in resistance of the ON condition and the capacitance to the gate circuit. With a differential amplifier input impedance of 500 k ohms or greater, the loading error of the two gates in each circuit will be less than 0.12 percent. The actual error will be considerably less than this figure, since the amplifier will initially be fabricated to offset the nominal FET switch resistive loading error, thereby reducing the error to the variation in the resistance of the FET's, rather than their absolute resistances. The actual error should be less than 0.04 percent. By using isolated power supplies in conjunction with the FET switches, the gate capacitance effect can be reduced considerably, so that the error contribution, including common mode current, will fall well within the acceptable value.

A representative schematic diagram of a differential switch using the FET switch element is shown in Fig. 14. When the control signal is true, the FET  $Q_1$  will appear as a low resistance, thereby applying a positive voltage to the gate load of  $Q_2$  and  $Q_3$ . Field-effect transistors  $Q_2$  and  $Q_3$ , which make up one differential input signal channel switch, will then turn on, thereby closing the double pole single throw switch.

c. Differential Amplifier

The multiplexer differential amplifier provides the isolation and amplification of the multiplexed analog signals. Because of the important role the amplifier plays in the multiplexer subsystem a detailed discussion of the design considerations are presented in Appendix B. A summary of the capability provided by the amplifier is given in Table 2.

| Table 2. Summary of Amplifier Capability |                                                                                 |                                                              |  |

|------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------|--|

| Voltage Gain:                            | Program selected s                                                              | Program selected steps of 1 and 100                          |  |

| Input Impedance:                         | Greater than 500 k s<br>transistor input cap                                    | •                                                            |  |

| Output Voltage:                          | 0 to $+5$ v nominal                                                             |                                                              |  |

| Settling Time:                           | In 30 usec to within of final value                                             | In 30 usec to within 0.05 percent of final value             |  |

| Common Mode Rejection:                   |                                                                                 |                                                              |  |

| DC Common Mode:                          | Common Mode Potential ±10 v<br>Source Impedance: 1000 ohms or<br>less resistive |                                                              |  |

|                                          |                                                                                 | l0 to 5000 ohms<br>resistive,<br>shunted by<br>0.5 to 150 uf |  |

|                                          | Rejection Ratio:                                                                | 20,000:1 for<br>50 mv channels                               |  |

|                                          |                                                                                 | 5,000:1 for 5 v<br>channels                                  |  |

| 4                                        | .4                                                                              |                                                              |  |

Table 2. (Cont)

AC Common Mode: Common Mode Potential 200 mvac

| Source Impedance: | As defined under<br>dc Common Mode<br>Source Impedance                                                                                                                                               |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rejection Ratio:  | 20,000:1 at dc<br>decreasing linearly<br>with frequency to<br>2000:1 at 10 kc<br>for 50 mv channels<br>5000:1 at dc<br>decreasing linearly<br>with frequency to<br>2000:1 at 10 kc<br>for 5 channels |

The programmable gain capability allows the use of a single differential amplifier. The voltage gain to be applied is selected by the DDP independently for each of the 64 channels.

d. Sample and Hold Circuit

The sample and hold circuit will be a hybrid thin film circuit using uncased transistors and diodes. The following requirements will be met by the sample and hold circuits:

| SAMPLE TIME    | Maximum of 5 usec occurring during the final 5 usec of amplifier settle time                     |

|----------------|--------------------------------------------------------------------------------------------------|

| HOLD TIME      | Minimum of 11 bit times (2.89 usec/bit)                                                          |

| ACCURACY       | Better than 0.15 percent of full scale                                                           |

| DATA SELECTION | Multiplexes the four differential<br>amplifier outputs from the basic and<br>add-on multiplexers |

The sample and hold circuit provides the capability for accurately measuring at finite points in time the varying dc outputs from the differential amplifier(s). It provides a constant, (held), output to the ADC during the digitizing process and allows the differential amplifier(s) to settle on the next data sample.

R, can be either a discrete resistor, thin film resistor, or a properly biased FET.

# Fig. 14. Double Pole, Single Throw FET Switch

#### 6. Add-On 192 Channel Multiplexer

The Add-On Multiplexer unit will be very similar to the Basic Multiplexer unit, with the exception of size. It will provide the capability for multiplexing 192 different channels and its differential amplifier outputs will be multiplexed into the Basic Multiplexer Sampleand-Hold circuit under DDP control. The circuit boards from the Add-On Multiplexer and the Basic Multiplexer will be interchangeable.

A block diagram of the add-on multiplexer is shown in Fig. 15. As can be seen by comparing the basic multiplexer shown in Fig. 12 with Fig. 15, the Add-On Multiplexer consists of three 64-channel multiplexer sections identical to the Basic Multiplexer with the exception of the Sample and Hold circuit.

7. Packaging

- a. PCM Data Processor Packaging and Thermal Characteristics

- (1) Physical Description.

(a) Packaging. The PCM Data Processor is packaged in a cast aluminum chassis having the required structural and thermal characteristics in addition to its primary function of containing the electronics and power supplies. The two power supply modules are mounted adjacent to the power input connector.

In order to achieve the best thermal characteristics with the restriction that no additional cooling outside of the compartment ambient is available, heat dissipating fins have been made an integral part of the chassis. Aluminum was chosen because of its high thermal conductivity in addition to other desirable physical properties. To achieve maximum heat transfer, the electronics boards are fastened to support structures with captive screws torqued down to effect a thermal interface of the board with the chassis. Analysis and tests have shown this method to be thermally efficient, and reduces the machining required when using board guide slots and other mechanical retainers.

Radio frequency interference integrity is maintained through the use of an RFI seal between the chassis and covers. The power input is protected by the use of an RFI filter integral with the input power connector. The unit, in addition to the RFI seal, has an environmental seal protecting the electronics against dust and moisture.

Interconnection of the electronics is effected through a single multilayer interconnect board (MIB) utilizing pin and socket connectors. The concept of design and construction have been perfected on the Minuteman II D37 Computer and utilizes the same connectors and fabrication techniques. Interconnections within the power supply section are effected by conventional point-to-point wire harness techniques.

(b) Thermal Considerations. The thermal design of this unit is similar to the method used in the D37C computer except that this unit makes use of free convection and radiation to remove heat from the package while the D37C computer is water cooled.

Heat generated within the unit is conducted along heat conducting strips on the module beards, through a controlled thermal joint and into the chassis. Once the heat has entered the chassis it is distributed uniformly throughout the chassis and is removed from the unit via free convection and radiation. To facilitate heat transfer from the unit, the ends are finned with 1/8 in. thick, 0.5 in. high fins. Radiation heat transfer is enhanced by providing the unit with a high emissivity (dull black) surface finish. The chassis material will have a minimum thermal conductivity of

92  $\frac{\text{BTU Ft}}{\text{Hr Ft}^2 \text{F}}$

b. Add-On Multiplexer Packaging

The add-on multiplexer will be packaged in an  $8.5 \times 8.5 \times 4.75$ in. cast aluminum chassis. The weight of the complete unit will be less than 12 lb. The chassis will provide necessary structural and thermal characteristics in addition to containing the circuit electronics.

To provide circuit card interchangeability and system uniformity, the add-on multiplexer chassis will be very similar to the basic PCM system chassis. The basic structure, thermal, and RFI characteristics will consequently be similar to those previously discussed, and will not be discussed here.

49

#### **B. D26 DETAILED DESCRIPTION**

Small size, low power consumption and reliable operation are prime requirements in airborne and space-system computers. To meet these objectives, Autonetics developed the D26J family of microminiature digital computers.

D26J logic design features parallel word transfer and computation, integrated circuits, coincident-current core memory, and advanced multilayer board construction.

D26J random access core memory can be expanded from 1024, twelve-bit words to 16,384, sixteen-bit words. Random access memory and parallel processing mean rapid computing speeds typified by a 12 usec add time and a 54 usec multiply time.

#### 1. Operational Characteristics

D26J has the speed necessary to perform the computations required in a real time control system. Speeds shown in Table 3 include access times for both data and instructions; the speeds are for a 16-bit version of the D26J.

Table 3. Typical Operation Times

| Add 16 b | its     | 12  | usec |

|----------|---------|-----|------|

| Add 32 b | its     | 18  | usec |

| Multiply | 16 bits | 54  | usec |

|          | 32 bits | 270 | usec |

| Divide   | 16 bits | 108 | usec |

D26J has double precision add, subtract, and store capability. It can be programmed for double precision multiplication and division. Double precision makes more effective use of memory because instructions and many words can be stored in the 16 (or 12) bit word length. A 16 (or 12) bit word allows faster arithmetic operations than a longer word. But double precision allows more accuracy where it is needed.

AUTONETICS

50

#### 2. Physical Characteristics

A D26J is composed of a general purpose section, an input/ output section and a memory. The general purpose (GP) section contains an arithmetic unit and control unit. This GP section is the same for any D26J. The input/output section and memory are tailored to user needs.

The D26J can vary in size, weight and power depending on I/O, memory size and word length. Table 4 lists the general characteristics of the D26J family.

Table 4. Characteristics of the D26J

General

| Type | Stored-program,   | general purpose | computer with |

|------|-------------------|-----------------|---------------|

|      | single-address lo | gic             |               |

| Data       | $\mathbf{Parallel}$ |

|------------|---------------------|

| Processing |                     |

Clock Rate 500 kilopulses/sec

Memory

Type Random-access core

Capacity 1024, 4096, 8192, or 16,384 words with 6 usec cycle time

Arithmetic

Numbe**r** System

perBinary with negative numbers represented inmtwo's complement form

Word Length

Instruction The 16-bit computer word has 5 bits for the operation code and 9 bits for operand address. The remaining 2 bits are spares and can be used as I/O instructions. The 12-bit computer word has 5 bits for the operation code and 7 bits for operand address.

Table 4. (Cont)

| Data                 | Single-precision, 12 bits including sign for the 12-bit machine. Sixteen bits including sign for the 16-bit machine. |

|----------------------|----------------------------------------------------------------------------------------------------------------------|

| Double-<br>Precision | Twenty three bits including sign for the 12-bit machine; 31 bits including sign for the 16-bit                       |

machine. The second sign bit is not used in

#### 3. Environmental Characteristics

The D26J case is hermetically sealed to protect it from humidity, sand, dust, and salt spray.

double-precision.

The computer will operate without malfunction under the following environmental conditions in all axes:

45 g sustained acceleration 100 g shock 11 ms

100 g (rms) vibration 10-2000 cps

It will operate in ambient magnetic fields up to 10 gauss and will operate in an ambient pressure environment from deep space (approaching zero psia) to pressures up to 45 psia without permanent degradations.

4. Input/Output Characteristics

A computer must be flexible if it is to communicate with other subsystems. Some subsystems use incremental information; for example, from accelerometers, fuel flow meters, and raw data from Doppler navigation systems. Flight control and CRT displays are d-c voltage devices while angle and attitude sensors for inertial navigation platform gimbals, star trackers, and radar antennas operate on shaft position information. The D26J communicates in all these forms.

The D26J input/output section is tailored to meet system needs and can be expanded, if necessary, with only a minor redesign.

52

#### 5. Packaging