X-521-67-271

# NASA TM X- 55828

# SOME VECTOR GENERATING TECHNIQUES FOR CATHODE RAY TUBE (CRT) DISPLAY SYSTEMS

## HERBERT R. DURBECK

BY

N<u>67-31302</u>

| (THRU)     |  |

|------------|--|

| /          |  |

| (CODE)     |  |

| 09         |  |

| (CATEGORY) |  |

|            |  |

### **JUNE 1967**

NASA

GODDARD SPACE FLIGHT CENTER GREENBELT, MARYLAND

X-521-67-271

#### SOME VECTOR GENERATING TECHNIQUES FOR CATHODE RAY TUBE (CRT) DISPLAY SYSTEMS

i

Herbert R. Durbeck

June 1967

GODDARD SPACE FLIGHT CENTER Greenbelt, Maryland

### PRECEDING PAGE BLANK NOT FILMED.

1/ -

#### CONTENTS

|                                                                  | Page  |

|------------------------------------------------------------------|-------|

| INTRODUCTION                                                     | 1     |

| GENERAL DISCUSSION                                               | 1     |

| INCREMENTAL POINT POSITIONING VS STROKE METHOD                   | 2     |

| AN INCREMENTAL POINT POSITIONING METHOD<br>FOR VECTOR GENERATION | 3     |

| GENERAL DISCUSSION OF STROKE VECTOR GENERATORS                   | 5     |

| A STROKE TYPE VECTOR GENERATOR                                   | , 11  |

| CONCLUSION                                                       | . 13  |

| APPENDIX A                                                       | . A-1 |

| APPENDIX B                                                       | . B-1 |

| APPENDIX C                                                       | . C-1 |

#### SOME VECTOR GENERATING TECHNIQUES FOR CATHODE RAY TUBE (CRT) DISPLAY SYSTEMS

#### INTRODUCTION

There exists at present a widespread use of Cathode Ray Tube (CRT) Systems for the display of computer generated data. Many of the older CRT display systems and some of the lower priced newer systems contain character generators for the production of alphanumeric characters, but have no vector generators for drawing graphic information. If at some time graphic display capability is required, a decision must be made as to whether the needed vector generator is to be purchased or developed in-house. There is a definite lack of information about vector generating techniques upon which to base this decision. This is also the case when buying a new CRT display system with an integral vector generator and trying to decide which system offers the most suitable graphic capability.

The purpose of this report is to provide a general discussion of vector generating techniques and to describe two straight-forward line drawing schemes for CRT display systems.

#### GENERAL DISCUSSION

This report will be confined to considering vector generating procedures for non-scan CRT displays, which constitute the majority of CRT display systems available today. In these systems electrical signals are supplied to horizontal (X) and vertical (Y) deflection circuits and the electron beam is moved to a position on the CRT screen, determined by the magnitude of these signals. Normally, digital X,Y information is generated by the computer to which the display system is attached, or by internal logic circuitry, and passed through D/A converters, amplifier and compensation circuitry to the deflection system of the CRT. The electron beam is moved to this position and a symbol, specified by an input code from the attached computer, is drawn by the character generator.

In order to produce a line segment on the CRT screen, the initial X, Y coordinates and the terminal X,Y coordinates must be presented to a vector generator by the attached computer. The electron beam is then moved from the initial to the terminal position in such a manner as to produce a straight line segment. Alternately, the initial X,Y coordinates and the horizontal  $(\Delta x)$  and vertical  $(\Delta Y)$  increments can be presented to the vector generator with the same effect. The vector generator can produce line segments in two different ways. It can generate a series of points between the initial and final coordinates of the vector, the incremental point positioning method, or it can continuously provide the deflection signal required to move the electron beam smoothly in a straight line path from the initial to the final location, the stroke method.

## INCREMENTAL POINT POSITIONING VS STROKE METHOD

The incremental point positioning method has the following advantages: complete compatibility with the original display system requiring no modification of the display system analog circuitry, accuracy and inherent stability, complete endpoint matching for connected vectors.

Furthermore, the intensity compensation that is required for some stroke type vector generators, when drawing vectors of different lengths, is not needed when using the incremental point positioning method, since all vectors, regardless of length, have equal brightness.

The incremental point positioning method has, however, the following disadvantages: line segments are a collection of points and not continuous, the time required for vector generation is high, there is a noticeable departure from a straight line for some of the simpler point generating techniques, there is little flexibility for adaptation to more complex curve generation (circular, parabolic, hyperbolic, etc.).

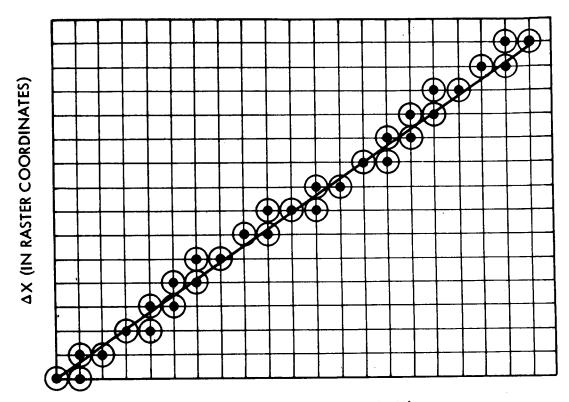

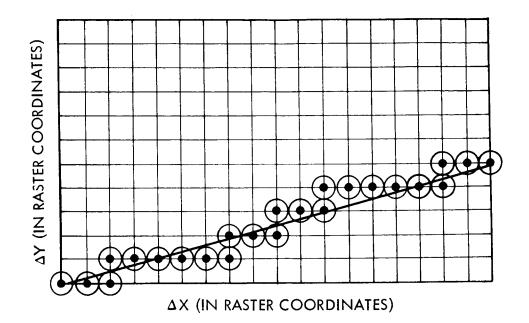

The quality of the vectors generated by the incremental point positioning method depends primarily on the point generating algorithm, the spot size of the electron beam, and the raster matrix used for point positioning. By the raster matrix we mean here the matrix of individually addressable discrete points, formed on the face of the CRT. Roughly, if the spot diameter is equal to or larger than the distance between adjacent raster points, good line continuity is achieved by a vector generator that plots points in near adjacent locations in generating a line. Of course, the more raster points that are addressable the better a straight line segment can be approximated, but on the other hand, the more points must be produced to construct a given vector. Most CRT display systems have a 1024 by 1024 raster matrix.

The principal reason for having a vector generator of the incremental point positioning type, rather than none at all, is to remove the necessity of storing

$\mathbf{2}$

all the intermediate points of a given line segment in the display computer, or the refresh buffer memory. No significant writing speed advantage is achieved by this method, except when the display computer or buffer refresh memory have a very slow memory cycle time.

#### AN INCREMENTAL POINT POSITIONING METHOD FOR VECTOR GENERATION

In this section one scheme of vector generation, using the incremental point positioning method will be presented. For the purposes of this discussion let us assume that we are given a typical display system having the following characteristics:

| Random Positioning time of the beam on the CRT face | 15 $\mu sec$       |

|-----------------------------------------------------|--------------------|

| Time Required to generate an adjacent point         | $1 \ \mu { m sec}$ |

| CRT display area                                    | 10" x 10"          |

| Raster matrix                                       | 1024 x 1024        |

| Display refresh rate                                | 30 times/second    |

In order to keep the vector drawing time within reasonable limits let us assume that the vector generator will produce up to 64 points per given increments  $\Delta X$  and  $\Delta Y$ . This corresponds to 6 bits and one sign bit in the  $\Delta X$  and  $\Delta Y$ registers, respectively, and a vector write time of 64  $\mu$  sec plus positioning time. For this system up to approximately 333 inches of connected vectors can be generated per flicker free frame.\*

The basic circuit requirements for this vector generator are:

- (a) a seven bit  $\triangle X$  register

- (b) a seven bit  $\triangle Y$  register

- (c) a 1 megahertz clock

<sup>\*</sup>This approximation is obtained by noting that for the system specified, the distance between adjacent raster points is approximately 0.01 inches. Since points are generated at a rate of one per microsecond for one thirtieth of a second (then the display must be refreshed), a total of .0333 sec

$<sup>\</sup>frac{.0333 \text{ sec}}{1 \times 10^{-6} \text{ sec}} = 3.33 \times 10^4$  points can be generated. This corresponds to 333 inches of line display.

- (d) a six stage counter

- (e) logic gates required to implement the point generating algorithm (this will be described in more detail in Appendix A)

- (f) The ten bit X and Y registers (normally found in the display system) which specify the instantaneous location of the electron beam will be replaced by two ten stage up/down counters with parallel input. This will not affect the normal operation of the display system.

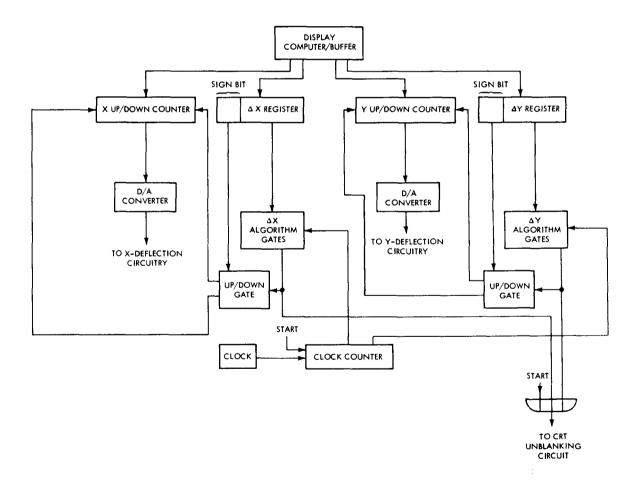

The functional diagram of the vector generator is given in Figure 1.

The display computer loads the X and Y up/down counters (by parallel input), and the  $\Delta X$  and  $\Delta Y$  registers. The coordinates of the starting point of the

4

vector are stored in the X and Y up/down counters, respectively, and the X and Y increments are stored in the  $\Delta X$  and  $\Delta Y$  registers, respectively. The internal logic of the display system will generate a signal to start the clock counter sequence. The successive states of the clock counter are gated with the  $\Delta X$  and  $\Delta Y$  registers through the  $\Delta X$  and  $\Delta Y$  Algorithm Gates and the resultant pulses are either added to or subtracted from the numbers stored in the X and Y up/down counters, depending on the state of the sign bit in the  $\Delta X$  and  $\Delta Y$  registers. Each time a pulse passes through either the  $\Delta X$  or  $\Delta Y$  Algorithm Gates a signal is routed to the CRT unblanking circuitry and a point is generated on the face of the CRT. The START pulse is also passed on to the unblanking circuits and is used to produce a point at the starting position of the vector. By this procedure a set of points is generated which will closely approximate the desired vector. The comparison between the actual vector and the generated set of points will be made in Appendix A, where the Algorithm Gates are discussed. The gating for the START pulse, the STOP and RESET of the clock counter at the end of the 64th count is not shown, but implied in Figure 1.

At the end of the 64th count the clock counter is reset and clock pulses to the counter are inhibited. The display computer can now load the X and Y counters and  $\Delta X$  and  $\Delta Y$  registers again and a new vector generating cycle can begin. For connected vectors only the  $\Delta X$  and  $\Delta Y$  registers will be loaded by the computer, since the electron beam is already at the starting point of the vector.

The main limitation of this method is the time required to generate a given vector. Other considerations are the fact that for the system just described the time required to draw a short and long vector is constant (64  $\mu$ sec + positioning time) and that the maximum vector length for one set of computer instructions is only one-sixteenth of the full diagonal distance on the CRT face. These last two limitations can be overcome by additional logic circuitry as will be shown in Appendix B. But it is unlikely that the time required to plot adjacent points can be reduced much below 1  $\mu$ sec; so that little can be done to lessen the total vector generating time. When the requirement for endpoint accuracy, stability, and compatibility with the original display system are the over-riding considerations, a longer vector generating time might be tolerable (especially if only a small amount of graphic information has to be displayed at one time). The extreme accuracy and stability of this method for vector generation makes its use desirable in computer aided design systems.

#### GENERAL DISCUSSION OF STROKE TYPE VECTOR GENERATORS

The two major limitations of the incremental point positioning technique, excessive vector drawing time and lack of continuity of the generated vectors, can be eliminated with the stroke method of line generation. Here a continuous signal is sent to the deflection circuitry of the CRT by the vector generator and the electron beam is moved smoothly from the initial to the terminal point.

There are basically two different types of deflection systems available for CRT's: electrostatic and electromagnetic.\*

The characteristics of both types of deflection systems are summarized below:<sup>†</sup>

| Characteristic           | Electromagnetic                        | Electrostatic                   |

|--------------------------|----------------------------------------|---------------------------------|

| Beam focus               | Well focused through-<br>out tube area | Beam defocused at<br>tube edges |

| Internal Structure       | Simple                                 | Complex                         |

| Tube Length              | Short                                  | Long                            |

| Spot brightness          | High                                   | Moderate                        |

| Deflection Sensitivity   | High                                   | Low                             |

| Complexity of Amplifiers | High                                   | Low                             |

| Deflection Speed         | Low                                    | High                            |

| Weight                   | Heavy                                  | Light                           |

Since electromagnetic deflection offers the advantages of a well defined beam over the entire tube face, high spot brightness, and high deflection sensitivity most present day display systems employ this mode of deflection.

For both types of systems, however, the shapes of the signals that must be produced by the vector generators are very similar. The difference between the two systems are found primarily in the different types of amplifiers that are required to drive the deflection circuits.

<sup>\*</sup>There is also a hybrid electrostatic-electromagnetic system where the electromagnetic portion is used for large deflections and the electrostatic for small deflections. In this case the electrostatic deflection is utilized to generate alphanumeric symbols at locations specified by the large scale electromagnetic deflection. The electromagnetic deflection is used for vector generation. +Charles W. Adams Associates, Inc., Computer Display Review, II. 11.0

For electrostatic deflection\*

$$\mathbf{D} = \mathbf{K}_1 \quad \frac{\mathbf{V}_1}{\mathbf{V}}$$

where, D = distance the beam is deflected from the center of the CRT face by the deflection voltage  $V_1$ .

$V_1$  = potential difference between deflection plates

V = accelerating voltage of the electron beam

$K_1$  = constant factor that is determined by the tube construction

For electromagnetic deflection<sup>†</sup>

$$D = K_2 \frac{H}{\sqrt{V}}$$

where D = distance the beam is deflected from the CRT face center by the magnetic field H

H = magnitude of the magnetic field at the center of the deflection coil

V = accelerating voltage of the electron beam

$K_{2}$  = constant factor that is determined by the tube construction

But since for a current carrying coil (containing no ferromagnet) the magnetic field in the interior is approximately proportional to this current.<sup>‡</sup>

$$\mathbf{H} = \mathbf{K}'' \quad \mathbf{i}$$

and,

Ì

$$D = \frac{K_3 i}{\sqrt{V}}$$

where i = current through the coil

$K_3 = tube parameter$

K" = deflection coil parameter

†Ibid, p. 304

‡Ibid, p. 3

<sup>\*</sup>Theodore Soller, Merle A. Starr, George E. Valley, Jr., Editors, MIT Radiation Laboratory Series, Cathode Ray Tube Display, McGraw Hill Book Company, 1948, p. 64

Thus it can be seen that in the electrostatic case the deflection of the electron beam is proportional to the potential difference between the deflection plates and in the electromagnetic case the deflection is proportional to the current in the deflection coil. The deflection speed of the beam is limited primarily by the capacitative time constant of the deflection plates in the electrostatic case and by the inductive time constant of the deflection coil in the electromagnetic case.

The function of the vector generator is to present linearly changing electrical signals to the X and Y deflection circuitry of the CRT, such that the amplitudes of the signals are proportional to  $\Delta X$  and  $\Delta Y$  respectively.

There are two ways in which the vector generator can do this. It can produce deflection signals which will cause the electron beam to go from the initial to the final point in a constant time interval, regardless of vector length - constant time vector generator. Or it can produce deflection signals which will cause the electron beam to travel from the initial to the final point with a fixed velocity - constant velocity vector generator.

The constant velocity method is preferable for two reasons. First, since the beam travels with a uniform speed over the face of the CRT, all vectors, regardless of length, will have the same brightness. Second, since most graphic information consists of a large collection of short length vectors, or combinations at short and long vectors, a more efficient use of the display system is made. In contrast, for the constant time vector generating scheme it takes as long to draw short vectors as it does long vectors, and the vector drawing time must be chosen to be of such a magnitude so as to allow the generation of the longest vector in the fixed time interval. Furthermore, since both long and short vectors are drawn in the same time period, the short vectors will be generated more slowly across the CRT than the long vectors and thus appear brighter, unless intensity compensation circuitry is provided.

However, it appears that constant time vector generators of good quality are easier to implement than the corresponding constant velocity generators.

For constant velocity vector generation the following vector generating procedure is followed (after the coordinates of the starting point and  $\triangle X$  and  $\triangle Y$  have been loaded into the appropriate registers of the display system by the display computer):

1. Compute the total vector length "L"

$L = \sqrt{(\Delta X)^2 + (\Delta Y)^2}$

2. Compute the time "T" required to draw the given vector

T = L/Swhere S = constant vector speed

3. Compute the X and Y components of velocity  $"S_1"$  and  $"S_2"$

where  $S_1 = \Delta X/T$

$$S_2 = \Delta Y/T$$

- 4. Generate a sawtooth signal for the X-deflection circuitry whose slope is "S<sub>1</sub>", for a time interval "T".

- 5. Simultaneously generate a sawtooth signal for the Y-deflection circuitry whose slope is "S<sub>2</sub>" for a time interval "T".

- 6. At the same time unblank the CRT beam for a time interval "T".

Even though the required calculations can be performed by analog, digital, and/or approximational techniques, all of the above functional steps must be carried out by the constant velocity vector generator.

On the other hand for the constant time vector generator the electron beam unblanking time is usually fixed. In that time interval sawtooth waveforms, whose slopes depend on the values found in the  $\triangle X$  and  $\triangle Y$  registers, are presented to the X and Y deflection circuitry of the CRT. Various methods are used to accomplish this, from the charging of delay lines to the use of operational amplifiers as high quality integrators. Perhaps the simplest, but not necessarily best, method is to convert the  $\triangle X$  and  $\triangle Y$  values (by D/A converters) to two square wavepulses whose amplitudes are proportional to the magnitudes of the numbers stored in the  $\Delta X$  and  $\Delta Y$  registers respectively. Then these pulses are presented to the X and Y deflection circuits and the triangular waveforms (whose forward slopes are used to deflect the CRT beam) are generated by the integration of the applied pulses through the inherent impedances of the deflection circuits. The main problem in this case is the lack of control over the integrating time constants, since these are determined by the structure of the deflection circuits. Also, unless the X and Y deflection circuit time constants are identical, amplitude compensation circuits must be provided after the D/A conversion of  $\triangle X$  and  $\triangle Y$ . Normally, vectors generated by this method are excessively distorted.

A constant time method of vector generation that provides control of the integrating time constant and yet is fairly simple to implement will be discussed in a section below.

The requirement of intensity compensation for constant time vector generators generally involves the determination of the vector length, since the intensity modulation of the CRT beam is proportional to this length.

Mathematically,

I = kL

where, I = intensity modulation required

L =length of the generated vector

k = parameter that depends on the CRT characteristics

As before,

-

$$L = \sqrt{(\Delta X)^2 + (\Delta Y)^2}$$

For the purposes of intensity compensation the following crude assumption can be made,

$$\mathbf{L} \approx \triangle \mathbf{X} + \triangle \mathbf{Y}$$

So that,

$$\mathbf{I} \approx \mathbf{k} (\Delta \mathbf{X} + \Delta \mathbf{Y})$$

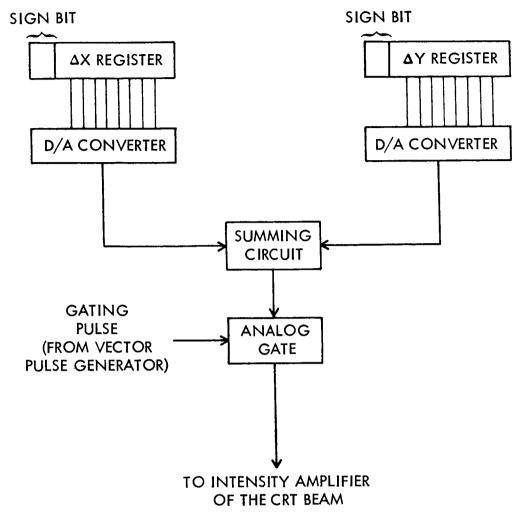

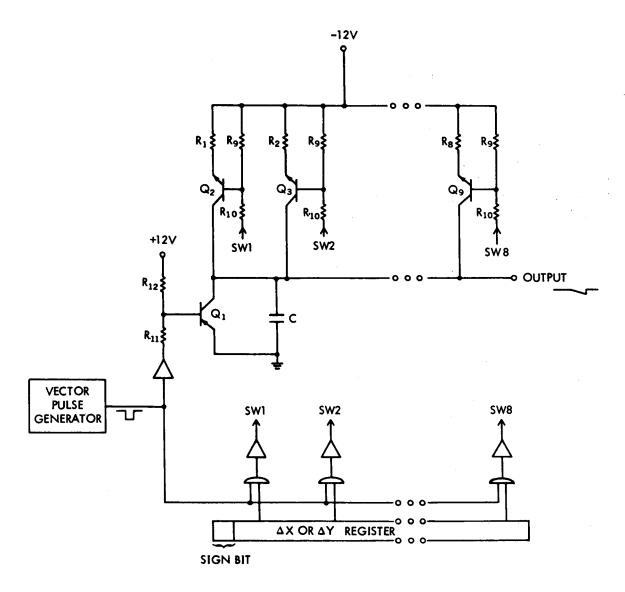

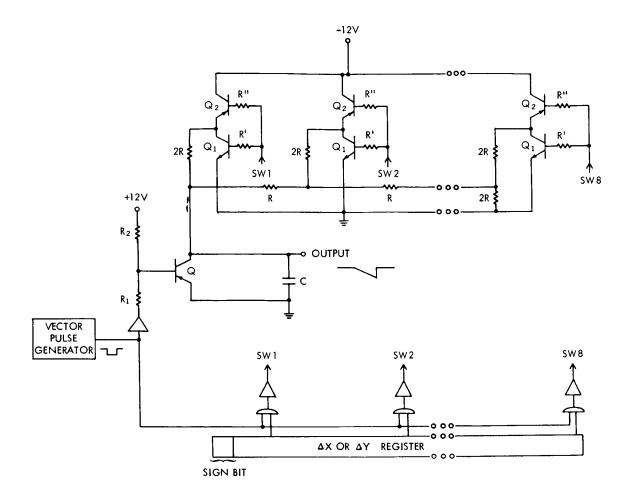

This approximation will not provide perfect intensity compensation, but will considerably facilitate implementation. One method for intensity compensation is then, clearly, to pass the magnitudes of  $\triangle X$  and  $\triangle Y$  through D/A converters, sum the result, and use it to modulate the amplifier that controls the intensity of the CRT beam.

At present the majority of the commerically available vector generators is of the constant time stroke variety. However, this is only a slim majority and, as component prices drop and the demand for display system increases, the constant velocity vector generators are becoming more and more popular.

#### A STROKE TYPE VECTOR GENERATOR

In this section a fairly simple and easy to implement approach to constant time stroke type vector generation will be presented.

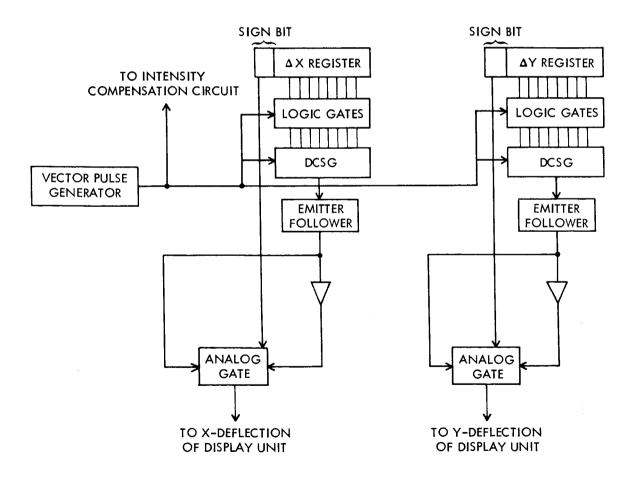

Basically, this method consists of producing sawtooth waveforms whose slopes depend on the magnitude of the numbers stored in the  $\Delta X$  and  $\Delta Y$  registers by means of two digitally controlled sawtooth generators (DCSG's) (the design of these DCSG's will be discussed in Appendix C). The resultant sawtooth waveforms are either inverted or not, depending on the values of the sign bits in the  $\Delta X$  and  $\Delta Y$  registers, and then passed on to the X and Y deflection circuitry of the CRT. A block diagram of this system is given in Figure 2.

The pulse generator will produce a timing pulse of fixed duration, starting at the beginning of the vector drawing sequence. In this time interval, the

Figure 2.

variable slope  $\Delta X$  and  $\Delta Y$  waveforms are produced and the CRT beam is unblanked. The time interval, which is essentially limited by the electrical inertia of the deflection circuitry, must be of sufficient length to allow the CRT beam to be deflected through the maximum vector increment.

Each analog gate in Figure 2 is really a combination of 2 analog gates, both controlled by the logical state of the respective sign bit, allowing either the sawtooth or its inverse to be transmitted to the CRT deflection circuitry.

The logic gates indicated in Figure 2 were implemented (see Appendix C) using Packard Bell Transistor Logic Cards. If digital logic cards, operating between different voltage levels are used, then the base biasing resistors of Figure C-1 will have to be adjusted accordingly.

The inverters shown in the functional diagram of the system (Figure 2) should be high quality DC amplifiers having as small a DC offset as possible. This can be achieved with a good grade operational amplifier, whose feedback loop is adjusted to provide a gain of unity.\*

The analog gates required to switch either the sawtooth or its inverse into the deflection system of the CRT can be implemented using Diode Bridge, transistor, or FET switching methods given in Johnson\*\* or Korn and Korn<sup>†</sup>. Good quality analog switches are also commercially available at reasonable prices<sup>††</sup>.

The intensity compensation required can be of the simple summation type mentioned at the end of the last section and is shown in Figure 3. As can be seen the modulation of the electron beam is only present in the vector drawing time interval as specified by the vector pulse generator.

This method offers the advantage of being able to display continuous vectors at high rates (being able to display a large amount of graphic information at one time). It can be readily applied in man/machine command and control consoles, where overall status is presented graphically and parameters requiring a high degree of accuracy are presented numerically, or in time shared remote consoles for the handling of mathematical problems, requiring the analysis of complex curves.

<sup>\*</sup>Burr-Brown Research Corporation, Handbook of Operational Amplifier Applications, pp. 8-10

<sup>\*\*</sup>T. E. Johnson, <u>Analog Generator for Real Time Display of Curves</u>, MIT Lincoln Laboratory, Technical Report 398, 28 July 1965

<sup>&</sup>lt;sup>†</sup>Granine A. Korn and Theresa M. Korn, <u>Electronic Analog and Hybrid Computers</u>, McGraw Hill Book Company, 1964, pp. 219-233

<sup>††</sup>Philco, System 4-D Digital System Building Blocks Applications Manual, SU-02, SU-04, SU-06, SU-03 analog Switch units specification sheets

Figure 3.

#### CONCLUSION

It can be seen that vector generators, either of the incremental point positioning or stroke type, depending on the user's requirements can be readily constructed. The incremental point positioning type vector generator can be implemented using any standard commercial digital logic line, requiring a minimum amount of system development.

The stroke type vector generator, while probably needing less hardware requires more development, because of its hybrid nature, but has the potential of providing more effective utilization of the graphic capability of the CRT.

#### APPENDIX A

#### Algorithm Gates for the Seven Bit Incremental

#### Point Positioning Vector Generator

As was mentioned, when the functional diagram of this vector generator (Figure 1) was discussed, the  $\Delta X$  and  $\Delta Y$  Algorithm Gates basically extract point generating pulses from the clock counter states, depending on the values stored in the  $\Delta X$  and  $\Delta Y$  registers.

Since the operation of the  $\Delta X$  and  $\Delta Y$  Algorithm Gates is identical, only the  $\Delta X$  Algorithm Gates will be described. The gating action will take place between the  $\Delta X$  register and the clock counter, and the resultant point generating pulses are passed on to the X up/down counter.

Let A = X up/down counter

$\mathbf{B} = \Delta \mathbf{X}$  register

C = clock counter

Let the letters with subscripts indicate the condition of a bit stage of a given counter or register. Thus  $A_0$  represents the first stage of the X up/down counter. The convention followed here is that the largest digit is stored in the lowest numbered stage. Thus  $A_1$  stores a digit that is twice as large as an equivalent digit in  $A_2$ , and  $A_9$  is least significant digit of the A up/down counter.

| A Up/Down Counter | A <sub>0</sub> | A              | A <sub>2</sub> | A <sub>3</sub> | A <sub>4</sub> | A <sub>5</sub> | A <sub>6</sub> | A <sub>7</sub> | A <sub>8</sub> | A <sub>9</sub> |

|-------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| B Register        | B <sub>0</sub> | B <sub>1</sub> | B <sub>2</sub> | B3             | B4             | B <sub>5</sub> | B <sub>6</sub> |                |                |                |

| C Counter         | C <sub>0</sub> | C <sub>1</sub> | C <sub>2</sub> | C3             | C <sub>4</sub> | C <sub>5</sub> |                |                |                |                |

In the B register  $B_0$  will represent the sign of  $\Delta X$ . Let "0" represent a "+" sign and "1" represent a "-" sign, where "+" causes the X up/down counter "A" to be set to count up and the "-" sign causes the X up/down counter A to be set to count down.

Basically, the higher digits of the  $\triangle X$  register are logically "anded" with the lower digits of the clock counter and the resultant pulses are either added

to or subtracted from the X up/down counter, depending on the value of the sign bit in  $\Delta X$ . For example, if the  $\Delta X$  register consists of all "1's" then every clock counter pulse will pass through the Algorithm Gates and produce a point on the CRT. If B<sub>1</sub> is "1" and the rest of the digits are all zero, then every other counter pulse is passed through the Algorithm gates and 32 points are produced.

If any of the more significant bits in the  $\triangle X$  register are "0's" followed by "1's" then we say that there exists a "gap" at the location of the first less significant "1".

Example, 000110 Gap position

In this case all the counter bits up to the corresponding gap are "anded" with zeros and pulses are passed on to the X up/down counter, if an "and/or" condition exists for all consecutive "1's" (in the B register) following the gap.

In this way the correct total number of pulses are passed on to the X up/ down counter (as will be illustrated by some examples in this appendix), producing the required vector increment  $\Delta X$ .

#### Sign bit

For example if the  $\triangle X$  register reads 0000110 then only the following clock counter states are passed through Algorithm Gates to produce point pulses:

| C <sub>0</sub> | C1 | C <sub>2</sub> | С <sub>3</sub> | C4 | C <sub>5</sub> | Decimal Equivalent of ter state | the clock coun- |

|----------------|----|----------------|----------------|----|----------------|---------------------------------|-----------------|

| 0              | 0  | 1              | 0              | 0  | 0              | 8                               |                 |

| 0              | 1  | 0              | 0              | 0  | 0              | 16                              | 1               |

| 0              | 1  | 1              | 0              | 0  | 0              | 24                              | - ( <b>)</b>    |

| 1              | 0  | 1              | 0              | 0  | 0              | 40                              |                 |

| 1              | 1  | 0              | 0              | 0  | 0              | 48                              |                 |

| 1              | 1  | 1              | 0              | 0  | 0              | 56                              |                 |

As can be seen, the 8th, 16th, etc. clock counts produce points. Of course, another point is produced at the starting location by the start pulse. Clearly, 6 incremental points are generated corresponding to  $\Delta X = 6$ .

A nice feature is the fact that the generated points are fairly evenly distributed over the clock counter cycle, corresponding to a nearly uniform change

A-2

in the X coordinate with time. Since the same procedure is followed by the Y portion of the vector generator, the requirement of a constant slope for the generated line is almost satisfied.

1.1

Let us express the logical gating required in terms of Boolean Algebra.

The most significant bit of the  $\Delta X$  register is "anded" with the least significant bit of the clock counter, the next most significant bit of  $\triangle X$  with the next least significant bit of the clock counter, etc., providing that no "gap" condition exists. If a "gap" is present then in order for a point pulse to be produced, all the less significant bit positions of the clock counter up to the "gap" must be zero, and all the following bits of the clock counter are "anded" with the bits of the B register, as before.

A point pulse " $P_x$ " is produced when any one of the following conditions exists:

| UNID               |                |                |                  |                    |                    |                    | (X h           | nere i         | indica         | tion c<br>ates t<br>'or" | chat a         | e ΔX register<br>a given bit |

|--------------------|----------------|----------------|------------------|--------------------|--------------------|--------------------|----------------|----------------|----------------|--------------------------|----------------|------------------------------|

|                    |                |                |                  |                    |                    |                    | B <sub>1</sub> | B <sub>2</sub> | B <sub>3</sub> | B <sub>4</sub>           | B <sub>5</sub> | B <sub>6</sub>               |

| B <sub>1</sub>     | C <sub>5</sub> |                |                  |                    |                    |                    | 1              |                |                |                          |                |                              |

| B1                 | B <sub>2</sub> | C4             |                  |                    |                    |                    | 1              | 1              |                |                          |                |                              |

| B <sub>1</sub>     | B <sub>2</sub> | C <b>4</b>     | ₹ <mark>5</mark> |                    |                    |                    | 0              | 1              |                |                          |                |                              |

| B <sub>1</sub>     | B <sub>2</sub> | B3             | C3               |                    |                    |                    | 1              | 1              | 1              |                          |                |                              |

| ₿ <sub>1</sub>     | B <sub>2</sub> | B3             | C3               | $\overline{C}_5$   |                    |                    | 0              | 1              | 1              |                          |                |                              |

| $\overline{B}_2$   | B <sub>3</sub> | С <b>з</b>     | $\overline{C}_4$ | $\overline{C}_{5}$ |                    |                    | Х              | 0              | 1              |                          |                |                              |

| B <sub>1</sub>     | B <sub>2</sub> | B <sub>3</sub> | B4               | C2                 |                    |                    | 1              | 1              | 1              | 1                        |                |                              |

| ₽ <mark>₿</mark>   | B <sub>2</sub> | B3             | B4               | C2                 | €5                 |                    | 0              | 1              | 1              | 1                        |                |                              |

| $\overline{B}_2$   | B <sub>3</sub> | B4             | C <sub>2</sub>   | $\overline{C}_4$   | $\overline{C}_{5}$ |                    | X              | 0              | 1              | 1                        |                |                              |

| $\overline{B}_{3}$ | B4             | C <sub>2</sub> | ₽<br>₽           | $\overline{C}_4$   | $\overline{C}_{5}$ |                    | X              | X              | 0              | 1                        |                |                              |

| B <sub>1</sub>     | B <sub>2</sub> | B3             | B4               | B <sub>5</sub>     | C1                 |                    | 1              | 1              | 1              | 1                        | 1              |                              |

| $\overline{B}_1$   | B <sub>2</sub> | B3             | B4               | B <sub>5</sub>     | C <sub>1</sub>     | $\overline{C}_{5}$ | 0              | 1              | 1              | 1                        | 1              |                              |

| $\overline{B}_2$   | B <sub>3</sub> | B4             | B <sub>5</sub>   | C <sub>1</sub>     | $\overline{C}_4$   | $\overline{C}_{5}$ | Х              | 0              | 1              | 1                        | 1              |                              |

| $\bar{B}_3$        | B4             | B <sub>5</sub> | C <sub>1</sub>   | ₹ <mark>3</mark>   | $\overline{C}_4$   | $\overline{C}_5$   | Х              | X              | 0              | 1                        | 1              |                              |

| $\overline{B}_4$   | B <sub>5</sub> | C1             | $\overline{C}_2$ | ₽<br>₽             | $\overline{C}_4$   | $\overline{C}_{5}$ | X              | X              | X              | 0                        | 1              |                              |

A-3

|                                                                                                                   |                                                       |                                                                                                                            |                                                      |                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ÷                                                                                                                                                                       |                                                                                         |                                                                  | B <sub>1</sub>                                                                | B <sub>2</sub>                                                          | B <sub>3</sub>                                                | B <sub>4</sub> | B <sub>5</sub>        | B <sub>6</sub> |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------|----------------|-----------------------|----------------|

| B <sub>1</sub>                                                                                                    | B <sub>2</sub>                                        | B <sub>3</sub>                                                                                                             | B4                                                   | B <sub>5</sub>                                                                                                                                                                                    | B <sub>6</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C <sub>0</sub>                                                                                                                                                          |                                                                                         |                                                                  | 1                                                                             | 1                                                                       | 1                                                             | 1              | 1                     | 1              |

| B <sub>1</sub>                                                                                                    | B <sub>2</sub>                                        | B3                                                                                                                         | B4                                                   | B <sub>5</sub>                                                                                                                                                                                    | B <sub>6</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C <sub>0</sub>                                                                                                                                                          | ₽ <b>5</b>                                                                              |                                                                  | 0                                                                             | 1                                                                       | 1                                                             | 1              | 1                     | 1              |

| $\overline{B}_2$                                                                                                  | B <sub>3</sub>                                        | B4                                                                                                                         | B <sub>5</sub>                                       | B <sub>6</sub>                                                                                                                                                                                    | C <sub>0</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ₹<br>₹                                                                                                                                                                  | $\overline{C}_{5}$                                                                      |                                                                  | X                                                                             | .0.                                                                     | 1                                                             | 1,             | 1                     | 1              |

| ₿ <sub>3</sub>                                                                                                    | B4                                                    | B <sub>5</sub>                                                                                                             | B <sub>6</sub>                                       | C <sub>0</sub>                                                                                                                                                                                    | <b>₹</b> 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\overline{C}_4$                                                                                                                                                        | ₹<br>5                                                                                  |                                                                  | X                                                                             | Х                                                                       | 0                                                             | 1              | 1                     | 1              |

| $\overline{B}_4$                                                                                                  | B <sub>5</sub>                                        | B <sub>6</sub>                                                                                                             | C <sub>0</sub>                                       | ₹₂                                                                                                                                                                                                | <b>₹</b> 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\overline{C}_4$                                                                                                                                                        | $\overline{C}_{5}$                                                                      |                                                                  | X                                                                             | X                                                                       | X                                                             | 0              | 1                     | 1              |

| $\mathbf{B}_{5}$                                                                                                  | B <sub>6</sub>                                        | C <sub>0</sub>                                                                                                             | $\overline{C_1}$                                     | <b>₹</b> 2                                                                                                                                                                                        | $\overline{C}_3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\overline{C}_4$                                                                                                                                                        | $\overline{C}_5$                                                                        |                                                                  | X                                                                             | X                                                                       | X                                                             | X              | 0                     | · 1            |

| $+ B_{1}$ $+ B_{1}$ $+ \overline{B}_{3}$ $+ \overline{B}_{1}$ $+ \overline{B}_{3}$ $+ B_{1}$ $+ \overline{B}_{2}$ | $B_2$ $B_2$ $B_4$ $B_2$ $B_4$ $B_2$ $B_4$ $B_2$ $B_3$ | B <sub>3</sub><br>B <sub>3</sub><br>C <sub>2</sub><br>B <sub>3</sub><br>B <sub>5</sub><br>B <sub>3</sub><br>B <sub>4</sub> | $C_3 + B_4$ $\overline{C}_3 + B_4$ $C_1 + B_4$ $B_5$ | $B_{2} C_{4}$ $\overline{B}_{1} E$ $C_{2} + \overline{E}$ $\overline{C}_{4} \overline{C}_{5}$ $B_{5} C_{1}$ $\overline{C}_{3} \overline{C}_{4}$ $B_{5} B_{6}$ $\overline{C}_{2} \overline{C}_{5}$ | $\begin{array}{cccc} \mathbf{B}_2 & \mathbf{B}_3 \\ \mathbf{B}_1 & \mathbf{B}_3 \\ \mathbf{B}_1 & \mathbf{C}_5 \\ \mathbf{B}_1 & \mathbf{C}_5 \\ \mathbf{C}_5 \\ \mathbf{C}_5 \\ \mathbf{C}_6 \\ $ | $\begin{array}{ccc} & C_{3} \\ & B_{3} \\ & B_{2} \\ & B_{2} \\ & + \overline{B}_{2} \\ & + \overline{B}_{4} \\ & + \overline{B}_{1} \\ & \overline{C}_{5} \end{array}$ | $ \overline{C}_{5} \\ B_{4} \\ B_{3} \\ B_{3} \\ B_{5} \\ B_{2} \\ - \overline{B}_{3} $ | $+ \overline{B}$ $C_{2}$ $B_{4}$ $B_{4}$ $C_{1}$ $B_{3}$ $B_{4}$ | $ \frac{\overline{C}_5}{B_5} $ $ \frac{B_5}{\overline{C}_2} $ $ B_4 $ $ B_5 $ | $+ \overline{B}_{2}$ $C_{1}$ $C_{1}$ $\overline{C}_{3}$ $B_{5}$ $B_{6}$ | $B_{3}$ $\overline{C}_{4}$ $\overline{C}_{4}$ $B_{6}$ $C_{0}$ | -              | 5<br>4 C <sub>5</sub> | i              |

This expression represents the action of the X Algorithm Gates. It can be reduced to:

$$P_{x} = B_{1} \quad C_{5} + B_{2} \quad (B_{1} + \overline{B}_{1} \quad \overline{C}_{5}) \quad (C_{4} + B_{3} \quad C_{3} + B_{3} \quad B_{4} \quad (C_{2} + B_{5} \quad C_{1} + B_{5} \quad B_{6} \quad C_{0})) + B_{5} \quad \overline{C}_{4} \quad \overline{C}_{5} \quad (C_{1} + B_{6} \quad C_{0}) \quad (\overline{B}_{4} \quad \overline{C}_{2} \quad \overline{C}_{3} + \overline{B}_{3} \quad B_{4} \quad \overline{C}_{3} + \overline{B}_{2} \quad B_{3} \quad B_{4}) + \overline{C}_{4} \quad \overline{C}_{5} \quad (\overline{B}_{2} \quad B_{3} \quad (C_{3} + B_{4} \quad C_{2}) + \overline{C}_{3} \quad (\overline{B}_{3} \quad B_{4} \quad C_{2} + \overline{B}_{5} \quad B_{6} \quad C_{0} \quad \overline{C}_{1} \quad \overline{C}_{2}))$$

Before actual implementation, this Boolean expression should be minimized by using a suitable computer minimization program.

It must be remembered that identical Algorithm Gates must be provided for the Y portion of the vector generator. At this point it will be useful to consider some examples of vector generation by this method

|                                 | B <sub>1</sub> | B <sub>2</sub> | B <sub>3</sub> | B4  | B <sub>5</sub> | B <sub>6</sub> |

|---------------------------------|----------------|----------------|----------------|-----|----------------|----------------|

| Let $\Delta X = 20$ (Decimal) = | 0              | 1              | 0              | 1   | 0              | 0              |

|                                 | $B_1'$         | $B'_2$         | $B'_3$         | B'4 | B'5            | B <sub>6</sub> |

| $\Delta Y = 14$ (Decimal) =     | 0              | 0              | 1              | 1   | 1              | 0              |