MARS SPACECRAFT POWER

SYSTEM DEVELOPMENT

— INTERIM REPORT

| GPO PRICE \$ _    |     |

|-------------------|-----|

| CFSTI PRICE(S) \$ |     |

| Hard copy (HC) _  | 300 |

| Microfiche (MF) _ | .65 |

ff 653 July 65

| ~         | N     | 68-        | 2    | 4 | 9 | 1 | 7 |        |

|-----------|-------|------------|------|---|---|---|---|--------|

| ORM 602   | (ACCE | SSION NUME | IER) |   | - |   |   | (THRU) |

| ICILITY F | 2/- C | (PAGES)    | 16 C | 3 | - |   |   | (CODE) |

# MARS SPACECRAFT POWER SYSTEM DEVELOPMENT - INTERIM REPORT

PREPARED BY:

J. HAYDEN

A. KIRPICH

R. PELLMANN

M. READ

$A_{\text{PPROVED}} \; B_{\text{Y}}$

R. P. Wolfson

PREPARED FOR

JET PROPULSION LABORATORY

CALIFORNIA INSTITUTE OF TECHNOLOGY

4800 OAK GROVE DRIVE

PASADENA, CALIFORNIA

UNDER JPL CONTRACT NO. 952150

SPACECRAFT DEPARTMENT

A Department of the Missile and Space Division

Valley Forge Space Technology Center

P. O. Box 8555 • Philadelphia, Penna. 19101

# PRECEDING PAGE BLANK NOT, FILMED.

## TABLE OF CONTENTS

| Section |                                         | Page |

|---------|-----------------------------------------|------|

| 1       | INTRODUCTION                            | 1-1  |

| 2       | CONSTRAINTS AND GUIDELINES              | 2-1  |

|         | 2.1 Power System Type                   | 2-1  |

|         | 2.2 Solar Array Orientation             | 2-1  |

|         | 2.3 Distribution                        | 2-1  |

|         | 2.4 Load Profile                        | 2-1  |

|         | 2.5 Transit and Orbit Characteristics   | 2-4  |

| 3       | POWER SYSTEM SELECTION                  | 3-1  |

|         | 3.1 Influence of Solar Array            | 3-1  |

|         | 3.2 Regulator Efficiency                | 3-4  |

|         | 3.3 Candidate Descriptions              | 3-5  |

|         | 3.4 Candidate Comparison                | 3-15 |

| 4       | BATTERY CONSIDERATIONS                  | 4-1  |

|         | 4.1 Requirements                        | 4-1  |

|         | 4.2 Battery Candidates                  | 4-1  |

| 5       | RELIABILITY SENSITIVITY STUDIES         | 5-1  |

|         | 5.1 Approach                            | 5-1  |

|         | 5.2 Series Example                      | 5-1  |

|         | 5.3 Parallel Example                    | 5-3  |

|         | 5.4 Fault Sensing and Switching         | 5-5  |

|         | 5.5 General Conclusions/Recommendations | 5-13 |

| 6       | FAULT SENSING CRITERIA                  | 6-1  |

|         | 6.1 Series Dissipative Regulator        | 6-5  |

|         | 6.2 Inverter or Converter               | 6-5  |

|         | 6.3 Switching Regulators                | 6-8  |

|         | 6.4 Shunt Regulator                     | 6-8  |

|         | 6.5 Discussion                          | 6-10 |

# TABLE OF CONTENTS (Cont)

| Section |       |                                                       | Page |

|---------|-------|-------------------------------------------------------|------|

| 7       | DIST  | RIBUTION FREQUENCY OPTIMIZATION                       | 7-1  |

|         | 7.1   | Inverter Weight                                       | 7-1  |

|         | 7.2   | Transformer-Rectifier (T/R) Weight                    | 7-3  |

|         | 7.3   | Power Source Weight                                   | 7-4  |

|         | 7.4   | Conclusions                                           | 7-6  |

| 8       | POW   | ER SWITCHING AND DISTRIBUTION                         | 8-1  |

|         | 8.1   | Flexibility                                           | 8-1  |

|         | 8.2   | Command Input Redundancy                              | 8-3  |

|         | 8.3   | Driver Failure Protection                             | 8-3  |

|         | 8.4   | Command Matrix Implementation                         | 8-4  |

|         | 8.5   | Noise Sensitivity                                     | 8-6  |

|         | 8.6   | Relay Coil Suppression                                | 8-7  |

|         | 8.8   | Contact Suppression                                   | 8-9  |

| 9       | MM    | 69 POWER SYSTEM CIRCUIT REVIEW                        | 9-1  |

|         | 9.1   | Diodes Across Power Transistors                       | 9-1  |

|         | 9.2   | Failure Detector Transient Susceptibility - Module 4A | 9-1  |

|         | 9.3   | Inverter Synchronization                              | 9-1  |

|         | 9.4   | Boost Regulator Overload Protection                   | 9-2  |

| 10      | FUT   | URE PLANS                                             | 10-1 |

| APPEND  | OIX A | PROCEDURE FOR PREDICTING SOLAR ARRAY VOLTAGE-         |      |

|         |       | CURRENT CHARACTERISTICS                               | A-1  |

| APPENI  | X B   | INVERTER EFFICIENCY ANALYSIS                          | B-1  |

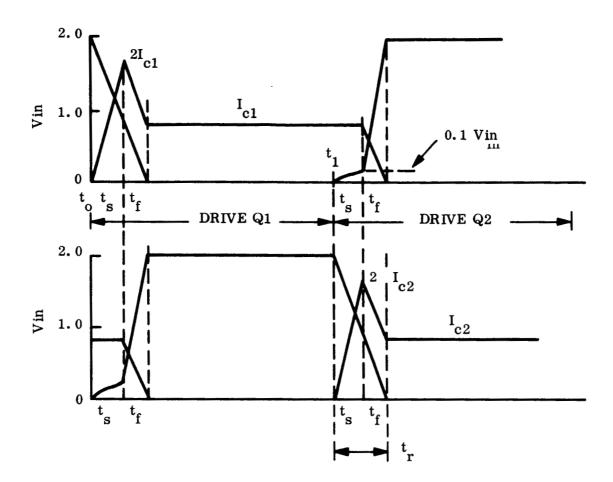

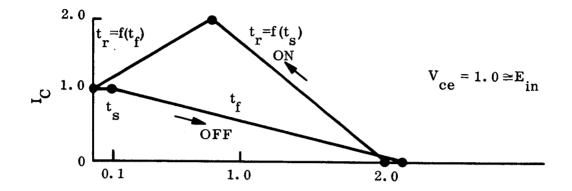

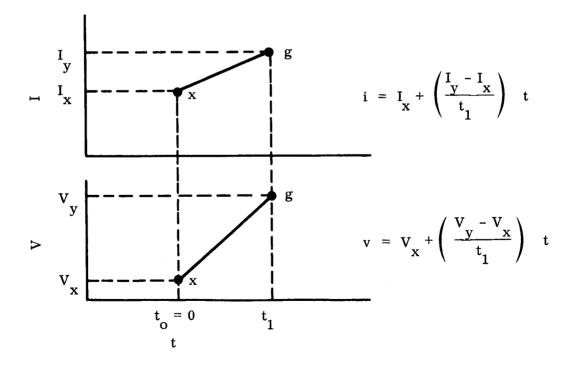

|         |       | B.1 Transistor Switching Losses                       | B-1  |

|         |       | B.2 Transistor Switching Diagrams                     | B-2  |

|         |       | B.3 Power Dissipation General Case                    | B-3  |

|         |       | B.4 Deviation of Transistor Switch Loss               | B-5  |

|         |       | B.5 Collector Current Frequency Correction            | B-7  |

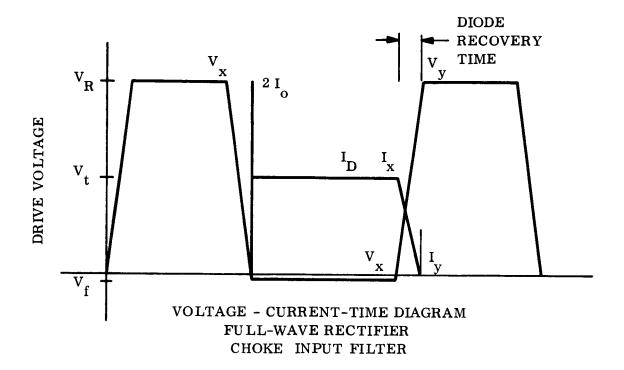

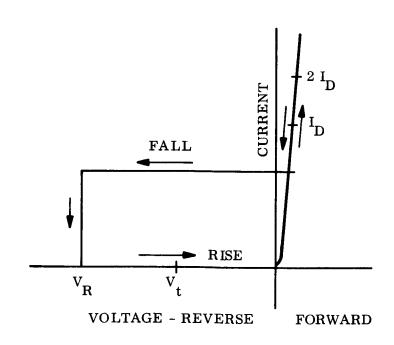

| APPEND  | OTX C | RECTIFIER SWITCHING LOSSES                            | C-1  |

## LIST OF ILLUSTRATIONS

| Figure      |                                                                      | Page            |

|-------------|----------------------------------------------------------------------|-----------------|

| 1-1         | Work Flow Diagram - Mass Spacecraft Power System Development.        | 1-1             |

| 3-1         | Normalized P-V Solar Array Curves                                    | 3-3             |

| 3-2         | Solar Array Temperature Versus Sun Distance                          | 3-3             |

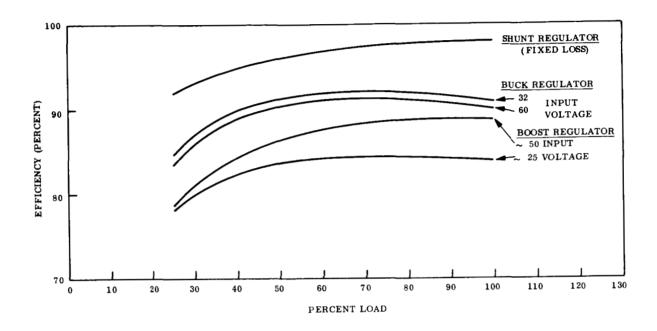

| 3-3         | Regulator Efficiency Data                                            | 3-4             |

| 3-4         | Boost Candidate                                                      | 3-7             |

| 3-5         | Buck Candidate                                                       | 3-8             |

| 3-6         | Shunt Candidate                                                      | 3-11            |

| 3-7         | Raw Power Source Alternative                                         | 3-12            |

| 3-8         | Shunt Regulator Options                                              | 3-13            |

| 3-9         | Shunt Performance                                                    | 3-14            |

| 4-1         | Ampere Hours Versus Charge Time                                      | 4-3             |

| 4-2         | Charging Characteristics 50 AH, Ag-Zn Cells, 1.94 volts/cell         |                 |

|             | Limit                                                                | 4-5             |

| 4-3         | Volts Versus Discharge Rate                                          | 4-5             |

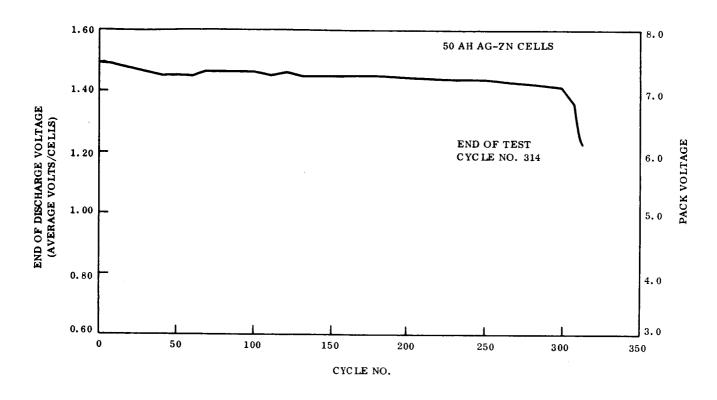

| 4-4         | End Discharge Voltage Versus Cycle, 20 Percent and DOD, 7-hour Cycle | 4-7             |

| 4-5         | Pack 811-26 to 30, 5-50 AH Ag-Zn Cells                               | 4-7             |

| 4-6         | Silver-Zinc Secondary Cells Discharge Volts Versus Time for 20       | <del>1</del> -( |

| 4-0         | Amp Discharge                                                        | 4-8             |

| 4-7         | Volts Versus Discharge Rate for 20 AH Silver Cadmium Sealed          | <b>1</b> -0     |

| <b>T</b> -1 | Cells                                                                | 4-10            |

| 4-8         | Pack 812-F 6-20 AH Ag-Cd Cells 7-hour Cycle, 40 Percent DOD,         |                 |

| 4.0         | 75°F, End of Discharge                                               | 4-12            |

| 4-9         | Silver Cadmium Cellpack 812-D Cycle 109, 40% DOD, 24-hour            | 4 16            |

| 4.40        | Cycle                                                                | 4-13            |

| 4-10        | Cycle Life Versus DOD for Ag-Zn, Ag-Cd, and Ni-Cd Cells at           |                 |

|             | 25°C                                                                 | 4-15            |

| 5-1         | Series Block Diagram                                                 | 5-2             |

| 5-2         | Series System Reliability                                            | 5-2             |

| 5-3         | Parallel Block Diagram                                               | 5-4             |

| 5-4         | Parallel System Reliability                                          | 5-4             |

| 5-5         | Paired Regulator Inverter                                            | 5-7             |

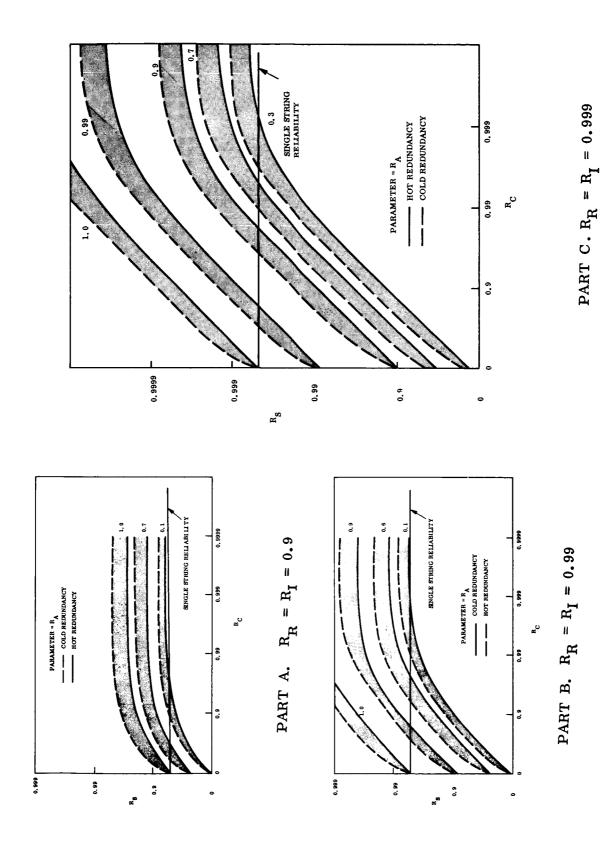

| 5-6         | Cold Redundancy Versus Hot Redundancy                                | 5-9             |

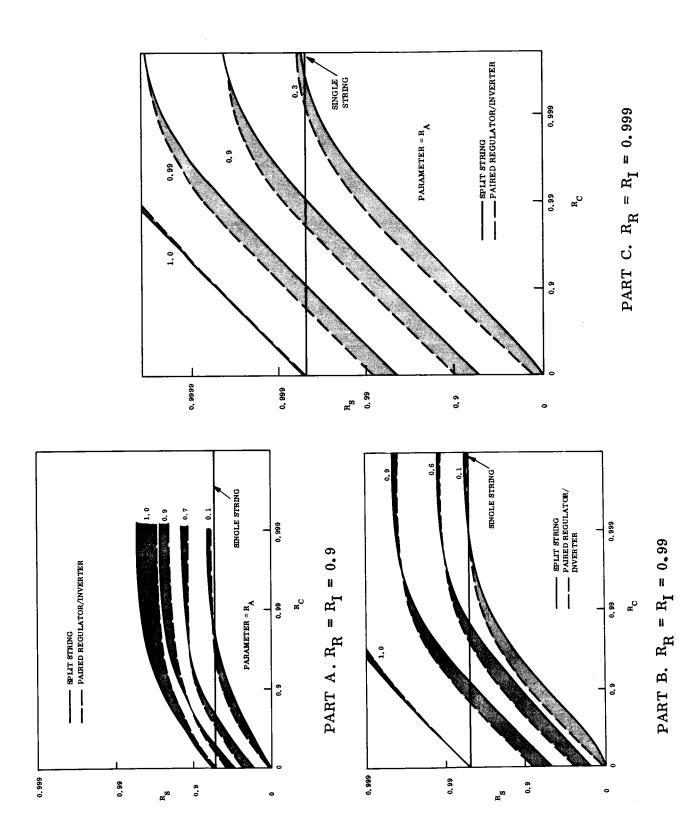

| 5-7         | Split String Regulator/Inverter                                      | 5-11            |

| 5-8         | Split String Versus Paired Regulator/Inverter                        | 5-12            |

| 5-9         | Mariner Mars '69 Regulator/Inverter/Fault Sensing                    | 5-14            |

| 5-10        | Mariner Mars '69 Regulator/Inverter/Fault Sensing                    | 5-14            |

# LIST OF ILLUSTRATIONS (Cont)

| Figure |                                                                 | Page        |

|--------|-----------------------------------------------------------------|-------------|

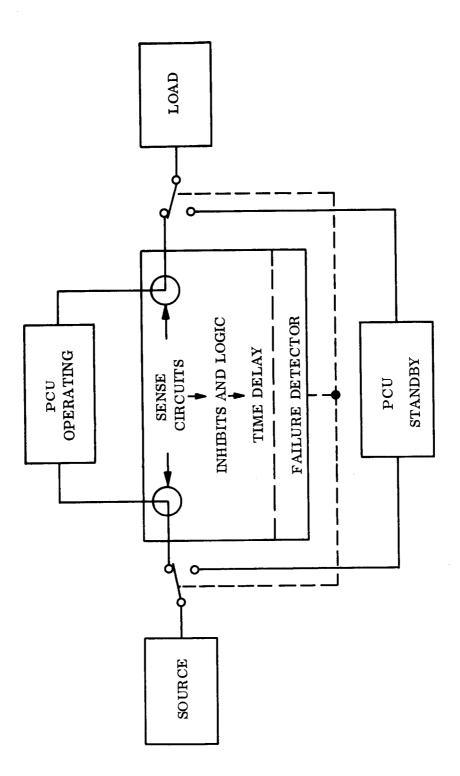

| 6-1    | System Block Diagram                                            | 6-2         |

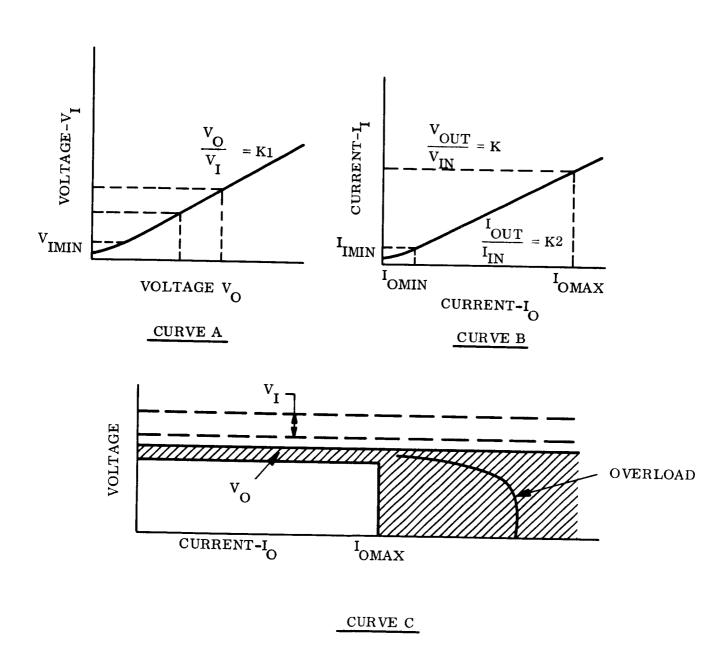

| 6-2    | Voltage-Current Characteristics of Series Dissipative Regulator | 6-6         |

| 6-3    | Voltage-Current Characteristics of Inverter or Converter        | 6-7         |

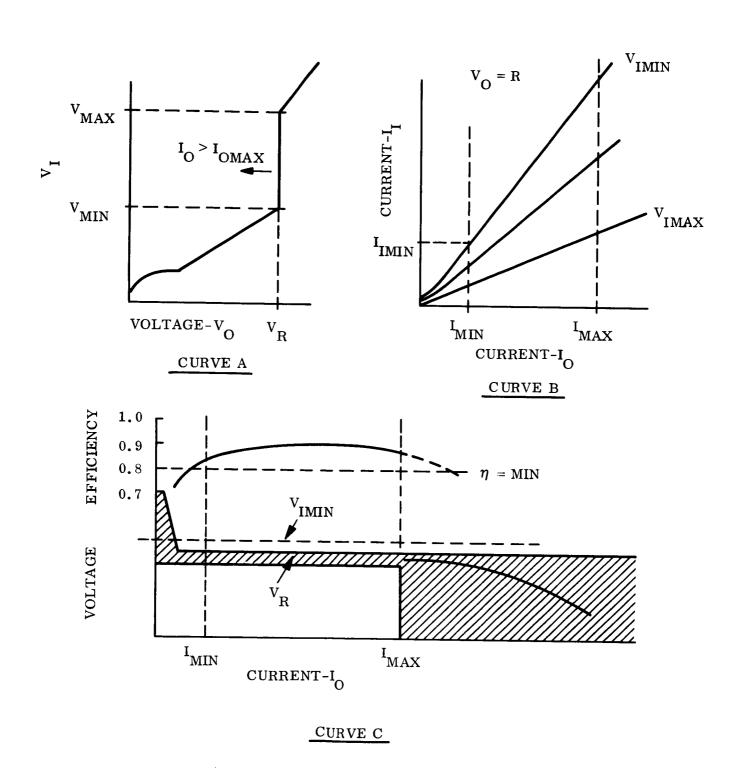

| 6-4    | Voltage-Current Characteristics of Switching Regulator          | 6-9         |

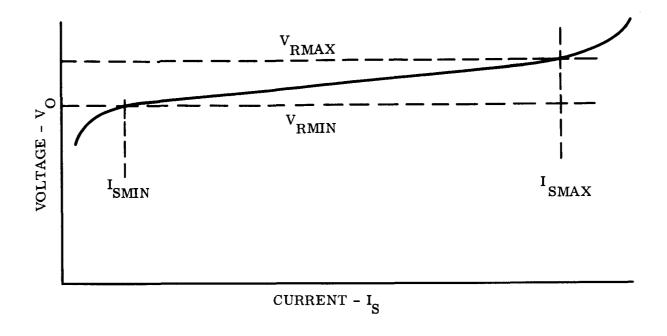

| 6-5    | Shunt Regulator Characteristics                                 | 6-10        |

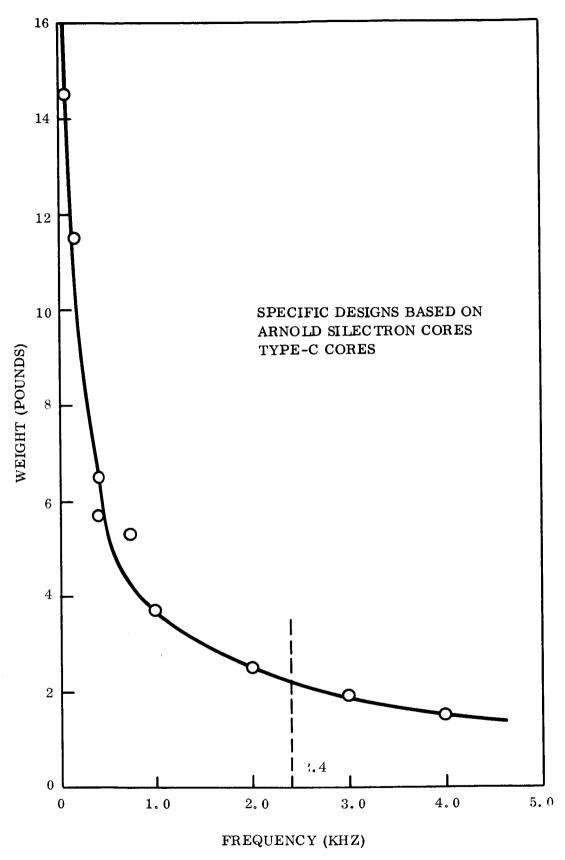

| 7-1    | Transformer Weight 200 Watt Output, 97 Percent Efficiency       | 7-2         |

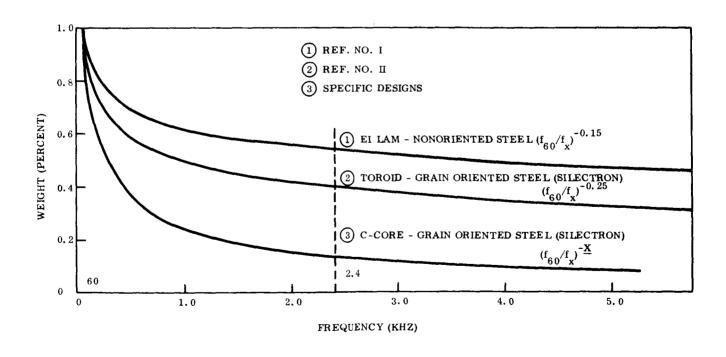

| 7-2    | Transformer Weight Percent Reference to 60 HZ                   | 7-3         |

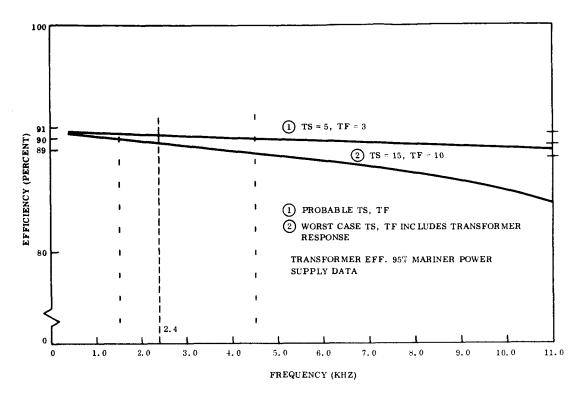

| 7-3    | Square Wave Inverter Efficiency                                 | 7-6         |

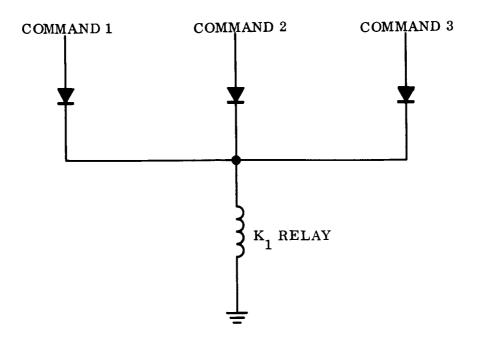

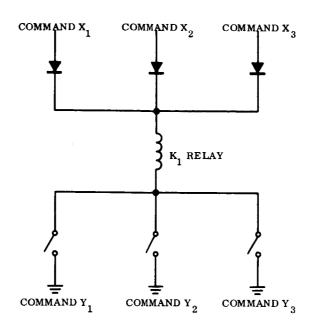

| 8-1    | Redundant Commanding                                            | 8-4         |

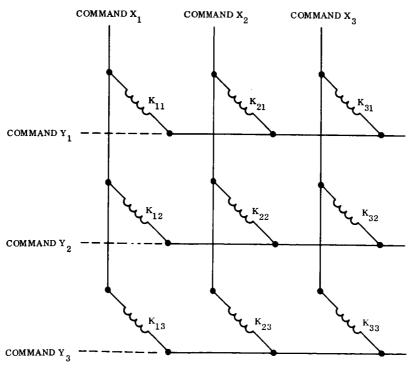

| 8-2    | Driver Failure Protection                                       | 8-5         |

| 8-3    | Simplified Command Matrix                                       | 8-5         |

| 8-4    | Relays Insensitive to Noise                                     | 8-7         |

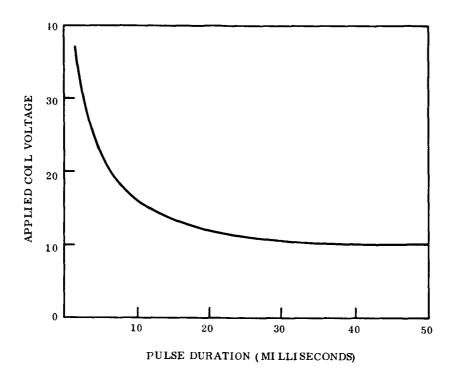

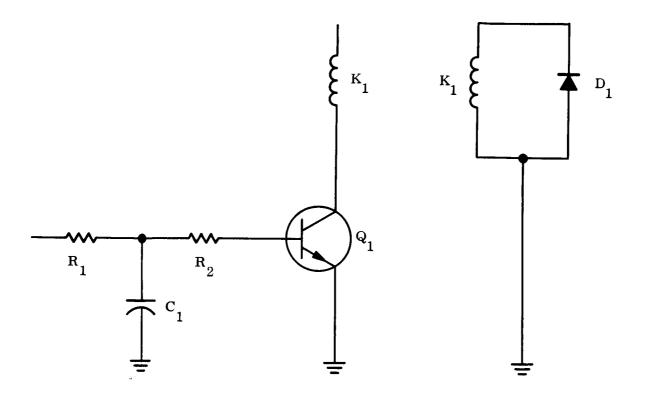

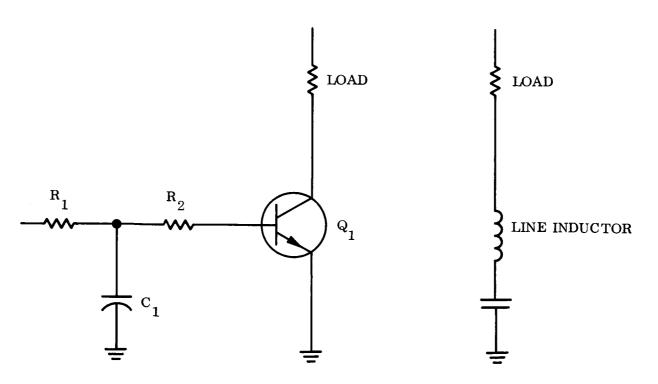

| 8-5    | Coil Suppression                                                | 8-8         |

| 8-6    | Soft Commutation                                                | 8-8         |

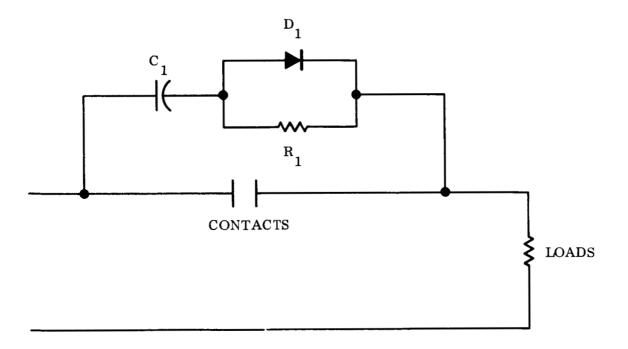

| 8-9    | Contact Suppression                                             | 8 <b>-9</b> |

| A-1    | Voltage-Current Characteristics of 1-ohm-cm N/P Solar Cells     | A-2         |

| A-2    | Voltage-Current Translation for Reduced Illumination            | A-3         |

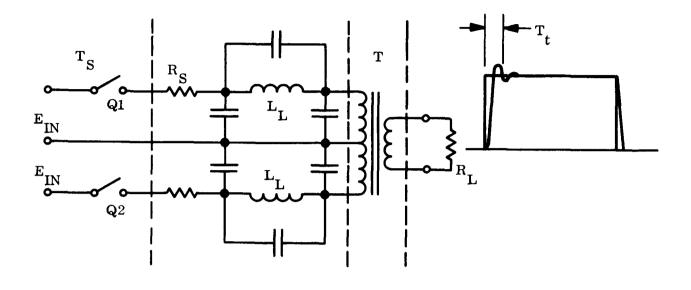

| B-1    | Transformer Equivalent Circuit                                  | B-2         |

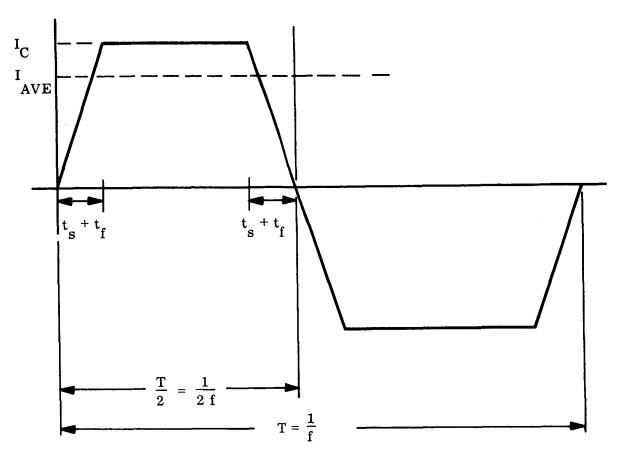

| B-2    | Switch Voltage-Current-Time Diagram of Push-Pull Inverter       | B-3         |

| B-3    | Switching Diagram                                               | B-4         |

| B-4    | Linear Switching                                                | B-4         |

| B-5    | Inverter Collector Current-Time Diagram                         | B-9         |

| C-1    | Rectifier Switching Characteristics                             | C-2         |

## SECTION 1

#### INTRODUCTION

This is the midterm report of the Mars Spacecraft Power System Development Program conducted in accordance with JPL Contract No. 952150.

The aim of this program is to investigate and recommend possible changes in existing Mariner power system designs for use in future Mars flyby and orbiter missions. The Mariner Mars 1969 power system is used as the reference design against which all comparisons and recommendations will be made.

As evidenced by guidelines and information provided by JPL during the early phases of the program, the principal interest is centered on orbiter missions as exemplified by the 1971 opportunity. As a result, more emphasis is being placed on a design meeting orbiter requirements rather than flyby requirements. However, possible flyby improvements will be inclusive in the study of orbiter power systems, e.g., the application of fault sensing and redundancy. Thus, at the conclusion of the study, all of the necessary information will be available to identify potential flyby power system improvements as well.

A work plan for conducting the study was developed in the early weeks of the program and is shown on Figure 1-1. The cross-hatched areas indicate the degree of completion of the designated tasks. The principal results at this point in the study are summarized below:

- A shunt regulation system has been selected as the prime contender for more detailed study.

- Upon review of available test data it has been concluded that only silver-zinc and nickel-cadmium batteries will be considered in the upcoming study phase.

- Reliability sensitivity studies indicate that fault sensing and switchover devices should be considered only if their net reliability is equal to or greater than the reliability of the functions being protected (e.g. regulator or inverters). No clearcut reliability advantage has been identified for fault sensing the regulator and inverter separately or as a pair. The choice will lie more in which approach is easier to implement.

- Fault criteria have been identified for the principal types of power conditioning units (PCUs'). These criteria distinguish between PCU and source/load faults.

- A frequency optimization study indicates that a change from the presently used frequency of 2.4 kHz is not warranted.

- General guidelines and design practices in the area of power switching and distribution have been provided.

- Circuits of the MM '69 power system were reviewed, several potential problem areas identified, and alternate approaches suggested.

WORK FLOW DIAGRAM - MARS SPACECRAFT POWER SYSTEM DEVELOPME S FINAL REPORT PREPARATI POLDOUT FRANK COMPLETE ANALYS IS MODEL SHUNT SYSTEM C SYSTEM DESIGNS COMPLETE CALCULATE SENSITIVITY STUDY AM '69 FOLDOUT BRAME FOLDOUT FRAME TASK & 0 AC DISTRIBUTION FREQUENCY STUDY TASK 3.0 POWER SYSTEM DEFINITION AND DESIGN IMPLEMENTATION TASK 1.0 POWER SYSTEM CONCEPT EVALUATION TASK 4.0 System level Reliability Analysis MEETINGS AND REPORTS

#### SECTION 2

#### CONSTRAINTS AND GUIDE LINES

Guidelines for the study are largely drawn from the requirements for the MM '69 power system and from load profile estimates for a 1971 orbiter mission. Specific characteristics, either specified or implied, are summarized below.

## 2.1 POWER SYSTEM TYPE

The power system will utilize solar arrays for power generation and electrochemical batteries for energy storage.

## 2.2 SOLAR ARRAY ORIENTATION

The solar arrays will be fully sun oriented, except for brief maneuver periods when power will be supplied by the spacecraft batteries.

## 2.3 DISTRIBUTION

To least disturb the power system interface with other spacecraft subsystems and OSE as presently defined for the MM '69 system, the types of distributed power will be identical to that of the MM '69 system:

## Regulated ac power

50 volt rms, single phase, 2.4 kHz

27.2 volt rms, three phase, 400 Hz

28 volt rms, single phase, 400 Hz

## Unregulated dc power

25 to 50 volts, extreme limits

#### 2.4 LOAD PROFILE

Power requirements by user designation, power type, and mission phase for the 1971 orbiting mission have been furnished by JPL and are summarized on Table 2-1.

Table 2-1. Power Requirements (Watts), 1971 Orbiting Mission

| m Direc Siv   | m Tri Donne Direc | mirror Brown Bires Siv | vi N out d | Sire of Sire | 2     | -     | Š     | Flight | Flight Phases | Nine  | Ten   | Eleven | Twelve | Thirteen | Fourteen |

|---------------|-------------------|------------------------|------------|--------------|-------|-------|-------|--------|---------------|-------|-------|--------|--------|----------|----------|

|               |                   | One                    | Two        | Three        | rour  | FIVE  | 90 00 | 90     | 00.0          | -0.00 | -0.00 | 20.00  | -0.00  | -0.00    | -0.00    |

| ã             | DAS               | -0.00                  | 0.00       | 00.0         | 00.00 | -0.00 | 32.00 | -0.00  | -0.00         | -0.00 | -0.00 | 32.00  | -0.00  | -0.00    | -0.00    |

| -             | e l               | 8 9                    | 8 8        | 00.0         | -0.00 | -0.00 | 3.00  | -0.00  | -0.00         | -0.00 | -0.00 | 3.00   | -0.00  | -0.00    | -0.00    |

| <b>E</b>      | IKK               | 00.00                  | 00.00      | -0.00        | -0.00 | -0.00 | 4.00  | -0.00  | -0.00         | -0.00 | -0.00 | 4.00   | -0.00  | -0.00    | -0.00    |

|               | SMI               | 8 9                    | -0.00      | -0.00        | -0.00 | -0.00 | 12.00 | -0.00  | -0.00         | -0.00 | -0.00 | 12.00  | -0.00  | -0.00    | -0.00    |

| 2             | FTS               | 15.00                  | 15.00      | 15.00        | 15.00 | 15.00 | 15.00 | 15.00  | 15.00         | 15.00 | 15.00 | 15.00  | 15.00  | 15.00    | 15.00    |

| 1 5           | FCS               | 3.20                   | 3.20       | 3.20         | 3.20  | 3.20  | 3.20  | 3.20   | 3,20          | 3.20  | 3.20  | 3.20   | 3.20   | 3.20     | 3.20     |

|               | CC&S              | 39.00                  | 19.00      | 19.00        | 19.00 | 19.00 | 19.00 | 19.00  | 19.00         | 19.00 | 19.00 | 19.00  | 19.00  | 19.00    | 19.00    |

|               |                   |                        | 00 -       | 1.00         | 1.00  | 1.00  | 1.00  | 1.00   | 1.00          | 1.00  | 1.00  | 1.00   | 1.00   | 1.00     | 1.00     |

| 2.4 KHZ       | PWRD              | 20.00                  | 2.25       | 2.25         | 2.25  | 2.25  | 2, 25 | 2, 25  | 2, 25         | 2.25  | 2. 25 | 2.25   | 2, 25  | 2.25     | 2.25     |

|               | DSS               | 21.00                  | 22.00      | 10.00        | 10.00 | 10.00 | 18.00 | 10.00  | 19.00         | 10.00 | 10.00 | 23.00  | 15.00  | 19.00    | 18.00    |

| 4             | A /C1             | 13.00                  | 25.00      | 4.00         | 4.00  | 23.00 | 4.00  | 23.00  | 4.00          | 23.00 | 4.00  | 4.00   | 4.00   | 4.00     | 4.00     |

|               | A /C2             | -0.00                  | -0.00      | -0.00        | -0.00 | 10.50 | -0.00 | 10.50  | -0.00         | 10.50 | -0.00 | -0.00  | -0.00  | -0.00    | -0.00    |

| ; ] ŏ         | SCINE             | 5.30                   | 5,30       | 5.30         | 5.30  | 5.30  | 28.50 | 5.30   | 5.30          | 5.30  | 5.30  | 16.50  | 5.30   | 5.30     | 5.30     |

| "             | RES               | 32, 20                 | 32.20      | 32.20        | 32.20 | 32.20 | 32.20 | 32.20  | 32.20         | 32.20 | 32.20 | 32.20  | 32.20  | 32.20    | 32.20    |

|               | GYRE              | 8.00                   | 8.00       | -0.00        | -0.00 | 8.00  | -0.00 | 8.00   | -0.00         | 8.00  | -0.00 | -0.00  | -0.00  | -0.00    | -0.00    |

| <u> </u>      | T/C1              | 50.00                  | 50.00      | 50.00        | 50.00 | 50.00 | -0.00 | 20.00  | 50.00         | 50.00 | 50.00 | -0.00  | 50.00  | 50.00    | 20.00    |

| 400 Hz. 3 & G | GYRO              | 9.00                   | 9.00       | -0.00        | -0.00 | 9.00  | -0.00 | 9,00   | -0.00         | 9.00  | -0.00 | -0.00  | -0.00  | -0.00    | -0.00    |

| +             | 71.00             | 9                      | 00 0       | 00 0-        | -0.00 | -0.00 | 12.00 | -0.00  | -0.00         | -0.00 | -0.00 | 12.00  | -0.00  | -0.00    | -0.00    |

| 400 Hz, 1¢    | IRSM              | -0.00                  | -0.00      | -0.00        | -0.00 | -0.00 | -0.00 | -0.00  | -0.00         | -0.00 | -0.00 | 3.50   | -0.00  | -0.00    | -0.00    |

|               | VAIV              | -0.00                  | -0.00      | -0.00        | -0.00 | 30.00 | -0.00 | 30.00  | -0.00         | 30.00 | -0.00 | -0.00  | -0.00  | -0.00    | -0.00    |

| 28 VDC        | GIMB              | -0.00                  | -0.00      | -0.00        | -0.00 | 35.00 | -0.00 | 35.00  | -0.00         | 35.00 | -0.00 | -0.00  | -0.00  | -0.00    | -0.00    |

| +             | 100               | 6                      | 90         | 15.00        | 15.00 | 15.00 | 15.00 | 15.00  | 15.00         | 15.00 | 15.00 | 15.00  | 15.00  | 15.00    | 15.00    |

|               | T/C2              | 7.30                   | 19.00      | 90 01        | 00 01 | 10.00 | 10.00 | 10.00  | 10.00         | 10.00 | 10.00 | 10.00  | 10.00  | 10.00    | 10.00    |

|               | T/C3              | 4.90                   | 20.01      | 25.00        | 55.00 | 55.00 | 89.00 | 55.00  | 89.00         | 55.00 | 55.00 | 89.00  | 55.00  | 89.00    | 55.00    |

| 25-50 VDC     | IWI               | 00.00                  | 0 50       | 25.00        | 0.50  | 0.50  | 0.50  | 0.50   | 25.00         | 0.50  | 25.00 | 0.50   | 0.50   | 0.50     | 0.50     |

|               | 3100              | 00.00                  | 3          |              |       |       |       | 5      | 1 50          | 1.50  | 1 50  | 1.50   | 1.50   | 1.50     | 1.50     |

Special Load Conditions:

1. For those cases where GYRO = 0.00, abnormal alternative condition may be that GYRO = 9.00 with concurrent condition that

A/C 1 = 16.00 and GYRE = 8.00.

2. T/C 2 = 15.00 (array operation) = 7.30 (battery operation)

3. T/C 3 = 10.00 (array operation)

3 = 10.00 (array operation) = 4.90 (battery operation)

Table 2-1. Power Requirements (Watts), 1971 Orbiting Mission (Cont)

| Phase Number | Phase Name                      | Duration                  |

|--------------|---------------------------------|---------------------------|

| One          | Launch                          | 45 minutes max.           |

| Two          | Star Acquisition                | Not specified             |

| Three        | Cruise I (Battery Charger On)   | Not specified             |

| Four         | Cruise II (Battery Charger Off) | Not specified             |

| Five         | Maneuver                        | 40 minutes                |

| Six          | Far Encounter                   | Not specified             |

| Seven        | Orbit Insertion                 | 100 minutes               |

| Eight        | Playback - Far Encounter        | Not specified             |

| Nine         | Orbit Trim                      | 20 to 40 minutes (Note A) |

| Ten          | Orbit Cruise - CC&S Update      | Not specified             |

| Eleven       | TV Sequence                     | Not specified             |

| Twelve       | Earth Occultation               | Not specified             |

| Thirteen     | Playback ATR                    | Not specified             |

| Fourteen     | Playback DTR                    | Not specified             |

## Notes:

- A. 1<sup>st</sup> orbit trim no sooner than 24 hours after Orbit Insertion; subsequent orbit trims no sooner than 24 hours after previous orbit trim.

- B. Sun-probe distance:

Encounter: 212 x 10<sup>6</sup> kilometers

Encounter plus 30 days:  $217 \times 10^6$  kilometers

Encounter plus 90 days: 228 x 10<sup>6</sup> kilometers

## 2.5 TRANSIT AND ORBIT CHARACTERISTICS

Also based on information supplied by JPL, the significant orbit characteristics relating to the power system design are:

Transit time: Approximately 8 months

Arrival date: 14 November 1971

Orbit period: 12 hours

Onset of Solar Occultations: 130 days after arrival

Length of Solar Occultations: Up to 90 minutes

#### SECTION 3

#### POWER SYSTEM SELECTION

A shunt regulation system has been selected for further detailed design and comparison with the MM'69 power system. This selection was based on the relatively higher scoring of the shunt system over other candidates when judged against numerous criteria.

Three principal power system candidates were evaluated in the selection process: (1) a boost regulation system, (2) a series switching (buck) regulation system, and (3) the shunt regulation system. A single representative arrangement of the functional elements was evaluated for each candidate. Only those functions necessary to provide regulated and raw dc power were considered. Although the guidelines listed earlier indicate the distribution of ac power, its impact on candidate evaluation is not significant since dc/ac conditioning equipment is quite similar for any candidate. Any other features that could be applied with equal advantage to all candidates were also not included, such as improved methods of battery charging. The solutions to this and similar questions are considered as part of the detailed design phase which follows the selection of the principal candidate.

## 3.1 INFLUENCE OF SOLAR ARRAY

The variations in solar array characteristics associated with Earth/Mars transfer provide a logical starting point for considering power system candidates. It seems valid to consider that future Mariner spacecraft will utilize rigid deployed panel solar arrays similar to those used previously. Given a particular solar array design, its voltage-current characteristics with sun distance will vary in a particular way depending to a large extent on its thermal properties.

The variation in voltage-current characteristics are thus largely independent of the subsystem arrangement of which the solar array is a part. It is therefore possible to use a generalized set of solar array characteristics in examining possible subsystem arrangements.

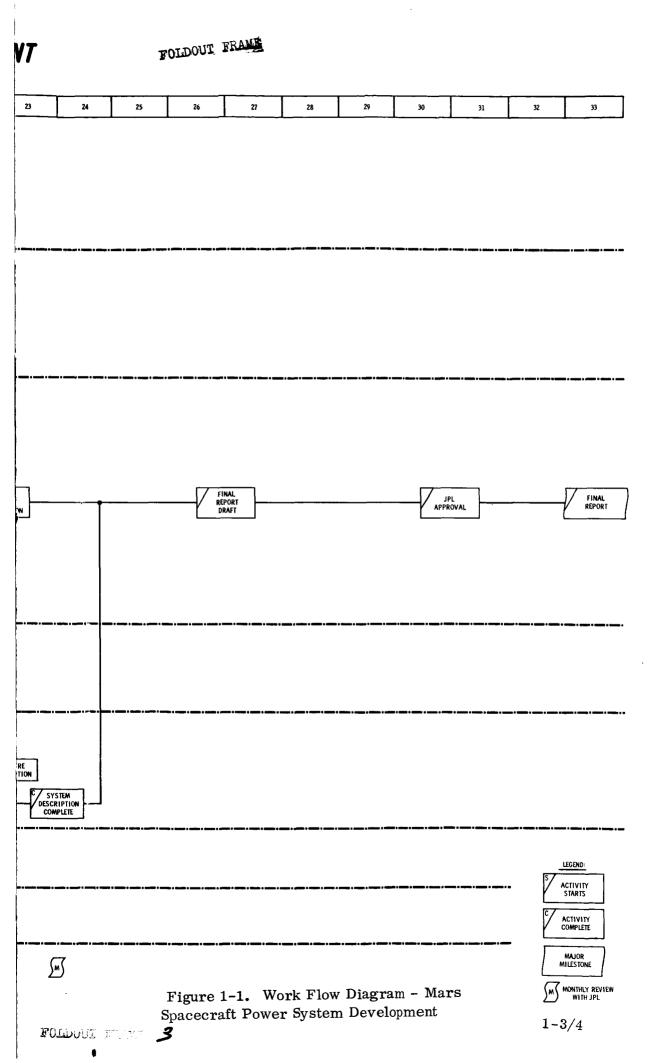

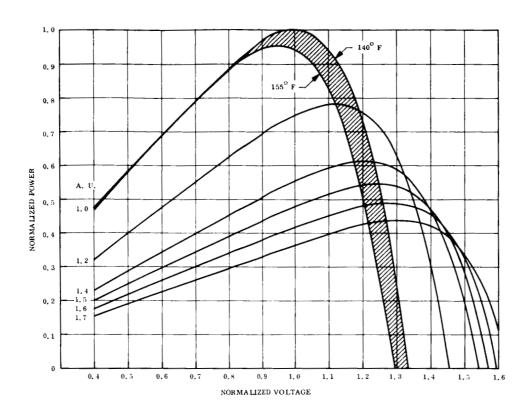

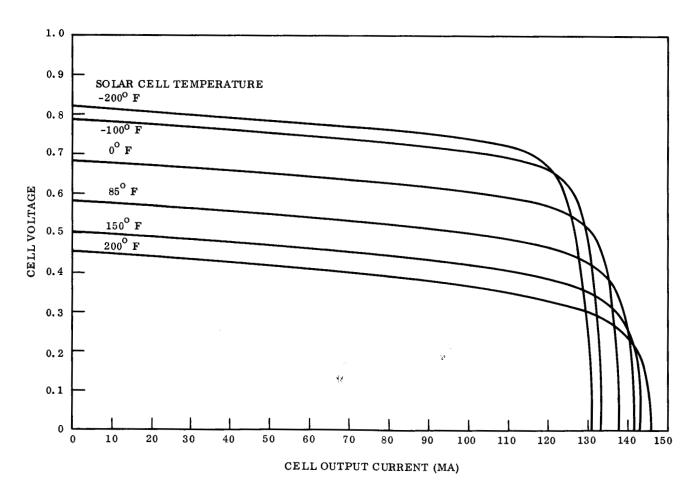

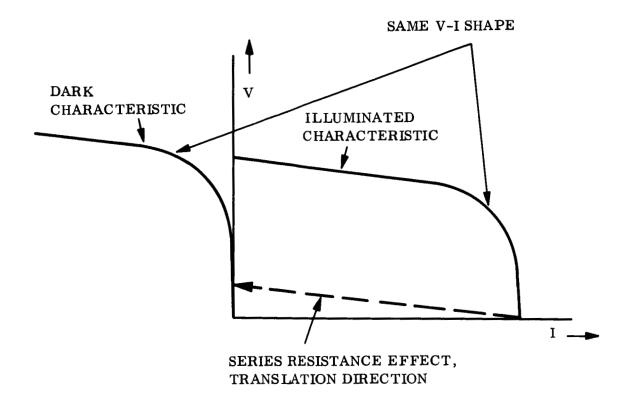

Figure 3-1 shows a set of normalized power-voltage curves for a representative Mars spacecraft solar array design. The relative variations in the P-V curves are based on the temperature distance profile shown on Figure 3-2. The P-V curves are based on measurements made on a set of RCA 1-ohm/cm N/P cells. The procedures used in predicting the P-V variation with sun distance are summarized in Appendix A. The effect of possible errors in temperature prediction are also included in the P-V plot for 1.0 AU.

To permit relative assessments of the solar array effect on candidate subsystem arrangements, the P-V curves are normalized and hence independent of specific series-parallel arrangements of the solar cells. Normalization is shown with respect to maximum power and voltage at 1.0 AU and  $140^{\circ}$ F.

In the power system candidate discussion which follows, the influence of the P-V curves of Figure 3-1 will be referenced. It is stressed that these curves are the result of a particular cell type, namely the RCA cells mentioned earlier. The conclusions regarding solar array influence on candidate selection may be somewhat modified if other cell types are considered. This is a question being analyzed presently in relation to the shunt system detailed design activity.

The use of the P-V curves previously described implies that no active means would be used to electrically rearrange solar array sections by switching. The purpose of such switching would be twofold: (1) to add or remove array sections and thus minimize problems of handling excess power, (2) to change the series-parallel solar cell matrix to permit power availability at more favorable voltage levels as a result of large changes in V-I characteristics with sun distance. All of the power system candidates described later are able to cope with these conditions without the necessity for switching; therefore, this possibility was not considered further.

Figure 3-1. Normalized P-V Solar Array Curves

Figure 3-2. Solar Array Temperature Versus Sun Distance

## 3.2 REGULATOR EFFICIENCY

Regulator efficiency data used in evaluating the candidate systems is shown on Figure 3-3.

Figure 3-3. Regulator Efficiency Data

The boost regulator data is based on the efficiencies cited in the 1971 load profile information and reflects the performance of the regulator used in the MM'69 power system.

The buck regulator data is based on a design rated at 600 watts and 30 vdc which was built as a breadboard and performance tested.

The shunt regulator data is based on assuming an efficiency of 98 percent at rated load with 2 percent used for the regulator control electronics. At partial loads, it is assumed that the same amount of control power is required which results in the overall efficiency decrease shown.

## 3. 3 CANDIDATE DESCRIPTIONS

#### 3. 3. 1 BOOST SYSTEM

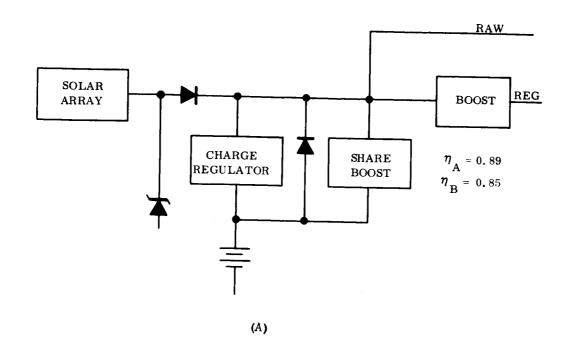

This candidate system is shown on Figure 3-4(a) and has the general characteristics of the MM'69 power system.

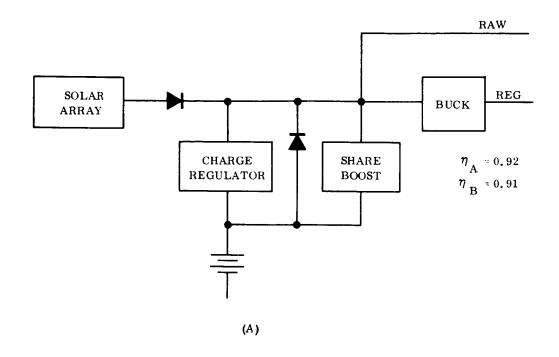

The boost regulator requires that all input operating voltages be lower than the regulated output voltage. The necessary voltages to meet this condition are shown on Figure 3-4(b) with reference to the normalized values for the solar array (Figure 3-1). The procedure for selecting these levels is described in the following paragraphs.

First, as shown on Figure 3-1, for an arrival at Mars between 1.4 and 1.6 AU, maximum power is available at a normalized voltage,  $V_N$ , of around 1.25. For these particular P-V curves, there is a negligible power difference if  $V_N$  is used between 1.2 and 1.3, corresponding to AU distances of 1.4 and 1.6, respectively. An intermediate value of 1.25 appears appropriate under this circumstance.

With array power at Mars drawn at  $V_N=1.25$ , it is necessary that the maximum allowable boost input level be set higher than 1.25, with allowance made for zener shunt tolerances. The zener shunt is used to assure that the boost input limit is not exceeded. This could occur as a result of solar array tolerance buildups or upon emergence from solar occultations (i.e., a cold array producing high voltage). With these constraints,  $V_N$  for the boost output bus is set at 1.4 with a loose zener tolerance of  $V_N$  equal to 1.3-1.4.

A battery charging voltage must be selected which does not interfere with the ability to draw sufficient array power in the near-Earth phase of operations. If, for example, a series dissipative charge regulator is used and its minimum input voltage is set at  $V_N = 1.25$ , then Figure 3-1 indicates that insufficient array power is available at 1.0 AU, especially if the solar array operates at  $155^{\circ}$ F rather than the nominally predicted temperature of  $140^{\circ}$ F for Mariner panels. By lowering the charger input to  $V_N = 1.05$ , this problem is avoided and the only penalty is the need for a wider boost input voltage range.

The battery charge to discharge voltage ratio is typically 1.35:1 (for Ag-Zn,  $V_{charge} = 1.94$  and  $V_{discharge} = 1.44$ ). With a conservative allowance made for a voltage drop through the charge regulator, the total voltage ratio of charger input to battery discharge is about 1.5:1 corresponding to the  $V_{N}$  values of 1.05 and 0.7 shown on Figure 3-4(b).

The limits described above result in a 2:1 variation in raw voltage.

With a boost system designed for these general limits, considerable latitude exists in the design voltage for the solar array. If the array were designed to provide sufficient near-Earth power at  $V_N=1.05$  (the charger input lower limit), this would represent an array voltage reduction of 12 percent from the  $V_N$  value of 1.19 which provides the same power for 1.0 AU and  $155^{\circ}$ F array as at  $V_N=1.25$  and 1.5 AU. This is the same as saying that the number of solar cells in series may be varied by about 12 percent without affecting system operation.

The boost system requires a means for avoiding the simultaneous supply of power from the solar array and battery, although the array might be fully capable of supplying all power. This possibility could occur during certain sequences when the battery clamps the array voltage at a value below its optimum point. A share boost regulator is incorporated to avoid this condition in the manner used on the MM'69 system. Another possibility is to reduce the load momentarily through appropriate sensing logic.

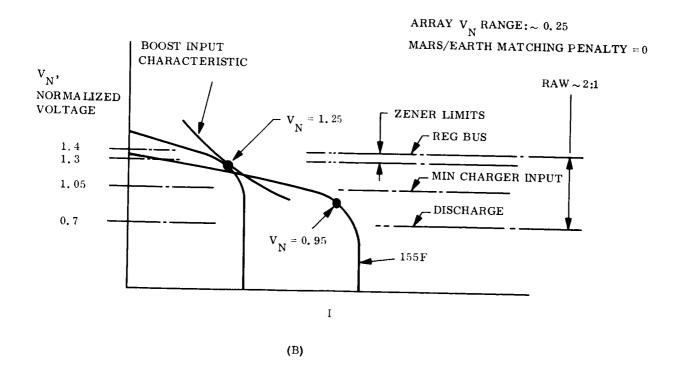

## 3. 3. 2 SERIES SWITCHING (BUCK) SYSTEM

This candidate system is shown on Figure 3-5(a).

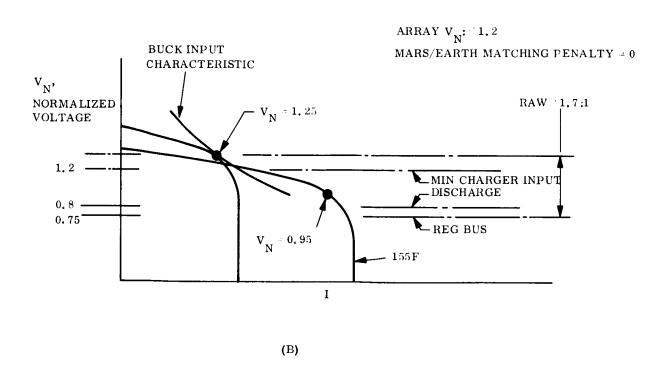

The buck regulator requires that all input operating voltages be higher than the regulated output voltage as shown on Figure 3-5(b).

As with the boost system, maximum power at Mars is available at  $V_N \approx$  1.25. Sufficient near-Earth power is available at  $V_N \approx$  1.2 which sets the minimum charge regulator input

Figure 3-4. Boost Candidate

Figure 3-5. Buck Candidate

voltage. Again, conservatively allowing a 1.5:1 ratio for the relationship of charger input voltage to battery discharge voltage, the latter voltage is set at  $V_N = 0.8$ . An estimated minimum voltage drop of  $V_N = 0.05$  is allocated to the buck regulator to result in a regulated bus level at 0.75.

These established limits result in a 1.7:1 variation in raw voltage.

In this system, an even greater variation in the array design voltage exists. The lower limit is set by conditions which mutually satisfy the near-Earth power demand and the charger input voltage. The higher limit is set by the regulator transistor ratings or the desire to limit the raw power range. A 2:1 input to output range for a buck regulator is realistic which would allow an increase to  $V_N=1.5$  over 1.25. This is equivalent to permitting an array design with 20 percent more cells in series. If the 2:1 range on the regulator was an absolute requirement, it is likely that zener shunts would be required to prevent excess voltage during cold array conditions (emergence from occultations, etc.).

This system also requires a means for avoiding the array/battery load sharing problem.

## 3.3.3 SHUNT SYSTEM

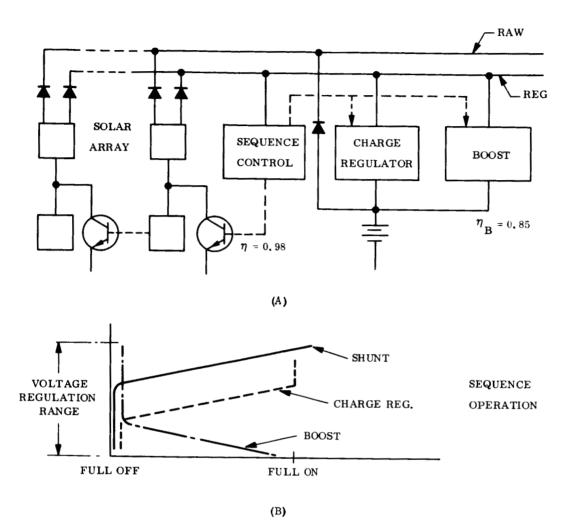

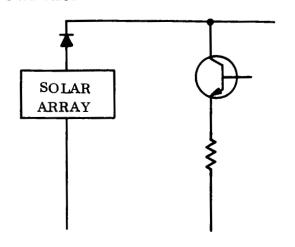

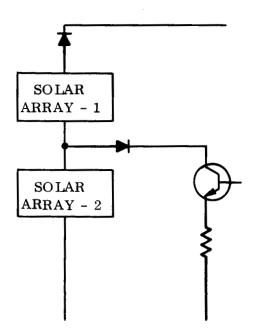

This candidate system is shown on Figure 3-6.

Regulated dc power is drawn directly from the solar array and is controlled by a partial shunt regulator in the form of multiple shunt transistors across separate semi-sections of the solar array.

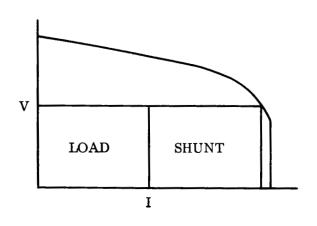

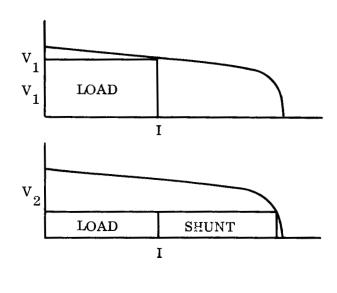

The Sequence Control provides the base drive signal to the shunt transistors and also provides control signals for sequencing operation of the charge regulator and boost regulator. This sequencing is necessary to prevent (1) simultaneous shunt and boost operation, and (2) simultaneous battery charging and boost operation. The method of sequencing is explained more fully on Figure 3-6(b). The Sequence Control establishes shunt, charge regulator,

and boost regulator operation as a function of the voltage level within the voltage regulation range. Assume for example that the regulated bus is set at 50 volts ±1 volt; then the voltage regulation range is 2 volts. Figure 3-6 indicates that the range is divided into three roughly equivalent bands, each devoted to a different control mode. The range of the upper band varies the shunt from "full on" at its high level to "full off" at its low level. The middle band similarly varies the charge regulator, and the lower band inversely varies the boost from "full off" at its high level to "full on" at its low level. The Sequence Control of the charge regulator is an override control over the normal charge regulator control functions. If the shunt regulator is operating, i.e., it is draining away excess array power, and the battery is fully charged, the charge regulator would probably only be supplying trickle power depending on the charging method used. Any subsequent Sequence Control override signal would in that case not affect the charge regulator operation.

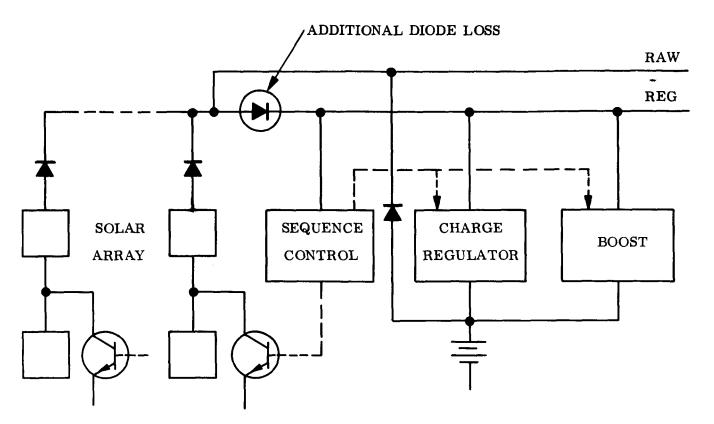

Raw power is drawn from a separate set of solar array isolation diodes or through a diode from the battery. It would have been possible to use the scheme shown on Figure 3-7 which results in an additional diode voltage loss for solar array power. In the interest of efficiency, the arrangement of Figure 3-6(a) was selected for further study.

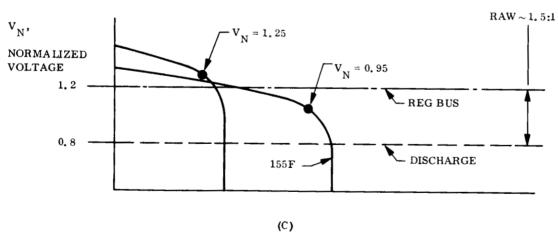

The determination of relative voltage levels is shown on Figure 3-6(c). Again  $V_N=1.25$  provides the maximum power capability at Mars. However, since the array voltage is constant throughout the mission (same as regulated voltage), there would be a power deficiency in near-Earth operation as seen on Figure 3-1. The selection  $V_N=1.2$  avoids this condition with a penalty of several percent in the power available at Mars.

The 1.5:1 ratio for the relative values of charger input to battery discharge is used as before which results in a similar ratio for the raw power range.

The selection of a partial shunt over a full shunt is based on its lower thermal dissipation within the shunt elements. Figure 3-8 shows the full and partial shunt options and their modes of operation relative to the solar array V-I curve. If the voltages of the two V-I curves for

## MARS/EARTH MATCHING PENALTY $\sim 2\%$

Figure 3-6. Shunt Candidate

Figure 3-7. Raw Power Source Alternative

the partial shunt case were added, they would result in the full shunt V-I curve. As shown on the sketch, these are drawn to scale relative to each other, and it becomes apparent that the partial shunt dissipation is significantly less. It is also clear that the current requirement for both types is about equivalent.

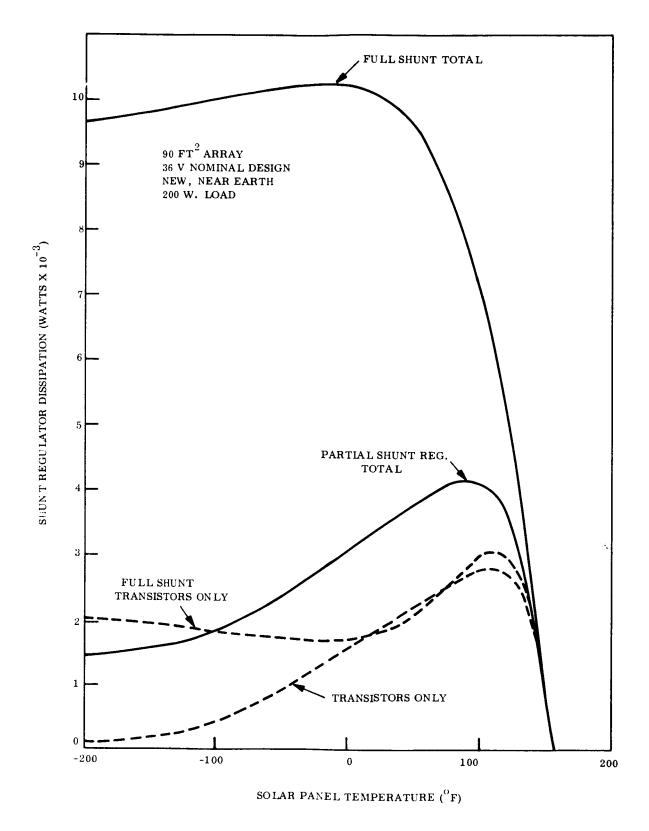

Figure 3-9 shows the shunt analysis for a solar array quite similar in size to the MM'69 solar panels. This particular array would produce about 900 watts at 1.0 AU at a panel temperature of 100°F. The curve shows the dissipation from either a full or partial shunt for a nominal demand load of 200 watts. The dissipation is shown as a function of array temperature to identify the maximum dissipation that might occur during emergence from an Earth eclipse. Each shunt section has a transistor and resistor in series. The dotted lines indicate the heat dissipation associated only with the transistors which is almost the same for the full and partial shunt cases. It is possible that no resistors will be required for the partial shunt case. It was therefore selected for use in the shunt system candidate.

## FU LL SHUNT

## • PARTIAL SHUNT - SINGLE SECTION

Figure 3-8. Shunt Regulator Options

Figure 3-9. Shunt Performance

## 3.4 CANDIDATE COMPARISON

The three candidate systems are compared on the matrix shown on Table 3-1. The rating of each candidate against a particular criterion is indicated in the rating columns where "1" indicates the highest rating, "2" the intermediate rating, and "3" the lowest rating. The lowest summation of these ratings provides the basis for candidate selection.

Pertinent discussion for each criterion is provided below:

## Relative Battery Demand

For regulated loads, battery demand in the boost and buck systems is inversely proportional to the regulator efficiency and the discharge diode efficiency, assumed to be 0.97. Then the relative demands are:

$$\frac{\text{Buck demand}}{\text{Boost demand}} = \frac{0.85 \times 0.97}{0.91 \times 0.97} = 0.94$$

using the regulator efficiencies cited in Figure 3-3. The shunt system does not contain a battery discharge diode to the boost regulator and therefore,

$$\frac{\text{Shunt demand}}{\text{Boost demand}} = \frac{0.85 \times 0.97}{1.85} = 0.97$$

For raw loads, all three candidates provide battery power to the raw bus through diodes and therefore no battery demand difference exists.

## Relative Array Demand

For regulated loads, array demand is inversely proportional to regulator efficiency:

$$\frac{\text{Buck demand}}{\text{Boost demand}} = \frac{0.89}{0.92} = 0.97$$

Table 3-1. Candidate Comparison

| Criterion                  |                 | Boost                        | R* | Buck                         | R* | Shunt                                    | R*           |

|----------------------------|-----------------|------------------------------|----|------------------------------|----|------------------------------------------|--------------|

| Relative                   | Reg<br>loads    | 1.0                          | 3  | 0.94                         | 1  | 0.97                                     | 2            |

| Battery<br>Demand          | Raw<br>loads    | 1.0                          | _  | 1.0                          | -  |                                          | _            |

| Relative                   | Reg<br>loads    | 1.0                          | 3  | 0.97                         | 2  | 0.93                                     | 1            |

| Array<br>Demand            | Raw<br>loads    | 1.0                          | 1  | 1.0                          | 1  | 1.02                                     | 2            |

|                            | Charge<br>Power | small+                       | _  | small                        | _  | small-                                   | -            |

| Packaging                  |                 | Compact                      | 2  | Compact                      | 1  | Shunt<br>wiring                          | 3            |

| Bay Therm<br>Design        | al              | Battery<br>Integr.           |    | Battery<br>Integr.           | -  | Battery<br>Integr.                       | _            |

| Raw Bus<br>Limits          |                 | 2:1                          | 2  | ≥ 1.7:1<br>(Zeners?)         | 2  | 1.5:1                                    | 1            |

| Reg Bus<br>Limits          |                 | <u>+</u> 2%                  | -  | <u>+</u> 2%                  | 1  | <u>+</u> 2%                              | _            |

| Ripple                     | -               | PWM reg                      | 2  | PWM reg                      | 2  | Shunt                                    | 1            |

| Ripple<br>Respor           | , night<br>ise  | PWM reg<br>Medium            | -  | PWM reg<br>Medium            | -  | PWM reg<br>Medium                        | <del>-</del> |

| Battery Ch.<br>Integration | _               | Variable<br>Voltage<br>Input | 2  | Variable<br>Voltage<br>Input | 3  | Fixed<br>Voltage<br>Input                | 1            |

| Operationa<br>Complexity   |                 | Share<br>Boost               | 2  | Share<br>Boost               | 2  | Sequence control, no switching           | 1            |

| Flexibility,<br>Growth     | /               | Regulator<br>Size<br>Limit   | 2  | Regulator<br>Size<br>Limit   | 2  | Add shunt<br>elements<br>(day operation) | 1            |

| Redundancy<br>Implement    |                 | Single<br>Function           | 1  | Single<br>Function           | 1  | Multi-<br>Functions                      | 2            |

Table 3-1. Candidate Comparison (cont)

| Criterion                       | Boost                                   | R * | Buck                                                            | R * | Shunt                                                      | R* |

|---------------------------------|-----------------------------------------|-----|-----------------------------------------------------------------|-----|------------------------------------------------------------|----|

| Failure Modes                   |                                         |     |                                                                 |     |                                                            |    |

| Regulator-Array<br>Operation:   |                                         |     |                                                                 |     |                                                            |    |

| Open                            | Results in<br>short                     | 2   | Complete<br>power loss                                          | 2   | Minor effect<br>(multiple units)                           | 1  |

| Short                           | ${ m v}_{ m BUS} \ { m < v}_{ m BATT}$  | 3   | V <sub>BUS</sub> =<br>V <sub>ARRAY</sub>                        | 2   | Array section loss                                         | 1  |

| Control Failure                 | $v_{	ext{BUS}}$                         | 3   | 0 ≤ V <sub>BUS</sub><br>≤V <sub>ARRAY</sub>                     | 2   | V <sub>BATT</sub> ≤V <sub>BUS</sub><br>≤V <sub>ARRAY</sub> | 1  |

| Regulator-Battery<br>Operation: | ľ                                       | i   |                                                                 |     |                                                            |    |

| Open                            | Results in<br>short                     | -   | Complete<br>power loss                                          | -   | Results in short                                           | -  |

| Short                           | V <sub>BUS</sub><br><v<sub>BATT</v<sub> | 2   | $egin{array}{c} V_{	ext{BUS}}^{=} \ V_{	ext{BATT}} \end{array}$ | 1   | V <sub>BUS</sub> <v<sub>BATT</v<sub>                       | 2  |

| Control Failure                 | V <sub>BUS</sub><br>≥ V <sub>BATT</sub> | 1   | $0 \le V_{\text{BUS}}$ $\le V_{\text{BATT}}$                    | 2   | $v_{	ext{BUS}}^{\geq V}_{	ext{BATT}}$                      | 1  |

| Ease of Test<br>On Pad          | Wide ground<br>power limits             |     | Wide ground<br>power limits                                     | 1   | Tight ground power limits, shunt simulation probable       | 2  |

| Flight<br>Demonstration         | Yes                                     | 1   | Partly<br>(Nimbus B)                                            | 3   | Partly (Lunar<br>Orbiter)                                  | 2  |

| TOTALS                          | 5                                       | 33  |                                                                 | 30  |                                                            | 25 |

<sup>\*</sup> Rating Scale:

1 = Highest

2 = Intermediate

3 = Lowest

$$\frac{\text{Shunt demand}}{\text{Boost demand}} = \frac{0.89}{0.98} = 0.91$$

The shunt system incurs an Earth/Mars matching penalty of several percent (see Subsection 3.3.3) and therefore, the relative shunt demand is raised to 0.93.

For raw loads, array power is supplied directly to the raw bus for all candidates. Again the shunt system is penalized by two percent to raise its relative demand to 1.02.

For charge power, small differences in charge power are associated with the relative battery demand—this is not significant as a measure.

## Packaging

No major differences are involved. The bay equipment is about the same for all candidates. The buck system may or may not require zener shunts on the array. The boost system requires zeners; the shunt system requires transistors plus additional wiring for the base drivers. Therefore, they are rated 1, 2, 3 in that order.

## Bay Thermal Design

No significant difference. Main thermal problem is probably battery integration which is common to all candidates.

## Raw Bus Limits

Limits are indicated on Figures 3-4, 3-5 and 3-6.

## Regulated Bus Limits

No measure—similar limits should be achievable with pulse width modulated electronics of all candidates.

Ripple, day; with array power, the shunt system should be best since switching electronics is not in use.

Ripple, night; no measure--with battery power switching electronics is used in all candidates.

Response; no measure--all candidates depend on response of switching electronics.

## **Battery Charger Integration**

A smaller variation in the charger input voltage results in a smaller average drop through the regulator resulting in more efficient power usage. The shunt system, with a fixed charger input voltage, is best in this regard. The buck system may or may not be worse than the boost system depending on whether or not zener array voltage limiters are used.

## Operational Complexity

The boost and buck systems require some means for avoiding solar array/battery load sharing while the shunt system requires a sequence control. Since no switching of relays is required for the shunt system, it is rated better.

## Flexibility/Growth

Power capability during array operation for the boost and buck system is limited by the regulator ratings. The growth of the shunt system is accommodated by adding shunt elements. (Shunt control can be initially designed for possible growth.) During battery operation all systems are limited by regulator size.

## Redundancy Implementation

Redundancy schemes for the shunt system may be complicated by multi-functions operating from a single Sequence Control.

## Failure Modes

## Regulator-Array Operation

- a. Open power transistor: Circuit review of the boost regulator indicates that an open circuit of one transistor would result in a short to ground of the remaining transistor with complete power loss; the bypass diode capability would be ineffective. An open transistor in the buck regulator obviously results in complete power loss. An open shunt transistor of the shunt system results in no power loss; the system can be easily designed to permit several such failures with remaining transistors absorbing the additional shunt load.

- b. Shorted power transistor: For the boost regulator circuit, this is a short to ground with probable full power loss. For the buck regulator, this is a through short and the output is the same as the array voltage input. A shorted shunt transistor only results in loss of the associated array section.

- c. Control failure: With bypass diode capability in the boost regulator the output could be higher but no less than the array input voltage. Inherently the buck regulator cannot produce an output voltage higher than its input; therefore, a control failure could result in output between zero and the highest array input. With the shunt system the array voltage and bus voltage are identical; this voltage can be drawn downward to the battery voltage by virtue of the bypass diode capability of the battery discharge boost regulator.

### Regulator-Battery Operation

- a. Open power transistor: Complete power loss for all candidate systems--no measure.

- b. Shorted power transistor: Probable complete power loss for boost system or shunt system due to short to ground of boost regulator. Through short of buck regulator results in bus voltage same as battery voltage.

- c. Control failure: With bypass diode capability in boost regulator the output could be higher but no less than the battery input voltage; this applies to the boost and shunt systems. Buck regulator maximum output is limited to battery input voltage.

## Ease of Test-On Pad

Both the boost and buck systems can accept wide variations in ground power voltage during on-pad operations by way of array simulation or other power supplies. The boost and buck regulators automatically condition this raw input. The shunt system cannot function in this

way since the shunt transistors are diode isolated on the solar array. Until appropriate solutions are found, the shunt system is rated lower on this criterion.

## Flight Demonstration

The boost system has been used extensively on Mariner and Ranger spacecraft. The buck system has been used on battery powered military satellites and is used on the Nimbus B spacecraft to be launched shortly. The shunt system was used on the Lunar Orbiter spacecraft in a somewhat different arrangement.

The summation of ratings results in the selection of the shunt system as the candidate for further comparison with the MM'69 power system.

#### SECTION 4

### BATTERY CONSIDERATIONS

### 4.1 REQUIREMENTS

The power requirements for the Mars vehicle have been summarized in Section 2. Some of the more important facts concerning the battery design will be outlined here.

The primary difference between the battery requirements for this mission and other Mariner missions is that battery power will be required at the time of planet encounter and also after encounter. This requirement may exist for one of two cases. In Case I power is required for orbit insertion maneuvers and subsequent orbit trim maneuvers. In Case II power is required for solar eclipse periods during planetary orbit in addition to the insertion and orbit trim maneuvers. The orbit cycle would be in the order of 12 to 24 hours with a 1 to 2 hour eclipse. The battery requirement could be from just a few to several hundred cycles, with the battery being charged during daylight periods by the solar array.

## 4.2 BATTERY CANDIDATES

There are three types of batteries which could be considered for use in the Mars vehicle power system. These batteries, all of the alkaline class, are secondary silver zinc, silver cadmium, and nickel cadmium.

The present Mariner battery is representative of a secondary silver-zinc battery and is an important contender in any future Mariner-type missions. Other silver-zinc batteries specifically designed for maximum cycle life with maximum energy density, are also worthy of consideration. Consequently GE-MSD initiated a test program two years ago to investigate the operating characteristics of such silver-zinc and silver-cadmium batteries. Previous work carried out by GE-MSD and work performed by other investigators was believed extensive enough to develop the characteristics of standard nickel-cadmium cells and were not included in the aforementioned test program. However, cells containing a new "third electrode" charge control device have been purchased recently and are being tested. Some of the highlights of the silver cell test program are reported here.

As mentioned previously, these test were concerned with secondary, or rechargeable cells. The primary purpose of the test program was to determine the float capability and cycle life of silver cells representative of the latest state of the art. The Eagle Picher Company of Joplin, Missouri was selected as the vendor for both types of cells.

#### 4.2.1 SILVER-ZINC CELLS

The silver-zinc cells have a nominal capacity of 50 ampere-hours and are assembled in Lustran plastic cases with pressure gages attached. Each cell measures 6-1/8 inch high by 3-1/8 inch wide by 1-1/16 inch thick and weighs 1.55 pounds, exclusive of the pressure gage assembled to each cell. The 152 square inches of silver oxide is contained on 6 plates while the negative electrode consists of 7 zinc plates containing 2 percent mercuric oxide. Separation consists of two layers of polyvinyl alcohol and six layers of cellophane. Each cell contains 113 cc of 40 percent KOH electrolyte.

Cells were tested in packs of five and underwent charge and discharge characteristic tests, and 7- and 24-hour charge/discharge cycles. In addition, some cell packs were placed on float charge for several months and then subjected to repetitive cycling. A summary of tests on the silver-zinc cells is shown in Table 4-1. All cycle tests included a one hour discharge.

Table 4-1. AG-ZN Test Summary

| Pack No.  | Months Test<br>1 2 3 4 5 6 7 8 9 10 11    | Cycles<br>To<br>Failure |

|-----------|-------------------------------------------|-------------------------|

| 1 to 5    | ★ Charge Tests                            |                         |

| 6 to 10   | ₩ 7 Hr Cycle, 40% DOD                     | 94                      |

| 11 to 15  | 7 Hr Cycle, 20% DOD                       | 314                     |

|           | ₩ 24 Hr Cycle, 40% DOD                    | 83                      |

| 21 to 25  | 7 Mo. Float 7 Hr Cycle 20% DOD            | 169                     |

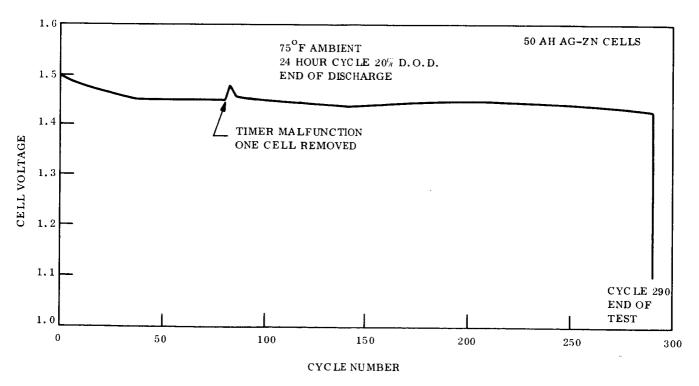

| *26 to 30 | 20% DOD  24 Hr Cycle 20% DOD              | 290                     |

| *31 to 35 | Voyager Power Profile-<br>Float and Cycle |                         |

| *36 to 40 | Float and Cycle at 30° F                  |                         |

<sup>\*</sup> Tests Continuing

# 4.2.1.1 Charge Tests

To determine the most favorable charging procedure to use with these cells, the first part of the test program consisted of charge characterization tests. The charge regime selected was a constant current to a selected voltage limit, with the current tapering at this point holding the charge voltage at the selected level throughout the remainder of the charge period.

After several formation cycles, the pack was discharged a fixed amount (60, 40, or 20 percent of nominal capacity) and recharged to a specified voltage limit (1.96, 1.94, or 1.92 volts/cell, average). Maximum current levels were from 2 to 10 amps. Most of the charge tests were carried out at 75°F, with a few at 30°F for comparative purposes. The only difference attributable to the lower temperature was that charge acceptance was somewhat lower at low temperatures.

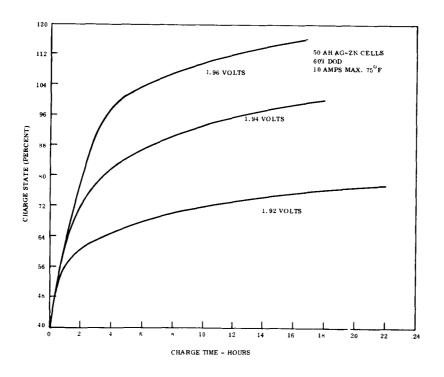

Typical data is plotted in Figure 4-1, where charge acceptance as a function of charge time is shown for three different voltage levels for a battery which had previously been discharged to a 60 percent depth of discharge.

Figure 4-1. Ampere Hours Versus Charge Time

From these tests it was possible to determine the optimum charge voltage to use as a function of depth of discharge and charge time. It was determined that an average voltage level of 1.92 volts per cell was generally too low to allow completion of the charge while a voltage level of 1.96 volts per cell frequently resulted in gas generation during the charge. The level of 1.94 volts was selected for charging, resulting in a limitation on the depth of discharge for shorter cycles.

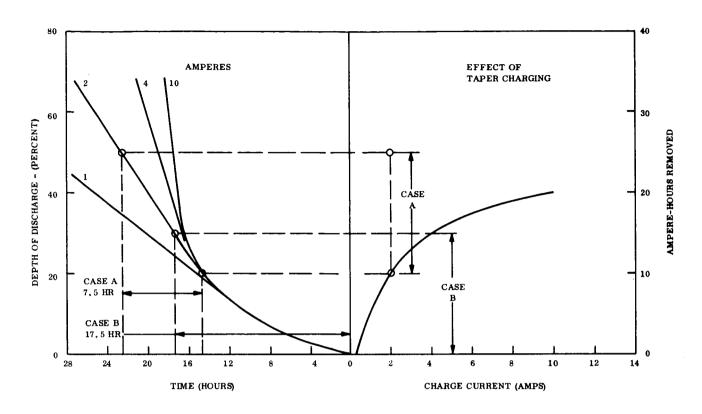

The charge data may be represented in another way as shown in Figure 4-2. Here the point at which tapering of the current occurs is plotted as a function of the charge current. The curve is valid for a cell voltage limit of 1.94 volts per cell. The plot shows the time necessary to complete the charge from a given depth of discharge. In Case A, a 2.0 amp rate is used as the maximum charge current. Starting from a 50 percent depth of discharge (DOD) it can be seen that 15 ampere-hours may be returned in 7.5 hours reducing the DOD to 20 percent. To complete the charge requires an additional 14.5 hours.

A close study of the data presented in Figure 4-2 suggests that it might be advisable to operate the battery at less than full charge. Suppose that it is desired to remove 15 amperehours of capacity from the battery. Case A shows that in operating between 20 and 50 percent DOD, the 15 ampere-hours could be returned to the battery in 7.5 hours, while Case B shows that trying to return this 15 ampere-hours to a battery operating between 30 percent DOD and full charge would require 17.5 hours. It must be assured that cycle life does not suffer from the fact that the battery is operating from less than a fully charged condition.

#### 4.2.1.2 Discharge Tests

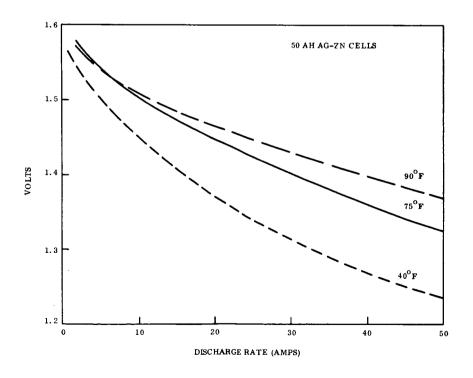

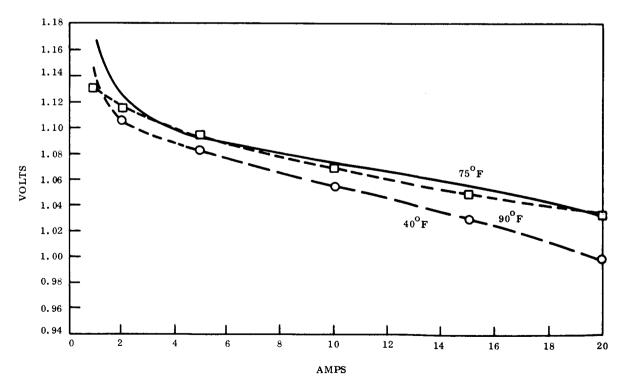

A set of typical V/I curves was generated for this cell by discharging the cell at various rates and measuring the corresponding stabilized voltage. Data is shown in Figure 4-3 for temperatures of 40, 75, and 90°F.

Figure 4-2. Charging Characteristics 50 AH, Ag-Zn Cells, 1.94 Volts/Cell Limit

Figure 4-3. Volts Versus Discharge Rate

# 4.2.1.3 Cycle Tests

Cell packs were put on automatic 7- and 24-hour cycles at room ambient conditions discharging to a 20 or 40 percent depth of discharge. The results of the tests are summarized in Table 4-1. When comparing the results of the tests it may be noted that the total life of the battery pack appears to be a function of the number of cycles rather than the time on test. Compare the 40 percent DOD tests (94 7-hour cycles and 83 24-hour cycles) with the 20 percent DOD tests (314 7-hour cycles and 290 24-hour cycles). While the results of the 40 percent DOD tests are disappointing, the 20 percent DOD tests are encouraging, especially when it is recalled that this silver-zinc cell at a 15 percent DOD is equivalent in usable energy density to a nickel-cadmium cell at a 60 percent DOD.

Plots of average end-of-discharge voltage versus cycle number are shown in Figure 4-4 for the 20 percent DOD 7-hour cycle and in Figure 4-5 for the 20 percent DOD 7-hour cycle.

In all cases, silver-zinc cell failure was caused by internal cell shorting. Because of the use of a relatively low charge voltage limit, 1.94 volts/cell, cell gassing was not a problem and cells did not leak or dry out. Also the polyvinyl alcohol, coupled with the cellophane separator system virtually eliminated the problem of silver migration. Failure was eventually caused by solution and precipitation of the negative material until the separator was either punctured or bypassed.

#### 4.2.1.4 Float Tests

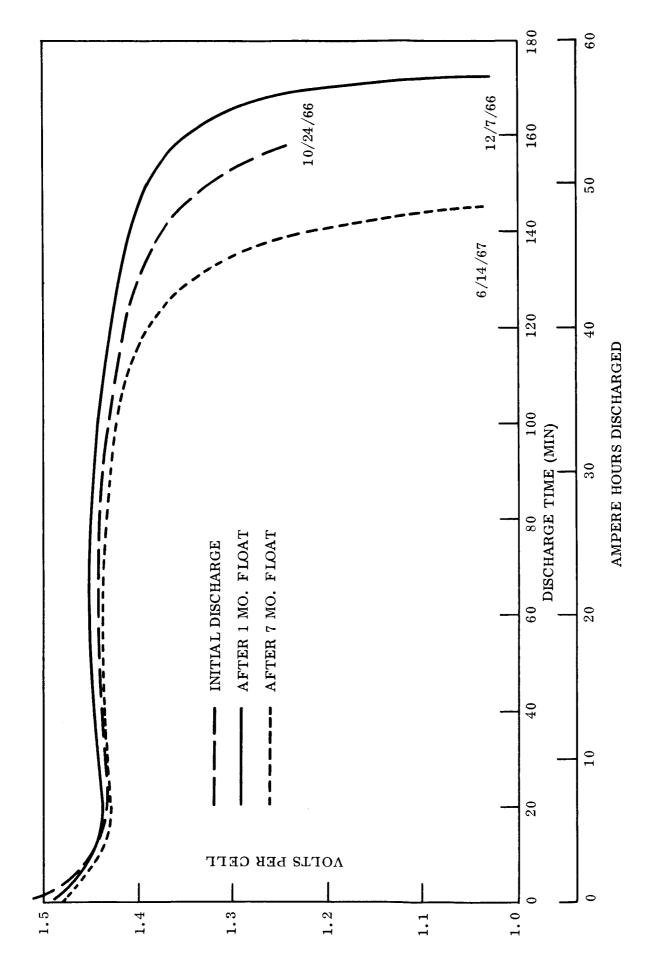

Pack 811-21 to 25 was floated in a fully charged condition at an average voltage level of 1.87 volts/cell for 7 months. Following the float period, the pack was put on a 7-hour cycle at a 20 percent DOD. Figure 4-6 shows the results of several capacity discharges of this pack.

Figure 4-4. End Discharge Voltage Versus Cycle, 20 Percent DOD, 7-Hour Cycle

Figure 4-5. Pack 811-26 to 30, 5-50 AH Ag-Zn Cells

Figure 4-6. Silver-Zinc Secondary Cells Discharge Volts Versus Time for 20 Amp Discharge

It may be seen that the total capacity of the pack was not appreciably degraded; however, when placed on cycle test the pack failed after only 169 20-percent DOD cycles as compared to 314 cycles for a pack which had not undergone the float period. Upon inspection of the failed cells it was observed that the PVA separator had degraded considerably and this was believed to be the reason for the decreased cycle life.

Additional packs are now in the float portion of other float/cycle tests to determine if lower depths of discharge can be sustained for longer time periods and to see if a 30°F environment causes a significant change in operation.

# 4.2.2 SILVER-CADMIUM CELLS

The silver-cadmium cells have a nominal capacity of 20 ampere-hours and are assembled in 302 stainless steel cans. Each cell has two ceramic bushings, insulating the negative and positive terminals from the case. Each cell measures 3-7/16 inches high by 3-3/16 inches wide by 1-7/16 inches in thickness and weighs 1.5 pounds, exclusive of the pressure gage. The 154 square inches of silver oxide is contained on 12 plates while 13 plates contain the negative cadmium material. Separation consists of two layers of polyvinyl alcohol and four layers of cellophane. The electrolyte, in all cases but one, consists of 93 cc of 30 percent KOH. Pack 812-F contains 80 cc of 40 percent KOH.

Cells were tested in packs of six to determine charge and discharge characteristics and cycling capability on 7- and 24-hour charge/discharge cycles. In addition, one pack was placed on float to determine cycling capability after an extended period of floating in a fully charged condition. A summary of the silver cadmium tests is shown in Table 4-2.

# 4.2.2.1 Charge Tests

Charge tests, similar to tests carried out on the silver-zinc cells, were also performed on the silver-cadmium cells. Voltage levels of 1.48, 1.50 and 1.52 volts/cell average were used, recharging from 60, 40, and 20 percent depth of discharge. A 3.0 amp maximum rate was used in all cases. All of the charge tests on the silver-cadmium cells were conducted at

room ambient, about 75°F. Data was obtained similar to that obtained for the silver-zinc cells. It was determined that 1.48 volts/cell was too low for efficient charging, but that 1.50 or 1.52 volts/cell would be satisfactory under certain conditions, if the depth of discharge is not too great. Under certain conditions (pack 812-F) 1.54 volts/cell was used satisfactorily, but usually this voltage level resulted in severe unbalancing during charging with the result that gassing occurred in some cells in the test pack.

# 4.2.2.2 Discharge Tests

Silver-cadmium cells were discharged at 40, 75, and  $90^{\circ}$ F to generate typical V/I curves. The results are shown in Figure 4-7 where data is plotted for rates of 1 to 20 amps.

#### 4.2.2.3 Cycle Tests

Packs were put on 24-hour cycles at 60 and 40 percent DOD and on 7-hour cycles at 40 and 20 percent DOD. Results of these tests are summarized in Table 4-2. No correlation of cycle life with depth of discharge or cycle period is possible, however, cycle life was disappointingly poor except for pack 812-F.

Figure 4-7. Volts Versus Discharge Rate for 20 AH Silver-Cadmium Sealed Cells

Table 4-2. AG-CD Test Summary

| Pack No. | Months Test 1 2 3 4 5 6 7 8 9 10 11                   | Cycles<br>To<br>Failure |

|----------|-------------------------------------------------------|-------------------------|

| Α        | Charge 7 Mo Float 7 Hr Cycle Tests 7 Hr Cycle 20% DOI |                         |

| В        | 7 Hr Cycle, 40% DOD                                   | 285                     |

| C        | 24 Hr Cycle, 60% DOD                                  | 126                     |

| D        | 24 Hr Cycle, 40% DOD                                  | 135                     |

| Е        | 7 Hr Cycle,                                           | 705                     |

| *F       | 7 Hr Cycle<br>40% DOD<br>40% KOH, 2<br>Change         | > 1000<br>Step          |

<sup>\*</sup> Test Continuing

Considering that the nominal energy density is only about 14 watt-hours per pound, these cells would not be competitive with nickel-cadmium cells unless a definite magnetic cleanliness requirement existed.

All silver-cadmium cells failed by a low end-of-discharge voltage phenomenon. When the end-of-charge voltage was increased to increase the charge input, cell unbalancing occurred resulting in gas generation in some of the cells. Failure analysis showed no signs of internal shorting or silver migration. From this it was deduced that failure was caused by negative plate fading or passivation. This phenomena was discussed with the manufacturer who concurred in the explanation, because the negative plate was of pasted construction rather than impregnated on a sintered nickel substrate.

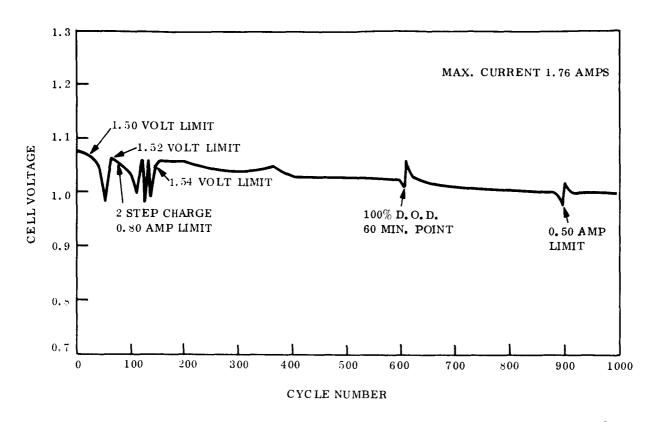

Pack 812-F behaved quite differently and has exceeded 1000 cycles at a 40 percent DOD on a 7-hour cycle. Figure 4-8 shows end-of-discharge voltage versus cycle number. The reason

Figure 4-8. Pack 812-F 6 20 AH Ag-Cd Cells 7-Hr Cycle, 40 Percent DOD, 75°F End-of-Discharge

for this improved operation can be explained by any one of three unique factors existing for this pack:

- a. By an extremely fortunate set of circumstances, six well-balanced cells were selected that can be operated at a charge voltage equivalent to 1.54 volts per cell without becoming unbalanced and generating gas.

- b. The inception of a two-step voltage limit causes the charge voltage to drop to a safe value before unbalancing occurs. Operation in this mode is illustrated by Figure 4-9, where the upper voltage level of 1.54 volts per cell is maintained until the charge current decays to 0.21 amp. At this point the cell voltage is reduced to an average of 1.42 volts/cell, just above the open circuit voltage.

- c. The cells were filled with 40 percent KOH rather than 30 percent KOH electrolyte, resulting in less severe fading and degradation.

Figure 4-9. Silver-Cadmium Cell Pack 8-2-D Cycle 109, 40 Percent DOD, 24-Hr Cycle

## 4.2.2.4 Float Tests

One pack was placed on a 7-month float at 1.42 volts/cell and then cycled at a 20 percent depth of discharge on a 7-hour cycle. The pack survived only 97 cycles before failure occurred as a result of the inability to accept a charge. It was concluded that this cell is severely penalized by long periods on float charge and would not be satisfactory for a Mariner-type mission.

No additional silver-cadmium cells were placed on float test, but it was decided that the use of 40 percent KOH electrolyte for silver-cadmium cells did warrant further investigation.

#### 4.2.3 NICKEL CADMIUM CELLS

# 4.2.3.1 Standard Nickel Cadmium Cells

The Space Systems Organization has carried out a considerable amount of testing with hermetically-sealed nickel-cadmium cells. Batteries have been tested in thermal-vacuum chambers to determine thermal characteristics, on 5-hour and synchronous orbit-type cycles to determine cycle life capability, and on continuous overcharge tests.

Cells used for the latter tests were 11 to 12 ampere-hour cells, purchased in late 1961, which were placed on a continuous charge for over 500 days at a C/7 rate and following a capacity discharge, when they delivered over 12 ampere hours of capacity, were put in storage in the laboratory for over two years. They were subsequently removed from storage, given a few conditioning cycles, and placed on a continuous 24-hour cycle, discharging to a 60 percent DOD. These cells have completed over 500 cycles and are still operating satisfactorily.

#### 4.2.3.2 Third Electrode Nickel-Cadmium Cells

A relatively new method in battery charge controls employs the use of a third or auxiliary electrode to signal when a cell has reached full charge. Using this method, a nickel-cadmium battery may be recharged at a rapid rate, and reduced to a safe trickle rate when the charge has been completed. Several 20 ampere-hour cells containing third electrodes have been procured for evaluation. It is expected that they will be tested at several charge rates and temperatures to determine the effect of these parameters on the third electrode signal and the charge acceptance of the cells.

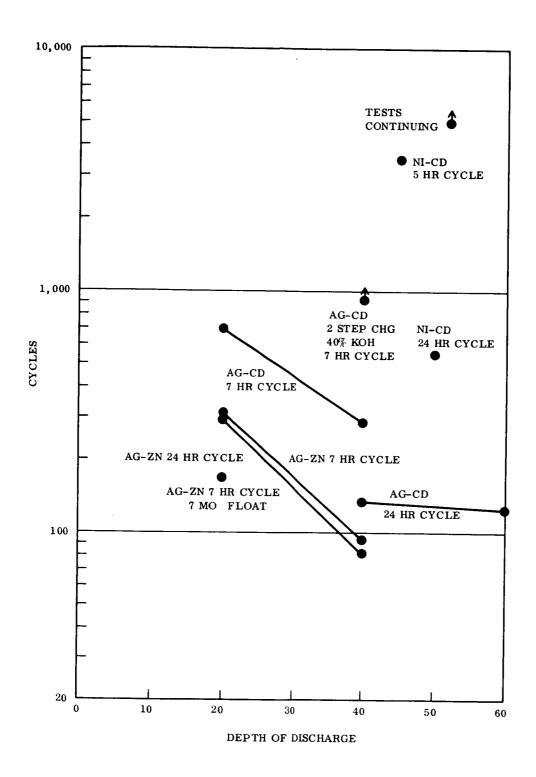

An overall comparison of silver-zinc, silver-cadmium cycle-life capability as a function of depth of discharge is shown in Figure 4-10.

Figure 4-10. Cycle Life Versus DOD for Ag-Zn, Ag-Cd, and Ni-Cd Cells at  $25^{\circ}\mathrm{C}$

#### SECTION 5

#### RELIABILITY SENSITIVITY STUDIES

# 5.1 APPROACH

It is very difficult to accurately predict or calculate the reliability of various piece parts, subunits of a blackbox or the complete blackbox, because of uncertainties in reliability data and shortcomings in reliability modeling techniques. Consequently, the approach taken on this study is to perform selected sensitivity studies in a parametric fashion to illuminate key questions concerning the operation of the subsystem elements.

Utilizing parametric sensitivity studies we can plot results, for specific points to be analyzed, for the full range of reliability from 0 to 1, and then we can assess the relative importance of various questions, even though we do not know with any confidence the actual hardware reliabilities of the various elements. By way of illustrating this approach, and how the results of such studies can provide insight into certain fundamental questions, the first two examples, discussed separately in the following section, consider the cases of two series elements and two parallel elements. These examples, as well as the remainder of the analysis in this section, have been studied with the use of the remote access time sharing computer system.

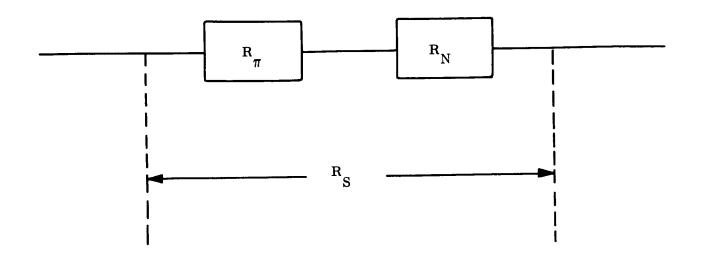

#### 5.2 SERIES EXAMPLE

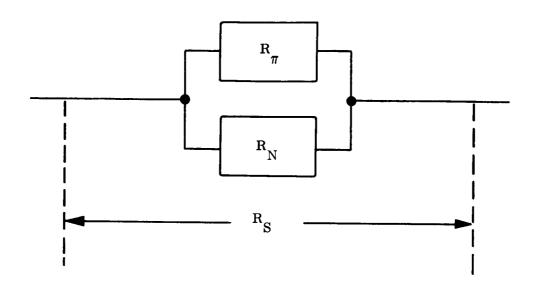

Figure 5-1 shows the block diagram being analyzed.  $R_{\pi}$  represents the reliability of one black box and  $R_{N}$  represents the reliability of the second black box. For the system to work both black boxes must work; hence, the series diagram.  $R_{S}$  is the reliability of the system and is:

$$R_{S} = R_{\pi} \times R_{N} \tag{5-1}$$

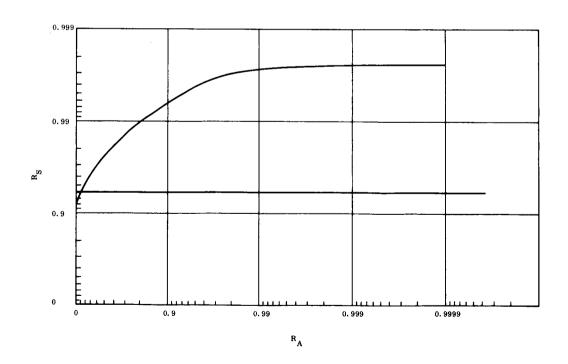

Figure 5-2 is a plot of the system reliability,  $R_s$ , versus the reliability of the first black box,  $R_{\pi}$ . The parameter represents the reliability of the second black box,  $R_N$ .

Figure 5-1. Series Block Diagram

Figure 5-2. Series System Reliability

#### 5.2.1 CONCLUSIONS

Several general conclusions concerning a series system can be seen from examination of Figure 5-2 and Equation 5-1.

- a.  $R_{\pi}$  and  $R_N$  are interchangeable; consequently any statement made about one black box equally applies to the other.

- b. The system reliability never exceeds the reliability of the lower element.

- c. The system reliability improves linearly with improvement of the lowest element until the lowest element is nearly as reliable as the highest element.

- d. Once the most reliable element is about any order of magnitude better than the lowest element, no significant system improvement follows from further improvement of the highest element.

- e.  $R_{\pi}$  and/or  $R_N$  can represent the reliability of a single black box or the reliability of several black boxes in series.

- f. From b and c, above, it follows that to improve the system, effort should be concentrated on improving the least reliable element.

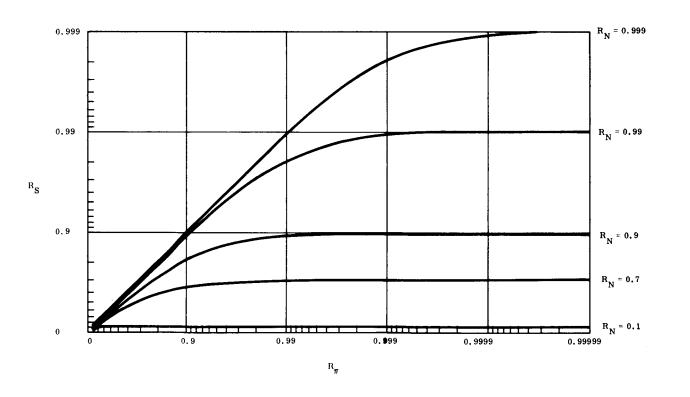

#### 5.3 PARALLEL EXAMPLE

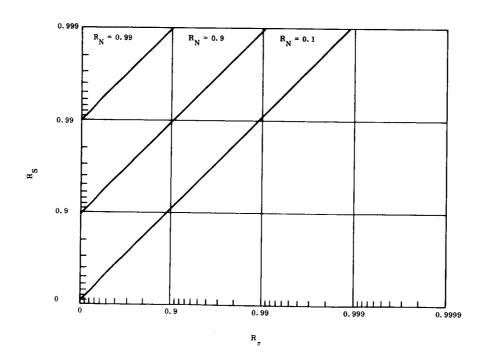

Figure 5-3 shows the block diagram being analyzed.  $R_{\pi}$  represents the reliability of one black box and  $R_{N}$  represents the reliability of a second black box. The system works successfully if either black box works, hence the parallel diagram.  $R_{s}$  is the reliability of the system and is:

$$R_{s} = R_{\pi} + R_{N} - R_{\pi} R_{N}$$

(5-2)

Figure 5-4 is a plot of the system reliability,  $R_s$ , versus the reliability of one black box,  $R_\pi$ . The parameter represents the reliability of the second black box,  $R_N$ .

Figure 5-3. Parallel Block Diagram

Figure 5-4. Parallel System Reliability

#### 5.3.1 CONCLUSIONS

Several general conclusions concerning a parallel system can be seen from Figure 5-4.

- a.  $R_{\pi}$  and  $R_N$  are interchangeable, consequently any statement made about one black box equally applies to the other.

- b. The system reliability always exceeds the reliability of the highest element.

- c. The system reliability improves with improvement of either element.

- d. The system reliability always improves with improvement of either element reliability: no matter what the relative reliabilities are.

- e.  $R_{\pi}$  and/or  $R_N$  can represent the reliability of a single black box or the reliability of several black boxes in series.

- f. From b, c and d, it follows that to improve the system, effort can be applied to either element; hence, which element is easiest to improve would become the main criteria.

# 5.4 FAULT SENSING AND SWITCHING

One of the major areas of interest on this study is the subject of switched redundancy for regulators and inverters. The use of a standby regulator and/or inverter in conjunction with a fault detection and switching system always raises the question of whether the system reliability might not have actually been degraded by the additional fault sensing complexity. The following sections describe studies aimed at illuminating this general question.

# 5.4.1 COLD VERSUS HOT REDUNDANCY

Standby redundancy can be implemented in two ways:

- a. Hot redundancy where the standby unit is always turned on

- b. Cold redundancy where the standby unit is not turned on until the main unit has failed.

Presumably cold redundancy would be the most reliable since the standby unit is not on until the main unit fails, hence, its operating life is shorter. The following analysis sheds some light on this specific question as well as the general subject of fault sensing and switching of a redundant element.

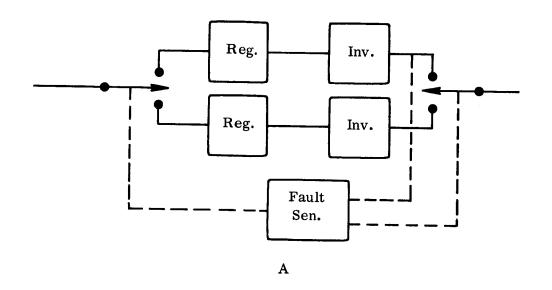

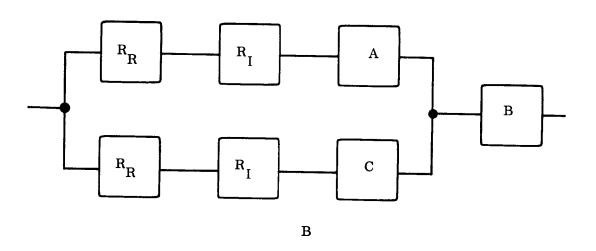

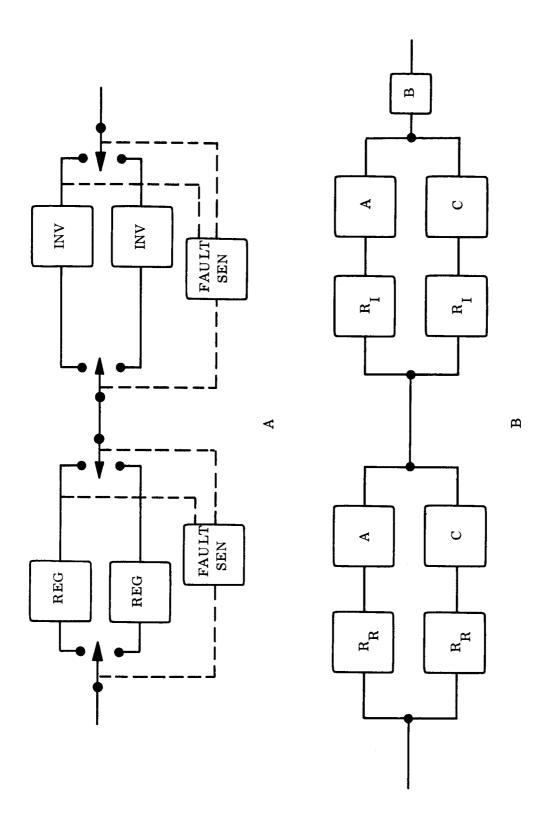

Figure 5-5, Part A, shows the basic circuit being analyzed, and Figure 5-5, Part B, the corresponding block diagram used to assess the system reliability.

$R_R$  and  $R_I$  represent the reliabilities of the regulator and inverter, respectively. The A, B, and C blocks represent the reliability of the fault sensing and switching. The failure modes which are incorporated in the A, B, and C blocks are listed below:

$\mathbf{B}$

A Open top relay

Pole of relays open

• Open relay coil

• False detection and switching

contacts

- Pole side relay connections open

- Welded top contacts

C

- Fault sensor fails to detect failure and/or switchover

- Bottom contact open

For the hot redundancy situation the total system reliability is:

$$R_{s} = [1 - (1 - R_{R} R_{I} R_{A}) (1 - R_{R} R_{I} R_{C})] R_{B}$$

(5-3)

For the cold redundancy situation the total system reliability is:

$$R_{s} = e^{-(\alpha + \lambda_{\beta}) T} + \frac{\alpha}{\beta - \alpha} e^{-(\beta + \lambda_{\beta}) T} \left[ e^{-(\alpha - \beta) T} - 1 \right]$$

(5-4)\*

<sup>\*</sup> This equation assumes: (1) the A block must work from the beginning of the mission until a switchover to the redundant string occurs, (2) the B block must work for the entire mission, and, (3) the C block must work from the time the standby chain is first used until the end of the mission. Actually most of the C block items must work only until a switchover to the standby chain occurs. This analysis was checked and the numerical results are essentially the same for either time of operation of the C block.

Figure 5-5. Paired Regulator Inverter

where:

$$\alpha = \lambda_{\mathbf{R}} + \lambda_{\mathbf{I}} + \lambda_{\mathbf{A}} ,$$

$$\beta = \lambda_{\mathbf{R}} + \lambda_{\mathbf{I}} + \lambda_{\mathbf{C}} ,$$

$\lambda_{i}$  = the failure rate of the  $i^{th}$  component,

T = mission time

all reliability functions are assumed to be exponential functions.

# 5.4.1.1 Conclusions