#### **General Disclaimer**

# One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some

of the material. However, it is the best reproduction available from the original

submission.

Produced by the NASA Center for Aerospace Information (CASI)

FINAL REPORT

STUDY OF STATE-OF-THE-ART

STATIC INVERTER DESIGN

LIBRARY COPY

AUG 8 1966

MANNED SPACECRAFT CENTER HOUSTON, TEXAS PREPARED FOR

# NATIONAL AERONAUTICS and SPACE ADMINISTRATION

JUNE 16,1966 CONTRAC: NAS 9-5580

LIBRARY COPY

MAR 27 1967

HANNED SPACEGRAFT CENTER HOUSTON, TEXAS

STATIC POWER DIVISION

BIOMETRICS INSTRUMENT CORP.

1600 DALLAS NORTH PARKWAY,

PLAND, TEXAS 75074

# FINAL REPORT

# STUDY OF STATE-OF-THE-ART STATIC INVERTER DESIGN

ВҮ

C. L. PAYNE, M. G. WARFORD, D. C. NIPPER, J. P. SMITH, AND J. D. GILLETT

PREPARED FOR

# NATIONAL AERONAUTICS and SPACE ADMINISTRATION

JUNE 16,1966 CONTRACT NAS 9-5580

TECHNICAL MANAGEMENT, NASA - MANNED SPACECRAFT CENTER

INSTRUMENTATION AND ELECTRONICS SYSTEMS DIVISION, F.E. EASTMAN

STATIC POWER DIVISION

BIOMETRICS INSTRUMENT CORP. 1600 DALLAS NORTH PARKWAY, PLANO, TEXAS 75074

# TABLE OF CONTENTS

| Section   | Title                                                | Page |

|-----------|------------------------------------------------------|------|

|           | SUMMARY                                              | 1    |

| I         | INTRODUCTION                                         | 2    |

| II        | STATE-OF-THE-ART STUDY                               | e't  |

| A.        | INTRODUCTION                                         | 4    |

| B.        | DISCUSSION                                           | 5    |

| C.        | DESIGN SELECTION                                     | 27   |

| III       | ELECTRICAL DISCUSSION                                | 30   |

| A.        | GENERAL CIRCUIT DESCRIPTION                          | 30   |

| В.        | DETAILED CIRCUIT DESCRIPTION                         | 37   |

| C.        | THREE-PHASE AND PARALLEL OPERATION                   | 74   |

| IV        | DESIGN ANALYSIS AND CONSIDERATIONS                   | 81   |

| Α.        | BASIC DESIGN CONSIDERATION                           | 82   |

| B.        | PULSE-WIDTH MODULATION ANALYSIS                      |      |

| C.        | DEMODULATOR STAGE AND DRIVE                          | 98   |

| D.        | POWER STAGE AND DRIVE                                | 114  |

| E.        | FILTERING                                            | 115  |

| F.        | CONTROL FUNCTIONS                                    | 130  |

| V         | MECHANICAL DESIGN                                    | 131  |

| VI        | RELIABILITY ANALYSIS                                 | 137  |

| <b>A.</b> | PRELIMINARY RELIABILITY ANALYSIS                     | 137  |

| В.        | RELIABILITY DISCUSSION                               | 137  |

| VII       | DESIGN RECOMMENDATIONS                               | 141  |

|           | APPENDICES                                           |      |

| A.        | BIBLIOGRAPHY                                         |      |

| В.        | PHASE-DEMODULATED HIGH-FREQUENCY<br>INVERTER DESIGNS |      |

| C         | ΠΕΤΔΙΙΕΝ ΝΑΡΥς ΙΙΚΉ                                  |      |

# LIST OF TABLES

HERMAN

Homissian

| Table | Title                                                                                       | Page |

|-------|---------------------------------------------------------------------------------------------|------|

| 1     | Step-Wave Output Steps vs Distortion                                                        | 17   |

| 2     | Inverter Design Evaluation                                                                  | 29   |

| 3     | Calculated Amplitude Distribution of a Trailing Edge Modulated Waveform vs Modulation Index | 90   |

| 4     | Calculated vs Measured Amplitude Distribution of Trailing Edge Modulated Waveform           | 91   |

| 5     | Calculated Amplitude Distribution of a Double Edge Modulated Waveform vs Modulation Index   | 107  |

| 6     | Calculated vs Measured Amplitude Distribution of a Double Edge Modulated Waveform           | 107  |

| 7     | High-Voltage Switching Transistors                                                          | 109  |

| 8     | High Power Switching Transistors                                                            | 114a |

| 9     | Power Dissipation                                                                           | 134  |

| 10    | Weight Analysis                                                                             | 135  |

| 11    | Reliability Analysis Summary                                                                | 137a |

# LIST OF FIGURES

| Figure | Title                                                        | Page |

|--------|--------------------------------------------------------------|------|

| 1      | Parallel Inverter                                            | 6    |

| 2      | Chopper REgulator                                            | 8    |

| 3      | Quasi-Square Wave Voltage Waveform                           | 9.   |

| 4      | Harmonic Distribution                                        | 11   |

| 5      | Series Connected Parallel Inverter                           | 12   |

| 6      | Bridge Inverter                                              | 14   |

| 7      | Step-Wave Inverter                                           | 16   |

| 8      | High-Frequency Step-Wave Inverter                            | 19   |

| 9      | High-Frequency DC-DC Converter/Inverter                      | 21   |

| 10     | Pulse-Width Modulated Inverter                               | 23   |

| 11     | Pulse Demodulated High-Frequency Inverter                    | 25   |

| 12     | Modulated Waveforms                                          | 31   |

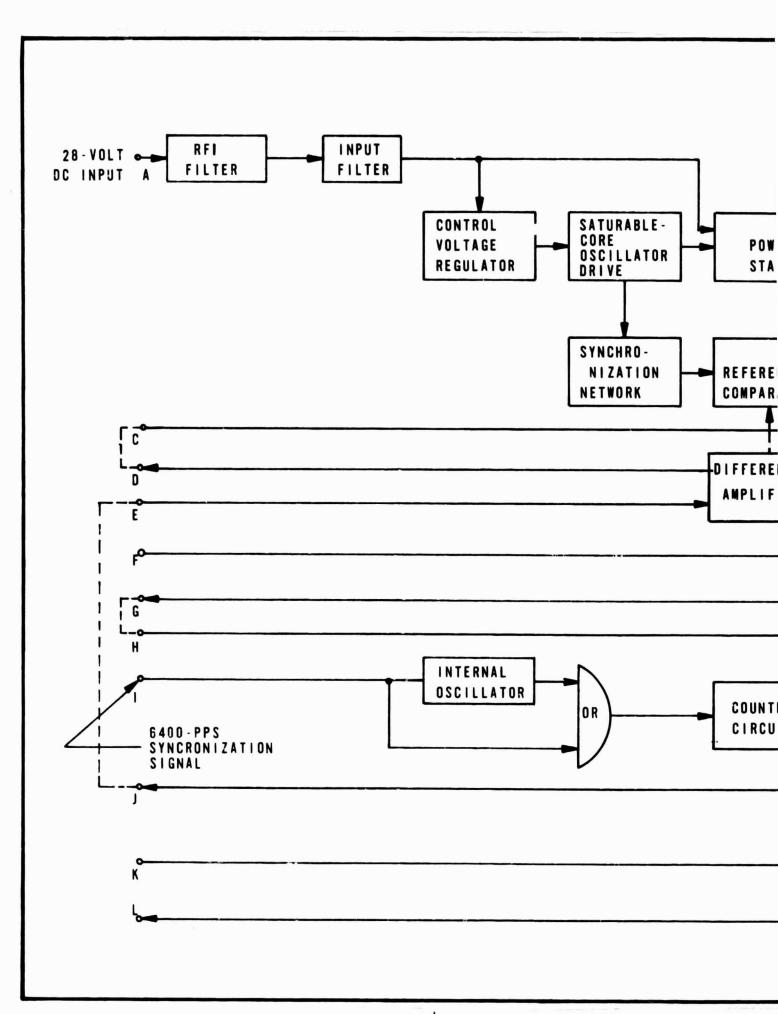

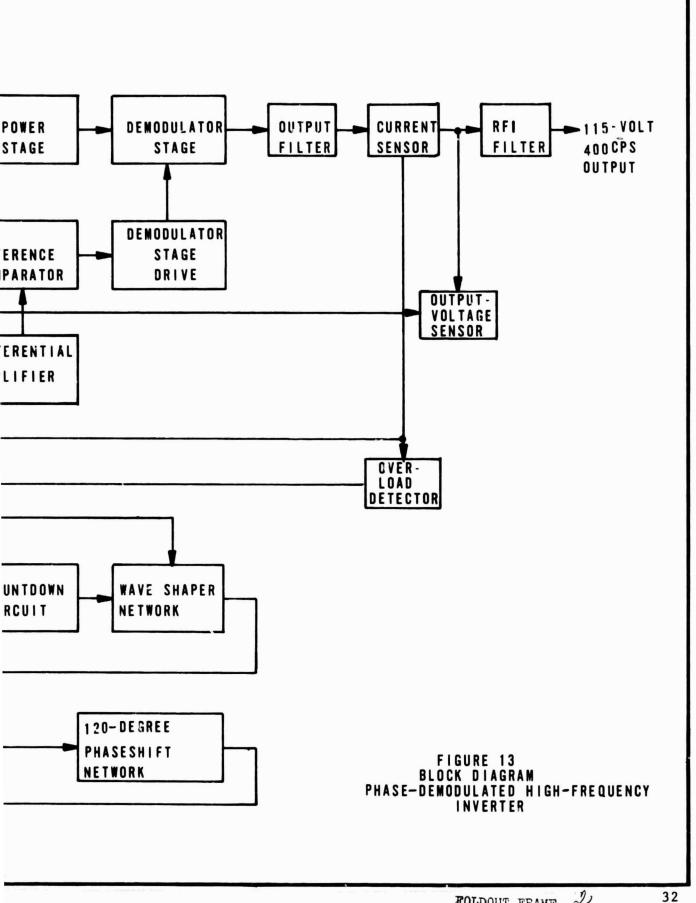

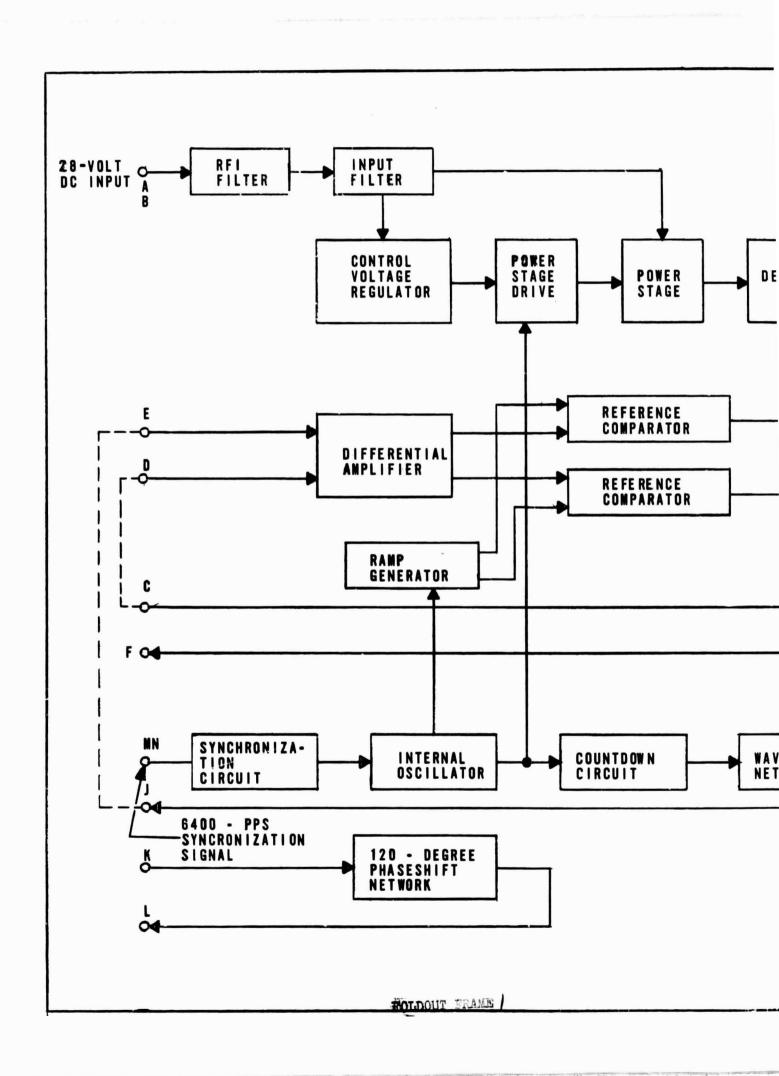

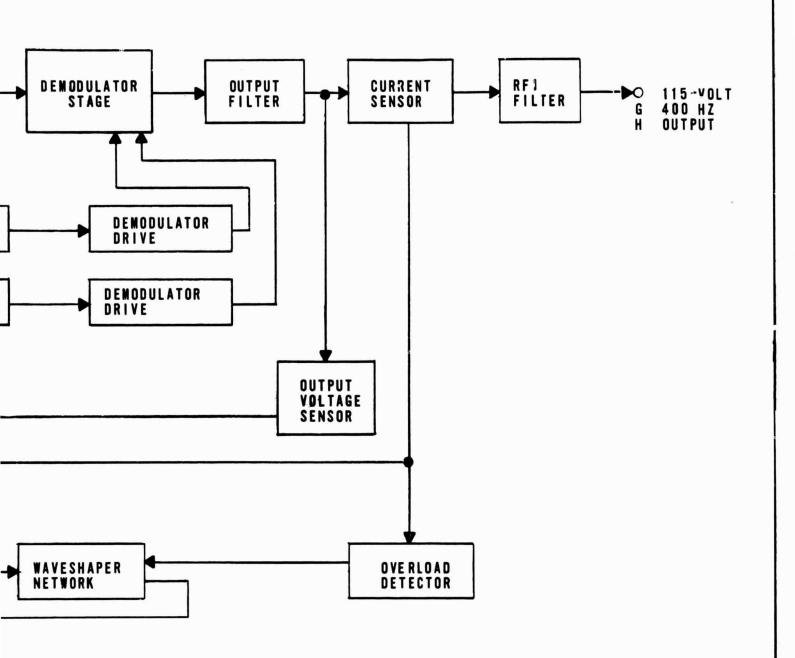

| 13     | Block Diagram - Phase Demodulated High<br>Frequency Inverter | 32   |

| 14     | Demodulated High-Frequency Bridge Inverter                   | 33   |

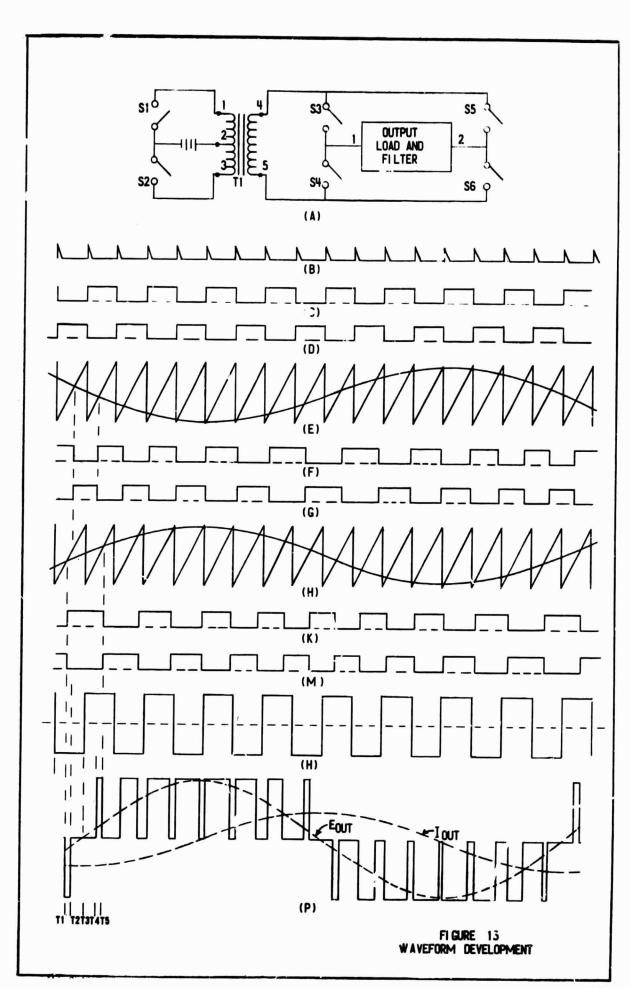

| 15     | Waveform Development                                         | 35   |

| 16     | Schematic Diagram                                            | 38   |

| 17     | Control Voltage Regulator                                    | 40   |

| 18     | Chopper Regulator                                            | 41   |

| 19     | Series Regulator                                             | 43   |

| 20     | Oscillator Network                                           | 44   |

| 21     | Power Stage Drive                                            | 46   |

| 22     | Drive Stage Waveforms                                        | 47   |

| 23     | Power Stage                                                  | 49   |

| 24     | Power Stage Waveforms                                        | 50   |

| 25     | Countdown and Filter Network                                 | 51   |

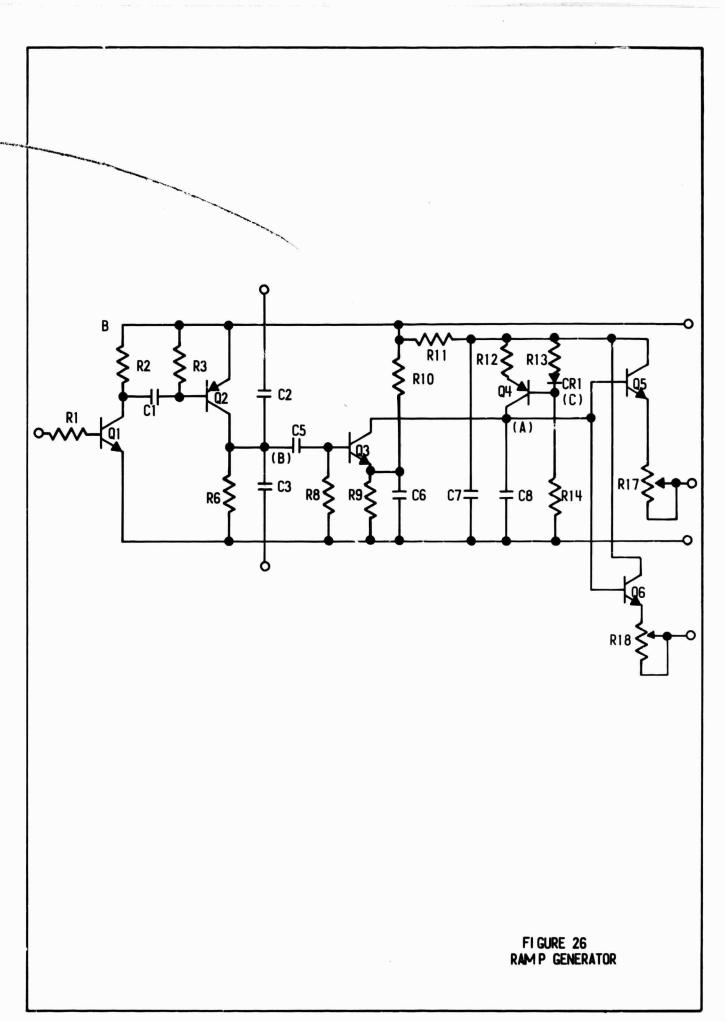

| 26     | Ramp Generator                                               | 53   |

| 27     | Sawtooth Waveforms                                           | 54   |

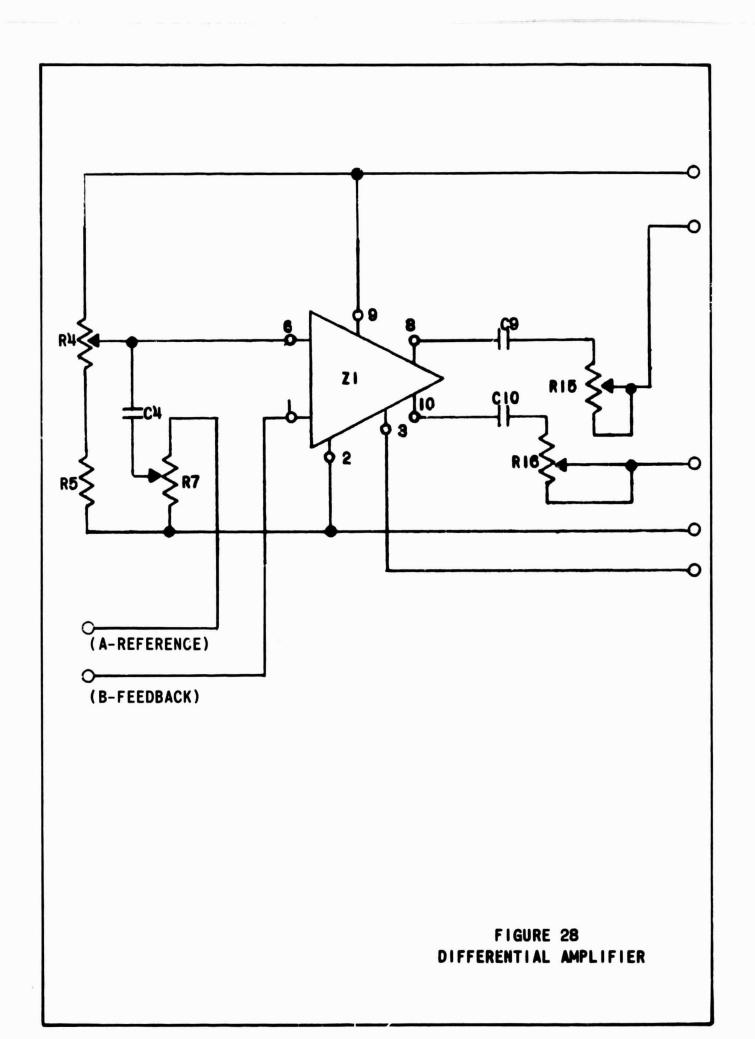

| 28     | Differential Amplifier                                       | 56   |

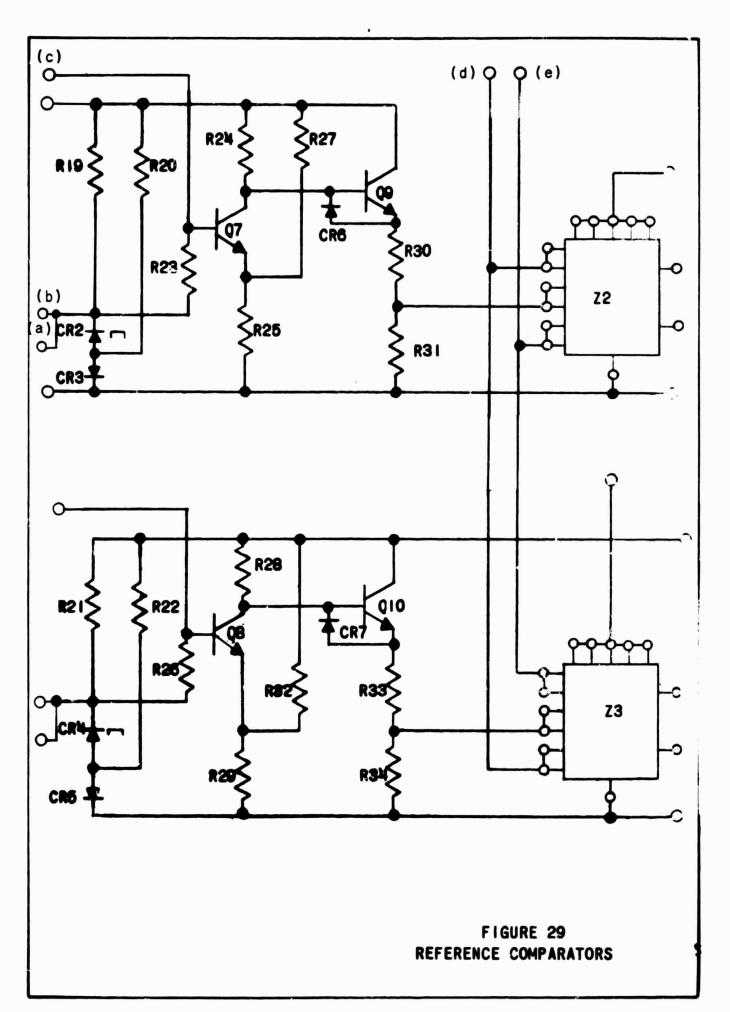

| 29     | Reference Comparators                                        | 57   |

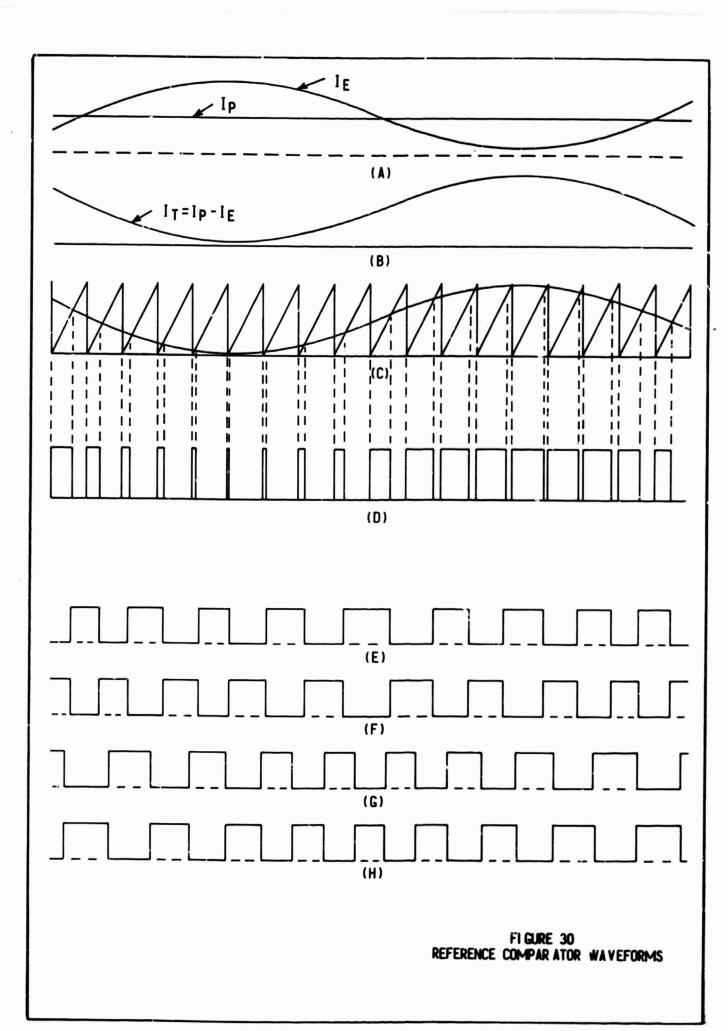

| 30     | Reference Comparator Waveforms                               | 58   |

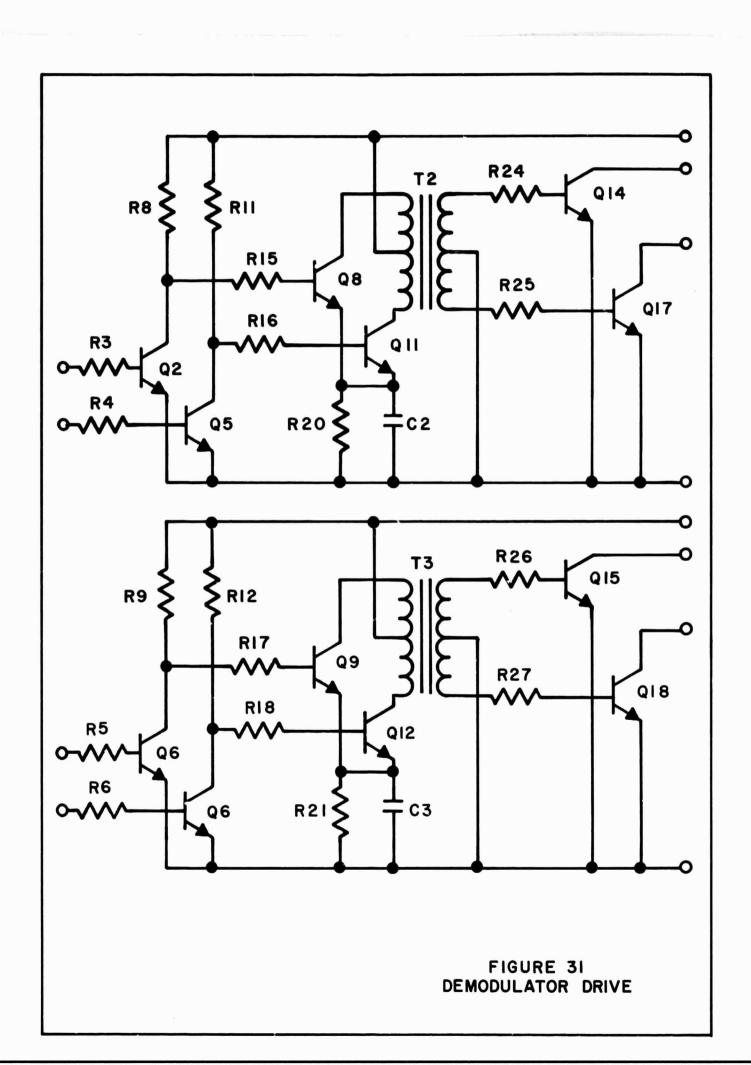

| 31     | Demodulator Drive                                            | 61   |

| 32     | Demodulator Stage                                            | 62   |

| 33     | Bilateral Switch                                             | 63   |

| Figure | Title                                                                        | Page |

|--------|------------------------------------------------------------------------------|------|

| 34     | Simplified Schematic                                                         | 64   |

| 35     | Demodulator Waveforms                                                        | 65   |

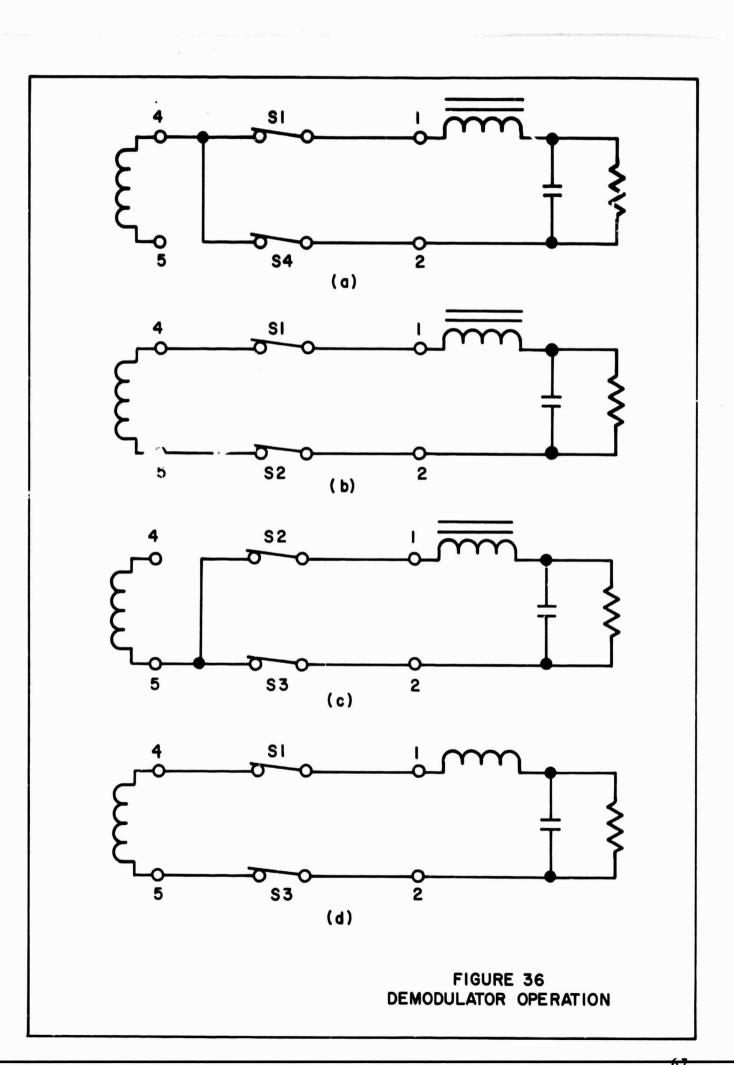

| 36     | Demodulator Operation                                                        | 67   |

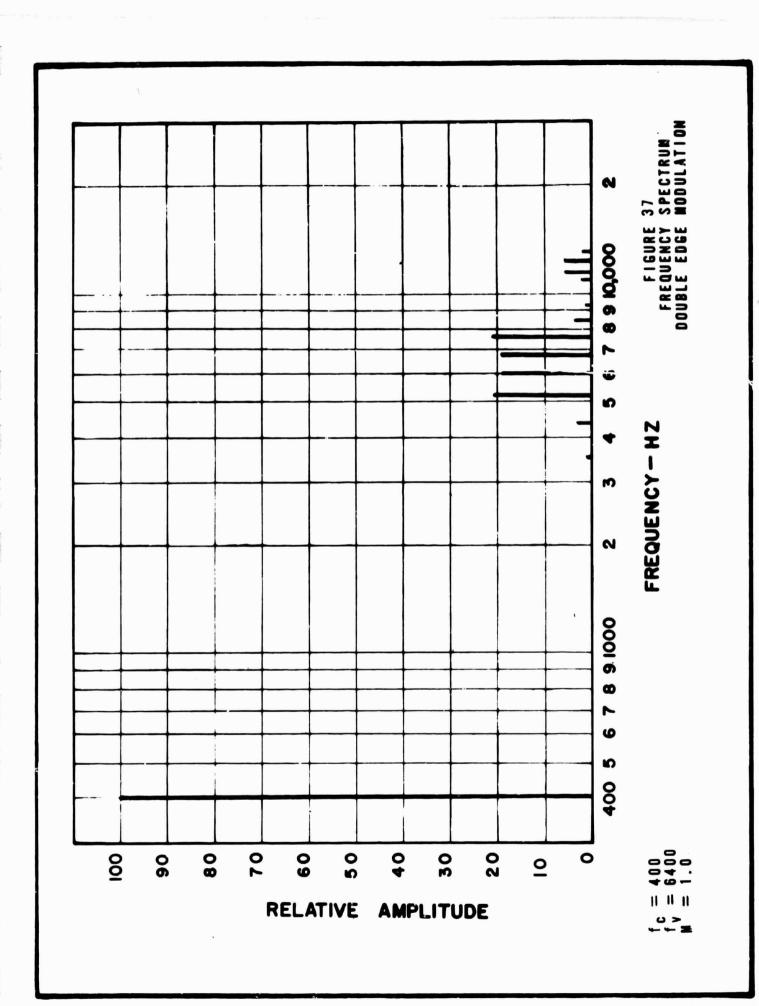

| 37     | Frequency Spectrum Double Edge Modulation                                    | 69   |

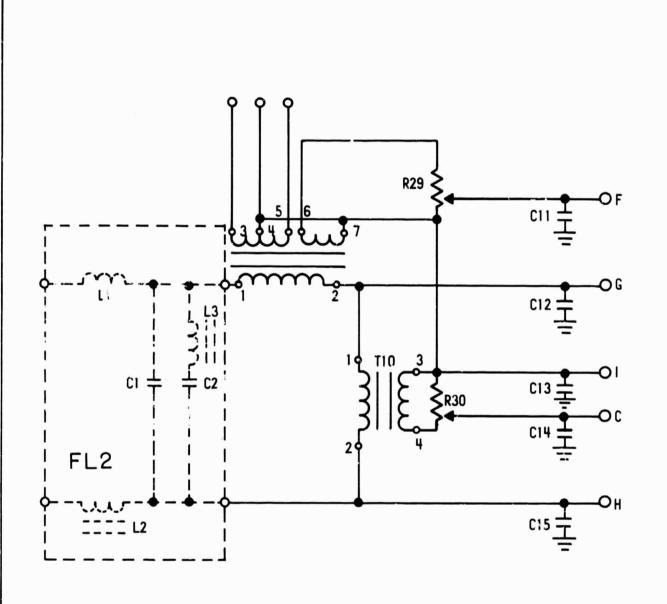

| 38     | Output Network                                                               | 70   |

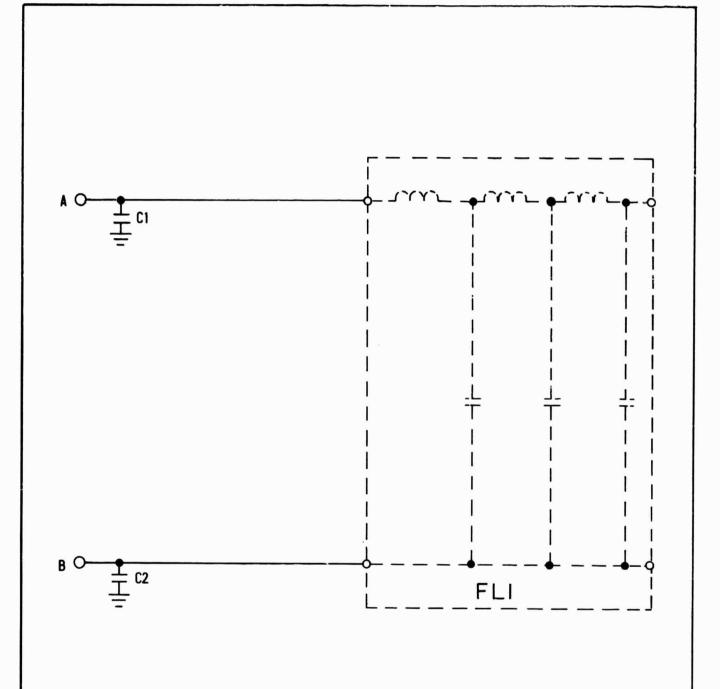

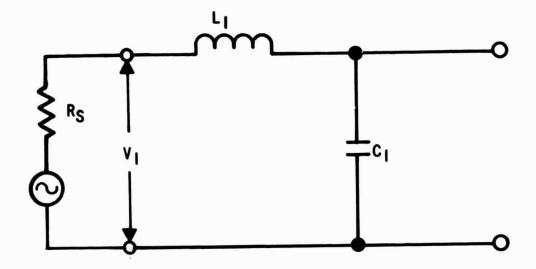

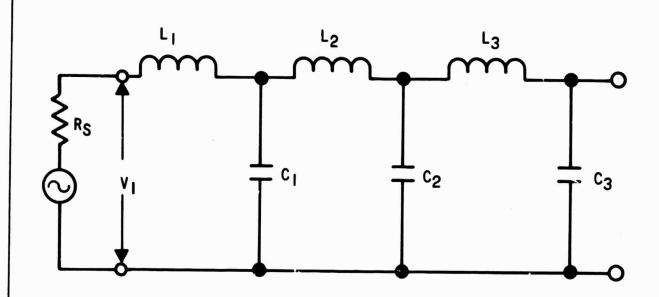

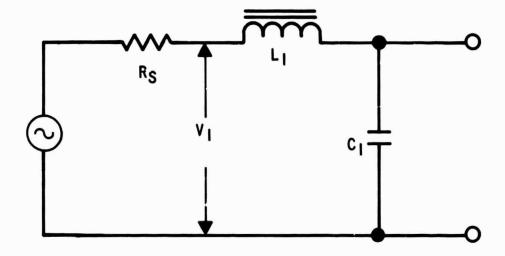

| 39     | Input Filter                                                                 | 71   |

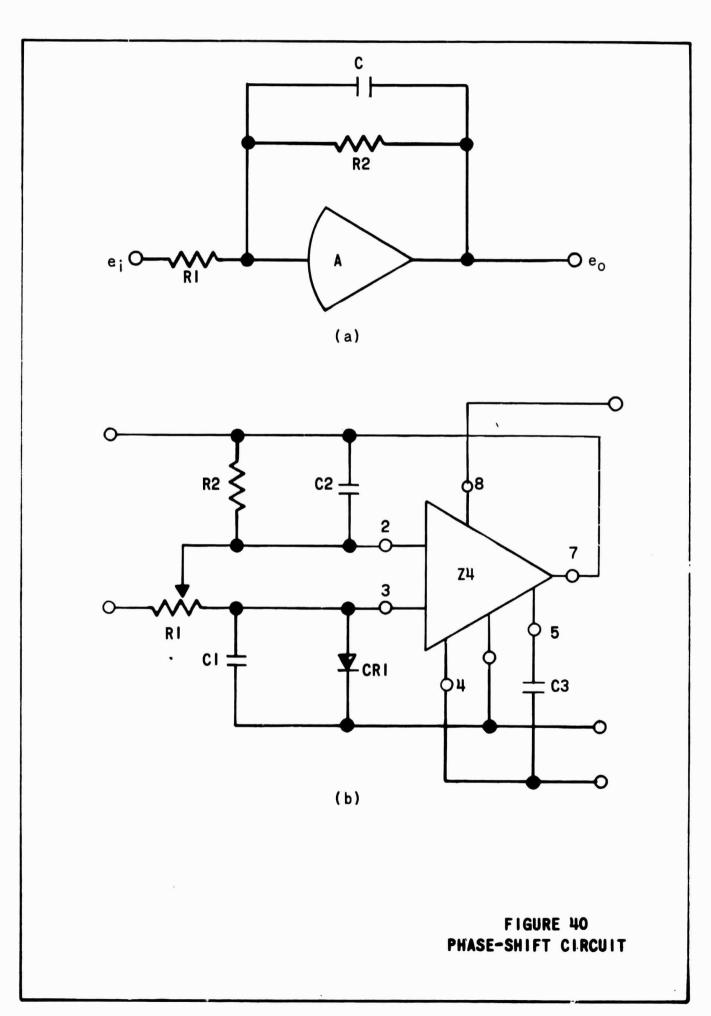

| 40     | Phase Shift Circuit                                                          | 75   |

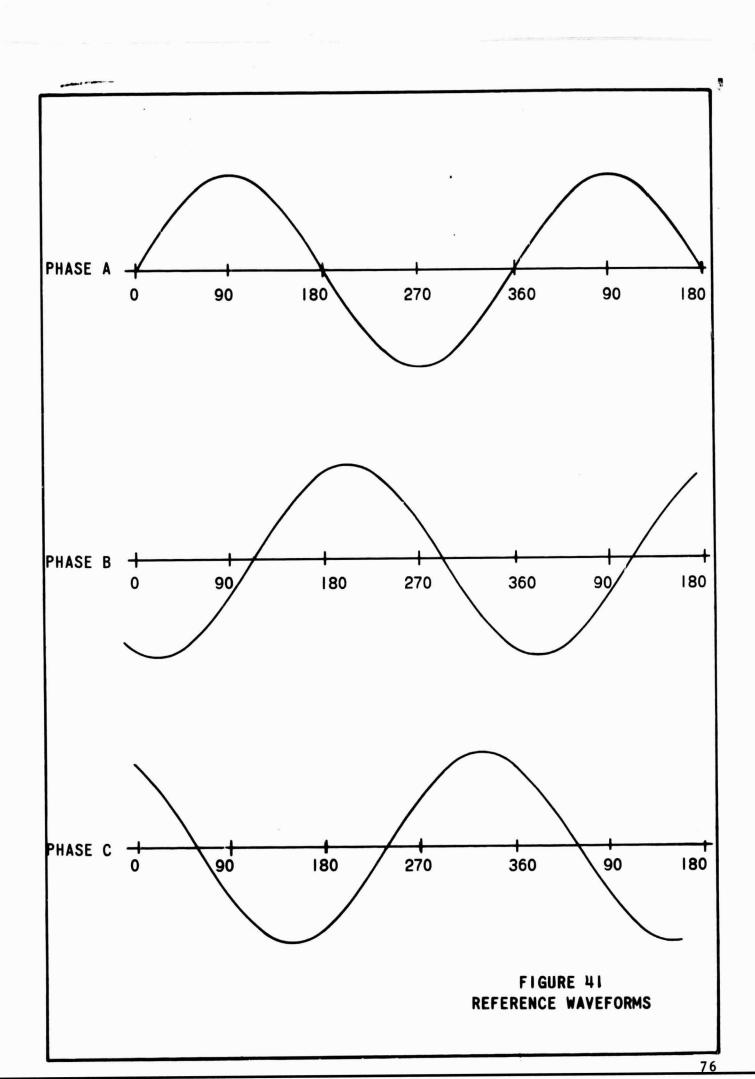

| 41     | Reference Waveforms                                                          | 76   |

| 42     | Three-Phase Interconnections                                                 | 77   |

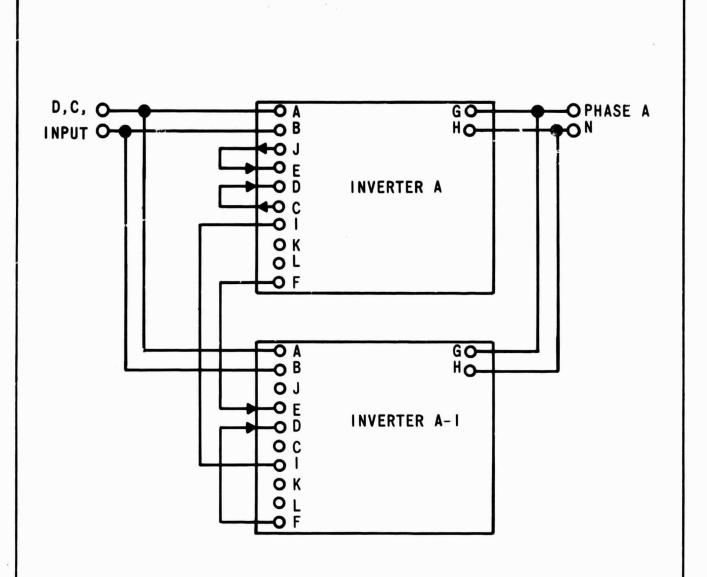

| 43     | Parallel Interconnections                                                    | 79   |

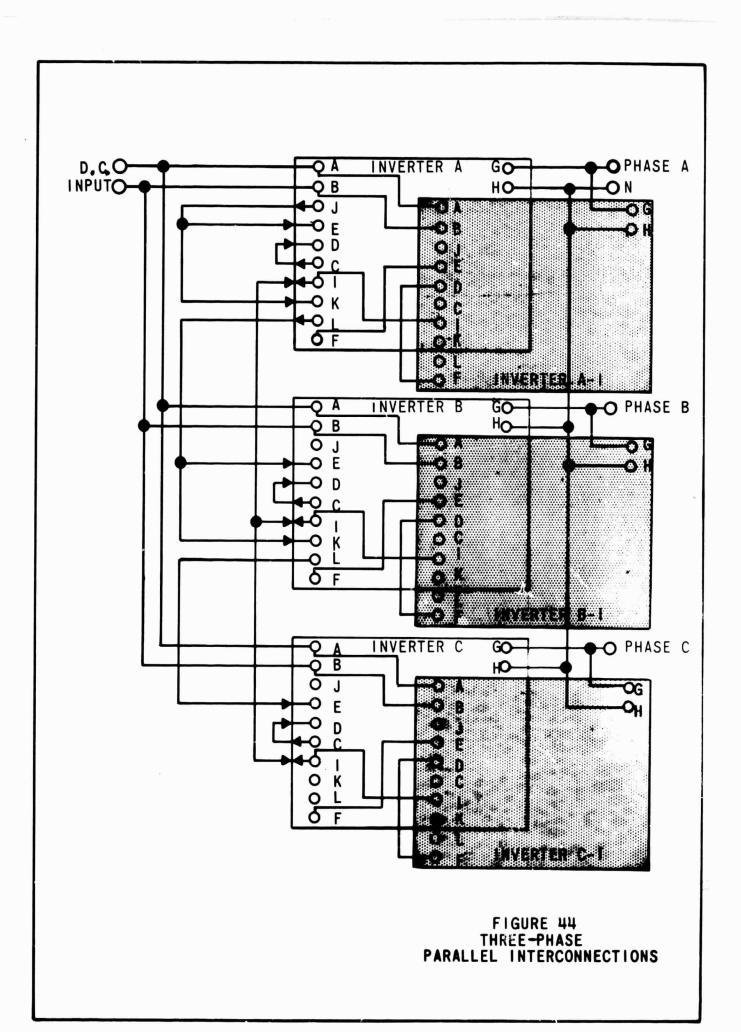

| 44     | Three-Phase Parallel Interconnections                                        | 80   |

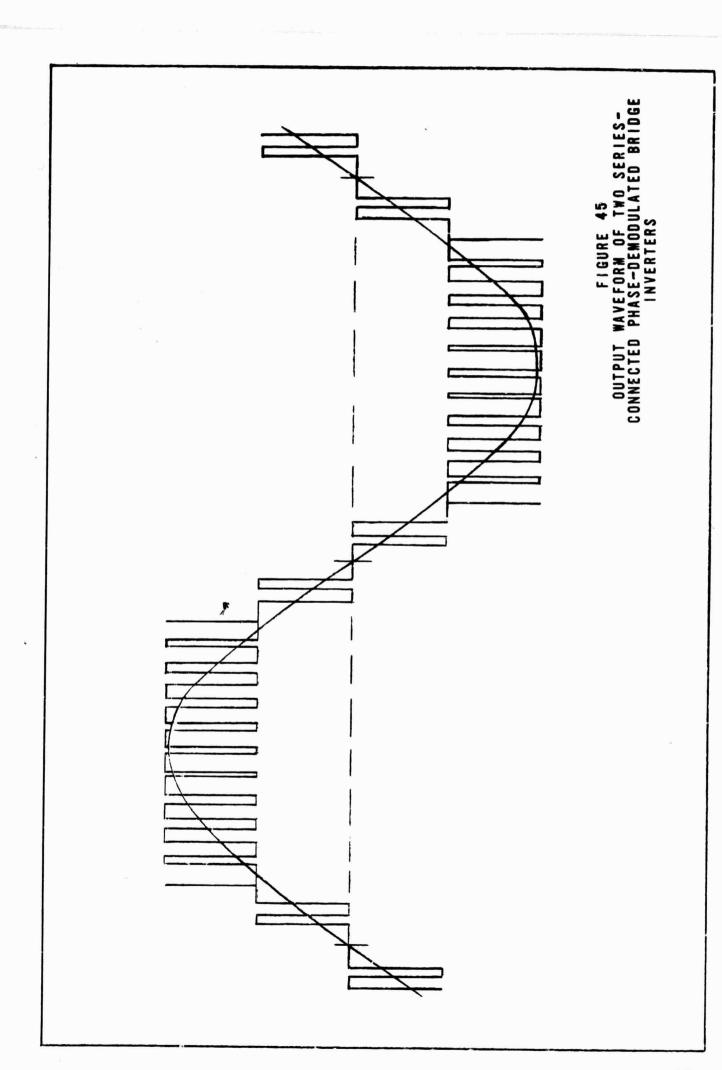

| 45     | Output Waveform of Two Series  Connected Phase Demodulated  Bridge Inverters | 83   |

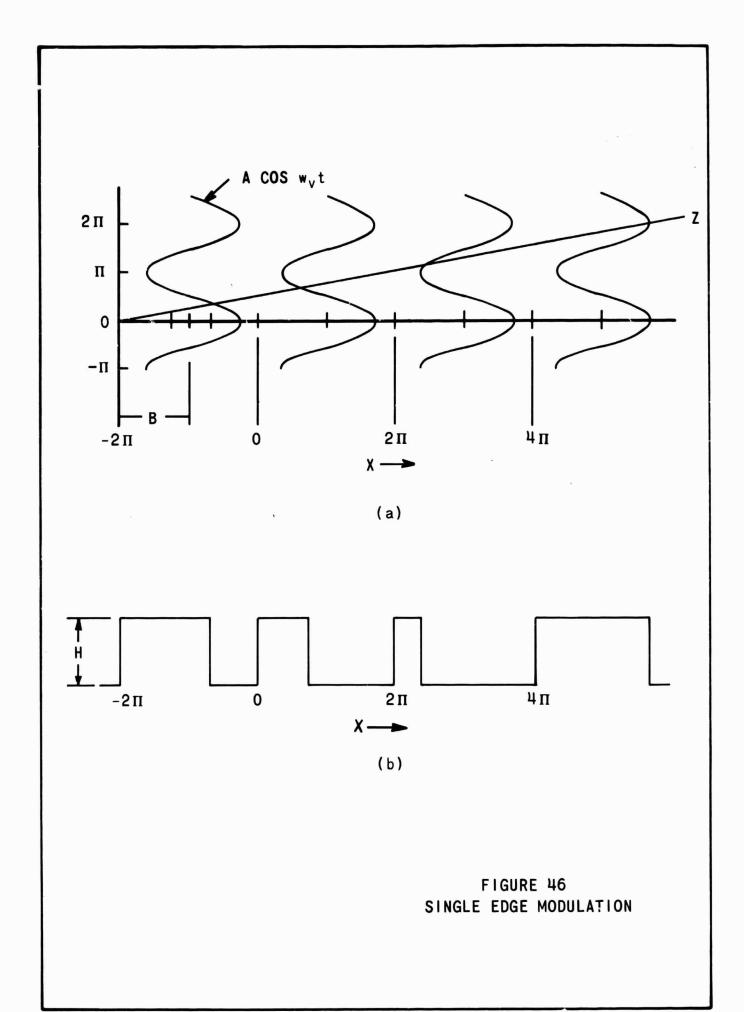

| 46     | Single Edge Modulation                                                       | 87   |

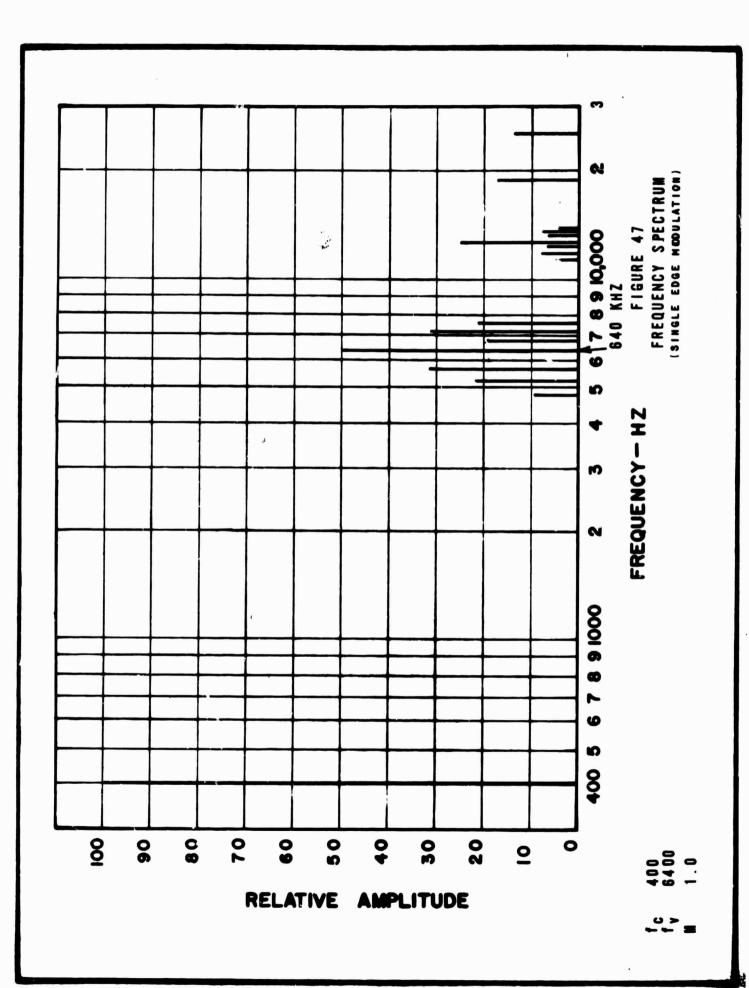

| 47     | Frequency Spectrum                                                           | 92   |

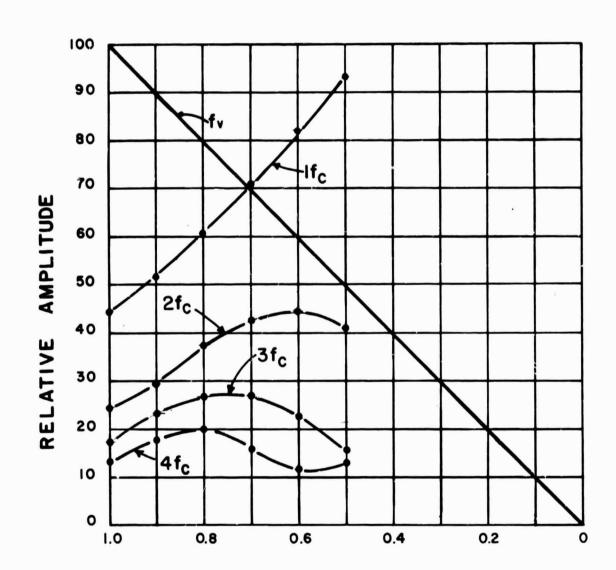

| 48     | Relative Amplitude VA Modulation Index                                       | 93   |

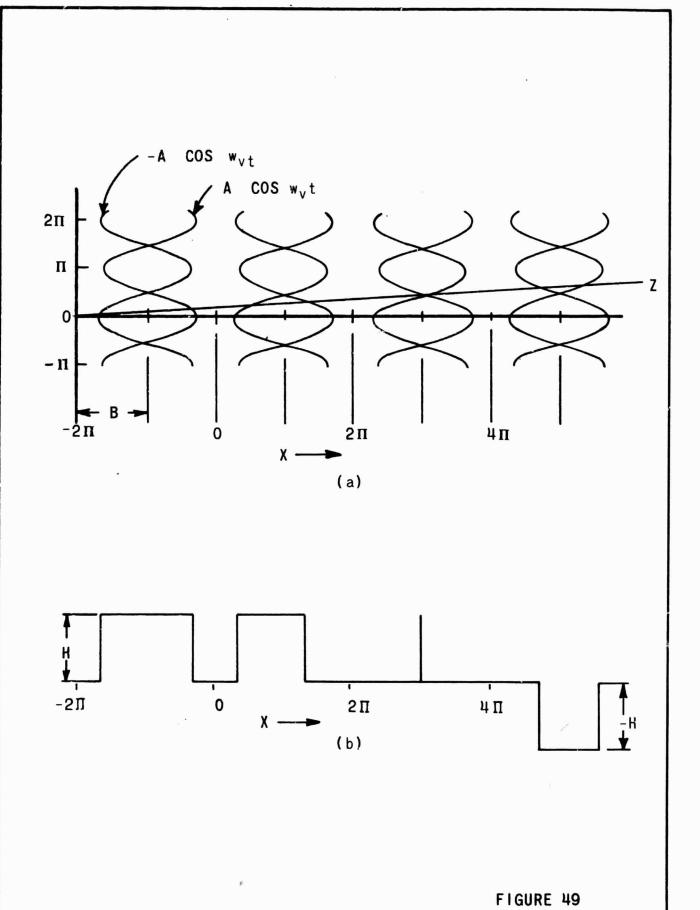

| 49     | Double Edge Modulation                                                       | 96   |

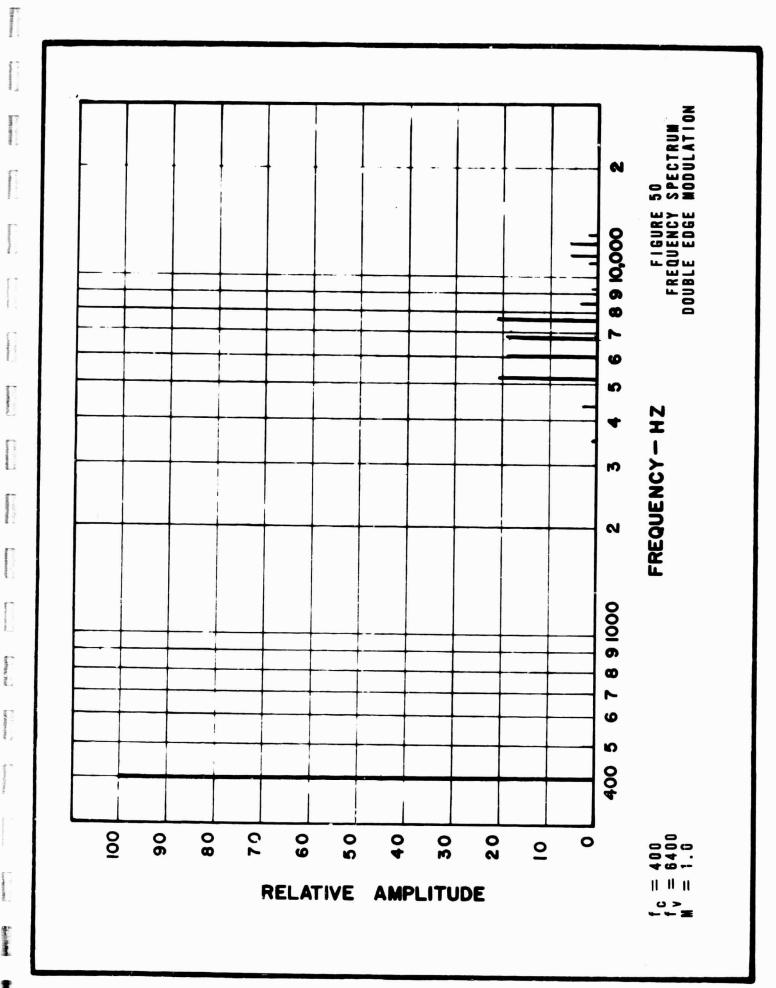

| 50     | Frequency Spectrum                                                           | 99   |

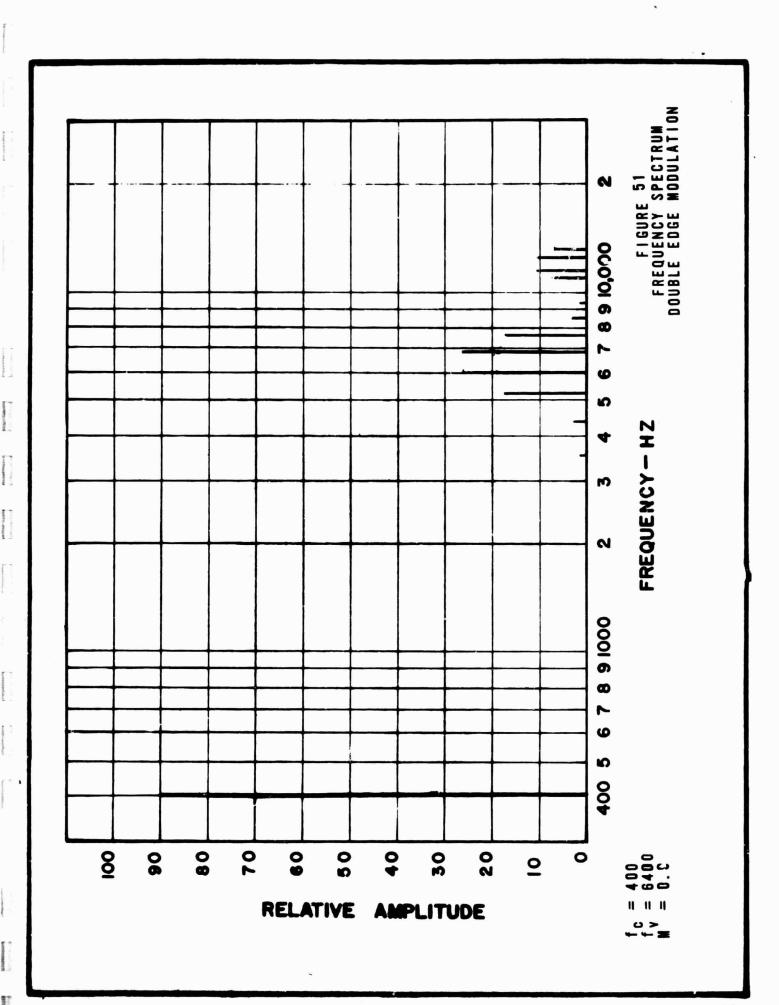

| 51     | Frequency Spectrum                                                           | 100  |

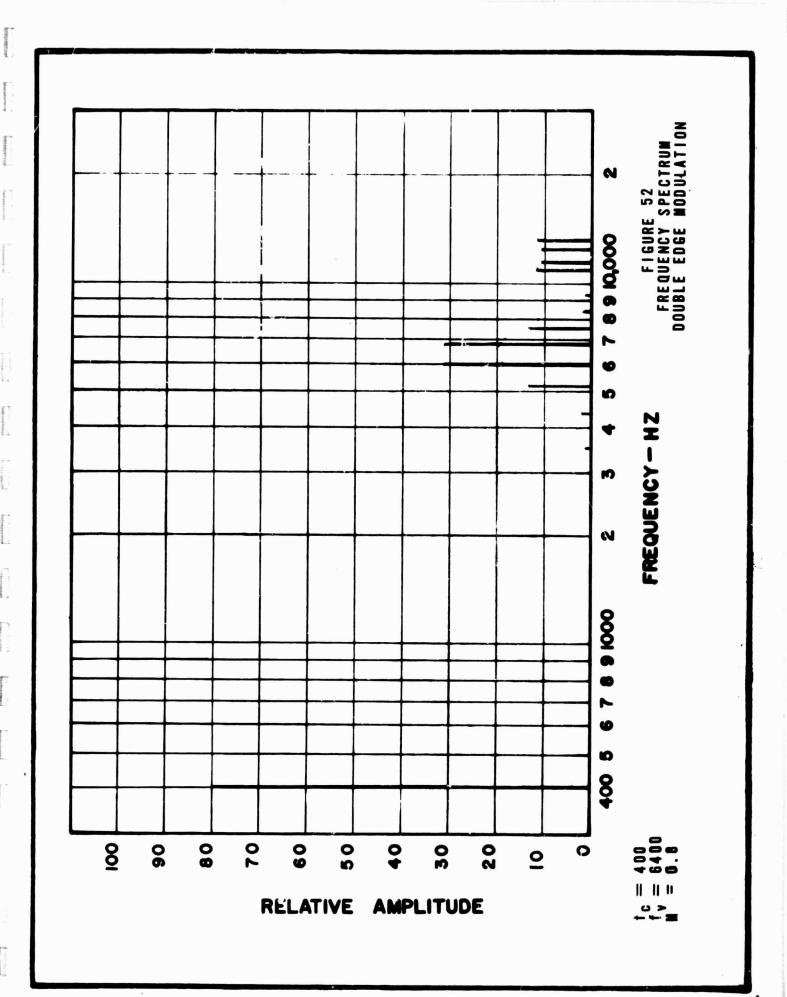

| 52     | Frequency Spectrum                                                           | 101  |

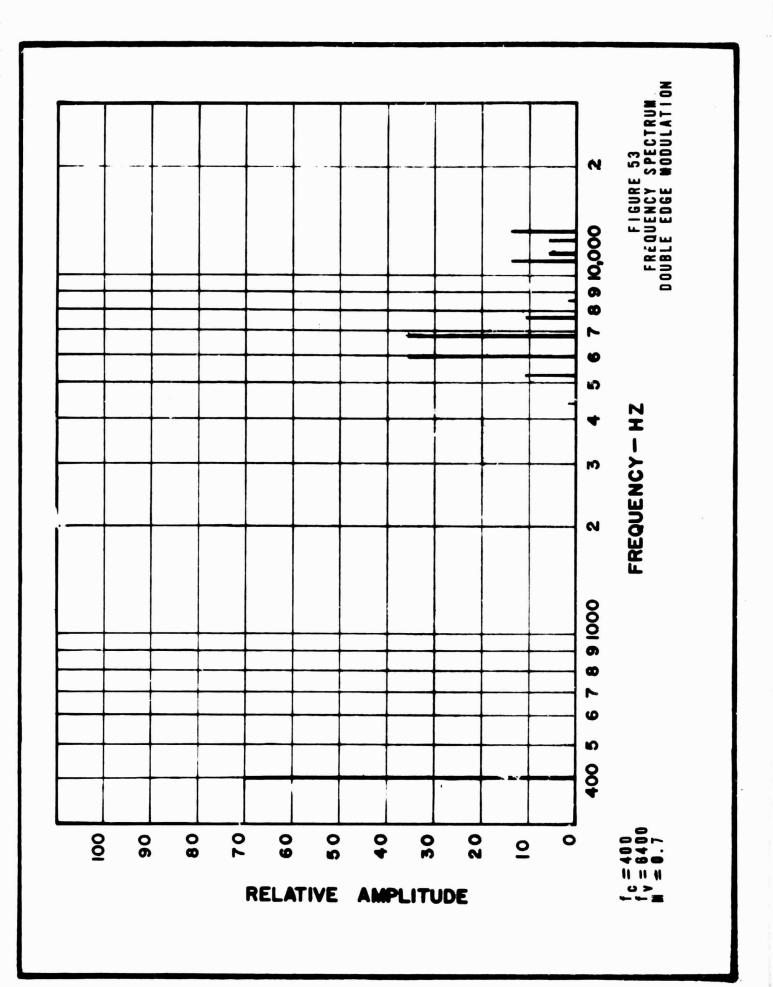

| 53     | Frequency Spectrum                                                           | 102  |

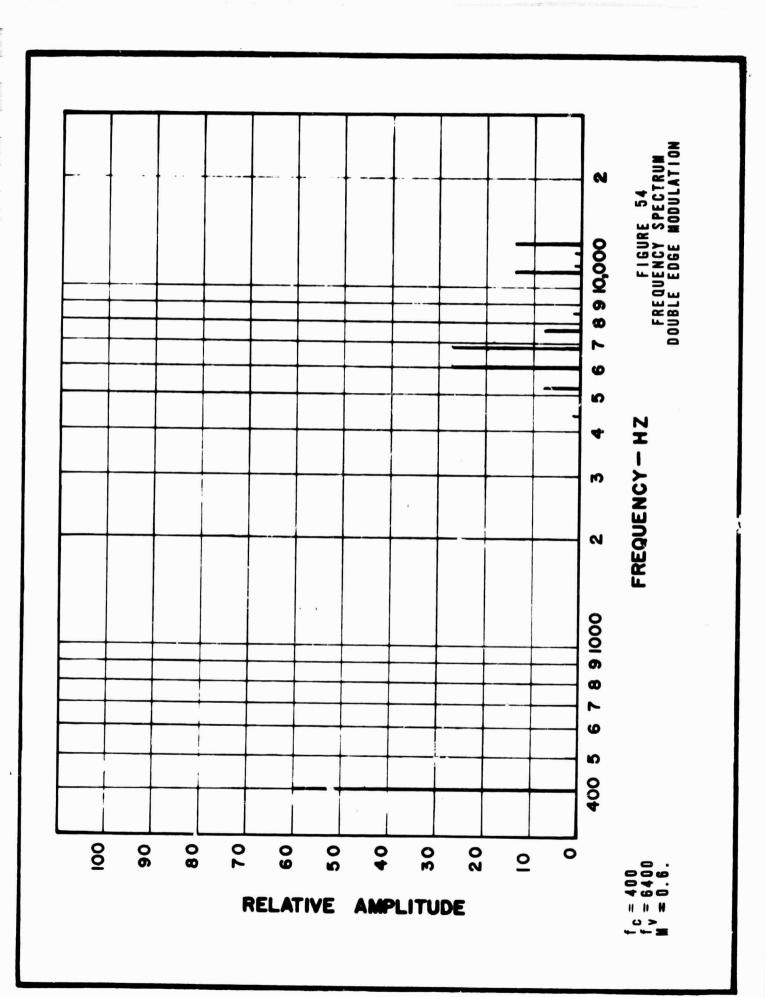

| 54     | Frequency Spectrum                                                           | 103  |

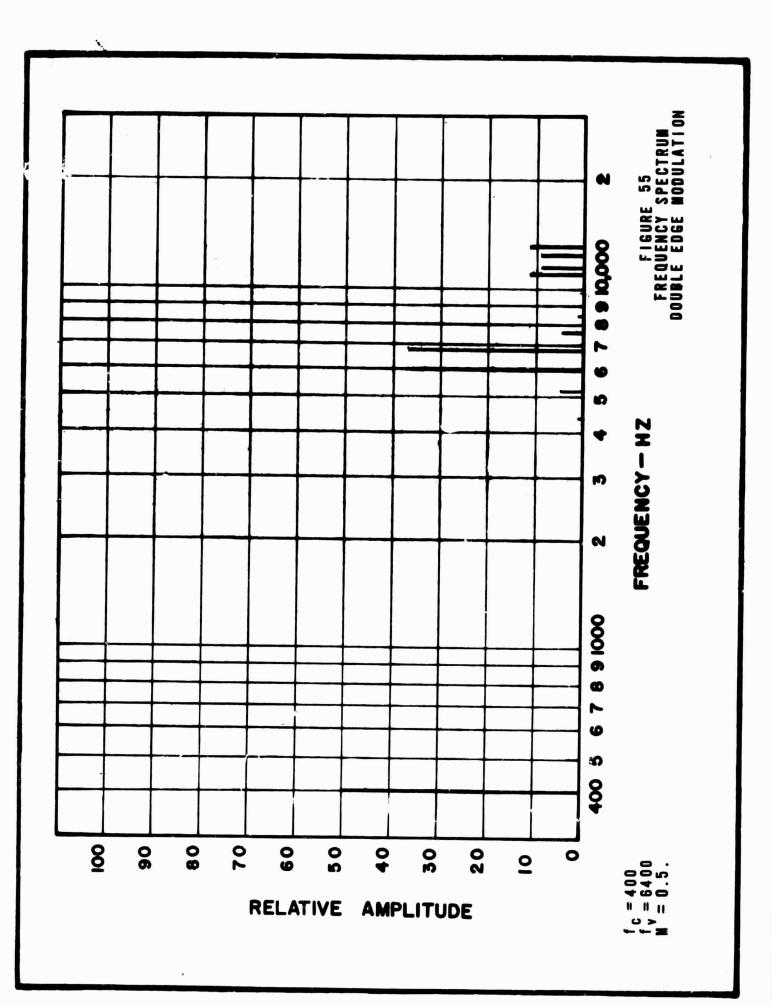

| 55     | Frequency Spectrum                                                           | 104  |

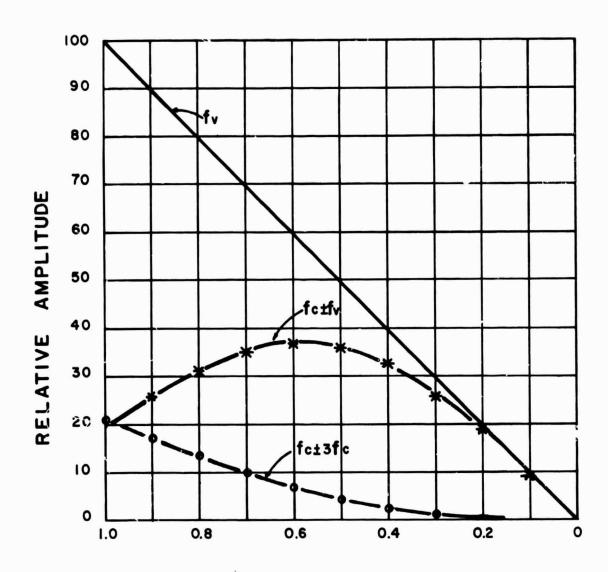

| 56     | Relative Amplitude                                                           | 105  |

| 57     | Frequency Spectrum                                                           | 106  |

| 58     | Losses vs Collector Current                                                  | 111  |

| 59     | Switching Times                                                              | 112  |

| 60     | Input Current Waveforms                                                      | 116  |

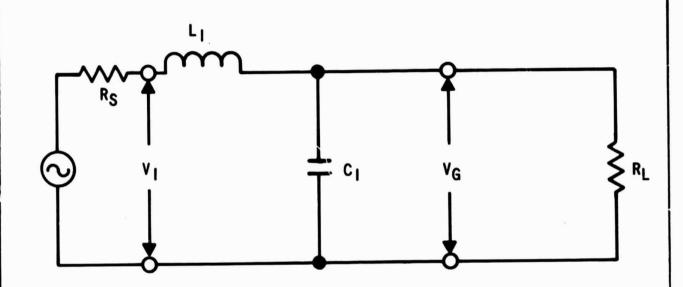

| 61     | Basic Input Filter                                                           | 117  |

| 62     | Cascade Input Filter                                                         | 119  |

| 63     | Simulated Input Filter                                                       | 120  |

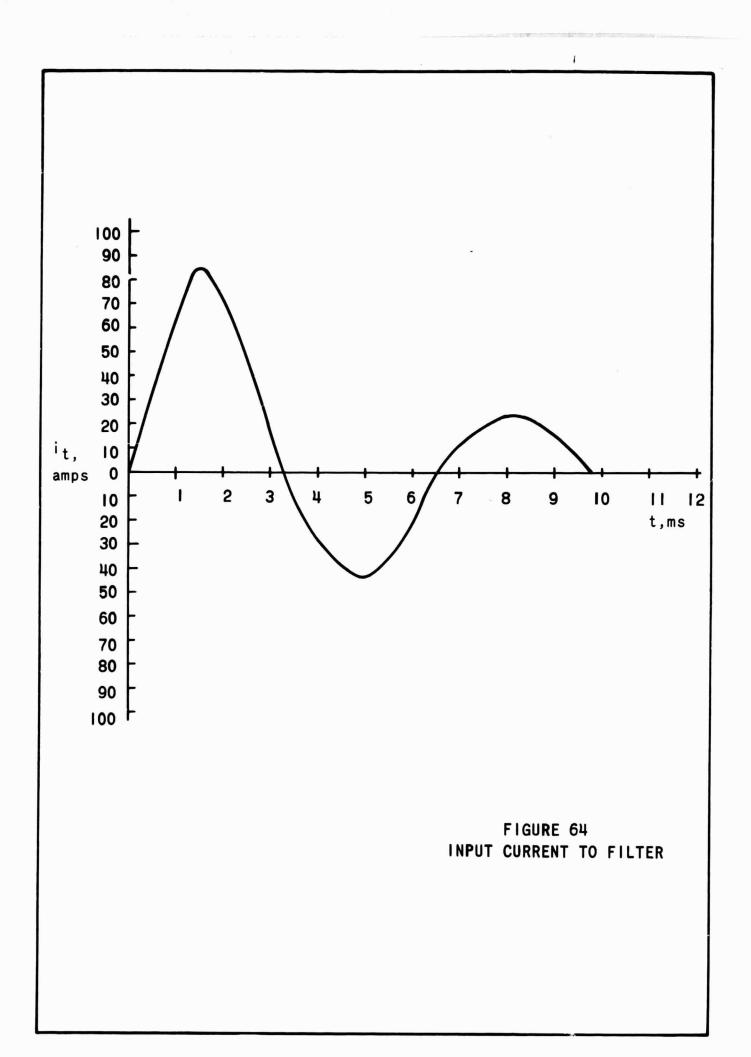

| 64     | Input Current to Filter                                                      | 121  |

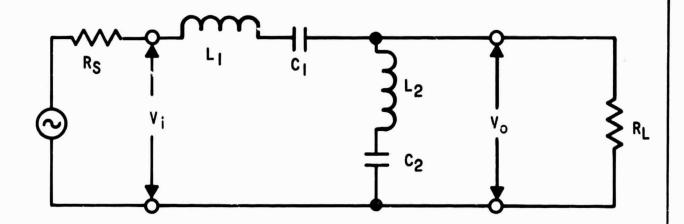

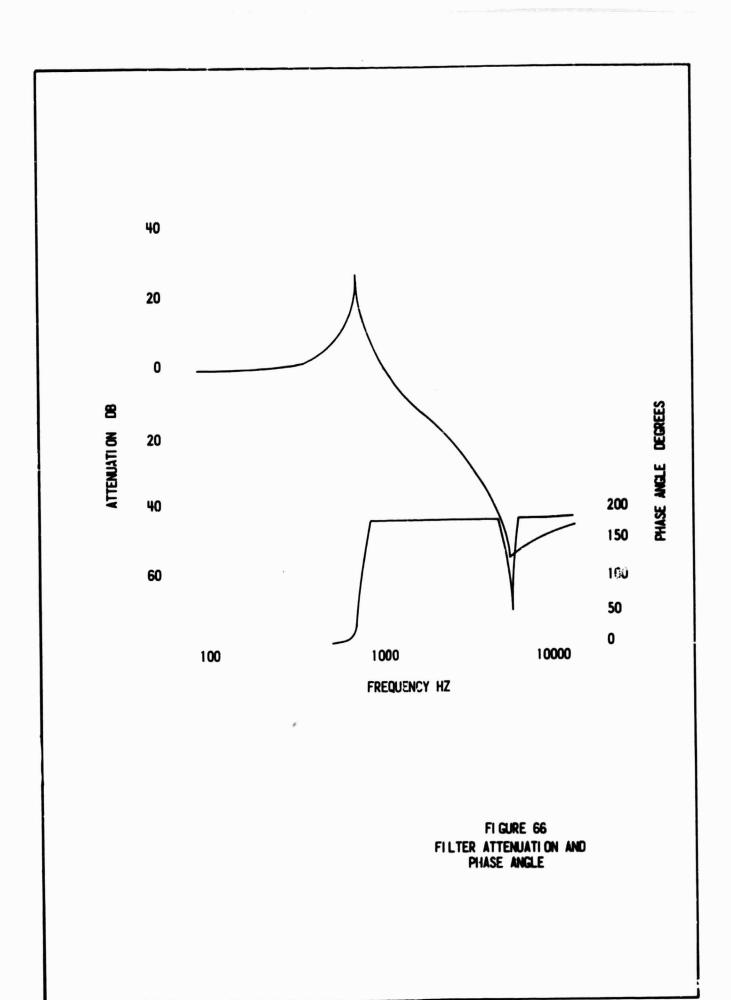

| 65     | Series-Ted Filter                                                            | 124  |

| 66     | Filter Attenuation and Phase Angle                                           | 126  |

| 67     | Single-Section Filger                                                        | 127  |

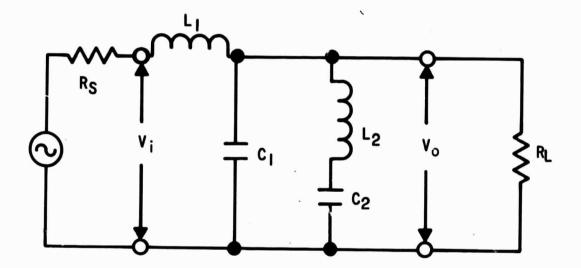

| 68     | Shunt Series Filter                                                          | 129  |

| Figure | Title                                   | Page |

|--------|-----------------------------------------|------|

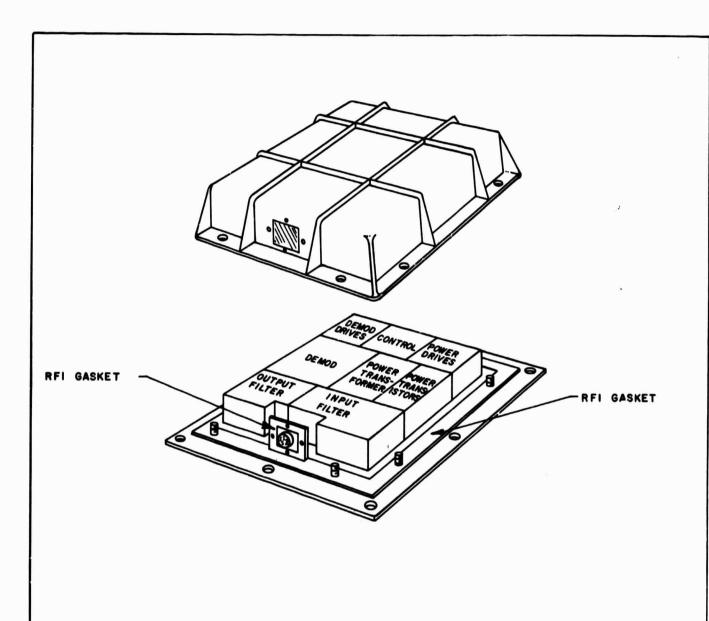

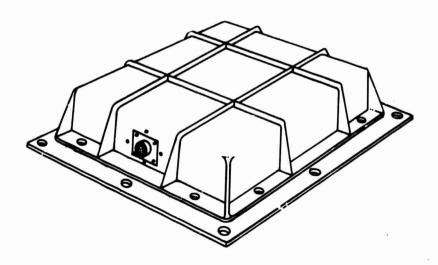

| 69     | 500-VA Inverter                         | 132  |

| 70     | Three-Phase, 3- KVA, 60-Hz Inverter     | B-2  |

| 71     | 250-VA, Single-Phase Multiple-Frequency | B-5  |

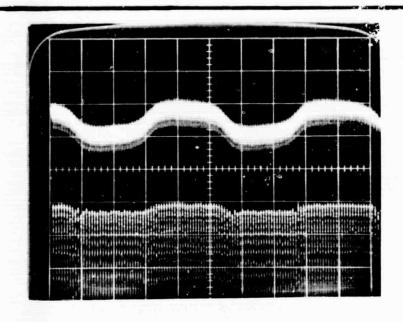

| 72     | Output Voltage                          | B-6  |

| 73     | Output Voltage                          | B-6  |

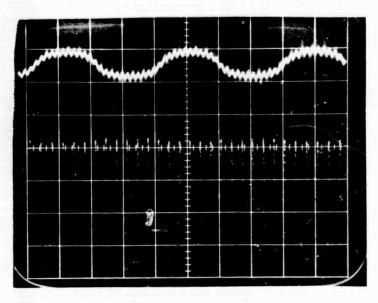

| 74     | Unfiltered Demodulated Voltage          | B-6  |

| 75     | Output Voltage and Output Current       | B-7  |

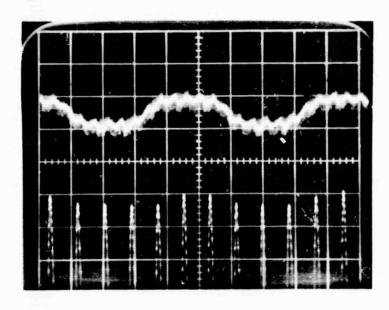

| 76     | Output Current                          | B-7  |

| 77     | Input/Output Voltage                    | B-8  |

| 78     | Input/Output Voltage                    | B-8  |

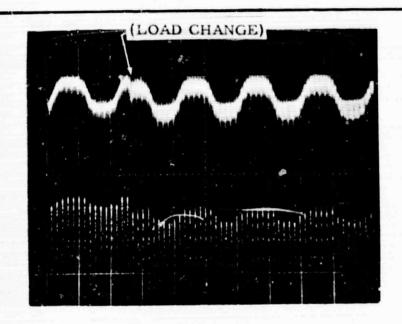

| 79     | Input/Output Voltage                    | B-8  |

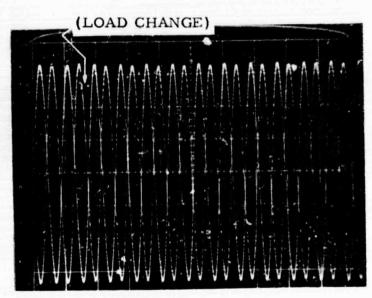

| 80     | No Lord to 150-VA Load                  | B-9  |

| 81     | 11 - Valt RMS, 0-150-VA Load Change     | B-9  |

| 82     | Output: Starting Current                | B-9  |

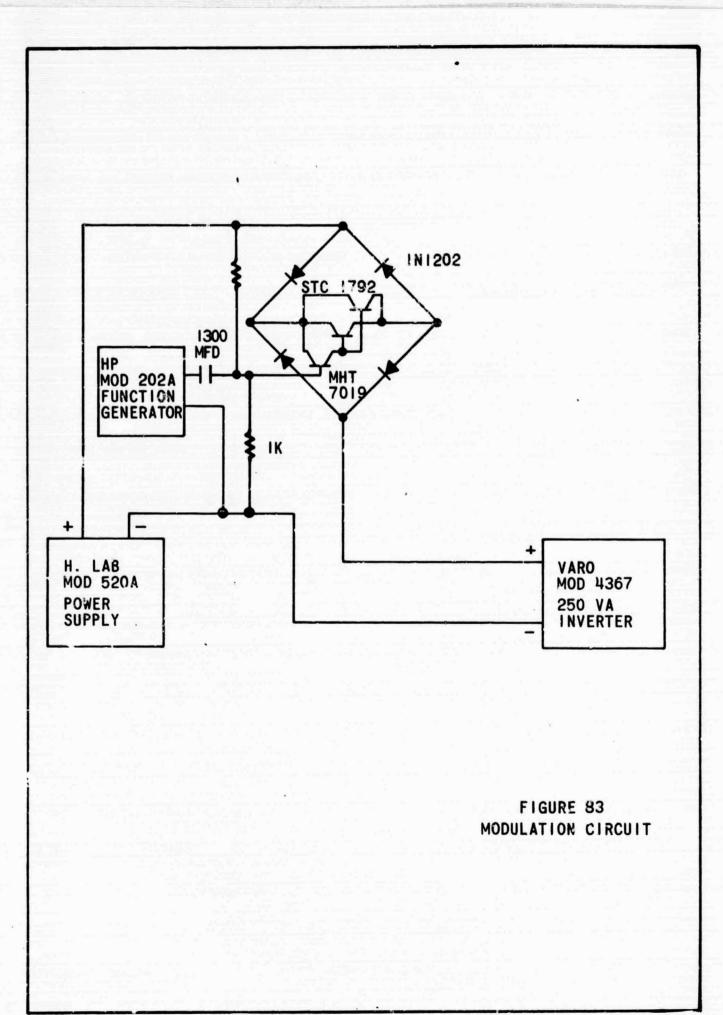

| 83     | Modulation Circuit                      | B-10 |

Constitution of the Consti

The state of

#### SUMMARY

This document is the final report covering work performed in the study of state-of-the-art static inverter designs under Contract NAS9-5580. This report covers the time from January 6, 1966, to June 6, 1966.

It presents the research of the state-of-the-art inverter designs and the selection of a design approach to fulfill the objective for the proposed inverter. As part of this report the recommended design is analyzed, the primary circuit is developed, and recommendations for design objectives and design requirements are made.

#### I. INTRODUCTION

In aircraft, satellite, or spacecraft applications the source of power is generally derived from some DC source such as a battery or fuel cell. This raw DC power must be conditioned by static inverters and/or static converters to a useable form before it reaches the utilizing equipment.

Since the utilizing equipment may consist of radar, altitude control, communication and other life support or operation equipment, the inverter or converter must be most reliable. Also these units must have an efficiency as high as possible, while keeping their weight as light as practical. These objectives (reliability, efficiency, weight) may be specified but, in general, the specified values are minimum quantities and it is desirable that they be exceeded whenever possible.

In the design of an inverter the approach chosen has a direct bearing on each of the above design objectives, as well as on the ability of the inverter to meet general specification requirements. In this phase of the program, research of the state of the art in inverter design has led to development of an advanced design for a multiple-purpose inverter.

The first section of this report is devoted to the state-of-the-art study. In this study, basic inverter design concepts are reviewed. The ability of each design concept to develop an inverter which can meet the design specifications is discussed. To aid in these discussions, a simplified circuit diagram and waveshapes are illustrated for each design.

The selected design is explained in detail. Operation of the individual circuits is explained. The relationship between design requirements and circuit functions is also covered. The circuit is analyzed and basic circuit components are selected. The waveforms of this design and similar designs are compared and analyzed for optimum circuit design and component selection. The requirement of "switching-speed-of-transistors vs. frequency-of-operation-for -transformer-and-filter-design" is discussed. Preliminary quantative reliability analysis is made to weigh redundancy considerations. Other reliability considerations are also discussed.

The preliminary circuit diagram and a proposed bill of material is developed. To establish system performance and physical characteristics, a detailed loss, or efficiency-and-weight, study is made. The possible design configuration is outlined for evaluation.

Design specifications are reviewed and recommendations made for the final design. These recommendations are made on a basis of possible trade-offs between various performance parameters and design goals.

#### II. STATE-OF-THE-ART STUDY

#### A. INTRODUCTION

The main purpose of the study phase of this program has been to search the state of the art in inverter design for a design that can produce an inverter to meet the design requirements of the proposed multiple-purpose inverter. Many excellent designs have been used often to produce a number of well-engineered inverters. Since most of these basic designs have been analyzed at different times in detail, only a brief description of the circuit of each and its major disadvantage is given. This report cannot be considered complete in that rapidly advancing state of the art in design and components brings about new concepts continually. It is the intent of this report to include those designs considered feasible at this time.

The basic function of an inverter is to transform input DC power to usable AC power of the correct voltage and frequency. This transformation requires two basic functions in the inverter: (1) a switching device to convert the DC voltage to an AC voltage; and (2) a scaling device, such as a transformer, to convert the AC voltage to the proper level.

Most solid-state inverters are designed around two basic types of switching devices; i.e., a power transistor and a silicon-controlled rectifier (SCR). The SCR, in general, has a much higher voltage range than the transistor; however, the SCR suffers from two basic problems -- turnOFF control and switching speed. In most inverter designs the SCRs must be forced to turn OFF, thus they require more circuits than transistor designs. The transistor, in turn, has lower current-carrying ability and requires more drive power than the SCR. For the expected power level and operating conditions, the transistor is considered the best device for this application. Thus, the various circuits are explained on the basis of using power transistors for the major switching devices. Most of these circuits would work equally well, however, using SCRs and with only slight circuit modifications.

The transformer (which scales the voltage) and the filter (which shapes the voltage) together form the major weight-determining elements in an inverter.

The transformer is not only used to scale the output voltage, but is also utilized to isolate various DC and AC circuits -- a prime requirement of many systems.

Inductors and capacitors utilized in the output filter for waveshaping are also used in various input filter configurations to form AC impedance barriers between the DC power source and the inverter. Since these items make up a large part of the inverter weight, it is of paramount importance that their use be kept to a minimum. Filtering can be reduced through linear operation of the transistor; however, losses are prohibitive in most power inverter applications. Investigation of the various inverter designs attempted to evaluate such problems in conjunction with the overall design requirements.

#### B. DISCUSSION OF INVERTER TYPES

This discussion of inverter designs covers not only the more complex state-of-the-art designs but also the simpler basic designs. The simpler designs are used as an introduction to the more complex designs. Discussion of the simpler circuit is held to a minimum since these circuits have been studied in previous reports and are well known to the industry. Circuits discussed:

- 1. PARALLEL INVERTER

- 2. CHOPPER REGULATED PARALLEL INVERTER

- 3. PULSE-WIDTH REGULATED PARALLEL INVERTER

- 4. SERIES CONNECTED PARALLEL INVERTER

- 5. BRIDGE INVERTER

- 6. STEP-WAVE INVERTER

- 7. HIGH-FREQUENCY STEP-WAVE INVERTER

- 8. HIGH-FREQUENCY DC-DC CONVERTER-INVERTER

- 9. PULSE-WIDTH MODULATED INVERTER

- PHASE-DEMODULATED INVERTER

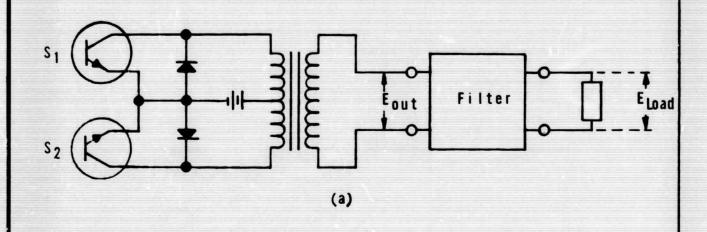

# 1. Parallel Inverter (Figure 1)

The first design to be considered and one of the most basic designs is the parallel inverter. The schematic for this circuit is illustrated in Figure 1a. The main switching elements are power transistors S1 and S2. These transistors are operated as switches; i.e., they are either OFF or ON, and are operated in a

FIGURE 1 PARALLEL INVERTER push-pull mode. This process produces a squarewave voltage (E<sub>out</sub>) as illustrated in Figure 1b. This squarewave voltage is filtered to produce a low-distorted sine wave, also illustrated in Figure 1b. The filter requirements are determined by the maximum harmonic of this waveform - approximately 48 percent.

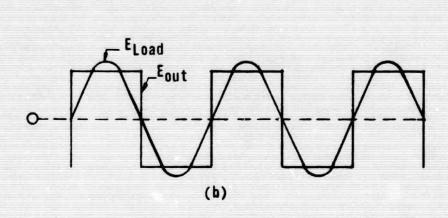

# 2. Chopper Regulated Parallel Inverter (Figure 2)

To be of use, the output voltage must be regulated by some means because a change in input DC voltage or load causes a change in the output AC voltage. One method of achieving this is to regulate the input DC voltage before it goes to the inverter. This regulation can be accomplished by using a series regulator or a chopper regulator. Due to the excessive power dissipation of a series regulator, only the chopper regulator is discussed.

A simple chopper regulator circuit is illustrated in Figure 2a. The chopper regulator consists of OFF-ON switch-transistor Sl and an L-C filter. Sl is turned OFF and ON as a function of the output DC level. The voltage out of Sl is illustrated in Figure 2e. As the input voltage, Figure 2b, changes levels, the OFF-ON time ratio of Sl changes. Choke L, in the filter, is designed for a minimum load current and a maximum OFF time of transistor Sl. To provide a current path for load current when the transistor is OFF, fly-back diode Dl is provided. Typical currents for the transistor and the diode are illustrated in Figures 2c and 2d.

Output regulation of the inverter is a direct function of the DC voltage out of the chopper regulator. If the inverter output must be well regulated, output of the chopper is made a function of the AC output by connecting the AC output to the regulator. Any change in the AC output is reflected as a DC error signal to the regulator which causes a change in the DC output of the chopper.

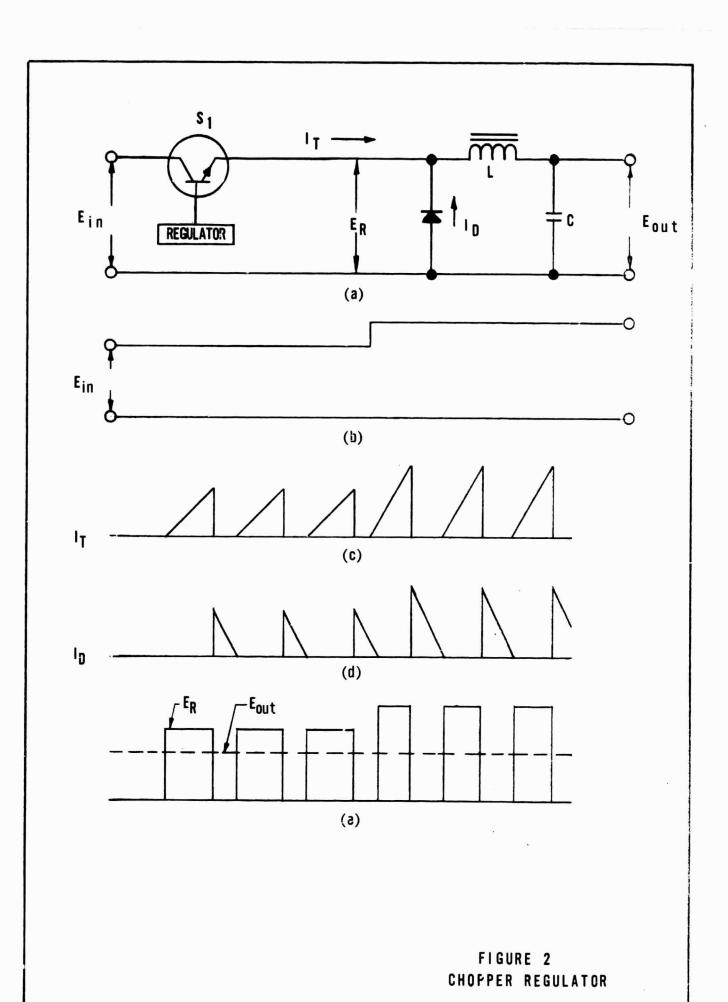

# 3. Pulse-Width Regulated Parallel Inverter (Figure 3)

A second method of regulation for a parallel inverter is termed pulse-width control. This type of control produces a quasi-squarewave. Output sine wave voltage E is a direct function of the width of the quasi-squarewave and can be expressed mathematically by the Fourier Series:

E (wt) =  $\frac{4V}{27}$  (SIN wt COS 0 - 1/3 SIN 3wt COS 0 + 1/5 SIN 5wt COS 5 0 - 1/7 SIN 7wt COS 7 0 + 1/9 SIN 9wt COS 9 0 ------)

FIGURE 3 QUASI-SQUARE WAVE VOLTAGE WAVEFORM

$$E(\omega_{t}) = \frac{4 \text{ V}}{\pi} (\sin \omega_{t} \cos \theta - \frac{1}{3} \sin 3 \omega_{t} \cos 3 \theta + \frac{1}{5} \sin 5 \omega_{t} \cos 5 \theta - \frac{1}{7} \sin 7 \omega_{t} \cos 7 \theta + \frac{1}{9} \sin 9 \omega_{t} \cos 9 \theta - - - ).$$

Inspection of this equation shows that the function  $\theta$  controls the amplitude of the harmonic voltages as well as the fundamental voltage. A plot of this equation is shown in Figure 4. As seen in the plot, as  $\theta$  varies then the amount of total harmonic content varies. This variation places additional requirements on the harmonic filter because it has to be designed to handle higher voltages and to block out more of the harmonic as compared with the fundamental.

Much of the information presented on the parallel inverter is well known to the inverter field; however, it is the basic design for almost all inverters and a general discussion of its operation is prerequisite to the later design discussions. This discussion of the parallel inverter should not be considered complete, however, in any way since many of the basic design problems, such as reactive currents, are not covered at ail.

The basic disadvantage of the parallel inverter is the weight of the transformer and filter. For this reason this basic approach in itself is not given further consideration.

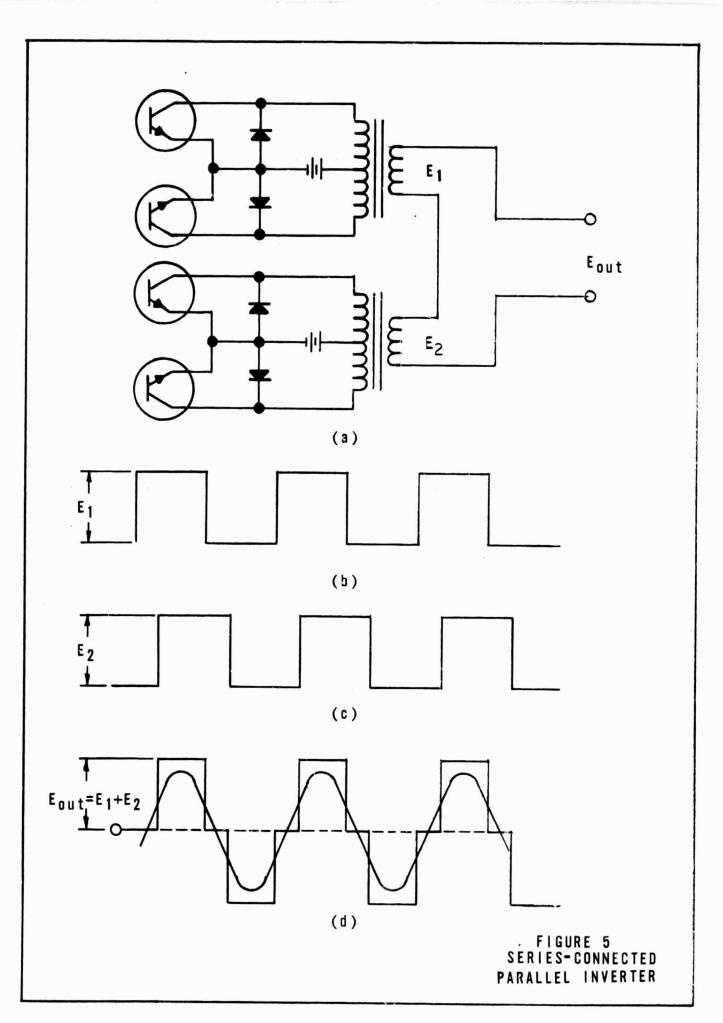

## 4. Series Connected Parallel Inverter (Figure 5)

A second basic design to be considered is the series connected parallel inverter. The basic schematic for this design is illustrated in Figure 5a. Inspection of this schematic shows it to be two parallel inverters connected in series, just as the name implies. Output voltage E1 of the first inverter is considered to be the reference for the second inverter. By phase shifting output voltage E2 of the second inverter and adding it to the first inverter, a quasi-squarewave voltage is developed. The advantage of this design is that it offers a low impedance current path for current flow when there is no voltage. In the

FIGURE 4

HARMONIC DISTRIBUTION

quasi-squarewave parallel inverter this presents a problem and causes additional problems for the filter. Although the low impedance of this circuit reduces the filter size, it makes poor utilization of the power transformer and power transistors. The increased size and weight of the power transformer more than makes up for the reduced filter weight, thus ruling out use of this design.

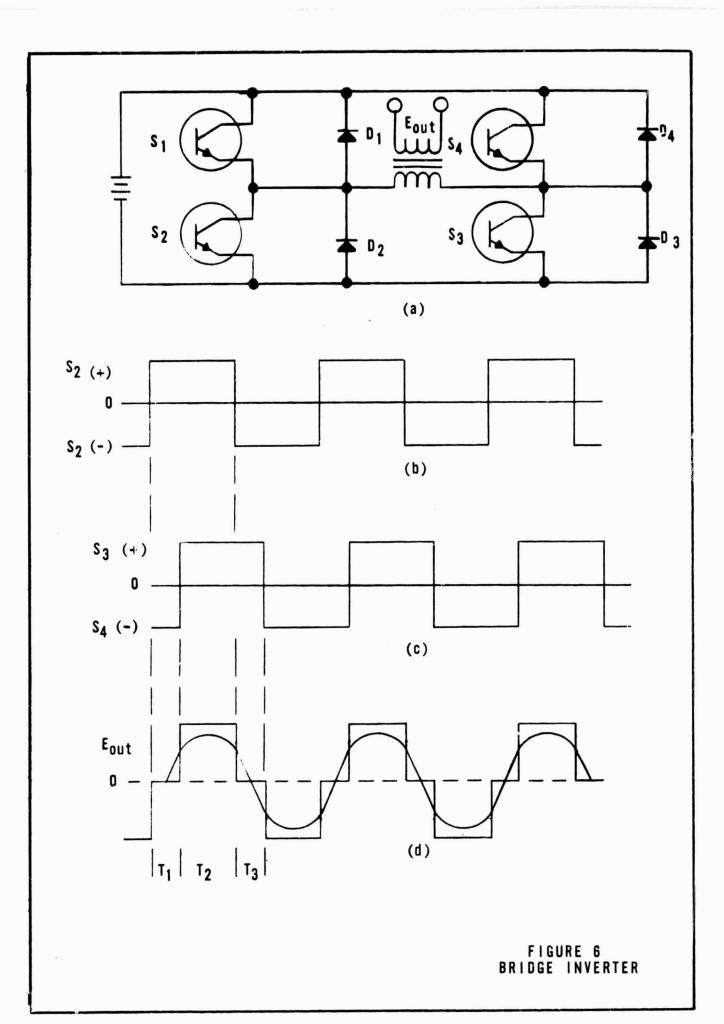

## Bridge Inverter (Figure 6)

A design which overcomes the disadvantage of transformer size and still has a low impedance source is the bridge inverter. (Design schematic, Figure 6a.) The voltage waveforms of Figure 6b and 6c illustrate the output of two drive transformers used to drive power transistors S1 through S4. When the voltage of Figure 6b is positive, transistor S1 is ON and S2 is OFF; when it is negative, S2 is ON and S1 is OFF. When the voltage illustrated in Figure 6c is positive, S3 is ON and S4 is OFF; when it is negative, S4 is ON and S3 is OFF.

The output waveform, Figure 6d, may now be developed through the use of the switching action of the transistors shown in Figure 6b and 6c.

During the first time period, T<sub>1</sub>, transistors S1 and S4 are ON while transistors S2 and S3 are OFF, which, in effect, shorts out the input to the transformer, providing a current through transistor S1 and diode D4 or transistor S4 and diode D1. At time period T<sub>2</sub>, transistor S3 turns ON while transistor S4 turns OFF, connecting the transformer to the battery through transistors S1 and S3, and producing the output voltage as illustrated. During time period T<sub>3</sub>, transistors S2 and S3 are ON while S1 and S4 are OFF, again shorting out the primary of the transformer. During time period T<sub>4</sub>, transistor S2 and S4 are ON, placing the battery across the transformer but with an opposite polarity from that experienced during time period T<sub>2</sub>.

This approach is much better than the previous designs; however, it does not provide any major weight advantage since the transformer must carry fundamental voltage. The major disadvantage is that each time a set of power transistors switch conduction states, a short circuit is placed across the input power source. A second disadvantage is the requirement of two transistors in series, thus increasing overall losses. This design is very good, but will not fulfill requirements of the proposed inverter.

13

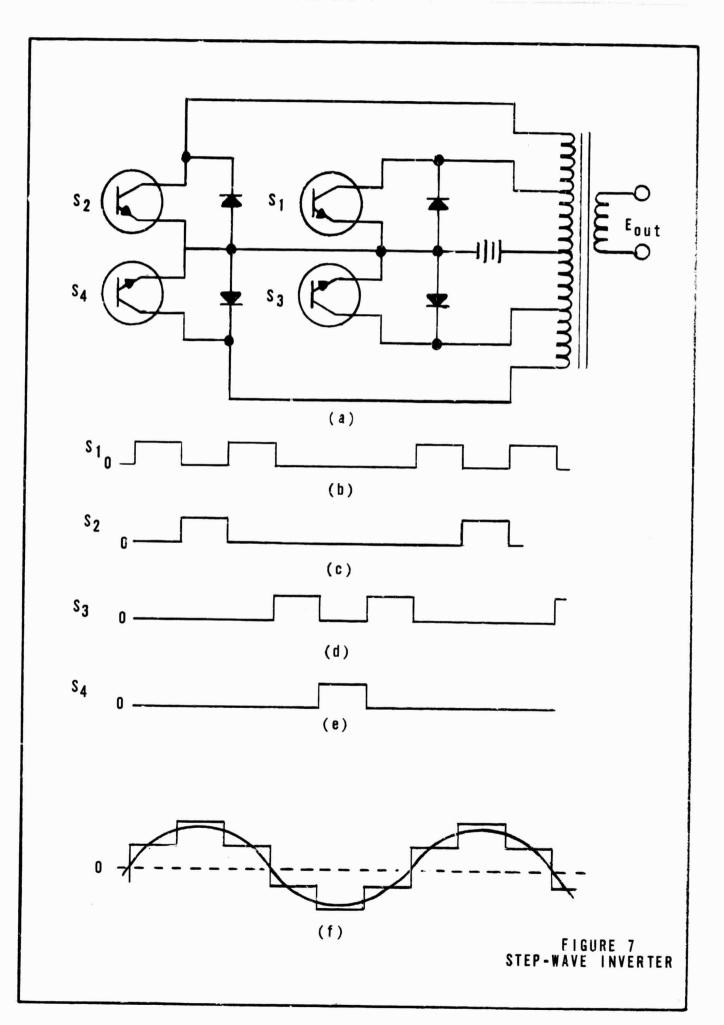

## 6. Step-Wave Inverter (Figure 7)

The step-wave inverter is the first design to offer a major advantage over the previous designs. For the purpose of discussion the simplest type of step-wave inverter is used. A schematic of this design is illustrated in Figure 7a. In this circuit the power transformer primary is tapped to provide intermediate levels of output voltage. Illustrated in Figure 7f is the output voltage before and after filtering, termed a six-step equal-time equal-height step-wave output with a total fundamental value of 1.35 E, and a total harmonic content of 31 percent of the fundamental. This simple design used for discussion does not provide minimum distortion vs. number of steps, however.

The output of the parallel inverter illustrated in Figure 1b is considered a two-step equal-time output. The value of the fundamental for this wave is 0.9 E and total harmonic content is 48 percent. Thus, by varying the number of steps, the value of the harmonic can be varied. If the height of the steps is varied, distortion is also varied. The height of the steps is not difficult to change since it requires only a change in the transformer turns ratio. The more steps taken, however, the more complex the control circuit becomes. Thus, as the number of steps is increased to reduce the filter requirement, the control circuit becomes more complex. In the large power unit where the control circuit weight and size is small, compared with the power stage, more steps can be taken with a greater advantage than in smaller VA units.

Table I lists a few of the basic step-wave designs with the approximate total harmonic content as a percent of the fundamental voltage. Inspection of this table shows that as the number of steps are increased, the total distortion decreases. The biggest drop in distortion is between the two-step and the six-step waveform. It is also noted that there is an optimum harmonic content depending upon the step width and step height chosen.

This type design has the advantage of a lightweight filter, but the power transformer must still carry the fundamental output voltage. A second disadvantage is no direct means of control of the output voltage. The output is generally controlled by a chopper regulator on the input as previously discussed.

TABLE I STEP-WAVE OUTPUT STEPS VS DISTORTION

| TWO STEP-EQUAL TIME  FOUR STEP-UNEQUAL TIME  FOUR STEP-UNEQUAL TIME -1  FOUR STEP-UNEQUAL TIME -11  SIX STEP-EQUAL TIME-EQUAL HEIGHT  SIX STEP-UNEQUAL TIME-UNEQUAL HEIGHT  EIGHT STEP-EQUAL TIME-UNEQUAL HEIGHT  EIGHT STEP-UNEQUAL TIME-EQUAL HEIGHT  TEN STEP-UNEQUAL TIME-UNEQUAL HEIGHT  TWELVE STEP-EQUAL TIME-UNEQUAL HEIGHT  TWELVE STEP-UNEQUAL TIME-UNEQUAL HEIGHT  SIXTEEN STEP-UNEQUAL TIME-UNEQUAL HEIGHT  EIGHTEEN STEP-EQUAL TIME-UNEQUAL HEIGHT | 48.<br>48.<br>31.<br>29.<br>31.<br>23.<br>23.<br>17.<br>18.<br>15.<br>15.<br>10. |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

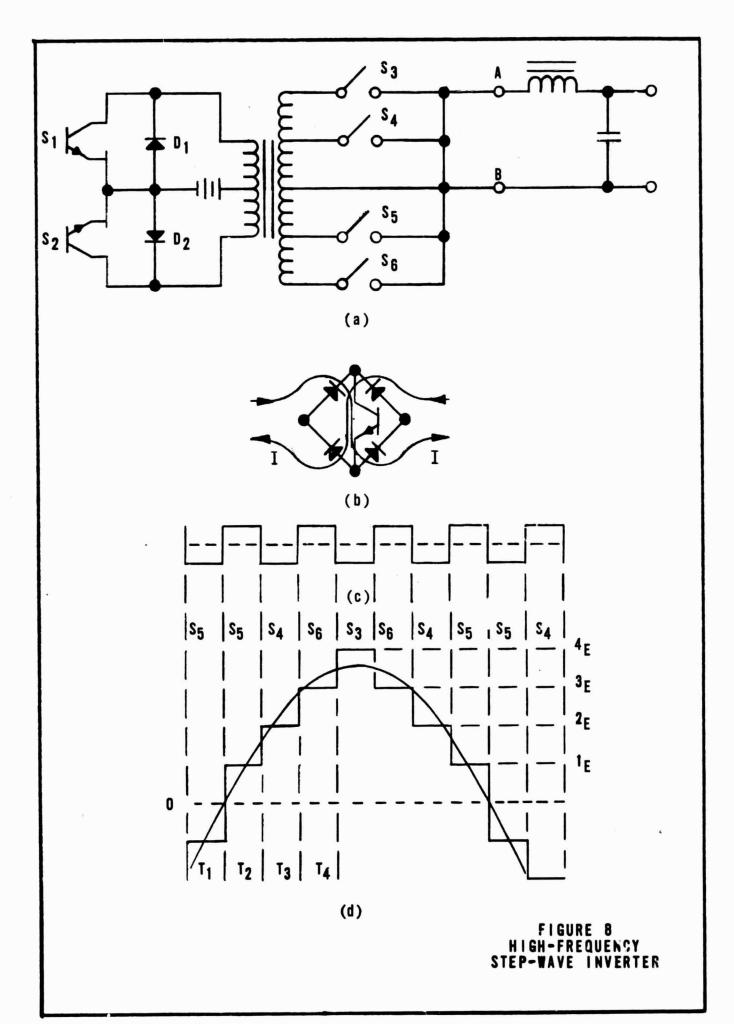

# 7. High-Frequency Step-Wave Inverter (Figure 8)

The high-frequency step-wave inverter is a further improvement of the basic concept of the step-wave inverter.

The high-frequency step-wave inverter reduces not only filter requirements by waveshaping, but reduces transformer size through the use of a high-frequency power stage. A simplified schematic is presented in Figure 8a.

Comparison of Figure 8a with 7a shows that the basic stepping switches have been moved from the primary of the power transformer to the secondary. The power stage consists of a standard parallel inverter operating at some predetermined high-frequency switching rate. Its frequency is determined by the number of steps and is some multiple of the output frequency. The voltage out of this type inverter is a squarewave (Figure 8c) and for the purpose of discussion is 2800 cycles.

The output is stepped or steered by bilateral switches S3 through S6. A typical circuit diagram for a bilateral switch is shown in Figure 8b. The bilateral switch consists of four diodes and a power transistor, and allows current to flow in either direction whenever the transistor is turned ON.

The output of this inverter (Figure 8d) is easily developed by following the switching actions and time periods as illustrated.

Figure 8c represents the basic polarity out of the power transformer and is used as a reference. At time period T<sub>1</sub>, bilateral switch S5 is ON and a negative voltage is impressed at point A of the filter. At time period T<sub>2</sub>, bilateral switch S5 is still ON, but the output of the power transformer has reversed polarity. A positive voltage is now imposed at point A of the filter. At time period T<sub>3</sub>, the output of the transformer again reverses polarity; however, switch S5 was turned OFF and switch S4 turned ON, applying a positive voltage of 2E to point A of the filter. At time period T<sub>4</sub>, the polarity reverses, switch S4 is turned OFF, switch S6 is turned ON, and a positive voltage of 3E is applied to point A. By continuing this process, the 14-step step-wave illustrated in Figure 8d is generated.

This method not only has the advantage of low filter requirement for the output filter, but also the power transformer which does not carry the fundamental output voltage can be designed for the carrier frequency. This arrangement allows the transformer to be small, thus bringing about a further reduction in weight over the standard step-wave inverter.

Again, the disadvantage of this system is that it provides no direct method of output voltage regulation. This regulation may be accomplished, however, by use of the input chopper regulator discussed previously. A second disadvantage is the logic circuit required for correct operation of the bilateral switches. Even with these disadvantages, this design is considered to be one of the better designs for a low-weight inverter. It has one major advantage over many other high-frequency type inverters -- a low output impedance; that is, it allows current flow from the load back into the primary.

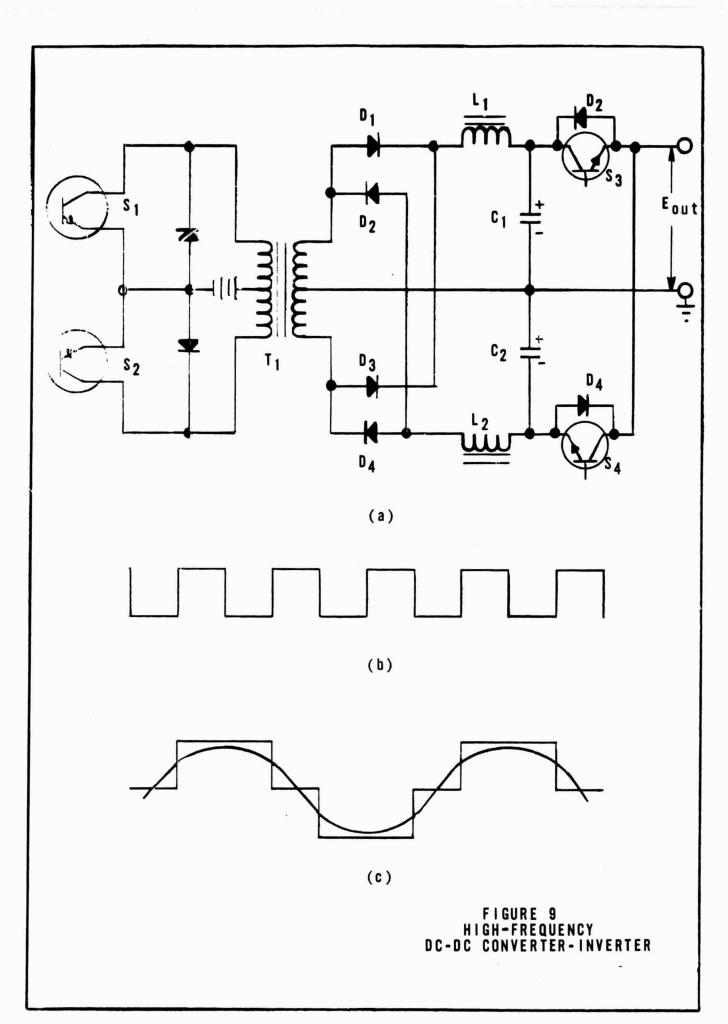

# 8. High-Frequency DC-DC Converter-Inverter (Figure 9)

The high-frequency DC-DC converter-inverter is basically a DC-DC converter with an inverter attached to its output. The converter output is double ended; that is, it has a positive and a negative output with a common ground. The converter is followed by an inverter stage which converts the high-voltage DC to the proper AC voltage and frequency. The circuit for this design is shown in Figure 9a. If the inverter is of the self-regulating quasi-squarewave type, then the converter output can be unregulated. If the inverter has a square-wave output or if it has a fixed output phase angle  $(\theta)$ , then the converter output must be regulated. Figure 9b shows the high-frequency voltage waveform of the converter power stage. Figure 9c shows the inverter output with a fixed phase angle, before and after filtering.

This approach offers a design advantage in that the converter can be operated at an optimum high-frequency, thus, reducing the power transformer weight. The converter frequency can be selected independent of the output frequency. The self-regulating type inverter is less complex than the fixed output type inverter because the converter does not require a preregulator; however, the fixed output inverter may be designed with a phase angle fixed for

minimum distortion. The reduced inverter output filter requirements may overcome the additional weight of the DC regulator for the converter input.

The major disadvantage of this system is the DC filter requirements for the converter output. If the inverter operates into a reactive load, the DC filter capacitor must be large enough to store the reactive current to prevent the DC voltage from being modulated - the major problem area of this design.

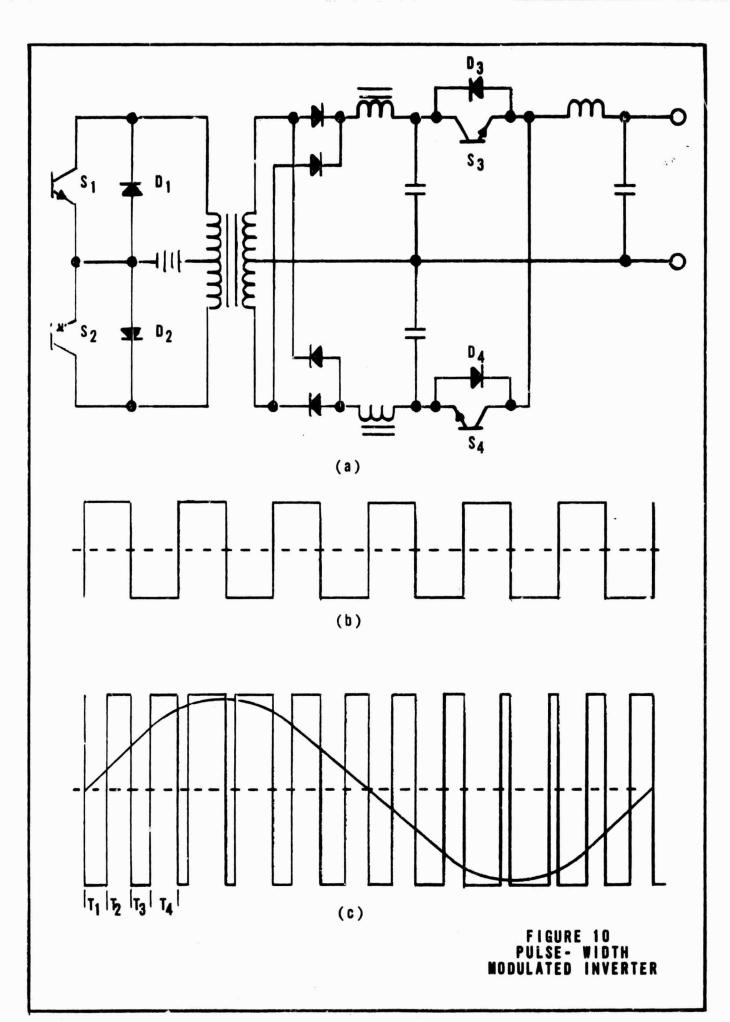

### 9. Pulse-Width Modulated Inverter (Figure 10)

The pulse-width modulated inverter is one of the more advanced state-of-the-art designs for inverters. This design combines the advantage of a high-frequency transformer with that of a low-pass AC output filter. The schematic for the pulse-width modulated inverter (Figure 10a) is very similar to that of the high-frequency DC-DC converter-inverter (Figure 9a). The basic difference is in how the inverter transistors (S3 and S4) are controlled.

In the pulse-width modulated inverter, the inverter transistors are switched at a high frequency to produce a modulated output at the required inverter output frequency. This modulated voltage is illustrated in Figure 10c along with the output sine wave.

By using the time periods of Figure 10c and the schematic of Figure 10a, basic operation of this circuit can best be explained. The positive bus, or B+ bus, is connected to the output filter through transistor switch S3 while transistor switch S4 connects the negative bus to the output filter. When switch S3 is ON, the filter has a positive voltage applied to its input terminals. When S4 is ON, it has a negative voltage applied to its input. Transistors S3 and S4 are never ON at the same time, one is turned ON as the other is turned OFF. Transistor S4 is ON during time period T1, producing a negative voltage at the input of the filter at point A. At time period T2, S4 turns OFF and S3 turns ON, applying B+ to the filter. For time period T3, S4 is again ON, while for time period T4, S3 is ON. This switching produces a series of voltage pulses at the input of the filter.

Inspection of these pulses shows that positive pulses are wider

than negative pulses for this group of time cycles. Further, inspection of Figure 10c shows that there is a burst of wide pulses and then a burst of negative pulses. Since the widths of the pulses are controlled as a function of a sine wave, the modulated waveform of Figure 10c produces a sine wave when passed through a low-pass filter.

Design of the filter is a function of the ratio of the high-frequency carrier to the low-frequency output. The upper limit of this ratio is limited by the switching frequency of transistor switches S3 and S4. In determining the operating frequency, some tradeoff must be made between transformer and filter size and inverter efficiency.

Output voltage amplitude and frequency are determined by the sine wave which modulates switches S3 and S4. If the sine wave is fixed, then the output may be regulated by controlling the DC input voltage.

A second more direct method of regulation is to make the modulating sine wave a direct function of the output sine wave. When there is a change in output voltage it is reflected to the sine wave reference directly, making regulation time a function of the carrier frequency and not the output frequency.

A complete description is not given for this waveform as it is covered in the main body of the report.

The basic disadvantage of this circuit is reactive current flow.

The DC filters on the output of the converter must be designed to take care of the reactive current flow from the inverter. If this flow is very large, then the size and weight become increasingly larger, reducing the size and weight advantage of the design.

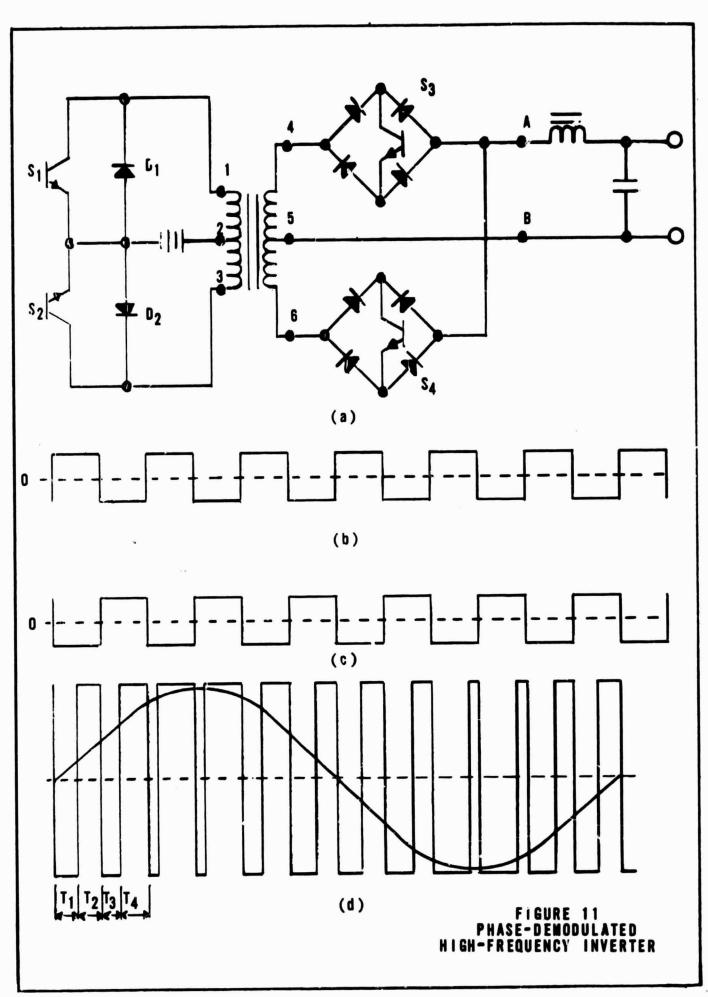

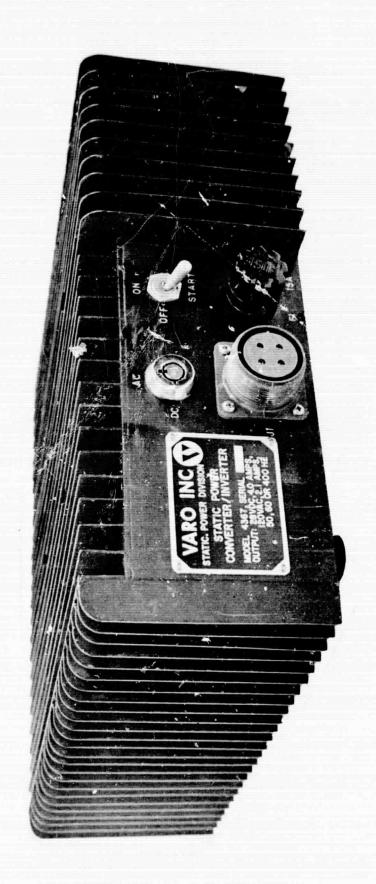

# 10. <u>Phase-Demodulated Inverter</u> (Figure 11)

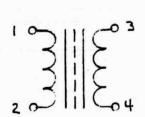

The phase-demodulated inverter is a new and unique state-of-theart inverter developed by Varo in early 1965. The basic design concept was tested and proved in a 200-VA variable-frequency inverter. The basic circuitry for this design is illustrated in Figure 11a. Input DC power is amplified by a squarewave parallel inverter at some high frequency predetermined by the design

requirements. The output of the power transformer is push-pull and is illustrated in Figure 11b and 11c. Figure 11b illustrates the voltage as it appears at terminals 4-5 of power transformer T<sub>1</sub>. Figure 11c illustrates the voltage that appears at terminals 5-6 of T<sub>1</sub>.

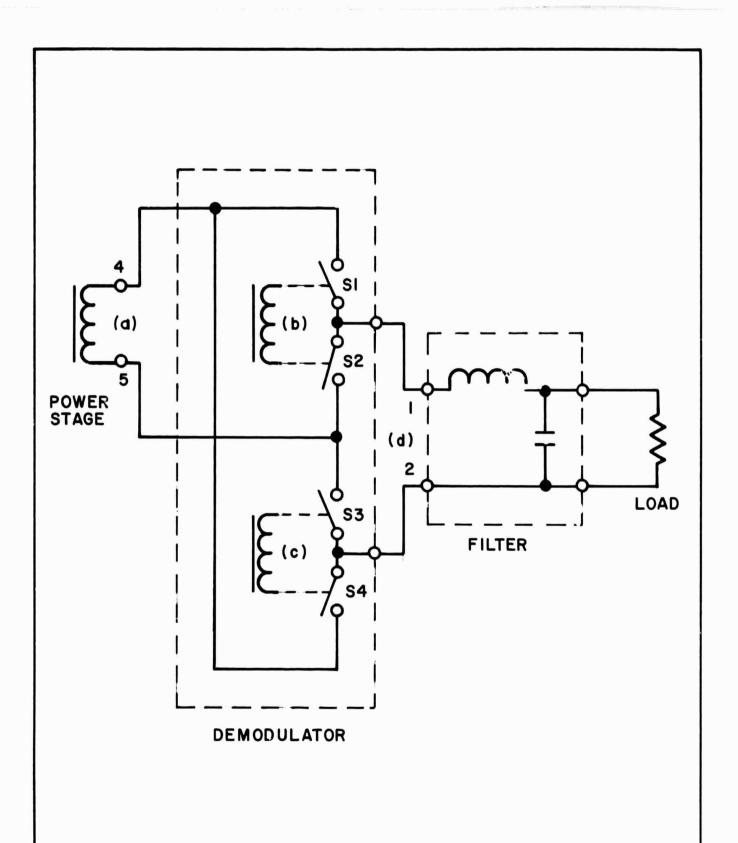

Terminals 4 and 6 are connected to the output filter by bilateral switches S3 and S4. By phasing the operation of switches S3 and S4 correctly, the high-frequency squarewave out of the power transformer is phase-demodulated to produce a pulse-width modulated voltage with a sine wave envelope. By the use of a simple low-pass filter, the modulated high-frequency wave is smoothed out to form a low-distorted sine wave.

The output AC voltage and frequency is controlled by varying the phase-demodulation of the high-frequency squarewave. Figures 11b, 11c, and 11d show the basic phase relationship of the power transformer output and switches S3 and S4. At time period T1, switch S4 is ON, connecting the negative voltage of terminal 6 to point A of the filter. At time period T2, switch S3 is turned ON and switch S4 is turned OFF, applying the positive voltage of terminal 4 to point A of the filter. At time period T3, the power stage reverses output voltage; however, transistor S3 stays ON, applying a negative voltage to point A for time period T3. Switches S3 and S4 again switch ON-OFF states at time period T4, again applying a positive voltage to point A. This switching is continued to produce the pulsewidth modulated voltage waveform illustrated in Figure 11d.

Output voltage and amplitude are a direct function of the modulating sine wave controlling the action of switches S3 and S4. This sine wave is an error signal developed by comparing the output voltage with a fixed sine wave reference voltage of the correct amplitude and frequency. This design provides an optimum in weight reduction since the power transformer is designed for the high-frequency carrier, the filter is of the low-pass design, and the required control circuit is not overly complex

A complete description of the operation of this circuit is provided in this report.

#### C. DESIGN SELECTION

All of the designs presented have innate advantages and disadvantages.

Selection of the best design weighed the basic design against the operational requirements of the inverter. Since a reduction of weight and space is a primary objective of the program, the first five basic designs can be removed from consideration. This leaves the following designs to be considered:

- 6. STEP-WAVE INVERTER

- 7. HIGH-FREQUENCY STEP-WAVE INVERTER

- 8. HIGH-FREQUENCY DC-DC CONVERTER-INVERTER

- 9. PULSE-WIDTH MODULATED INVERTER

- 10. PHASE-DEMODULATED INVERTER

Of the five remaining designs only the step-wave inverter is of the low-frequency type inverter designs. All of the remaining four designs utilize high-frequency power amplification in some means. Since the high-frequency step-wave inverter includes the basic advantage of the step-wave inverter, the step-wave will not be given further consideration.

One additional consideration to be given is the fact that all of the high-frequency units require high-voltage transistors. This problem has become less important than it was a year ago because most major device manufacturing companies are working on high-voltage devices and rapid advancements are being made in this field.

Of the four remaining designs, a basic separation of ability and desirability may be made. Reinspection of Figure 9a and Figure 10a shows that the high-frequency DC-DC converter-inverter and the Pulse-Width Modulated Inverter have the same basic circuit diagram. The pulse-width modulated inverter has two basic advantages: lighter weight, due to less filtering, and a basic ability to be paralleled. The converter-inverter approach should prove to be more efficient since the inverter transistor switch is at a much lower frequency.

The high-frequency step-wave inverter is an excellent design, except for the input DC regulation requirement. Also, the gating circuit to step and phase lock the output switches would be more complex than desired when weighed with the paralleling and three-phase requirements.

The Phase-Demodulated-High-Frequency Inverter is the most desirable of the designs considered. It offers a maximum weight reduction with a minimum of power and control circuitry. The output regulation is a function of the high-frequency carrier and not the output frequency. The resulting fast response allows units to be paralleled with a minimum of additional circuitry. Use of the output sine wave as part of the regulation loop provides for minimum phase chift of the output with respect to the reference, which, in turn, provides for good phase angle control when units are connected in three-phase configurations. These and many other advantages are more apparent from the detailed circuit description.

To provide a basic guide line for inverter selection, the best five designs are listed in Table II with a few of their evaluating factors. A 1-5 rating consideration was used for evaluation, where I is the most desirable. These ratings are provided only as a basic guide since a circuit modification could result in the re-evaluation of any of the individual ratings.

TABLE 2

INVERTER DESIGN EVALUATION

|                                            | WEIGHTING FACTORS |               |                 |                           |              |            |          |             |            |      |        |                       |

|--------------------------------------------|-------------------|---------------|-----------------|---------------------------|--------------|------------|----------|-------------|------------|------|--------|-----------------------|

| INVERTER TYPE                              | TRANSFORMER       | OUTPUT FILTER | CONTROL CIRCUIT | INTERMEDIATE DC<br>FILTER | POWER FACTOR | EFFICIENCY | PARALLEL | THREE PHASE | COMPLEXITY | SIZE | WEIGHT | TRANSIENT<br>RESPONSE |

| STEP-WAVE INVERTER                         | 5                 | 3             | 4               | NA                        | 2            | 1          | 4        | 4           | 2          | 5    | 5      | 5                     |

| HIGH-FREQUENCY STEP-<br>MAVE INVERTER      | 2                 | 3             | 5               | 5                         | 1            | 3          | 3        | 3           | 4          | 2    | 2      | 4                     |

| HIGH-FREQUENCY DC-DC<br>CONVERTER-INVERTER | 1                 | 5             | 2               | 5                         | 5            | 3          | 4        | 4           | 3          | 4    | 4      | 5                     |

| PULSE-WIDTH MODULATED INVERTER             | 1                 | 1             | 2               | 5                         | 3            | 3          | 2        | 1           | 3          | 3    | 3      | 3                     |

| PHASE-DEMODULATED INVERTER                 | 1                 | 1             | 2               | N A                       | 1            | 2          | 1        | 1           | 2          | 1    | 1      | 1                     |

NOTES: 1-5 RATING USED, 1 MOST DESIRABLE, NA - NOT APPLICABLE

### III. ELECTRICAL DISCUSSION

#### A. GENERAL CIRCUIT DESCRIPTION

The Phase-Demodu ated High-Frequency Inverter was selected not only for its general design advantages, but also for its overall versatility. This versatility is being demonstrated in several lightweight, multiple-frequency inverters being furnished to the U. S. Army Engineer Research and Development Laboratories. A list of these units is provided in Appendix B. The inverters furnished have utilized several basic design configurations, the best of which has been selected for use in the development of this inverter.

In the state-of-the-art study, only the basic Phase-Demodulated High-Frequency Inverter concept was described; however, the design to be utilized for this application is termed a Phase-Demodulated High-Frequency Bridge Inverter and has been used in the development of a 250-VA multiple-frequency inverter.

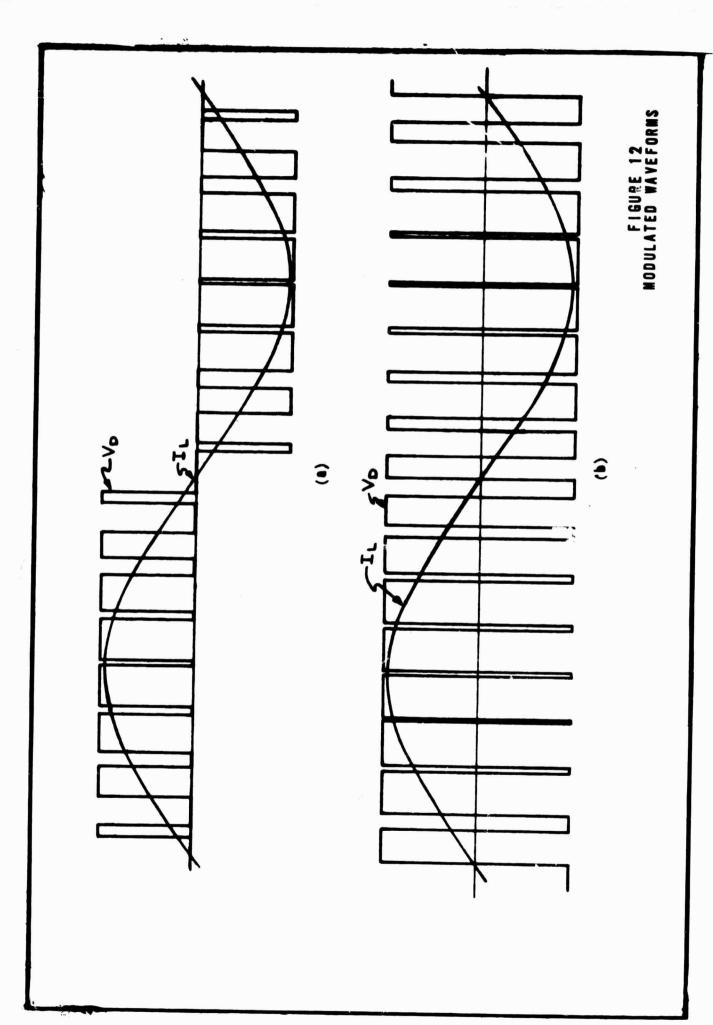

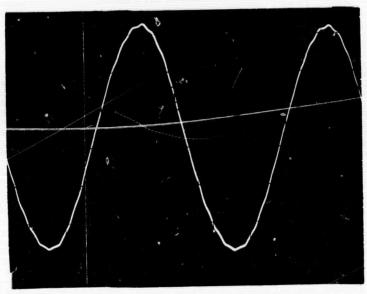

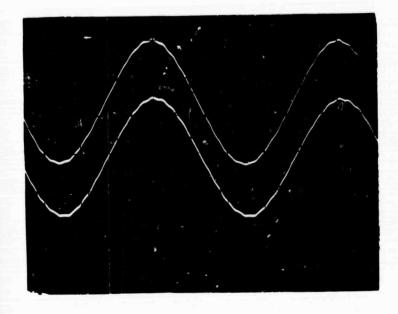

The advantage of the improved design is apparent in the comparison of output waveforms of the two designs. The output of the Phase-Demodulated High-Frequency Inverter is illustrated in Figure 12b, while the output of the improved design is illustrated in 12a. The modulated waveform of Figure 12a requires less output filtering and also results in less volt-ampere loading of the power transformer.

This improvement in design is Frought about with a minimum of additional circuitry. Figure 13 is a block diagram for a Phase-Demodulated High-Frequency Inverter which fulfills the basic design requirements. Figure 14 is the block diagram for the Phase-Demodulated High-Frequency Bridge Inverter. The basic difference in the two designs is the addition of an extra reference comparator circuit and a demodulator drive circuit.

Figure 14 includes all of the basic functions for single-phase, three-phase, and parallel operation of the inverter. The connection illustrated is for single-phase operation. Blank connections F, K, and L are for three-phase and/or parallel operation which is covered in a later section. A step-by-step discussion of Figure 14 provides a good understanding of the design concept of the Phase-

FIGURE 14

PHASE-DEMODULATED HIGH-FREQUENCY

BRIDGE INVERTER

Demodulated High-Frequency Bridge Inverter.

To protect the input DC line from RFI and line modulation due to the inverter, appropriate RFI and power filtering is provided. The RFI filtering is minor since the input filter suppresses RFI conduction in the input lines.

Power for the various control functions is provided by the control voltage regulator. This regulator provides all the proper level and degree of regulation.

Operation of the control functions and their relationships to the power stage and phase demodulator can best be explained through the use of waveforms illustrated in Figure 15. Figure 15a is a simplified schematic of the power stage and the demodulator, and is used to show the proper phase relationships between the various waveforms.

The 6400-Hz output of the internal oscillator is illustrated in Figure 15b. This output is frequency locked to the external signal through the synchronization circuit. The output of the oscillator provides the reference trigger for the power stage drive, the reference comparators, and the countdown circuit.

The power stage drive consists primarily of a flip-flop and several power amplifier stages. The pulse of Figure 15b triggers the flip-flop which is in turn amplified to produce the 3200-Hz push-pull drive voltage as illustrated in Figure 15c and 15d. This voltage is used to drive the power transistors illustrated as simple switches S1 and S2 in Figure 15a. Power transformer T1 amplifies this voltage to the proper level (Figure 15h).

The 6400-Hz signal is reduced to a 400-Hz squarewave voltage by the countdown Crcuit. The waveshaper network is an active filter which produces a precise 400-Hz sine wave from this squarewave voltage. This differential amplifier compares the output voltage of the inverter with the sine wave reference to produce a pair of sine wave error signals. These error signals (Figures 15e and 15h) control the output of the inverter. A change in the reference voltage or the output voltage causes an opposite change in the error signal.

Also illustrated in Figures 15e and 15h is a 3200-Hz ramp waveform which represents the control voltage of the two reference comparators. These

when the sine wave of Figure 15e crosses the ramp, a pulse is generated at the output of reference comparator (A). This pulse triggers a flip-flop in the demodulator drive (A) to produce a push-pull drive signal as illustrated in Figures 15f and 15g. Signal 15f drives bilateral switch S3 while signal 15g drives bilateral switch S4. The sine wave and ramp of Figure 15h, in turn, produces the drive signals of Figures 15k and 15m. Signal 15k drives bilateral switch S6 while 15m drives bilateral switch S5.

By using the time periods illustrated in Figure 15p, the relationship between the control function is shown as the output-modulated voltage waveform is developed. At time period  $T_1$  the sine wave signal and ramp signal of Figure 15h intersect, causing a change in the output of demodulator drive (B) which is reflected in the drive voltages shown in Figures 15k and 15m. This change in drive voltage turns switch S6 ON and switch S5 OFF, connecting terminal 2 of the output filter to terminal 5 of the power transformer. Terminal 1 of the output filter, connected to terminal 4 of the power transformer, did not change states at time period  $T_1$ . Negative output voltage, Figure 15h, is applied to the filter as shown in Figure 15p.

The next time period T<sub>2</sub> shows the sine wave and ramp signal of Figure 15e intersecting, causing switch S3 to turn OFF and switch S4 to turn ON. This action disconnects terminal 1 of the filter from the power transformer and connects it to terminal 2 of the filter, shorting out the input to the filter, and open circuiting the secondary of the power transformer.

At time period T<sub>3</sub> the output of the power transformer reverses, as illustrated in Figure 15h. Also, at this time the ramps are reset; however, there is no switching action of the demodulator switches during the resetting action. Since the demodulator did not change states, the input to the filter is still short circuited.

At time period T<sub>4</sub>, demodulator switches S3 and S4 again reverse states: switch S3 is turned ON and switch S4 is turned OFF. This action again connects terminal 1 of the filter to terminal 4 of the transformer. The short from the

filter is removed and the positive voltage of the transformer is connected to the filter input.

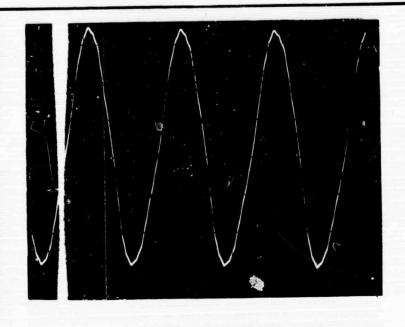

By following the action of the two control ramps and their error sine waves throughout a complete cycle of the output frequency, it is seen that the modulated voltage is passed through a low-pass filter to produce the low-distorted sine wave output voltage.

The inverter is protected from overloads by the output voltage sensor. When the output exceeds a predetermined level, a voltage signal to the waveshaper network causes the output reference sine wave to decrease, in turn, reducing the output voltage.

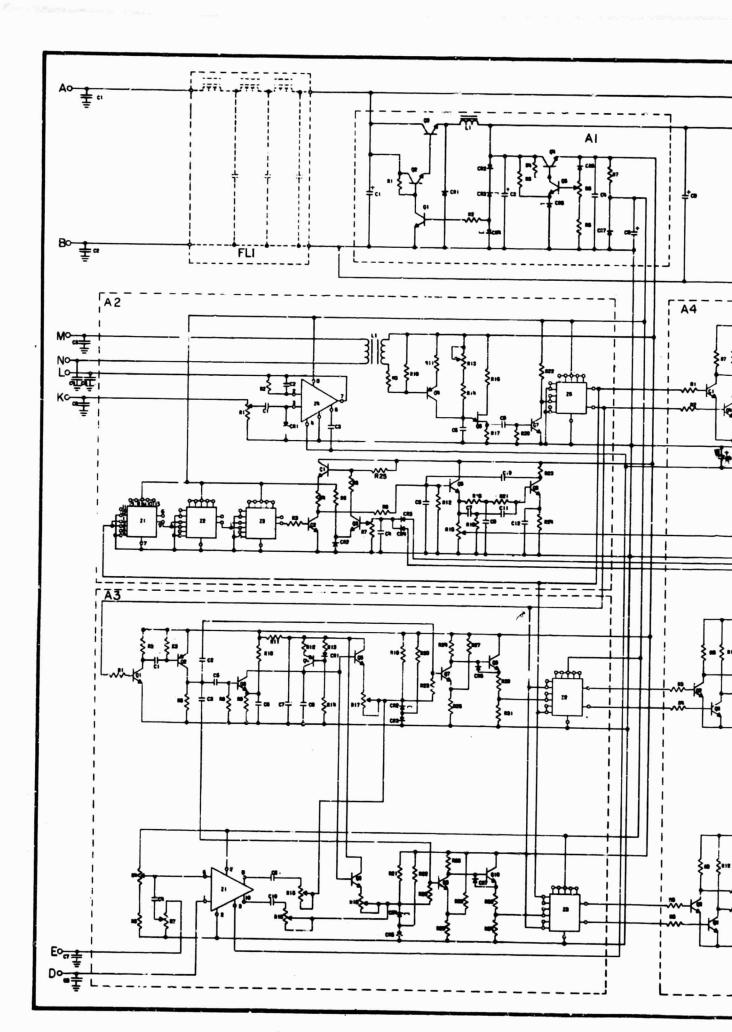

### B. DETAILED CIRCUIT DESCRIPTION (Figure 16)

The completed schematic diagram for the High-Frequency PhaseDemodulated Bridge Inverter (Figure 16) includes not only the components required for single-phase operation but also those required for parallel operation,

three-phase operation, and parallel-three-phase operation. To ensure complete

understanding of the inverter design concept as well as the operation of each of

the modules, a detailed description of the operation of each module is provided.

The schematic is divided into five major sections, the first three sections Al.

A2, A3, are control functions, and the last two, A4 and A5, are power functions.

Control sections A1, A2, and A3 represent three possible printed circuit board

arrangements. Section A4 represents the amplifier or drive stages (this function

could be one or three separated modules as determined by the final mechanical

design). Section A5 is all hardware normally connected to the main chassis

because of size or heatsink requirements.

Discussion of various circuits is not necessarily in the order of their location on the schematic, but is in logical sequence of their operation and relationship to each other:

- 1. Centrol Voltage Regulator

- 2. Synchronization Circuit and Internal Oscillator

- 3. Power Stage Drive and Power Stage

- 4. Countdown Circuit and Filter Network

- 5. Ramp Generator Differential Amplifier and Reference Comparators

- 6. Demodulator Drives and Demodulator

- 7. Filtering Output and Input and RFI

- 8. Voltage and Current Sensing

- 9. Three-Phase and Parallel Interconnection

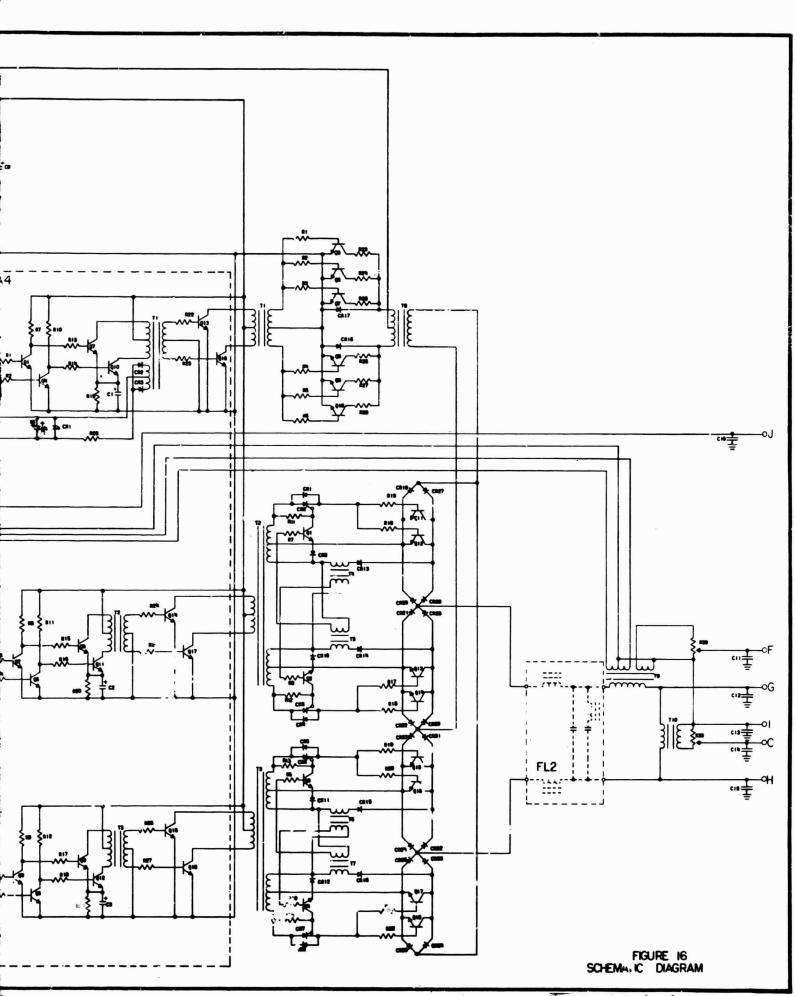

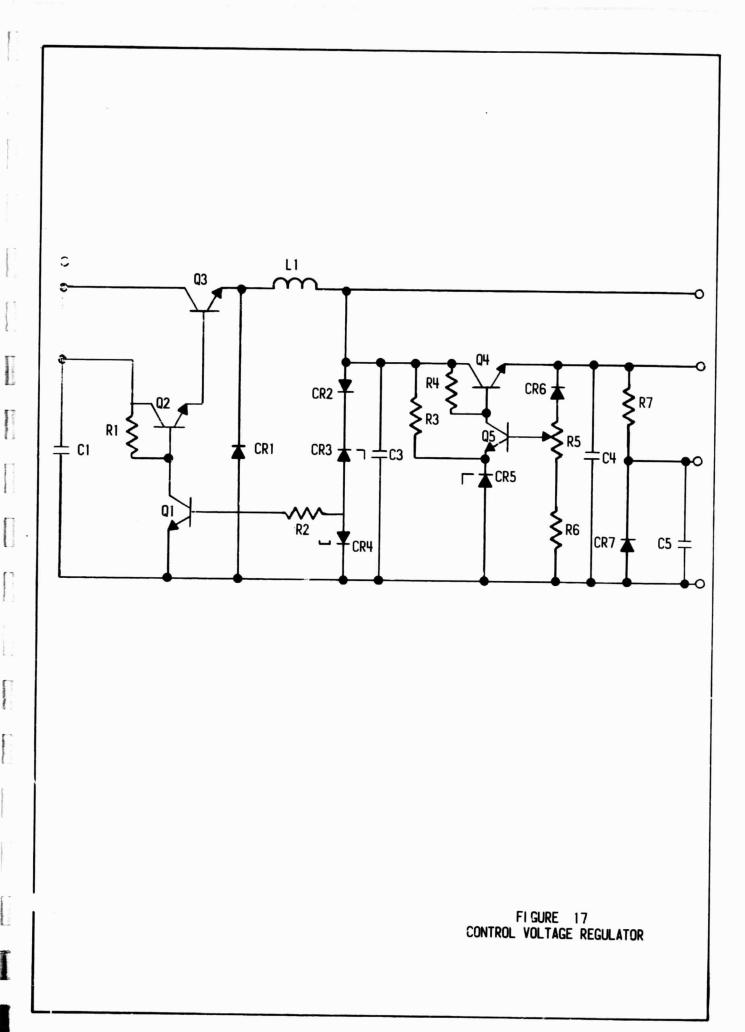

## 1. Control Voltage Regulator (Figure 17)

The control voltage regulator contains a chopper regulator, a series regulator, and a zener regulator. The combined use of several types of power controls was selected to achieve maximum efficiency with maximum performance of the control sections.

The chopper regulator is the most efficient, acts as preregulator for the other regulator circuits and provides all power for the drive circuits.

Through the use of this preregulator, the losses normally associated with series regulator circuits, zener circuits, and base drive circuits are greatly reduced.

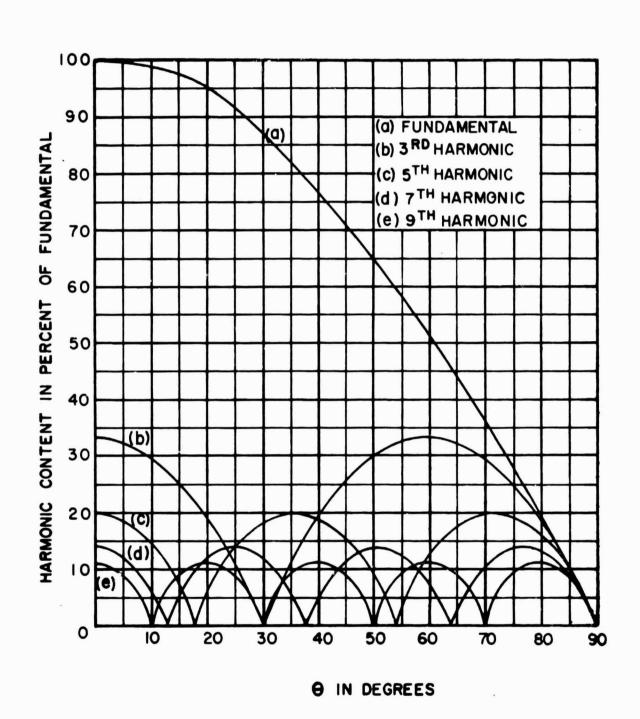

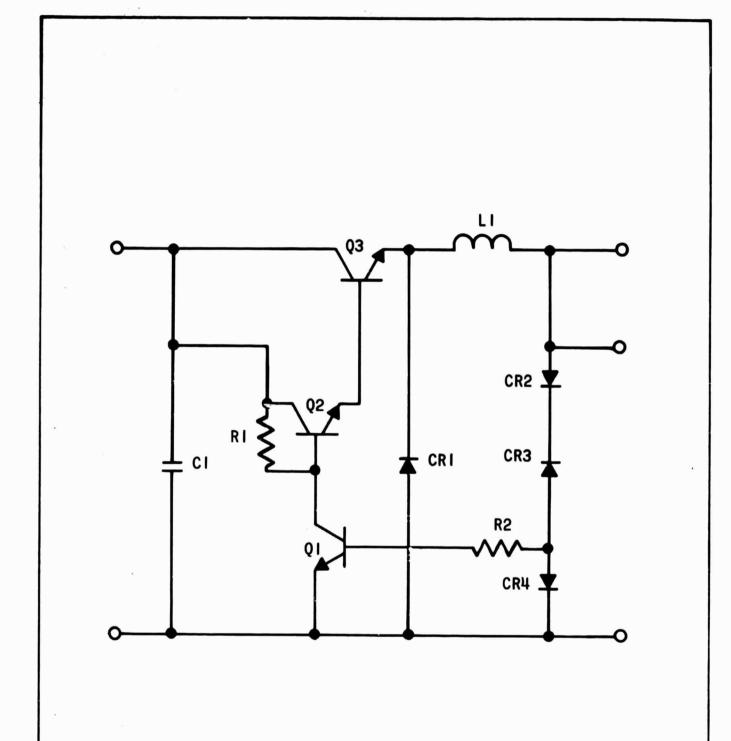

The chopper regulator circuit is illustrated in Figure 18.

Transistors Q1, Q2, and Q3 are operated in a saturated switching mode; that is, they are either ON or OFF. Their ON state is made a direct function of the output DC level and is controlled by constant current diode CR2, zener diode CR3, and tunnel diode CR4.

The DC output voltage level is established by the zener diode CR3. The constant current diode CR2 limits the current through the zener, thus allowing a low power zener to be utilized as a reference. The tunnel diode CR4 performs the actual regulation of the period of oscillation determined by the current through the tunnel diode. When there is an increase in the output voltage, there is a corresponding increase in the current through CR2, thus causing the tunnel diode to go into a low impedance state. At this time the voltage across the tunnel diode increases, turning transistor Q1 ON, turning OFF transistor Q2; Q3 in turn causes a drop in the output voltage which reduces the current through the tunnel diode, returning it to its original state.

FIGURE 18

CHOPPER REGULATOR

The frequency of oscillation is determined by the LC circuit and load current which in turn varies the current through CR4. Since the current through the tunnel diode is a direct function of the voltage out of the regulator, the tunnel diode regulates the output voltage by controlling the OFF-ON condition of transistor Ql. The output regulation and ripple is a function of the zener diode and the tunnel diode. Regulation runs about 2 percent with the 2 percent ripple voltage and an overall efficiency of about 95 percent.

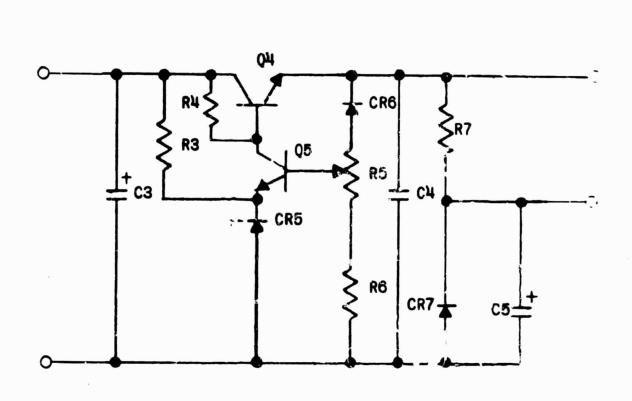

Since many of the control functions cannot tolerate the voltage variation and ripple of the chopper regulator circuit while maintaining the desired output requirements, a separate DC source must be established for these functions. The series regulator provides the precise power requirements of the control circuits. Since it operates off the chopper regulator output, its power dissipation is at a minimum.

The series regulator circuit (Figure 19) is a standard series regulator in which the output voltage is compared with a reference voltage established by zener diode CR5. The voltage change of the output is compared through transistor Q5 and voltage sensing network R6, R5, and CR6. Zener diode CR6 was added to the sensing network to increase the amount of the error signal appearing at the base of transistor Q5.

Also illustrated in Figure 19 is the zener diode circuit consisting of R7 and CR7. This circuit establishes required bias levels for the integrated circuit networks.

The various capacitors illustrated in the various regulator circuits are used for filtering and to help decouple the different regulator circuits.

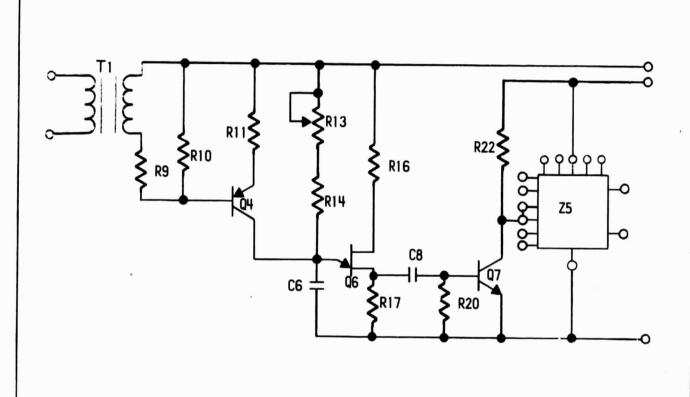

### 2. Synchronization Circuit and Internal Oscillator

The internal oscillator circuit is a 6400-Hz relaxation oscillator designed around unijunction transistor Q6 in Figure 20. In the free-running mode, capacitor C6 is charged through resistors R13 and R14 and discharged through emitter base one junction of transistor Q6 as the firing point of the unijunction transistor is reached. At this point the current through resistors R13 and R14

FIGURE 19 SERIES REGULATOR

FI GURE 20 OSCI LLATOR NETWORK

is insufficient to maintain the ON condition in transistor Q6, thus the cycle is repeated.

The positive voltage-pulse developed across resistor R17 when transistor Q6 turns ON is amplified and inverted by transistor Q7, providing a negative pulse to trigger bistable multivibrator Z5. Multivibrator Z5 then develops a 3200-Hz squarewave.

In the synchronized mode, the input squarewave is transformer coupled to the base of switching transistor Q4, turning Q4 ON and OFF on alternate half-cycles. This feature is used to synchronize the unijunction transistor oscillator to the input signal. Resistor R11 is of sufficiently low value so that when transistor Q4 is turned ON, capacitor C6 is abruptly charged and transistor Q6 turns ON. Transistor Q6 remains ON as long as Q4 is ON because the current through resistor R11 is greater than the holding current for transistor Q6. After one half-cycle, transistor Q4 and, in turn, transistor Q6 turn OFF. Then capacitor C6 again starts charging through resistors R13 and R14. Thus, transistor Q6 is actually locked in phase with transistor Q4, and with the input squarewave.

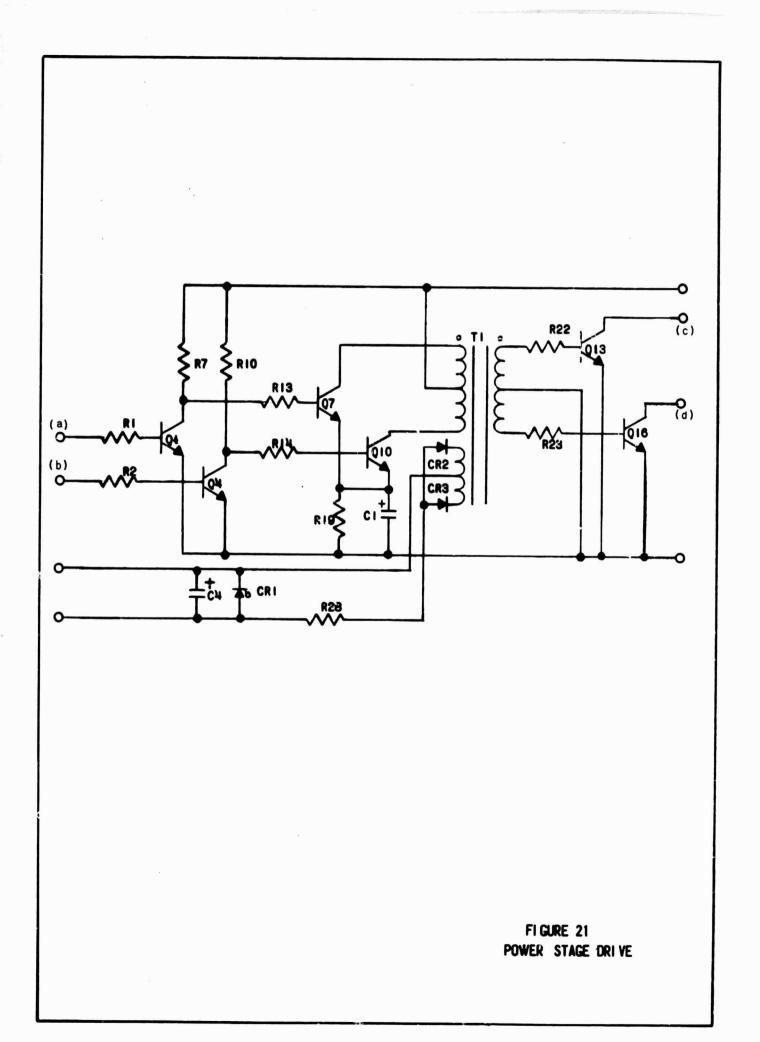

### 3. Power Stage Drive and Power Stage

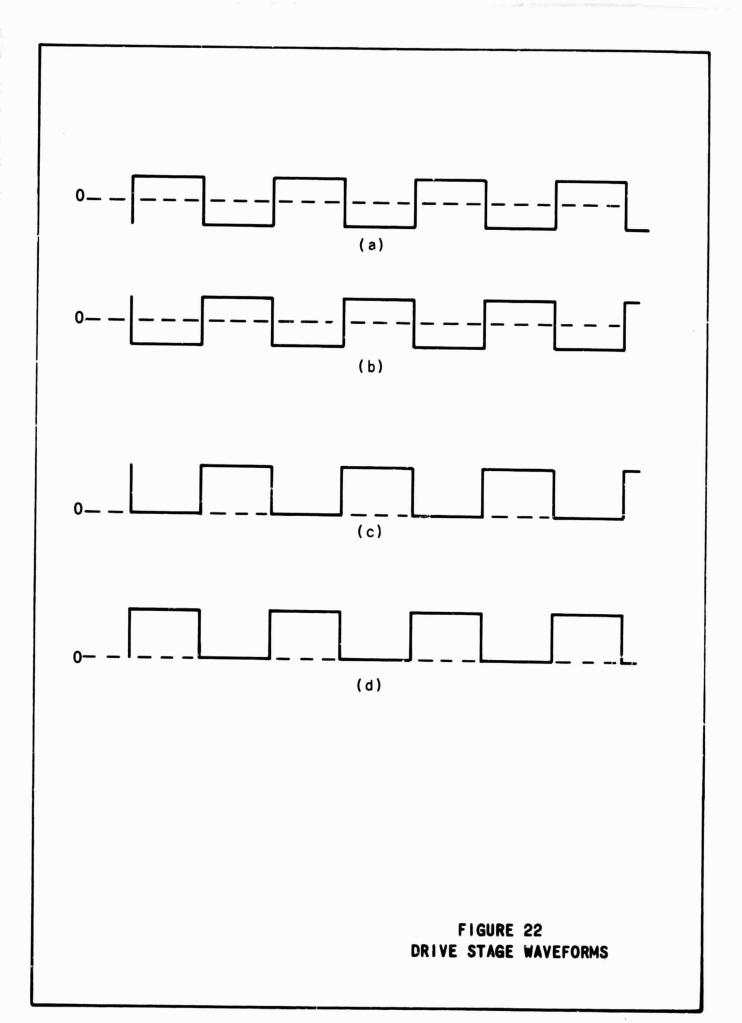

The power stage drive is primarily a power amplifier which amplifies the two squarewave voltages produced by the internal oscillator flip-flop. This amplifier, or drive circuit, is illustrated in Figure 21. The voltage at the base of transistor Ql is illustrated in Figure 22a, while Figure 22b illustrates the voltage at the base of transistor Q2. When the voltage of Figure 21a is positive, transistor Q1 is ON, turning transistor Q7 OFF. Transistor Q16 is ON at this time, producing a positive voltage at the base of transistor Q13 and turning it ON. The collector voltage of Q13 is illustrated in Figure 22c, while Figure 22d illustrates the collector voltage of transistor Q16. Thus, Figure 22 illustrates the input and output voltages of the drive stage with the proper phasing.

The drive stage also has a secondary function of providing negative voltage requirements to the differential amplifier and phase-shift network.

This function is accomplished by adding an additional secondary winding to

transformer Tl. The output of this winding is rectified, filtered, and zenered to provide precise voltage level.

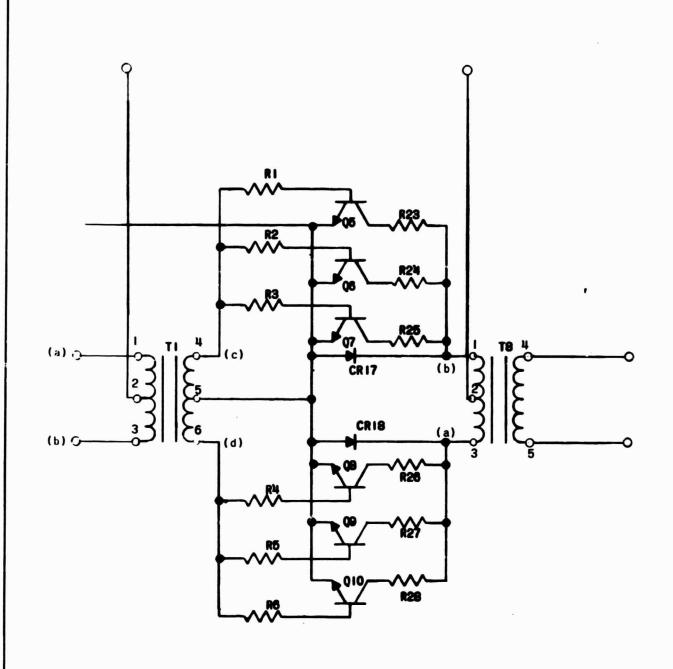

The primary function of the power stage is to convert the input DC voltage to an AC voltage and amplify this AC voltage to the proper level for use by the demodulator stage. The power stage is illustrated in Figure 23 and consists primarily of a drive transformer, power transistors, and a power transformer.

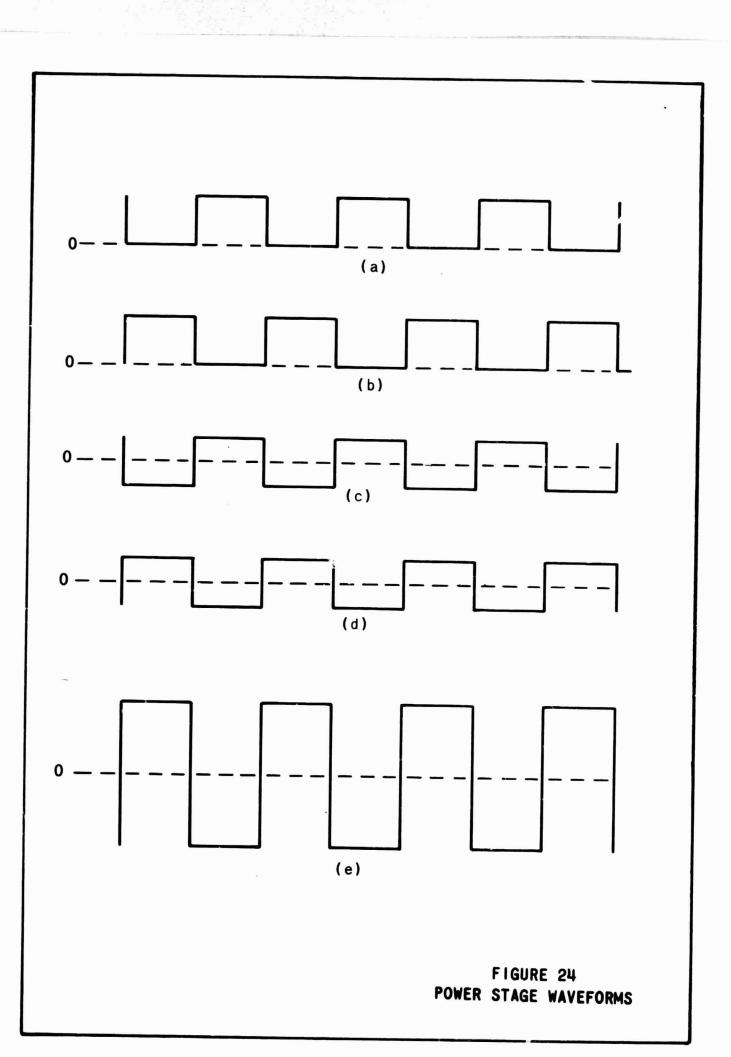

Drive transformer T1 is used for impedance matching between the power transistor and the drive stage. The push-pull input to the drive transformer is illustrated in Figure 24. The voltage at terminal 1 of T1 is illustrated in Figure 22a while Figure 22b illustrates the voltage at terminal 3. The voltages of terminal 4 are shown in Figure 24c while the inverse of this voltage appears at terminal 6, Figure 24d. These voltages drive power transistors Q5 through Q10. By using fast-rising squarewave drive voltages, switching losses are kept to a minimum. Resistors R1 through R6 are current-sharing resistors used to equalize the drive voltages and currents of the power transistors.

Transistors Q5 through Q7 are turned ON when the drive voltage, Figure 24c, is positive. Transistors Q8 through Q10 are biased OFF at this time by their drive voltage (Figure 24d). The push-pull action of the power transistors produces an AC voltage at the primary of power transformer T8 which is amplified, producing the 3200-Hz squarewave voltage illustrated in Figure 24e.

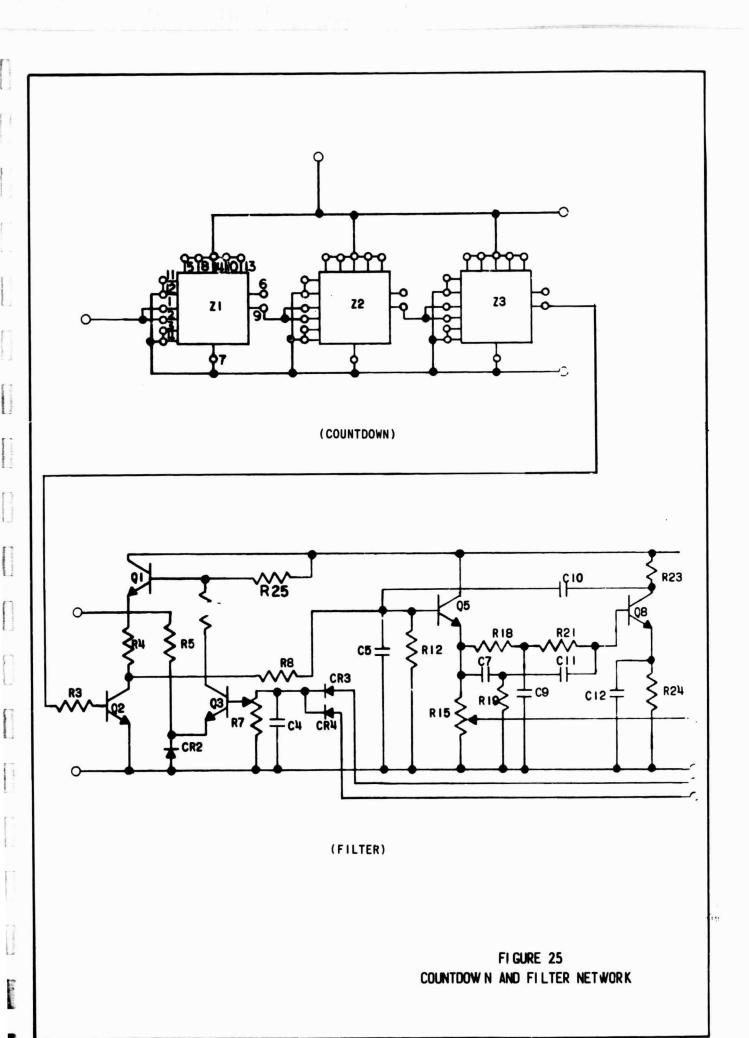

### 4. Countdown Circuit and Filter Network

A 400-Hz squarewave is developed by binary countdown from the 3200-Hz squarewave. Three bistable multi-vibrators are diagrammed in block form as Z1, Z2, and Z3 in Figure 25, along with the 400-Hz filter circuit.

Transistor Q2 is used as a saturating amplifier to isolate Z3 from the filter. The filter itself is of the active type, designed around a twintee network which is tuned to 400 Hz. Transistor Q5 is an emitter follower input stage. The twin-tee passes all frequencies except 400 Hz to the base of inverting

FI GURE 23 POWER STAGE

amplifier stage Q6. Then feedback capacitor C10 provides negative feedback for all frequencies, except 400 Hz. Thus, the odd harmonic content of the 400-Hz squarewave is filtered out, leaving a 400-Hz low-distorted sine wave.

5. Ramp Generator, Differential Amplifier, and Reference

Comparators (Figure 26)

These four circuits represent the basic feedback or regulator loop of the inverter. They are illustrated as a group, showing the interrelationships.

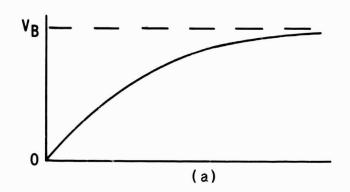

The ramp generator (Figure 26) is basically what its name implies; a circuit that generates a linear ramp function. To provide a detailed understanding of the operation of the ramp generator, various voltage and current waveforms are illustrated (Figure 27) along with discussion of how they are obtained.

If transistor Q4 were ON and a voltage applied to resistor R12, a voltage would develop at point A, Figure 27a. This is the charging potential that appears across a capacitor as it is charged through a resistor from a DC source. The 3200-Hz squarewave output voltage of the internal oscillator is integrated to form a 3200-Hz synchronizing pulse, Figure 27b, at point B. As this pulse turns transistor Q3 ON, point A is clamped to ground, forcing capacitor C8 to discharge. The voltage now appearing across capacitor C8, point A, is illustrated in Figure 27c.

To make the ramp more linear, the charging current must be held constant. This is done by holding the voltage across R12 constant. Resistors R13 and R14 form a voltage divider network to which the base of transistor Q4 is connected. Diode CR1 is for temperature compensation. Since the base current is small compared with the fixed current of R13 and R14, the voltage at point C remains fixed. This, in turn, holds the voltage across resistor R12 constant, producing the sawtooth voltage illustrated in Figure 27d. Transistors Q5 and Q6 act as emitter followers to produce the ramp currents (Figure 27e) used by the reference comparator circuits.

The key to the operation of this circuit is the synchronizing

FIGURE 27

SAWTOOTH WAVEFORMS

pulse which prevents transistor Q4 from operating out of its active region.

(If Q4 becomes saturated, the oltage waveform becomes nonlinear.) The synchronizing pulse also synchronizes the reference comparator circuits to be explained later.

The differential amplifier is a high-gain amplifier used to compare the output voltage with a fixed reference voltage established by the filter network. The amplifier circuit is illustrated in Figure 28. So that the inverter meets the paralleling and three-phase interconnection requirements, the amplifier is designed to provide the correct error signals at points C and D with predetermined signals at points A and B. This is necessary so that the inverter may be connected in parallel or three-phase without readjustments.

The amplifier compares the feedback sine wave with the reference sine wave and produces two sine wave error signals. One error signal is in phase with the output while the other error signal is 180 degrees out of phase. An increase in the output voltage of the inverter causes a decrease in the two error signals, thus causing the output voltage to be reduced in proportion to the change in the error signal. This relationship becomes more obvious in the discussion of reference comparators.

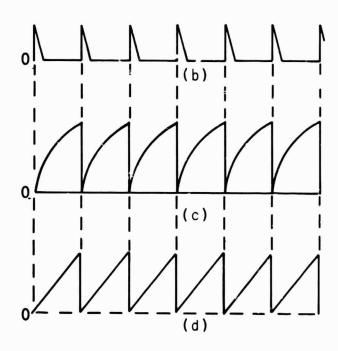

The function of the reference comparator circuits is to furnish two sets of 3200-Hz modulated squarewave drive voltages for the demodulator stage. Modulation of the squarewave voltages is a function of the sine wave error signals and is determined by the reference comparator. Since operation of both reference comparators is identical, a detailed explanation of only one comparator is given. Waveforms for both circuits are illustrated in Figure 30, while the schematic diagram for the comparators is illustrated in Figure 29.

The heart of the comparator is tunnel diodes CR2 and CR4. As is well known, a tunnel diode has a negative resistance region which is a function of the current through the diode. When current through the diode reaches a predetermined level, known as Ip, voltage across the diode takes an immediate step jump to some higher value determined by the load line of the device. This increase in voltage across the tunnel diode is in the order of

magnitude of five. Corresponding with this increase in voltage, there is a decrease in current through the tunnel diode due to its negative resistance characteristics. This characteristic is utilized to obtain a step voltage without a corresponding increase in current. Again referring to Figure 29, it is seen that the step voltage appearing across tunnel diode CR2 turns transistor Q7 ON.

The waveforms of Figure 30 further illustrate the regulating action of the tunnel diode. The Ip, or trigger level, of the tunnel diode is illustrated in Figure 30a. Now, if sinusoidal error current IE from the reference comparator is superimposed over Ip, then the locus of a new trigger point, IT, may be plotted (Figure 30b). Trigger point IT of tunnel diode CR2 is now a sinusoidal function of error signal IE.

By combining sawtooth current IS with trip current IT, transistor Q7 may be driven in a modulated form. Figure 30c shows that each time ramp current IS of the sawtooth crosses trip point IT of the tunnel diode, the tunnel diode changes states, turning transistor Q7 ON. This, in turn, turns transistor Q9 OFF. Each time the ramp is reset the tunnel diode is reset and transistor Q7 is turned OFF through Point C which is connected to capacitor C2 in the ramp generator circuit.

The output of transistor Q9 (Figure 30d) drives flip-flop Z<sub>2</sub>. When this voltage (Figure 30d) goes negative, the flip-flop reverts states (Figures 30e and 30f).

Operation of the second reference comparator is identical to that of the first, except that tunnel diode trip point IT is phase shifted 180 degrees from that of the first reference comparator. The output of transistor Q10 is the same as illustrated in Figure 10d, except inverted. This output, in turn, drives flip-flop Z3, which has an output (Figures 30g and 30h).

To ensure proper phasing between the demodulator stage and the power stage, flip-flops Z2 and Z3 are phase locked to the output of Z5 of the oscillator circuit through connections d and e.

# 6. Demodulator Drive and Demodulator (Figure 31)

Demodulator drive stage operation is the same as the power stage drive operation, thus a detailed discussion is not furnished.

The demodulator drive stage amplifies the signal from the flipflop of the reference comparator to a level usable by the demodulator stage

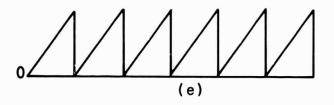

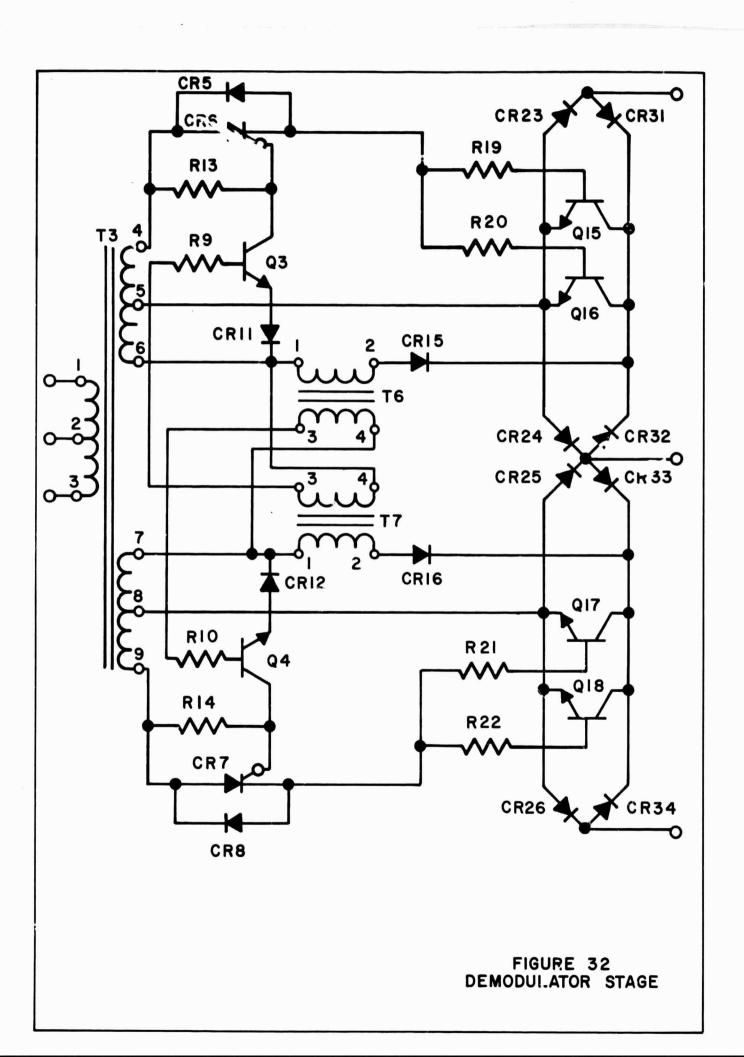

The object of the demodulator stage is to convert the 3200-Hz squarewave voltage to a pulse-width modulated voltage. Half of the demodulator stage is illustrated in Figure 32. The complete demodulator (Figure 16) is made up of four bilateral switches and four base drive impedance-matching networks. The impedance-matching networks form the same function as the power stage, except that they have been modified to improve switching characteristics. This function is described more fully in the Design Analysis section of the report.

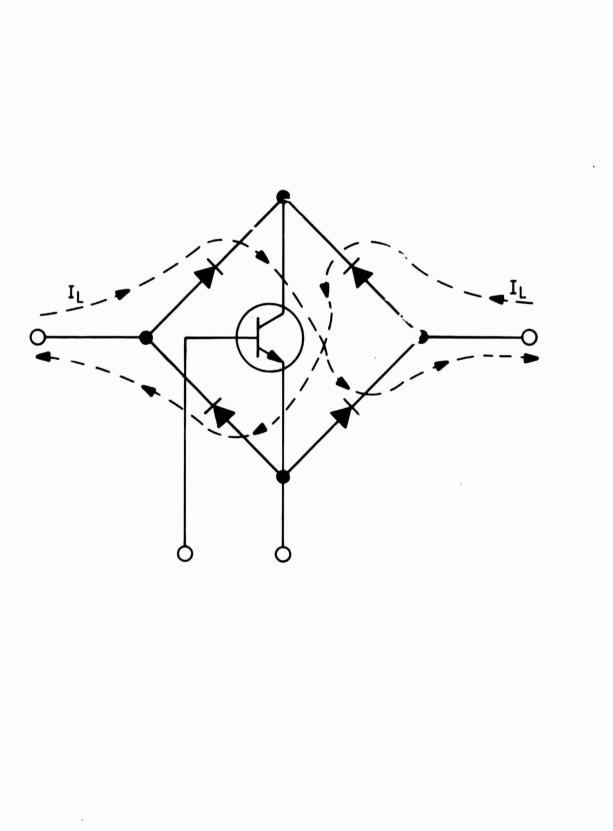

The bilateral switches, consisting of transistors Q11 through Q18 and diodes CR19 through CR34, convert the 3200-Hz squarewave voltage to a pulse-width modulated voltage. A simplified version of the bilateral switch showing possible current flow is shown in Figure 33.

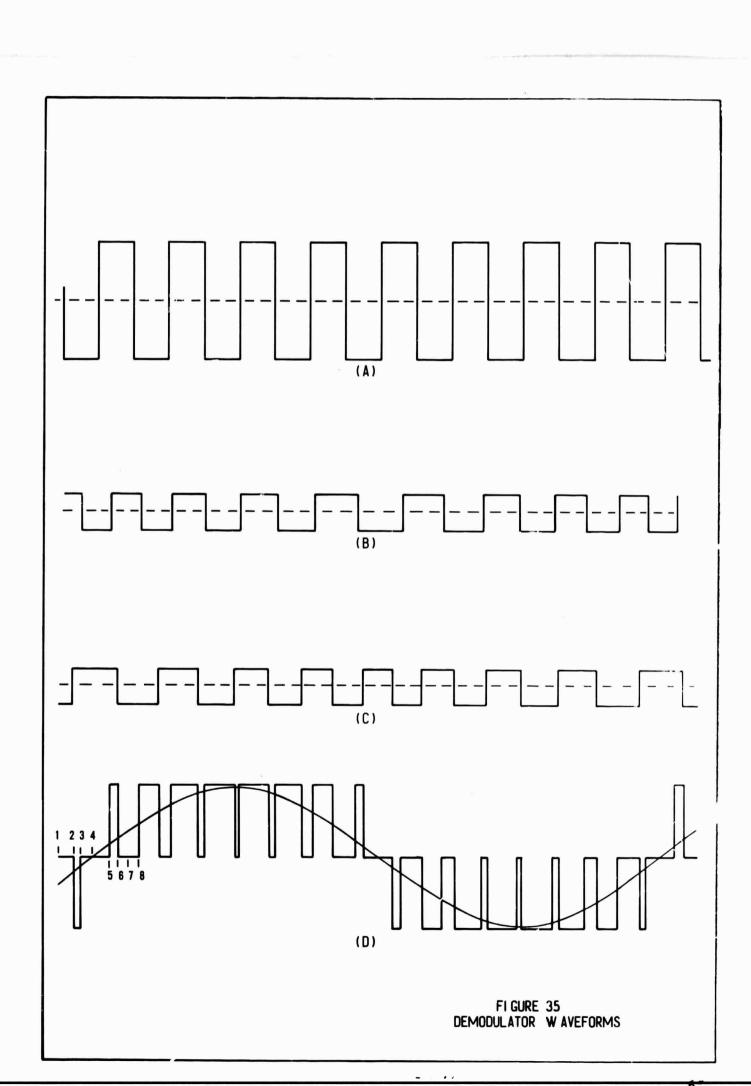

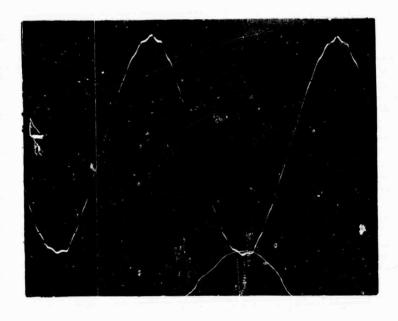

The simplified schematic of Figure 34 along with the waveforms of Figure 35 are used to show the phase and modulation operation of the demodulator stage. Figure 34a is the 3200-Hz squarewave out of the power stage. Figure 34b is the push-pull voltage from a reference comparator which controls the operations of the bilateral switches. When the voltage (Figure 34b) is positive, switch S1 is closed and S2 is open. The output of the other reference comparator (Figure 35c) drives switches S3 and S4. When it is positive, S3 is ON and S4 is OFF. The demodulator stage output, a 6400-Hz pulse-width modulated voltage waveform (Figure 35d) may now be developed. To help in the explanation, a set of reference points (1-8) are added to Figure 35d.

At point 1, the power stage output reverses so that it is negative. Also, at this time switch 1 and switch 4 are ON due to the voltage condition illustrated in Figures 35b and 35c. This condition places a short circuit on the input of the filter. Since switches S2 and S3 are OFF, or open, the secondary of the power transformer is unloaded and there is no voltage at the input of the filter.

FIGURE 33

BILATERAL SWITCH

FIGURE 34

SIMPLIFIED SCHEMATIC

This condition is illustrated in simplified form in Figure 36a.

At point 2, the voltage to switches 3 and 4 reverses, turning switch 4 OFF and turning switch 3 ON. Inspection of Figure 34 shows that under this condition terminal 1 of the filter is connected to terminal 4 of the power stage and terminal 5 of the power stage is connected to terminal 2 of the filter. Since the output of the transformer (4 to 5) is negative, then a negative voltage appears at the input of the filter. This circuit is illustrated in Figure 36b, and its waveform in Figure 35d, points 2 to 3.

At point 3, the drive (Figure 35b) for switches 1 and 2 reverses, turning switch 1 OFF and switch 2 ON. This again shorts out the input to the filter (Figure 36c).

At point 4, the output of the power stage reverses polarity as in Figure 35a; however, there was no action by the demodulator switches, thus the input to the filter does not change (Figure 35d).

At point 5, the drive (Figure 35b) again reverses, turning switch S2 OFF while turning switch S1 ON. This action connects the transformer to the filter (Figure 36d). Since the output of the transformer is positive, a positive voltage appears at the input to the filter.

By following the switching action of the power stage and the controlling action of the demodulator switches, the pulse-width modulated voltage (Figure 35d) is developed. Pulse-width modulation is a function of the operation of the modulator switches which are controlled by the reference comparators. The amount of modulation, or the pulse width, of the pulses determines the amplitude of the output sine wave (Figure 35d).

# Filtering Output, Input, and RFI

The output of the demodulator consists primarily of a group of positive going and negative going pulses with a basic frequency of 6400 Hz (Figure 35d). The primary function of the output filter is to waveshape this modulated voltage to form a sine wave containing a minimum amount of distortion. It is also desirable that the filter achieve this function without producing any

unnecessary voltage-ampere burden on the demodulator or power stage. It is further desired that the filtering operation be independent of the inverter load.

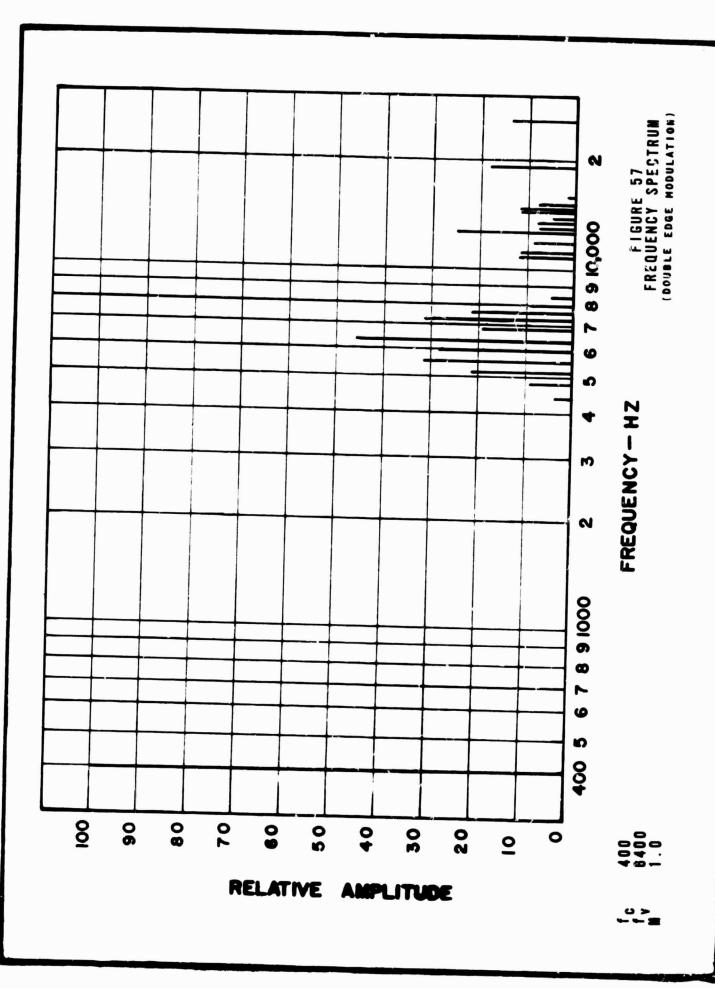

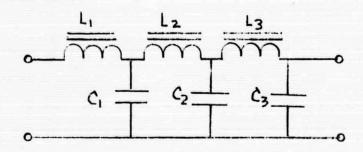

Figure 35d shows that fundamental voltage is a direct function of the amount of modulation; however, the major requirement for the filter design is a knowledge of the harmonic voltages present and their respective frequencies. Figure 37 is a plot of the frequency spectrum of the pulse-width modulated wave-form shown in Figure 35d. This spectrum is for a modulation index of one and reveals that the four major harmonic voltages present are located at 5200 Hz, 6000 Hz, 6800 Hz, and 7600 Hz. These four harmonic voltages represent the major harmonics that must be filtered by the filter while passing the fundamental 400-Hz frequency.

The design which offers the maximum design advantage is presented as FL2 in Figure 38. This is a simple low-pass filter designed for the specific 400-Hz load conditions. To further attenuate the four basic harmonic frequencies, a series-tuned 4600-Hz trap is added.

To reduce the RFI requirements, the parallel inductor, normally one device, is split into two separate inductors ( $L_1$  and  $L_2$ ). Since this is a low-pass filter, simple bypass capacitors reduce the RFI to the desired level.

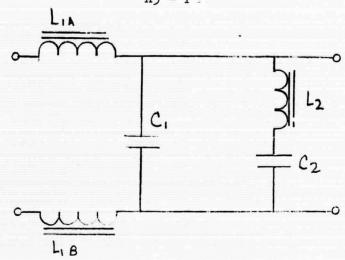

The input filter shown in Figure 39 as FL1 isolates the input DC line from modulation and ripple generated by the inverter. It also isolates the inverter from high-voltage surges on the DC line.

The filter design is based primarily on the modulation requirement -- the governing factor. A 400-Hz inverter modulates the input at an 800-cycle rate; therefore, filter requirements are basically those of a 400-cycle rectified sine wave with the load current and source impedance determining the filter requirements. One additional requirement of the phase-demodulated inverter is that the input current is a combination of 6400-Hz pulses and a 400-Hz rectified sine wave.

(Final design will be determined through test and evaluation of the waveforms generated by the prototype inverter. This determination is necessary for maximum efficiency with minimum weight. This filter will also act as

FI GURE 38 OUTPUT NETWORK

FIGURE 39 INPUT FILTER

the primary RFI filter with bypass capacitors for additional safety. The input, as well as the output, filter must be located as close as possible to the connector to provide maximum efficiency in the reduction of RFI.)

## Voltage and Sensing

Sensing functions are performed by a set of transformers to provide isolation between input and output. Voltage transformer T10 and current transformer T9 are shown in Figure 38.

The voltage sensing transformer is a 400-Hz step-down transformer. Output of the transformer is connected to output terminals I and C through voltage adjustment resistor R30. The output of terminal I and C is set at 2.5 volts peak-to-peak with 115 volts from the inverter. This setting is a requirement for the three-phase operation to be discussed later. In normal operation this output signal is fed directly back into the inverter at terminal D. Since terminal I is the internal control ground lead, it does not require reconnecting.

The current-sensing transformer has two secondary windings.

Windings 6-7 is used for parallel operation which is discussed in the next section.