PRICES SUBJECT TO

NASA CR 115187 c.1(R)

LOAN COPY: RE APWL TECHNICAL KIRTLAND AFB

N71 36771

UNCLES

MTERMETRICS

1. NASA CR 115187

CR-1/5/87

Final Report

Standard Interface Definition. For Avionics Data Bus Systems, FINAL REPORT (16 Dec 70 -

Alex L. Kosmala, Joseph A. Saponaro, and John P. Green, Jr.

May 1971

Prepared under Contract NAS 9-11477 by

3. INTERMETRICS, INC. 380 Green Street Cambridge, Mass. 02139

#### Foreword

This document is the final report on the definition of a Standard Interface Unit for avionics data bus systems. The study was sponsored by the Manned Spacecraft Center, Houston, Texas, under Contract NAS 9-11477. It was performed by Intermetrics, Inc., Cambridge, Massachusetts, under the technical direction of Mr. Alex L. Kosmala.

The study program covered the period from 16 December 1970 through May 16 1971. The Technical Monitor for the Manned Spacecraft Center was Mr. Cline W. Frasier.

The publication of this report does not constitute approval by the NASA of the findings or recommendations contained therein.

## Table of Contents

| Chapter 1 | Introduction                                                                                                            |                |

|-----------|-------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.1       | Background to the Study                                                                                                 | •              |

| 1.2       | Objectives of the Study                                                                                                 | ;              |

| 1.3       | Approach to the Study                                                                                                   | •              |

| 1.4       | Overview of the Report                                                                                                  | 4              |

| 1.5       | Summary of Recommendations                                                                                              | 4              |

|           | 1.5.1 Bus Control Summary Recommendations 1.5.2 Recommendation of Standard Interface Unit Organization                  | 5              |

| Chapter 2 | Space Shuttle Data Bus Definitions and Ground Rules                                                                     | 7              |

| 2.1.      | Introduction                                                                                                            | 7              |

| 2.2       | Data Bus Definition and Terminology                                                                                     | 7              |

|           | 2.2.1 Definition 2.2.2 Terminology                                                                                      | 7              |

| 2.3       | Review of Shuttle Data Bus Requirements and Ground Rules                                                                | 10             |

| Chapter 3 | Reliability, Redundancy and Organization                                                                                | 15             |

| 3.1       | Definition of Failure Tolerance                                                                                         | 15             |

| 3.2       | Failure Detection and Isolation                                                                                         | 18             |

|           | 3.2.1 Computer Failure Detection and Recovery 3.2.2 Data Bus Error Detection and Recovery 3.2.3 Subsystem Output Voting | 18<br>21<br>23 |

| 3.3       | Redundancy Interfacing                                                                                                  | 24             |

|           | 3.3.1 Computer to Bus Interface 3.3.2 Bus-to-LRU Interface                                                              | 24<br>30       |

| 3.4       | Relationship of Computer to Bus                                                                                         | 37             |

|           | 3.4.1 Central Computer, Single Bus 3.4.2 Distributed Computers, Single Bus 3.4.3 Distributed Computers, Multiple Buses  | 38<br>40<br>44 |

| Chapter 4 | Operation and Control of the Data Bus                                                                                                                                                                                                                                                                                                   | 4                                            |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 4.1       | Data Bus Access and Control Philosophy                                                                                                                                                                                                                                                                                                  | 4                                            |

|           | 4.1.1 General Description of Bus Access Methods 4.1.2 Qualitative Evaluation of Access Methods                                                                                                                                                                                                                                          | 4:                                           |

| 4.2       | Control and Operation of the Data Bus by the BCU                                                                                                                                                                                                                                                                                        | 5                                            |

|           | 4.2.1 Bus Message Format                                                                                                                                                                                                                                                                                                                | 5 (                                          |

| 4.3       | Operation and Control of the Data Bus by the Computer                                                                                                                                                                                                                                                                                   | 60                                           |

|           | <ul> <li>4.3.1 Overview of Computer I/O Operations</li> <li>4.3.2 Computer to Bus Operations</li> <li>4.3.3 I/O - Processing Memory Conflicts (Buffering and Interlocking)</li> </ul>                                                                                                                                                   | 60<br>62<br>67                               |

| 4.4       | Description and Analysis of I/O Transactions                                                                                                                                                                                                                                                                                            | 68                                           |

|           | 4.4.1 Definition of an "I/O Transaction" 4.4.2 Functional Description of Bus Transactions 4.4.3 Description of the Transaction Sequence 4.4.4 Bus Efficiency and Latency                                                                                                                                                                | 68<br>69<br>72<br>74                         |

| 4.5       | I/O Timing Difficulties                                                                                                                                                                                                                                                                                                                 | 78                                           |

| Chapter 5 | Data Bus Error Control                                                                                                                                                                                                                                                                                                                  | <br>79                                       |

| 5.1       | Introduction                                                                                                                                                                                                                                                                                                                            | 79                                           |

| 5.2       | Information Coding Review Discussion                                                                                                                                                                                                                                                                                                    | 80                                           |

|           | 5.2.1 Coding Theory 5.2.2 Single Parity 5.2.3 Error Correcting Codes 5.2.4 Higher Order Error Correcting Codes 5.2.5 Burst Errors and Burst Codes 5.2.6 Fire Codes and Other Burst Codes 5.2.7 Horizontal and Vertical Parity Coding 5.2.8 Repeated Transmission 5.2.9 Transmission Over Multiple Paths 5.2.10 Data Feedback/Echo Check | 80<br>80<br>81<br>83<br>85<br>85<br>86<br>86 |

| 5.3       | Detection and Retransmission Vs. Forward Error Correction                                                                                                                                                                                                                                                                               | 87                                           |

| Chapter 6 | Bus Implementation Factors                                                                                                                                                                                                                                                                                                              | 9.1                                          |

| 6.1       | Transmission Problems                                                                                                                                                                                                                                                                                                                   | 91                                           |

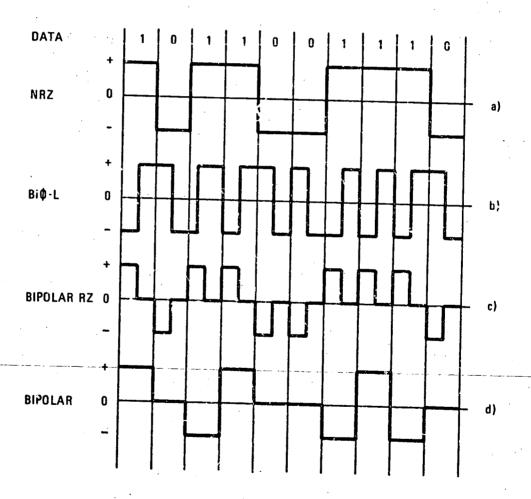

| 6.2       | Non-carrier (Base-band) Signalling Schemes                                                                                                                                                                                                                                                                                              | 92                                           |

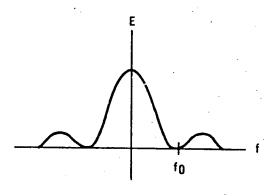

| 6.3       | Carrier Modulation Techniques                                                                                                                                                                                                                                                                                                           | 96                                           |

|       | 6.4    | Bit Synchronization                                                                                                                                                                                                        | 9                               |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|       | 6.5    | Transmission Media                                                                                                                                                                                                         | 9                               |

| Chapt | ter 7  | Summary Review and Recommendation                                                                                                                                                                                          | 10:                             |

| ,     | 7.1    | Introduction                                                                                                                                                                                                               | 10                              |

|       | 7.2    | Command and Control of the Shuttle Data Bus                                                                                                                                                                                | 106                             |

|       |        | <ul><li>7.2.1 System Configuration</li><li>7.2.2 Bus Control Policy</li><li>7.2.3 Bus Data Structure</li><li>7.2.4 Functions of the Interface Unit</li></ul>                                                               | 107<br>108<br>112<br>115        |

|       | 7.3    | Organization of the Data Bus Terminal                                                                                                                                                                                      | 118                             |

|       |        | 7.3.1 Introduction 7.3.2 Functions of the Bus Terminal 7.3.3 Interfacing the LRU to the Bus 7.3.4 Recommended Bus/SIU/EIU Configuration 7.3.5 Recommended Bus/SIU Interface Design 7.3.6 Expansion of SIU/EIU Capabilities | 118<br>118<br>123<br>127<br>129 |

| : .   |        |                                                                                                                                                                                                                            |                                 |

| Appen | dix A  | A Discussion of the Effects of Cross-strapping                                                                                                                                                                             | 135                             |

|       |        | 3 Analysis of a Typical Avionics System                                                                                                                                                                                    | 143                             |

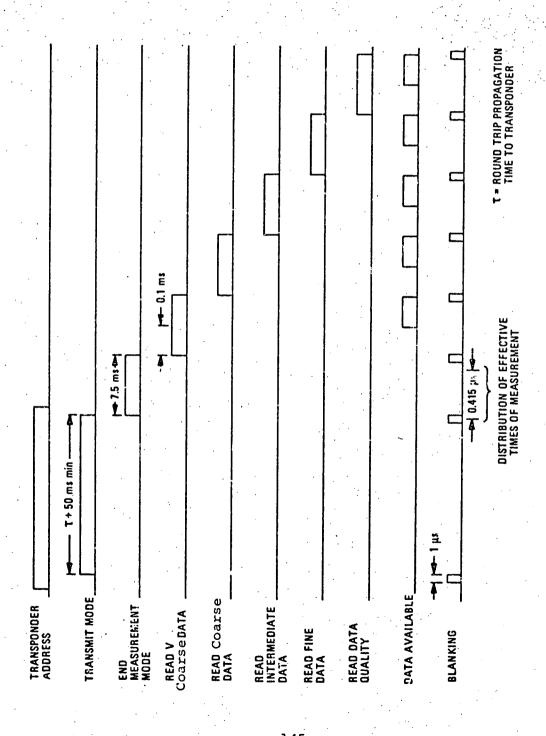

| . ,   | B.1    | Introduction                                                                                                                                                                                                               | 143                             |

|       | B.2    | Operation                                                                                                                                                                                                                  | 144                             |

| ٠     | B.3    | Control Requirements                                                                                                                                                                                                       | 147                             |

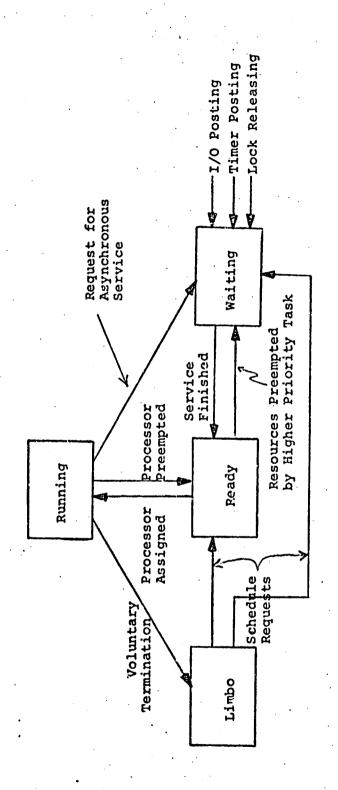

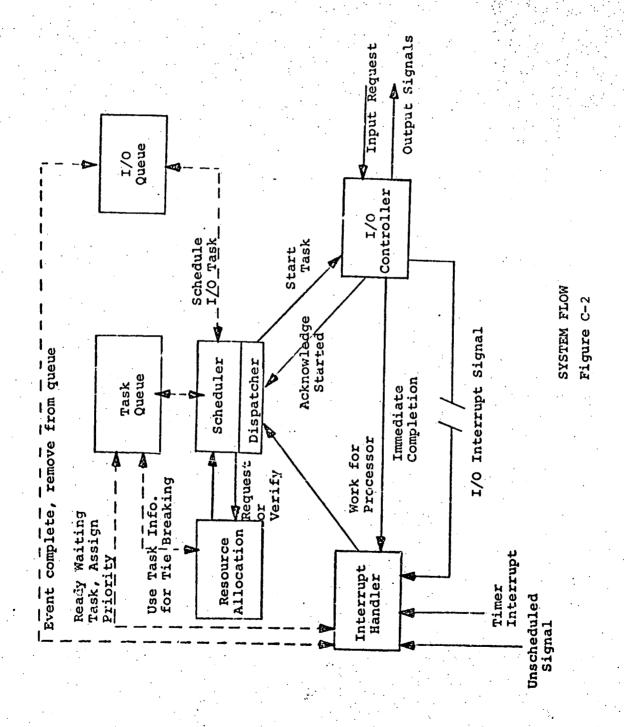

| Appen | dix C  | Shuttle Software Structure and Organization                                                                                                                                                                                | 149                             |

|       | C.1    | Introduction                                                                                                                                                                                                               | 149                             |

| •     | C.2    | Overview of Shuttle Software                                                                                                                                                                                               | 149                             |

|       | C.3    | Synchronous Control Structure                                                                                                                                                                                              | 151                             |

|       | ·<br>· | <pre>C.3.1 Description of Synchronous Operation C.3.2 Advantages and Disadvantages of a</pre>                                                                                                                              | 151<br>152                      |

| ·     | C.4    | Asynchronous Software Structure                                                                                                                                                                                            |                                 |

|       |        |                                                                                                                                                                                                                            | 153                             |

|       |        | C.4.2 Overview of Asynchronous Operation C.4.3 Advantages & Disadvantages of an                                                                                                                                            | 154<br>154                      |

|       |        | Asynchronous Structure                                                                                                                                                                                                     | 155                             |

| C.5 | Computer Interrupts and Their Effect on Organization | 156 |

|-----|------------------------------------------------------|-----|

| C.6 | Sunmary of I/O Operations Versus Software Structures | 1 - |

# List of Figures

|        |      |                                                           | Page N | 0 |

|--------|------|-----------------------------------------------------------|--------|---|

| Figure | 2.1  | Data bus system elements and terminology                  | . 8    |   |

| Figure | 3.1  | Computer configuration with external comparator and voter | 20     |   |

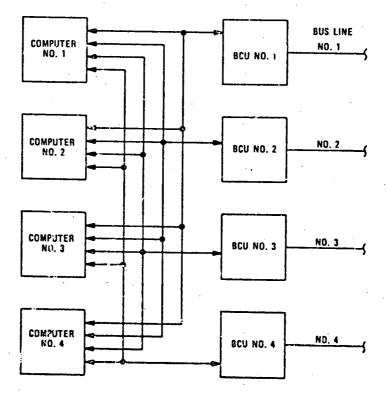

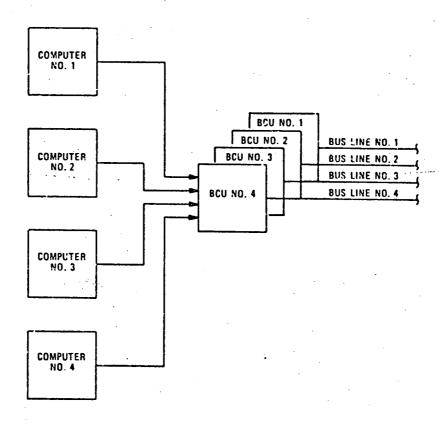

| Figure | 3.2  | single strings without cross connection                   | 25     |   |

| Figure | 3.3  | Cross connection between BCU and bus                      | 27     |   |

| Figure | 3.4  | Cross connection between computer and BCU                 | 27     |   |

| Figure | 3.5  | Quad redundant BCU configuration                          | 29     |   |

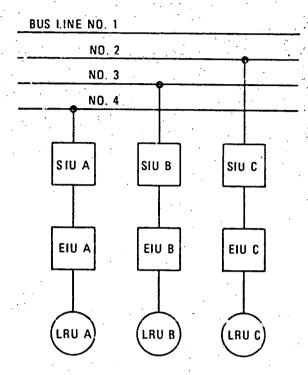

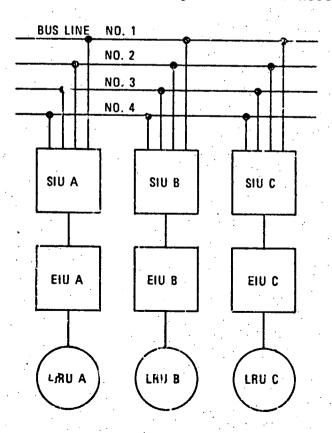

| Figure | 3.6  | Single string no cross connection                         | 31     |   |

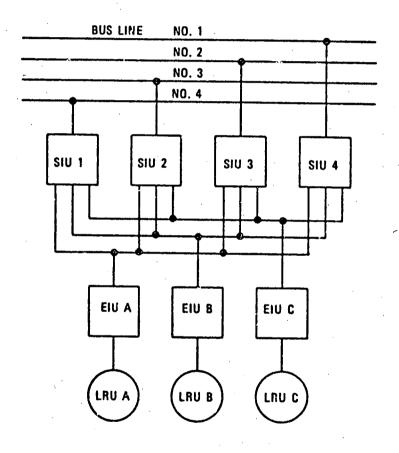

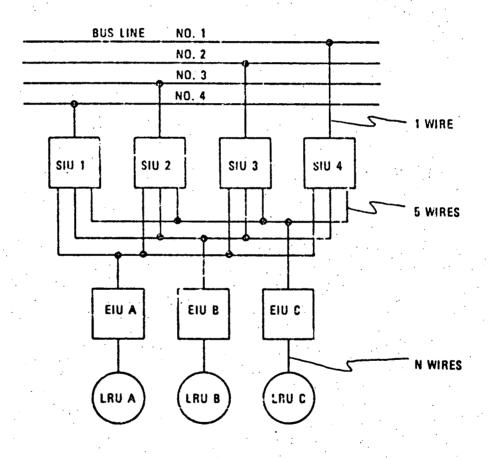

| Figure | 3.7  | Cross connection between SIU and bus                      | 31     |   |

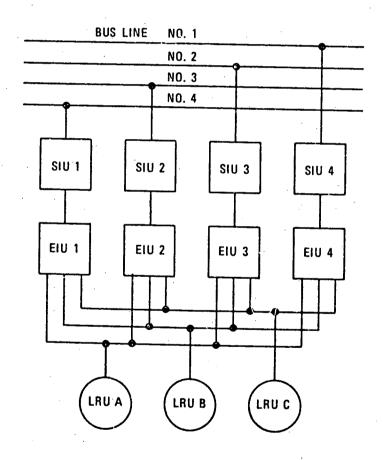

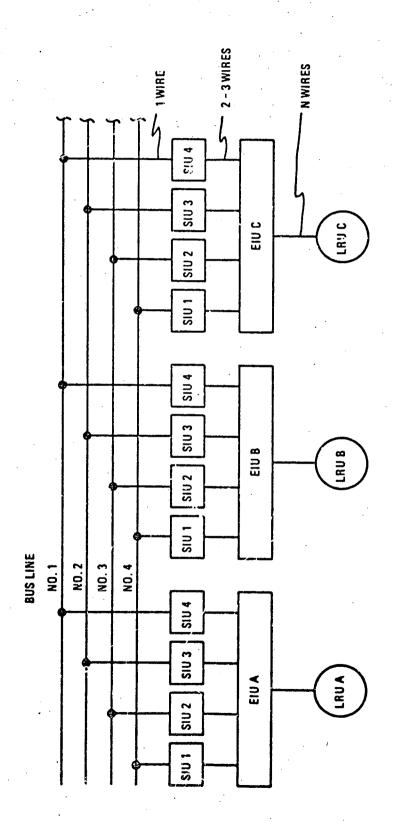

| Figure | 3.8  | Cross connection between SIU and EIU                      | 33     |   |

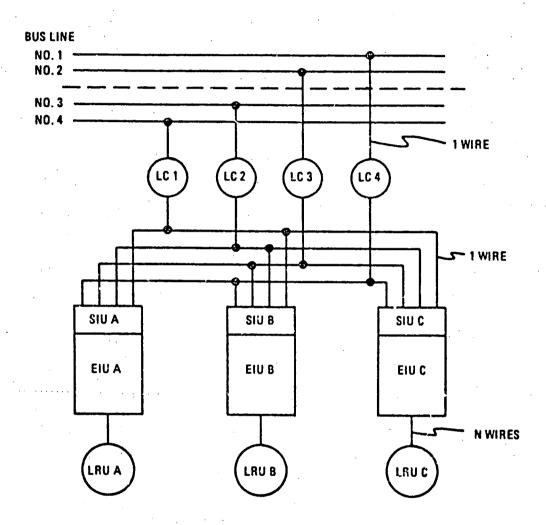

| Figure | 3.9  | Cross connection between EIU and LRU                      | 35     |   |

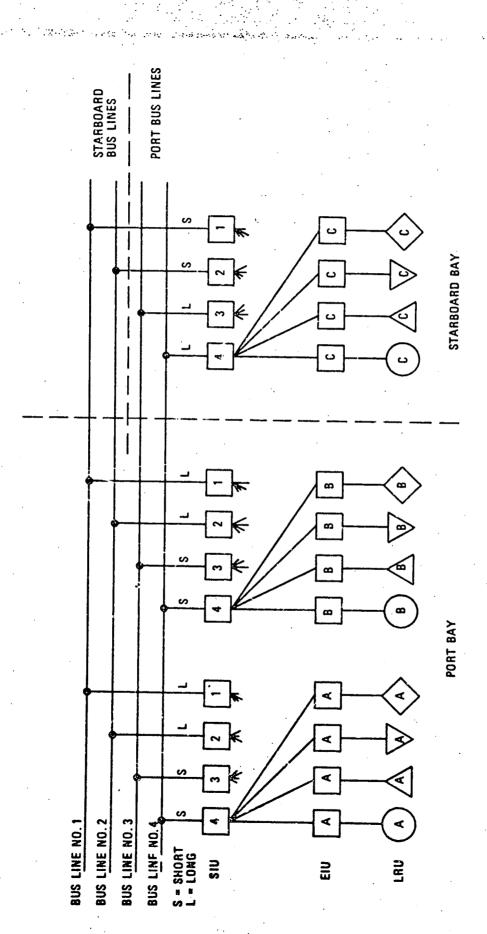

| Figure | 3.10 | Bay oriented configuration                                | 36     |   |

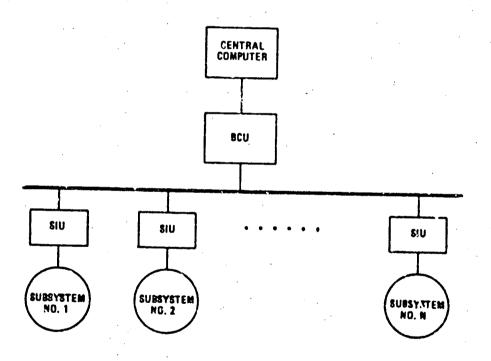

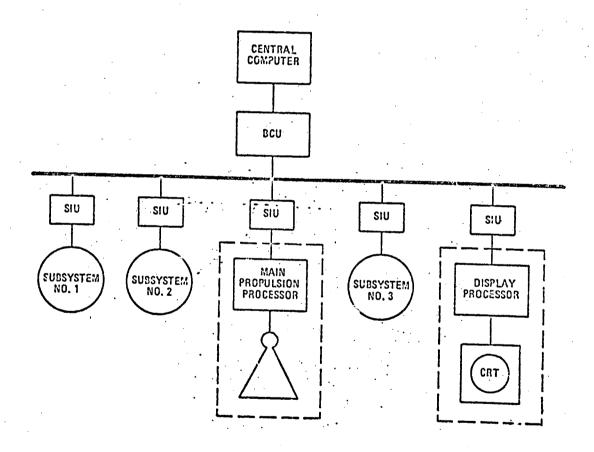

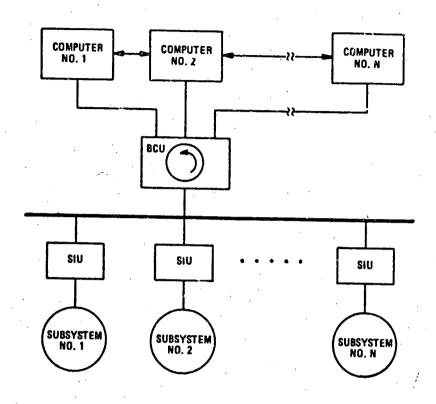

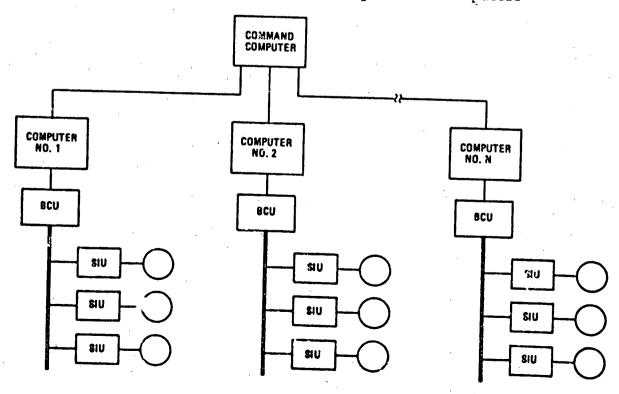

| Figure | 3.11 | Central computer control                                  | 39     |   |

| Figure | 3.12 | Central bus control with distributed processing           | 41     |   |

| Figure | 3.13 | Bus control by several computers                          | 43     |   |

| Figure | 3.14 | Distributed computers and multiple buses                  | 43     |   |

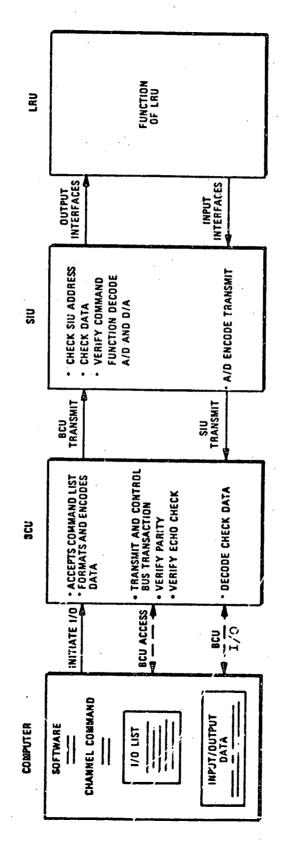

| Figure | 4.1  | Basic functions during a bus transaction                  | 55     |   |

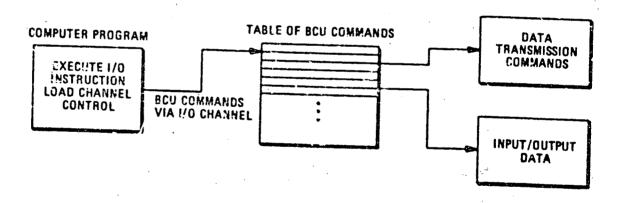

| Figure | 4.2  | Computer to BCU I/O compand operation                     | 64     |   |

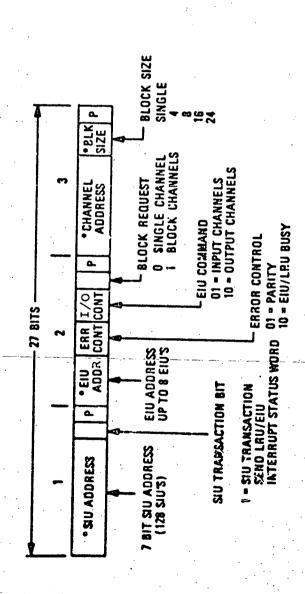

| Figure | 4.3  | Representative bus command message organization           | 71     |   |

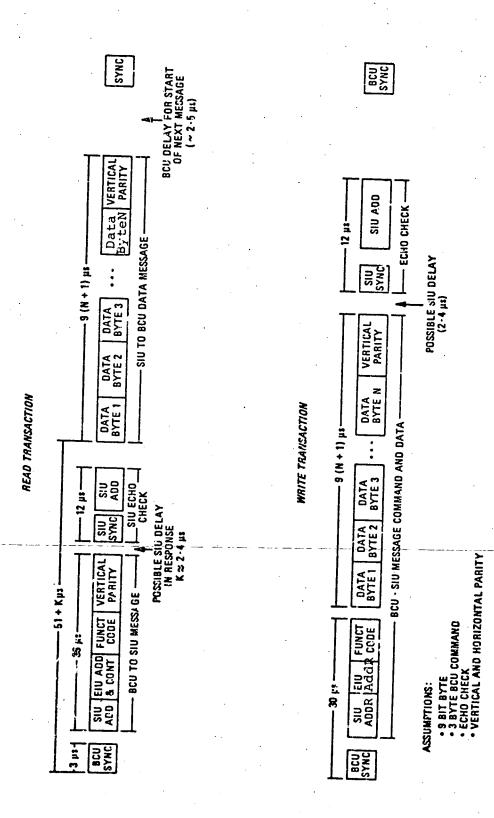

| Figure | 4.4  | Sample read/write transactions                            | 73     |   |

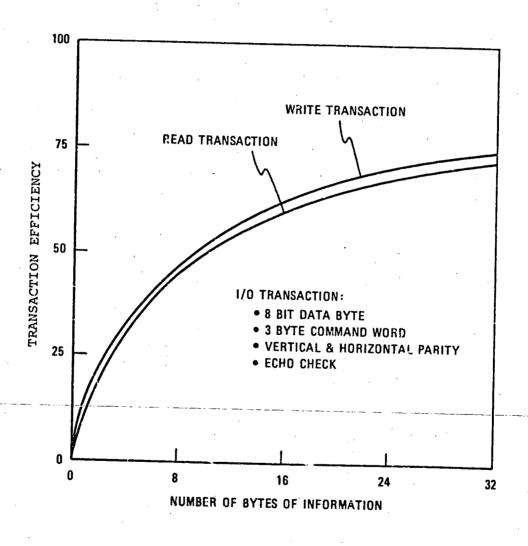

| Figure | 4.5  | Bus I/O transaction efficiency                            | 75     |   |

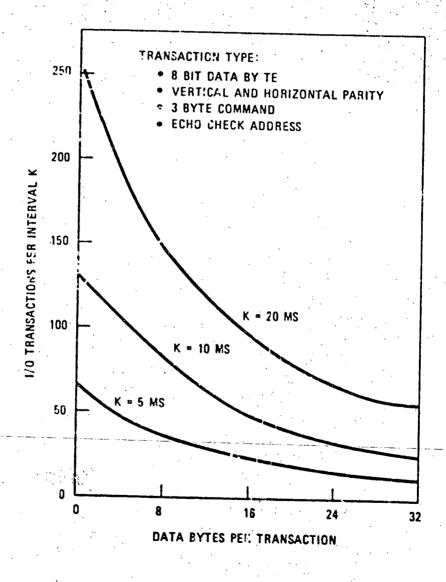

| Figure 4.6 | Frequency of I/O transactions versus number of data bytes                            | 76    |

|------------|--------------------------------------------------------------------------------------|-------|

| Figure 6.1 | Modulation waveforms                                                                 | 94    |

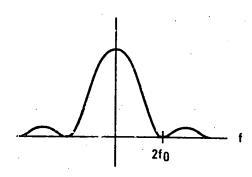

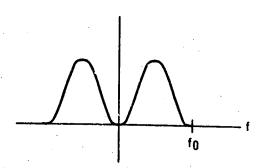

| Figure 6.2 | Modulation energy spectra                                                            | 97    |

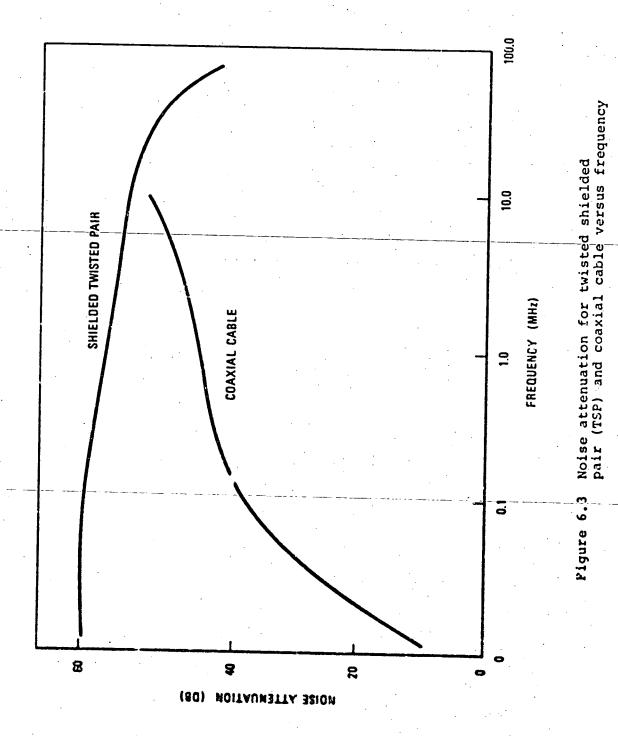

| Figure 6.3 | Noise attenuation for twisted shielded pair (TSP) and coaxial cable versus frequency | 102   |

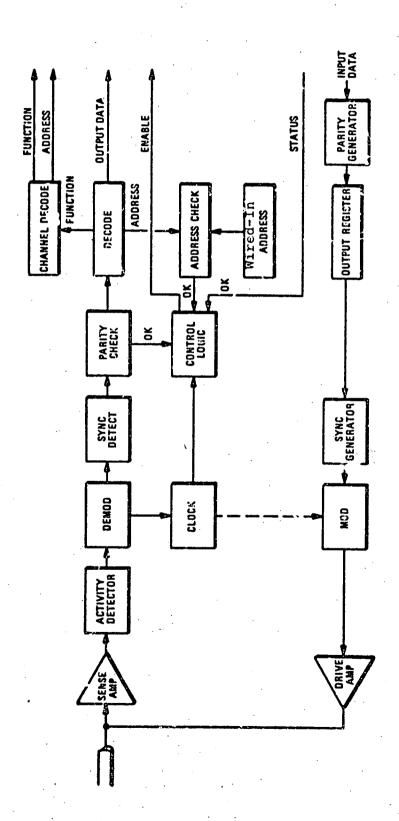

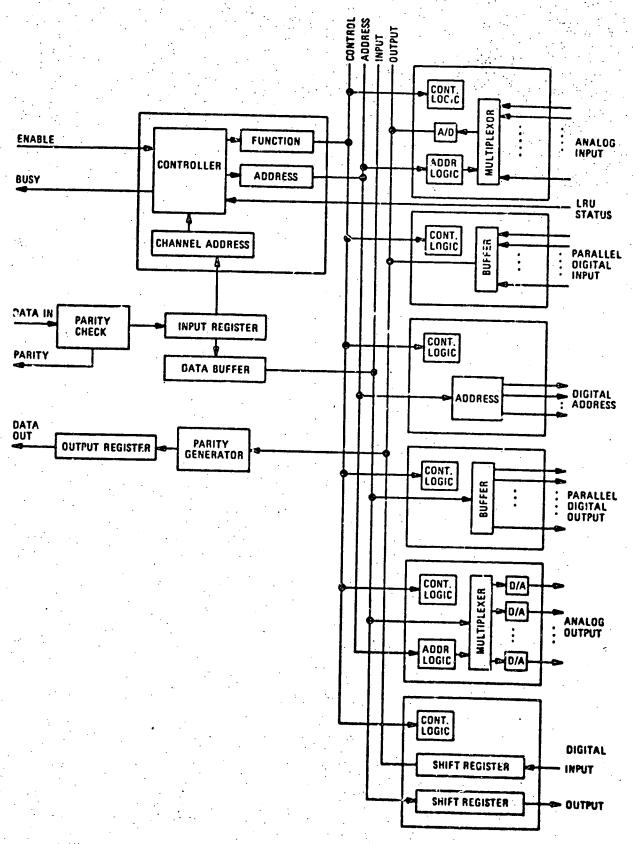

| Figure 7.1 | Standard bus interface functions                                                     | 120   |

| Figure 7.2 | Electronic interface functions                                                       | 122   |

| Figure 7.3 | SIU to EIU cross connection complexity                                               | 124   |

| Figure 7.4 | Cross connection at bus via separate SIU                                             | 126   |

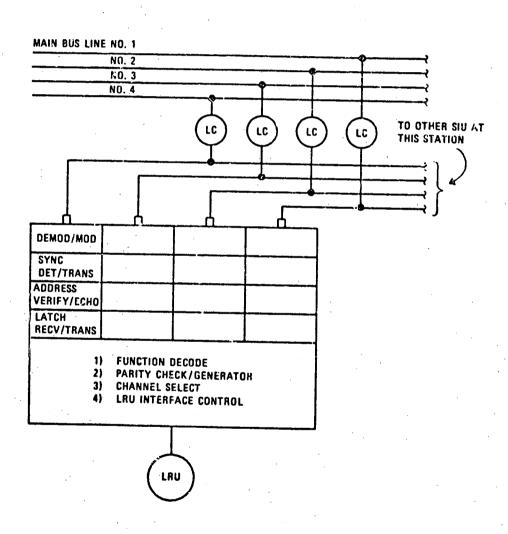

| Figure 7.5 | Cross connection at bus via line couplers                                            | 128   |

| Figure 7.6 | Recommended SIU/EIU terminal organization                                            | . 131 |

| Figure A.1 | Simple and cross connected configurations                                            | 136   |

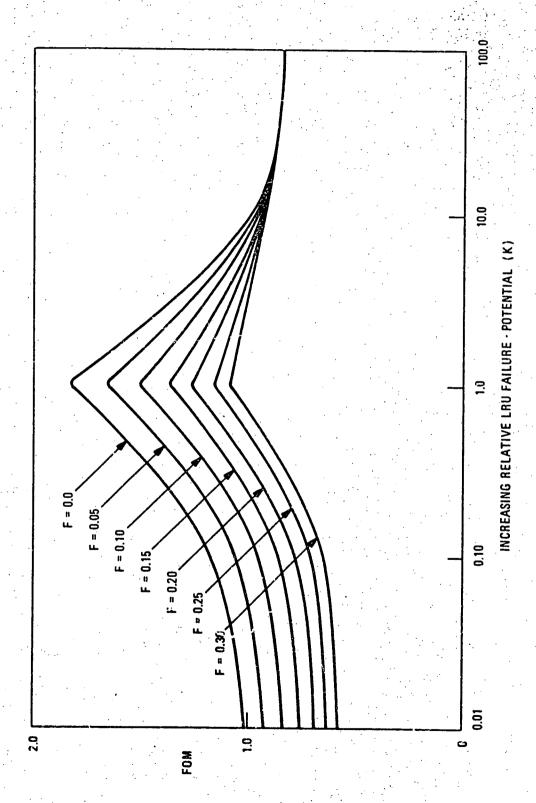

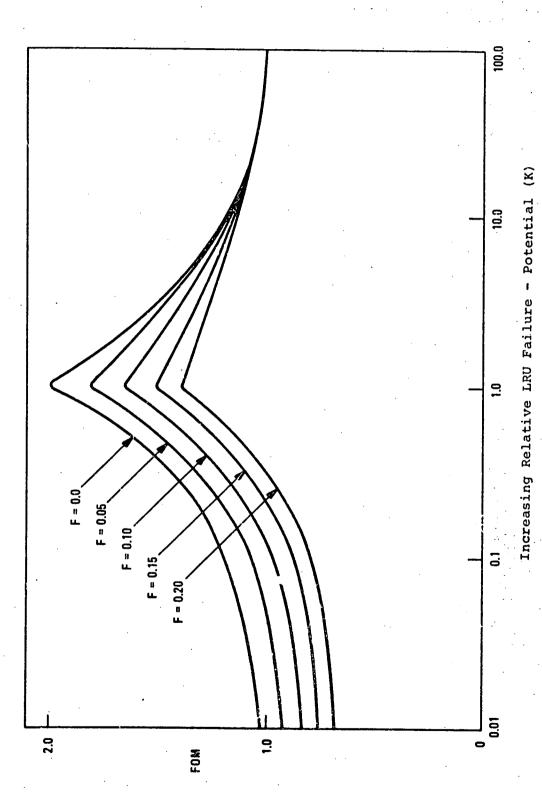

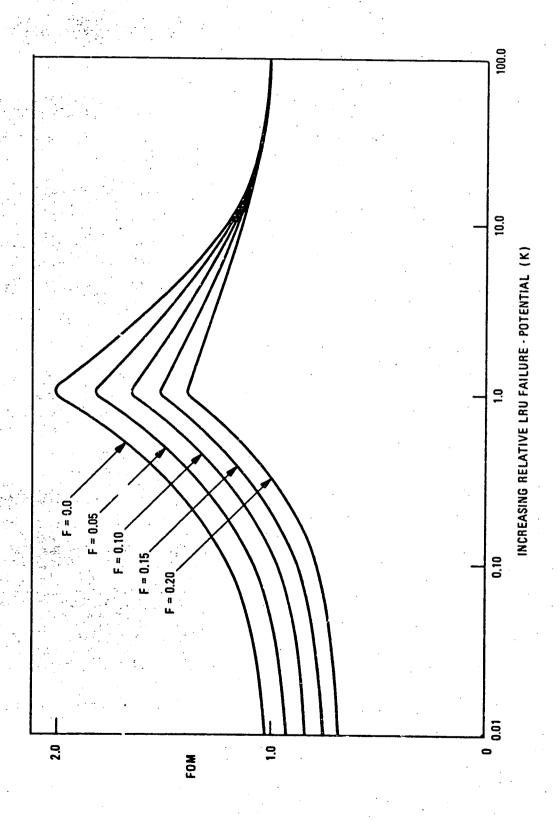

| Figure A.2 | Figure of merit $(P(A)/P(B))$ for $P_c = 10^{-1}$                                    | 139   |

| Figure A.3 | Figure of merit $(P(A)/P(B))$ for $P_S = 10^{-4}$                                    | 140   |

| Figure A.4 | Figure of merit $(P(A)/(PB))$ for $P_c = 10^{-8}$                                    | 141   |

| Figure B.1 | Control sequence for range measurement                                               | 1.45  |

| Figure B.2 | Control sequence for range and range rate measurement                                | 146   |

| Figure C.1 | Task States                                                                          | 158   |

| Figure C.2 | System Flow                                                                          | 150   |

lakens ib

### Chapter 1

#### Introduction

## 1.1 Background to the Study

Design concepts for the next generation of manned space vehicles have been formulated over the last few years and are currently being evaluated to establish specifications for the vehicles, their subsystems and the operational procedures. Common to all the proposed concepts has been an integrated approach to the avionics system, in which all subsystems communicate with, and are coordinated and controlled by the onboard computer system. A shared data bus has been proposed as the common communication link between subsystems and the computer(s).

This study has been concerned with the major factors that influence the design of a data bus for the avionics system of the proposed NASA Space Shuttle. Although the various design approaches to the Shuttle data bus developed to date have differed in many aspects, all recommend the concept of a multiply redundant data bus, a data bus control unit, and a bus interface unit for connecting the avionics subsystems to the common bus. Designs for the bus interface unit have stressed commonality and standardization, because a standard interface unit is estimated to minimize the number of types and the complexity of hardware and vendor interfaces required for each subsystem. Key issues in the design of the bus system are: the functions and role of the interface unit as a part of the bus system, error detection and recovery, redundancy, and bus control philosophy. Since the interface unit is an integral part of the data bus system and cannot be viewed as a "stand alone" element, its definition and design must be considered with respect to the total approach to the bus system design.

#### 1.2 Objectives of the Study

The central effort has been to identify those factors that form the major design drivers for the bus system, and to define the functional interfaces between the data bus, the bus control unit, and a standard bus interface unit. It was not the objective of this effort to determine the specific requirements for, nor to develop a detailed design of the total data bus system. was to review already defined requirements and identify those key design features of the bus that affect the nature of the computer-to-subsystem communication and consequently, the specification of the standard interface unit. Although this study analyzed the communications between the computer and standard interface unit, it did not include detailed evaluation of the bus control unit design, nor the detailed design of the standard interface unit-to-subsystem interface. The objective of this study was to analyze the various approaches to an integrated Shuttle avionics organization, and to make recommendations on general characteristics of the data bus system with emphasis on the definition and functional specification of a standard data bus interface unit.

#### 1.3 Approach to the Study

Since the scope of this study did not include a derivation of the primary performance and operational requirements for the Shuttle data bus, initial reviews of Shuttle data requirements and existing studies of proposed data bus designs were undertaken. It was intended to gather information on the various approaches such as design objectives and functional requirements; elements of the bus system and their functions; bus control method; configuration management technique; number of communication paths; command format; error detection and recovery scheme; modulation technique; physical considerations; and redundancy interfacing. Some difficulty was encountered in obtaining this information in sufficient quantity and detail. This was because of the preliminary nature of the studies, the continually changing requirements, and often because the desired information was proprietary in nature.

It was realized early in the study that in order to define the functions of the elements of the data bus it was necessary to evaluate a number of higher level aspects of data bus design. A significant effort was expended in analyzing the problems and possible solutions associated with the following areas:

- a) Computer configuration. The communication of data and control over the data bus was found to be greatly influenced by the configuration of the control computer(s) with respect to the data bus.

- b) Failure tolerance and reliability. The effect of the Shuttle failure tolerance criterion on the degree of redundancy in the data bus system, the techniques for the detection of failures and eventual reconfiguration of the bus were found to impact the design of the bus elements directly.

- c) Data bus management. Several data bus control techniques were analyzed for relevance to the Shuttle. The type of control was found to impact the nature of the computer I/O with the bus, and the design of the standard interface unit.

The definition of a functional specification for a standard interface unit should only be made when a comprehensive list of requirements for it is known. Because of the early stage of development of the Shuttle vehicle concept this level of information was not available. The various designs under consideration at the beginning of this study were based on different (and changing) requirements and ground rules. It was consequently difficult to evaluate several design approaches on a common basis.

In the absence of a specific set of requirements for the Shuttic data bus it became apparent that no single approach to a design stood out as a clear candidate for implementation. A general impression was gained that almost any suggested approach could be made to do the job. Some criteria for evaluation had to be established in order to arrive at a set of specific recommendations. Chapter 2 provides a summary of the basic requirements, ground rules, and assumptions that this study used as a foundation. The evaluation and recommendations presented in Chapter 7 were guided by two basic ground rules, namely: 1) choose the simpler approach, and 2) choose the approach that solves one problem at a time, wherever the requirements or assumptions provided no clear decision path.

Finally, one other conclusion was reached early in the study. It was that the implementational details of a data bus design such as technology, transmission media, modulation techniques, etc. are of significantly less importance than the higher level questions above. This was reflected in the amount of effort apportioned to this aspect of the problem.

### 1.4 Overview of the Report

This report is divided into seven chapters. Chapters 3, 4, 5, and 6 are presented in no particular logical order or degree of importance of their subject matters.

- a) Chapter 2 lists the requirements for the Shuttle data bus system that were adopted for the purpose of this study, and gives reasons for the less substantiated assumptions that were made.

- b) Chapter 3 provides a discussion of the impact on data bus complexity and management difficulty of the assumed FO-FO-FS failure criterion. Various configurations for interconnecting computers and bus control unit, buses, and interface units are reviewed.

- c) Chapter 4 presents a detailed appraisal of the problems of providing command, control, and data acquisition over a common data bus. Bus access methods, data formats and bus traffic are analyzed.

- d) Chapter 5 reviews a variety of error control techniques. Error coding, transmission feedback, retransmission, and voting are included in the discussion.

- c) Chapter 6 gives a brief treatment of selected hardware problem areas. Modulation techniques, transmission media, coupling and synchronization are discussed.

- f) Chapter 7 reviews the material of the previous chapters and makes specific recommendations in the area of bus control, and the functions of a standard interface unit.

## 1.5 Summary of Recommendations

The recommendations fall into two categories:

- a) those associated with the general problems of command, control, and data acquisition by a common data bus in an integrated avionics system;

- b) the definition of the functional organization of a standard data bus interface unit.

The major points are very briefly summarized in the following paragraphs. For definitions of the terms used, and for further clarification of the recommendations, reference should be made to chapters 2 and 7.

## 1.5.1 Bus Control Summary Recommendations

- a) One authority, i.e. the computer/BCU, should control all commands and data acquisition via the data bus. Any other computer must be interfaced to the bus via a standard interface unit, and must be regarded as any other subsystem.

- b) The computer should initiate and control all bus communications. Control should be by the command/response address technique. No remote terminal may determine its own need to access the bus. Each terminal will respond only to the computer/BCU. A possible waiver of this rule may be made in the case of recording, telemetry, or display equipment, but a non-standard interface unit is then required.

- c) The following error control transmission policy is recommended:

- path verification via feedback transmission by each SIU of at least its address bits upon being accessed by the BCU. No verification of echo check by the LCU is recommended prior to the release of the data to the LRU by the terminal.

- 2) Message verification at the terminal and the BCU by horizontal and vertical parity bits. Message verification at the terminal is required before feedback of address echo.

- 3) Error correction by re-transmission or re-request of message by the BCU.

- 4) Higher security for "critical" commands to be achieved outside of the bus by software controlled multiple transmission of message; successful receipt to be determined by the subsystem.

- d) A byte-serial data transmission is recommended.

The data byte size should be a submultiple of the computer memory word/byte length. The bus command byte should be determined by the nature of the bus traffic, when more exactly known.

- e) A variable length message format with a limit of 32 bytes is recommended. A 2-bit field in the control format is sufficient to specify a 1,4, 8 or 32 byte data block.

- f) A "busy" indication by the terminal is recommended to allow for terminal and LRU latency, and as a mechanism for expanded terminal capabilities.

# 1.5.2 Recommendation of Standard Interface Unit Organization

- a) The communication of data to and from the subsystem should be the interface unit's prime design consideration. Additional functions may be added later, but must abide by the constraints of the bus control structure and data formats.

- b) A standard interface with the bus is recommended for all terminals. For the subsystem interface a fixed maximum of 512 electronic interface channels is recommended, in order to size the channel address field. A maximum of 16 channels each of analog, parallel digital and serial digital input and output signals is suggested as a standard electronic interface, with modular expansion from 0 to 16 to suit the requirements of a particular equipment. An "invalid channel address" signal is recommended to indicate a less than maximum interface implementation. (This standard interface cannot be made a recommendation of the study, since specific equipment requirements have not been determined to date.)

- c) The 512 channels could be assigned differently than above, but a non-standard electronic interface would be the result. A modular internal structure could alleviate the problem of terminal diversity.

- d) A unified terminal with combined SIU and EIU facilities is recommended, although a separate input channel for each bus line should be provided to the point of address comparison.

- e) Redundancy interfacing should be performed at the bus-toterminal interface by special line coup.ing elements, which provide 4-to-many and many-to-4 interfacing.

- f) Line conditioning, signal amplification and noise discrimination should be provided. They may be conveniently accommodated in the line coupler.

#### Chapter 2

Space Shuttle Data Bus Definitions and Ground Rules

#### 2.1 Introduction

The definition of a standard interface unit for the Shuttle data bus depends directly on, and is constrained by, such factors as: the avionics configuration requirements, avionics subsystem and equipment data requirements, redundancy techniques and centralization versus decentralization of functions. The objective and the scope of this study did not include a detailed analysis of the avionics system requirements. These were assumed to be as formulated and derived by others.

## 2.2 Data Bus Definition and Terminology

#### 2.2.1 Definition

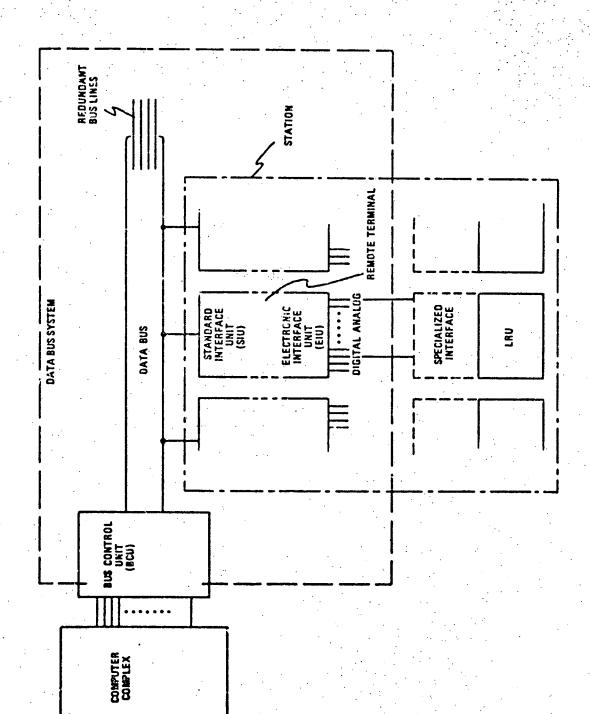

The space Shuttle data bus system is the principal medium of communication between components of the integrated avionic system and the computer complex. It is a multiply redundant, common, shared interface to flight electronics and mechanical equipment providing remote acquisition and distribution of commands, data and other information. The Shuttle data bus system illustrated in Figure 2.1 is composed of three major elements:

- a) a bus control unit,

- b) a redundant set of transmission lines, and

- c) a number of remote terminals.

Figure 2.1 Data bus system elements and terminology

#### 2.2.2 Terminology

The nomenclature utilized throughout the report attempts to utilize, as much as possible, existing terminology and acronyms rather than defining new ones. However, to avoid confusion and preconceived associations the following definitions are provided.

- The data bus. The data bus is composed of a set of redundant bus lines. Each bus line is a single communication channel, capable of two-way transmission of serial digital information between several remote terminals and the bus control unit. Physically a bus line may be a ingle coaxial cable, or balanced line such as a twisted shielded pair, on which information is transmitted by time or frequency division multiplexing.

- b) BCU ("us Control Unit). The BCU is the control element of the data bus system. It provides the primary interface of the bus system to the computer complex. It is the primary I/O peripheral to the computer complex, containing a parallel interface with control and shared access to the computer memory. The functions of the BCU are discussed in more detail in Chapters 4 and 7.

- c) Terminal. The terminal is a remote unit which interfaces between a bus line and a remote avionics equipment. A terminal is addressable by the computer/BCU for the input or output of data to the equipment. It consists of two basic elements: a standard interface unit (SIU) and an electronic interface unit (EIU), which may or may not be physically separated.

- d) Standard Interface Unit (SIU). The SIU is that part of a terminal associated with the functions necessary to interface with the bus. It contains line termination, signal modulation and demodulation, transmitter and receiver control, and terminal address decoding logic.

- e) Electronic Interface Unit (EIU). The EIU is that part of a terminal associated with the functions necessary to interface avionics equipment. The EIU inputs and outputs information to a number of analog and digital 1/0 interfaces in response to I/O commands. Data and commands received or acquired by the EIU are routed through the SIU portion of the terminal for communication on the bus.

- f) Lowest Replaceable Unit (LRU). In this study LRU is defined as the smallest piece of avicnics equipment recognized and addressed by the bus system. More than one LRU may be connected to an EIU. The following could all be categorized as LRU's: a single beacon, a VHF transceiver, an inertial measuring unit, a remote processing computer.

- g) Station. A station is defined as a collection of terminals associated with a functional avionics subsystem.

- h) Subsystem. A subsystem is defined as a collection of LRU's which constitutes a function recognized within the integrated avionics hierarchy. Examples of subsystems are the reaction control system (RCS), the electrical power system (EPS), the environmental control system (ECS), the inertial subsystem. A subsystem may be geographically distributed about the vehicle.

# 2.3 Review of Shuttle Data Bus Requirements and Ground Rule

Several organizations, including the Phase B contractors, have conducted analyses of data bus and other Shuttle system requirements. The results of many of these studies have been published for the NASA Manned Spacecraft Center. A review of the information made available during the course of this study was conducted. Several problems arose in obtaining a common set of data and communication requirements for the bus, principally due to the continually changing nature of Shuttle operational requirements, and the differences in system design approaches and objectives. A summary of the major requirements of the Shuttle obtained from this review are listed below. Although there are many detailed system requirements for the Shuttle avionics system, only those pertinent to the functional specification of interface unit were used.

a) The study has assumed that the Shuttle data bus system meets the failure tolerance requirement specified for all electronic subsystems; namely, that it shall "fail operational" after the failure of two most critical components, and "fail safe" after the third failure. Accordingly, the failure tolerance specification has been interpreted as requiring quadruply redundant bus lines. A more detailed interpretation of this failure tolerance requirement is presented in Chapter 3.

Although this failure tolerance requirement has been assumed and not analyzed or justified in detail, it is clearly of significant impact to the organization of the bus elements, in particular the remote terminal. The necessity of interconnecting an avionic subsystem of m-level redundancy with a quad redundant bus has been a key design driver in formulating the SIU requirements.

b) The concept of a central shared data bus with standard remote interfaces to avionics equipment is assumed to be the most cost effective concept for both the Shuttle orbiter and booster vehicles.

The college to the last tracks and well representations and

- c) The primary function of the data bus system is to provide a communication path between the avionics equipment and the prime computer complex. No general requirement for terminal to terminal communication which cannot, or need not be routed through the computer complex has been identified.

- d) Subsystem interfaces. The data bus must provide a capability of interfacing to redundant electronic subsystems. The exact number and type of such subsystems has been changing as the operational requirements evolve. The representative list provided below was assumed to indicate the scale of the system.

- Primary propulsion subsystem: this system consists of two orbital insertion engines and one orbital maneuvering engine.

- 2) Reaction control subsystem: at least 20 RCS jets located in the nose, wings and tail for effecting rotation and translation in space.

- Hydraulic system: hydraulic power generation, distribution, control, and conversion of mechanical energy. It consists of supply lines, gimbals, pumps, aerodynamic surfaces, flaps, wheel controls, etc.

- 4) Electrical power generation and distribution system: fuel cells and battery, and the auxiliary power units located throughout the Shuttle.

- 5) Navigation aids/air data: a collection of equipment providing navigation and landing capabilities (ALS, radar altimeter, TACAN, DME, etc.).

- 6) Environmental control system: the environmental control system provides temperature, pressure, and humidity control of equipment, equipment bays, and personnel compartments.

- 7) Cryogenic system: contains the hydrogen and oxygen for the primary propulsion, the reaction control system, the fuel cells and the auxiliary power units.

- 8) Displays and controls: this system is assumed to have local processing capability and accepts dynamic data through the bus for updating of display parameters.

- 9) Telecommunication: this system consists of various transmitters and receivers including S-band, C-band, VHF, telemetry encoder, EVA communications, air traffic control communications, etc.

- 10) Guidance, navigation and control: this subsystem is composed of elements necessary to control, stabilize and navigate the Shuttle vehicle during all phases of the mission. It interfaces to the reaction control system, jet engines, aerodynamic control surfaces, and landing gear, etc. It has access to sensors which include the inertial subsystem, horizon and star trackers, approach landing aids, rendezvous radar, radar altimeter, etc.

Although this list of subsystems may not be complete for the final organization of the avionics system it is meant to be representative. It is estimated that approximately 150 to 250 LRU's are associated with the subsystems listed above.

- e) Data requirements. The following is a summary of the data requirements abstracted from the various studies of Phase B contractors.

- 1) Speed. Peak load estimates of data rate for both the Shuttle and orbiter have ranged between 100,000 and 250,000 bits per second, including overhead. Considering an average overhead of approximately 50% for each bus transaction and allowing for a minimum of 100% expansion to the maximum speed, a capability of 100 bits per second has been assumed to be an adequate requirement. This speed should allow the computer to acquire data at a rate of approximately 10,000 average transactions per second.

- 2) Measurements. Estimates have ranged between 4000 and 6500 unique data points to be sampled from the total complement of avionics equipment by the central computer. Data types include:

digital parallel digital serial analog discrete The majority of these data points are measurements input to the computer, and are estimated at approximately 60% to 70% of the traffic on the data bus.

- 3) Response time/sampling frequency. The maximum sampling frequency of measurements is estimated at fifty samples per second. The average sampling frequency for status information is between 2 and 5 samples per second. Very little information was made available on response requirements and load distribution of subsystems.

- 4) Number of terminals. The number of terminals estimated varies considerably depending upon the degree of redundancy, interfacing policy and the design of the terminal. The number of independently addressable terminals is assumed to be somewhere between 50 and 200.

- f) Physical requirements. Each bus line was assumed to be physically separated aboard the vehicle for reasons of reliability. It was assumed that bus lines will be run down each side of the vehicle, and that the bus will be capable of transmitting over distances of 300 to 500 feet. It is assumed that the equipment will be located in several equipment bays located throughout the vehicle. Terminals must be capable of being separated from the bus by distances of up to 50 feet.

## PRECEDING PAGE BLANK NOT FILMED

#### Chapter 3

Reliability, Redundancy and Organization

#### 3.1 Definition of Failure Tolerance

Before a detailed evaluation of the Shuttle data bus can be undertaken it is important to consider the requirement for failure tolerance, since it is this factor that introduces the greatest complexity into an integrated Shuttle avionics system. As usually stated, the avionics system must remain fully operational after the first and second failures, and must fail in a safe manner after the third. In a practical system failure tolerance implies that each major element in the system must possess internal functional redundancy, and a highly effective technique for failure detection to allow quick reconfiguration in the event of a failure.

The high level of redundancy that is required for a multiple failure criterion allows application of voting and comparison techniques to systems which generate output data; for example, the computer, and sensors such as the IMU, radar, pressure and temperature transducers. Voting of passive elements such as actuators requires the feedback of information which indicates the element's response to the command.

The penalty that must be paid for voting as an approach to failure protection is that all redundant copies of a given piece of equipment must be powered up, functional, and operating identically.

The level of redundancy and the technique of failure detection depend on the interpretation of the failure criterion. The greatest difficulty attaches to the definition of the "failed safe" condition. Two interpretations are possible:

a) To treat the "failed safe" conditions as "graceful degradation". In this concept the failure results in a reduced system capability which, nevertheless, retains certain functions critical to the safety of the crew and the vehicle. The security of these functions must, therefore, be treated as part of the system design specification. This approach allows the greatest economy of equipment, but suffers from a difficulty of definition and of sophistication of system design, especially in the area of software.

b) To treate the "failed safe" condition as "operational". This obviates the need to specify a diminished set of critical functions, and avoids the difficulty of their implementation. It suffers, however, from the need for full redundancy of equipment to allow performance in an undegraded fashion after the failure to the "safe" condition.

The second approach has been assumed during this study, because the detailed definitions required for graceful degradation cannot be undertaken at this early stage of Shuttle development.

A clarification of the "operational" condition prior to the "failed safe" is necessary to establish the degree of redundancy required by the second definition above.

- a) It may be defined as a fully operational condition in which there will be a 100% certainty of failure detection, with a near-instantaneous reconfiguration.

- b) It may be less strictly interpreted, as a fully operational state with a small but finite probability that certain failure modes may pass undetected, or remain unresolved, and that a small, but finite time may be required to recover from a failure transient.

The first inverpretation virtually demands that sufficient redundancy among the unfailed elements remains for majority voting to take place even in the penultimate failure state. Majority voting provides almost perfect error detection when errors occur relatively infrequently in an uncorrelated random fashion. An added attraction is the capability for immediate error correction upon determination of the dissenting vote. The penalty is that at least triple redundancy is required prior to the failure to the safe condition. For the full FO-FO-FS tolerance this implies that five levels of redundancy must initially be available.

The second interpretation above allows the requirements of the failure detection technique to be relaxed, and a lower degree of redundancy to be used. At least dual redundancy is required by the "operational" definition of the "failed safe" state, and allows comparison to be used to trap the final failure. For the failure characteristics described above comparison provides for almost certain detection. Consequently, FO-FO-FS tolerance can be provided by four levels of redundancy, rather than five. Comparison, however, does not provide an indication of which of the redundant signals or equipment has failed. A supplementary metnod must be employed to identify and isolate the failure:

a) Self-diagnosis. In the case of computers, a degree of assurance can be provided by special self-test software which exercises most of the basic operations in the processors, memory, and I/O. However, the volume and complexity of the diagnostic routines required for near certain probability of fault isolation precludes their use in parallel with the operational software. These routines must replace the operational software for as long as it takes to track down the ailing element. During this period the computer can obviously not provide the full complement of capabilities to the system.

For the less "intelligent" systems in the avionics less extensive diagnostics are possible, and in fact, less are needed.

- b) Built-in test equipment (BITE) can be designed into the avionics equipment, to provide measurement data not normally utilized in operation. When a failure is indicated these measurements are sampled, either by the computer in the system, or by special sequencing and comparison circuitry to determine the malfunction. Hardware complexity limits the degree of isolation by BITE.

- c) Functional Testing. The suspected equipment is cycled through a functional sequence of operations of which it is required to be capable by specification, again either by the computer, or by special equipment. This is the least exhaustive technique, but it demands the least amount of diagnostic hardware and software. In conjunction with failure detection by comparison it may provide the most cost effective approach.

It is obvious from the foregoing discussion that a less-than-100% certainty of detection and recovery for the final failure must be included in the definition of the "safe" condition, as must the finite response time to resume an operational status.

## 3.2 Failure Detection and Isolation

hen about the water place

Having discussed the impact of a given failure tolerance criterion on the degree of redundancy in the system, some of the finer points of failure detection and recovery by voting, comparison, and other diagnostics will now be reviewed. In a well designed system, with high signal to noise ratios and a minimal likelihood of widespread or catastrophic failure modes errors will be random, uncorrelated, and infrequent. In this environment comparison of redundant, independently-computed output data provides a near certainty of failure detection. Current estimates are that the Shuttle avionics system will probably be characterized as such a system. Comparison is being proposed for error detection in the Shuttle data bus system in the areas of:

- a) the computers

- b) the data bus

- c) other sensors.

These areas will now be examined in turn.

# 3.2.1 Computer Failure Detection and Recovery

Although the computer operates in a highly involved and complex fashion, it is deterministic and exact: a given operation will always yield the same result if repeated with the same input data. The major problem for computer comparison in a real time environment such as the Shuttle data bus is the synchronization of computations which involve time dependent functions and input data. Synchronization can be achieved by:

- a) central control of the computer clocks;

- b) careful gating and distribution of input data;

- c) strict identity of hardware and software operation.

A comparator/voter mechanism adds to the hardware and software complexity. It also incurs operational delays, because time is required:

- a) to wait for synchronization of clock and data;

- b) to perform the comparison;

- c) to decide on the results of comparison;

- d) to take corrective action.

To minimize overhead, the comparison should, therefore, take place at a fairly high level of operation, rather than instruction by instruction. Comparing the operation of the computers at the point where they influence their environment, i.e., at the computer/bus interface, is a logical choice, provided that outputs occur frequently enough.

Comparison and voting can be done in varying degrees, with varying hardware and software complexity:

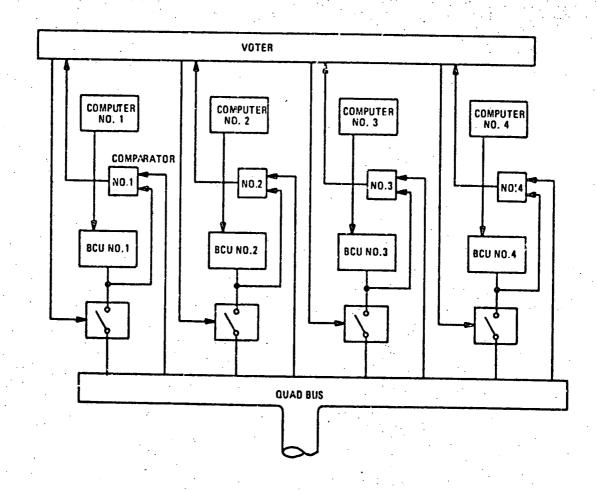

- a) majority voting on the output data of three or more computers, reducing to comparison with diagnostics when less than three good computers remain. The bus receives only the data derived from the majority vote. Failure isolation and correction is automatic as part of the voting process. The complex voter that this requires must be sufficiently redundant and possess adequate error protection to meet the failure telerance criterion, because it is an in-line element in the data bus.

- Majority voting on the indications of health, but not on the output data. One computer is selected to be "active" and its outputs control the bus directly. The other computers are used as standards to provide independent checks on the operation of the active computer. A voting mechanism decides on the basis of a majority of comparator results whether the active computer is operating correctly. It may also determine which of the inactive computers has developed a failure (see Figure 3.1). In the event of a failure of the active computer one of the others is made active. The voter mechanism may be considerably simpler than the data voter of the previous paragraph, since it only operates on binary values; its response time need only match the reconfiguration dynamics, not the transmission frequency of the bus. Furthermore, since it is not an inline element of the system, it may not have to meet the same stringent failure tolerance requirements. Each comparator can be considered a part of a computer's I/O section and is thus naturally redundant. In fact, the comparison could be performed, by software, internal to each computer.

As a consequence of voting binary, rather than many-valued byte or word data, the simplicity of the second method pays a penalty in the lower inherent certainty of correctly interpreting failure conditions. There is a greater possibility for split vote situations to arise with binary variables, and a greater likelihood of identical multiple failure. However, these conditions will only arise when failures in the comparison and voting logic itself produce erroneous indication of computer health; the lower complexity of this voter will aid the achievement of the necessary reliability.

Figure 3.1 Computer configuration with external comparator and voter

For either voting approach, once less than three good computers remain, reliance must be placed on self-diagnosis to determine the faulty computer. No self-diagnostic technique can be infallible; a disagreement between two computers could yield the following conditions:

- a) one computer determines itself to be faulty, the other finds itself healthy. This is the expected result.

- b) Neither computer detects a malfunction. This may be because the fault was transient, or because it was a borderline case beyond the capability of the diagnostic method.

- c) Both computers detect malfunctions. This event is highly unlikely in the case of uncorrelated random errors, but may easily occur for common mode problems such as physical environmental transients (e.g., power supply and thermal variations).

One insidious possibility for a processing failure that may not be trapped by any of the techniques discussed so far is that of the software error. The software in each of the redundantly operating computers must, for the purpose of comparison and voting, be virtually identical. It is, therefore, inherently non-redundant. A software fault will produce data which, being identically erroneous, will appear to compare correctly. This condition must be classed as a design error which, along with the similar logical hardware fault, must be prevented by careful design and adequate verification, rather than by complicating the system in an effort to make it immune to conceptual errors.

## 3.2.2 Data Bus Error Detection and Recovery

Although there are two causes of failure in the bus system, namely hardware failures and transmission errors, these may not be separable in cause or cure. Usually, the same error detection and recovery procedure handles both. Of the two main approaches, error correction coding or voting on multiple transmission, the first is treated in some detail in Chapter 5 and the second in Appendix A.

The repeated transmission of a message over a single path is a well known form of coding and can be used for error detection (by comparison, requiring all messages to be identical) or error correction (by voting, and accepting the message that is made up of the most often received bits). It is easy to

implement, but as coding systems go, it is relatively inefficient. In order to get a Hamming distance four code for three error detection, the message must be repeated four times. The same error detecting capability can be obtained with many fewer bit; using other coding schemes.

The transmission of the message over multiple separate paths is in many ways similar to the multiple transmission over a single path. It is true that the message is received and verified at the output with less delay than is associated with the sequential transmission scheme, but on an overall basis, there is no improvement in the utilization rate of the available channel capacity. In analyzing the probability of an undetected error, for random independent errors, there is no difference between the two schemes. For errors caused by external influences, such as EMI, the probability of having all of the channels affected in the same way by an external occurrence appears to be quite low, especially if the channels are physically separated. In severe cases, it is possible to offset the multiple transmissions from each other by a small number of bits, so that the same information bit will not be affected on each line. However, the probability of having some number of sequential transmissions over a single channel be altered identically by sequential external occurrences, is of very low probability. Therefore, unless the reduction in throughput rate becomes unacceptable, there appears to be little advantage, from the point of view of error detection and correction, to be derived by parallel transmission. The redundancy of the bus should be determined by the need for hardware failure protection alone.

Voting on multiple transmissions from the computers implies a complexity at the receiving terminal:

- a) storage must be provided to hold each transmission, if sequential;

- b) a majority voter to act on the redundant transmissions is required;

- c) for parallel transmission, a back-up error detection policy is required in the event of hard bus failures since voting is not feasible with less than three good lines;

- d) the results of decisions on transmission validity made at the terminal must be communicated back to the control computer to maintain an up-to-date configuration status. This prevents the use of a pure command/response bus control policy (see Chapter 4).

e) For parallel transmission each terminal must access all buses to perform voting. The catastrophic failure of a terminal could incapacitate the whole bus system. In addition, for physically separated bus lines (e.g., port and starboard cable routing), extra weight is incurred for cross connections.

This complexity discourages the use of transmission voting as an error detection and correction scheme for all communications, since other techniques such as echo checking, described later, offer as much security without the overhead. However, critical communications can be conducted with a higher degree of confidence by repeated serial transmissions. The buffering and voting of these should properly occur outside of the bus, in the particular subsystem involved. It should be noted that in the absence of a comparison mode of SIU operation, it becomes almost imperative that bus transmissions should only occur on one line at a time to avoid the confusion that would result at the subsystem from the receipt of several simultaneous messages. This is especially true for configurations that require only one SIU connection to each bus line.

## 3.2.3 Subsystem Output Voting

The voting of data received over the bus by the computer has less value so far as validating the transmission of the information, since the computer has considerable flexibility in determining correct system operation (error coding, echo checking, etc.) that does not involve the complexity of voting, or multiple transmission by terminals. However, comparison of data from redundant subsystems provides a powerful fault detection and isolation capability which would be difficult to match by other diagnostic techniques (e.g., BITE). capability should, however, have little influence on the design of the bus system: it is more a problem of data management by the software. Each computer in a redundant configuration must be able to access the data from each redundant element of the subsystem, which imposes a constraint on the interconnection of computers, bus lines and terminals. This will be discussed in the next section.

Multiply generated data from transducing subsystems, such as the inertial reference, present other problems for voting in addition to those of time synchronization described earlier. Such data is generally derived from analog quantities and is subject to drift, scale factor errors, etc.

#### 3.3 Redundancy Interfacing

This section will discuss the interconnection of the basic units of the Shuttle data bus system; i.e., the computer, bus control unit, bus, bus interface unit, and subsystem. Although five levels of redundancy could be required to meet the FO-FO-FS criterion, a maximum of four will be assumed in the discussion. It is expected that strict adherence to FO-FO-FS throughout the avionics systems will not be demanded, nor will it, indeed, be practical. It has been assumed for this study that some systems, because of non-criticality or extreme reliability will not be required to demonstrate four-fold redundancy, but will, nevertheless, demand the full failure tolerance from the bus. To interface these to the quad-redundant bus presents a redundancy matching problem; cross connection, or cross-strapping of the different levels becomes necessary. That an overall increase in system reliability may be a by-product of cross-strapping is indicated in Appendix A. Another reason for cross-strapping is to provide a greater flexibility for the application of comparison and voting among the redundant levels, and for the management of system reconfiguration. Finally, in a real Shuttle environment with geographically divided bus lines, cross-strapping prevents a situation in which the left side computers could not run the right side equipment. The question of cross-strapping occurs mainly at the computer/bus and at the bus/subsystem inter-These areas will be examined in turn.

#### 3.3.1 Computer to Bus Interface

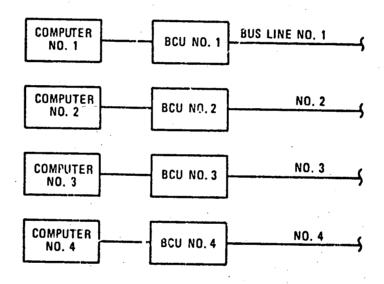

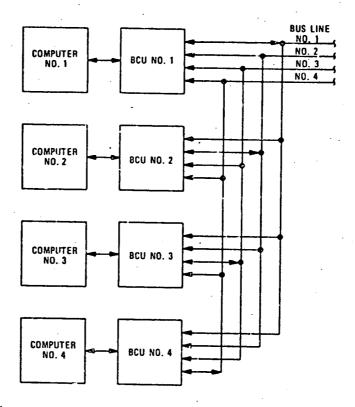

This interface involves the computers, BCU's and the bus lines. Only the expected case of quad redundant computers and four buses will be considered. The several options are illustrated in Figures 3.2 through 3.5 and are now compared in turn.

#### a) Configuration 1 (Figure 3.2)

This is the simple approach of no strapping at all. The computer, BCU and bus constitute a single string unit. A failure of one of the elements in the string fails one entire bus line. Communication of data between computers must be done via the bus terminal or by special purpose cross links between the computers. Error checking of the bus by comparison is impossible at the computer end. Each bus terminal must access all bus lines, which makes the whole bus system vulnerable to a catastrophic terminal failure. The bus terminal is complicated by having to bear the brunt of bus system failure detection and correction, reconfiguration, and status monitoring. If comparison

Figure 3.2 4 single strings without cross connection

10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.000 10.00

or voting of the computers and the BCU's is to be done in this configuration, it must be accomplished by the terminals. Voting of sensor outputs is plainly not possible, even at the terminals. Certain subsystems must have all LRU's powered up and running; e.g., the inertial measurement unit. These subsystems require all the string elements of the bus to be up and running: partial bus operation is not feasible without cross-strapping.

## b) Configuration 2 (Figure 3.3)

In this configuration the computer and BCU are a single string unit: cross-strapping occurs at the BCU/bus line interface, enabling each computer/BCU to access any bus line. The access may consist of either

transmit and receive on one line and receiveonly on the others

or

2) transmit and receive on all.

## Configuration 2 provides:

- the capability for each computer/ECU to monitor the bus line outputs of the others, thereby enabling the comparison/voting of computer performances discussed in Section 3.2.1. Note that this arrangement includes the BCU in the error detection loop.

- 2) The ability to reconfigure the arrangement of active computer/BCU and bus lines in the event of failure. In this configuration it is not possible to transmit onto the bus the majority voted output from the several computer/BCU's, since data for voting is only available after the bus has received the active computer's output. Furthermore, a failure to the active computer/BCU is detected only after the erroneous message has been transmitted into the bus system. Since the terminal in this configuration need not access every bus line, as was necessary in Configuration 1, it has been relieved of the burden of checking on computer operation.

The Control of the Co

Figure 3.3 Cross connection between BCU and bus

Figure 3.4 Cross connection between computer and BCU

#### c) Configuration 3 (Figure 3.4)

This is an alternate cross-strapping arrangement which, as far as the bus lines and the terminals are concerned, has similar characteristics to that of Configuration 2. However, each BCU/bus line is now the single string element, rather than the computer/BCU. Cross-strapping occurs between the computers, which makes possible the parallel transfer of data with a great increase in the speed of comparison. This may allow comparison to be performed before erroneous data is transmitted to the bus, and a measure of majority output voting, even with only one active computer. Comparison and voting may be performed with software, with consequent flexibility.

However, since the computer to BCU is likely to be a parallel data interface, it will be complex. Cross-strapping at this point will therefore present considerable difficulty. The complexity can be limited if a computer's access to the other BCU's is restricted to receive-only, and if it transmits to the bus only through its own BCU, which is in turn dedicated to a particular bus line. This restriction means, however, that a bus line failure will, in effect, disable a computer.

#### d) Configuration 4 (Figure 3.5)

In this configuration the computers, the BCU's and the bus lines are all separately reconfigurable. Cross-connection exists between the computers and the BCU's and between the BCU's and the bus lines. This arrangement can be considered:

- 1) as a combination of Configurations 2 and 3 above. The reconfiguration flexibility thereby achieved is severely off-set by the complexity of the interconnections and the magnitude of the configuration management task;

- 2) As the only one that allows full majority voting of compa outputs by the BCU before transmission over the s.

In the second of these two roles, illustrated in Figure 1.3.4, Configuration 4 suffers from a number of disadvantages:

1) Since the BCU functions as a majority voter on all the computer outputs, it is necessarily a single point element of the system. It must, therefore, be internally redundant to meet the FO-FO-FS critcrion, and in addition must possess its own failure detection, isolation and reconfiguration mechanism.

Figure 3.5 Quad redundant BCU configuration

1. 如此我们并以为我们的人。

2) It is not possible to drive the bus lines with non-identical data (as might be desired in a future expansion of the capabilities of the bus system), since there is no clear dedication of a BCU to each bus line. For the same reason parallel input voting would be difficult.

The foregoing discussions have assumed that the computer is performing a central function in the control of the bus, and that replication is purely to achieve failure tolerance. It is possible to consider more than one computer in the operation of the bus system, as described in Chapter 4, but these cases will not be discussed here. Suffice it to say that the complexities of cross-connection, failure detection and isolation, and reconfiguration management increase steeply with each multiply redundant computer that is added to the system.

### 3.3.2 Bus-To-LRU Interface

The configuration of this interface is influenced by the configuration of the computer/bus interface and by the redundancy levels existing in the subsystem to be serviced by the bus. The elements of this interface are shown in Figur 3 3.6 through 3.10 which illustrate the major options for cross-strapping the connection from a quad redundant bus to a triply redundant subsystem. From the point of view of reducing interfacing these elements are characterized as follow:

- a) SIU connects to each bus line by a single, serial data pach. May be simplex or internally redundant.

- b) EIU connects to each SIU by one or two serial data paths, and several control lines. Need not be physically separate from the SIU (or from subsystem, depending on configuration).

- c) LRU connects to each SIU by a complex interface that may consist of various signal types: serial, parallel, discrete and analog, of up to 50 or 100 signal paths.

Taking each cross-strapping option in turn the following observations can be made.

### a) Configuration 5 (Figure 3.6)

This is the trivial case of no cross-strapping at the terminal. The bus, SIU, EIU and LRU constitute a single string element. A failure of any one component fails the whose string. Reconfiguration consists of isolating the faulty string and switching to a good one. This has the advantage of simplicity. LRU's may be geographically separated without involving local cross-connection penalties. However, the subsystem is serviced by a bus that does not meet the FO-FO-FS failure criterion, since the fourth line is not connected.

Figure 3.6 Single string no cross connection

Figure 3.7 Cross connection between SIU and bus

以為 教教教 医人名西西科巴斯 医腹腔腹膜炎病 化多头

# b) Configuration 6 (Figure 3.7)

Cross-strapping occurs at the bus/SIU interface. The SIU, EIU, and LRU are nere a single string element, and each LRU can be accessed by all bus lines. The full failure tolerance of the bus is therefore available to the subsystem. Reconfiguration is, as for the first example above, still a matter of switching to a good string. Disadvantages of this approach are:

- The SIU and EIU are considered a part of, and their redundancy is determined by, the subsystem. The complexity of the SIU/EIU combination may force the use of a higher level of redundancy in a subsystem of superior reliability than would otherwise be considered.

- 2) Each level of subsystem redundancy requires four connections to the bus, in this case a total of 12. Bus connections should be minimized, as is discussed in Chapter 6.

- 3) A catastrophic failure of one SIU can disable the whole bus system. (The use of bus line couplers can limit this to failure of the subsystem only.)

- 4) Comparison of the outputs of LRU's cannot be accomplished locally. (This is not a serious drawback, since local voting may be undesirable in any case on grounds of complexity.)

- 5) It is not possible for one terminal to compare, or vote on, multiple, parallel bus transmissions.

- 6) A separate address in the bus control word format must be provided for each SIU to allow for reconfiguration.

- 7) Only one EIU may be serviced by each SIU.

# c) Configuration 7 (Figure 3.8)

Here cross-strapping occurs at the SIU/EIU interface. The SIU becomes an element of the bus, and the EIU is considered a part of the LRU. The degrees of redundancy of SIU and EIU are, therefore, determined by the bus and subsystem respectively. The advantages of this arrangement are:

Figure 3.8 Cross connection between SIU and EIU

- No single SIU failure can disable the bus system, although it could disable all EIU's (and therefore the subsystem).

- 2) LRU comparison could be done at the SIU level (although at considerable cost in complexity).

- 3) If bus configuration is controlled by the computer/BCU (which is probable), then a separate address is not required by each SIU at a terminal.

- 4) Cross-strapping involves only a few physical paths, since data at this point is still largely serial.

#### The disadvantages are:

ी हरें को को संस्थित के समाने अनुसार के स्वाप्त कर है है।

- 1) Four SIU's are required even if the subsystem redundancy level is lower (this is only a real disadvantage for reliable but critical subsystems which require the full FO-FO-FS bus tolerance).

- 2) The bus system can only be run in a simplex communication mode (e.g., command and data cannot be assigned separate paths).

- 3) The cross-strapping complexity, though much lower than Configuration 8, may exceed that of 6. This is of concern if the bus lines are separated by considerable geographical distance.

## d) Configuration 8 (Figure 3.9)