December 1972

B72-10755

NASA Headquarters

NASA Tech Briefs announce new technology derived from the U.S. space program. They are issued to encourage commercial application. Tech Briefs are available on a subscription basis from the National Technical Information Service, Springfield, Virginia 22151. Requests for individual copies or questions relating to the Tech Brief program may be directed to the Technology Utilization Office, NASA, Code KT, Washington, D.C. 20546.

# Gate Protective Device for SOS Array

# The problem:

One of the problems in CMOS (complementarysymmetry metal-oxide semiconductor) technology is that SOS (silicon oxide on sapphire) arrays are subject to breakdown voltages caused by electrostatic discharge from a person or a piece of equipment in contact with the external leads of the circuit. Because breakdown voltage BV<sub>ox</sub> across thin (1000 angstroms) gate oxides is about 70 volts, it can be easily exceeded by such discharges.

# How it's done:

As a function of the human body resistance, the limiting of transient voltage across the gate oxide requires that the dynamic impedance  $R_{dyn}$  of the protective device be

$$R_{dyn} \leq \frac{BV_{ox}}{V_{body}} R_{body}$$

#### The solution:

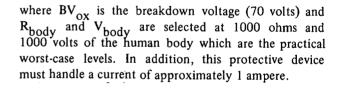

A gate protective device was made which consists of alternate heavily doped  $n^+$  and  $p^+$  diffusions to eliminate the problem.

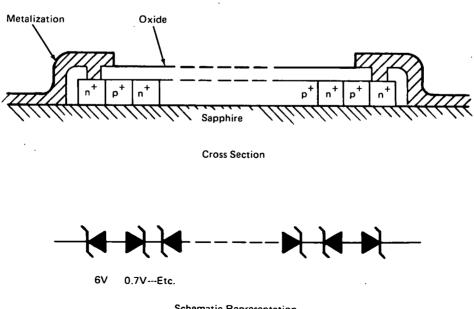

Schematic Representation

(continued overleaf)

This document was prepared under the sponsorship of the National Aeronautics and Space Administration. Neither the United States Government nor any person acting on behalf of the United States

Government assumes any liability resulting from the use of the information contained in this document, or warrants that such use will be free from privately owned rights.

A device satisfying these requirements consists of alternate heavily doped n<sup>+</sup> and p<sup>+</sup> diffusions which are easily produced during the normal double epitaxial processing. Schematically, this device represents a series of reversebiased zener diodes and alternate forward diodes, as shown in the figure. For a junction doped heavily on both sides  $(10^9/\text{cm}^3)$ , the zener breakdown voltage is approximately 6 volts. Thus, for a string of 2n junctions, there are n 6-volt zener diodes and n forward diode drops of approximately 0.7 volt each in series. The total voltage drop can be easily fixed with the appropriate number of junctions.

Several devices of this geometry were made which consisted of nine alternately diffused strips (eight junctions). Results showed that each device had a 27-volt breakdown in either direction. This breakdown was reproducible across the entire wafer with a tolerance of better than  $\pm 2$  volts.

## Note:

Requests for further information may be directed to: Technology Utilization Officer NASA Headquarters Code KT Washington, D. C. 20546 Reference: B72-10755

## Patent status:

Title to this invention has been waived under the provisions of the National Aeronautics and Space Act [42 U.S.C. 2457 (f)], to the RCA Corp., Princeton, N. J. 08540.

Source: J. E. Meyer, Jr. and J. H. Scott of David Sarnoff Research Center of RCA Corp. under contract to NASA Headquarters (HQN-10745)

-T-K2C HD2' HW: T3T3 N&2I-2