N 7 2 - 28 24 6 NASA CR-112099

# DEVELOPMENT OF BEAM-LEADED LOW-POWER LOGIC CIRCUITS

# CASE FILE COPY

**Final Report**

NASA Contract No. NAS1-10532

March 1972

By Bill Wiley Smith and Farris Malone

TEXAS INSTRUMENTS INCORPORATED P.O. Box 5012 Dallas, Texas 75222

> Langley Research Center Hampton, Virginia 23365

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

NASA CR-112099

# DEVELOPMENT OF BEAM-LEADED LOW-POWER LOGIC CIRCUITS

**Final Report**

NASA Contract No. NAS1-10532

By Bill Wiley Smith and Farris Malone TEXAS INSTRUMENTS INCORPORATED P.O. Box 5012 Dallas, Texas 75222

Langley Research Center Hampton, Virginia 23365 NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

# TABLE OF CONTENTS

| Section    | Title                                  | Page |

|------------|----------------------------------------|------|

| I.         | SUMMARY                                | 1    |

| II.        | INTRODUCTION                           | 3    |

| III.       | DISCUSSION                             | 7    |

|            | A. Processing                          | 7    |

|            | B. Beam Lead Assembly                  | 11   |

|            | 1. Unmounted Bars                      | 15   |

|            | 2. Mounted Bars                        | 15   |

|            | C. Circuit Descriptions                | 19   |

|            | 1. Theory of Operation-BL54L67/BL54L68 | 22   |

|            | 2. Resistor Process-1000 Ohm-cm/cm     | 23   |

| IV.        | TESTING AND EVALUATION                 | 27   |

|            | A. Probe Test and Lot Qualification    | 27   |

|            | B. Device Characterization             | 29   |

| <b>v</b> . | RESULTS                                | 33   |

# APPENDIX

| BEAM LEAD CIRCUITS SCHEMATICS AND PHOTOGRAPHS | APHS · · · · · · · · · · · · · · · · · · · | APHS | IS SCHEMATICS AND PHOTO | IRCUITS S | LEAD | BEAM |

|-----------------------------------------------|--------------------------------------------|------|-------------------------|-----------|------|------|

|-----------------------------------------------|--------------------------------------------|------|-------------------------|-----------|------|------|

# LIST OF ILLUSTRATIONS

F

| igure | Title                                                | Page |

|-------|------------------------------------------------------|------|

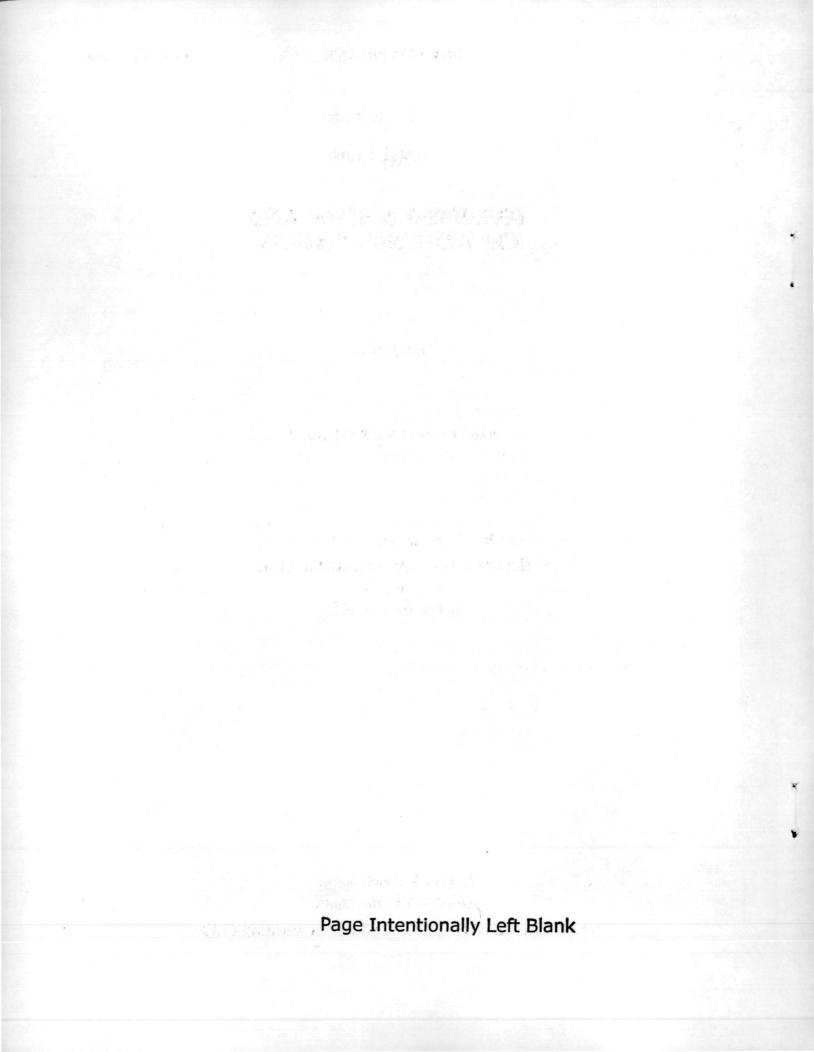

| 1.    | Cross Section of Beam Lead IC Bar                    | 4    |

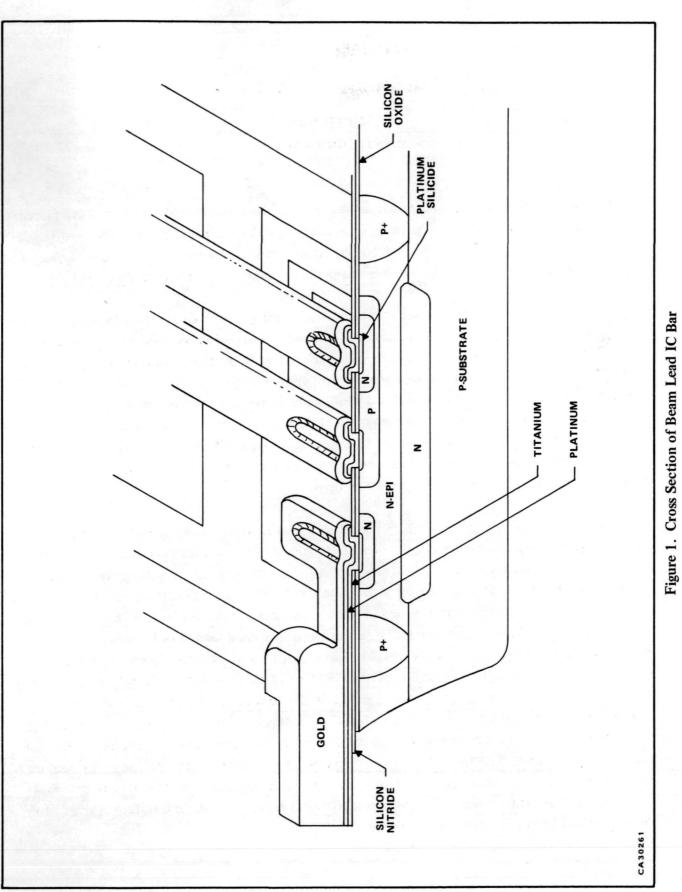

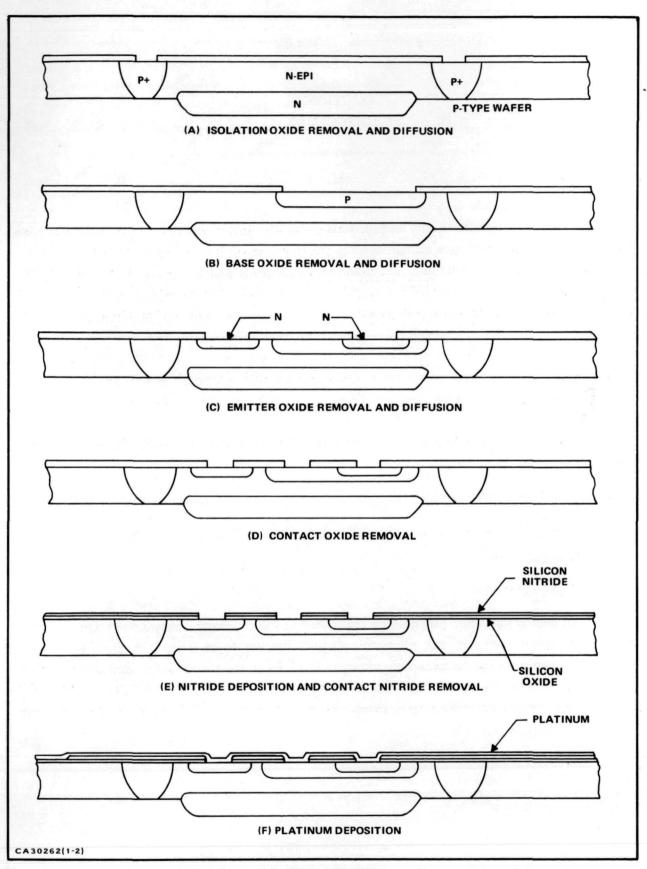

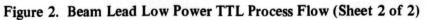

| 2.    | Beam Lead Low Power TTL Process Flow                 | 8    |

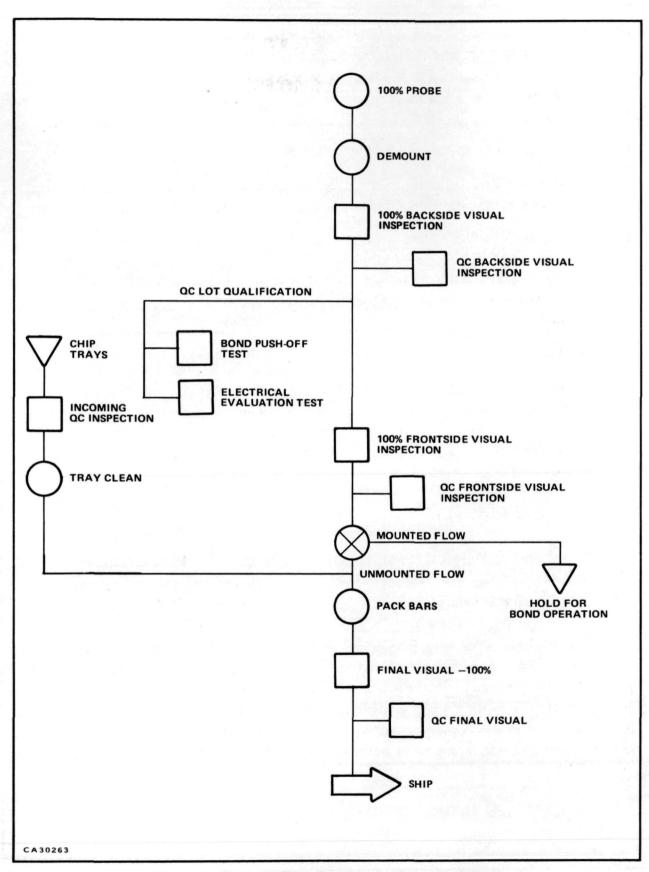

| 3.    | Assembly Flow Diagram for Beam Lead Bars             | 12   |

| 4.    | Assembly Flow Diagram for Unsealed Beam Lead Headers | 13   |

| 5.    | Beam Lead Transfer Fixture                           | 14   |

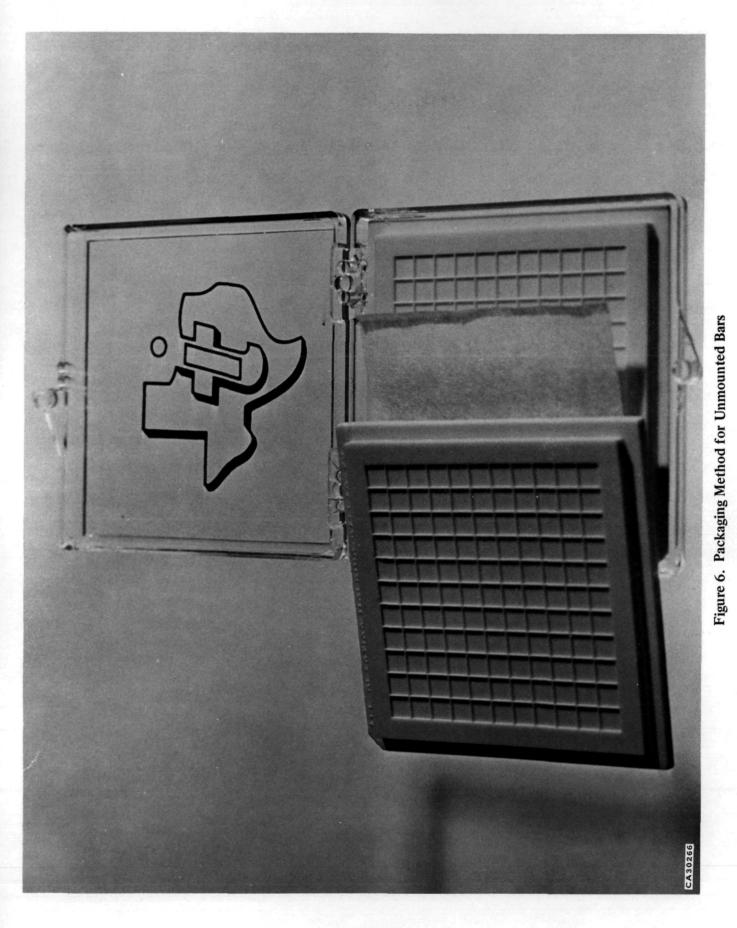

| 6.    | Packaging Method for Unmounted Bars                  | 16   |

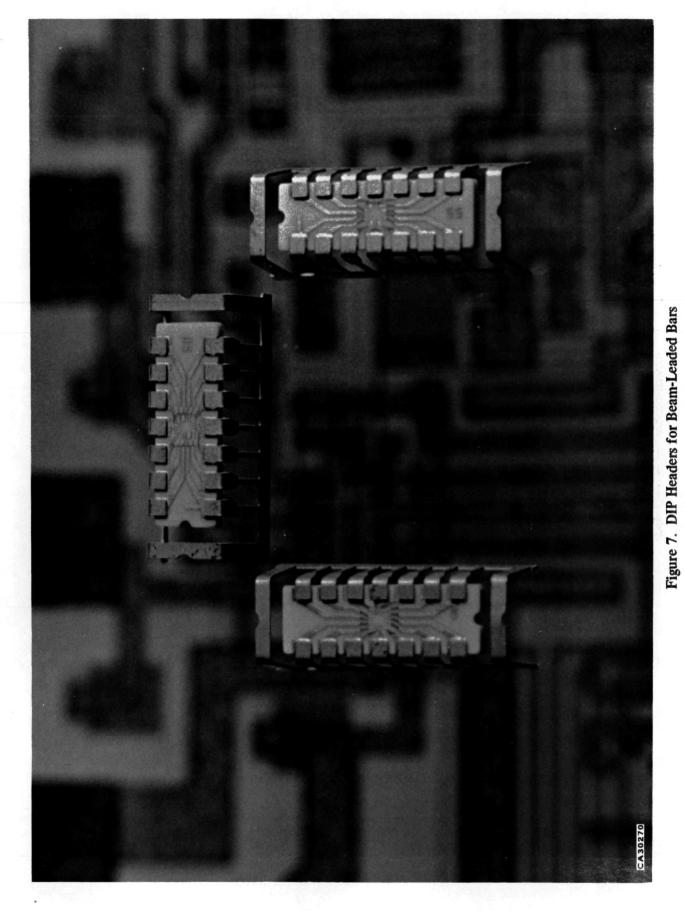

| 7.    | DIP Headers for Beam-Leaded Bars                     | 17   |

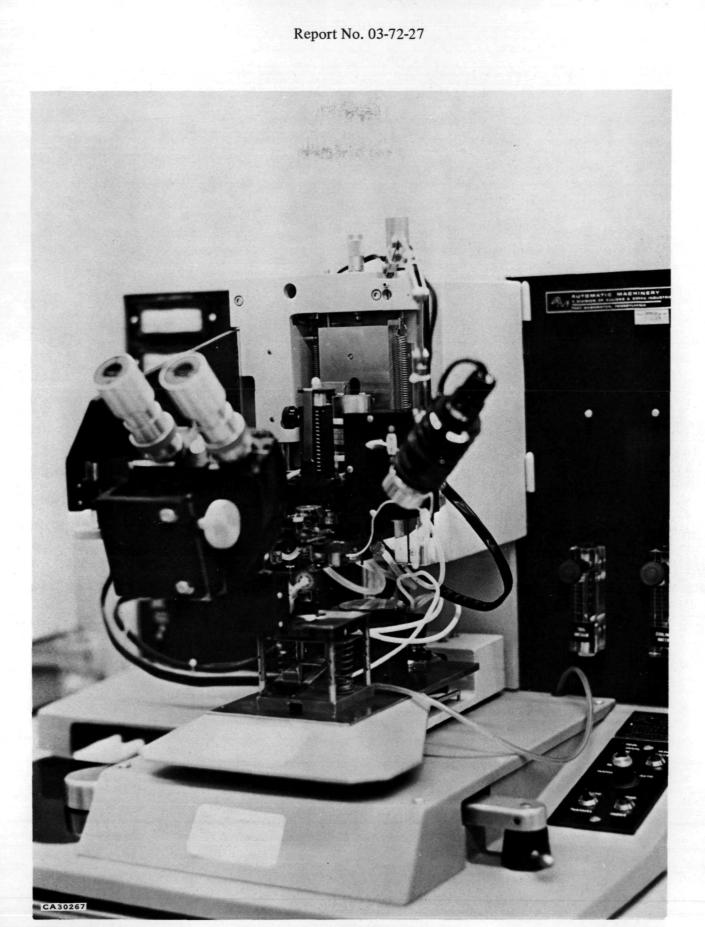

| 8.    | Beam Lead Wobble Bonder                              | 18   |

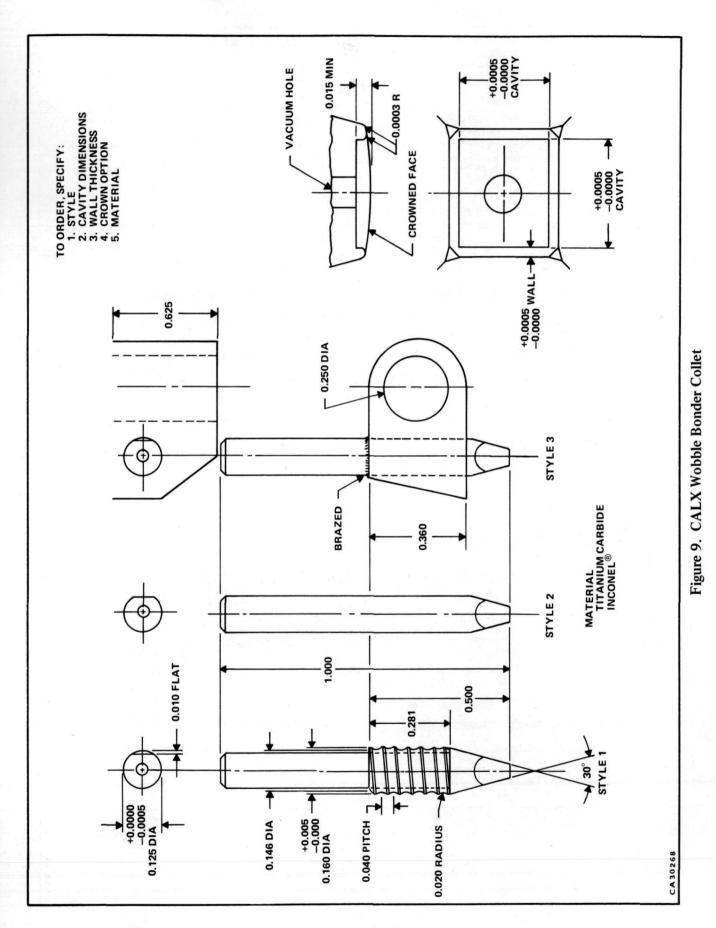

| 9.    | CALX Wobble Bonder Collet                            | 20   |

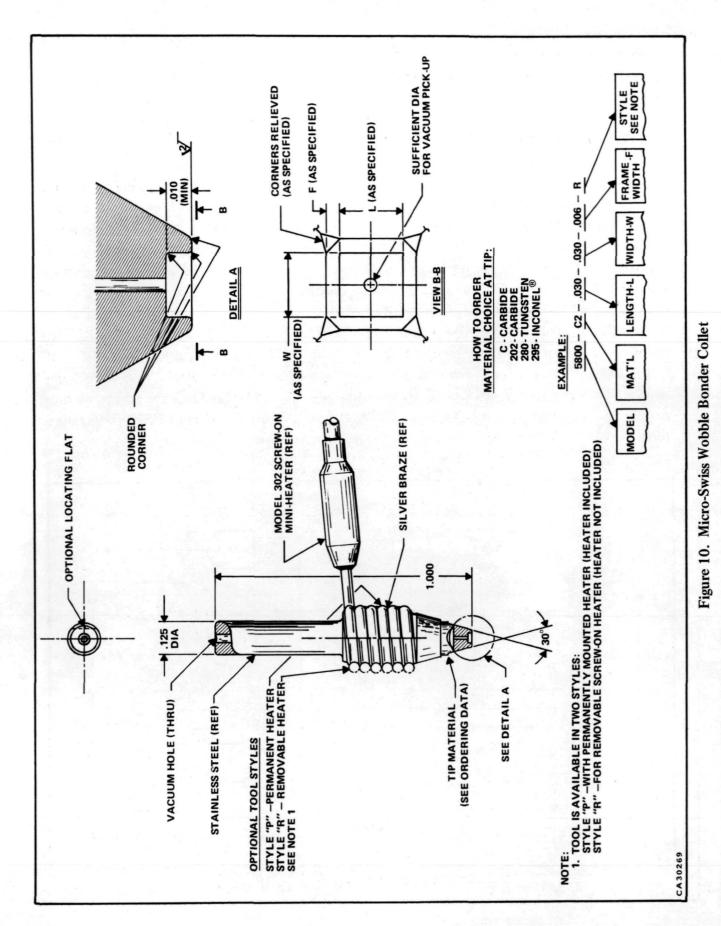

| 10.   | Micro-Swiss Wobble Bonder Collet                     | 21   |

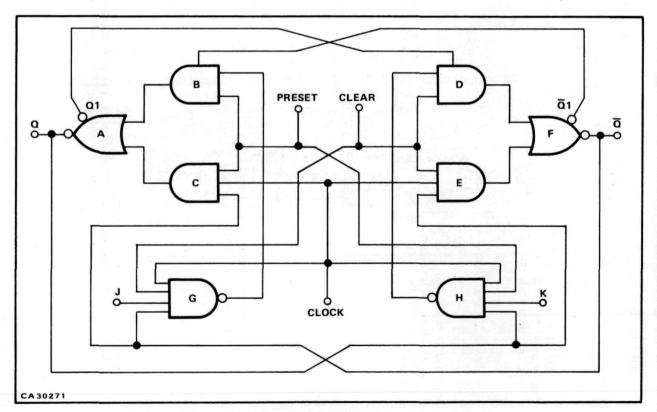

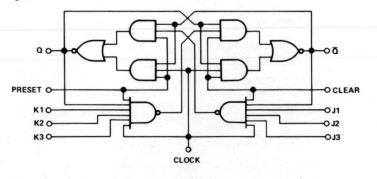

| 11.   | BL54L67/BL54L68 Logic Diagram                        | 22   |

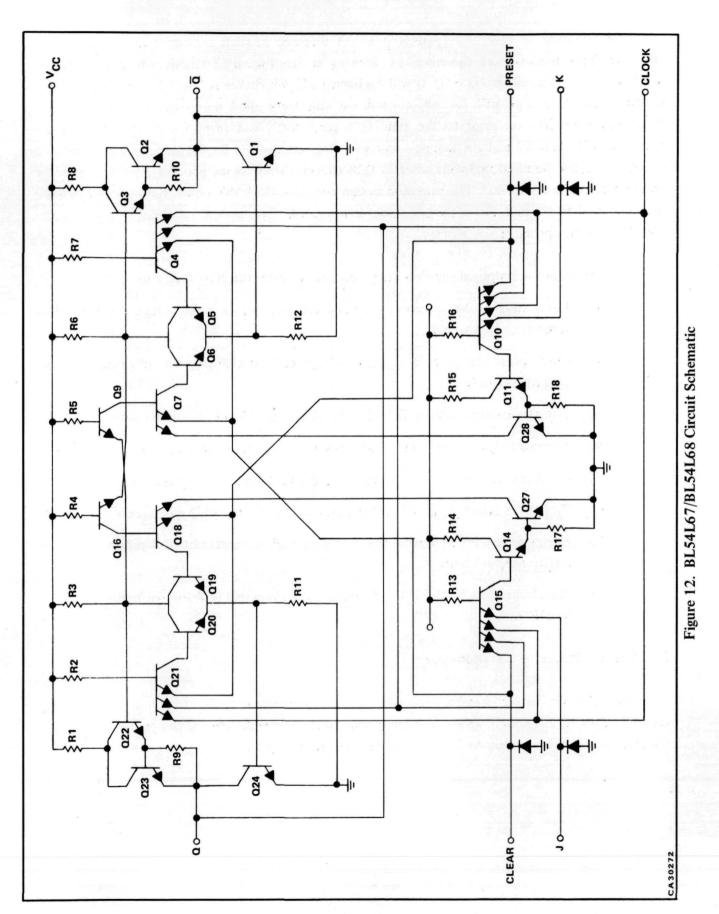

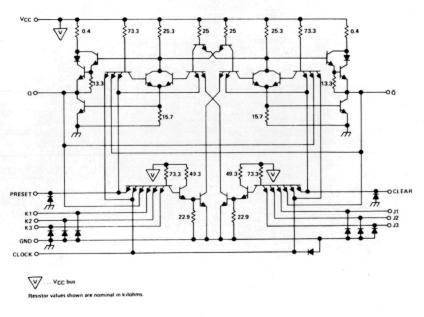

| 12.   | BL54L67/BL54L68 Circuit Schematic                    | 24   |

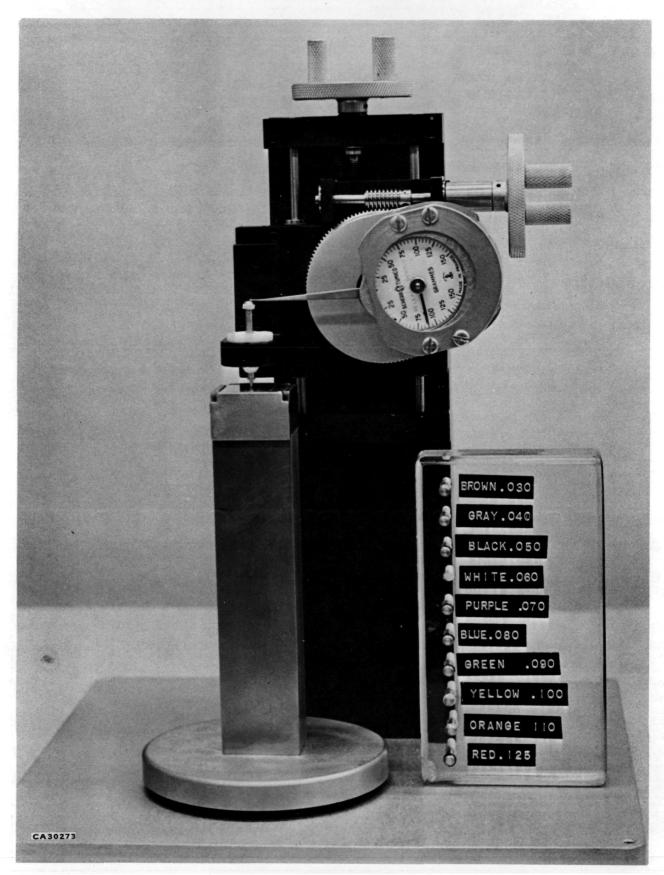

| 13.   | Beam Lead Push-Off Tester                            | 28   |

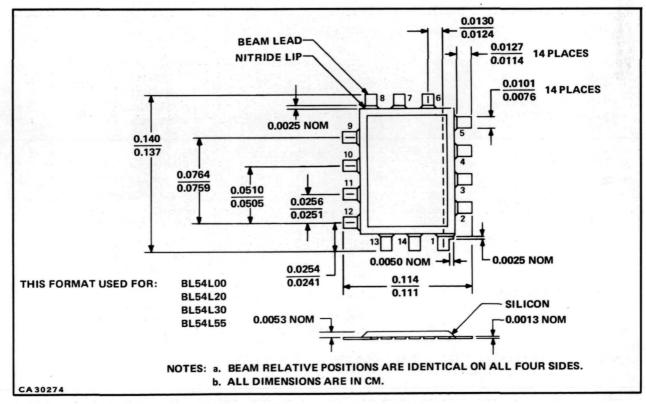

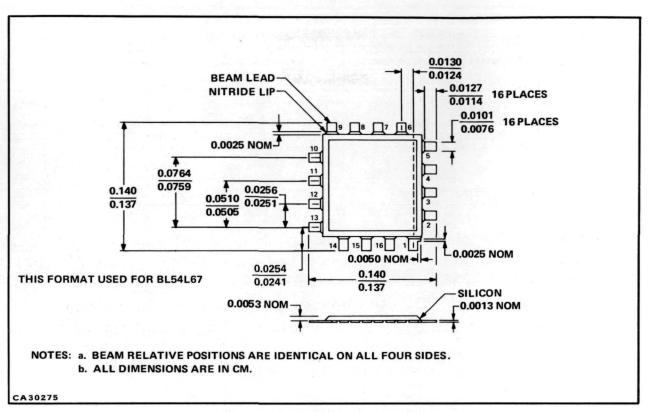

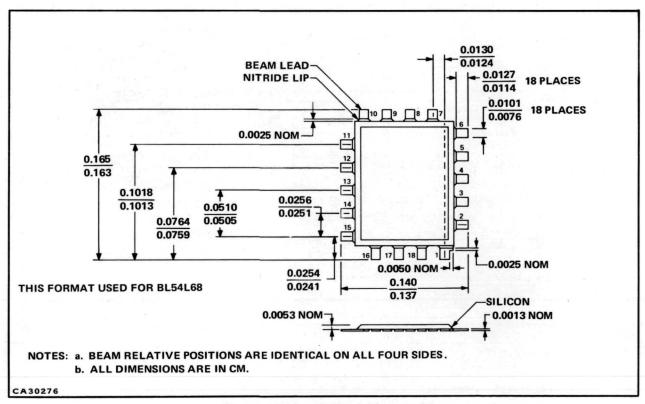

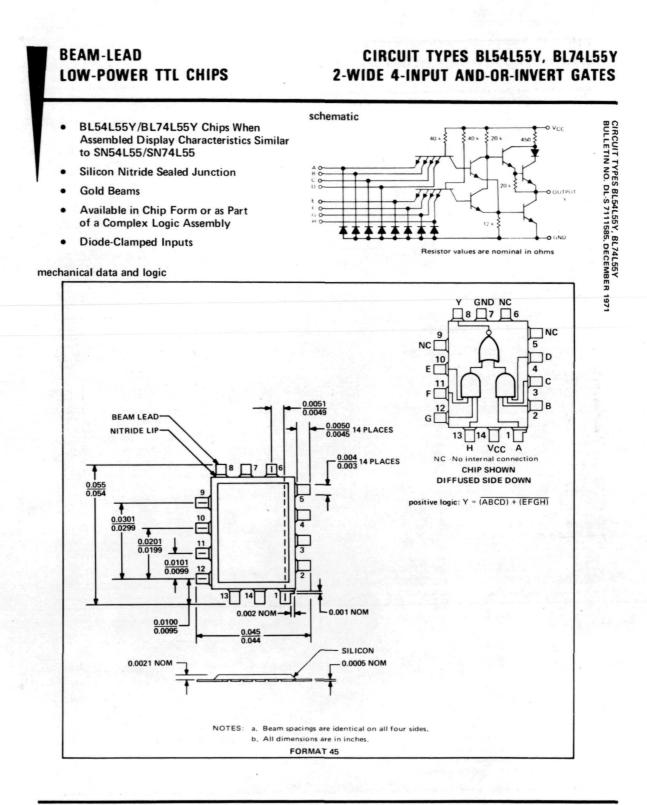

| 14.   | Beam Lead Format 45                                  | 29   |

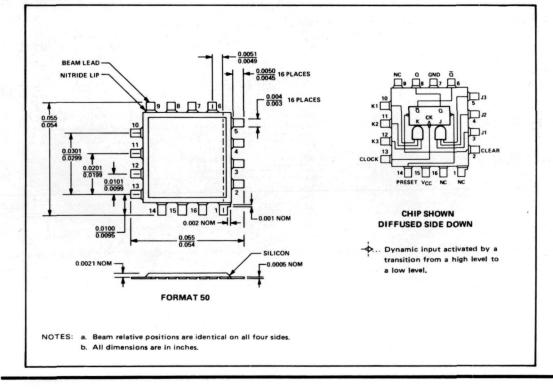

| 15.   | Beam Lead Format 50                                  | 30   |

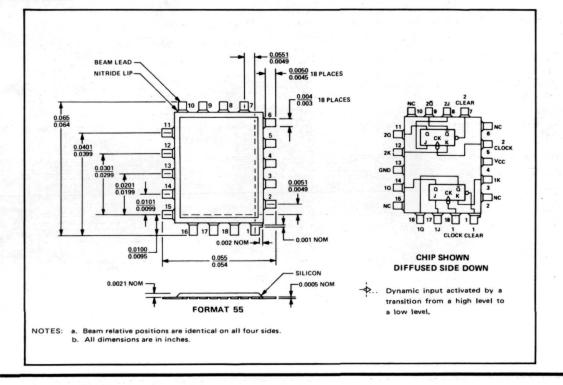

| 16.   | Beam Lead Format 55                                  | 30   |

| 17.   | Circuit Types BL54L00Y and BL74L00Y Schematic        | 37   |

| 18.   | Circuit Types BL54L20Y and BL74L20Y Schematic        | 39   |

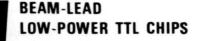

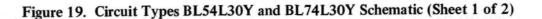

| 19.   | Circuit Types BL54L30Y and BL74L30Y Schematic        | 41   |

| 20.   | Circuit Types BL54L55Y and BL74L55Y Schematic        | 43   |

| 21.   | Circuit Types BL54L67Y and BL74L67Y Schematic        | 45   |

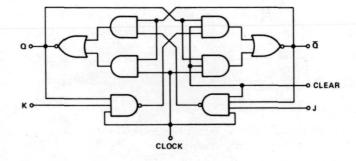

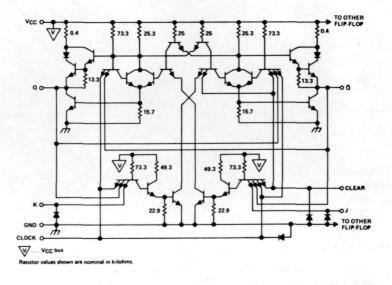

| 22.   | Circuit Types BL54L68Y and BL74L68Y Schematic        | 49   |

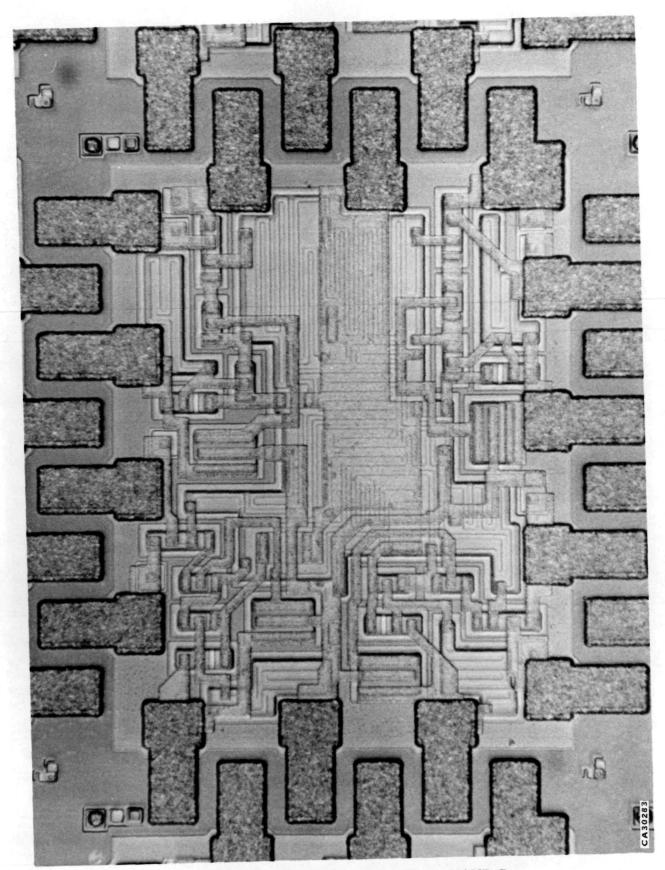

| 23.   | BL54L00–Quad 2-Input NAND Gate                       | 53   |

| 24.   | BL54L20–Dual 4-Input NAND Gate                       | 54   |

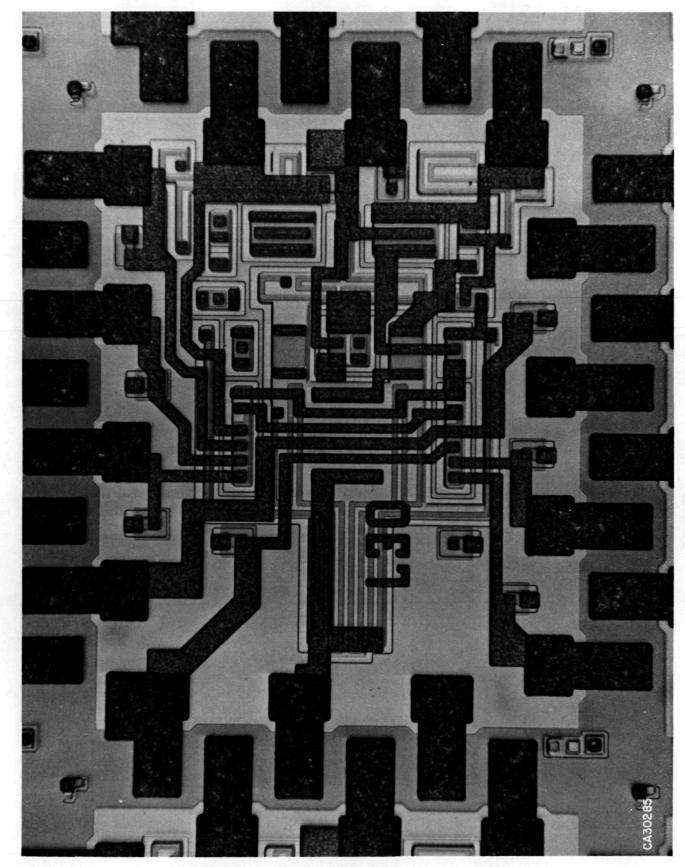

| 25.   | BL54L30–Single 8-Input NAND Gate                     | 55   |

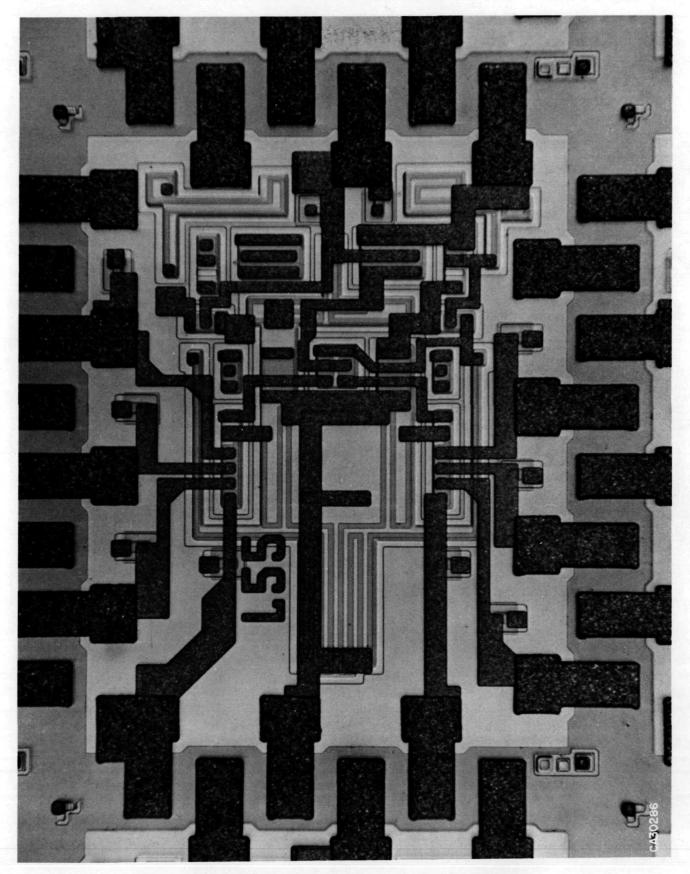

| 26.   | BL54L55–Two-Wide 4-Input AND-OR-INVERT               | 56   |

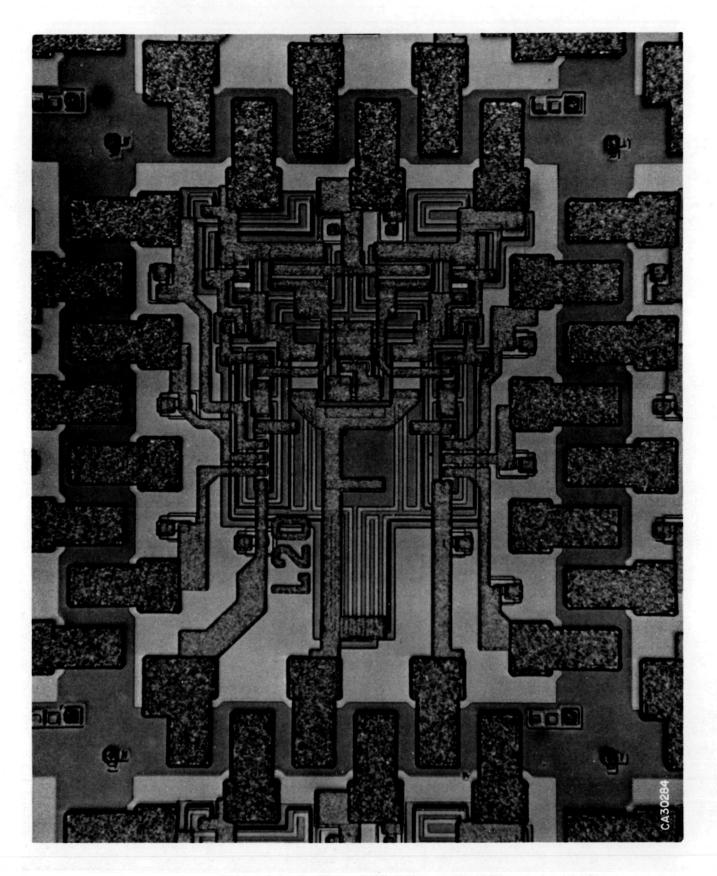

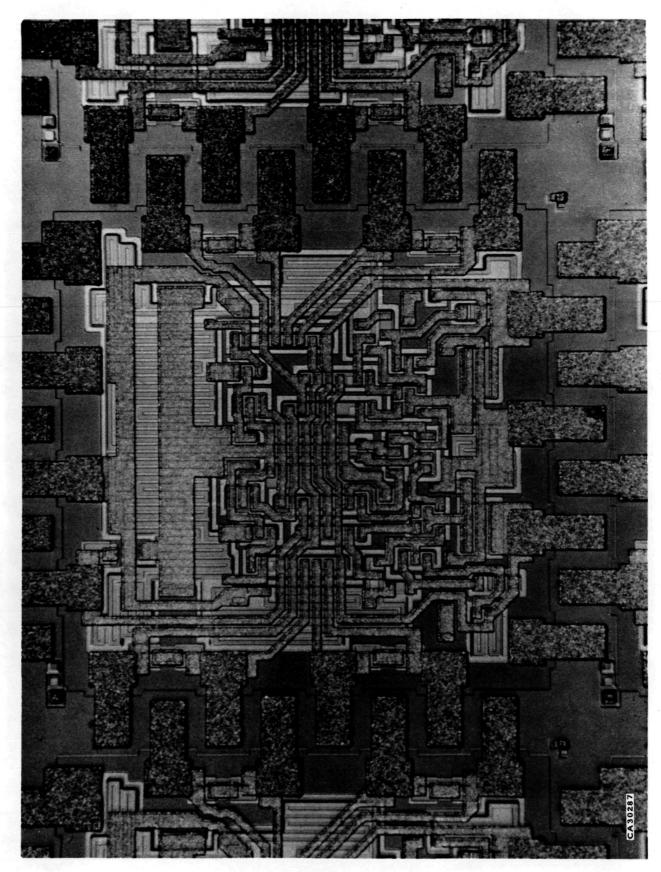

| 27.   | BL54L67–J-K Flip-Flop                                | 57   |

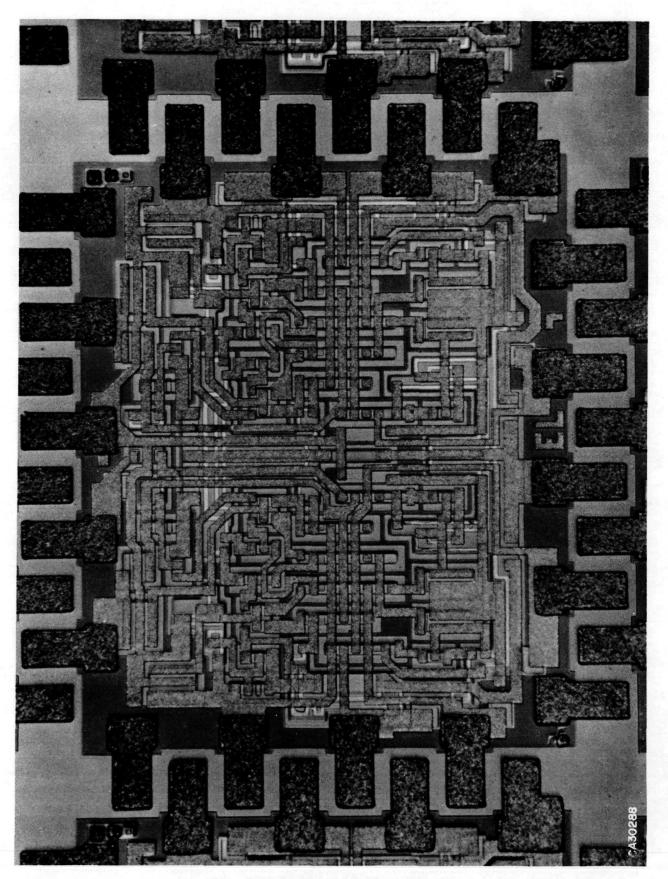

| 28.   | BL54L68–Dual J-K Flip-Flop                           | 58   |

#### LIST OF ABBREVIATIONS AND SYMBOLS

Å = angstroms

atm/cc = atmospheres per cubic centimeter

- cm = centimeter

- °C = degrees Centigrade

- °K = degrees Kelvin

- IC = integrated circuit

K ohms = kilo ohms

l/minute = liters per minute

54L = low power transistor transistor logic family

m = meter

$\mu A = microamps$

$\mu$ m = micrometers (microns)

mA = milliamps

nsec = nanoseconds

N-Epi = N-type epitaxial layer

$\Omega$ -cm/cm = ohm centimeter per centimeter (ohms per square)

OR = oxide removal

ppm = parts per million

PtSi = platinum silicide

$Si_3N_4 = silicon nitride$

TiPt = titanium platinum

TTL = transistor transistor logic

V = volts

## Development of Beam-Leaded Low-Power Logic Circuits

By Bill Wiley Smith and Farris Malone Texas Instruments Incorporated

#### SECTION I SUMMARY

The technologies of low power TTL and beam lead processing have been merged into a single product family. This family offers the power and thermal advantages of low power (54L), while providing the additional reliability advantages of beam leads. The reduction in the power and heat levels also allows the system designer to take advantage, through beam lead, multichip assemblies, of increased package density to reduce system size and weight.

1

Page Intentionally Left Blank

### SECTION II INTRODUCTION

The conservation of heat and power as well as the need for increased reliability have placed increasing restrictions upon the systems used in airborne and space applications. This need is not now satisfied by components available to the system users. Therefore, new technologies or combinations of existing technologies that might present a solution to the problem were sought.

The problems in heat and power can be solved by using currently available low-power TTL integrated circuits (54L). This family offers a power reduction, and hence a heat reduction, of an order of magnitude over standard power TTL. This decrease in heat, because of the reduced junction temperature of the operating circuits, also contributes to an increase in system reliability. It also allows the system to be contained in a smaller area without creating a system "hot spot" that would be difficult to cool. The decrease in power also eases the restrictions on resistance of package leads and system interconnects in that the system operates at a much lower current level in both signal and power leads. This reduction in power required also leads to a further system savings by allowing smaller, less costly power supplies to be used.

While the use of low-power TTL does lead to increased system reliability, further reliability increases are needed. This need was satisfied with the advent of beam-leaded devices. The beam lead process eliminates the major cause of integrated circuits component failure, wire bonds. It replaces the wire bond with a bar to package interconnect that is an integral part of the bar's metal system. This beam interconnect, shown in Figure 1, features an electroplated gold beam and an attach cross-sectional area larger than that of a wire bond. A second feature of the beam lead bar is silicon nitride passivated junctions. The silicon nitride acts as an effective block against sodium intrusion creating a hermetic bar. Protection against latent failures is inherent in two aspects of the beam lead process. Since the beam lead bar is not die bonded in the conventional bar attach manner, there does not exist the thermal coefficient factor that frequently causes bar cracking. The beam lead bar is attached to the package through malleable gold beams that absorb the expansion differential. The beam lead bar is separated by a chemical etch instead of by scribing and breaking as are conventional bars. This method of separation eliminates the stresses and cracks caused by scribing and breaking that contribute to bar breakage later in temperature cycling. Thus the reliability features of a beam lead bars are:

4

- 1) Integral bar to package interconnect

- 2) Silicon nitride junction passivation

- 3) No high temperature die bond

- 4) Chemical etch bar separation

The complete solution to the existing problem was not found as a product, thus it was desirable to integrate these two technologies, low-power TTL and beam lead processing, to form a single product family.

5

Page Intentionally Left Blank

## SECTION III DISCUSSION

#### A. PROCESSING

The object of applying beam lead processing to the low-power TTL (54L) line has been achieved. The two technologies needed for this program existed as separate operations, but some unknowns needed to be overcome in combining beam leads and low-power TTL into a single product family. In general, a modified 54L diffusion process and the Western Electric<sup>1</sup> beam lead process were used. The standard 54L process had to be modified due to the addition of silicon nitride.

The final beam lead low-power process is presented with a discussion concerning areas that differ from the standard low-power process. Figure 2 is a representation of the process.

The initial steps are identical to the standard 54L process. The process begins with buried layer wafers.

#### 1. Oxidation

- 2. Isolation Diffusion

- 3. Base Diffusion

- 4. Emitter Diffusion

All high temperature processing is completed at this point on standard parts. On the beam lead parts, however, the silicon nitride film has yet to be deposited. Since the nitride deposition temperature is high enough  $(1123^{\circ}K)$  to reduce the gold concentration used for lifetime control, the gold on the beam lead parts is added after the silicon nitride has been deposited, rather than before or during emitter diffusion, as is common with conventional circuits.

<sup>1.</sup> Hause, S. S. and Whitner, R. A., "Manufacturing Beam-Lead Sealed-Junction Monolithic Integrated Circuits," Western Electric Engineer (December 1967), p. 3.

Figure 2. Beam Lead Low Power TTL Process Flow (Sheet 1 of 2)

#### 5. Nitride Film

Silicon nitride is deposited to a thickness of  $10^{-7}$  meters by pyrolytic decomposition of ammonia (NH<sub>3</sub>) and silane (SiH<sub>4</sub>) at 1123°K. The nitride is not deposited directly onto the silicon surface but a layer (3 X  $10^{-8}$  meters) of thermal oxide is grown first to serve as a barrier and to prevent an unstable surface condition. The temperature of 1120°K was chosen because previous work has shown that at that temperature and below, amorphous films are formed. It was further shown that an amorphous film forms a better barrier to sodium diffusion than do those deposited as higher temperatures which tend to have larger crystallites.

Contact openings and paths for separation etch must be cut through the nitride film. The silicon nitride is etched in boiling phosphoric acid at  $432^{\circ}$ K using a mask of photoresist. The oxide that was beneath the nitride in the contact openings is etched in buffered HF using the Si<sub>3</sub>N<sub>4</sub> film as a mask.

The checks which are made to ensure consistency of the nitride layers are listed below.

Deposition Conditions. For a silane/ammonia ratio less than 0.1, the film characteristics are more easily repeatable so the ratio was always kept less than that. Further, any deviations from the established growth rate are grounds for rejecting the slice.

*Etch Rate.* The HF etch rate test is becoming the standard test for acceptable nitride. In using this test, the etch rate of each lot is determined from a pilot. The maximum permissible rate of 49% HF at room temperature is 300 Å/min.

Blocking Tests. Temperature bias tests are used to verify the ion (sodium) blocking capability of the nitride. Water saturated with salt is allowed to dry on the units to be tested. They are then reverse biased to 80% of  $BV_{CBO}$  and heated to 575°K under H<sub>2</sub>. Any increase in I<sub>CBO</sub> is usually attributed to sodium penetrating the nitride barrier.

6. Gold Diffusion

Gold is evaporated onto the slices and alloyed in the contact windows. The excess gold is removed by aqua regia. The slices are then diffused at approximately  $1350^{\circ}$ K to redistribute the gold. The choice of  $1350^{\circ}$ K is dictated by the requirement to have enough gold in the collector region adjacent to the base to provide the required minimum offset voltage of 60 mV.

#### 7. Gold Leads

Gold is plated over the entire slice to a thickness of  $1-2 \mu m$ . Lea-Ronal Aurall 292 gold-plating solution is used for this operation (leads) and for beams as well. Leads are formed by chemically removing the excess gold in a cyanide etch using resist as a mask.

8. Beams

Gold beams are plated through a resist pattern to a thickness of  $11-17 \,\mu\text{m}$ . The beam hardness is important in bonding and must be constantly monitored. Knoop numbers of 60-90 are typical when measured with the Leitz Mini-Load hardness tester using a 5-gm load.

9. Mount and Grind

The metallized slices are mounted metal side down onto a polished sapphire disc and secured by wax and ground to a nominal thickness of 5.7 X  $10^{-3}$  cm.

Photoresist is then applied to the ground side of the wafer and a separation etch pattern is aligned to the diffusion using an infrared alignment technique. The slices are then etched

- until the individual bars are separated. Care is taken to etch enough to expose the nitride lip protecting the beams and yet not overetch to such an extent as to expose the beam anchor area.

- 10. Probe

The wafers are 100% probed from the back while they are still mounted on the sapphire disc. The program used tests the bars to all dc parameters and a full functional series. This is similar to the final test procedures used on conventionally packaged parts (see Section IV). The tighter screen is used because most parts will be used without being mounted in a single chip header.

#### B. BEAM LEAD ASSEMBLY

The assembly is broken into two parts because of the need to have both mounted and unmounted bars as final products (Figures 3 and 4). The basic flow, until the bond operation, is the same for both bars and mounted parts.

After the 100% probe test, the bars are in a separated form but still mounted in wax to a sapphire disc. The wafers are mounted into a transfer fixture (Figure 5) during the removal of the wax to prevent dislocation of the bars. The wax is dissolved using boiling trichlorethylene. The slice is then removed from the transfer fixture and subjected to a 40X backside inspection. The good bars are removed to another transfer fixture and turned for a 100X frontside inspection. The good bars are now loaded into chip trays for either shipment or for transfer into the bonding operation.

Figure 3. Assembly Flow Diagram for Beam Lead Bars

Figure 4. Assembly Flow Diagram for Unsealed Beam Lead Headers

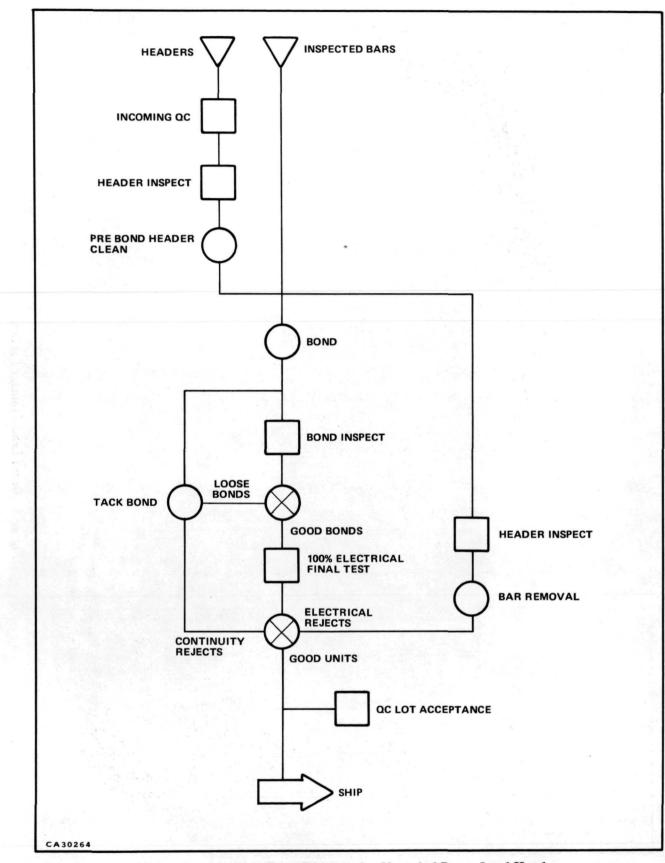

Figure 5. Beam Lead Transfer Fixture

#### 1. Unmounted Bars

The bars are loaded into 2 X 2-inch plastic chip trays after the trays have been cleaned with alcohol. The part number and manufacturer for these trays is listed in Table I.

After a 20X final inspection, the tray is covered by a sheet of lint-free paper and a second tray placed as a lid on top of the first tray as shown in Figure 6. The sandwich is then placed into a clear plastic compact and the compact sealed for shipment.

| Manufacturer         | Pocket size<br>inches | No. of<br>pockets | Manufacturers<br>Part no. | Color  |

|----------------------|-----------------------|-------------------|---------------------------|--------|

| Flouroware, Inc.     | 0.130 X 0.130         | 100               | 420-130                   | Brown  |

| All-Plastics Molding | 0.125 X 0.125         | 121               | 70-1072-004               | Yellow |

| Table I. | Chip | Tray | Descrip | otions |

|----------|------|------|---------|--------|

|----------|------|------|---------|--------|

#### 2. Mounted Bars

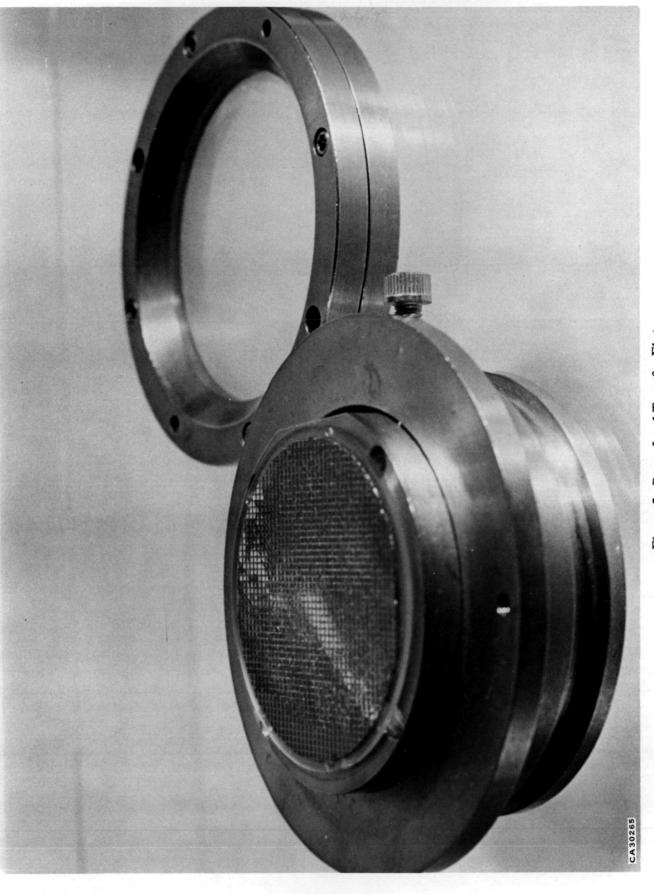

Nonlidded headers were used to mount the beam-leaded bars for evaluation. This was done to simplify the development effort and keep the bars exposed during evaluation for study. The headers shown in Figure 7 are constructed of alumina with a gold-plated molymanganese metal system. The leads are brazed to the gold-plated molymanganese. A screened metal package was discarded early in the program due to an unevenness of the beam attach pads. Photo-etching the metal resulted in a bar attach area of sufficient planarity to allow a complete bond. The bonding is done by a Kulicke and Soffa Industries, Inc. wobble bonder. This type of bonder (Figure 8) requires that the bar attach area be extremely coplanar. The requirement was not a problem in this program after the change was made to a photo-etched header.

The wobble bonder collet sizes used to bond the various part types are shown in Table II. The collets of two different manufacturers (Figures 9 and 10) were used on this program. The Calx, Inc. collet is preferred because of its cost advantage and its one-piece construction.

Figure 8. Beam Lead Wobble Bonder

|        |                                          |                     | Calx, Inc.           |                           |                 |                     |

|--------|------------------------------------------|---------------------|----------------------|---------------------------|-----------------|---------------------|

| Format | Circuit<br>type                          | Style               | Cavity<br>inch       | Wall<br>thickness<br>inch | Crown<br>option | Material            |

| 45     | BL54L00<br>BL54L20<br>BL54L30<br>BL54L55 | 1                   | 0.039 X 0.049        | 0.006                     | No<br>Crown     | Titanium<br>Carbide |

| 50     | BL54L67                                  | 1                   | 0.049 X 0.049        | 0.006                     | No<br>Crown     | Titaniun<br>Carbide |

| 55     | BL54L68                                  | 1                   | 0.049 X 0.059        | 0.006                     | No<br>Crown     | Titaniun<br>Carbide |

|        | 4<br>·.                                  |                     | Aicro-Swiss, Inc. (K | BLS)                      | 1               |                     |

| Format | Circuit<br>type                          | Cavity Size<br>inch |                      | Manuf                     | acturers part   | t number            |

| 45     | BL54L00<br>BL54L20<br>BL54L30<br>BL54L55 | 0.039 X 0.049       |                      | C5800-                    | 20203904        | 9006-R              |

| 50     | BL54L67                                  | 0.049 X 0.049       |                      | C5800-                    | 202049-,04      | 9-,006-R            |

| 55     | BL54L68                                  | 0.049 ×             | 0.059                | C5800-                    | 20204905        | 9006-R              |

#### Table II. Wobble Bonder Collet Descriptions

#### C. CIRCUIT DESCRIPTIONS

The circuit types developed in beam leads are basically like their counterparts in the standard low-power line (54L). The additions were made to each circuit. A clamp diode was added to each circuit input to dampen oscillation in the input signal and a Darlington stage was added to the top of each output. Refer to the Appendix for exact circuit configurations and for pictures of each part type.

A logic and circuit design change was made in the flip-flop used in the 54L72, single J-K flip-flop, and in the 54L73, Dual J-K flip-flop. This redesign improved the performance of these flip-flops as described in paragraph 1, to such an extent as to make renumbering necessary to avoid confusion. The number change is:

| Old Number | New Number |

|------------|------------|

| 54L72      | BL54L67    |

| 54L73      | BL54L68    |

20

The prefix, BL, has been adopted to indicate that the parts are beam leaded. The description of operation of these new circuits as well as their advantages over the standard circuits are discussed below. Also, the process for the 1000  $\Omega$ -cm/cm resistor used in the design of the 54L68 is explained.

#### 1. Theory of Operation-BL54L67/BL54L68

The circuit in Figure 11 is an edge-triggered J-K flip-flop which obeys all the same application rules as the catalog SN54L72/74L72. The clock input is ANDED with J and K inputs to lock data out for logical "0" clock inputs. The cross-coupled AND-OR-INVERT GATES of the output, logically lock out data from the J and K NAND gates when the clock is high. Thus there is no way that data can pass through the device except as controlled by the clock. With the clock high, data will enter the J and K NAND gates. If this data is oriented to cause the flip-flop to change state on clocking, a "0" will be input to either the B or D AND gate. This "0" will not disturb the output because the "1" fed back from the other output to the C or F AND gate will predominate. The "1" coupled from either G or H will have no effect on the outputs in this situation as it is ANDED with a "0" from the other output. When the clock is taken low, J and K are disabled, and at the same time, whichever of C or F was causing their respective output to be "on", will be taken low then causing the output to go "off". An internal node is cross-coupled to the opposite side which then turns the "off" side "on". Thus this logic circuit performs its desired function.

Figure 11. BL54L67/BL54L68 Logic Diagram

One potential ac race exists which must be designed in such a manner as to control the outcome. This race is best described by looking at the Figure 12 circuit schematic. On the negative-going clock, either Q5 or Q20 will be turned off, whichever is "on". Let us just consider the case with Q5 going "off". Its collector will rise and hence allow base current to turn on Q19. This must turn Q19 on prior to the time Q28 goes "off" and turns Q6 "on". The turn-off impedances R1 and R2 and the required voltage swings are used to fix the race. Q5 collector must swing only a few hundred millivolts whereas Q28 collector must swing about 1.3 volts. Hence the race can easily be controlled. The proposed design sets R1 = R2 = 18K ohms. Reducing R1 and R2 is detrimental to the race. So, in the lab, values as low as 6K ohms proved sufficient to maintain the race. Thus, a race problem was avoided.

Advantages of the proposed flip-flop design over the original flip-flop design are:

- 1) Logic state of J-K inputs may be changed when clock pulse is high if a prescribed setup time is observed.

- 2) Clock pulse can go to a negative voltage without changing the information at the outputs Q and  $\overline{Q}$ .

- 3) The maximum zero level (0.7 V) of the clock and J-K inputs are the same.

- 4) Increased high state fan-out capabilities due to the Darlington pull up.

- 5) Increased clock frequency due to reduced gate delays to set up latches.

- 6)  $T_{Pd}$  "0" is faster.  $T_{Pd}$  "0" has been reduced from 2 to 1-1/2 propagation delays.

- Clamp diodes on all inputs. This will keep high currents out of flip-flop inputs for negative input transients.

- The device does not have a high temperature threshold problem for temperatures up to 473°K.

#### 2. Resistor Process-1000 Ohm-cm/cm

The 1000 ohm-cm/cm resistor process produces a penetration of 2-1/2 Hg lines and a surface concentration of 2.5 X  $10^{18}$  atoms/cc. (The phosphorus oxide from the emitter process is left over the resistor to act as a barrier to the movement of positive ions.)

24

The temperature coefficient for the 240 ohm-cm/cm resistor is 1760 ppm/K° and it is  $3016 \text{ ppm/K}^\circ$  for the 1000 ohm-cm/cm resistor. The resistor change,  $\Delta R$ , due to a change in temperature,  $\Delta T$ , is given by

# $\Delta R = F X R X \Delta T X 10^{-6}$

where F is the temperature coefficient given above and R is the resistor value at  $298^{\circ}$ K. The slight increase in the coefficient for the 1000 ohm-cm/cm resistor is due to the slightly lower surface concentration.

Page Intentionally Left Blank

## SECTION IV TESTING AND EVALUATION

#### A. PROBE TEST AND LOT QUALIFICATION

The primary product of a beam lead family is unmounted bars. These bars must be capable of operation over the full military temperature range,  $-55^{\circ}$ C to  $125^{\circ}$ C ( $218^{\circ}$ K to  $398^{\circ}$ K). To meet this criteria, the 100% probe test for beam lead bars must be as stringent as the final test for standard packaged parts. The probe test for standard product is normally used only as a screen to remove the catastrophic rejects. The various product categories are separated at final test. Guaranteeing ac performance is also a problem in beam lead testing because it is extremely difficult to perform switching and propagation delay measurements at probe on a production basis.

The decision was made to perform a full functional test as well as a guard-banded parametric test at the 100% probe test. The guard-bands are set to guarantee the electrical performance of the part over the temperature range specified. In addition to the 100% probe test, a sample from each diffusion lot is taken, mounted on headers and tested for full functional, parametric and ac performance. This sample test serves to qualify the switching and dynamic integrity of the lot since the parameters that effect switching times are diffusion lot dependent.

The beam bond strength is also established on a diffusion lot sample basis. The bar sample is bonded on a gold-plated Kovar substrate. The bars are positioned over a square hole in the Kovar. After a visual inspection to eliminate badly bonded bars from the test, the substrates are placed in the bond strength test machine shown in Figure 13. A square needle sized for the bar under test is inserted into the hole in the Kovar plate and brought to rest against the bar. Force is then exerted by the operator until the bar either breaks or the beams are pushed away from the substrate. The force necessary to cause the failure and the mode of failure are noted by the operator. The pressure is compared with a minimum requirement of 0.7 grams/mil of beam width  $(1.0 \times 10^6 \text{ newton/meter}^2)$ . This would set a minimum of 2.1 grams force (0.02 newtons) for each 3 mil (7.62 X  $10^{-3}$  cm) beam. Initial push-off tests have given the results shown in Table III. Refer to Figures 14 through 16 for format descriptions.

Figure 13. Beam Lead Push-Off Tester

| Format No. | No. of beams | Push-of | Sample size    |    |

|------------|--------------|---------|----------------|----|

|            |              | Average | Failure limits |    |

| 45         | 14           | 0.500   | 0.304 to 0.637 | 12 |

| 50         | 16           | 0.618   | 0.392 to 0.804 | 12 |

| 55         | 18           | 0.658   | 0.343 to 0.932 | 12 |

Table III. Bond Push-Off Test Strength

#### **B. DEVICE CHARACTERIZATION**

The mounted bars were subjected to complete dc (parametric and functional) and ac (switching and dynamic) testing as shown in the Appendix, at  $-55^{\circ}$ C,  $25^{\circ}$ C, and  $125^{\circ}$ C ( $218^{\circ}$ K,  $298^{\circ}$ K, and  $398^{\circ}$ K). These tests were used to screen thermal and ac rejects and to establish the guard-bands required at probe. The results of the evaluation tests in the form of mean values are given in Table IV. In general, the beam-leaded parts compare favorably with the standard low-power TTL.

Figure 14. Beam Lead Format 45

Figure 15. Beam Lead Format 50

Figure 16. Beam Lead Format 55

|                                    | ICCL VI TPHL TPLH<br>mÅ volts nsec nsec | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                  | <pre>&lt;1.02 &lt;-1.5 &lt;60 &lt;60<br/>0.60 -1.237 37.572 45.175<br/>0.656 -1.317 43.504 31.552<br/>0.805 -1.370 49.893 22.490</pre> | <0.51                                                                                                                                  | <0.65                                                                                              | IL, mA  | J or K or Clear Clock Min Max         | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                 | <pre>&lt;-0.18 &lt;-0.54 &lt;-0.72 &gt;-3&lt;-15<br/>-0.025 -0.053 -0.094 -7.299<br/>-0.029 -0.059 -0.113 -8.254<br/>-</pre> | tpHL, nsec | Preset Preset<br>Clock or Clear or Clear | <pre>&lt;150 &lt;150 &lt;150 &lt;200 40.909 47.732 56.384 39.459 44.475 50.474 52.143 61.422 64.671</pre> | <ul> <li>&lt;150</li> <li>&lt;150</li> <li>&lt;150</li> <li>&lt;200</li> <li>53.154</li> <li>60.056</li> <li>53.154</li> <li>59.664</li> </ul> |

|------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Beam Lead Evaluation (Mean Values) | los lcch<br>mA                          | >-3 <-15 <0.8<br>-9.146 0.578<br>-10.045 0.595<br>-10.374 0.612                                                                        | >-3 <-15 <0.4<br>-8.526 0.232<br>-9.622 0.254<br>-10.102 -                                                                             | >-3 <-15 <0.33<br>-7.701 0.115<br>-9.141 0.128<br>-9.627 0.132                                                                         | >-3<-15<0.34<br>-8.4590.334<br>-9.5770.347                                                         | -       | Volts Volts<br>Volts Volts<br>Max Min | <ul> <li>&lt;0.3</li> <li>&gt;2.4</li> <li>0.189</li> <li>3.241</li> <li>0.166</li> <li>3.058</li> <li>0.130</li> <li>2.805</li> </ul> | <pre>&lt;0.3 &gt;2.4 0.203 3.026 0.177 2.956</pre>                                                                           | tpLH, nsec | Preset<br>or Clear                       | <75<br>43.87<br>31.049<br>36.038                                                                          | <75<br>54.073<br>43.028                                                                                                                        |

| Lead Evaluation                    | lıL<br>mA                               | <pre>~ -0.18<br/>-0.116<br/>-0.128<br/>-0.138</pre>                                                                                    | <pre>&lt;-0.18 &lt;-0.103 -0.103 -0.115 -0.125</pre>                                                                                   | <pre>&lt; -0.18 &lt; -0.118 -0.118 -0.118 -0.129</pre>                                                                                 | <pre>&lt; -0.18 </pre>                                                                             | Pu      | et<br>ear Clock                       | 0 <40<br>3.110<br>2.638<br>5 2.707                                                                                                     | 0 <40<br>22 1.761<br>22 1.609<br>-                                                                                           | tPLH       | Clock                                    | <75<br>44.448<br>35.512<br>33.395                                                                         | <75<br>62.313<br>48.032                                                                                                                        |

| Table IV. Beam                     | VOL VOH<br>volts volts                  | <ul> <li>&lt;0.3</li> <li>&gt;2.4</li> <li>0.182</li> <li>2.932</li> <li>0.162</li> <li>2.882</li> <li>0.135</li> <li>2.799</li> </ul> | <ul> <li>&lt;0.3</li> <li>&gt;2.4</li> <li>0.181</li> <li>3.03</li> <li>0.157</li> <li>3.012</li> <li>0.135</li> <li>2.816</li> </ul>  | <ul> <li>&lt;0.3</li> <li>&gt;2.4</li> <li>0.196</li> <li>2.810</li> <li>0.148</li> <li>2.845</li> <li>0.137</li> <li>2.813</li> </ul> | <ul> <li>&lt;0.3 &gt;2.4</li> <li>0.170 2.879</li> <li>0.150 2.919</li> <li>0.127 2.806</li> </ul> | HII, mA | J or K or Clear                       | <10 <30<br><br>- 1.175                                                                                                                 | <pre>&lt;10 &lt;30 </pre> <pre>&lt;10 &lt;30 </pre>                                                                          |            | VI<br>volts                              | <pre>&lt;-1.5 -1.029 -1.101 -1.101</pre>                                                                  | <ul><li>&lt;-1.5</li><li>-0.896</li><li>-0.981</li></ul>                                                                                       |

|                                    | HII<br>THE                              | <10<br>5.493<br>4.273<br>3.732                                                                                                         | <10<br>4.015<br>6.167                                                                                                                  | <10<br>2.745<br>2.026<br>1.868                                                                                                         | <10<br>4.671<br>3.967<br>3.258                                                                     | I, mA   | Preset<br>Clear-Clock                 | <pre>&lt;200</pre>                                                                                                                     | <pre>&lt;200</pre>                                                                                                           |            | AC                                       | <1.44<br>0.997<br>1.086<br>1.071                                                                          | <2.88<br>1.344<br>1.513                                                                                                                        |

|                                    | Ι                                       | <100<br>8.411<br>7.197<br>5.479                                                                                                        | <100<br>3.719<br>6.850                                                                                                                 | <pre>&lt;100 5.996 3.330 4.734</pre>                                                                                                   | <ul><li>&lt; 100</li><li>9.067</li><li>9.665</li><li>6.699</li></ul>                               | -       | J or K                                | <pre>&gt; 100</pre>                                                                                                                    | ∨<br>1 1 1 1                                                                                                                 |            | TA                                       | Spec<br>125°C<br>25°C                                                                                     | Spec<br>125°C<br>25°C                                                                                                                          |

|                                    | TA                                      | Spec<br>125°C<br>25°C<br>–55°C                                                                                                         | Spec<br>125°C<br>25°C<br>–55°C                                                                                                         | Spec<br>125°C<br>25°C                                                                                                                  | Spec<br>Spec<br>125°C<br>25°C                                                                      |         | TA                                    | Spec<br>125°C<br>25°C<br>–55°C                                                                                                         | Spec<br>125°C<br>-55°C                                                                                                       |            |                                          | w <b>←</b> 1                                                                                              | 0 <b>–</b> 1                                                                                                                                   |

|                                    | Circuit                                 | BL54L00                                                                                                                                | BL54L20                                                                                                                                | BL54L30                                                                                                                                | BL54L55                                                                                            |         | Circuit                               | BL54L67                                                                                                                                | BL54L68                                                                                                                      |            | Circuit                                  | BL54L67                                                                                                   | BL54L68                                                                                                                                        |

Report No. 03-72-27

31

\*Test on BL54L68 at  $-55^{\circ}$ C was invalid due to frosting of package.

These results are for a sample size of 50 pieces.

Some problems were encountered in the testing of the parts at  $-55^{\circ}$ C (218°K). The equipment used to lower the ambient temperature employs compressed nitrogen gas. Although the gas is relatively dry, a frost forms on the parts. This causes a problem because of the fine line definition on the headers shown in Figure 7, particularly on the low current dc and all ac measurements. To overcome the problem, Dow Corning 62-047WE, Junction Coating Resin was used to coat the top of the headers. Several parts were damaged in this operation because of operator error in using excessive air pressure to spray the parts. The high pressure forced the face of the bars into contact with metallization on the header causing an electrical short circuit. Further testing needs to be performed on the coating method to be used on future beam lead assemblies. Most of the units used for the evaluation were not coated because of this problem. The incompleteness of the data in Table IV reflects inaccurate data caused by the problem of units frosting at low temperature.

## SECTION V RESULTS

The objective of the program to beam lead selected parts of the low-power TTL (54L) family has been met. The circuits and electrical performance reflected in the data sheets (Appendix) meet or exceed the standard part type's values. This inventory of parts now forms a base for use in systems in which heat, power, size, weight, and reliability are controlling factors.

Also, the process has been established for processing future parts to be added to the beam-leaded low-power TTL family.

APPENDIX BEAM LEAD CIRCUITS SCHEMATICS AND PHOTOGRAPHS

Page Intentionally Left Black

Page Intentionally Left Blank

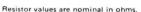

schematic (each gate)

# **BEAM-LEAD** LOW-POWER TTL CHIPS

## **CIRCUIT TYPES BL54LOOY, BL74LOOY** QUADRUPLE 2-INPUT POSITIVE-NAND GATES

- BL54L00Y/BL74L00Y Chips When Assembled Display Characteristics Similar to SN54L00/SN74L00

- Silicon Nitride Sealed Junction

- **Gold Beams**

- Available in Chip Form or as Part of a Complex Logic Assembly

- **Diode-Clamped Inputs**

20 45 OUTPUT 12 GND

1271

PRELIMINARY DATA SHEET: Supplementary data may be published at a later date.

TEXAS INSTRUMENTS POST OFFICE BOX 5012 . DALLAS. TEXAS 75222

## CIRCUIT TYPES BL54LOOY, BL74LOOY QUADRUPLE 2-INPUT POSITIVE-NAND GATES

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1) .    |          | <br> | <br>8V             |

|---------------------------------------|----------|------|--------------------|

| Input voltage (see Note 1)            |          | <br> | <br>5.5 V          |

| Interemitter voltage (see Note 2) .   |          |      |                    |

| Operating free-air temperature range: | BL54L00Y |      | –55°C to 125°C     |

|                                       | BL74L00Y |      |                    |

| Storage temperature range             |          | <br> | <br>-65°C to 150°C |

NOTES: 1. Voltage values are with respect to network ground terminal.

2. This is the voltage between two emitters of a multiple-emitter input transistor.

#### recommended operating conditions

| and and the second of second | B   | BL54L00Y |     |      |     |      | UNIT |

|------------------------------------------------------------------------------------------------------------------|-----|----------|-----|------|-----|------|------|

|                                                                                                                  | MIN | NOM      | MAX | MIN  | NOM | MAX  |      |

| Supply voltage, V <sub>CC</sub>                                                                                  | 4.5 | 5        | 5.5 | 4.75 | 5   | 5.25 | V    |

| Normalized fan-out from each output, N                                                                           |     |          | 10  |      |     | 10   |      |

| Operating free-air temperature, TA                                                                               | -55 |          | 125 | 0    |     | 70   | °C   |

electrical characteristics over recommended operating free-air temperature range

|      | PARAMETER                                            | TEST CONDITIONS <sup>†</sup>                     | MIN                                      | MAX   | UNIT |

|------|------------------------------------------------------|--------------------------------------------------|------------------------------------------|-------|------|

| VIH  | High-level input voltage                             |                                                  | 2                                        |       | V    |

| VIL  | Low-level input voltage                              |                                                  |                                          | 0.7   | V    |

| VI   | Input clamp voltage                                  | $V_{CC} = MIN$ , $I_I = -8 mA$                   | 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1. | - 1.5 | V    |

| VOH  | High-level output voltage                            | $V_{CC} = MIN, V_I = 0.7 V, I_{OH} = -100 \mu A$ | 2.4                                      |       | V    |

| VOL  | Low-level output voltage                             | $V_{CC} = MIN, V_I = 2V, I_{OL} = 2 mA$          |                                          | 0.3   | V    |

| 1    | Input current at maximum input voltage               | $V_{CC} = MAX, V_I = 5.5 V$                      | 1.1.1.1                                  | 100   | μA   |

| Чн   | High-level input current                             | $V_{CC} = MAX, V_I = 2.4 V$                      |                                          | 10    | μA   |

| IL   | Low-level input current                              | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.3 V    |                                          | -0.18 | mA   |

| los  | Short-circuit output current §                       | $V_{CC} = MAX, V_I = 0$                          | -3                                       | -15   | mA   |

| ССН  | Supply current, high-level output (average per gate) | V <sub>CC</sub> = MAX, All inputs at 0 V         | 212.2                                    | 0.2   | mA   |

| ICCL | Supply current, low-level output (average per gate)  | V <sub>CC</sub> = MAX, All inputs at 5 V         | 200                                      | 0.51  | mA   |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type. <sup>§</sup> Not more than one output should be shorted at a time.

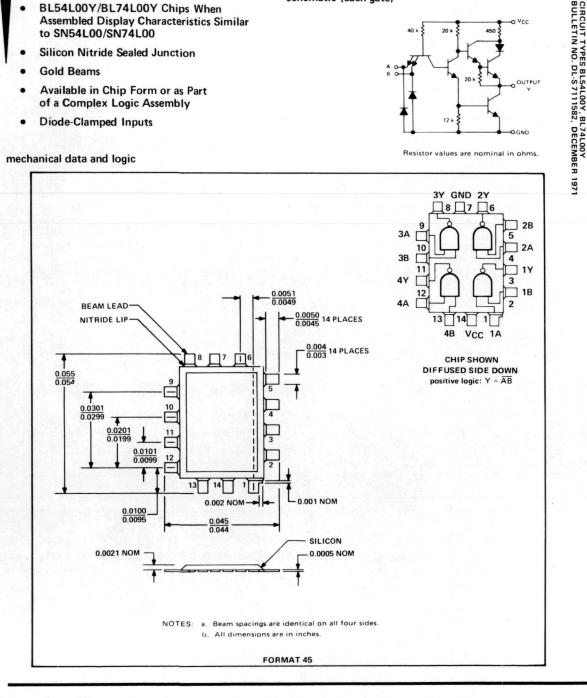

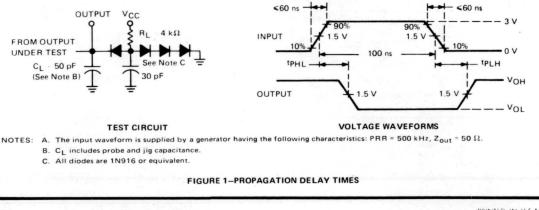

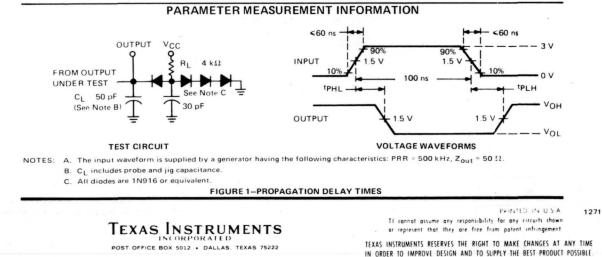

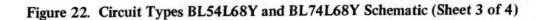

## switching characteristics, $V_{CC} = 5 V$ , $T_A = 25^{\circ}C$ , N = 10

|             | PARAMETER                                        | TEST CONDITIONS                                                      | MIN | TYP | MAX | UNIT |

|-------------|--------------------------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| <b>tPLH</b> | Propagation delay time, low-to-high-level output |                                                                      |     | 35  | 60  | ns   |

| TPHL        | Propagation delay time, high-to-low-level output | $C_L = 50 \text{ pF}, R_L = 4 \text{ k}\Omega, \text{ See Figure 1}$ |     | 31  | 60  | ns   |

Figure 17. Circuit Types BL54L00Y and BL74L00Y Schematic (Sheet 2 of 2)

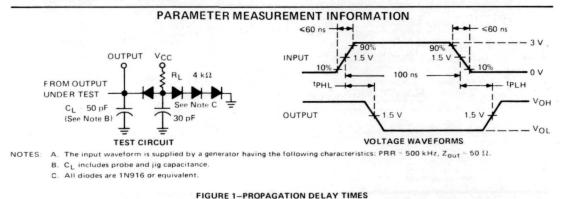

# BEAM-LEAD LOW-POWER TTL CHIPS

## CIRCUIT TYPES BL54L20Y, BL74L20Y DUAL 4-INPUT POSITIVE-NAND GATES

schematic (each gate) CIRCUIT TYPES BL54L20Y, BL74L20Y BULLETIN NO. DL-S 7111583, DECEMBER 1971 BL54L20Y/BL74L20Y Chips When Assembled Display Characteristics Similar to SN54L20/SN74L20 Silicon Nitride Sealed Junction **Gold Beams** OUTPUT Available in Chip Form or as Part of a Complex Logic Assembly **Diode-Clamped Inputs** . Resistor values are nominal in ohms mechanical data and logic 1Y 口6 2Y GND 1D 2AC 5 ] 1C 10 2B 4 D NC 11 NC 🗌 3 0.0051 🗋 1B 12 2C [ 2 BEAM LEAD 0.0050 0.0045 14 PLACES NITRIDE LIP 13 2D VCC 1A 0.004 0.003 14 PLACES NC-No internal connection CHIP SHOWN 0.055 DIFFUSED SIDE DOWN positive logic:  $Y = \overline{ABCD}$ 4 0.0301 10 -1 0.0201 11 + 0.0101 12 13 14 ıΠ 0.001 NOM 0.002 NOM 0.0100 0.045 SILICON 0.0021 NOM 0.0005 NOM NOTES: a. Beam spacings are identical on all four sides. b. All dimensions are in inches. FORMAT 45

1271

PRELIMINARY DATA SHEET: Supplementary data may be published at a later date. TEXAS INSTRUMENTS

# CIRCUIT TYPES BL54L20Y, BL74L20Y DUAL 4-INPUT POSITIVE-NAND GATES

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage Voc (see Note 1)       |   |     |     |     |    |      |     |  |   |    |   |   |   |   |   |   |   |   |    |     |      | 0.1    | , |

|---------------------------------------|---|-----|-----|-----|----|------|-----|--|---|----|---|---|---|---|---|---|---|---|----|-----|------|--------|---|

| Supply voltage, VCC (see Note 1) .    | • |     | •   | •   | •  |      |     |  | • | •  | • | • | • | • | • | • | • | • |    |     |      | . 81   | / |

| Input voltage (see Note 1)            |   |     | •   |     |    | •    |     |  |   | •, |   |   |   |   |   |   |   |   |    |     |      | 5.5 \  | 1 |

| Interemitter voltage (see Note 2) .   |   |     | . ' |     |    | •    |     |  |   |    |   |   |   |   |   |   |   |   |    |     |      | 5.5 \  | 1 |

| Operating free-air temperature range: | B | L54 | L2  | 20Y | Ci | rcu  | its |  |   |    |   |   |   |   |   |   |   |   | -5 | 5°( | c to | 125°C  | 2 |

|                                       | B | L74 | L2  | 20Y | Ci | ircu | its |  |   |    |   |   |   |   |   |   |   |   |    | 0°  | C t  | o 70°C | ; |

| Storage temperature range             |   |     |     | •   |    | •    |     |  |   |    |   |   |   |   |   |   |   |   | -6 | 5°C | to   | 150°C  | ; |

|                                       |   |     |     |     |    |      |     |  |   |    |   |   |   |   |   |   |   |   |    |     |      |        |   |

NOTES: 1. Voltage values are with respect to network ground terminal. 2. This is the voltage between two emitters of a multiple-emitter input transistor.

#### recommended operating conditions

|                                        | В                                       | L54L20 | Y   | В    | UNIT          |      |    |

|----------------------------------------|-----------------------------------------|--------|-----|------|---------------|------|----|

|                                        | MIN                                     | NOM    | MAX | MIN  | NOM           | MAX  |    |

| Supply voltage, V <sub>CC</sub>        | 4.5                                     | 5      | 5.5 | 4.75 | 5             | 5.25 | V  |

| Normalized fan-out from each output, N | * . · · · · · · · · · · · · · · · · · · |        | 10  | 1    | in the second | 10   |    |

| Operating free-air temperature, TA     | -55                                     | 17     | 125 | 0    |               | 70   | °C |

electrical characteristics over recommended operating free-air temperature range

|      | PARAMETER                                            | TEST CONDITIONS <sup>†</sup>                           | MIN | MAX   | UNIT |

|------|------------------------------------------------------|--------------------------------------------------------|-----|-------|------|

| VIH  | High-level input voltage                             |                                                        | 2   |       | v    |

| VIL  | Low-level input voltage                              |                                                        |     | 0.7   | V    |

| VI   | Input clamp voltage                                  | $V_{CC} = MIN$ , $I_I = -8 \text{ mA}$                 | 2   | -1.5  | V    |

| VOH  | High-level output voltage                            | $V_{CC} = MIN$ , $V_I = 0.7 V$ , $I_{OH} = -100 \mu A$ | 2.4 |       | V    |

| VOL  | Low-level output voltage                             | $V_{CC} = MIN$ , $V_I = 2V$ , $I_{OL} = 2 mA$          |     | 0.3   | V    |

| 4    | Input current at maximum input voltage               | V <sub>CC</sub> = MAX, V <sub>I</sub> = 5.5 V          |     | 100   | μA   |

| Чн   | High-level input current                             | V <sub>CC</sub> = MAX, V <sub>I</sub> = 2.4 V          |     | 10    | μA   |

| 11L  | Low-level input current                              | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.3 V          |     | -0.18 | mA   |

| los  | Short-circuit output current §                       | $V_{CC} = MAX, V_I = 0$                                | -3  | -15   | mA   |

| ССН  | Supply current, high-level output (average per gate) | V <sub>CC</sub> = MAX, All inputs at 0 V               | 100 | 0.2   | mA   |

| ICCL | Supply current, low-level output (average per gate)  | V <sub>CC</sub> = MAX, All inputs at 5 V               |     | 0.51  | mA   |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device types.

SNot more than one output should be shorted at a time.

## switching characteristics, $V_{CC}$ = 5 V, TA = 25°C, N = 10

TEXAS INSTRUMENTS

OST OFFICE BOX 5012 . DALLAS. TEXAS 75222

|             | PARAMETER                                        | TEST CONDITIONS                                                      | MIN  | TYP | MAX | UNIT |

|-------------|--------------------------------------------------|----------------------------------------------------------------------|------|-----|-----|------|

| <b>tPLH</b> | Propagation delay time, low-to-high-level output |                                                                      | 1.1  | 35  | 60  | ns   |

| TPHL        | Propagation delay time, high-to-low-level output | $-$ C <sub>L</sub> = 50 pF, R <sub>L</sub> = 4 k\Omega, See Figure 1 | 15 E | 31  | 60  | ns   |

## PARAMETER MEASUREMENT INFORMATION

PPINTED IN U.S.A. 127 TI cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

TEXAS INSTRUMENTS RESERVES THE RIGHT TO MAKE CHANGES AT ANY TIME IN ORDER TO IMPROVE DESIGN AND TO SUPPLY THE BEST PRODUCT POSSIBLE.

Figure 18. Circuit Types BL54L20Y and BL74L20Y Schematic (Sheet 2 of 2)

## CIRCUIT TYPES BL54L30Y, BL74L30Y 8-INPUT POSITIVE-NAND GATES

1271

PRELIMINARY DATA SHEET: Supplementary data may be published at a later date. TEXAS INSTRUMENTS

POST OFFICE BOX 5012 . DALLAS. TEXAS 75222

# CIRCUIT TYPES BL54L30Y, BL74L30Y 8-INPUT POSITIVE-NAND GATES

| absolute maximum ratings over | operating free-air temper | ature range (unless otherwise noted) |

|-------------------------------|---------------------------|--------------------------------------|

|                               |                           |                                      |

| Supply voltage, VCC (see Note 1)      |                          |                |

|---------------------------------------|--------------------------|----------------|

|                                       |                          |                |

| 1                                     |                          |                |

| Operating free-air temperature range: |                          |                |

|                                       | <b>BL74L30Y</b> Circuits | 0°C to 70°C    |

| Storage temperature range             |                          | -65°C to 150°C |

NOTES: 1. Voltage values are with respect to network ground terminal.

2. This is the voltage between two emitters of a multiple-emitter input transistor.

#### recommended operating conditions

|                                        | 6                                        | BL54L30Y |     |      |     |      | UNIT |

|----------------------------------------|------------------------------------------|----------|-----|------|-----|------|------|

|                                        | MIN                                      | NOM      | MAX | MIN  | NOM | MAX  | UNIT |

| Supply voltage, V <sub>CC</sub>        | 4.5                                      | 5        | 5.5 | 4.75 | 5   | 5.25 | V    |

| Normalized fan-out from each output, N | 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1 |          | 10  | 100  |     | 10   |      |

| Operating free-air temperature, TA     | -55                                      | 1995     | 125 | 0    |     | 70   | ° C  |

electrical characteristics over recommended operating free-air temperature range

|      | PARAMETER                                            | TEST CONDITIONS <sup>†</sup>                     | MIN | MAX    | UNIT |

|------|------------------------------------------------------|--------------------------------------------------|-----|--------|------|

| VIH  | High-level input voltage                             |                                                  | 2   | 1      | v    |

| VIL  | Low-level input voltage                              |                                                  |     | 0.7    | V    |

| VI   | Input clamp voltage                                  | $V_{CC} = MIN$ , $I_I = -8 \text{ mA}$           |     | - 1.5  | V    |

| VOH  | High-level output voltage                            | $V_{CC} = MIN, V_I = 0.7 V, I_{OH} = -100 \mu A$ | 2.4 |        | V    |

| VOL  | Low-level output voltage                             | $V_{CC} = MIN$ , $V_I = 2V$ , $I_{OL} = 2mA$     |     | 0.3    | V    |

| 4    | Input current at maximum input voltage               | V <sub>CC</sub> = MAX, V <sub>I</sub> = 5.5 V    |     | 100    | μA   |

| ЧΗ   | High-level input current                             | V <sub>CC</sub> = MAX, V <sub>I</sub> = 2.4 V    |     | 10     | μA   |

| IL.  | Low-level input current                              | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.3 V    |     | - 0.18 | mA   |

| los  | Short-circuit output current §                       | $V_{CC} = MAX, V_I = 0$                          | -3  | -15    | mA   |

| ССН  | Supply current, high-level output (average per gate) | V <sub>CC</sub> = MAX, All inputs at 0 V         |     | 0.33   | mA   |

| ICCL | Supply current, low-level output (average per gate)  | V <sub>CC</sub> = MAX, All inputs at 5 V         |     | 0.51   | mA   |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

Not more than one output should be shorted at a time.

## switching characteristics, V<sub>CC</sub> = 5 V, T<sub>A</sub> = $25^{\circ}$ C, N = 10

|             | PARAMETER                                        | TEST CONDITIONS                                                      | MIN | TYP | MAX | UNIT |

|-------------|--------------------------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| <b>tPLH</b> | Propagation delay time, low-to-high-level output | 0 50 5 D 410 8-5                                                     |     | 35  | 60  | ns   |

| TPHL        | Propagation delay time, high-to-low-level output | $C_L = 50 \text{ pF}, R_L = 4 \text{ k}\Omega, \text{ See Figure 1}$ |     | 70  | 100 | ns   |

Figure 19. Circuit Types BL54L30Y and BL74L30Y Schematic (Sheet 2 of 2)

1271

PRELIMINARY DATA SHEET: Supplementary data may be published at a later date. TEXAS INSTRUMENTS

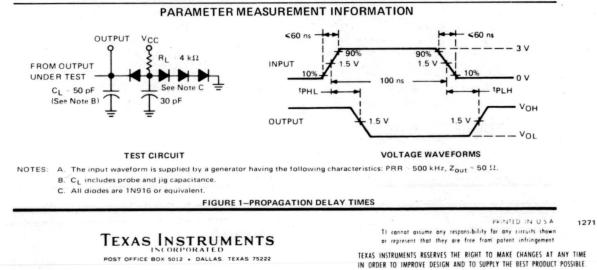

Figure 20. Circuit Types BL54L55Y and BL74L55Y Schematic (Sheet 1 of 2)

## **CIRCUIT TYPES BL54L55Y, BL74L55Y** 2-WIDE 4-INPUT AND-OR-INVERT GATES

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1) .    |   |     |     |      |    |      |      |  |  |  |  |  |   |  |  |    |     |      | 8 V    |  |

|---------------------------------------|---|-----|-----|------|----|------|------|--|--|--|--|--|---|--|--|----|-----|------|--------|--|

| Input voltage (see Note 1)            |   |     |     |      |    |      |      |  |  |  |  |  |   |  |  |    |     |      | 5.5 V  |  |

| Interemitter voltage (see Note 2) .   |   |     |     |      |    |      |      |  |  |  |  |  |   |  |  |    |     |      | 5.5 V  |  |

| Operating free-air temperature range: | B | L54 | 415 | 55Y  | C  | ircu | iits |  |  |  |  |  |   |  |  |    |     |      | 125°C  |  |

|                                       | B | L74 | 4L5 | 55 Y | Ci | ircu | its  |  |  |  |  |  |   |  |  |    | 0   | °C t | o 70°C |  |

| Storage temperature range             | • |     |     |      |    |      |      |  |  |  |  |  | • |  |  | -6 | 5°( | C to | 150°C  |  |

|                                       |   |     |     |      |    |      |      |  |  |  |  |  |   |  |  |    |     |      |        |  |

NOTES: 1. Voltage values are with respect to network ground terminal.

2. This is the voltage between two emitters of a multiple-emitter input transistor.

#### recommended operating conditions

|                                        | B   | L54L55 | Y   | B    | L74L55 | Y    |      |

|----------------------------------------|-----|--------|-----|------|--------|------|------|

|                                        | MIN | NOM    | MAX | MIN  | NOM    | MAX  | UNIT |

| Supply voltage, V <sub>CC</sub>        | 4.5 | 5      | 5.5 | 4.75 | 5      | 5.25 | V    |

| Normalized fan-out from each output, N |     |        | 10  |      |        | 10   |      |

| Operating free-air temperature, TA     | -55 |        | 125 | 0    |        | 70   | C    |

electrical characteristics over recommended operating free-air temperature range

|     | PARAMETER                                            | TEST CONDITIONS <sup>†</sup>                     | MIN | MAX   | UNIT |

|-----|------------------------------------------------------|--------------------------------------------------|-----|-------|------|

| VIH | High-level input voltage                             |                                                  | 2   |       | V    |

| VIL | Low-level input voltage                              |                                                  |     | 0.7   | V    |

| VI  | Input clamp voltage                                  | $V_{CC} = MIN$ , $I_I = -8 \text{ mA}$           |     | -1.5  | V    |

| VOH | High-level output voltage                            | $V_{CC} = MIN, V_I = 0.7 V, I_{OH} = -100 \mu A$ | 2.4 |       | V    |

| VOL | Low-level output voltage                             | $V_{CC} = MIN$ , $V_I = 2V$ , $I_{OL} = 2 mA$    |     | 0.3   | V    |

| 4   | Input current at maximum input voltage               | V <sub>CC</sub> = MAX, V <sub>I</sub> = 5.5 V    |     | 100   | μA   |

| Чн  | High-level input current                             | V <sub>CC</sub> = MAX, V <sub>I</sub> = 2.4 V    |     | 10    | μA   |

| 1L  | Low-level input current                              | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.3 V    |     | -0.18 | mA   |

| los | Short-circuit output current §                       | $V_{CC} = MAX, V_I = 0$                          | -3  | -15   | mA   |

| ССН | Supply current, high-level output (average per gate) | V <sub>CC</sub> = MAX, All inputs at 0 V         |     | 0.4   | mA   |

| CCL | Supply current, low-level output (average per gate)  | V <sub>CC</sub> = MAX, All inputs at 5 V         |     | 0.65  | mA   |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.  $\frac{8}{5}$  Not more than one output should be shorted at a time.

#### switching characteristics, VCC = 5 V, TA = 25°C, N = 10

|                  | PARAMETER                                        | TEST CONDITIONS                                                          | MIN | TYP | MAX | UŅIT |

|------------------|--------------------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

| <b>tPLH</b>      | Propagation delay time, low-to-high-level output | C = EQ =E R = A k() See Figure 1                                         |     | 50  | 90  | ns   |

| <sup>t</sup> PHL | Propagation delay time, high-to-low-level output | $-$ C <sub>L</sub> = 50 pF, R <sub>L</sub> = 4 k $\Omega$ , See Figure 1 |     | 35  | 60  | ns   |

Figure 20. Circuit Types BL54L55Y and BL74L55Y Schematic (Sheet 2 of 2)

Report No. 03-72-27

## **BEAM-LEAD** LOW-POWER TTL CHIPS

## CIRCUIT TYPES BL54L67Y, BL74L67Y J-K EDGE-TRIGGERED FLIP-FLOPS

- BL54L67Y/BL74L67Y Chips When Assembled Can Replace SN54L72/SN74L72 in Most Applications

- Silicon-Nitride-Sealed Junctions

- **Gold Beams** .

- Available in Chip Form or as Part of a **Complex Logic Assembly**

- **Diode-Clamped Inputs**

#### description

These edge-triggered flip-flop circuits feature gated J and K inputs and asynchronous preset and clear inputs. When the clock goes high, the inputs are enabled and data will be accepted. The logic levels of the J and K inputs may be allowed to change while the clock pulse is high and the bistable will perform according to the truth table, provided that minimum

| INPUTS | AT t <sub>n</sub> | OUTPUTS | SAT tn+1 |

|--------|-------------------|---------|----------|

| J      | ĸ                 | ٩       | ā        |

| L      | L                 | Qn      | ān       |

| L      | н                 | L       | н        |

| н      | L                 | н       | L        |

| н      | н                 | ān      | Qn       |

CIRCUIT TYPES BL54L67Y, BL74L67Y BULLETIN NO. DL-S 7211635, JANUARY 1972

| J = J1 • J2 • J3                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------|

| K = K1·K2·K3                                                                                                              |

| t <sub>n</sub> = bit time before clock pulse                                                                              |

| tn+1 = bit time after clock pulse                                                                                         |

| H = high level, L = low level                                                                                             |

| $Q_n = $ level of output Q at $t_n$                                                                                       |

| $\overline{\mathbf{Q}}_{\mathbf{n}}$ = complement of $\mathbf{Q}_{\mathbf{n}}$ or level of output $\overline{\mathbf{Q}}$ |

| at t <sub>n</sub>                                                                                                         |

| Low input to preset sets Q to high level.                                                                                 |

| Low input to clear resets Q to low level.                                                                                 |

|                                                                                                                           |

Preset and clear are independent of clock.

setup and hold times are observed. Input data is transferred to the outputs on the negative-going edge of the clock pulse.

The BL54L67Y chip is characterized for operation over the full military temperature range of -55°C to 125°C; the BL74L67Y is characterized for operation from 0°C to 70°C.

#### mechanical data

172

PRELIMINARY DATA SHEET: Supplementary data may be published at a later date.

TEXAS INSTRUMENTS POST OFFICE BOX 5012 . DALLAS, TEXAS 75222

Figure 21. Circuit Types BL54L67Y and BL74L67Y Schematic (Sheet 1 of 4)

## CIRCUIT TYPES BL54L67Y, BL74L67Y J-K EDGE-TRIGGERED FLIP-FLOPS

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Sup  | ply voltage,   | Vcc (    | see N  | ote 1  | )   |   |    |    |    |    |     |     |      |  |  |  |   |  |    |  |  |     |     |      | 8 V   |

|------|----------------|----------|--------|--------|-----|---|----|----|----|----|-----|-----|------|--|--|--|---|--|----|--|--|-----|-----|------|-------|

| Inpu | ut voltage     |          |        |        |     |   |    |    |    |    |     |     |      |  |  |  |   |  |    |  |  |     |     |      | 5.5 V |

| Inte | eremitter vol  | Itage (s | ee N   | ote 2  | )   |   |    |    |    |    |     |     |      |  |  |  | ÷ |  | ۰. |  |  |     |     |      | 5.5 \ |

| Ope  | erating free-a | ir temp  | peratu | ire ra | nge | : | BL | 54 | L6 | 7Y | C C | irc | uits |  |  |  |   |  |    |  |  | -55 | 5°C | to   | 125°  |

|      |                |          |        |        |     |   | BL | 74 | L6 | 7Y | C'C | irc | uits |  |  |  |   |  |    |  |  |     | 0°  | C to | 5 70° |

| Stor | rage tempera   | ature ra | inge   |        |     |   |    |    |    |    |     |     |      |  |  |  |   |  | ۰. |  |  | -65 | °C  | to   | 150°  |

2. This is the voltage between two emitters of a multiple-emitter input transistor.

#### recommended operating conditions

|                                                   | в   | L54L67 | Y   | В    | L74L67 | Y    | UNIT |

|---------------------------------------------------|-----|--------|-----|------|--------|------|------|

|                                                   | MIN | NOM    | MAX | MIN  | NOM    | MAX  |      |

| Supply voltage, V <sub>CC</sub>                   | 4.5 | 5      | 5.5 | 4.75 | 5      | 5.25 | V    |

| Normalized fan-out from each output, N            |     |        | 10  |      |        | 10   |      |

| Width of clock pulse, tw(clock)                   | 200 |        |     | 200  |        |      | ns   |

| Width of preset pulse, tw(preset)                 | 100 | 1      | -   | 100  |        |      | ns   |

| Width of clear pulse, tw(clear)                   | 100 | 1.1    |     | 100  |        |      | ns   |

| Input setup time, t <sub>setup</sub> (see Note 3) | 30  | 1.5    |     | 30   |        |      | ns   |

| Input hold time, thold (see Note 4)               | 0   |        |     | 0    |        |      | ns   |

| Operating free-air temperature, TA                | -55 |        | 125 | 0    |        | 70   | °C   |

|                                                   |     |        |     |      |        |      |      |

NOTES: 3. Setup time is the interval immediately preceeding the negative-going edge of the clock pulse during which interval the data to be recognized must be maintained at the input to ensure its recognition.

4. Hold time is the interval immediately following the negative going edge of the clock pulse during which interval the data to be recognized must be maintained at the input to ensure its continued recognition.

#### electrical characteristics over recommended operating free-air temperature range

|     | PARAMETER                              |                         | TEST CONDITIONS <sup>†</sup>                     | MIN | MAX   | UNIT |

|-----|----------------------------------------|-------------------------|--------------------------------------------------|-----|-------|------|

| VIH | High-level input voltage               |                         |                                                  | 2   |       | V    |

| VIL | Low-level input voltage                |                         |                                                  |     | 0.7   | V    |

| VI  | Input clamp voltage                    |                         | V <sub>CC</sub> = MIN, I <sub>I</sub> = -8 mA    |     | -1.5  | V    |

| VOH | High-level output voltage              |                         | V <sub>CC</sub> = MIN, I <sub>OH</sub> = -100 µA | 2.4 |       | V    |

| VOL | Low-level output voltage               |                         | V <sub>CC</sub> = MIN, I <sub>OL</sub> = 2 mA    | 2 A | 0.3   | V    |

|     |                                        | Any J or K              | V MAY V-EEV                                      |     | 100   |      |

| 4   | Input current at maximum input voltage | Preset, clear, or clock | $V_{CC} = MAX, V_I = 5.5 V$                      |     | · 200 | μA   |

|     |                                        | Any J or K              |                                                  |     | 10    |      |

| Чн  | High-level input current               | Preset or clear         | $V_{CC} = MAX, V_I = 2.4 V$                      |     | 30    | μA   |

|     |                                        | Clock                   | 1                                                |     | 40    |      |

|     |                                        | Any J or K              |                                                  |     | -0.18 |      |

| hL. | Low-level input current                | Preset or clear         | $V_{CC} = MAX, V_I = 0.3 V$                      |     | -0.54 | mA   |

|     |                                        | Clock                   |                                                  |     | -0.72 |      |

| los | Short-circuit output current ‡         |                         | V <sub>CC</sub> = MAX                            | -3  | -15   | mA   |

| 1CC | Supply current                         |                         | VCC = MAX, See Note 5                            |     | 1.44  | mA   |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type. <sup>‡</sup>Not more than one output should be shorted at a time.

NOTE 5: ICC is measured with outputs open, clock grounded, and all other inputs at 4.5 V.

# TEXAS INSTRUMENTS

172

Figure 21. Circuit Types BL54L67Y and BL74L67Y Schematic (Sheet 2 of 4)

# CIRCUIT TYPES BL54L67Y, BL74L67Y J-K EDGE-TRIGGERED FLIP-FLOPS

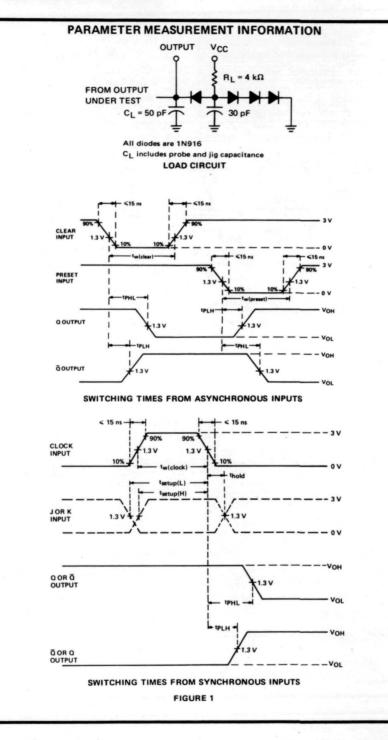

### switching characteristics, $V_{CC} = 5 V$ , $T_A = 25^{\circ}C$ , N = 10, see figure 1

| PARAMETERS       | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST                     | CONDITIONS                                      | MIN | түр | MAX        | UNIT |

|------------------|-----------------|----------------|--------------------------|-------------------------------------------------|-----|-----|------------|------|

| f <sub>max</sub> |                 |                | CL = 50 pF,              | $R_L = 4 k\Omega$                               |     | 10  |            | MHz  |

| <b>tPLH</b>      | Preset or clear | Q or Q         | CL = 50 pF,              | $R_L = 4 k\Omega$                               |     | 35  | 75         | ns   |

| <sup>t</sup> PHL | Preset or clear | ā or Q         | CL = 50 pF,<br>RL = 4 kΩ | $\frac{V_{I(clock)} = 2.4 V}{V_{I(clock)} = 0}$ | _   | 60  | 150<br>200 | ns   |

| <b>tPLH</b>      | Clock           | Q or Q         | CL = 50 pF,              | $R_L = 4 k\Omega$                               | 10  | 35  | 75         | ns   |

| <b>tPHL</b>      | Clock           | Q or Q         | CL = 50 pF,              | $R_L = 4 k\Omega$                               | 10  | 60  | 150        | ns   |

$\begin{cases} s_{max} \equiv maximum \ clock \ frequency \\ t_{pLH} \equiv propagation \ delay \ time, \ low-to-high-level \ output \\ t_{pHL} \equiv propagation \ delay \ time, \ high-to-low-level \ output \end{cases}$

functional block diagram

#### schematic

#### 172

TEXAS INSTRUMENTS

POST OFFICE BOX 5012 . DALLAS. TEXAS 75222

Figure 21. Circuit Types BL54L67Y and BL74L67Y Schematic (Sheet 3 of 4)

## CIRCUIT TYPES BL54L67Y, BL74L67Y J-K EDGE-TRIGGERED FLIP-FLOPS

TEXAS INSTRUMENTS INCORPORATED POST OFFICE BOX 5012 + DALLAS. TEXAS 75222 TI cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement. TEXAS INSTRUMENTS RESERVES THE RIGHT TO MAKE CHANGES AT ANY TIME IN ORDER TO IMPROVE DESIGN AND TO SUPPLY THE BEST PRODUCT POSSIBLE.

PRINTED IN USA

172

Figure 21. Circuit Types BL54L67Y and BL74L67Y Schematic (Sheet 4 of 4)

## BEAM-LEAD LOW-POWER TTL CHIPS

## CIRCUIT TYPES BL54L68Y, BL74L68Y DUAL J-K EDGE-TRIGGERED FLIP-FLOPS

CIRCUIT TYPES BL54L68Y, BL74L68Y BULLETIN NO. DL-S 7211634, JANUARY 1972

- BL54L68Y/BL74L68Y Chips When Assembled Can Replace SN54L73/SN74L73 in Most Applications

- Silicon-Nitride-Sealed Junctions

- Gold Beams

- Available in Chip Form or as Part of a Complex Logic Assembly

- Diode-Clamped Inputs

#### description

These edge-triggered dual flip-flop circuits featuren+1individual J, K, clock, and asynchronous clear inputs to $Q_n =$ each flip-flop. When the clock goes high, the inputs $\overline{Q}_n =$ are enabled and data will be accepted. The logic levelsof the J and K inputs may be allowed to change whileLowthe clock pulse is high and the bistable will performClearaccording to the truth table, provided that minimumsetup and hold times are observed. Input data istransferred to the outputs on the negative-going edge of the clock pulse.

| INPUT | SAT t <sub>n</sub> | OUTPUTS AT t |    |  |  |  |  |  |

|-------|--------------------|--------------|----|--|--|--|--|--|

| J     | к                  | ۵            | ā  |  |  |  |  |  |

| L     | L                  | Qn           | ā  |  |  |  |  |  |

| L     | н                  | L            | н  |  |  |  |  |  |

| н     | L                  | н            | L  |  |  |  |  |  |

| н     | н                  | ān           | Qn |  |  |  |  |  |

$\begin{array}{l} \mathfrak{r}_n = \mbox{bit time before clock pulse} \\ \mathfrak{t}_{n+1} = \mbox{bit time after clock pulse} \\ \mathbb{H} = \mbox{high level, } L = \mbox{low level} \\ \mathbb{Q}_n = \mbox{level of output } \mathbb{Q} \mbox{ at } \mathfrak{r}_n \\ \overline{\mathbb{Q}}_n = \mbox{complement of } \mathbb{Q}_n \mbox{ or level of output } \overline{\mathbb{Q}} \end{array}$