CONTRACT NAS9-9953 MSC \02271 DRL NO: MSC-T-575, LINE ITEM 72

CR-128536

SD 72-SA-0114-3

## MODULAR Space station

PHASE B EXTENSION

1 2 2 1 4

2-1

## INFORMATION MANAGEMENT ADVANCED DEVELOPMENT FINAL REPORT

Volume III: Digital Data Bus Breadboard

PREPARED BY PROGRAM ENGINEERING JULY 31, 1972

CONTRACT NAS9-9953 MSC 02471 DRL NO: MSC-T-575, LINE ITEM 72

SD 72-SA-0114-3

# MODULAR Space station

## PHASE B EXTENSION

## **INFORMATION MANAGEMENT ADVANCED DEVELOPMENT FINAL REPORT**

Volume III: Digital Data Bus Breadboard

31 JULY 1972 PREPARED BY PROGRAM ENGINEERING

Approved by

Kennell

James Madewell Director Space Applications Programs

i de la

12214 Lakewood Boulevard, Downey, California 90241

#### TECHNICAL REPORT INDEX/ABSTRACT

| CESSION NUN                                                                           | BER                  |                            |               |              |                      |          | DOCUMENT SE | CLASSIFI |         | DN .  |     |          |

|---------------------------------------------------------------------------------------|----------------------|----------------------------|---------------|--------------|----------------------|----------|-------------|----------|---------|-------|-----|----------|

| INFORMATI                                                                             | ON M                 | ANAGE                      |               |              |                      |          | FINAL REI   | PORT     |         | LIBR  | ARY | JSE ONLY |

| Gerber, (                                                                             | . R.                 | , et.a                     | al.           |              |                      |          |             |          |         |       |     |          |

| CODE                                                                                  |                      |                            |               | Y AND        | OTHER SO             | RCES     |             |          | DOCUMEN | TNUMB | ER  |          |

| QN085282 Space Division of North American<br>Rockwell Corporation, Downey, California |                      |                            |               | SD 72-S      | A-011                | 4-3      |             |          |         |       |     |          |

| PUBLICATION                                                                           | DATE                 |                            |               |              | CONTRAC              | NUMBER   |             |          |         |       |     |          |

| July                                                                                  | <u>, 31.</u>         | 1972                       |               |              |                      | NAS9-995 | 53          |          |         |       |     |          |

| MODULAR<br>*ADVANCEI<br>*DATA BUS                                                     | SPAC<br>DEV<br>5, *B | E STAT<br>ELOPMI<br>READBO | ENT,<br>DARD, | *DATA<br>*TE | A ACQUIS<br>CHNOLOGY | ITION,   | EMENT,      |          |         |       |     | <u> </u> |

| *SPECIFIC                                                                             | -                    |                            | -             |              |                      | ,        |             |          |         |       |     |          |

#### ABSTRACT

THIS DOCUMENT IS VOLUME III OF THE FINAL REPORT OF THE MODULAR SPACE STATION ADVANCED DEVELOPMENT STUDY. IT SUMMARIZES THE EFFORT AND RESULTS OF THE ANALYSIS AND BREADBOARDING OF A DATA ACQUISITION AND CONTROL SUBASSEMBLY (DACS) TO PROVIDE THE NECESSARY INTERFLOW OF DATA BETWEEN TWO CENTRAL PROCESSORS, SUBSYSTEMS AND EXPERIMENT EQUIPMENT. THE DACS WAS DEFINED TO INCLUDE THE DIGITAL DATA BUS (DDB) THE DATA BUS CONTROL UNIT (BDCU), AND THE REMOTE ACQUISITION AND CONTROL UNIT (RACU); THE FIRST TWO OF THESE WERE ANALYZED AND BREADBOARDED AS A PART OF THE EFFORT. THE PRIMARY OBJECTIVE OF THE DACS BREADBOARD IS TO VERIFY THE DIGITAL DATA BUS CONCEPT FOR THE MODULAR SPACE STATION. IT DEMONSTRATES THE AVAILABILITY OF TECHNOLOGY TO PROVIDE ACCURACY OF DATA TRANSFER, RECONFIGURABILITY, FAILURE TOLERANCE, LONG USEFUL LIFE, AND STANDARDIZATION OF INTERFACES.

#### FOREWORD

This document is one of a series required by Contract NAS9-9953, Exhibit C, Statement of Work for the Phase B Extension - Modular Space Station Program Definition. It has been prepared by the Space Division, North American Rockwell Corporation, and is submitted to the National Aeronautics and Space Administration's Manned Spacecraft Center, Houston, Texas, in accordance with the requirements of the Data Requirements List (DRL) MSC-T-575, Line Item 72.

This document is Volume III of the Modular Space Station Information Management System Advanced Development Technology Report, which has been prepared in the following six volumes:

| Ι   | IMS ADT Summary                               | SD72-SA-0114-1 |

|-----|-----------------------------------------------|----------------|

| II  | IMS ADT Communications Terminal<br>Breadboard | SD72-SA-0114-2 |

| III | IMS ADT Digital Data Bus Breadboard           | SD72-SA-0114-3 |

| IV  | IMS ADT Data Processing Assembly              | SD72-SA-0114-4 |

| v   | IMS ADT Software Assembly                     | SD72-SA-0114-5 |

#### ACKNOWLEDGEMENTS

The following persons have participated in the conduct of the IMS ADT tasks, and have contributed to this report:

| C. W. Roberts    | Experiment/Electronics Manager       |

|------------------|--------------------------------------|

| C. R. Gerber     | Information Systems Project Engineer |

| B. A. Logan, Jr. | Information Systems                  |

| E. Mehrbach      | Information Systems                  |

| D. W. Brewer     | Information Systems                  |

| V. R. Hodgson    | Information Systems                  |

The following subcontractors have supported the IMS ADT tasks in specialized areas:

| International Tel. & Tel<br>Nutley, New Jersey<br>B. Cooper, Proj. Mgr. | Communications Terminal B.B.<br>Data Bus BB |

|-------------------------------------------------------------------------|---------------------------------------------|

| Intermetrics<br>Cambridge, Mass.<br>J. Miller, Prog. Mgr.               | Data Processing Assy                        |

| System Develop. Corp<br>Santa Monica, Calif.<br>R. Bilek, Prog. Mrg.    | Data Processing Assy<br>Software Assy       |

| Gen'l Electric Corp.<br>Valley Forge, Pa.<br>R. Kirby, Prog. Mgr.       | Bulk Storage Technology                     |

| NR-Autonetics<br>Anaheim, Calif.<br>J. Jurison, Proj. Mgr.              | Data Bus BB<br>Data Processing Assy         |

Preceding page blank

PRECEDING PAGE BLANK NOT FILMED

### CONTENTS

| Section |                                                                                                                                                                                                                          | Page                                      |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 1       | I.I DACS REQUIREMENTS SUMMARY                                                                                                                                                                                            | .  - <br>.  - <br>.  -3                   |

| 2       | 2.1DIGITAL BUS2.2ANALOG BUS2.3COUPLING CONFIGURATION                                                                                                                                                                     | . 2-1<br>. 2-1<br>. 2-4<br>. 2-4<br>. 2-7 |

| 3       | 3.1INTRODUCTION AND SUMMARY.3.2RECOMMENDED DACS BREADBOARD                                                                                                                                                               | . 3-1<br>. 3-1<br>. 3-1                   |

| 4       | <ul> <li>DACS REDUNDANCY CONCEPTS</li> <li>4.1 INTRODUCTION AND SUMMARY OF<br/>REDUNDANCY REQUIREMENTS</li> <li>4.2 SUBSYSTEM MODELS AND CONFIGURATIONS</li> <li>4.3 DACS REDUNDANCY AND RELIABILITY CONCEPTS</li> </ul> | . 4-1<br>. 4-1<br>. 4-2                   |

| 5       | 5.1 GENERAL REQUIREMENTS                                                                                                                                                                                                 | . 5-l<br>. 5-l<br>. 5-2                   |

| 6       | 6.1 GENERAL REQUIREMENTS                                                                                                                                                                                                 | . 6-1<br>. 6-1<br>. 6-2                   |

## Preceding page blank

PRECEDING PAGE BLANK NOT FILMED

Section

| Page |

|------|

|------|

| 7 | DBCU BREADBOARD PERFORMANC   | e an  | D INT | ERFAC | CE |            |

|---|------------------------------|-------|-------|-------|----|------------|

|   | REQUIREMENTS                 | •     | •     | •     | •  | 7-1        |

|   | 7.1 ITEM DEFINITION .        | •     | •     | •     |    | 7-1        |

|   | 7.2 FUNCTIONAL DESCRIPTION   |       | • .   | •     | •  | 7-1        |

|   | 7.3 INTERFACE DEFINITION     | •     | •     |       |    | 7-1        |

|   | 7.4 PERFORMANCE              | •     |       |       |    | 7-14       |

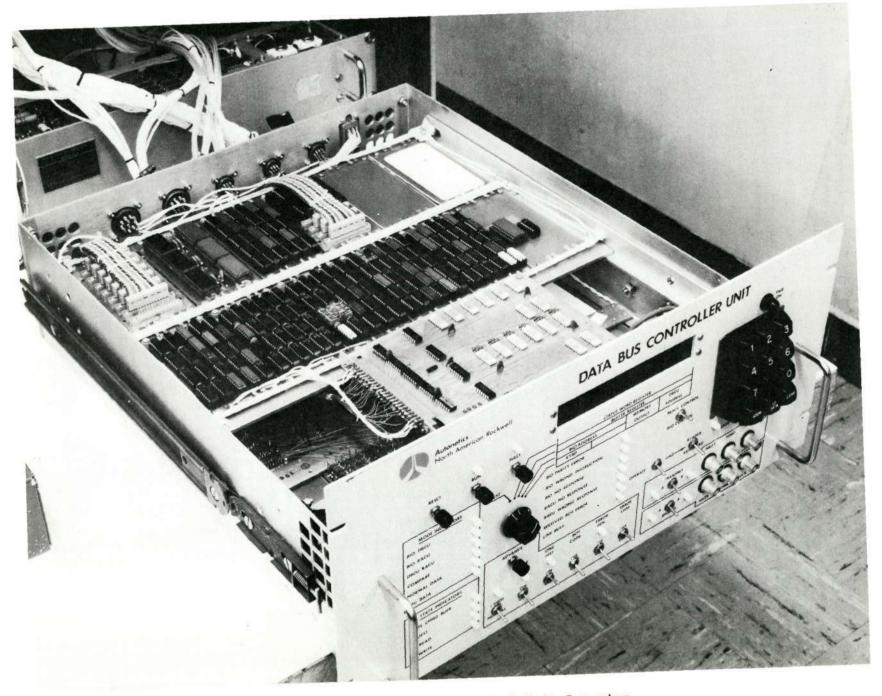

|   | 7.5 PHYSICAL CHARACTERISTICS | 5.    | _     | -     |    | 7-24       |

|   | 7.6 ENVIRONMENTAL .          |       |       | •     |    | 7-26       |

|   |                              | Ē     | •     | •     | •  | , 20       |

| 8 | DIGITAL DATA BUS DESIGN .    | •     | •     | •     |    | 8-1        |

|   | 8.1 SYSTEM SPECIFICATIONS    | •     |       |       |    | 8-1        |

|   | 8.2 COMPONENT PERFORMANC     | E     |       |       | -  | •          |

|   | SPECIFICATIONS .             | •     | •     | •     | •  | 8-4        |

| 9 | DBCU DESIGN                  |       |       |       |    | <b>0</b> 1 |

| 7 |                              | •     | •     | •     | •  | 9-1        |

|   | 9.1 PHYSICAL DESCRIPTION     | •     | •     | •     | •  | 9-1        |

|   | 9.2 CONTROLS AND DISPLAYS    | •     | •     | •     | •  | 9-2        |

|   | 9.3 BASIC OPERATION .        | •     | •     | •     | •  | 9-9        |

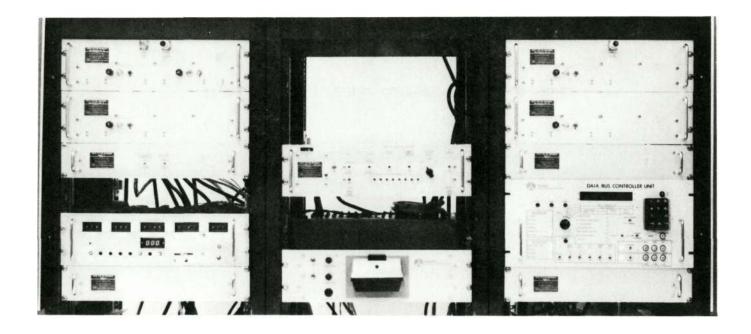

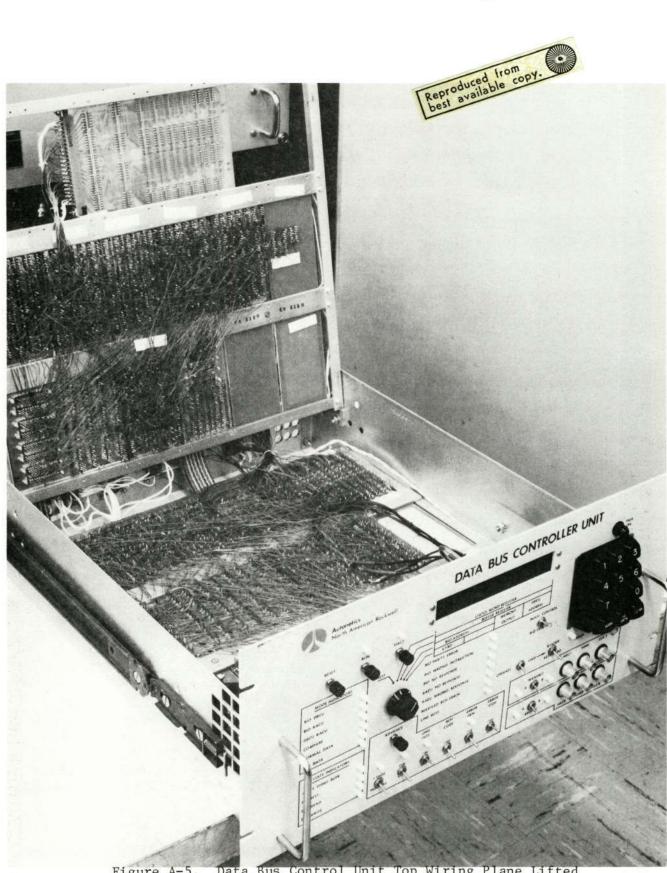

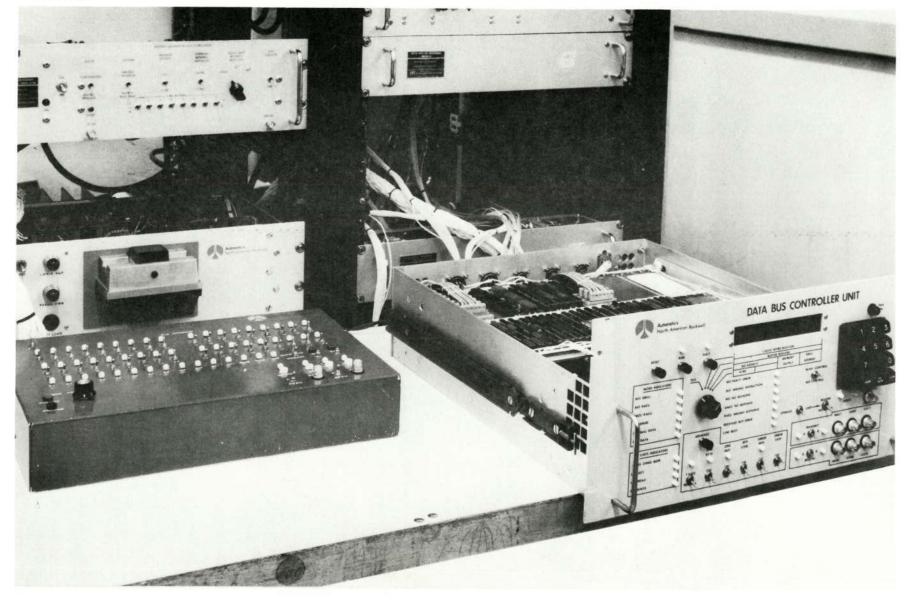

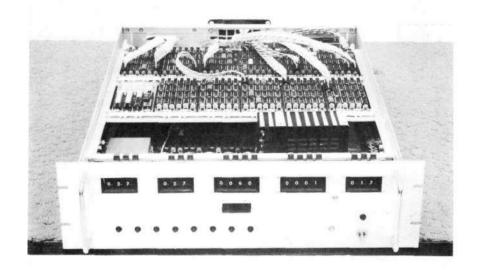

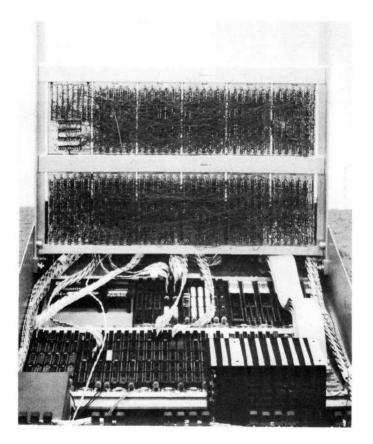

|   | APPENDIX A PRELIMINARY DACS  | BREAT |       | ۲D    |    |            |

|   | LAYOUT                       | •     | •     | •     |    | A-I        |

### ILLUSTRATIONS

| Figure      |                                                         |     |   | Page |

|-------------|---------------------------------------------------------|-----|---|------|

| 1-1         | DACS Work Breakdown and Flow                            |     | • | -2   |

| 1-2         | Recommended DACS Configuration                          |     | • | 1-4  |

| 1-3         | Functional Relationship of Breadboard Elements          |     | • | 1-6  |

| <b> </b> -4 | Dual Redundant DACS Breadboard                          |     | • | 1-7  |

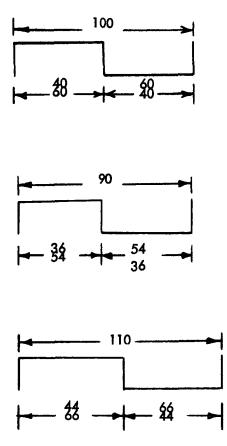

| 2-1         | Digital Data Bus, First Configuration                   |     | • | 2-2  |

| 2-2         | Digital Data Bus, Second Configuration                  |     | • | 2-3  |

| 2–3         | Methods of Coupling                                     |     | • | 2-5  |

| 2-4         | Direct and Transformer Coupling with T-Pads             |     | • | 2-6  |

| 3-1         | Data Management Subsystem EEM Growth Sequence .         |     | • | 3-6  |

| 4-1         | Non-critical Subsystem Functional Loop Models           |     | • | 4-3  |

| 4-2         | Non-Time Critical Subsystem Functional Loop Models .    |     | • | 4-4  |

| 4-3         | Time-Critical Subsystem Functional Loop Models .        |     | • | 4-6  |

| 4-4         | Candidate DB-1, Four Simplex Data Bus Subassemblies .   |     | • | 4-9  |

| 4–5         | Candidate DB-2, Two Dual Redundant Data Bus             |     |   |      |

|             | Assemblies                                              |     | • | 4-10 |

| 4-6         | Candidate DB-3, One Quad Redundant Data Bus<br>Assembly |     | • | 4-12 |

| 4-7         | Candidate R-1, RACU with Simplex Data Bus Interface .   | ,   | • | 4-15 |

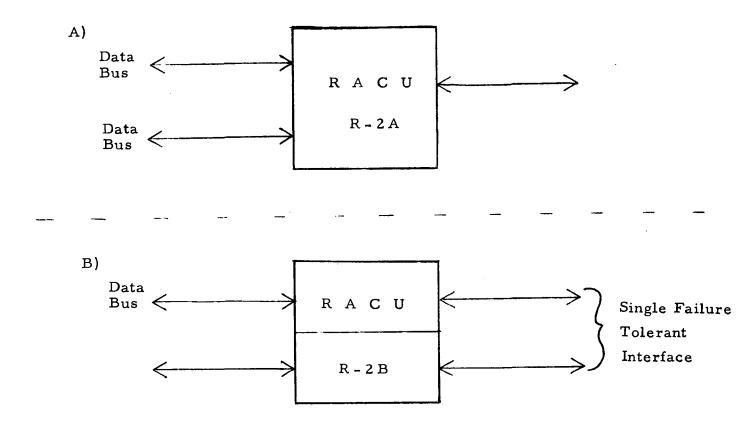

| 4-8         | Candidate R-2, RACU with Dual Data Bus Interface .      |     | • | 4-18 |

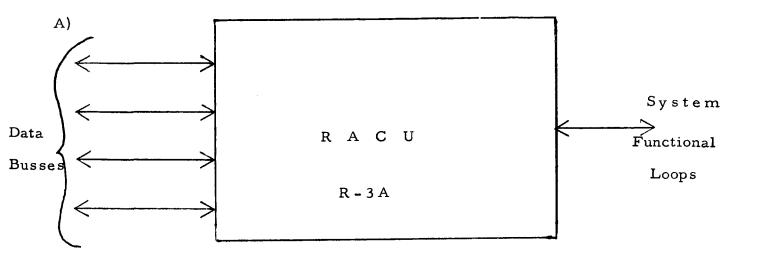

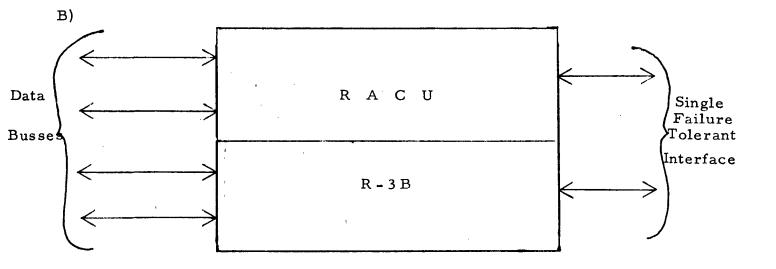

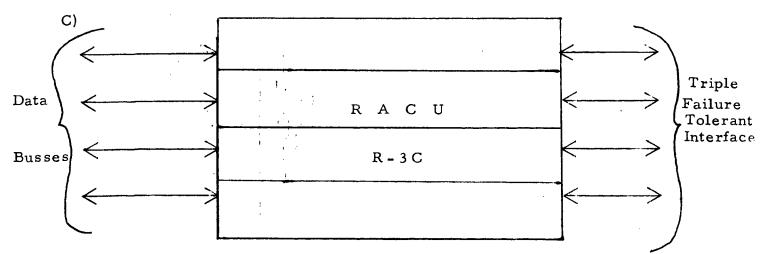

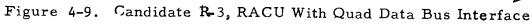

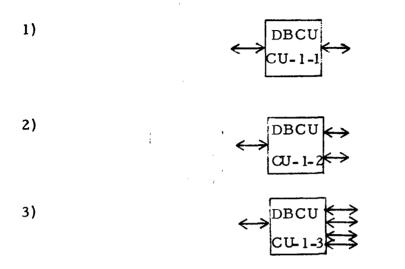

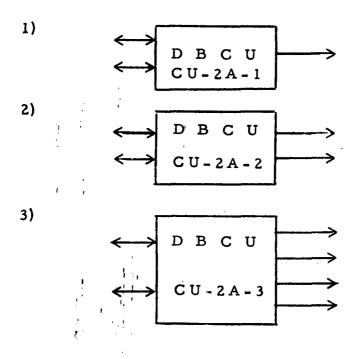

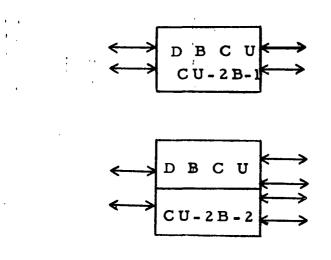

| 4-9         | Candidate R-3, RACU with Quad Data Bus Interface .      |     |   | 4-2I |

| 4-10        | Candidate CU-1, Single IOP Simplex DBCU                 | ,   | • | 4-27 |

| 4-11        | Candidate CU-2A, Dual IOP Simplex DBCU                  |     | • | 4-29 |

| 4-12        | Candidate CU-2B, Dual IOP Single Failure Tolerance D    | BCU | • | 4-31 |

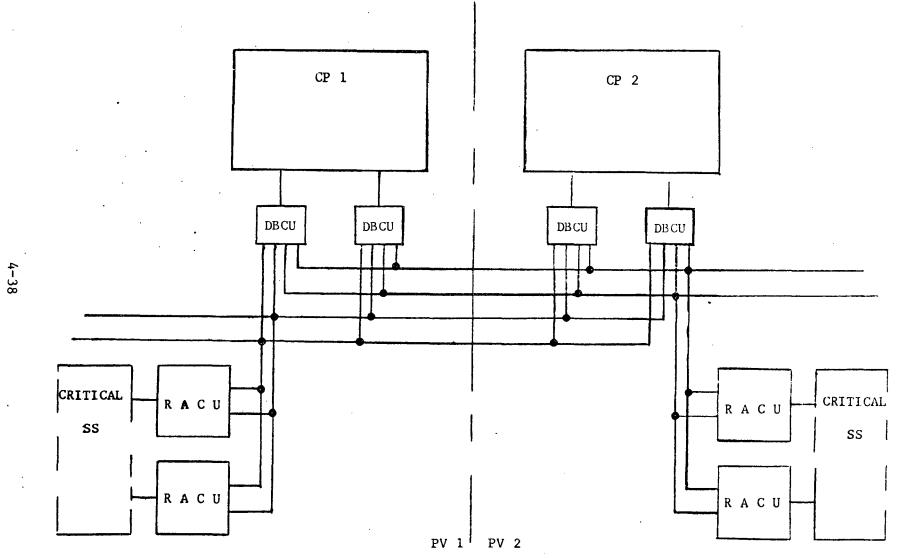

| 4-13        | Recommended DACS Configuration                          |     | • | 4-38 |

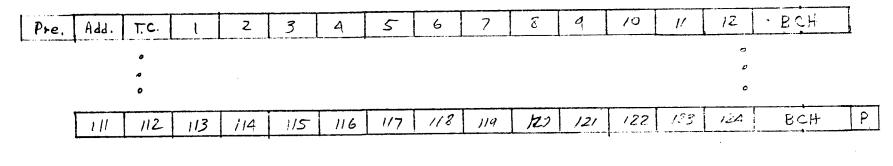

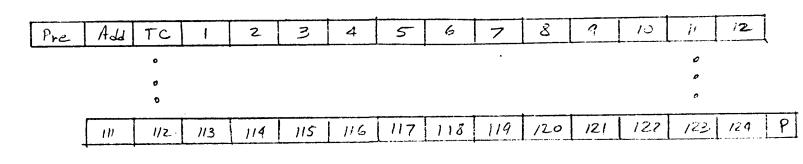

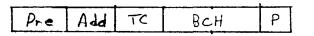

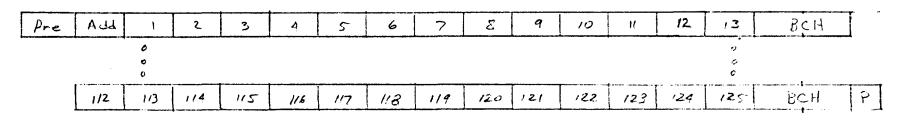

| 5-1         | Message Formats                                         | ı   | • | 5-8  |

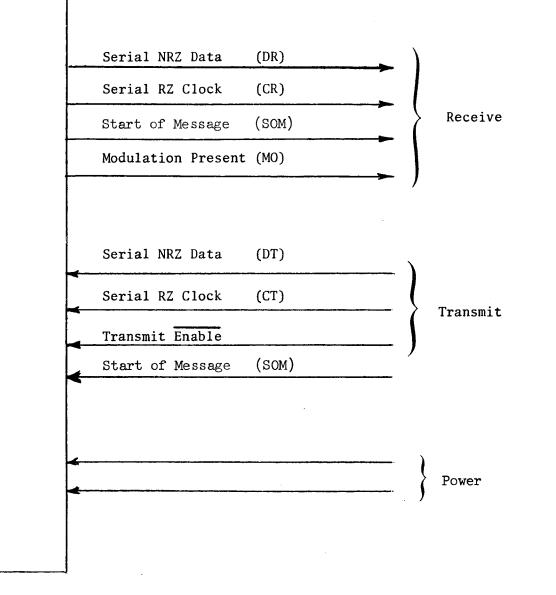

| 5-2         | Breadboard Modem Unit Functional Interface              | ,   | • | 5-15 |

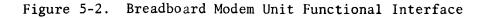

| 5-3         | Breadboard External Test Function Interface             | ,   | • | 5-19 |

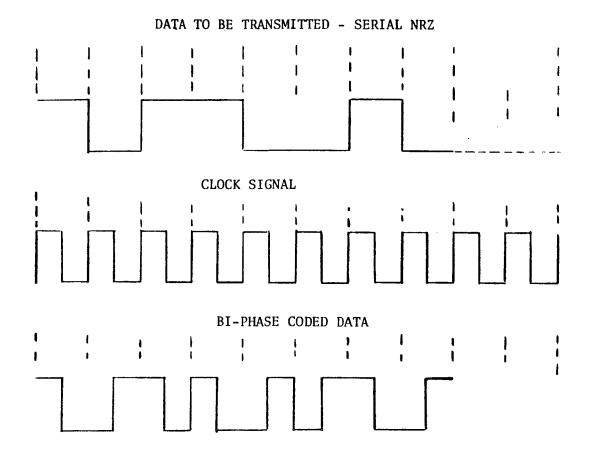

| 6-1         | Bi-Phase Level Data Encoding                            | ,   | • | 6-6  |

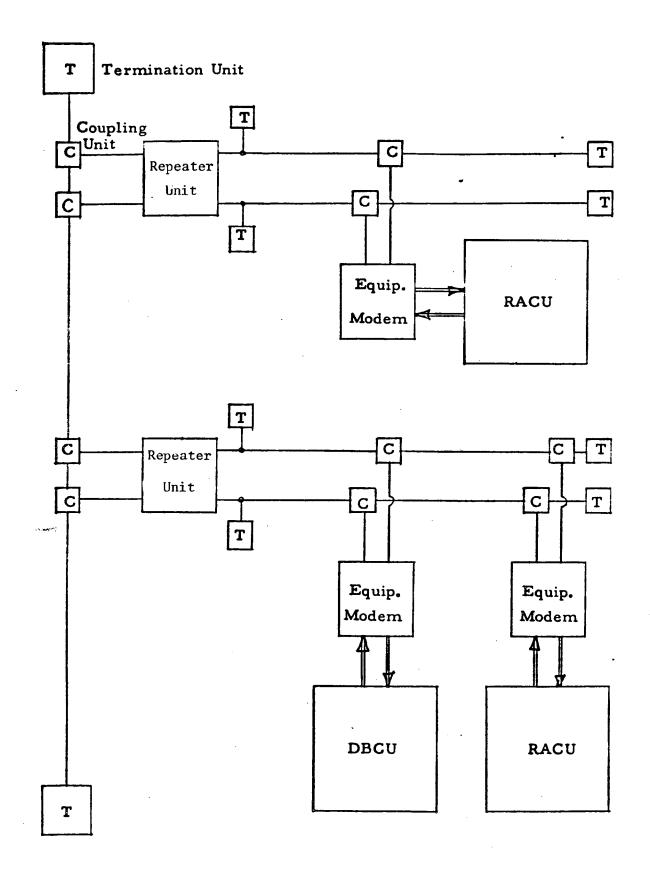

| 6-2         | Uni-directional Equipment/Bi-directional Core           | ,   | • | 6-12 |

•

| Figure |                                          |         |       |    |   | Page |

|--------|------------------------------------------|---------|-------|----|---|------|

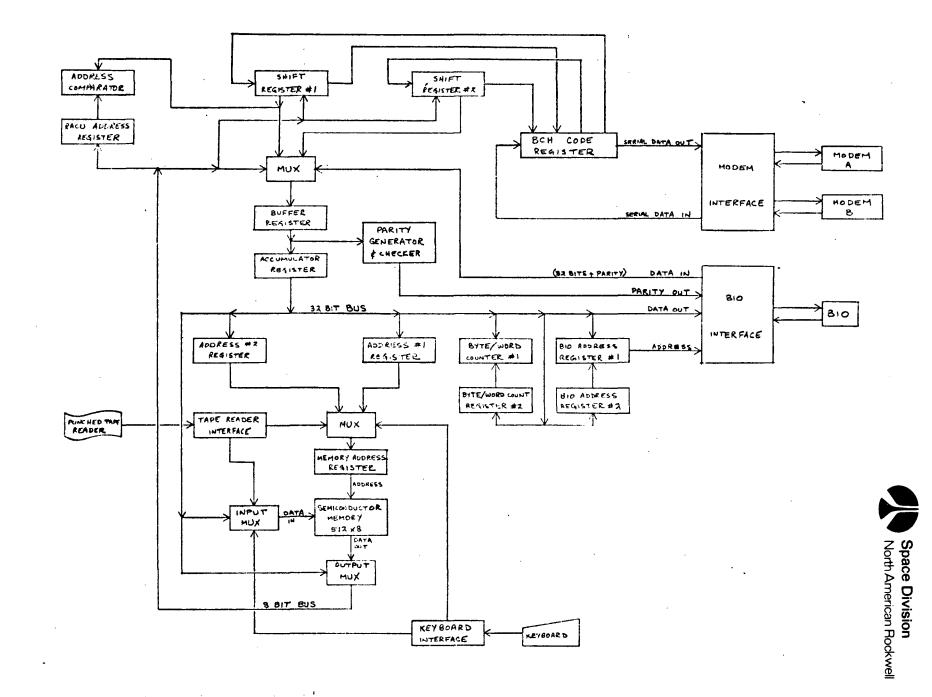

| 7-1    | Functional Relationship of Various Bread | board I | lemen | ts |   | 7-2  |

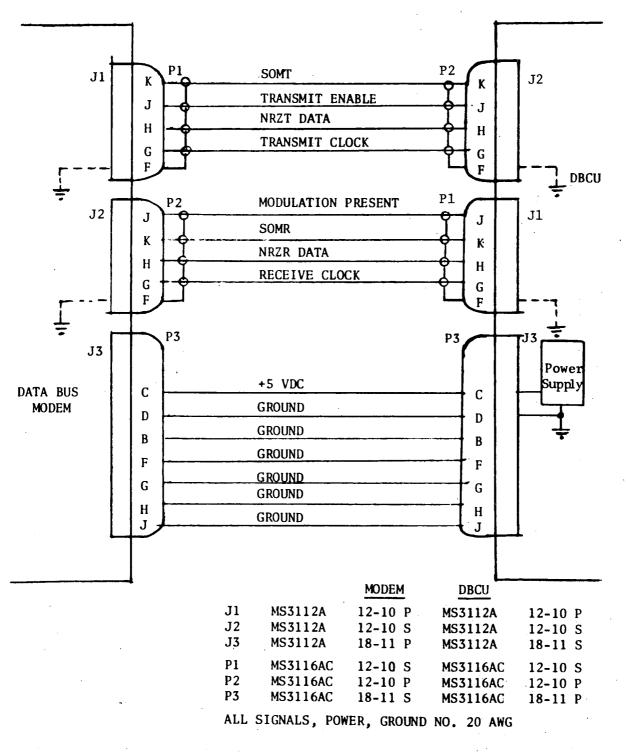

| 7-2    | DBCU/MODEM Interface                     |         |       | •  |   | 7-3  |

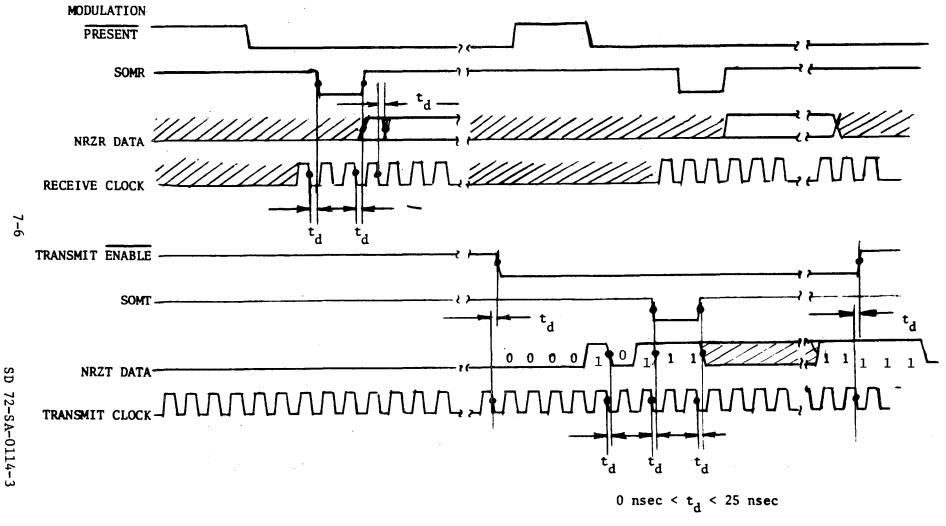

| 7-3    | DBCU/MODEM Interface Timing Diagram      | n.      | •     | •  |   | 7-6  |

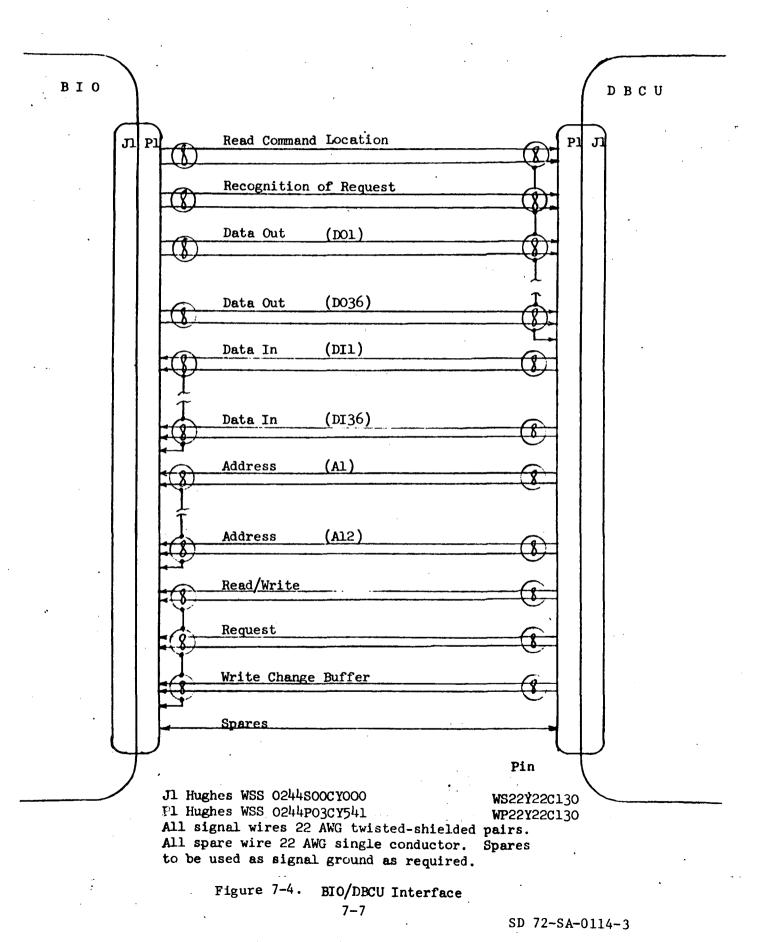

| 7-4    | BIO/DBCU Interface                       | •       | •     | •  |   | 7-7  |

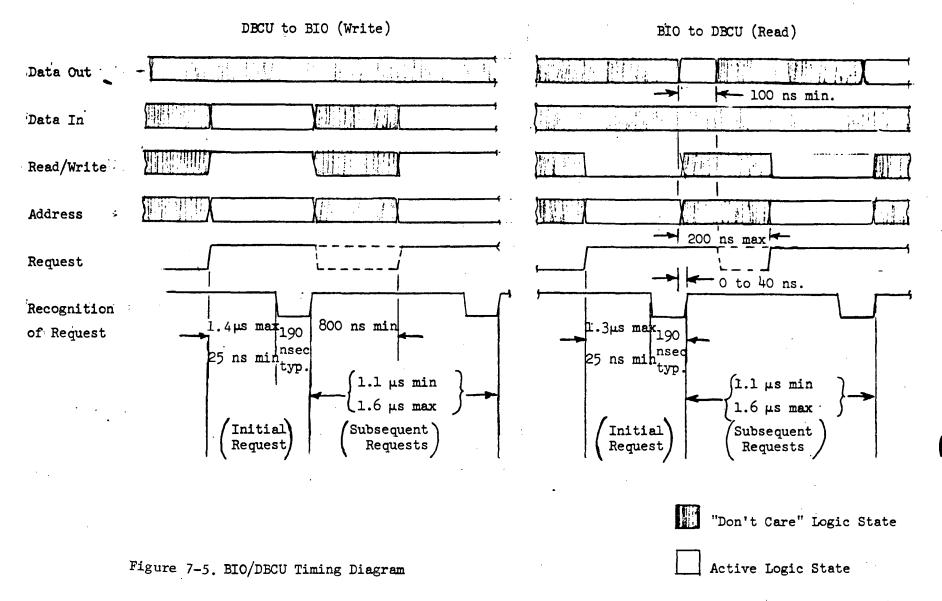

| 7-5    | BIO/DBCU Timing Diagram                  |         |       | •  |   | 7-10 |

| 7-6    | DBCU/STE Interface                       | •       |       | •  | • | 7-12 |

| 7-7    | DBCU Functional Organization .           | •       | •     | •  |   | 7-15 |

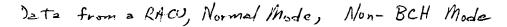

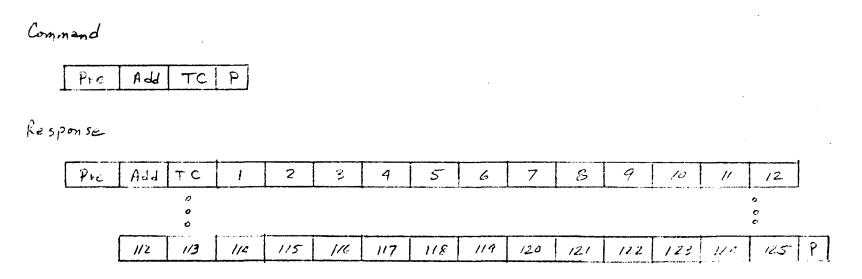

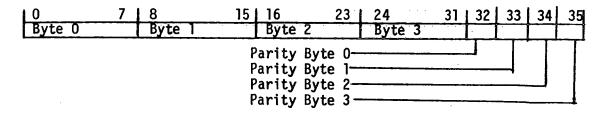

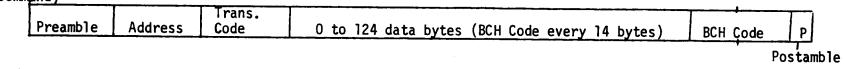

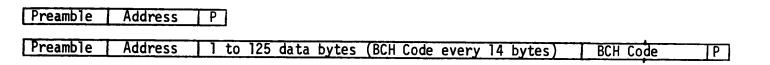

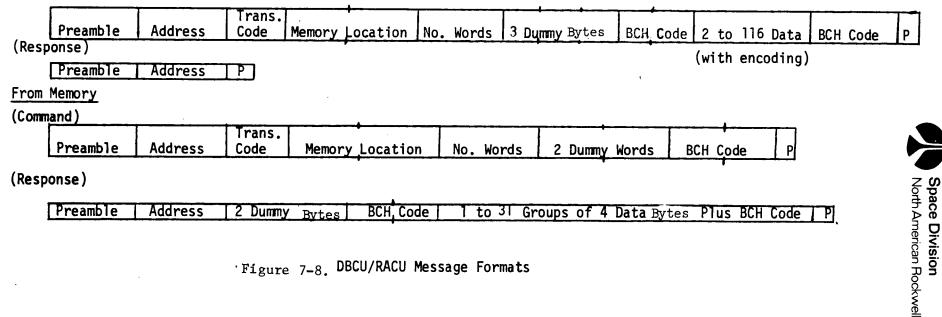

| 7-8    | DBCU/RACU Message Formats .              | •       |       | •  | • | 7-19 |

| 7-9    | Transmission Code Formats                |         | •     | •  | • | 7-23 |

| 8-1    | Skeleton Diagram of Data Bus System      | •       |       | •  | • | 8-2  |

| 8-2    | Breadboard Configuration, Block Diagram  | n.      | •     | •  | • | 8-3  |

| 8-3    | Coupler, Schematic Diagram               | •       |       | •  | • | 8-5  |

| 8-4    | Receive Clock Tolerance                  | •       | •     |    |   | 8-9  |

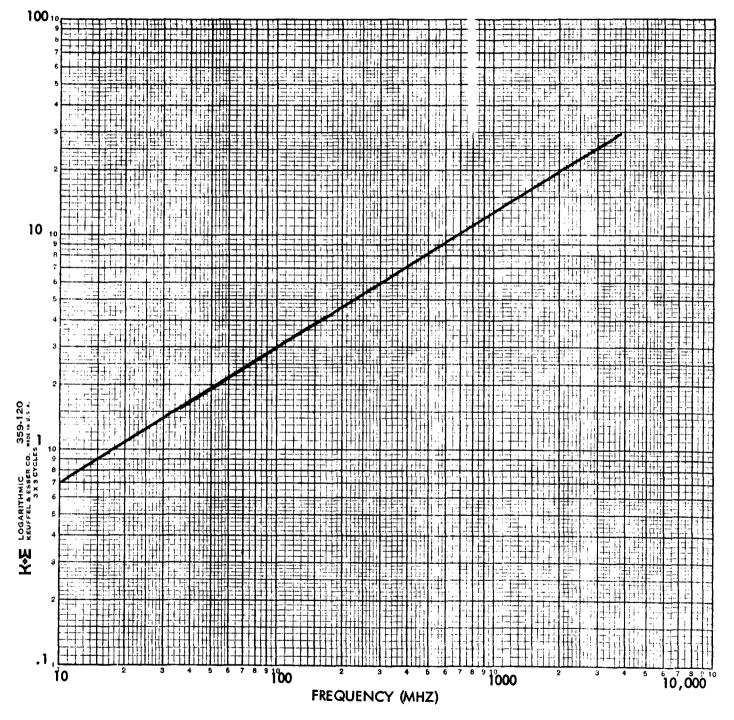

| 8-5    | Attenuation vs. Frequency for RG-22B/J   | Cable   | •     | •  | • | 8-11 |

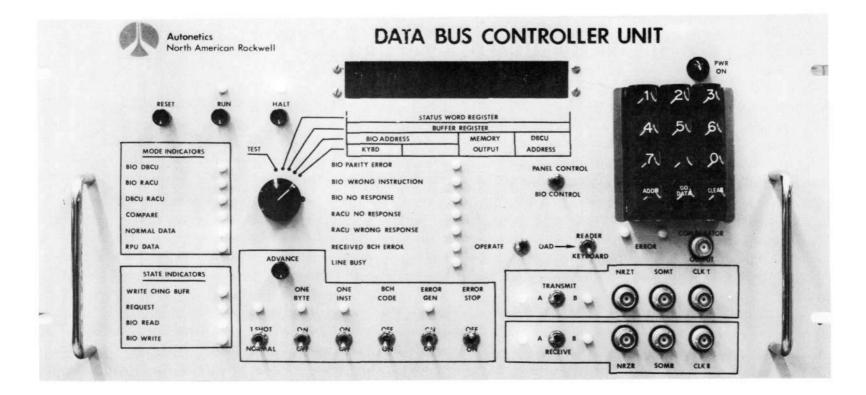

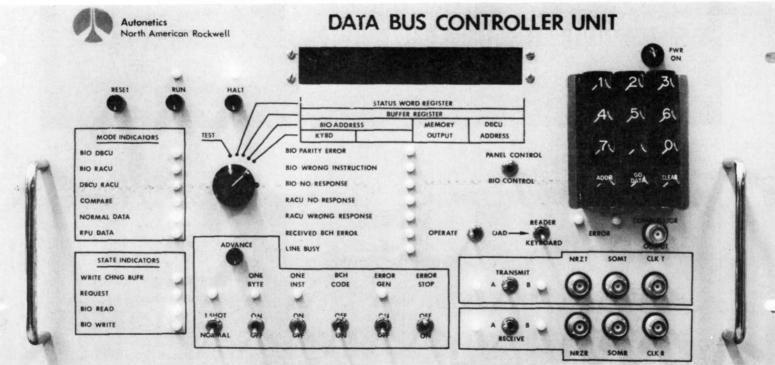

| 9-1    | DBCU Front Panel                         | •       |       |    |   | 9-3  |

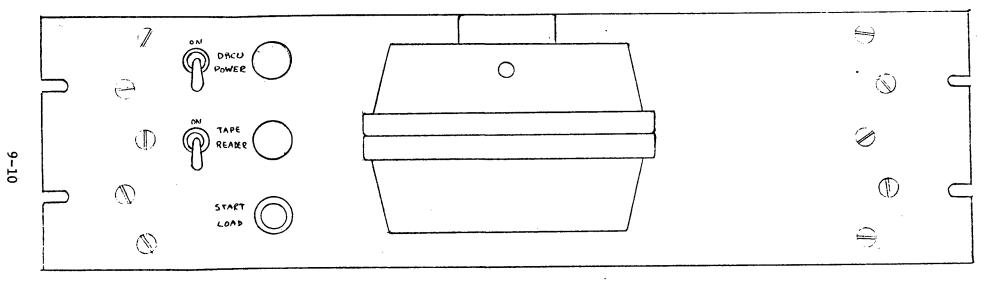

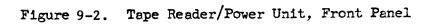

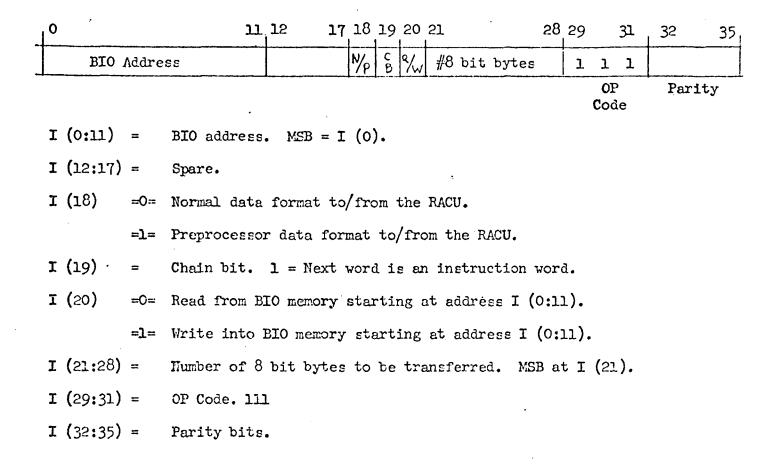

| 9-2    | Tape Reader/Power Unit – Front Panel     | •       | •     | •  | • | 9-10 |

| 9-3    | Compare                                  |         | •     |    |   | 9-12 |

| 9-4    | Set Mode of Operations                   | •       | •     | •  | • | 9-13 |

| 9-5    | DBCU/RACU Data Transfer                  | •       |       | •  | • | 9-14 |

| 9-6    | BIO/RACU Data Transfer                   | •       |       | •  | • | 9-15 |

| 9-7    | BIO/DBCU Data Transfer                   | •       | •     | •  |   | 9-16 |

| 9-8    | Status Word                              | •       | •     | •  | • | 9-17 |

| 9-9    | DBCU Data Flow                           | •       | •     | •  | • | 9-18 |

## TABLES

| Table |                                                                                       | Page |

|-------|---------------------------------------------------------------------------------------|------|

| 4-1   | Number of RACU's Per Subsystem Functional Loop<br>Model for the Seven RACU Candidates | 4-24 |

| 4-2   | Minimum Number of Candidate Data Bus Control                                          |      |

|       | Units                                                                                 | 4-32 |

| 4-3   | DACS Element Candidates                                                               | 4-33 |

| 7-1   | Universal and Group Address Codes                                                     | 7-22 |

·

٠.

#### ABBREVIATIONS

| ADS<br>ADT<br>ADTX<br>AFC<br>AGC<br>AN | Advanced Data System<br>Advanced Development Technology<br>Advanced Development Technology Extension<br>Automatic Frequency Control<br>Automatic Gain Control<br>Autonetics (Division of North American<br>Rockwell Corporation) |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BPF                                    | Bandpass Filter                                                                                                                                                                                                                  |

| bps                                    | Bits Per Second                                                                                                                                                                                                                  |

| CAIRS                                  | Computer-Assisted Interactive Resource<br>Scheduling                                                                                                                                                                             |

| CCIR                                   | International Radio Consultative Committee                                                                                                                                                                                       |

| CDR                                    | Critical Design Review                                                                                                                                                                                                           |

| CEI                                    | Contract End Item                                                                                                                                                                                                                |

| CLASP                                  | Computer Language for Aeronautics and Space Programming                                                                                                                                                                          |

| CM                                     | Command Module (Apollo)                                                                                                                                                                                                          |

| COMPOOL                                | Common Pool (of Data)                                                                                                                                                                                                            |

| СР                                     | Central Processor or Circular Polarization                                                                                                                                                                                       |

| C.P.                                   | Computer Program                                                                                                                                                                                                                 |

| CPCEI                                  | Computer Program Contract End Item                                                                                                                                                                                               |

| CPCI                                   | Computer Program Configuration Item                                                                                                                                                                                              |

| CPDF                                   | Computer Program Development Facility                                                                                                                                                                                            |

| CPIC (A)                               | Computer Program Integration Contractor<br>(Agency)                                                                                                                                                                              |

| CPT&E                                  | Computer Programming Test and Evaluation                                                                                                                                                                                         |

| CR                                     | Change Report                                                                                                                                                                                                                    |

| CRT                                    | Cathode-Ray Tube (Display)                                                                                                                                                                                                       |

| CSS                                    | Crew Subsystem                                                                                                                                                                                                                   |

| СТВ                                    | Communications Terminal Breadboard                                                                                                                                                                                               |

| CTF                                    | Central Test Facility                                                                                                                                                                                                            |

| 011                                    | Gentral rest facility                                                                                                                                                                                                            |

| DACS                                   | Data Acquisition and Control Subassembly                                                                                                                                                                                         |

| dB                                     | Decibel                                                                                                                                                                                                                          |

| DBCU                                   | Data Bus Control Unit                                                                                                                                                                                                            |

| dBm                                    | Decibel Referred to One Milli-Watt                                                                                                                                                                                               |

| dBW                                    | Decibel Referred to One Watt                                                                                                                                                                                                     |

| DCR                                    | Design Change Request                                                                                                                                                                                                            |

| DDB                                    | Digital Data Bus                                                                                                                                                                                                                 |

| Demux                                  | De-Multiplex(er)                                                                                                                                                                                                                 |

| DMS                                    | Data Management System                                                                                                                                                                                                           |

| DPA                                    | Data Processing Assembly                                                                                                                                                                                                         |

| DPSK                                   | Dual Phase Shift Keying                                                                                                                                                                                                          |

| DRSS                                   | Data Relay Satellite System                                                                                                                                                                                                      |

Space Division North American Rockwell

| ECP                            | Engineering Change Proposal                          |

|--------------------------------|------------------------------------------------------|

| EDF                            | Experiment Data Facility                             |

| EEM                            | Engineering Evaluation Model                         |

| EEMP                           | Engineering Evaluation Model Processor               |

| EIRP                           | Effective Isotropic Radiated Power                   |

| EMC                            | Electromagnetic Compatability                        |

| EMI                            | Electromagnetic Interference                         |

| EOS                            | Earth Orbital Shuttle                                |

| EOSS                           | Earth Orbital Space Station                          |

| EPS                            | Electrical Power Subsystem                           |

| ETC/LSS or ECLSS               | Environment Control and Life Support                 |

| 110,100 01 10100               | Subsystem                                            |

| EVA                            | Extra-Vehicular Activity                             |

| EXT                            | External                                             |

|                                | Energy Per Bit to Noise Density Ratio                |

| E <sub>b</sub> /N <sub>o</sub> | Energy lef bit to house bensity harro                |

| FACS                           | Facsimile                                            |

| FDM                            | Frequency-Division Multiplex                         |

| FM                             | Frequency Modulation                                 |

| FQT                            | Formal Qualification Test                            |

| 1Q1 ·                          | Tormar Guarrieution Tobe                             |

| G&CS                           | Guidance and Control Subsystem                       |

| GFE                            | Government Furnished Equipment                       |

| GHz                            | Giga-Hertz                                           |

| GOA                            | Gated Operational Amplifier                          |

|                                |                                                      |

| HAL                            | Higher-Order Aerospace Programming Language          |

| HOL                            | Higher-Order Language                                |

| HOLM                           | Higher-Order Language Machine                        |

| Hz                             | Hertz                                                |

|                                | · · ·                                                |

| IF                             | Intermediate Frequency                               |

| IFRU                           | In-Flight Replaceable Unit                           |

| IM                             | Intermodulation Products                             |

| IMS                            | Information Management System                        |

| IMSIM                          | Information Management Simulation                    |

| IOC                            | Initial Operational Capability                       |

| IOCB                           | Input-Output Control Block                           |

| IOU                            | Input-Output Unit                                    |

| 1/0                            | Input-Output                                         |

| IPA                            | Intermediate Power Amplifier                         |

| IQL                            | Interactive Query Language                           |

| IR                             | Infra-Red                                            |

| ISS or IMS/S                   | Information (Management) Subsystem                   |

| ITT                            | International Telephone and Telegraph                |

| 111                            | International receptione and reception               |

| K-words                        | Thousands of (Computer) Words                        |

|                                |                                                      |

| K-EAPS                         |                                                      |

| K-EAPS                         | Thousands of Equivalent-Add Operations<br>Per Second |

| K-LAPS<br>K-bps                | Thousands of Equivalent-Add Operations               |

| LEM      | Lunar Excursion Module                     |

|----------|--------------------------------------------|

| LM       | Lunar Module                               |

| LNA      | Low Noise Amplifier                        |

| LO       | Local Oscillator                           |

| LPF      | Low Pass Filter                            |

| M1, M2   | (Computer) Memory Designation              |

| Mbps     | Megabits Per Second                        |

| MCB      | Module Control Block                       |

| MHz      | Megahertz                                  |

| MOF      | Mission Operations Facility                |

| MOL      | Manned Orbiting Laboratory                 |

| MSC      | Manned Spacecraft lenter                   |

| MSFN     | Manned Space Flight Network                |

| MSS      | Modular Space Station                      |

| MUX      | Multiplexer                                |

| mW       | Milli-Watts                                |

| MW       | Microwave                                  |

| mV       | Milli-Volts                                |

| .NF      | Noise Figure                               |

|          | -<br>                                      |

| OBCO     | On-Board Checkout                          |

| OCC      | Operations Control Center (On-Board)       |

| ODM      | Operational Data Management                |

| OM       | Operating Memory                           |

| PA       | Power Amplifier                            |

| PCM      | Pulse Code Modulation                      |

| PDR      | Preliminary Design Review                  |

| PL/1     | Procedure Language                         |

| PM       | Phase Modulation                           |

| PN (PRN) | Pseudo Random Noise                        |

| ppm      | Parts Per Million                          |

| POT      | Preliminary Qualification Tests            |

| PSK      | Phase Shift Keying                         |

| RAM      | Research and Applications Module           |

| RACU     | Remote Acquisition and Control Unit        |

| RCS      | Reaction Control Subsystem                 |

| RF       | Radio Frequency                            |

| RHCP     | Right-Hand Circular Polarization           |

| RPU      | Remote Processing Unit                     |

| Rx       | Receive                                    |

|          | · · · · · · · · · · · · · · · · · · ·      |

| S&C      | Standards and Conventions                  |

| SCCB     | Software Configuration Control Board       |

| SCN      | Specification Change Notice                |

| SD       | Space Division (of North American Rockwell |

| SDC      | Corporation)                               |

| 520      | Systems Development Corporation            |

`

SD 72-SA-0114-3

•

| S/N     | Signal to Noise Ratio                     |

|---------|-------------------------------------------|

| SOW     | Statement of Work                         |

| SPL     | Space Programming Language                |

| SRD     | Step-Recovery Diode                       |

| SSCB    | Solid-State Circuit-Breaker               |

| SSS     | Structures Subsystem                      |

| STE     | Support Test Equipment                    |

| TAV     | Test and Validation (Programs)            |

| TBD     | To Be Determined                          |

| TCXO    | Temperature-Controlled Crystal Oscillator |

| TDA     | Tunnel Diode Amplifier                    |

| TDM     | Time Division Multiplexing                |

| TDRS    | Tracking and Data Relay Satellite         |

| TIP     | Test and Integration Plan                 |

| TLM, TM | Telemetry                                 |

| TOOL    | Test Operations Oriented Language         |

| TRW     | Thompson Ramo Woolridge Corporation       |

| TT&C    | Telemetry, Tracking and Control           |

| TWT     | Traveling Wave Tube                       |

| TWTA    | Traveling Wave Tube Amplifier             |

| Tx      | Transmit                                  |

| USB (E) | Unified S-Band (Equipment)                |

| UV      | Ultra-Violet                              |

| VDD     | Version Description Document              |

| VHF     | Very High Frequency                       |

| VSB     | Vestigal Side Band                        |

| VSB     | Vestigal Side Band                        |

| VSWR    | Voltage Standing Wave Ratio               |

- xiv -

#### LIST OF INTERIM REPORTS

| AA-101      | DPA Flow Diagrams, September 1971                                                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|

| AA-102      | DPA Throughput and Authority Analysis,<br>February 1972                                                                       |

| AA-103      | DPA Configuration Selection, April 1972                                                                                       |

| AS-101      | Modular Space Station Computer Program<br>Standards and Conventions, December 1971                                            |

| AS-102      | Modular Space Station Computer Program<br>Specification Tree, February 1972                                                   |

| AS-103      | Modular Space Station Computer Program<br>Development, Test and Configuration<br>Control Plan, May 1972                       |

| AS-104      | Modular Space Station Computer-Assisted<br>Resource Allocations and Utilization<br>Recommendations, June 1972                 |

| CTB-101     | Concepts for Multiple RF Link<br>Mechanization, May 1971                                                                      |

| CTB-103     | Antenna-Mounted Electronics Component<br>Design, October 1971                                                                 |

| CTB-105/106 | CTB Integration and Test and Operations<br>Manual, June 1972                                                                  |

| DB-101      | Parametric Data for Bus Design, May 1971                                                                                      |

| DB-103      | Component Performance Requirements,<br>Schematics and Layout Drawings,<br>December 1971                                       |

| DB-104      | Digital Data Bus Breadboard Final Report,<br>May 1972                                                                         |

| DD-102      | Modular Space Station Data Processing<br>Assembly Parametric Evaluation of<br>Subsystems Input/Output Interface,<br>June 1971 |

| DD-103         | Modular Space Station Data Acquisition<br>and Control Subassembly Model Configuration<br>(SD 71-233), July 1971 |

|----------------|-----------------------------------------------------------------------------------------------------------------|

| DP-101         | Data Processing Assembly Configuration (Preliminary), June 1971                                                 |

| DP-102         | Data Processing Assembly Supervisor<br>Specification, May 1972                                                  |

| DP-103         | DPA Processor Performance Requirements<br>(Preliminary), August 1971                                            |

| DP-103         | DPA Processor Final Description, May 1972                                                                       |

| DP-104         | EEM DMS Processor Development Plan, June 1972                                                                   |

| DP-105         | Data Acquisition and Control Redundancy<br>Concepts, August 1971                                                |

| DP-106         | Application of Redundancy Concepts to<br>DPA, January 1971                                                      |

| DP-107         | Data Acquisition and Control Subassembly<br>Breadboard Design Requirements, October 1971                        |

| DP-108         | Data Bus Control Unit Performance<br>Requirements, January 1972                                                 |

| DP-109         | Data Bus Control Design Reports, March 1971                                                                     |

| DP-110         | DBCU Acceptance Report (to be published)                                                                        |

| EL-277         | Bulk Storage Development Plan                                                                                   |

| IB-101         | DPA Internal Flow and Traffic Pattern,<br>May 28, 1971                                                          |

| ICD #TRW 20549 | Interface Control Document - Data Bus<br>Modem/RACU, Revision A, January 17, 1972                               |

| ICD #AN 26465  | Interface Control Document - Data Bus<br>Controller Unit to Buffer I/O, Revision<br>January 21, 1972            |

| MD-101         | Mass Memory Parametric Data                                                                                     |

| RF-101         | Modular Space Station Communications<br>Terminal Breadboard Preliminary System<br>Specification, October 1971   |

| SA-101    | Central Processor Operational Analysis,<br>September 30, 1971                       |

|-----------|-------------------------------------------------------------------------------------|

| SA-102    | Central Processor Memory Organization and<br>Internal Bus Design, December 30, 1971 |

| SD 71-227 | Automatic Control and Onboard Checkout<br>Final Study Report                        |

SD 72-SA-0114-3

1

#### 1. INTRODUCTION

#### 1.1 DACS REQUIREMENTS SUMMARY

In the Modular Space Station the Data Processing Assembly (DPA) is highly distributed. The concept of two pressure volumes results in the division of the central processor in such a way that the computations associated with station operations and experiments can be performed in either volume. Similarly, the subsystems and experiments are divided between the two pressure volumes and, what is more, the subsystems are distributed throughout the modules that make up a 6-man or a 12-man configuration. Some of these subsystems require "on-the-spot" computations; these are provided in the DPA design by remote processing units (RPU's). All subsystems require computational support from the Data Processing Assembly. Therefore the DPA must acquire data from these distributed subsystems and return data, instructions and commands.

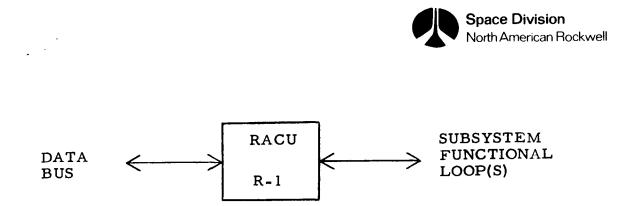

A significant portion of the ADT effort has been devoted to the analysis and breadboarding of a data acquisition and control subassembly (DACS) to provide the necessary interflow of data between the two central processors, the subsystems and the experiment equipment. The DACS has been defined to include the Digital Data Bus (DDB), the Data Bus Control Unit (DBCU), and the Remote Acquisition and Control Unit (RACU). Two of these have been analyzed and breadboarded as a part of the ADT effort; these are the DBCU and the DDB.

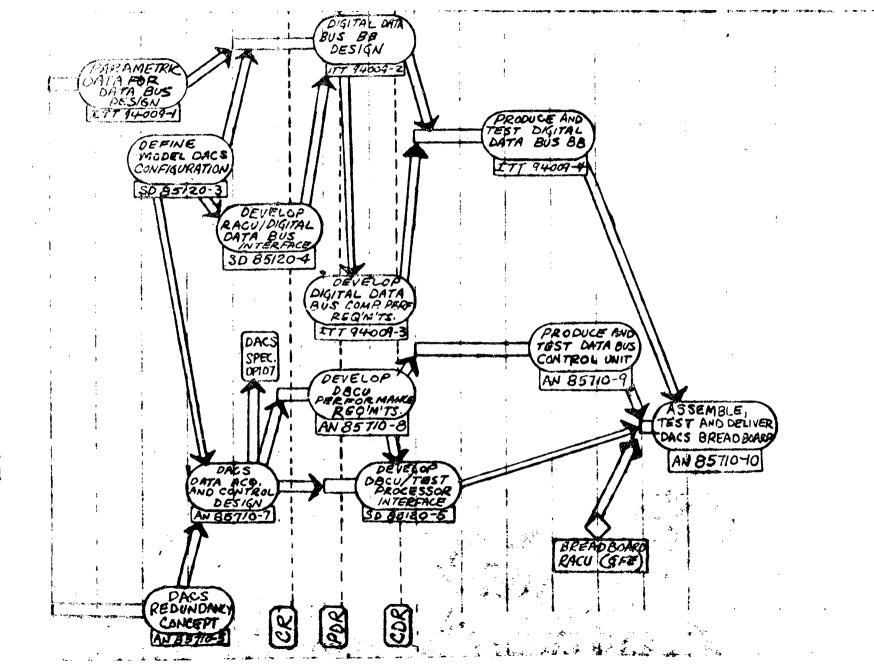

Figure 1-1 presents the task breakdown and flow which was followed in ultimately delivering breadboards of the DBCU and the DDB. Note that a RACU/RPU breadboard is GFE.

The data acquisition and control analyses began with a theoretical analysis of the parameters pertinent to the design and usage of data buses. The result of this analysis was a "design handbook" covering the significant aspect of wideband digital and analog data buses.

Then a model was defined for the Data Acquisiton and Control Subassembly (DACS) breadboard. The purpose of this definition was provide data to serve as a basis for the design of a DACS breadboard. It identifies the objectives of the breadboard, some potential vehicle related problems, and a simplified implementation concept.

The primary objective of the DACS breadboard is to verify the digital data bus concept for the Modular Space Station (MSS). It shall demonstrate the availability of technology to provide accurate data transfer, reconfigurability, failure tolerance, long life and standardization of interfaces.

1-1

Space Division North American Rockwell

Figure 1-1. DACS Work Breakdown and Flow 1-2

The analysis of DACS redundancy concepts covers the advantages and disadvantages of a general range of concepts and methods applicable to the DACS. Recommendations of methods were made and justified.

The overriding requirements were found to be the single and triple failure tolerance requirements and the physical separation of redundant subsystems into pressure isolatable volumes.

The recommendations for the degree, level and type of redundancy for each DACS element are presented. These recommendations include the split between hardware and/or software techniques, the utilization of error protection coding, the replacement/repair methods and a definition of the replaceable items, and the rationale for each selected candidate DACS element.

The following redundancy requirements were imposed on the station subsystems

- 1. A capability must be provided for each non-critical function to fail safe for the first failure.

- 2. For a critical function a capability must be provided for:

- A. Full operation subsequent to a first failure (fail operational)

- B. Reduced or "out of spec" performance subsequent to a second failure (fail degrade).

- C. Crew survival for at least 96 hours subsequent to a third failure (fail emergency)

- 3. Time critical functions require active (on-line continuous operation) redundancy. Non-time critical functions require at least standby (wired in and can be placed in operation with automatic or manual switchover.

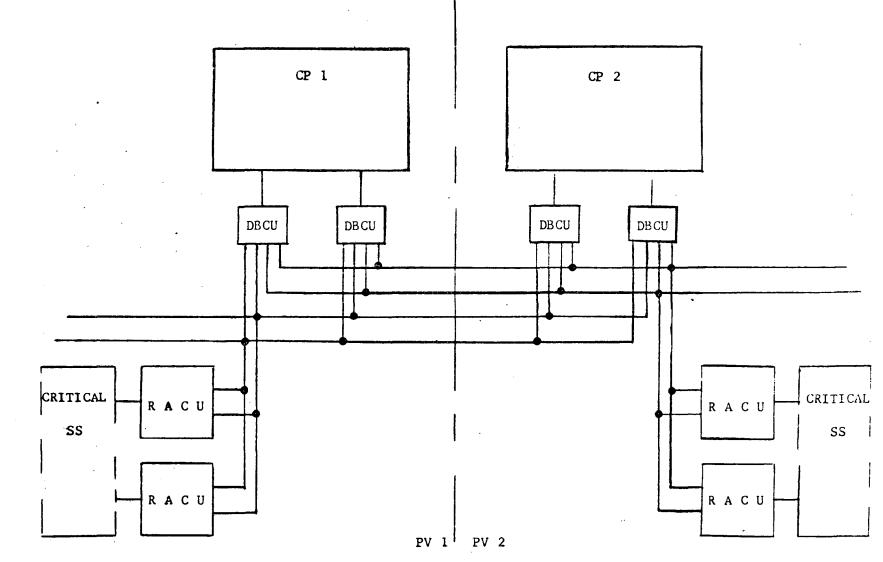

Figure 1-2 presents the recommended implementation of the DACS so that it will satisfy the failure criteria (redundancy requirements).

#### 1.2 DACS BREADBOARD DESIGN

The DACS breadboard is an engineering model that is representative of the concepts for the data acquisition and control function of the data processing assembly of the modular space station. The NASA defines a breadboard as a unit which performs the same functions and according to the same characteristics as those defined by the hardware design.

A data acquisition and control subsystem is a semiautonomous subsystem that provides controlled communication between a large number of remote locations and a control location. Insofar as possible, the DACS breadboard is a representation of such a subsystem. The DACS breadboard also provides a test bed for operational performance evaluation of numerous concepts for this type of subsystem oriented toward the specific needs and requirements imposed by the modular space station.

1 - 3

Figure 1-2. Recommended DACS Configuration

Space Division North American Rockwell

1-4

The overall breadboard concept for the DACS is a highly flexible, configuration independent, building block approach. This approach allows a large number of different DACS configurations to be assembled as an operating data acquisition and control subsystem breadboard. Each configuration concept can then be operated, tested and evaluated for overall DACS concept and performance valuation.

The DACS breadboard is an engineering model but is representative of the concepts for the data acquisition and control subassembly for the data process-ing assembly of the modular space station.

The communication spine for the DACS breadboard is provided by the data bus breadboard. All communication between the breadboard remote acquisition and control units (RACU's) and the data bus control unit (DBCU) utilize the data bus breadboard. This communication is also controlled by these other DACS breadboard units.

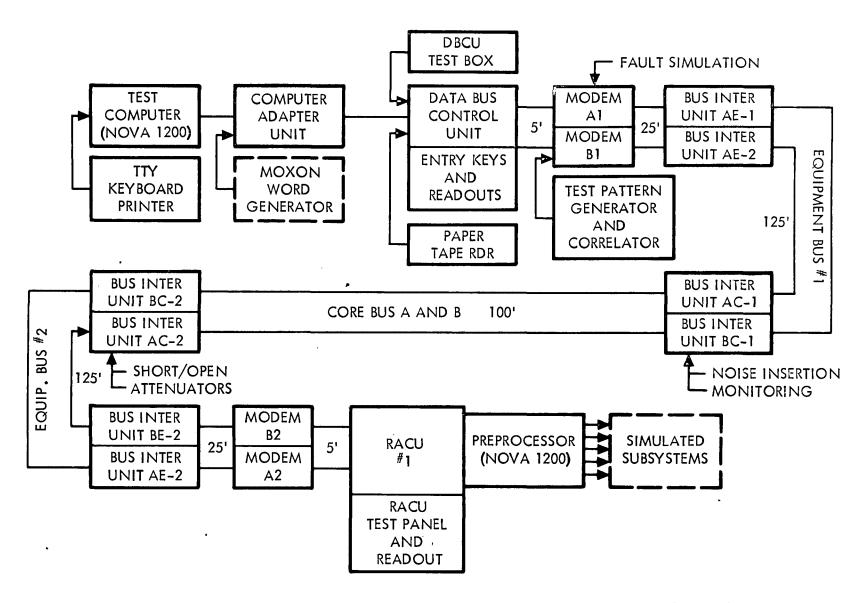

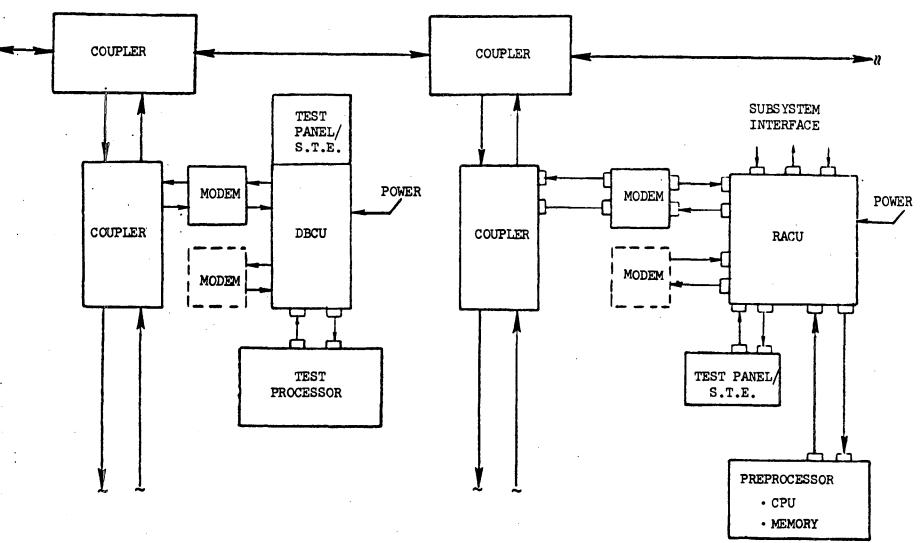

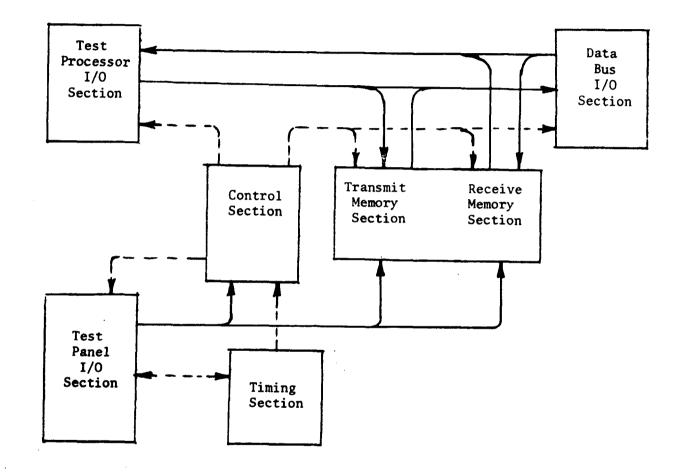

The data bus controller unit (DBCU) is one item of the major elements which make-up the modular space station (MSS) data processing assembly. The functional relationships of the various elements of the DACS breadboard equipments are shown in Figure 1-3. Direct interfacing elements with the breadboard DBCU include the test processor, test panel and special test equipment, MODEM, and prime power source.

The DBCU breadboard performs as an input/output device for the test processor, controls the information flow on the data bus, and performs the following functions:

- a. Provides all command and control capabilities to fully exercise the DACS breadboard, to communicate with the RACU breadboards via the breadboard MODEM units and data bus, and to operate the breadboard with or without the use of the test processor.

- b. Provides the capabilities to initiate all read/write actions with the test processor or test panel interfaces.

- c. Provides the buffering and formatting of all input/output data to the test processor, test panel, or data bus interfaces.

- d. Provides the capability for error protective encoding and checking of all data to and from the test processor or data bus as selected by the test panel.

Figure 1-3 indicates all of the components of the DACS breadboard, however, not all of those shown are part of the ADT effort. The others are GFE. Note in particular, that there are enough DDB components to configure a dual redundant data bus. It will be possible with this breadboard, then, to evaluate wideband digital data bus operation (10 Mbps), automatic fault detection and isolation, automatic reconfiguration, techniques for executive control of data traffic, etc.

Figure 1-3. Data Acquisition and Control Subassembly Breadboard Configuration

The requirements for the DACS breadboard itself and for its components, in particular, the DBCU breadboard and the data bus breadboard, are presented in specification format, Sections 5.0, 6.0, and 7.0. For this reason, the reader will notice some repitition in these sections. Furthermore, the requirements definition process was iterative and dependent upon the results of the supporting studies (Sections 2.0, 3.0, and 4.0), as well as the results of the simultaneous MSS Phase B studies. Hence, there may appear to be discrepancies in some of the numerical parameters used in specifying the breadboard requirements. For example, one parameter which varied with the progress of the Phase B study was the line lengths imposed by the modular configuration.

#### 2.0 PARAMETRIC DATA FOR BUS DESIGN

The data acquisition and control analyses began with a theoretical analysis of the parameters pertinent to the design and usage of data buses. The result of this analysis was a "design handbook" covering the significant aspect of wideband digital and analog data buses.

2.1 DIGITAL BUS

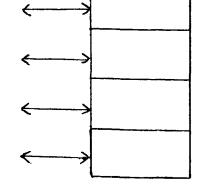

Two basic digital bus configurations, outlined below, were analyzed although within both there are variations.

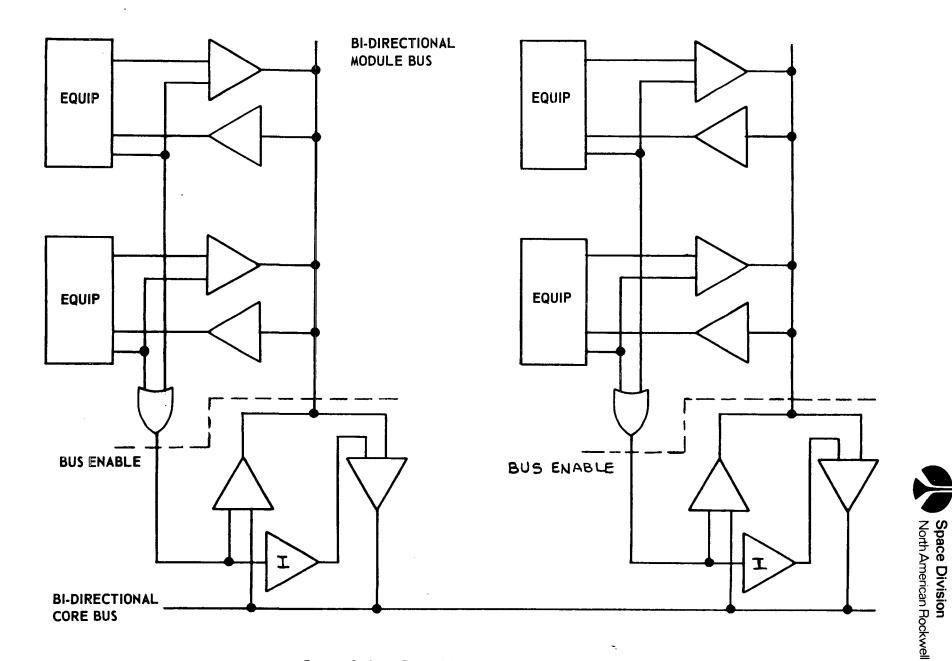

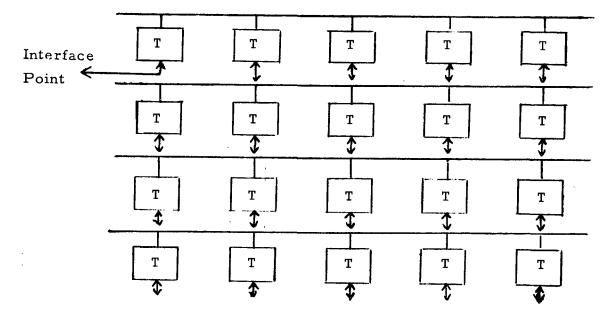

The first configuration shown in simplified form in Figure 2-1 consists of a core bus located in the core and a module bus located in each module. Both buses are bi-directional, therefore requiring bus enabling signals for time multiplexing digital signals and preventing ringing in bus coupling drivers and receivers.

The amplifiers are located at the module-core interface for isolation, and circuit drive requirements.

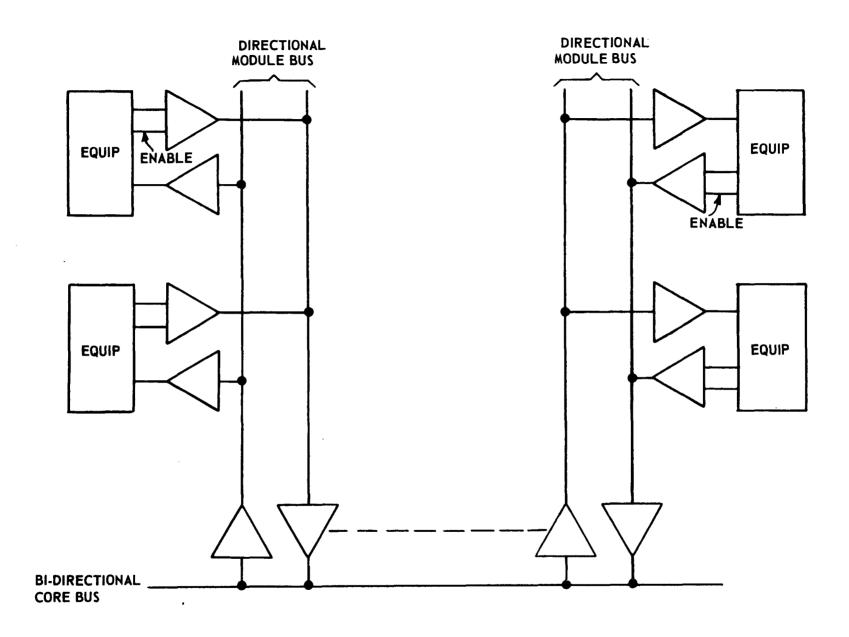

The second configuration shown in simplified form in Figure 2-2 retains the bi-directional core bus and provides directional module buses. This approach has the possibility of:

- . Eliminating the module bus enable signals, thus saving equipment

- . Improving the reliability of the system be eliminating the enable signal and by spreading the equipment loads over two buses instead of one

- . Eliminating the necessity of designing an enable bus control

- . Providing a reduction in spare parts

- . Costing the same as the other approach

The approach to both basic configurations were selected because they:

- . Allow checkout operations of individual modules

- . Allow the MSS to go through a buildup sequence without bus modification

- . Allow more reliable operations because the core bus is passive and the module buses are independent of each other.

The above approach is known as a spreaded star configuration due to the core length. A circular configuration with the bus looped in and out of each

Figure 2-1. Digital Data Bus, First Configuration

2-2

Space Division North American Rockwell

- -

2-3

module was examined but was discarded because of the problems it presented in reliability buildup sequence and module self check.

#### 2.2 ANALOG BUS

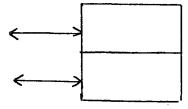

The analog bus is different from the digital bus in that the former is FDM and the latter is TDM. For this reason, the audio could best employ the configuration shown in Figure 2-2, except that there is no equipment enable (not required for FDM).

#### 2.3 COUPLING CONFIGURATION

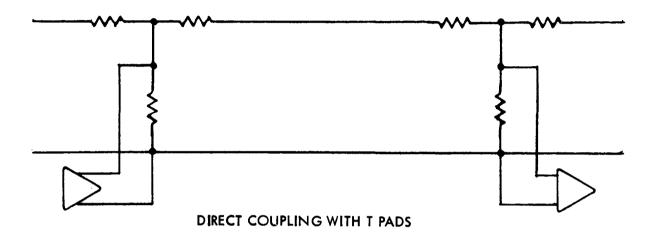

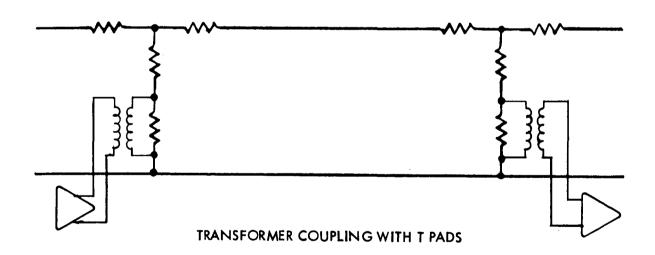

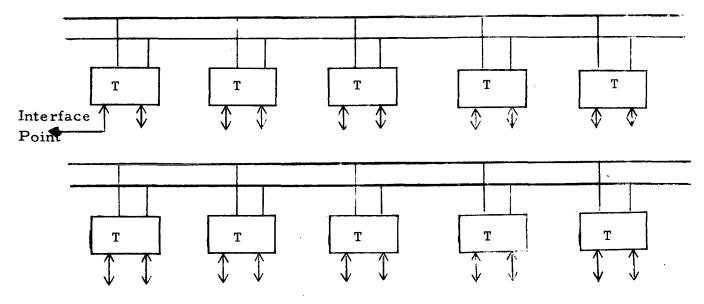

For digital and analog buses, both direct and transformer coupling techniques with surge protection were considered to interface the busses with their terminal devices and to interconnect sections of the bus.

#### 2.3.1 Digital Bus

The following were investigated for the digital bus (see Figure 2-3):

- . Direct coupling using off-the-shelf IC's

- . Transformer coupling using H-pad with shunt transformer

- . Transformer coupling using series transformer without padding

Two other methods are apparent and dual to choices two and three, and they are:

- Transformer coupling using O-pad with series transformer

- . Transformer coupling using shunt transformer without padding

The latter two methods were not examined because the padded series transformer is a dual of the padded shunt transformer and doesn't require a separate analysis and because, for the unpadded shunt transformer. sufficiently high impedance cannot be realized at 10 mbs. The data rate above which the unpadded shunt transformer becomes unrealizable lies somewhere between 10 and 100 kbs.

#### 2.3.2 Analog Bus

The following were investigated for the analog bus (see Figure 2-4):

- Direct coupling using T-pads

- Transformer coupling using T-pads with shunt transformer

Figure 2-3. Methods of Coupling

Figure 2-4. Direct and Transformer Coupling with T-Pads

#### 2.4 CONCLUSIONS AND RECOMMENDATIONS

The conclusions are as follows:

Configuration - The digital and audio bus should employ the same configuration: that is, the two-bus concept with bidirectional core bus and directional module buses (See Figure 2-2).

Coupling - The digital bus should employ transformer coupling: that is, the H-pad with shunt transformer. The analog bus should employ transformer coupling with a shunt transformer in a T-pad.

#### 3.0 DACS MODEL CONFIGURATION

#### 3.1 INTRODUCTION AND SUMMARY

The initial effort of the DACS BB study was to define a model for the Data Acquisition and Control Subassembly (DACS) breadboard. The purpose of this definition was to provide data to serve as a basis for the design studies of a DACS breadboard. This data was used, primarily as an input to WBS 85710-7, DACS Model Design, and WBS 94009-2, Data Bus Breadboard Design.

This section presents the recommended DACS breadboard system definition. It identifies the objectives of the breadboard, some potential vehicle related design problems, and a simplified implementation concept.

#### 3.2 RECOMMENDED DACS BREADBOARD CONFIGURATION

#### 3.2.1 Objective of DACS Breadboard

The primary objective of the DACS breadbroad is to verify the digital data bus concept for the modular space station (MSS). It shall be used to determine the availability of technology to provide accuracy of data transfer, reconfigurability, failure and tolerance, long useful life and standardization of interfaces. The following technology goals have been identified for the DACS breadboard; they are listed in descending order of priority.

1. Automatic line fault detection and isolation to a faulty connection, wire breakage, etc.

Automatic line fault detection is mainly an operation inherent in DBCU operation. The inability to communicate with one or a set of RACU's provides the detection. This item is reported by the breadboard DBCU to the test processor/panel. Line fault isolation requires data processing on numerous DBCU, indications of trouble to determine the fault location. This is mainly an operation external to the DBCU and, therefore, the DACS breadboard will utilize the test processor for whatever degree of fault isolation is required.

2. Automatic failure detection of DACS electronic hardware

Automatic failure detection of DACS hardware can sometimes be performed by the DACS itself. In a non-redundant configuration, however, this possibility wanes. The DBCU can report failures to communicate with RACU's and provide some amount of data useful in this determination. This is also a function of having more than one RACU on the same bus section to differentiate RACU fault from that of a bus section. The DBCU cannot, in general, report its own failure, nor does it have the data processing

capability for more than a gross level of failure detection (to multiple causes and equipments, for example). Thus the test processor is the logical location (as is the CP in the real DPA) for this final fault detection of DACS elements. The DBCU can and will report all fault indications to the test processor/ panel interface. Fault simulation is a requirement for all DACS breadboard units to enable testing this process.

3. Automatic reconfiguration, within microseconds, to continue operations

Reconfiguration, in microseconds or longer, requires equipment to be bypassed and, therefore, redundancy. This requires multiple breadboard units on a scale not yet contracted for by the NASA. It can be simulated in a gross sense with a nonredundant breadboard by DBCU/test panel indications; i.e., indicating a need to reconfigure at the proper time. These are the necessary first steps of the process. The breadboard operation is such that reconfiguration subroutines can be included in the DBCU memory if and when breadboard hardware is available to demonstrate it. At this time, an evaluation can be made. Time to reconfigure is dependent on the number of items in the system, and since this will always be less than the actual implementation, this must essentially be determined external to the breadboard.

4. Techniques for executive control of data traffic within the system

This goal is uppermost in the operational specifications for the breadboard units. A programmable DBCU is provided. The RACU breadboard is also flexible in terms of operational sequences and modes. A real-time interaction of the DBCU with a test processor/panel is also specified. This, too, can be used to evaluate executive control techniques as required.

5. Evaluation user-subsystem servicing techniques; i.e., polling, request/acknowledgement, etc.

This is similar to the discussion about goal 4. All of these items are provided in the requirements specification. Polling will be provided via the data bus in the breadboard by a specific DBCU routine and in conjunction with some of the normal data transfer operations.

Techniques for implementing several modes of operation concurrently

The DBCU will have the capability of operating in several modes. Full duplex operation of the data bus will also be available in the appropriate configurations. Simultaneous use of the data bus breadboard by the breadboard DBCU will be possible utilizing the external test interface. The DBCU by itself will not have the internal hardware for complete simultaneous operation. The use of a redundant breadboard with two DBCU's can easily demonstrate this operation.

7. Develop performance and interface constraints and design "rules" for production systems

Utilizing goals 4, 5, and 6, the breadboard can be very useful in this respect. The wide variation of operation will allow evaluation of all these items to the extent they are testable. Data collection for this evaluation will, of course, need to be performed external to the DACS breadboard.

8. Determine the optimum allocation of functions within the several components of the system

This is very difficult and costly goal for the breadboard since it would require locating these functional items in all breadboard units where they might be allocated. It also would not have very positive results because of the simulation nature and simplification utilized in constructing a breadboard. This is, however, specified in the breadboard for one very important function, that of error protection. Its allocation is such that error protective encoding and decoding can take place both internal to the breadboard units as well as by external devices through the external test interface. Some of the DBCU/test processor interaction also has this goal in mind. It is best done by analysis of the performance data collected on DACS breadboard operation external to the laboratory.

Note: Usage of this feature is hampered, at least, by the fact that the RACU breadboard, when in the non-BCH mode, still expects the timing to be unchanged from that of the BCH mode (see 5.2.1.4.2).

9. Two-way redundant transfer of digitally-coded signals at rates up to  $3 \times 10^7$  bits per second over distances up to 1000 feet

The DACS breadboard is presently specified to demonstrate twoway transfer of digitally-coded signals at rates up to  $1 \times 10^7$ bits per second over distances up to 400 feet. Redundant data transfer at these rates only requires additional breadboard units for implementation. This goal is evaluated by external monitoring.

10. Techniques for optimizing the efficiency of data transfers over the bus cable

The provisions in the DACS breadboard for technology goals 4, 5, and 6 provide the means to operate the breadboard and vary the required parameters. External data collection, analysis and evaluation is necessary to determine the data transfer efficiency measure and the DACS operations which optimize this measure.

11. Evaluate signal coding

Hardware signal coding for error protection is provided in the DACS breadboard. The results of the various possible encoding algorithms for various bus operations and external effects must be recorded, analyzed and evaluated external to the breadboard. Accumulation of error statistics requires, perhaps, test processor interaction which is available. Also, see note under goal 8.

12. Evaluate feasibility of standard intercoupling units (RACU's) to other equipments; develop a "family" of SIU devices

Some evaluation is possible and the development requirements are beyond the scope of this specification. Breadboard equipment, in general, provides little in the way of feasibility evaluation for standards. Since most items such as external interfaces are simulations of expected hardware, the situation is already idealized. The feasibility of standard interfaces always has its most serious test when applied to actual hardware, and this can be pursued in the breadboard by providing "real" subsystem hardware.

13. Evaluate methods of detection and/or recovery of erros in transmitted data (noise immunity)

This goal is included in goals 9, 10, and 11. It requires operation of the breadboard over long periods of time and through many variations and conditions. As stated in the discussion of goal 11, external recording and evaluation is a necessity.

14. Evaluate DACS redundancy concepts

To the extent that some of the DACS redundancy concepts are included in the breadboard units, such as alternate paths and operational modes, external evaluation can be performed. This will only be a gross evaluation without utilizing redundant breadboard equipments. Much can be done by external evaluation of results, derived from the non-redundant breadboard configurations, on paper, and in conjunction with recorded error statistics, etc. Also, proper design of breadboard tests and test sequences can enhance the capability of the breadboard to provide the necessary data.

15. Evaluate the reliability and user acceptability of "control-bywire" techniques

The reliability of operation, through results recorded externally, such as the number of incorrect data outputs or commands over a given period of time and operating rules, will allow some evaluation of this attribute. User acceptability is not necessarily enhanced by viewing breadboard demonstrations.

16. Evaluate performance limits of each element (RACU, DBCU, data bus assembly)

This goal is the easiest of the list to provide via the DACS breadboard. There are an astronomical number of possible "runs" which can be performed by the breadboard. The number of variables in the breadboard system are almost limitless. Attention to proper design of the breadboard performance tests can reduce this to a more manageable figure with just as reliable results. Almost all performance evaluation requires external data collection and "off-line" analysis.

Each technology goal has been discussed in terms of the breadboard DACS provisions relating to the goal. A brief rationale was given for the level at which each of these goals are incorporated into the design requirements for the DACS breadboard. The major constraints on satisfying the technology goals is one of cost. Redundant configurations, although considered in the DACS breadboard requirements, necessitate considerably more breadboard units than are now to be provided. The breadboard DACS can expand, at a future time, to satisfy most of these technology goals. And by proper design of breadboard tests, much of the need for additional breadboard units can be obviated.

#### 3.2.2 Potential Vehicle Design Problems

There exists a broad range of vehicle and subsystem configurations and the final choice of configuration could well be anywhere in this range; therefore, the DACS breadboard must be sufficiently flexible to simulate the DACS in whatever physical configuration may be selected for the MSS.

#### 3.2.3 The DACS Model

The DACS breadboard shall contain at least one of every piece of equipment needed in the DACS plus sufficient cable runs and junction points to demonstrate the performance of the DACS in different configurations. As a minimum, the model shall contain a DBCU or DBCU simulator, a RACU or RACU simulator, and a digital data bus breadboard.

The digital data bus breadboard should consist of enough cable segments to allow it to be connected into a number of configurations.

It is desired that the breadboard be capable of demonstrating both bilateral and unilateral data flow, and combinations of bilateral and unilateral. For example, one combination which should be demonstrated has a bilateral core bus and a unilateral module bus.

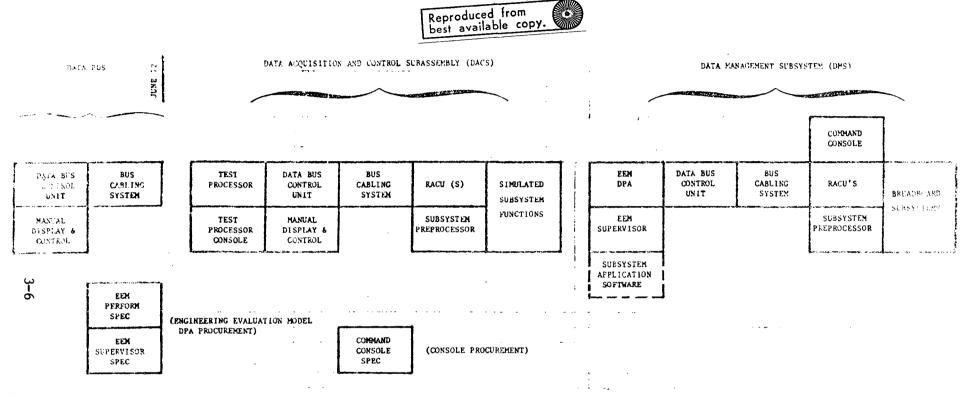

The DACS breadboard will ultimately become a part of a Data Management Subsystem (DMS) engineering evaluation model. The growth sequence is illustrated in Figure 3-1. The first phse of the growth sequence will encompass the following hardware:

> Digital data bus breadboard - ITT Demonstration support equipment for above - ITT

Data bus control unit breadboard - Autonetics Demonstration support equipment for DACS breadboard (other than standard laboratory equipment) - Autonetics

In addition to this hardware, RACU's or RACU simulators will be supplied (by NASA) and integrated with the above hardware to form an integrated DACS breadboard.

# 3.2.4 Performance Parameters

The following performance parameters have been identified as performance parameters for the DACS. The DACS breadboard should demonstrate satisfactory performance within the indicated range for each parameter.

| Parameter                                                                                                                                      | Range                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Probability of fault detection<br>Time to detect, isolate, and reconfigure<br>Number of simultaneous service requests<br>(assume <1 fault/sec) | >0.98<br><4 milliseconds<br><10                 |

| Data transfer rate<br>Maximum length of path<br>Maximum density of taps                                                                        | 1 MBPS to 30 MPBS<br><1200 feet<br><10 per feet |

Many of the design parameters and breadboard objectives have been modified or deleted during the course of development. Most notable was the decision to build a data bus optimized to operate at 10 MBPS. A point design was required by the ringing filter used for clock recovery. The 10 MPBS rate was based on the DPA requirements analysis (see Volume IV of this report).

# 4.0 DACS REDUNDANCY CONCEPTS

# 4.1 INTRODUCTION AND SUMMARY OF REDUNDANCY REQUIREMENTS

This section covers the advantages and disadvantages of a general range of concepts and methods applicable to the DACS. Recommendations of methods are made and justified.

The DACS is composed of three major elements. These are the remote acquisition and control units (RACU's), the digital data bus control unit (DBCU), and the digital data bus assembly. The DACS is a part of the central processor subassembly of the Data Processing Assembly (DPA).

The overriding requirements were found to be the single and triple failure tolerance requirements and the physical separation of redundant subsystems into pressure isolatable volumes.

Redundancy concepts and reliability enhancement techniques include parallel and serial redundancy, data protection and failure detection, isolation and repair and test concepts. The recommendations for the degree, level and type of redundancy for each DACS element are presented in this section. These recommendations include the split between hardware and/or software techniques, the utilization of error protection coding, the replacement/repair methods, and a definition of the replaceable items, and the rationale for each selected candidate DACS element.

The following redundancy requirements were imposed on the modular space station subsystems.

- 1. A capability must be provided for each non-critical function to fail safe for the first failure.

- 2. For a critical function a capability must be provided for:

- a. Full operation subsequent to a first failure (fail operational)

- Reduced or "out of spec" performance subsequent to a second failure (fail degrade)

- c. Crew survival for at least 96 hours subsequent to a third failure (fail emergency)

- 3. Time critical functions require active (on-line continuous operation) redundancy. Non-time critical functions require at least standby (wired in and can be placed in operation with automatic or manual switchover.

The analysis of methods of failure tolerance implementation begins with the Guidelines and Constraints imposed upon the modular space station, which is used to construct several applicable "loop" modules for each level of criticality. The models are then used to develop candidate mechanizations for each element of the data system (DACS); the data bus assembly, the RACU unit, and the data bus control unit. Recommendations for unit mechanization are made, then reassembled for a summation of the recommended configuration for DACS.

#### 4.2 SUBSYSTEM MODELS AND CONFIGURATIONS

There are three types of subsystem functional loops for which various models will be postulated and used to study the DACS redundancy criteria. They are non-critical, non-time critical, and time critical subsystem functional loops in order of increasing redundancy requirements. Previous discussions have generalized the redundancy requirements associated with each of these functions as fail-safe, requiring as a minimum standby redundancy, and requiring active redundancy in the same increasing order.

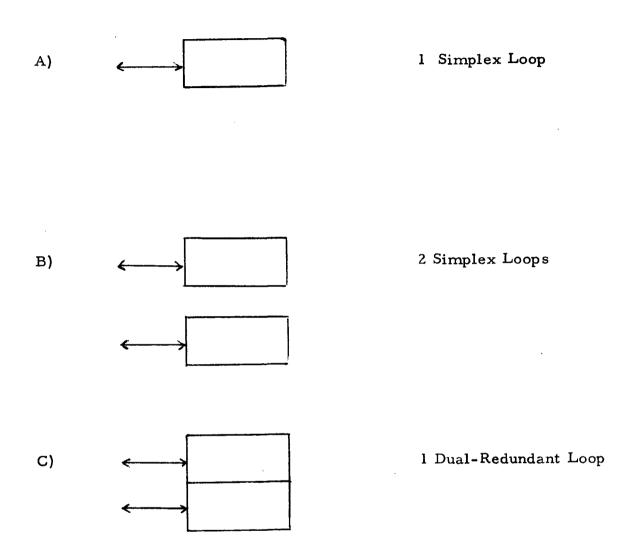

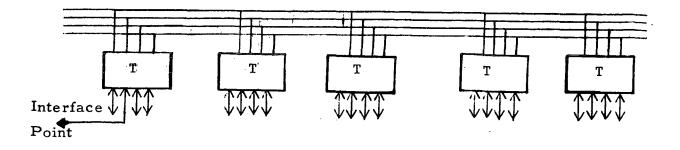

#### 4.2.1 Non-Critical Subsystem Functional Loops (Figure 4-1)

The models for non-critical subsystem functional loops can be of three types. The functional loop in its simplest form would be simplex in nature and only one such functional loop would exist on the space station. In general this model would not be fail-safe after the first failure (its own internal failure) since there would be no redundant mechanism to perform the "safe" function.

The second model of a non-critical loop would be two simplex loops. These two loops might be necessary for fail-safe capability, utility in performing the function in separate locations, constrained by physical relationship to other functional loops, or possible desirable maintenance or other considerations. In any of these events, such a model is possible and will be considered in providing the DACS interface.

A third model would be a dual-redundant loop for much the same reasons as the two-simplex loop model. This dual redundancy might or might not be the total loop. In all likelihood it would consist of enough redundancy to provide a true fail-safe (after the first failure) subsystem functional loop.

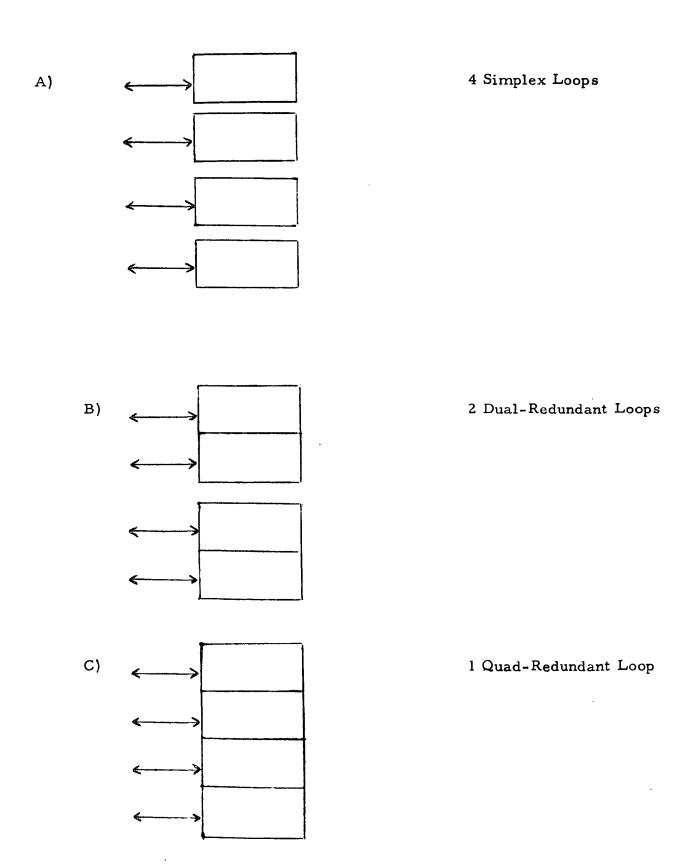

# 4.2.2 <u>Non-Time Critical Subsystem Functional Loops</u> (Figure 4-2)

Again there are three basic models of non-time critical subsystem functional loops providing the necessary space station function performed by each loop. These models do not contain at this time any instruction as to the method by which they operate internally, except as implied by the model definition. Each model may or may not require higher level authority or intervention for its operation.

Figure 4-1. Non-critical Subsystem Functional Loop Models

The first model is (as before) a simplex configuration. For non-time critical functional loops, four such simplex loops are required to meet the three failure tolerance criteria. One or more of the simplex loops may also have other functions, but are viewed in the modeling as that necessary to perform the one single non-time critical function as if no other loops existed.

The second non-time critical model would be two dual-redundant loops, each loop being single failure tolerant. This model is extremely important in light of the redundancy requirements and physical separation implied by pressure isolatable volumes. As in all models composed of multiple assemblies (containing similar or identical functional loops), the multiplicity assumes a physical separation is possible if desired. Each dual redundant loop may or may not contain simultaneously operating redundant elements.

The third model for non-time critical loops would be one quad-redundant functional loop. The quad-redundant assembly has the same characteristic as all models in that its internal operation is as yet unspecified. As can readily be seen for all redundant loop models, the options of type of redundancy (active, standby, distributed, parallel, serial, etc.) is left open to reduce confusion and model proliferation.

One may note that there is no model that utilizes triple-redundancy. Due to the stringent failure criteria, such a model would require two tripleredundant loops for three-failure tolerance. This certainly is possible, although it exceeds the requirements, and may be the method by which single failure (and no more) tolerance is achieved. For the purposes of this study this case will be assumed included in the second model utilizing two dualredundant loops, each loop having single failure tolerance. As stated before, no internal mechanization is assumed for these models and they might well require more the simply doubling all elements in the loop. In fact the terminology dual-redundant is only used to imply in a more recognizable fashion the minimum configuration necessary for single failure tolerance, and the terms "dual redundant" and "single failure tolerant" will be used interchangeably in this report.

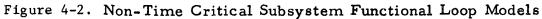

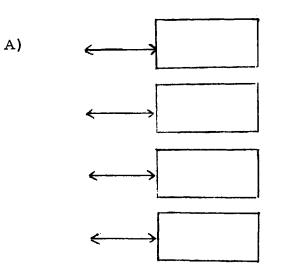

## 4.2.3 <u>Time Critical Subsystem Functional Loops</u> (Figure 4-3)

These functional loops are, of course, the mody critical on board the space station and the most costly in terms of DACS interaction. It is hoped that the number of such loops might be kept to a minimum, and as such they might not be the overriding design requirements, except in terms of failure tolerance. If they are few enough, it may be possible to over provide, in terms of redundancy, DACS elements more suited to the high usage loop models (non-critical models hopefully).

Three models for time-critical functions are again postulated similar in most respects to those for non-time critical functional loops. The differentiation between non-time and time-critical functions, in fact, is only one of response time and not of degree or level of redundancy, except in the option of more time to provide the redundancy. These three models for the timecritical functional loops are thus four simplex loops, two dual-redundant (single failure tolerant), and one quad-redundant loop.

B) ←→

C)

Time-Critical Subsystem Functional Loop Models

2 Dual-Redundant Loops

1 Quad-Redundant Loop

4-6

## 4.3 DACS REDUNDANCY AND RELIABILITY CONCEPTS

## 4.3.1 General

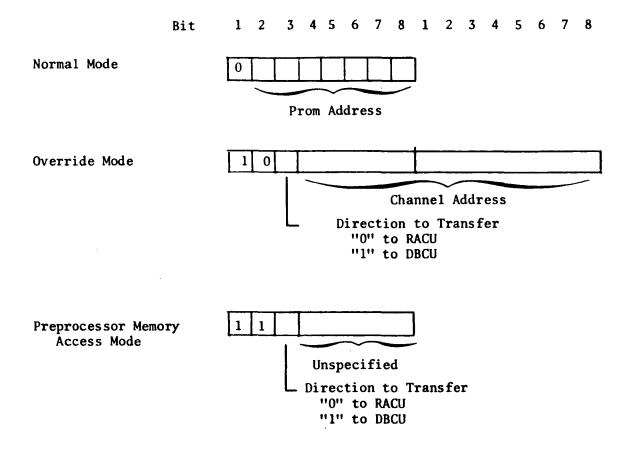

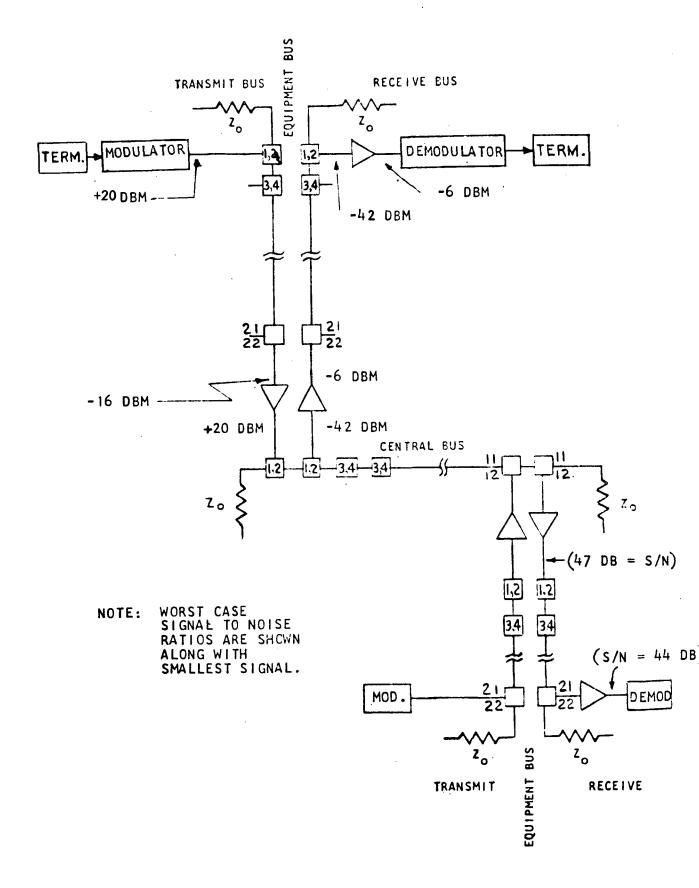

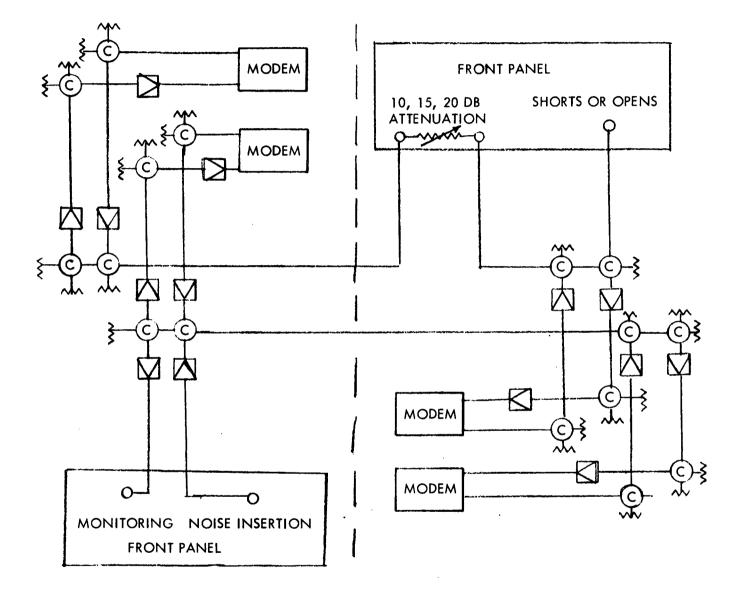

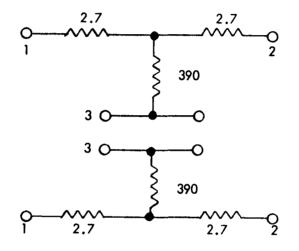

The overall DACS must be three-failure tolerant since it is assumed to be a necessary part of the control interface for <u>critical</u> functional loops. The "brute force" approach to meeting this requirement would be a total quadruple parallel redundancy for all DACS elements. Any approach to be considered must also meet the other design constraints and requirements, such as physical separation between pressure volumes, physical separation in the routing of the DACS data bus assembly, and control by two computer assemblies in separate pressure volume locations.