# A Reproduced Copy of

N73-17575

Reproduced for NASA  $by \ the \\ \textbf{NASA Scientific and Technical Information Facility}$

-173-10653 CR-12870Z C.1

# ELECTRON-PROTON SPECTROMETER DESIGN SUMMARY

LEC Document Number EPS- 522

TECHNICAL LIBRARY BUILDING 45

JAN 2 3 1973

Manned Spacecraft Center Houston, Texas 77053

#### Prepared by

Lockheed Electronics Company, Inc. Houston Aerospace Systems Division Houston, Texas

Under Contract NAS 9-11373

For

National Aeronautics and Space Administration

Manned Spacecraft Center

Houston, Texas

June 1972

N73-17575

(NASA-CR-128702) ELECTRON-PROTON SPECTROHETER DESIGN SUMMARY (Lockheed Electronics Co.) 147 p HC \$9.50

Unclas

CSCL 14B

C3/14 6271

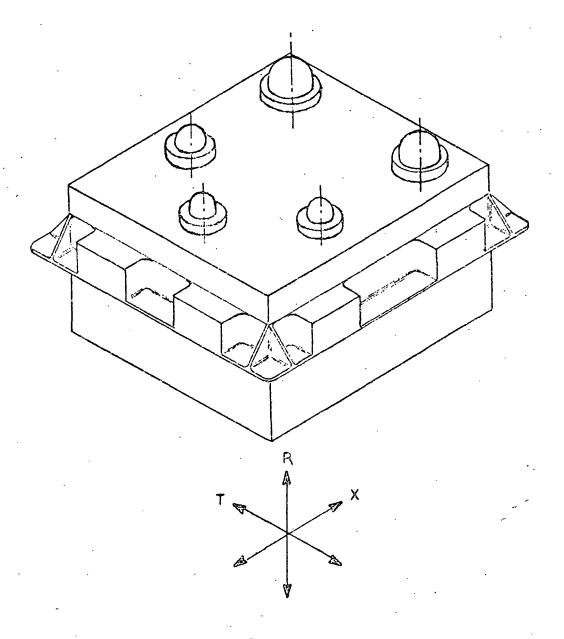

#### 1. DESIGN REQUIREMENTS

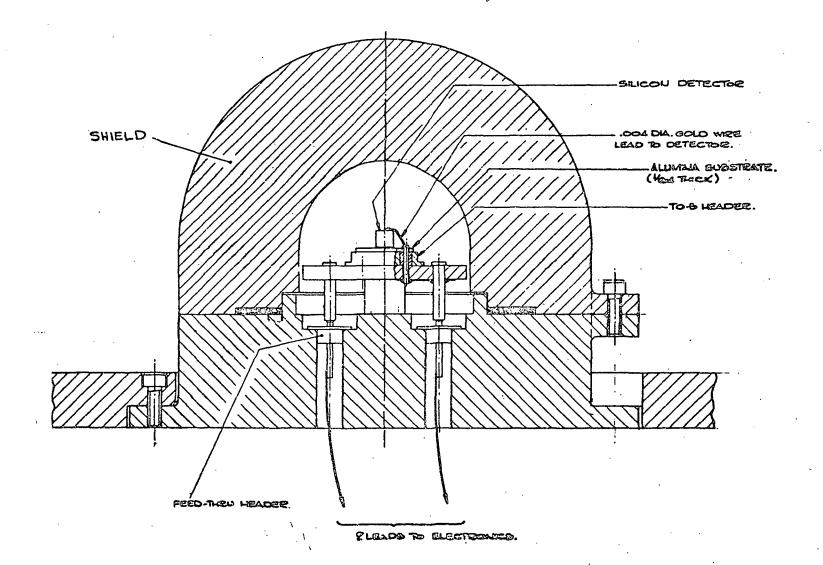

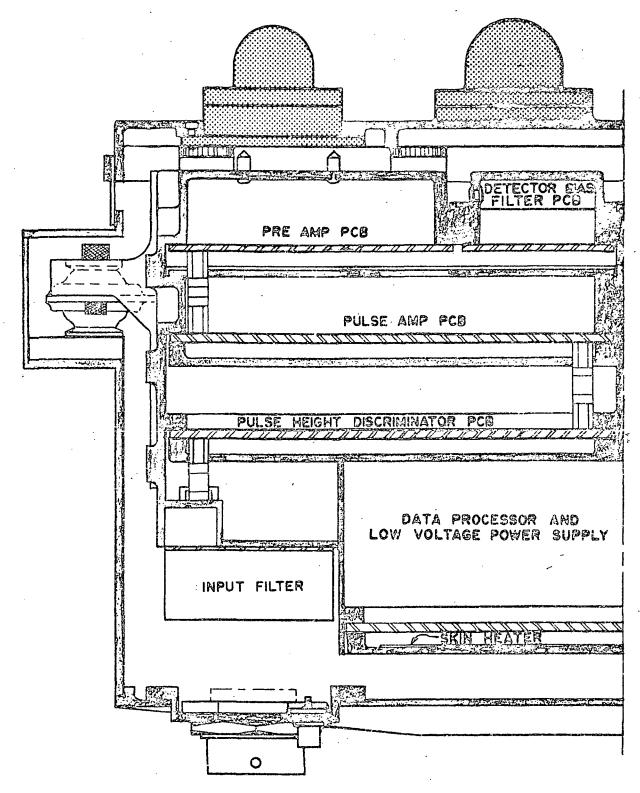

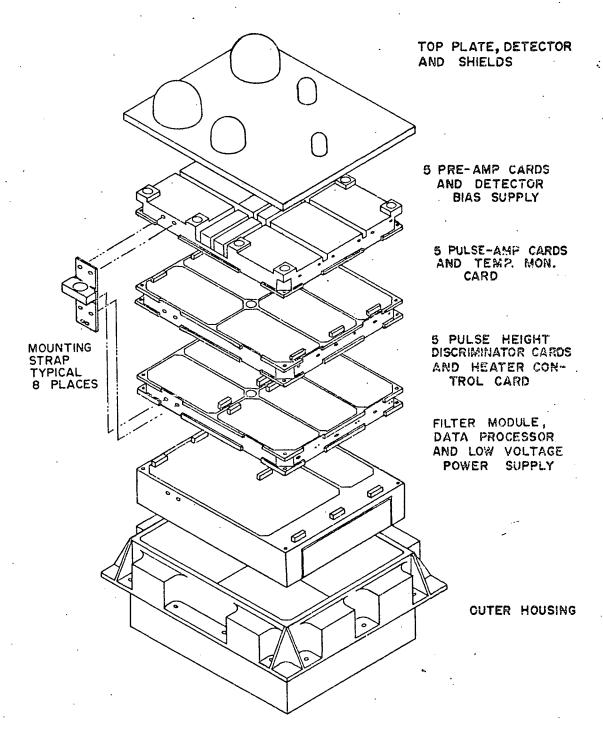

The Electron-Proton Spectrometer (EPS) (Figure 1) will be placed aboard the Skylab in order to provide data from which electron and proton radiation dose can be determined. The EPS has five sensors, each consisting of a shielded silicon detector, as shown in Figure 2, these provide four integral electron channels and five integral proton channels from which can be deduced four differential proton increments.

Primary dose from high energy charged particles can be calculated utilizing the range energy relation for energy degradation; that is, a charged particle of kinetic energy E will have an energy E' after penetrating a shield with a thickness t. The relation between E and E' is given by

$$R(E') = R(E) - t$$

Where R(E) and R(E') are the ranges in the shield material of a particle with kinetic energies E and E', respectively. The energy deposited in a volume at the center point of a spherical shell of thickness t is the dose at that point and is given by

$$D(t) = 1.6 \times 10^{-8} \int_{0}^{\infty} \frac{dF}{dE} \left( \frac{dE}{dx} \right)_{E} dE'$$

Where  $\frac{dF}{dE}$ , is the differential flux at that point,  $\left(\frac{dE}{dx}\right)_E$ , is the stopping power for a particle with energy E' in the element of volume at the center point of the shield.

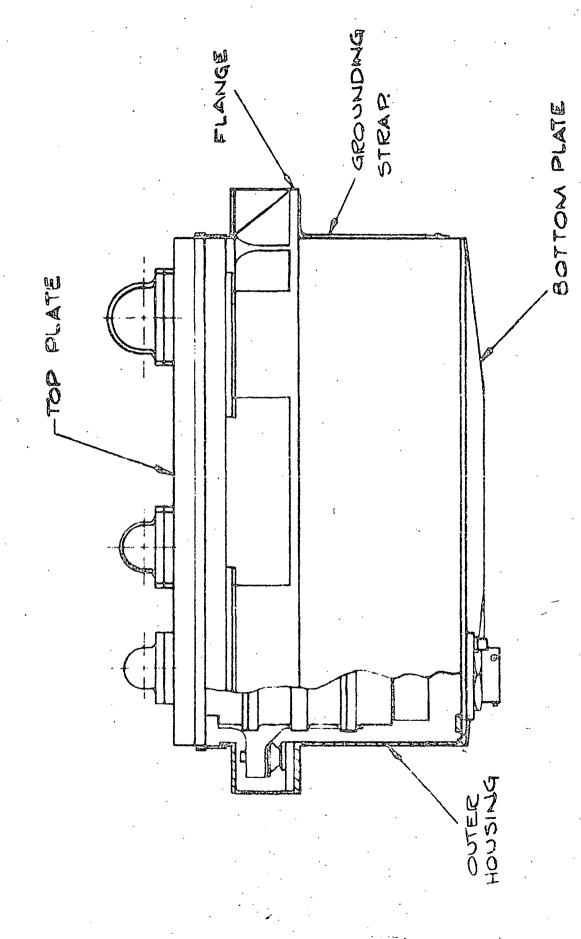

Figure 1. ELECTRON-PROTON SPECTROMETER

Figure 2. SHIELDED SILICON DETECTOR

$$\frac{dF}{dE}$$

$dE = \frac{dF}{dE}$ ,  $dE'$

into the equation for dose gives

$$D(t) = 1.6 \times 10^{-8} \int_{R^{-1}(t)}^{\infty} \frac{dF}{dE} \left(\frac{dE}{dx}\right)_{R^{-1}[R(E)-t]} dE$$

where  $R^{-1}(t)$  and  $R^{-1}[R(E)-t]$  are inverse ranges corresponding to energies whose ranges are t and R(E)-t, respectively. Hence, it can be seen that determination of the radiation dose inside a shield can be accomplished with knowledge of the shield thickness and the differential spectrum,  $\frac{dF}{dE}$ , incident on the shield. In the case of the Skylab, the shield thickness comes from the description of the vehicle geometry and the differential spectrum of the incident particulate radiation will be provided by the EPS.

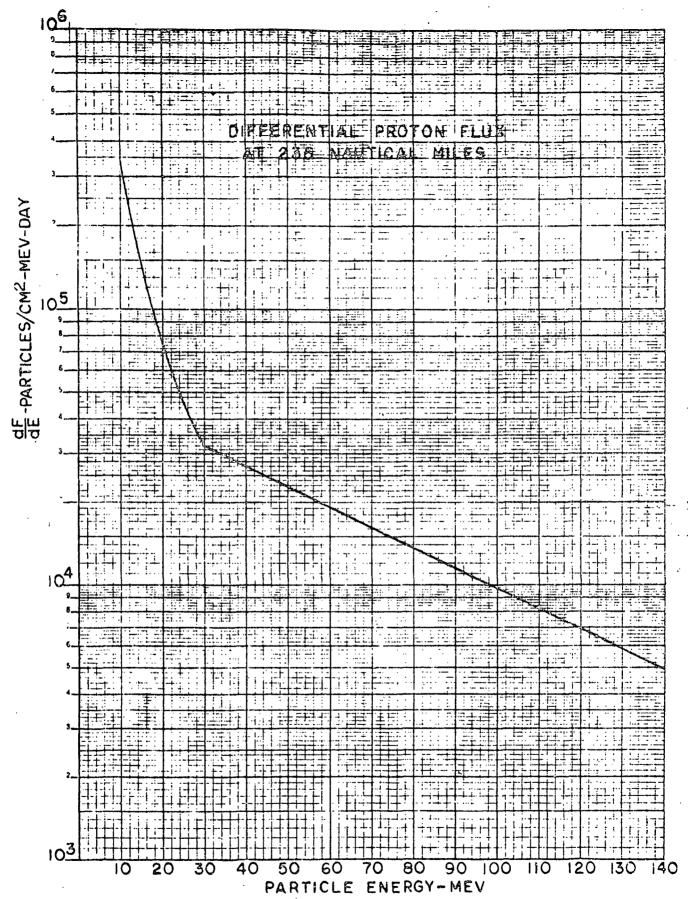

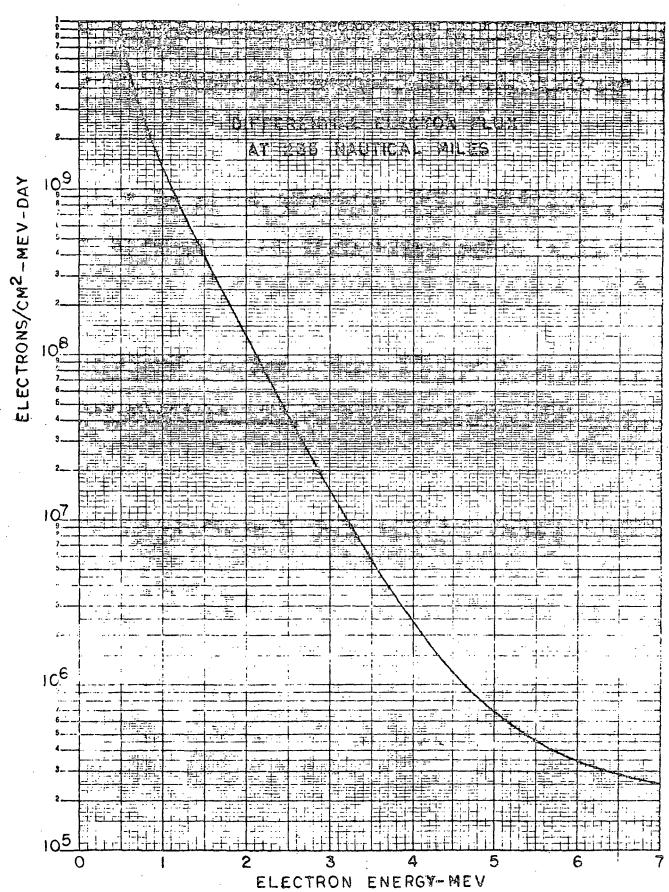

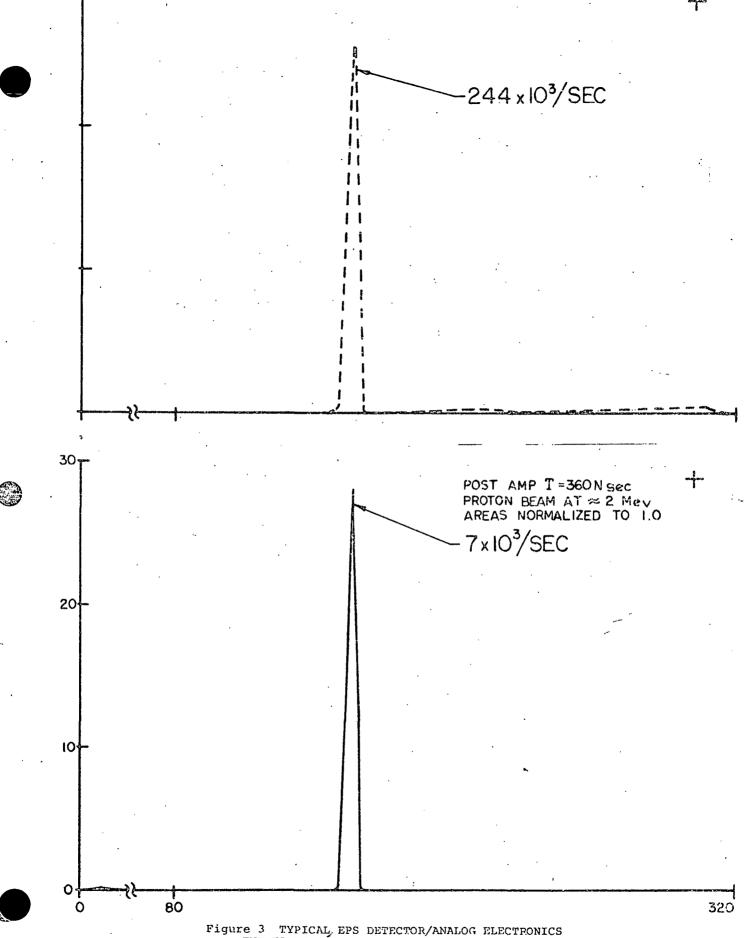

The anticipated differential proton spectrum at an orbit altitude of 235 nautical miles is shown in Figure 3 and can be represented by the sum of two expontials

$$\frac{dF}{dE} = 2.29 \times 10^{6} e^{-\frac{E}{4.88}} + 5.33 \times 10^{4} e^{-\frac{E}{58.75}}.$$

Figure 3. DIFFERENTIAL PROTON FLUX AT 235 NAUTICAL MILES

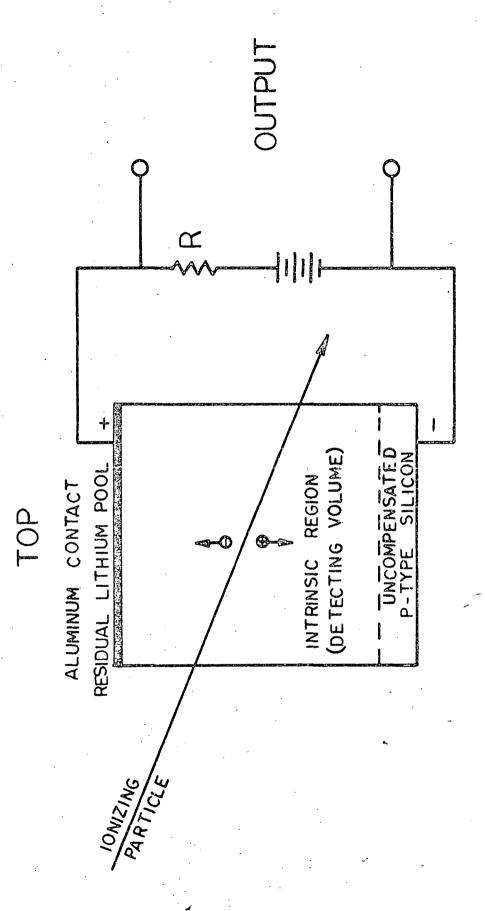

The sensitive element of the EPS sensor is the silicon detector which consists of a cube of lithium-drifted silicon crystal, as shown in Figure 5. The detector is operated as a reverse-biased diode. The ionization created by the passage of an energetic charged particle through the sensitive volume of the detector is proportional to the energy lost by the particle and when collected and amplified provides a signal which is a measure of the energy deposited in the detector.

Detection of electrons in the desired energy range will be accomplished by means of a low level discriminator, 200 - 300 keV, on each of the first four detector channels. By virtue of the low level discrimination the electron measurements will be integral. Separation of the protons and electrons will be accomplished by the fact that only a negligible percentage of electrons can deposit enough energy to be counted in the proton channels. The electron channels must be corrected for the response to protons.

Electronics discriminator set at approximately 2 MeV will comprise the five integral proton channels. The proton flux in four differential energy increments is obtained by subtraction of the contents of energy-adjacent proton channels and the use of iterative procedures, if necessary.

The parameters pertinent to the five detector channels are given in Table I.

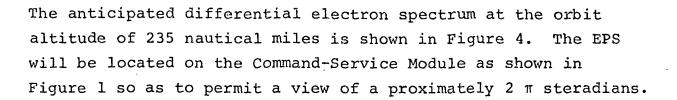

Figure 4, DIFFERENTIAL ELECTRON FLUX AT 235 NAUTICAL MILES

Figure 5. SILICON DETECTOR

TABLE I CHANNEL BOUNDARIES AND ENERGY LEVELS

| ELECTRON<br> HRESHOLD<br> ENERGY          | 0,45 | 1.22 | 2,38 | 3,90 |            |

|-------------------------------------------|------|------|------|------|------------|

| Disc.<br>Evel<br>(Mev)                    | 7    | 2    | 2    | 2    | <b>C</b> 1 |

| SHIELD<br>THICKNESS<br>(CM)               | ,037 | 180  | 904' | ,710 | ,890 BR    |

| INTEGRAL<br>PROTON<br>BOUNDARIES<br>(MEV) | 7.9  | 18,5 | 29,1 | 39,7 | 77.3       |

| Detector<br>SIZE<br>(MM)                  | 2    | 2    | 2    | 2    | 2          |

| DETECTOR<br>CHANNEL                       |      | 2    | Μ.   | . 17 | <u>ا</u> ب |

|                                           |      |      |      |      | J          |

The response of the integral proton channels to omnidirectional protons has been calculated. The calculation was based on the range energy relation for energy degradation and consisted of determining, as a function of angle, the portion of the detector thick enough to provide a pathlength long enough to absorb enough energy to exceed the discriminator level and integrating over 2  $\pi$  steradians.

A calibration program is planned to provide data needed to confirm the analytic response functions. Since the response function is strongly dependent upon the dimensions of the detector sensitive volumes, the detector thicknesses will be measured by means of penetrating protons from a cyclotron. Angular response data will be taken for protons to confirm or correct the analytic response functions. Electron angular response data will be taken in order to generate the electron response functions.

#### 2. SENSOR DESIGN

#### 2.1 DESCRIPTION AND PHYSICS OF DETECTORS

The detectors to be used on the EPS are constructed of lithium drifted silicon. This type of device is fabricated by starting with a moderately pure piece of P-type silicon. Lithium is deposited on one surface of the silicon and then diffused and drifted throughout the volume of silicon at elevated temperatures. The lithium, an N-Type (Donor) material, compensates electrically the principal impurity, namely, boron (acceptor) resulting in a structure of rather high resistivity.

The detector is operated basically as a reversed biased diode (Fig. 1). An ionizing particle, for example a proton, entering the detector loses energy by ionization in the silicon creating a series of hole-electron pairs along its path. Under the influence of the applied electric field (bias voltage) the holes move toward the negative electrode and the electrons toward the positive side setting up a voltage pulse across a load resistor. This pulse is then amplified and shaped by external circuitry. The number of hole-electron pairs created and hence the pulse output is linearly proportional to the energy lost in the active volume by the incident ionizing particle. In the case where the particle is stopped in the active volume the pulse output is linearly proportional to the incident particle energy. For particles energetic enough to penetrate the detector the pulse output will have a more complex energy dependency but will still be linearly proportional to the energy lost in the detector.

This type of detector has the ability to maintain a constant gain over a wide temperature range. Moreover it operates with a modest bias voltage of a few hundred volts and is relatively insensitive to bias voltage changes.

Figure 1 DETECTOR AND EXTERNAL CIRCUIT

#### 2.2 LIMITATIONS OF THE DETECTORS

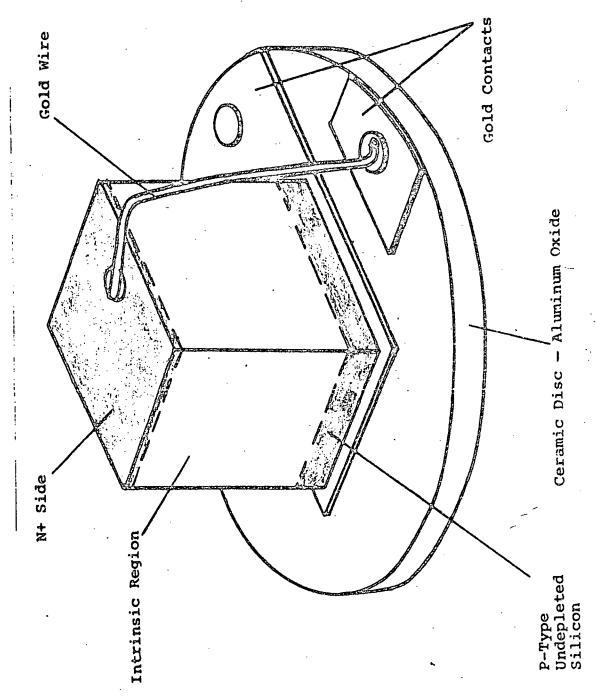

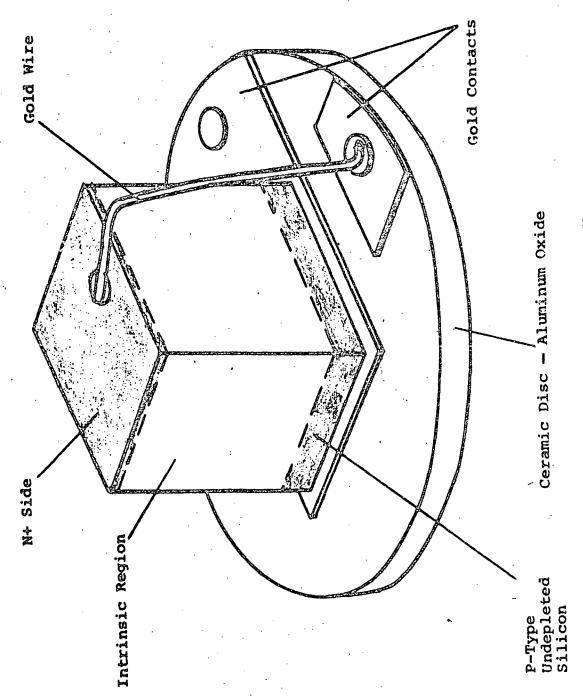

The EPS requirements of a 2 m steradian acceptance solid angle and omnidirectionality within this angle require a detector of open geometry. Figure 2 shows the geometry of an EPS detector. The silicon is mounted exposed on an aluminum oxide disc which is mounted on a T05 transistor header. Electrical contact is made to the top of the silicon by a fine gold wire bonded with conducting cement. The silicon cube is epoxy bonded to the aluminum oxide disc. The most probable point of mechanical failure, if incurred, would be at the bond between the cube and the disc during temp-cycling and/or vibration. It is intended to temperature cycle and vibration test each detector as part of the acceptance testing.

As in any type of solid state detector the EPS detectors exhibit a standing D.C. leakage current which in turn creates noise in the detector. The leakage current and hence the noise are directly proportional to temperature, although non-linearly. Detector noise affects instrument operation in two ways: 1) By contributing to the energy resolution and, 2) By contributing false counts. Neither of these are expected, however, to be significant at the anticipated flight temperatures.

Construction of this type geometry detector requires leaving a region of uncompensated P-Type silicon to accomodate the continued drift of the lithium. The lithium drift rate is temperature and bias dependent. At the anticipated flight temperatures, however, the total drift during the mission is expected to be within tolerable limits.

In the EPS detectors particles will enter the five exposed sides of the silicon cube, and in the case of the more energetic particles, will completely penetrate. A know-ledge therefore of the active volume of the detector is necessary. Previous measurements have shown that the lateral dimensions can be manufactured rather accurately. The thickness in the direction of the lithium drift, however, will be ascertained for each detector by means of nuclear thickness measurements with a particle accelerator.

Figure 2 DETECTOR GEOMETRY

#### 3. ELECTRICAL DESIGN

#### 3.1 SYSTEM OPERATION

The EPS electrical package consists of five systems, namely:

Scientific Analog System

Data Processor System

Housekeeping System

Power System

Heater System

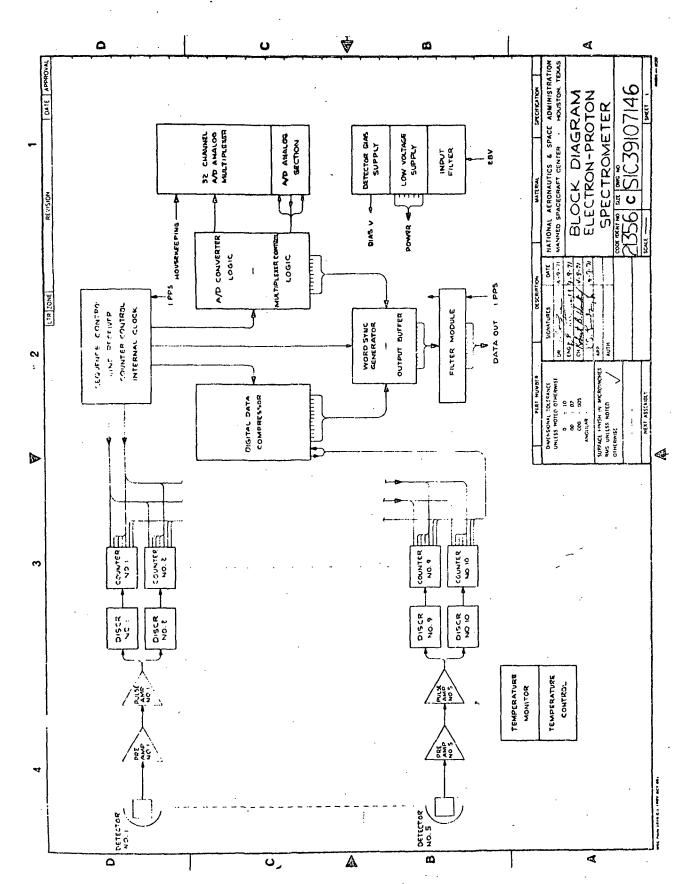

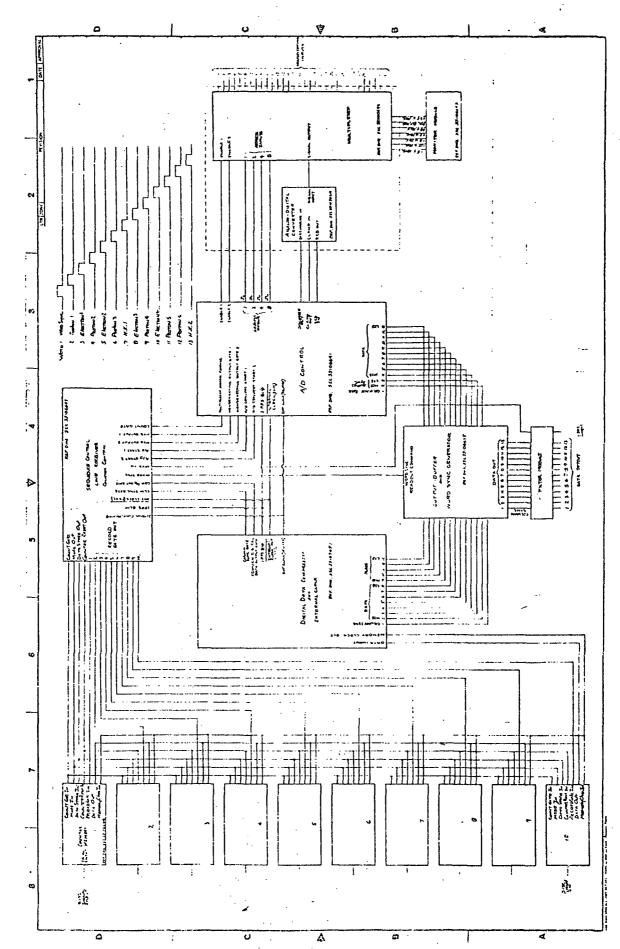

The functional interdependence of these systems is shown in Drawing SIC39107146, Block Diagram Electron-Proton Spectrometer.

The purpose of the Scientific Analog System (see block diagram) is to detect the random occurance of current impulses eminating from EPS detectors, determine if the total impulse charge exceeds a predetermined value, and if so submit an output signal for recording by the Data Processor. There are five scientific channels which are:

Independent

Adjustable in counting level to allow use with detectors having variable dimensions

Capable of single valued counting-rate performance to 10<sup>6</sup> counts per second

Immune to detector generated noise

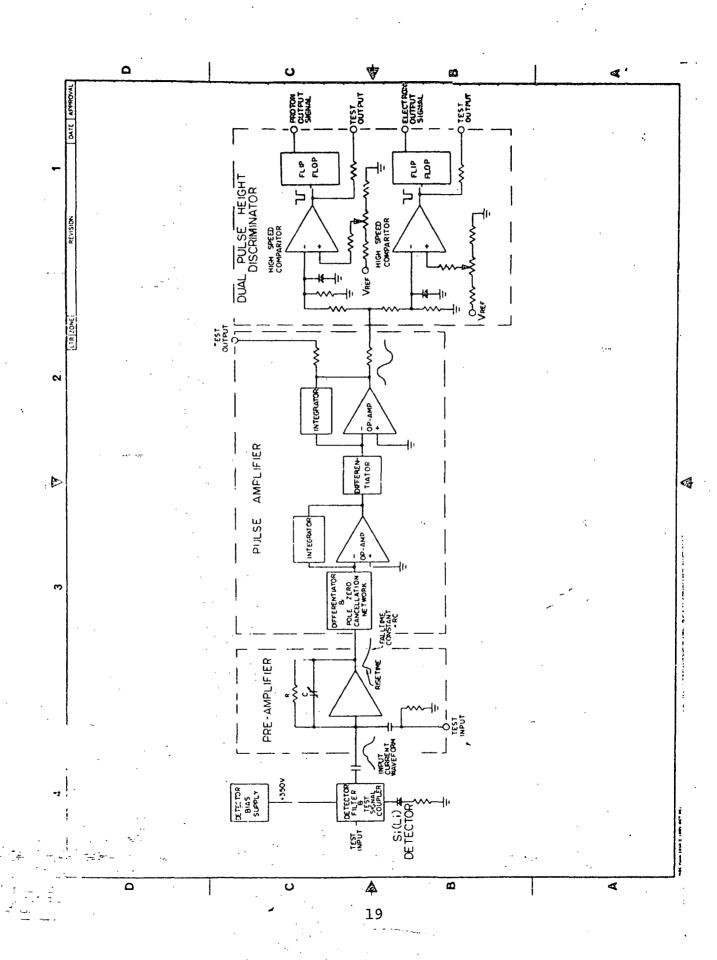

Each scientific channel is made up of a preamplifier, a pulse amplifier, and a dual pulse height discriminator.

The preamplifier converts the detector's current impulse to a slowly decaying step function whose amplitude is proportional to the total charge input. The pulse amplifier filters this step input producing a bipolar waveform at its output. The dual pulse height discriminator compares the bipolar wave form to two reference levels. If the input wave form exceeds either of these two reference levels, a corresponding output pulse is directed to a prescaler. The prescaler generates an output signal for every other excitation of the discriminator.

The function of the Data Processor is to digitally integrate the prescaler outputs individually and present the information to the spacecraft telemetry system in an acceptable form under control of the spacecraft. This integration provides 12 seconds of counting for every 13 seconds of real time. In addition, the Data Processor accepts analog housekeeping signals, digitizes them sequentially and properly mixes this with the scientific information. The data processor utilizes high reliability, low power TTL logic in its digital section and high reliability low power amplifiers in its analog to digital converter section. The Data Processor consists of the following modules:

Sequence Control, Line Receiver, Counter Control

Counter/Memory Module (10)

Digital Data Compressor and Internal Clock

Analog Digital Converter

A/D Control

Multiplexer Module

Output Buffer and Word Sync Generator

The Housekeeping System provides signals to the Data Processor analog to digital converter that yield information concerning the operational status of all important EPS parameters. Those functions monitored include:

detector leakage currents

detector resolutions

electronic package temperature

detector plate temperature

power supply levels

heater status

A time of 208 seconds is required to transmit a complete cycle of housekeeping information. Ground based analysis of this data allows proper manual control of EPS mode of operation.

The EPS Power System accepts spacecraft power and converts it to levels required by the EPS. Major subsystems are the Low Voltage Converter and the Detector Bias Supply.

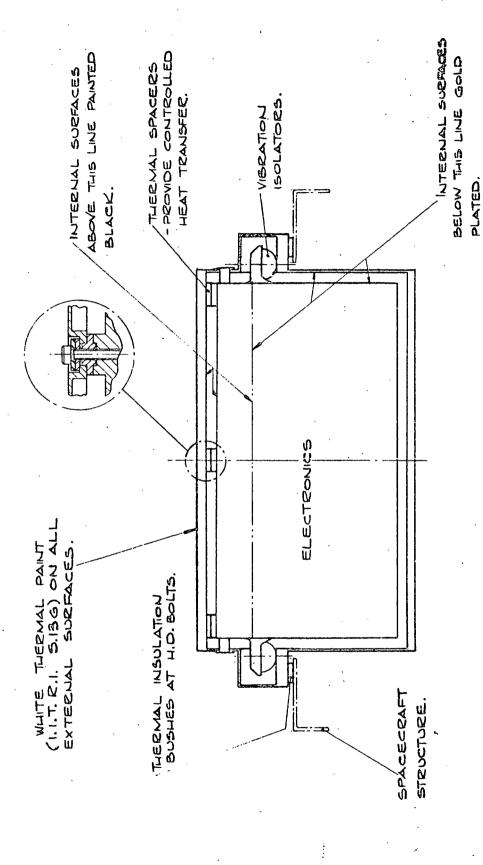

The Heater System functions in a temperature control capacity. An internal temperature sensor is continually monitored by control circuitry. If the package temperature drops below 0°C, six watts of power is dissipated in the inner housing structure by skin heaters. When the temperature rises above 10°C, the six watts of power is removed.

#### 3.2 SCIENTIFIC ANALOG SYSTEM

#### 3.2.1 PREAMPLIFIER

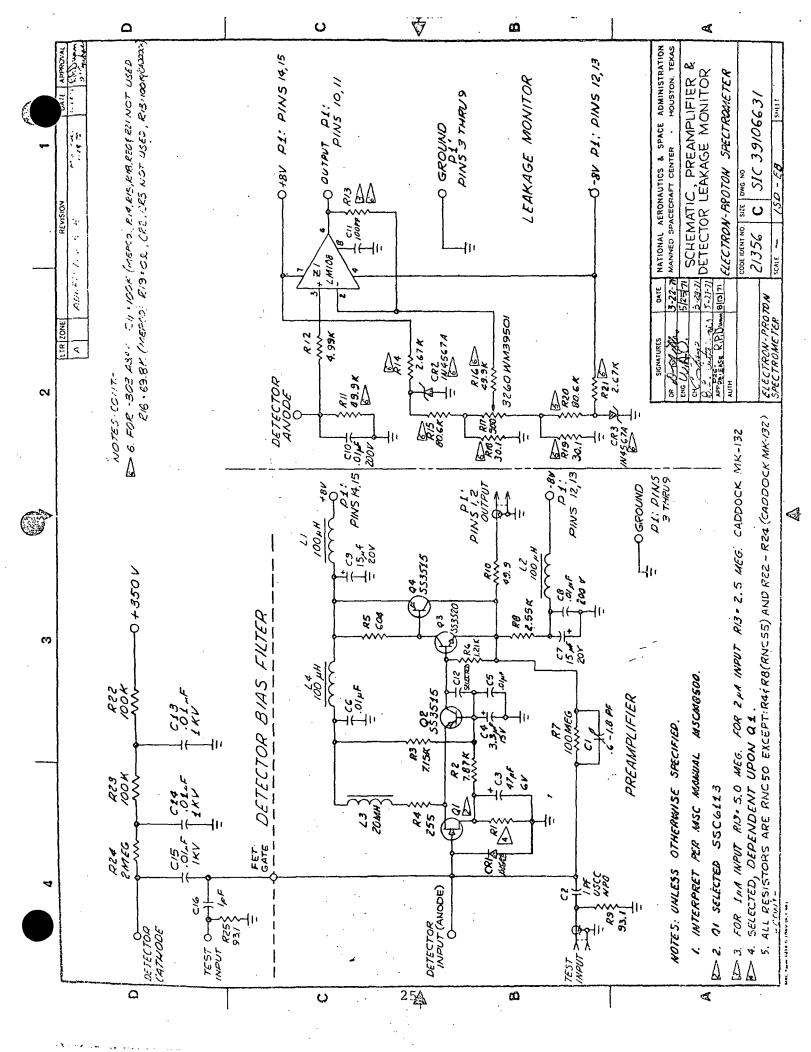

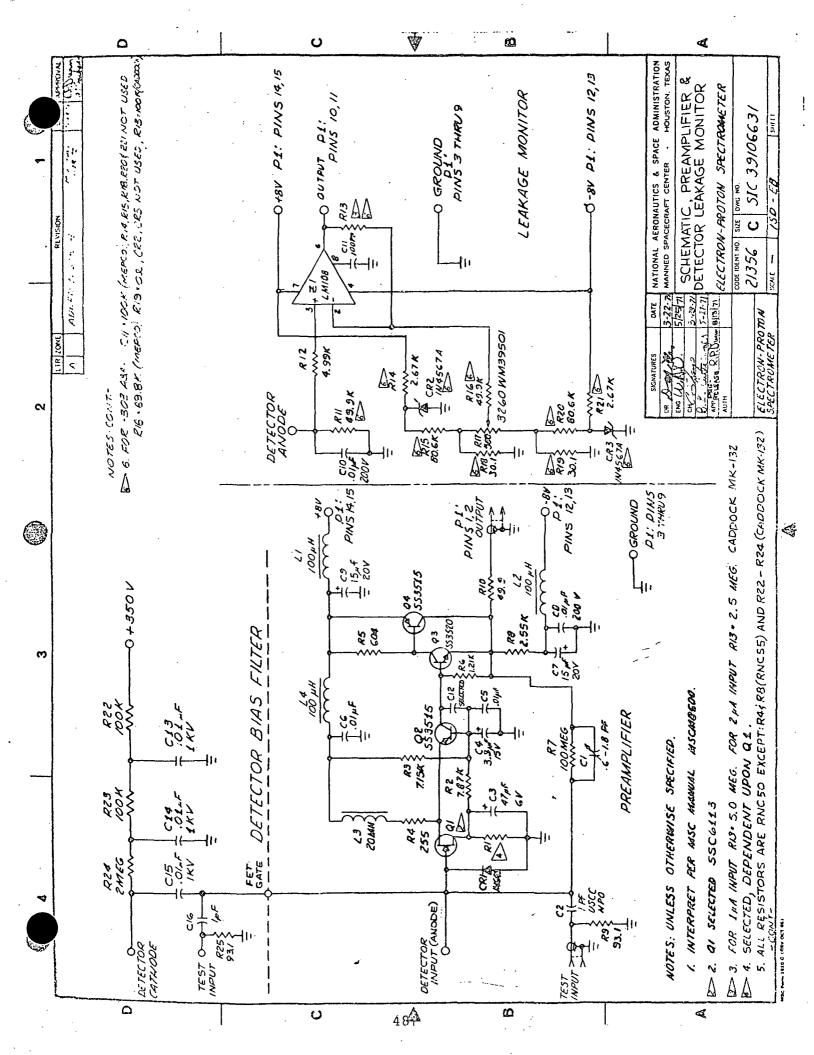

The EPS preamplifier (Schematic SIC39106631) was designed to provide amplification of signals from semiconductor detectors which were exposed to electron and proton radiation in the energy range between a few keV and several MeV.

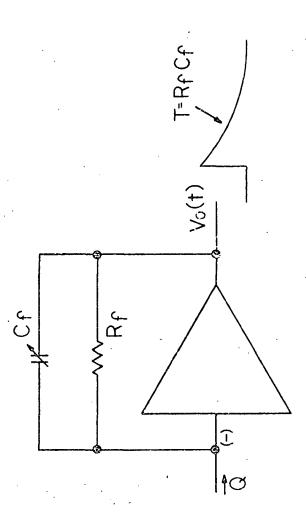

The preamplifier was implemented using a charge sensitive configuration whereby an impulse of current produced by energy deposition in the detector is transformed into a fast rising and slow decaying (practically a step function) voltage signal at the output of the preamplifier where the peak of this voltage is directly proportional to the amount of energy deposited in the detector.

The charge sensitive preamplifier (see block diagram) is basically an operational amplifier with the loop closed through the charge coupling capacitor (Cf) and provides good gain stability, linearity, and a fast rise time.

Upon absorbing some amount of energy the detector gives off an impulse of current containing a charge Q.

The time domain output voltage is given by:

$$Vo(t) = \frac{Q}{Cf} e^{-\frac{1}{RfCf}} t$$

which shows that for very short times the exponential term will approach 1 and the output voltage will be directly proportional to the input charge. The feedback capacitor serves as the constant of proportionality.

In the EPS preamplifier, Cf was made variable so as to provide a means of adjusting the charge conversion gain. To optimize the performance of the EPS preamplifier, a low noise, high transconductance FET  $(Q_1)$  is used as the input stage.

The detector and the detector bias filter are ac coupled to the FET's gate electrode.

The preamplifier was designed to operate from a dual power source, therefore, it is possible to dc couple the output to the pulse amplifier, thus improving the system's high count rate capabilities.

Overall power consumption of the preamplifier is low (144 mw) and the performance meet all the EPS specifications.

# EPS PREAMPLIFIER SPECIFICATION

- 1. Preamplifier Conversion Gain: 29.6 mV/Mev.

- 2. Output Rise Time vs Input Capacitance Less than 1.0 nsec/pf.

- 3. Output Amplitude vs Power Supply Change: Less than .002 Volt/Volt

- 4. Input Resolution vs Input Capacitance:

Less than 8.0 keV for Cin up to 30 pf.

Slope above 30 pf approximately .066 keV/pf.

- 5. Input Resolution vs Temperature:

Less than .04 keV/°C.

- 6. Output dc Offset Voltage: Between 100 mV and 300 mV.

- 7. Output Pulse Decay Time Constant:

Approximately 150 usec.

- 8. PHA Peak Channel Number vs Preamplifier Input Capacitance:

Less than .022%/pf.

- 9. Output Resistance: 49.9  $\Omega$

- 10. Power Dissipation:

- +8.1 volts at 14 mA.

-8.1 volts at 4 mA.

- $P_{TOTAL} = 144 \text{ mw}$

#### 3.2.2 PULSE AMPLIFIER

The pulse amplifier shapes the preamplifier's output and amplifies the signal to a level usable by the pulse height discriminators. Pulse shaping is necessary to minimize the system resolving time and narrow the bandwidth for good signal-to-noise ratio. The amplifier output is a bipolar pulse; this eliminates the need for a baseline restorer and reduces circuit complexity.

Other requirements are found in the "Pulse Amplifier Specifications" list. The circuit design has been optimized to meet these specifications with a minimum of power consumption.

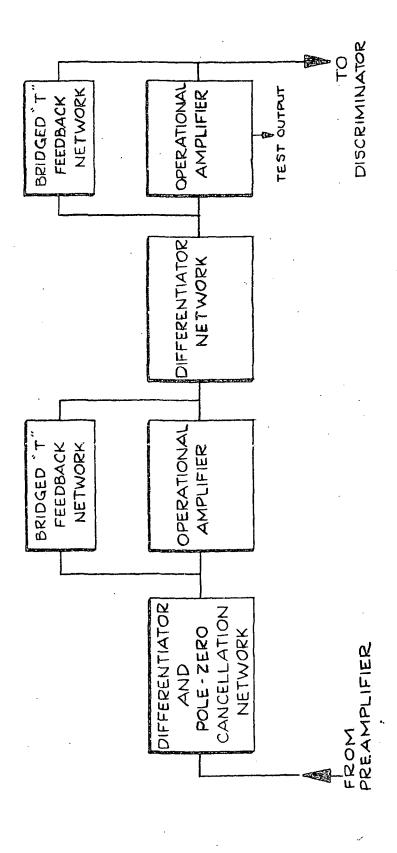

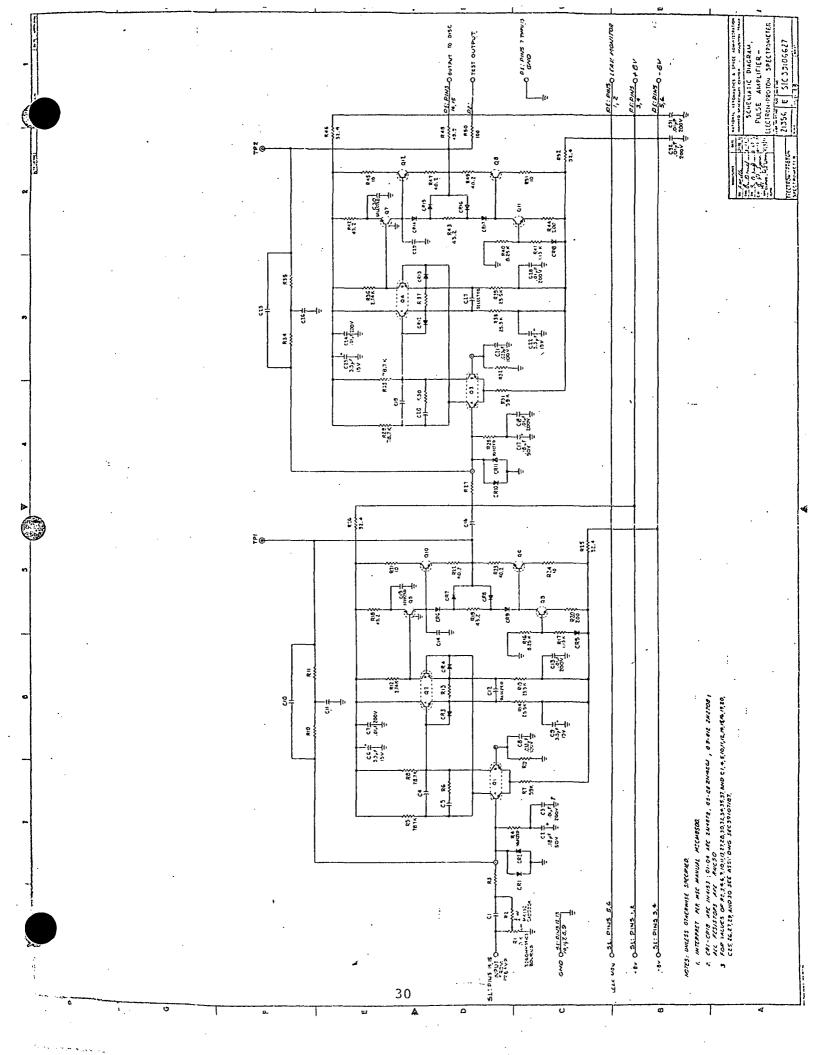

The pulse amplifier is composed of two cascaded active R-C filters (see pulse amplifier block diagram). Each filter contains a differentiator, an operational amplifier and feedback network.

The first differentiator is combined with an adjustable pole-zero concellator which is set to cancel the decay time constant of the preamplifier. This network is shown in detail on the Schematic SIC39106627 and consists of  $R_1$ ,  $R_2$ ,  $R_3$ , and  $C_1$ . The second differentiator consists of  $C_{16}$  and  $C_{17}$ .

The feedback networks consist of  $C_{10}$ ,  $C_{11}$ ,  $R_{10}$ ,  $R_{11}$ ,  $C_{25}$ ,  $C_{26}$ ,  $R_{34}$ , and  $R_{35}$ .

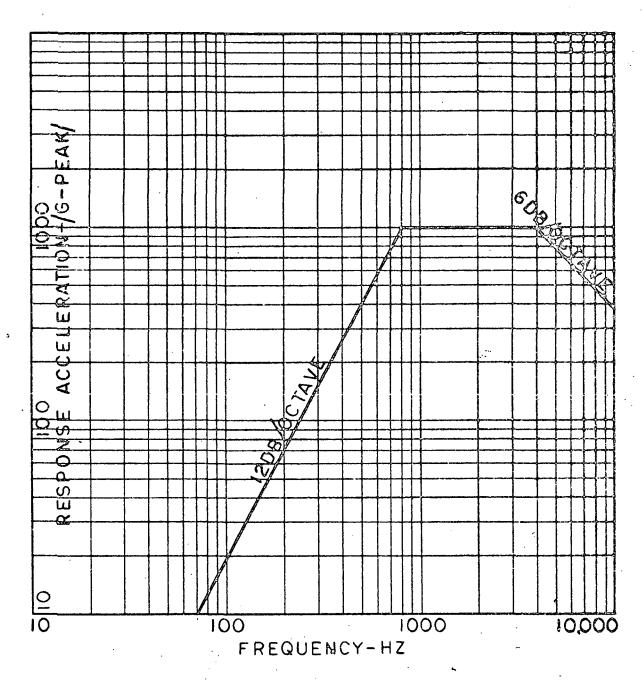

The operational amplifiers are identical except for the test output of the second one. This test output is needed for calibration. To obtain sufficient slew rate with minimum power consumption the amplifiers are compensated for an open loop frequency response with a 12 dB/octave roll off. As in the case of the differentiator and feedback components the compensation values are not given in the basic schematic but are listed on the assembly drawing. Diodes CR<sub>1</sub>, CR<sub>2</sub>, CR<sub>3</sub>, CR<sub>4</sub>, CR<sub>10</sub>, CR<sub>11</sub>, CR<sub>12</sub>, and CR<sub>13</sub> are used for protection of the transistors. Short circuit protection is obtained with CR<sub>7</sub>, CR<sub>8</sub>, CR<sub>15</sub>, and CR<sub>16</sub>.

The bipolar pulse is obtained by the use of the second differentiator. Placing this differentiator between the amplifiers instead of after the second amplifier results in a requirement for a lower power supply voltage, therefore, reducing power consumption to about one half.

PULSE AMPLIFIER BLOCK DIAGRAM

## PULSE AMPLIFIER SPECIFICATIONS

Pulse Gain: 16.0 ± 8%

Gain Stability:

Temperature Stability: Less than .02%/°C

Stability as a Function of Supply Voltage: Less than .2% for 0.1V change in both supplies.

Linearity: Less than 1.2% deviation from best straight line to ± 5V out.

Input Polarity: Positive

Output Polarity: Positive

Preamp-Post Amp Calibration: +5 V out = 10 mev

Pulse Shaping Time Constants: 360 ns

Pole-Zero Cancellation: Adjustable from 40 µs to infinity.

Overload Recovery: Recovers from X10 overload in < 2 normal pulse widths to less than lower discriminator setting.

Output Noise: Less than 1.0 mV FWHM for no input.

Average Baseline Shift with Counting Rate: < ± 5 mV

Baseline Stability Based on 10K Feedback Resistor +25°C Value: 6.6 mV max, 2 mV typ.

Temp. Stability: 72  $\mu$ V/°C max.

As a function of supply voltage: 0.13 mV typ for a change in both supplies of 0.1V.

Output Coupling: Direct.

Discriminator Output Load: 1.3 KΩ min, 10 pf max.

Power Requirements: +8V @ 10.8 mA typ, -8V @ 12.2 mA typ,

220 mw max.

Output Short Circuit Protected

Test Output Load: 4 K $\Omega$  min, 60 pf max.

Slew Rate: Greater than  $22V/\mu s$  for a time constant of 360 ns.

## OPERATIONAL AMPLIFIER SPECIFICATIONS

+25°C except as noted.

Open Loop Gain at 10 KC: 79 to 87 dB.

Open Loop Gain Stability: With temp. from +25°C to -25°C, less than 10%.

With supply voltage, less than 1% for 0.1 V charges in both supplies.

Linearity: Less than 12% from -5V to +5V out.

Output: ± 5V Maximum.

Input Offset Voltage (Max): 6.0 mv (2 mv typ.) +60  $\mu$ V/°C

Input Offset Current (Max): 60 nA + 1.2 nA/°C

Minimum Load Resistance (including feedback network):  $660\Omega$  Power Requirements:

± 8V, 100 mw max (90 mw typ).

+8V @ 5.4 ma typ.

-8V @ 6.1 ma typ.

Input Offset Voltage Change with Supply Voltage:

0.13 mv (typ) for any combination of 0.1V change in supply voltages.

Short Circuit Protected.

For use in the inverting configuration.

#### 3.2.3 DUAL DIFFERENTIAL PULSE HEIGHT DISCRIMINATOR

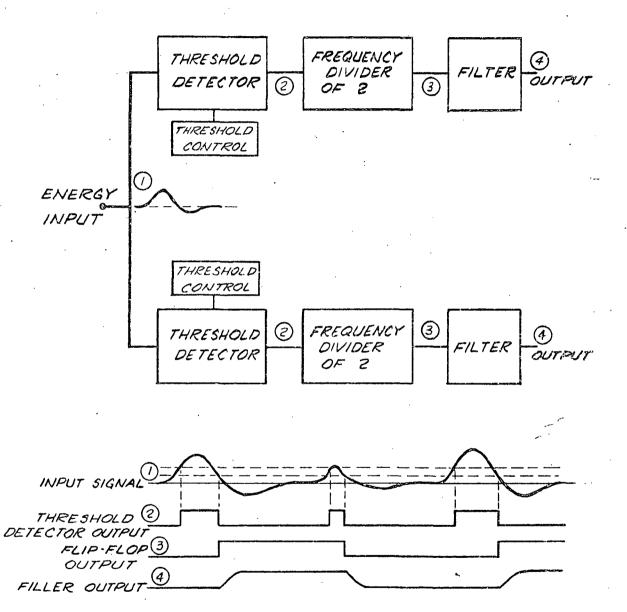

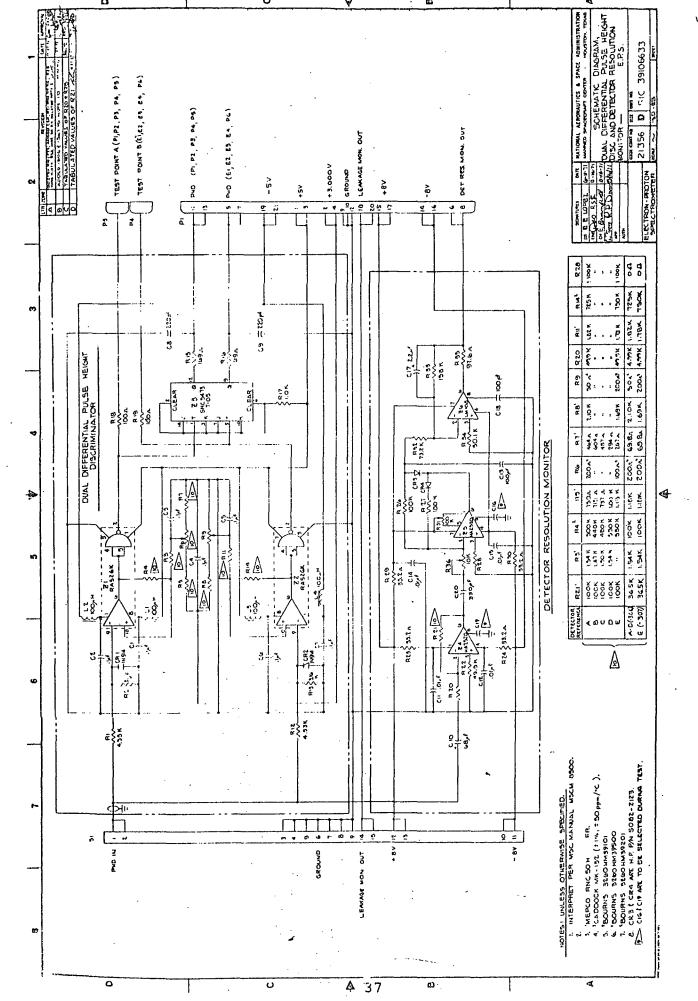

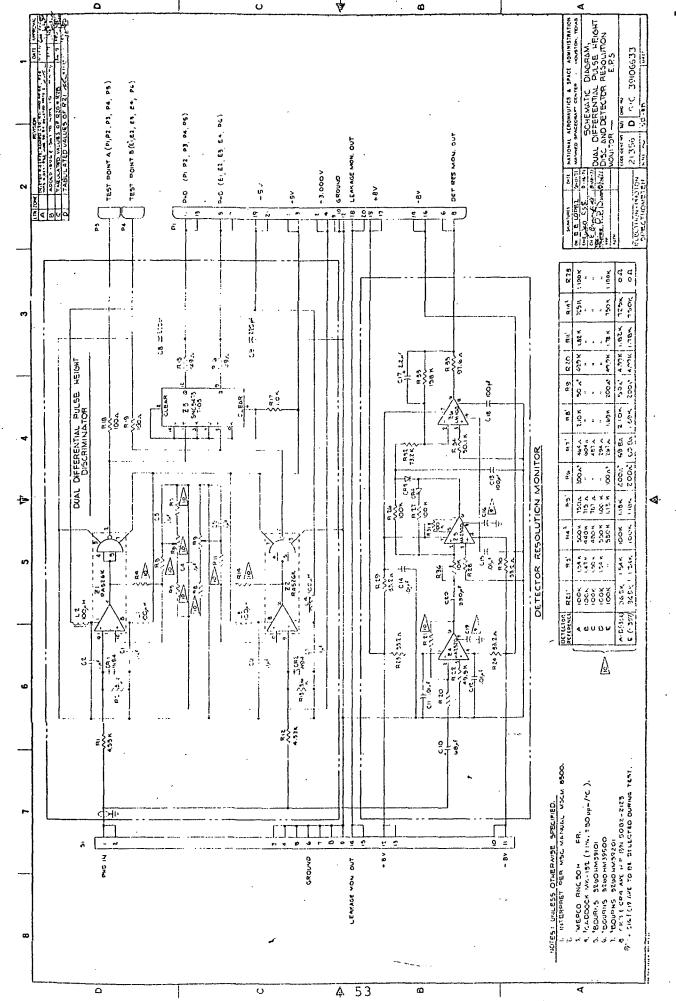

The dual pulse height discriminator consists of two functionally identical circuits whose purpose is to determine whether an energy deposition in the corresponding EPS detector exceeds two independently predetermined values. Electronically the two predetermined energy deposition values allow the detection of electron and proton events above a known energy level. A functional block diagram is included.

Due to counting-rate requirements, the portion of the input signal that is observed for analysis by the circuit is restricted to 1080 nsec for all channels. The time spent above the circuits threshold becomes vanishingly small for signals close to the threshold value, however. This requires the use of an exceptionally fast discriminator and resulting output signals may be as short as 20 nsec. Since these signals must eventually be recorded by the EPS Data Processor which is interconnected to the discriminator output by several inches of unshielded wire, a flip-flop is included to increase the pulse width to one capable of being handled by the lower frequency low-power counters. An output filter increases the rise time of signals transmitted to the data processor to approximately 30 nsec. this way the possibility of internally generated EMI is minimized.

DUAL DIFFERENTIAL PULSE HEIGHT DISCRIMINATOR BLOCK DIAGRAM

The Dual Pulse Height Discriminator Performance Specification, included, presents the design criteria for this circuit. All design criteria have been met.

Drawing SIC 39106633 is the schematic diagram of the Dual Pulse Height Discriminator. Resistors Rl and R2/R12 and R13 serve as an input signal attenuator to reduce the value of the largest possible positive input signal to the. derated maximum value of integrated circuit 21/22. CRI/CR2 serves to clamp the negative portion of any input signal to a value less than the derated maximum value of integrated circuit Z1/Z2. Integrated Circuit Z1/Z2 functions as a high speed differential amplifier. The input signal is directed to the amplifier's negative input terminal. ever the negative input terminal becomes more positive than the positive terminal, the amplifier's output switches from +4 volts to 0 volts. In this way the amplifier functions as a differential comparitor. The reference value (trip point) is determined by Resistors R5, R6, and R7/R8, R9, and R10 and the reference input voltage. By adjusting the values of these resistors, the threshold may be preset to any value: from 50 keV equivalent energy to 10 MeV equivalent energy. Resistors R3 and R4/R11 and R14 provide the amplifier with positive feedback to ensure very crisp (non oscillating) response by making the amplifier reset point 50 keV equivalent energy less than the trip point. Integrated circuit Z1/Z2 includes a TTL compatible two input Nand Gate. gate logically inverts the output signal to one of 0 volts to +4 volts. The gate's output is connected to the clock input of one of the flip-flops in Z3. This flip-flop

changes state each time the comparitor transitions from 0 volts to +4 volts. The signals are transferred to much longer ones for processing by the EPS data processor. Resistor R15, R16 and Capacitor C8/C9 increase the rise time of the flip-flop output to approximately 30 nsec to remove the possibility of cross coupling in the wires connecting the data processor. Resistors R18/R19 serve as cable terminations for test points P3/P4. Inductors L1 and L2/L3 and L4 and Capacitors C1 and C2/C6 and C7 function as supply line filters to the differential amplifier Z1/Z2.

## DUAL PULSE HEIGHT DISCRIMINATOR PERFORMANCE SPECIFICATION

## 1.0 Input Characteristics

A. Impedance: 3.85  $k\Omega$

B. Coupling: Direct

C. Signal Range

1) Normal: 0 to +5 volts bipolar positive edge leading

2) Overload: +8.0 volts to -10.0 volts continuous

D. Threshold Range:

1) Electron 1 200 keV to 300 keV

2) Electron 2 200 keV to 300 keV

3) Electron 3 200 keV to 300 keV

4) Electron 4 200 keV to 300 keV

5) Proton 1 2.500 MeV to 3.500 MeV

6) Proton 2 2.500 MeV to 3.500 MeV

7) Proton 3 2.500 MeV to 3.500 MeV

8) Proton 4 2.500 MeV to 3.500 MeV

9) Proton 5 2.500 MeV to 3.500 MeV

10) Proton 6 0.600 MeV to 1.000 MeV

E. Pulse Pair Time Resolution: ≤ 100 nsec

F. Input Rate (Fixed Frequency): ≥ 5 MHz

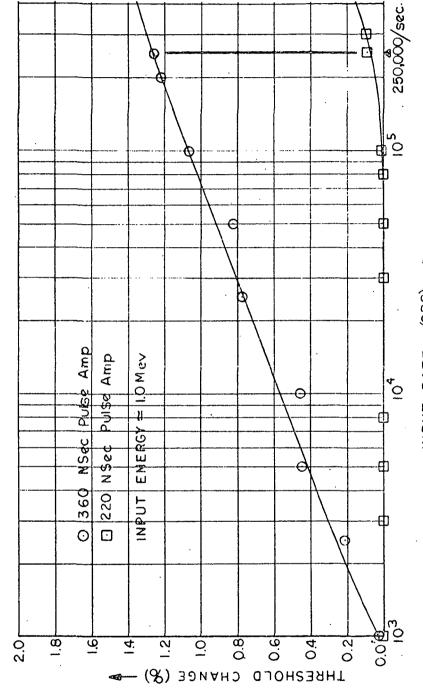

## 2.0 Discriminator Level Stability

## A. Temperature

1) 200 keV +3.0%

-25°C to +50°C ≤-1.5%

2) 7.000 MeV +0.2%

$-25^{\circ}$ C to  $+50^{\circ}$ C  $\leq -0.4%$

## B. Power Supply Variation

1) 200 keV

A) +5.0 volt supply (+4.8 VDC to +5.3 VDC)  $\leq -3.5\%$

B) -5.0 volt supply (-4.8 VDC to -5.3 VDC)  $\leq \frac{+0.58}{-1.28}$

C) +5.0 volt, -5.0 volt supply aggregate (4.8 VDC to 5.3 VDC

- D) +3.000 volt supply error equal to fractional error in supply value

- 2) 7.000 MeV

- A) +5.0 volt supply (+4.8 VDC to +5.3 VDC)  $\leq_{-0.5\%}^{+0.5\%}$

- B) -5.0 volt supply (-4.8 VDC to -5.3 VDC)  $\leq_{-0.5\%}^{+0.1\%}$

- C) +5.0 volt, -5.0 volt supply aggregate (4.8 VDC to 5.3 VD  $\leq_{-0.6\%}^{+1.1\%}$

- D) +3.000 volt supply error equal to fractional error in supply value

- 3.0 Discriminator Crispness:

⋅ ≤ 10 keV

4.0 Discriminator Hysteresis:

50 keV

5.0 Prescale Factor:

2

- 6.0 Output Characteristics

- A. Signal Output

- 1) DC levels:

TTL

2) Fanout:

≥ 3

- 3) Rise Time Constant Fall Time Constant: 10 nsec

- B. Test Output

- 1) DC Levels:

TTL

2) Output Impedance:

$100\Omega$

## 7.0 Power Requirement

| -25°C          | <u>0°C</u> | +25°C | +50°C |

|----------------|------------|-------|-------|

| +5.0 VDC 43mA  | 4 4mA      | 44mA  | 4 2mA |

| -5.0 VDC 18mA  | 18mA       | 21mA  | 20mA  |

| +3.000 VDC 4mA | 4mA        | 4mA   | 4mA   |

## 3.3 HOUSEKEEPING SYSTEM

A definite requirement exists to measure three detector parameters in order to determine the quality of each detector. These parameter measurements are required periodically: during shelf storage of the EPS flight instruments, during the time each flight instrument is mounted on the spacecraft, and during flight. Having the capability for making these periodic measurements is of paramount importance to the overall accuracy of the EPS flight data.

Analysis of the data collected as a result of these measurements maximizes the probability of a successful mission, by providing the capability to detect and replace any degraded detector prior to flight, and by applying correction factors to the data, if required, during flight.

Because of the different non-related but dependent failure modes of the detector(s), three parameter measurements are required. None of these measurements can be eliminated due to their interdependence, as the remaining measurements will not give a positive indication of the parameter measurement or failure mode eliminated.

The required parameter measurements are: 1) detector temperature, 2) detector leakage current, and 3) detector resolution. These are discussed in detail below.

## Detector Temperature Measurement

Measurement of the temperature of the detectors is required during flight as leakage current noise and lithium drift rates are dependent upon the temperature of the detectors. The leakage current increases 100 percent for approximately every 8°C increase in detector temperature, and the noise varies with leakage current, resulting in a deterioration of detector resolution, and thereby performance.

The lithium drift rate increases with an increase in temperature in addition to being linearly proportional to detector bias. Hence a knowledge of the temperature is required in order to

- 1) Partially or totally unbias the detector if the temperature rises too high and

- 2) Allow analytic corrections to the data to be made, if necessary, because of the increase of detector active volume caused by the continued lithium drift.

## Detector Resolution Noise Monitor

Although the resolution of the detectors varies directly as a function of temperature, one failure mode of the detector results in a degradation of resolution which is independent of temperature. Therefore, a detector resolution (noise) monitor is required for each of the five detectors.

The detector noise monitors have been built into each of the EPS instruments. This approach eliminates any requirement to disconnect the instrument from the spacecraft to exercise and monitor the status of the detector resolution prior to launch. Instead, this measurement may be made by having spacecraft power applied to the EPS and interpreting the data fed out by the spacecraft telemetry system. Correction factors can also be applied to the flight data if required, by monitoring the detector resolution during flight.

## Detector Leakage Current

The leakage current measurement provides a partial indication of the quality of the detector. Although leakage current varies directly with temperature, one particular failure mode of the detectors is that the leakage current can increase to prohibitive levels independent of the detector temperature. Therefore, a leakage current monitor is provided in the EPS for each detector.

## Electronic Status Monitors

All voltages, electronics package temperature, and heater ON-OFF status are also monitored as part of the house-keeping data, and are necessary parameters for overall evaluation of the instrument prior to launch. All have redundant channels on the multiplexer. The voltage monitor data is especially helpful in evaluating malfunctions or questions relating to data validity in case unusual data occurs. Package temperature data is required in

evaluating thermal design and in determining the environment experienced by the electronic circuitry, especially if the instrument power has been off for long periods in a cold, or hot environment. The heater monitor provides status of the heaters, whether in the "On" or "Off" condition. All housekeeping monitor voltages are conditioned to have a maximum value of 5 volts.

TABLE I. EPS DATA PROCESSOR HOUSEKEEPING SEQUENCE PARAMETER RANGE, ACCURACY, AND RESOLUTION CHART

|                              |    |     | RESOLUTION | 0.110°C       | 1.0 keV   | 0.02 µA      | 0.110°C    | 1.0 keV  | 0.02 µA      | 10 mv              | 1.0 keV      | 0.02 µA     | 10 mv           | 10 mv          | 54 mv          | 500 mv         | 20 mv          | 10 mv          | 6 mv         | 0.110°C       | 1.0 keV  | 0.02 µA      | 0.110°C      | 1.0 keV  | 0.02 µA                 | 10 mv     | ;        | !      | 10 mv             | 10 mv              | 54 mv              | 500 mv             | 20 mv              | 10 mv              | 6 mv           |

|------------------------------|----|-----|------------|---------------|-----------|--------------|------------|----------|--------------|--------------------|--------------|-------------|-----------------|----------------|----------------|----------------|----------------|----------------|--------------|---------------|----------|--------------|--------------|----------|-------------------------|-----------|----------|--------|-------------------|--------------------|--------------------|--------------------|--------------------|--------------------|----------------|

|                              |    |     | ACY        | ೦.0           | keV       | 5 µA         | 2°C        | keV      | 5 µA         | ωv                 | keV          | μА          | <b>&gt;</b>     | υv             | υv             | mv             | mv             |                | >            | ບູ            | keV      | μA           | 2°C          | keV      | 05 µA                   | mv        | <i>*</i> | !      | mv                | 0 mv               | 7 mv               | 50 mv              | 0                  | o my               | mv             |

|                              |    |     | A          | C to +50°C ±1 | 100 keV ± | A to 20 µA ± | to +50°C + | 100 keV  | A to 20 µA ± | ts to +10 volts ±5 | 100 keV . ±1 | to 20 µA ±. | to +10 volts ±5 | to -10 volts # | to +55 volts # | to 505 volts ± | to -20 volts ± | to -10 volts ± | o 6.002 V ±3 | C to +50°C ±1 | 100 keV  | A to 20 µA ± | 3 to +50°C ± | 100 keV  | A to $20 \mu A$ $\pm$ . | ts to +10 | 44       | ·<br>· | is to +10 volts ± | ts to -10 volts ±5 | ts to +55 volts ±2 | ts to 505 volts ±2 | ts to -20 volts ±1 | ts to -10 volts ±5 | to 6.0020 V ±3 |

|                              |    |     | RAN        | era           | oise 0    | eakage 0     | ate Temp   | oise 0   | akage        | nitor 0            | Noise 0      | ye 0,       | itor 0          | itor 0         | 0              | 0              | 0              |                | ۰۲ 0 ت       | re -50        | 0        | ye 0.        | •05- dua     | 0        | Leakage 0.              | itor      | tor      | tor    | itor 0            | itor 0             | nitor 0            | nitor              | nitor 0            | onitor 0 vol       | tef. Mon. 0 V  |

| E-<br>ING                    | ID | Ħ   | MEASUREM   | Package T     | Detector  | Detector     | Detector   | Detector | Detector     | +5 Volt M          | Detecto      | Detector    | +8 Volt 1       | -8 Volt 1      | +25 Volt       | 350 Volt       | -15 Volt       | -5 Volt I      | Discrim.     | Package .     | Detector | Detector     | , Detector   | Detector | Detector                | +5 Volt   | Heate    | Heater | +8 Volt           | -8 Volt M          | +25 Volt           | 350 Volt           | -15 Volt           | -5 Volt M          | D              |

| PRIME HOUSE-<br>FRAME KEEPIN |    | BIT |            |               |           |              |            |          |              |                    |              | 9A          | 0A              | lA             | 2A             | 3A             | 4A             |                | .6A          |               |          |              |              |          |                         |           |          |        | 0B                | 1B                 | 2B                 | 3B                 | 14B 0              | 5B                 | 6В             |

## 3.3.1 DETECTOR LEAKAGE MONITOR

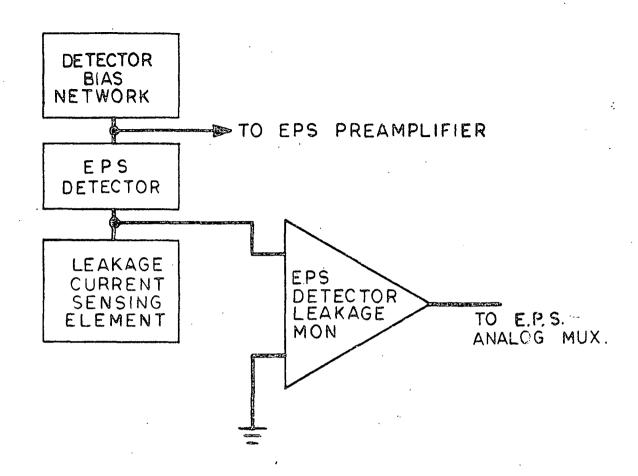

The EPS Detector Leakage Monitor provides a means of continually measuring the leakage current through the silicon energy sensing detector by amplifying the voltage drop across a resistor placed in series with the detector, as illustrated in the accompanying block diagram.

The Detector Leakage Current Monitor consists of a single gain stage utilizing a highly stable operational amplifier. This amplifier, LM 108/883, was specifically chosen because of its extremely low bias current (< lnA) and offset characteristics (< .5mV).

The monitor is capable of responding to a current variation equal to 1/1000 of the maximum predicted current through the detector and still outputting a voltage equivalent to the least significant bit of the EPS A-D Converter (5 mV).

Both inputs of the amplifier are protected by using two series resistors,  $R_{12}$  and  $R_{16}$  as shown on Schematic SIC39106631.

The amplifier's output has built-in protection; a short circuit of its output to ground for any length of time will cause no damage to the IC.

DETECTOR LEAKAGE MONITOR BLOCK DIAGRAM

Power supply voltage changes have little effect on the monitor's output. A power supply change of  $\pm$  1 V results in a change of  $\pm$  1 mV at the output.

# DETECTOR LEAKAGE MONITOR SPECIFICATION

- Maximum Input Current Range:

20 µA Full Scale

- 2. Maximum Output Voltage into Multiplexer:

5.0 volts

- 3. Amplifier Non-Inverting DC Voltage Gain

2.43 Volt/Volt

- 4. Amplifier Output Drift with Temperature:

Less than .5 mV/°C

- 5. Equivalent Input Current Drift with Temperature:

Less than .1 nA/°C

- 6. Transfer Characteristics:  $\Delta V_{\rm out}/\Delta I_{\rm in}$ 250 mV/ $\mu A$

- 7. Output Signal Power Supply Rejection:  $\Delta V_{\text{out}} \text{ less than 1 mv for } \Delta V_{\text{supply}} = \pm 1.0 \text{ volt}$

- 8. Load Driving Capacility: 1.3 mA maximum into  $10 \text{K}\Omega$  load.

- 9. Power Requirements:

- +8.1 volts at 1.0 mA maximum

- -8.1 volts at 1.0 mA maximum

## 3.3.2 DETECTOR RESOLUTION MONITOR

The EPS Detector Resolution Monitor provides a means of continually measuring the noise derived from the EPS detectors. Thus allowing one to evaluate any degradation of the detectors which might occur during storage or during flight.

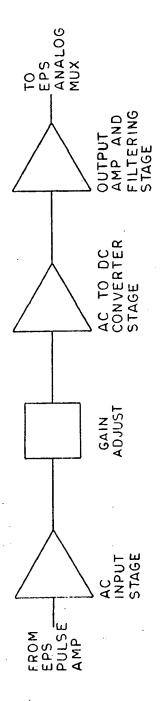

The resolution monitor senses this noise at the output of the EPS pulse amplifier and transforms it into a proportional DC voltage which is fed into the EPS multiplexer as shown in the accompanying block diagram.

The EPS Detector Resolution Monitor averages the input noise and is implemented with three high performance operational amplifiers. It is capable of responding to high frequency noise signals, having a 3 dB bandwidth of 300 KHz.

Two hot carrier diodes, CR<sub>3</sub> and CR<sub>4</sub>, shown on Schematic SIC39106633, are used as the rectifying Detector Resolution Monitor elements in the monitor's second stage because of their inherent low threshold voltages.

The transfer function will be represented by a fourth order equation relating preamplifier input resolution in keV and resolution monitor output voltage in volts dc.

The coefficients of this equation shall be determined during testing and calibration of the resolution monitor cards.

DETECTOR RESOLUTION MONITOR BLOCK DIAGRAM

The output stage can be short circuited to ground indefinitely and the overall circuit may be overloaded to any extent, without any damage being incurred by the components.

Power supply voltage changes have little effect on the monitor's output response; A  $\pm$  1 volt power supply change results in less than 10 mV output voltage change.

# DETECTOR RESOLUTION MONITOR SPECIFICATION

1. Overall Noise Gain:

The response curve slope can be adjusted to produce 25 mV dc at the output of the resolution monitor per keV of detector noise at the input of the preamplifier.

Maximum nominal output corresponds to 200 keV of preamplifier input resolution.

- 2. Minimum Input Sensitivity: Approximately 5.5 keV.

- 3. Input Resolution Transfer Equation:

The transfer function will be represented by a fourth order equation relating preamplifier input resolution in keV and resolution monitor output voltage in volts dc.

The coefficients of this equation shall be determined during testing and calibration of the resolution monitor cards.

- 4. Resolution Monitor Signal Bandwidth (-3 db): 300 KHz

- 5. Resolution Monitor Input Impedance: 5 K $\Omega$  in series with 68  $\mu F$ .

- 6. Power Requirements: ±8.1 volts at 10 mA.

## 3.3.3 TEMPERATURE MONITORS (DETECTOR AND PACKAGE)

The EPS Temperature Monitors provide a means of accurately measuring the temperature surrounding the detectors and electronic hardware in the range between -50°C to +50°C.

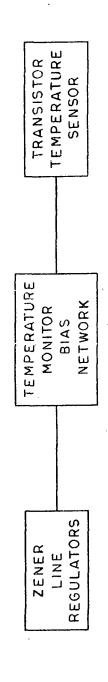

The temperature sensors are the PNP transistors which are biased in their linear region by the resistive bias network as shown on the Block Diagram.

The transistor DC collector voltage is a linear function of the emitter-to-base junction voltage and its variation with temperature.

The temperature monitor response curve is a straight line given by:

$$V_{O} = 2,500 + 50 \times T \quad (mV)$$

Where T is in °C.

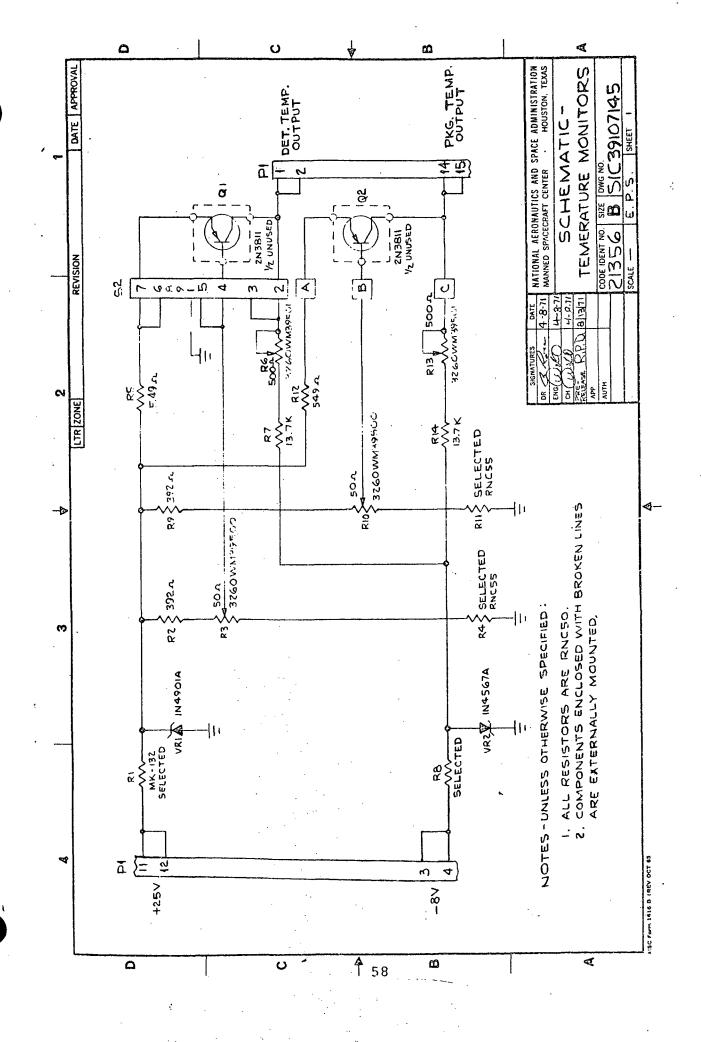

The response curve slope and intersept can be trimmed by adjusting  $R_3$  ( $R_{10}$ ) and  $R_6$  ( $R_{13}$ ) Potentiometers shown on Schematic SIC39107145.

In order to increase the circuit's ability to reject power supply variations, two zener diodes,  $\text{VR}_1$  and  $\text{VR}_2$ , which are temperature compensated, are used to regulate the positive and negative supply voltages.

TEMPERATURE MONITOR BLOCK DIAGRAM

# PACKAGE AND DETECTOR TEMPERATURE MONITORS SPECIFICATION

- 1. Temperature Range: -50°C to +50°C

- 2. Output Voltage Range: 0.0 to +5.0 Volts

- 3. Output Voltage Temperature Sensitivity: 50 mV/°C.

- 4. Worst Case Accuracy: ±1.5°C.

- 5. Resolution: (.1°C)

- 6. Power Requirements:+25 volts at 8.5 mA-8.1 volts at 2.5 mATotal power dissipation: 234 mw

#### 3.3.4 VOLTAGE MONITORS

As an aid in troubleshooting the instrument in the event of a failure and to determine the operational status during flight, the internal voltages utilized by the EPS are monitored and read out thru the telemetry link.

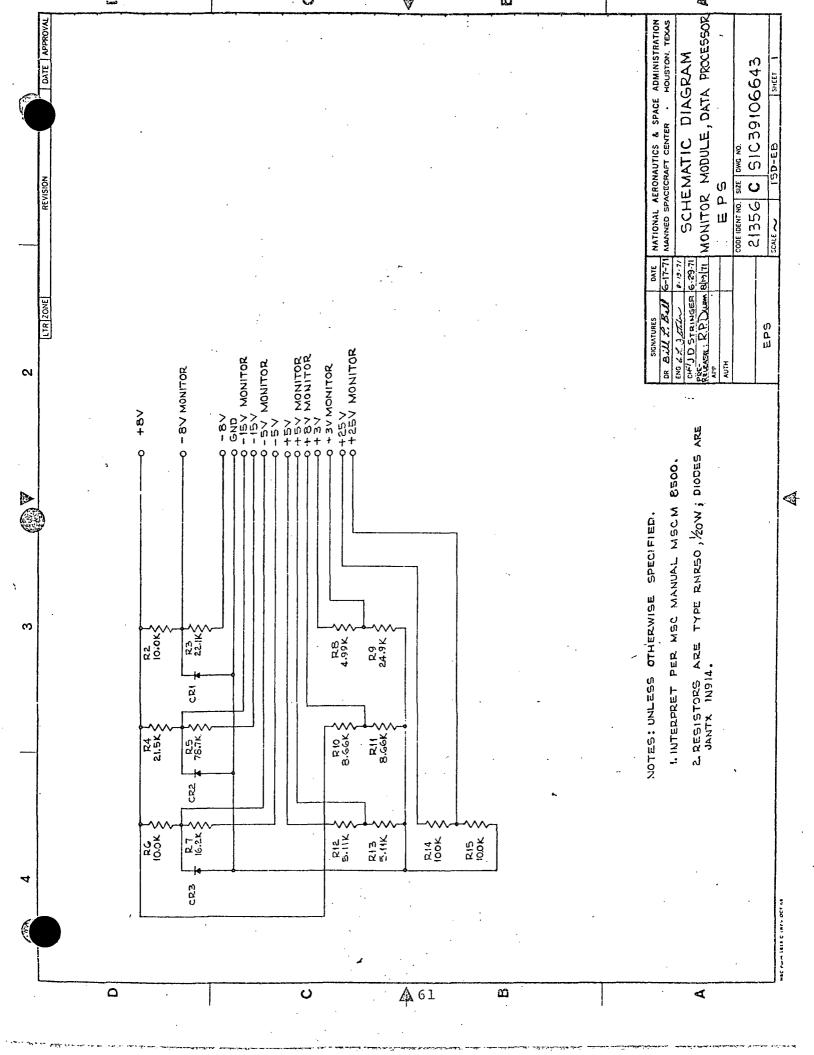

There are seven separate low voltages within the EPS instrument, four positive and three negative. As shown in the monitor module Schematic Diagram SIC39106643 the monitor outputs for the positive voltages are generated by resistive divider networks referenced to signal ground.

To generate the monitor signals for three negative voltages, the resistive dividers cannot be referenced to signal ground since the EPS multiplexer cannot multiplex a negative voltage. For this reason, these networks are tied to the +8 voltage supply, and the resistor values were selected to give positive voltages proportional to the negative voltages. The diodes attached to the negative voltage monitor outputs ensure that large negative voltages will not be applied to the input of the multiplexers.

The relationships for the various voltage monitors are:

- +8 volt monitor:  $Vmon (+8) = 0.5 V_{R}$

- +5 volt monitor:  $Vmon (+5) = 0.5 V_5$

- +3 volt monitor: Vmon (+3) =  $0.833 \text{ V}_3$

- +25 volt monitor:  $Vmon (+25) = 0.091 V_{25}$

- -8 volt monitor:  $Vmon (-8) = 0.688 V_8 0.312 V_{-8}$

- -5 volt monitor:  $Vmon (-5) = 0.618 V_8 0.382 V_{-5}$

- -15 volt monitor: Vmon (-15) =  $0.785 \text{ V}_8 0.215 \text{ V}_{-15}$

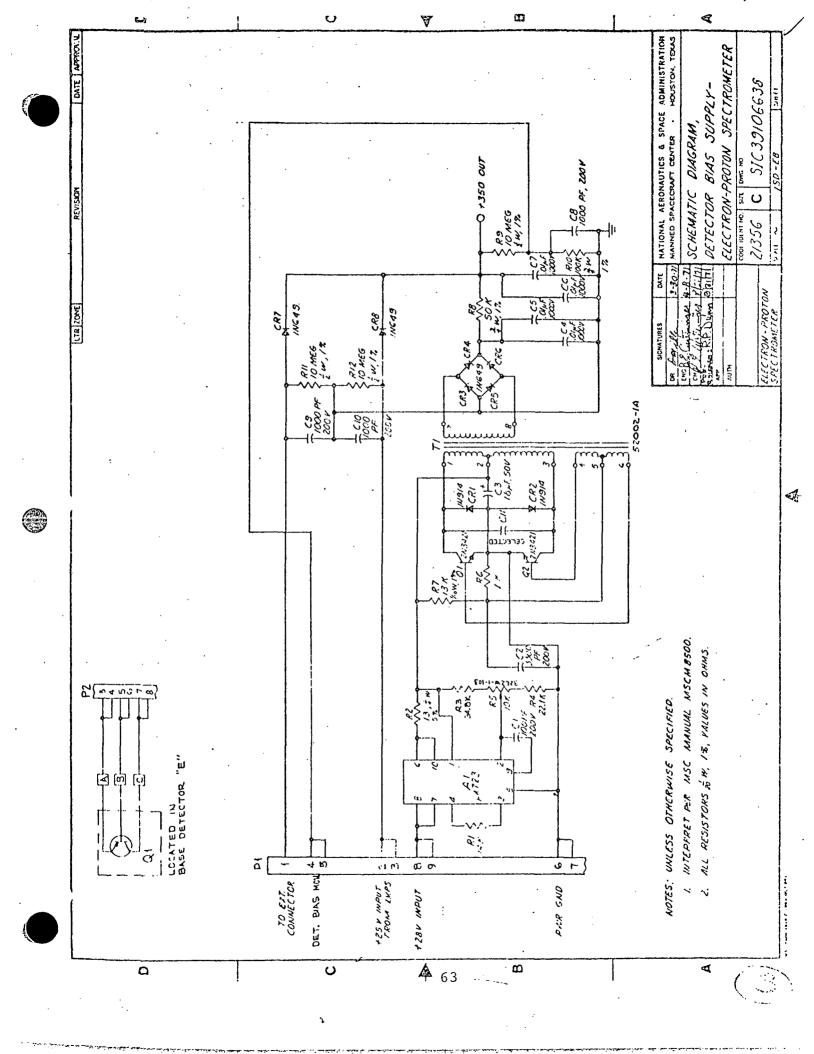

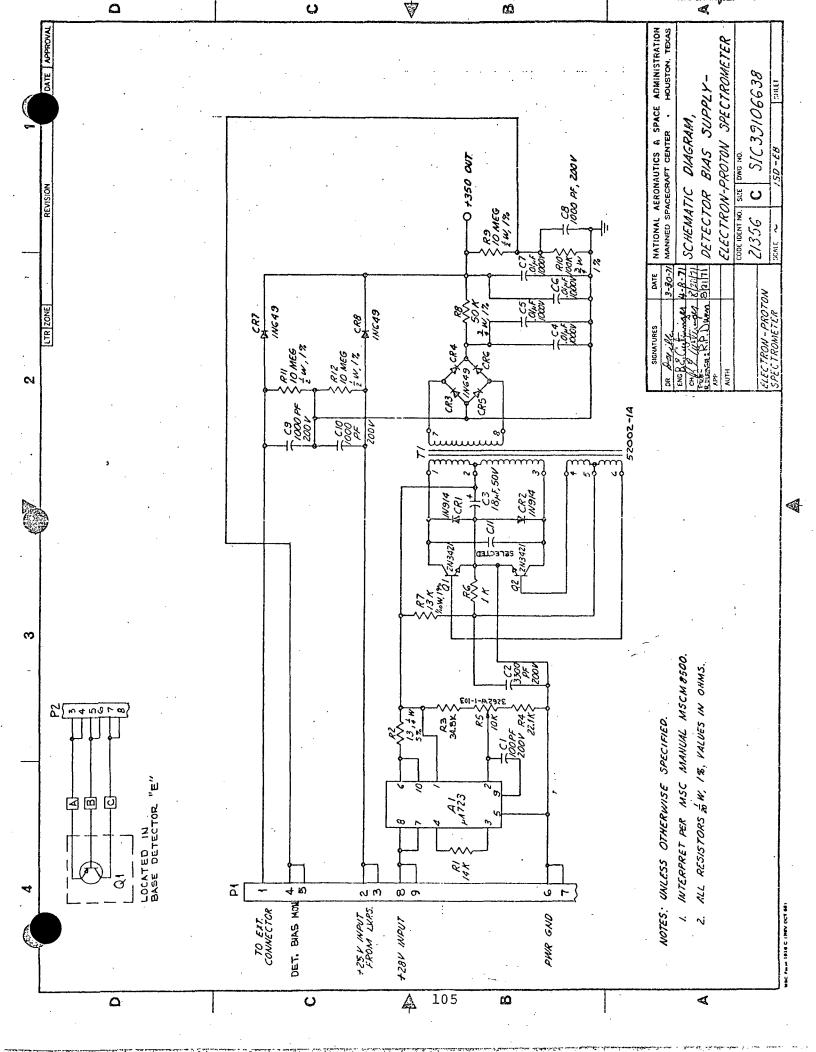

# 3.3.5 DETECTOR BIAS MONITOR SCHEMATIC SIC39106638

The status of the detector bias power supply is determined by the +350 volt monitor which is part of the housekeeping data. The voltage monitor resolution is 500 millivolts. Resistors R9 and R10 shown on drawing SIC39106638 set the voltage monitor output to 3.5 volts.

# 3.3.6 HEATER CONTROL MONITOR

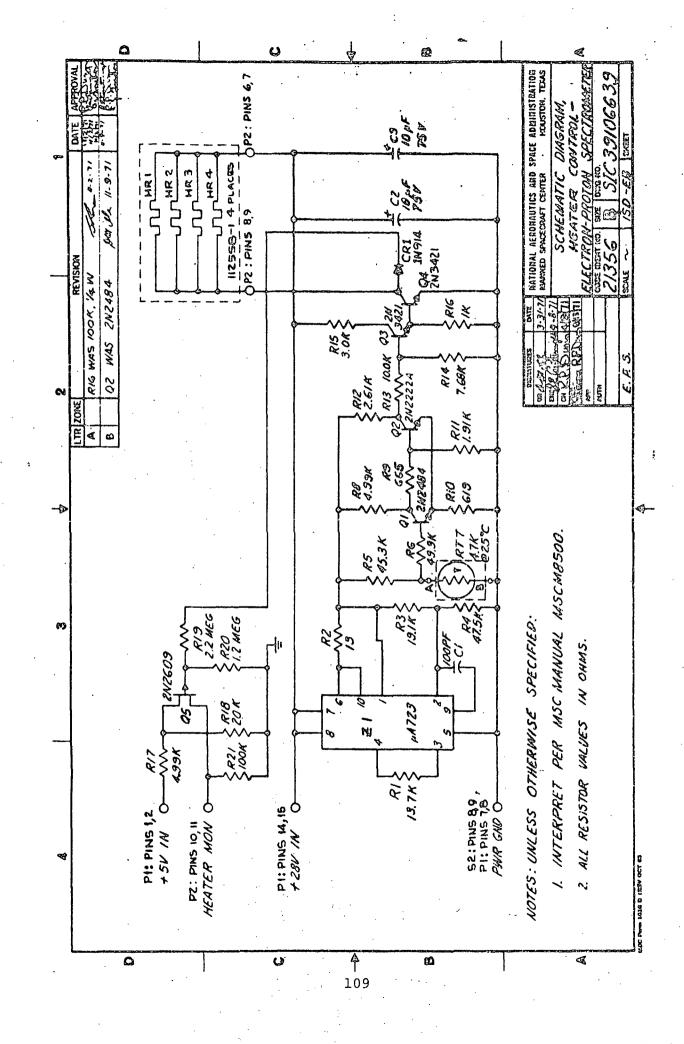

A buffered output from the schmitt trigger in the heater control circuit is fed to the data processor to provide the on or off status of heaters Schematic SIC39106639.

# 3.4 DATA PROCESSOR SYSTEM

The data processor is required to digitize all data and present it in the correct format and time to the telemetry system. The data must be identified so that after shutdown periods, specific data channels may be quickly recognized.

The data processor section is composed of seventeen modules mounted on a common motherboard. A pictorial view is shown in Fig. 1. The module breakdown is as follows:

| Counter-Register                                 | 10 ea. |

|--------------------------------------------------|--------|

| Sequence Control, Line Receiver, Counter Control | 1 ea.  |

| Data Compressor and Internal Clock               | l ea.  |

| Output Buffer and Word Sync Generator            | l ea.  |

| Analog - Digital Converter                       | l ea.  |

| A/D Control                                      | l ea.  |

| Multiplexer                                      | l ea.  |

| Monitor Module                                   | l ea.  |

The data processor block diagram is shown in Figure 2. Major interconnect lines are shown and identified to show the functional relationship between modules.

The data processor power requirement is as follows:

| Voltage    | Curre | ent   | Power | r  |

|------------|-------|-------|-------|----|

| +5         | 620 m | na    | 3100  | mW |

| <b>-</b> 5 | 2.5 n | na    | 12.5  | mW |

| +8         | 7.5 m | na    | 60    | mW |

| -8         | 42 n  | na    | 336   | mW |

| -15        | 1.8 m | na    | 27    | mW |

|            |       | Total | 3535  | mW |

Figure 1 DATA PROCESSOR MOTHER BOARD

Figure 2 DATA PROCESSOR BLOCK DIAGRAM

There are ten channels of detector information, plus twenty-one sources of housekeeping information. This data is processed and formated to be read out on 13 data lines which are sampled 1 time per second. The EPS Word Format and Main Frame Format are shown in Figure 3 and 4 respectively. All timing sequences are referred to a single clock pulse of one Hertz, which is fed to the instrument from the CSM. This one Hertz timing signal is referred to in the interface control document Number MH04-02119-234 as the CTE timing signal.

The major events and related timing is shown in the timing diagram, Figure 5.

The data processor operates properly from -50°C to +70°C. All digital circuits operate properly over this temperature while V<sub>CC</sub> is varied from 4.6 volts to 5.3 volts. The digital circuits are Texas Instrument low power T<sup>2</sup>L logic, except for four standard power packages where more drive capability is required. There are also four low power one-shot packages from Advanced Micro, and one comparator from National.

# EPS WORD FORMAT

|            | - |  |

|------------|---|--|

| 13         | 1 |  |

| 12         | 0 |  |

| 11         | Ι |  |

| 10         | 0 |  |

| <b>o</b>   | 0 |  |

| <b>∞</b> : | - |  |

| _          | 0 |  |

| 9          | 0 |  |

| Ŋ          | 0 |  |

| 4          | Н |  |

| 2          | Н |  |

| 2          |   |  |

| rl         | 0 |  |

DIGITAL DATA

| A   |  |

|-----|--|

| LSB |  |

|     |  |

| C   |  |

|     |  |

|     |  |

| MSB |  |

| LSB |  |

|     |  |

|     |  |

| B   |  |

|     |  |

|     |  |

| MSB |  |

| A   |  |

| 69  |  |

A - WORD SYNC (BINARY 0 FOR ALL WORDS EXCEPT ELECTRON 1)

B - DATA

C - PLACE

| -                                       |               |

|-----------------------------------------|---------------|

|                                         |               |

| -                                       |               |

| <del></del>                             | <u></u>       |

|                                         |               |

|                                         |               |

| *************************************** |               |

|                                         | <del></del> . |

HOUSEKEEPING DATA

| Eg A     | 1 |

|----------|---|

| LSB      | - |

|          | - |

|          |   |

|          |   |

|          |   |

|          |   |

|          | 1 |

|          |   |

|          | - |

|          |   |

| 1 1      |   |

| B        |   |

|          |   |

|          |   |

| 22       |   |

|          |   |

|          |   |

|          |   |

|          |   |

|          |   |

| <b> </b> | - |

| 4SB      |   |

|          | - |

| 8        |   |

|          |   |

| SB       |   |

| 区        |   |

| l ∀      | 1 |

|          | J |

| 0        |   |

A - HOUSEKEEPING SYNC B - DATA

EPS WORD FORMAT Figure 3

| 1       |

|---------|

| Ш       |

| AM      |

|         |

|         |

| X       |

| L       |

| _       |

| Z       |

|         |

| 4       |

| 5       |

| <i></i> |

| S       |

| _       |

| 0       |

| ĪIJ     |

| U       |

|          |                        |                                              |     |     |    |    |    |    |     |     |      |      |      |     |          | <u> </u>               |                                        |

|----------|------------------------|----------------------------------------------|-----|-----|----|----|----|----|-----|-----|------|------|------|-----|----------|------------------------|----------------------------------------|

| ত        | HOUSE<br>KPG<br>1B     | 28                                           | 38  | 4B  | 58 | 89 | 78 | 88 | 98  | 108 | 118  | 128  | 138  | 14B | <u>5</u> | E B                    |                                        |

| 42       | DET 5<br>PROT          | (Personal)                                   |     |     |    |    |    |    |     |     |      |      |      |     | -        | DET 5<br>PROT          |                                        |

|          | DET S<br>PROT          | <b>****</b> ******************************** |     |     |    |    |    |    |     |     |      |      |      |     |          | DET S<br>PROT          |                                        |

| 02       | DET 4<br>PROT          |                                              |     |     |    |    |    |    |     |     |      |      |      |     |          | DET4<br>PROT           |                                        |

| 6        | DET 4<br>ELEC          |                                              |     |     |    |    |    |    |     |     |      |      |      |     |          | DET 4<br>ELEC          | SECONDS                                |

| 7 00     | DET 3<br>PROT          |                                              |     |     |    |    |    |    |     |     |      |      |      |     |          | DET3<br>PROT           | B SE                                   |

| LOCATION | HOUSE<br>KPG<br>(A     | 42                                           | 3.8 | 4.A | 5A | 6A | ٧Ł | 8A | 9.A | ICA | II A | 12.A | 13.A | 14A | ISA      | 16.A                   | SECONDS<br>= 208                       |

| ~        | DET 3<br>ELEC          |                                              |     |     |    |    |    |    |     |     |      |      |      |     |          | CET 3                  | FRAME                                  |

| WORD 5   | DET 2<br>PROT          |                                              |     |     |    |    |    |    |     |     |      |      |      |     |          | DET2<br>PROT           | MAIN FR                                |

| 4        | DET 2<br>ELEC          |                                              |     |     | ·  |    |    |    |     |     |      |      |      |     |          | DET2<br>ELEC           | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

| 8        | DET I<br>PRÖT          |                                              |     |     |    |    |    |    |     |     |      |      |      |     | -        | DET I                  | A                                      |

| 2        | DET 1<br>ELEC          |                                              |     |     |    |    |    |    |     |     |      |      |      |     | ->-      | DET I                  |                                        |

| _        | PRIME<br>FRAME<br>SYNC |                                              |     |     |    |    |    |    |     |     |      |      |      |     |          | PRIME<br>FRAME<br>SYNC |                                        |

|          |                        | 2                                            | 3   | 4   | S  | 9  | 7  | ω  | 9   | 0   | =    | 2    | 5    | 4   | <u>.</u> | 9                      | •                                      |

PRIME FRAME NUMBER

IS HOUSEKEEPING CUITPUT GATE RECORD GATE I, ALD CONVERT START I, COLUMN SYNCGATE 12 RECORD GATE 10 RECORD GATE 6, A/D CONVERT 11 RECORD GATE 9 ? HOUSEKEEPING OUTPUT GATE COUNT GATE, M.K. MUX AOV, WORD SYNC OUTPUT GATE, COUNTER DUMP CONTROL 10 RECORD GATE & 9 10 11 12 13 1 RECORD GATE T RECORD GATE RECORD GATE RECORD GATE 3 00 RECORD GATE 2 9 2 3

71

1 PPS

Figure 5 TIMING DIAGRAM - WORD SEQUENCE/EVENTS

#### GENERAL DATA PROCESSOR SPECIFICATION

The EPS Data Processor consists of a sequence controller, ten counter registers, a digital data compressor, an analog to digital converter, A/D control, a 32 channel analog multiplexer and a parallel output buffer. The spacecraft information interface consists of thirteen bilevel data lines and one synchronizing command line. The thirteen bilevel lines are sampled, in parallel, at a rate of 1 Hz with each sample occurring a minimum of 20 milliseconds after the positive going transition of the 1 Hz synchronizing command. Scientific data accumulation specifications are:

- 1. Counting Interval 12 seconds

- 2. Recording Interval 13 seconds

- 3. Fractional Counter Livetime 92.3%

- 4. Counter Capacity  $-2^{24}-1 = 16,777,215$  events/channel

- 5. Counting Rate Maximum -2.80 x 10<sup>6</sup> cps/channel for no overflow.

- 6. Readout Format floating point binary compression, seven bit data word plus five bit place word.

- 7. Digital Accuracy ±0.5% of value

The EPS Housekeeping data accumulation specifications are:

- 1. Sample Rate .154/sec

- 2. Sample Rate Per Channel .0048/sec

- 3. Conversion Gain 10 bits

- 4. Number of Channels 32

- 5. Address, Range, Resolution, Accuracy See Table I

TABLE I. EPS DATA PROCESSOR HOUSEKEEPING SEQUENCE PARAMETER RANGE, ACCURACY, AND RESOLUTION CHART

|       |              |          | 티           | 0.110°C       | ×             | 02            | H               | S            | 02            | M V          | ~             | 0.02 µA      | E              | 10 mv        | 54 mv        | 500 mv           | 20 mv        | 10 mv     | λu.          | 110          | ×            | 0.02 µA      | .110             | ٠<br>۲          | 0.02 µA      | 10 mv          | !           | !!           | 10 mv        | 10 mv        | 54 mv         | 500 mv       | 20 mv            | 10 mv        | 6 mv            |

|-------|--------------|----------|-------------|---------------|---------------|---------------|-----------------|--------------|---------------|--------------|---------------|--------------|----------------|--------------|--------------|------------------|--------------|-----------|--------------|--------------|--------------|--------------|------------------|-----------------|--------------|----------------|-------------|--------------|--------------|--------------|---------------|--------------|------------------|--------------|-----------------|

|       |              |          | 잉           | $\dashv$      | 7             | ٠.            | 1.5°            | 70           | ±.05 µA       | u,           | _             | <b>→≀</b>    | £5 mv          | 41           | 41           |                  | -4.1         | ±50 mv    | 3            | ±1.5°C       | 10 k         | .05          | ä                | 101             |              | ±5 mv          | i i         | i<br>1       | ±5 mv        | +50 mv       | 2             | 25           |                  | ±50 mv       |                 |

|       |              |          | E GE        | 50°C to +     | o 100 ke      | .05 A to      | +50°C           | to 100 ke    | .05 A to      | volts to +10 | to 100 keV    | A to 20      | volts to +10   | volts to -10 | volts to +55 | s to 505         | volts to -20 | to -1     | V to 6.002 V | to +50°      | 0 to 100 keV | .05          | r)               | to l            | A to 2       | lts to +10     | On/Off      | On/Off       | ts to +10 vo | ts to -10 vo | $\mathcal{S}$ | ts to 505 vo | volts to -20 vol | ts to -10 vo | 0.V to 6.0020 V |

|       |              |          | MEASUREMENT | ackage Tempel | etector 1 No: | etector 1 Les | tector Plate Te | etector 2 No | etector Leaka | دلد          | etector 3 Noi | tector 3 Lea | 8 Volt Monitor | 8 Volt Monit | 25 Volt Moni | 50 Volt Moni     | 15 Volt Mon  | olt Monit | iscrim. Ref. | ackage Tempe | etector 4 No | etector 4 Le | etector Plate Te | etector 5 Noise | etector 5 Le | 5 Volt Monitor | ater Monito | eater Monitc | Volt Monit   | Volt Monit   | 5 Vol         | 50 Volt Moni | 5 Volt Mo        | t Monito     | scrim. Re       |

| USE-  | OI<br>ID     | T BIT    | ٣           | 0             | 0             | 0             | 0               | ~            | r-4           | l            | ٦             | 0            | 0              | 0            | 0            | <del>, -  </del> | <b>~</b> -1  | ٦         | ~            | 0            | Н            | 0            |                  | 0               | ٦            | 0              | ~-1         | 0            | ٦            | 0            | <u>-</u> 1    | 0            | ႕                | 0            | H               |

| OH    | I VE         | $\vdash$ | 2           | 0             | 0             | 0             | 0               | 0            | 0             | 0            | 0             | 7            | iЦ             | -            | <u>-</u> Н   | ~                | ~            | ~         | -            | 0            | 0            | <b></b> 1    | H                | 0               | 0            | rI             | ~           | 0            | 0            | <b>~</b>     | ٦             | 0            | 0                | <b>ч</b>     | <del>,</del> .  |

| PRIME | r KAME<br>NO |          |             | 1A            | 2A            | 3A            | 4.A             | 5A           | 6A            | 7A           | 8A            | 9 A          |                |              |              |                  |              | 15A       |              | 18           | 2B           | 38           | 4B               | SB              | 6B           | 73             | 8B          | 9B           |              | 11B          |               |              |                  | 15B          |                 |

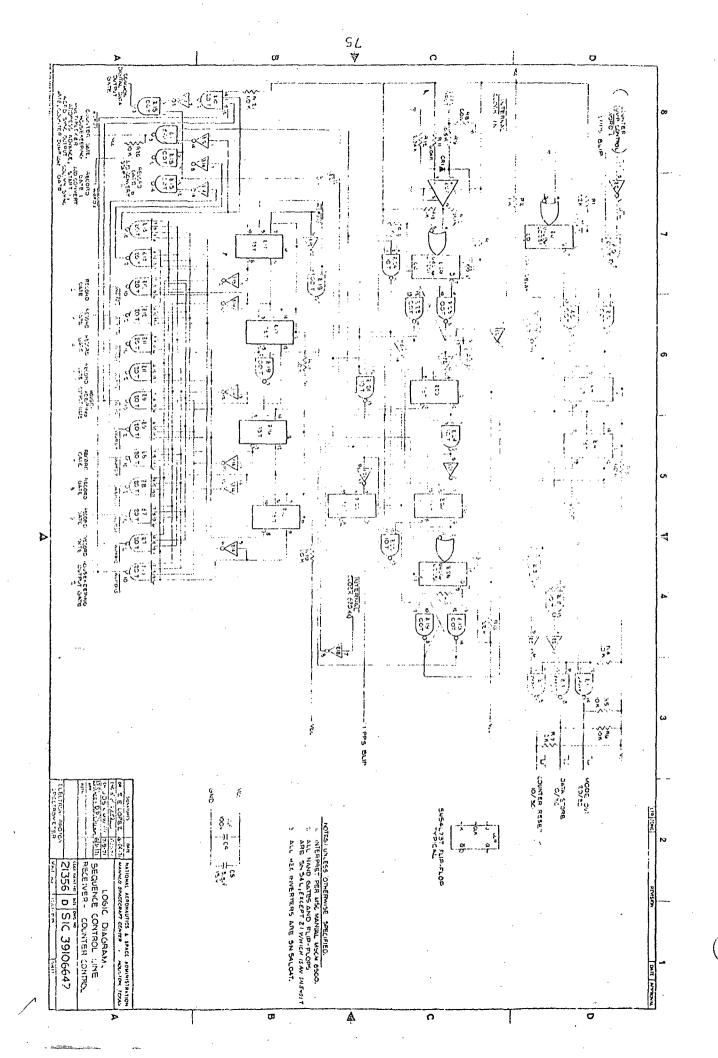

3.4.1 SEQUENCE CONTROL, LINE RECEIVER - COUNTER CONTROL

This module (Schematic SIC39106647) generates the timing

sequence for the thirteen word intervals. The one Hertz

Clock pulse is used in this module to synchronize all data

to the CSM data requirements. The counter control pulses

are also generated in this module and are used to start

the counter, shift the data from the counters to the

registers and reset the counters.

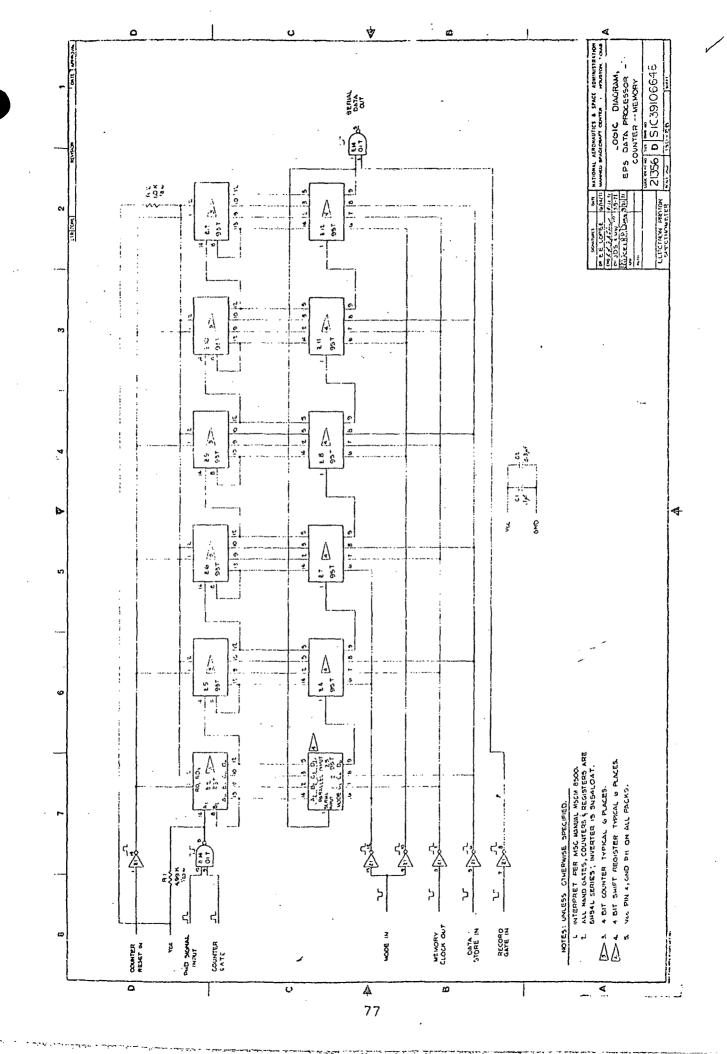

#### 3.4.2 COUNTER-MEMORY

The Counter-Memory Module (Schematic SIC39106648) contains a 24-bit counter and 24-bit parallel entry, serial out shift register. The counter counts pulses fed in at the PHD input. The counter has a count rate capability of 2.3 Mega Hertz. The counter is gated on by a positive counter gate signal. The normal count time is 12 seconds. Data is shifted into the register by the two signals called Mode and Data Store. The counter is then reset and ready to start another count cycle. The data is shifted through the shift register with a 24-pulse train. If the Record Gate is on, the data stored in the shift register will appear at the Serial Data output. The 24 pulses per shift cycle circulate the data by the output gate and return the data to its original position in the shift register. The data remains in the shift register until it is replaced by new data from the counters during the next data shift operation. are ten identical counter-memory modules in the EPS instrument.

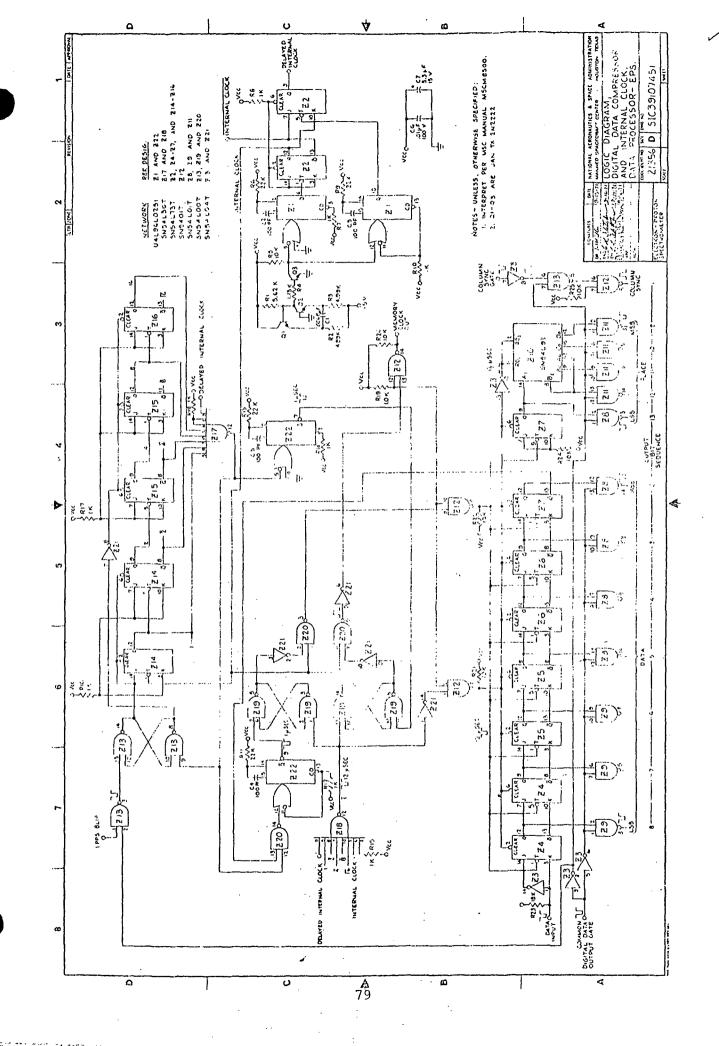

#### 3.4.3 DIGITAL DATA COMPRESSOR AND INTERNAL CLOCK

The Digital Data Compressor and Internal Clock module (Schematic SIC39107451) generates the memory clock (for shifting the digital data in the counter-memory modules), compresses the digital data so that the seven most significant bits are read out, and generates the internal, biphase clock pulses. The data from the shift register is shifted into the data compressor until a "1" is shifted into the MSB position, or until 24 shifts occur. The number of shifts which occur during any one shift cycle is counted by the 5-bit shift counter. Thus, the data output consists of 7 bits of data, 5 bits of shift data, or "place", and 1 bit which is called column sync. The column sync bit is a "0" except during the second word. Then it is a "1".

The bi-phase clock consists of a basic 40 k Hertz oscillator, two one-shots and a divide by two circuit, giving an internal clock frequency of 20 k Hertz. The delayed clock output lags the clock by 90 degrees and is used in decoding circuits to inhibit glitches on decoded outputs during flipflop transitions.

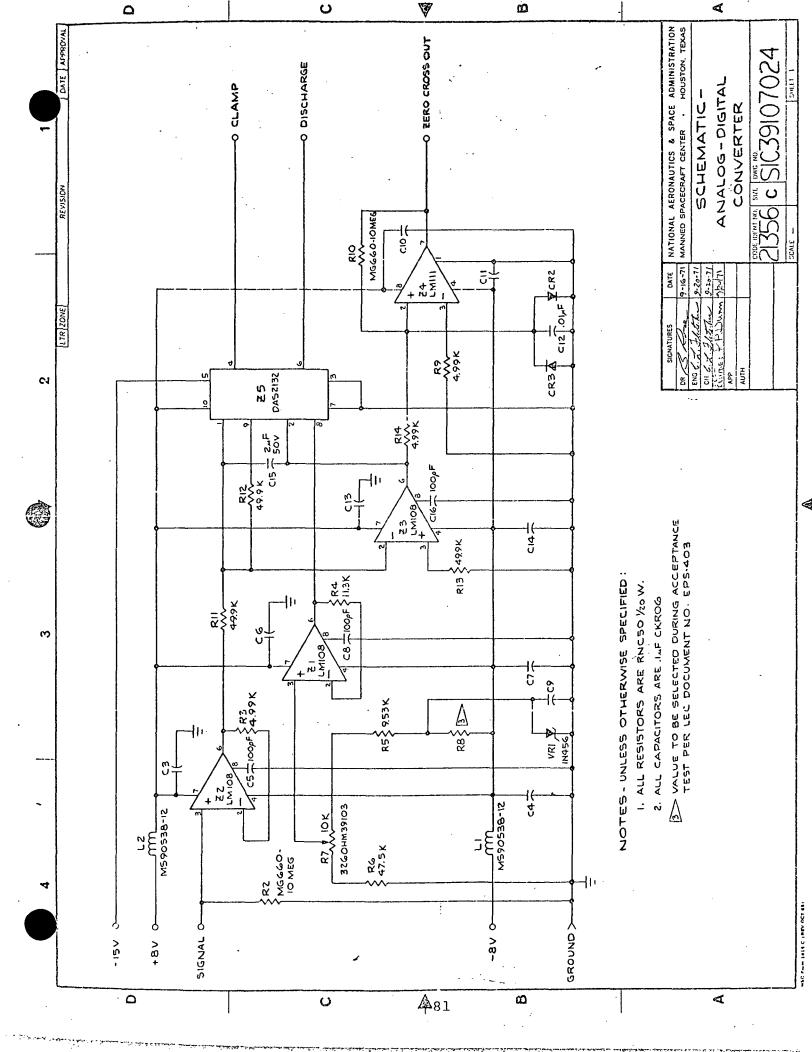

#### 3.4.4 ANALOG-DIGITAL CONVERTER (SCHEMATIC SIC39107024)

The analog to digital converter is a 10-bit unit utilizing the dual-slope principle and a zero-crossing detector. basic circuits are a buffer amplifier, reference amplifier, integrating amplifier, dual J-FET switch, and a comparator. The buffer amplifier serves as interface between all housekeeping data sources and the integrating amplifier. reference amplifier provides a very stable source of current and its reference is a temperature controlled Zener One of the J-FET switches controls the reference current to the integrating amplifier. The other J-FET switch discharges the integrating capacitor and holds it in a zero charge state during the clamp time interval. integrating capacitor is a 2 microfarad polycarbonate with very low leakage, low dissipation factor, and low temperature coefficient. The integrating amplifier provides drive to the comparator, which has approximately 10 mV of hysteresis to eliminate false zero-crossing output. The comparator output is used in the timing control of the A/D Control Logic.

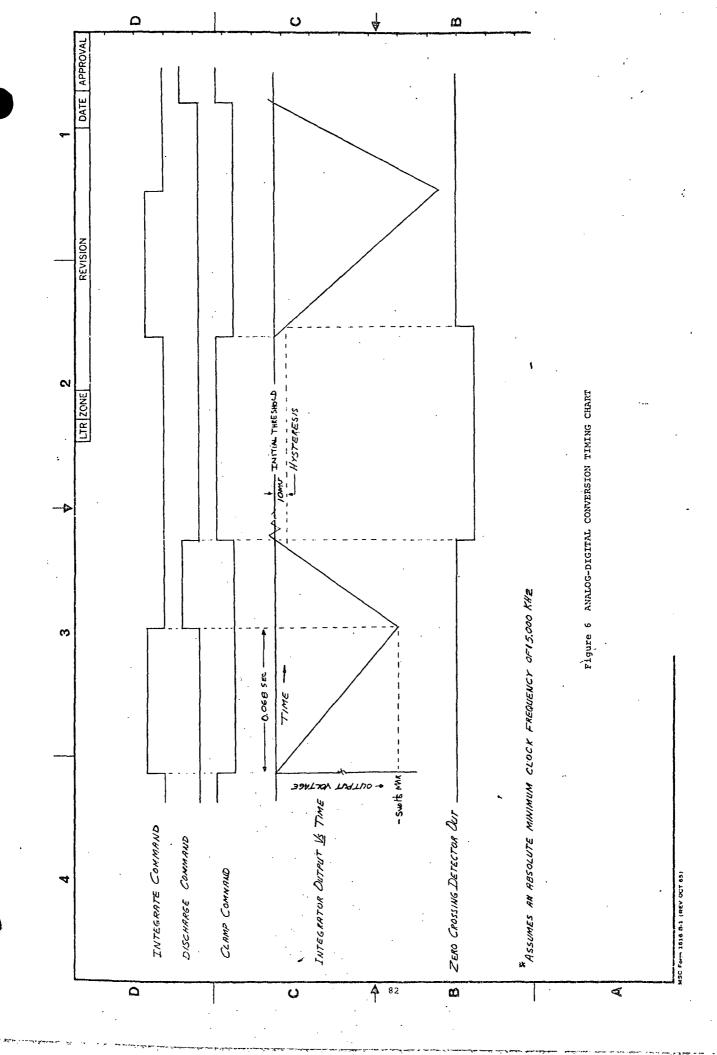

The timing sequence of the conversion process is shown in the Analog-Digital Conversion Timing Chart, Fig. 6.

The operation is as follows: The multiplexer is gated on (enabled) and an analog voltage is fed to the buffer amplifier, which charges the integrating capacitor through a 49.9 K ohm resistor for a fixed time (.051 sec.). The capacitor will assume a charge dependent upon the analog voltage level which is limited to a maximum of 5 volts. The multiplexer is then switched off, the reference current is switched in, and

the capacitor is discharged at a constant rate from the reference circuit. When the capacitor charge passes through zero the comparator changes state and stops the conversion process. The digital word is generated in the A/D Control Logic and is discussed in Section 3.4.5.

Sources of error in the analog-digital conversion are offset voltages in the amplifiers, leakage current through the J-FET switches, variation in the reference circuit and comparator offset. The offset voltage of the amplifiers and comparator are specified to be less than 3 mV.

Leakage current through the J-FET switches was measured and caused no error under actual circuit operation. The reference circuit has a temperature compensated Zener diode reference, and the actual measured temperature coefficient for the reference circuit is .0007%/°C over the -50°C to +70°C temperature range. The maximum analog voltage which may be measured is 5 volts. The resolution is 5 mV or 1 bit.

## ANALOG-DIGITAL CONVERTER SPECIFICATION

### 1. ADC Analog Section

The analog to digital converter is a dual slope type, with the input range of 0 to 5 volts. The output is 10 bits with an accuracy of  $\pm$  1 LSB over the temperature range of  $-25^{\circ}$  C to  $+50^{\circ}$  C.

## Reference Amplifier, Integrating Amplifier and Buffer Amplifier

$V_{\scriptsize{\text{OFFSET}}}$  3 mv max

$V_{\rm OFFSET}$  Temp. Coef. 15  $\mu V/^{\circ}C$

I<sub>OFFSET</sub> .4 na max

Operating Temp. Range -55°C to +125°C

Power Supply Require-

ment/Amplifier ±8 Volts @ .5 ma

Common Mode Rejection

Ratio 85 dB min

Power Supply Rejection

Rate 80 dB min

Large Signal Voltage

Gain 300 V/mv typical

## 3. Analog Switch

The analog switches are  $J_{\rm FET}$  devices with drivers. The DAS 2132 is a dual unit, each unit having separate control.

Power Supply Requirements

+8 volts 2 ma/switch "ON"

0 ma/switch "OFF"

-15 volts 1.6 ma/switch "ON"

0 ma/switch "OFF"

Logic Level Required for "ON-OFF"

Control (TTL Compatible)

Operating Temp. Range.

Resistance of Switch

"ON" + 3 Volt

"OFF" 0 Volt -55°C to +125°C

"ON" = 80 ohms

"OFF" 200 megohms

Turn-on Time

Turn-off Time

.5 µsec

.5 µsec

### Integrating Capacitor

Capacitance/Voltage

Insulation Resistance @ 60°C

Percentage Capacitance Change Over Temp. Range - 45°C to

+90°C

$2 \mu f/50 VDC$

3000 megohms - microfarads

+1%, -2%

Dissipation Factor (-50°C to

+125°C)

Capacitor Type

+.5%, -0.0%

metalized polycarbonate

#### 5. Comparator

Power Supply Requirements

Operating Temp. Range

Input Offset Voltage

Input Offset Current

Bias Current

+8 volts @ 10 ma

-55°C to +125°C

3 mv maximum

10 nA maximum

100 ηA maximum

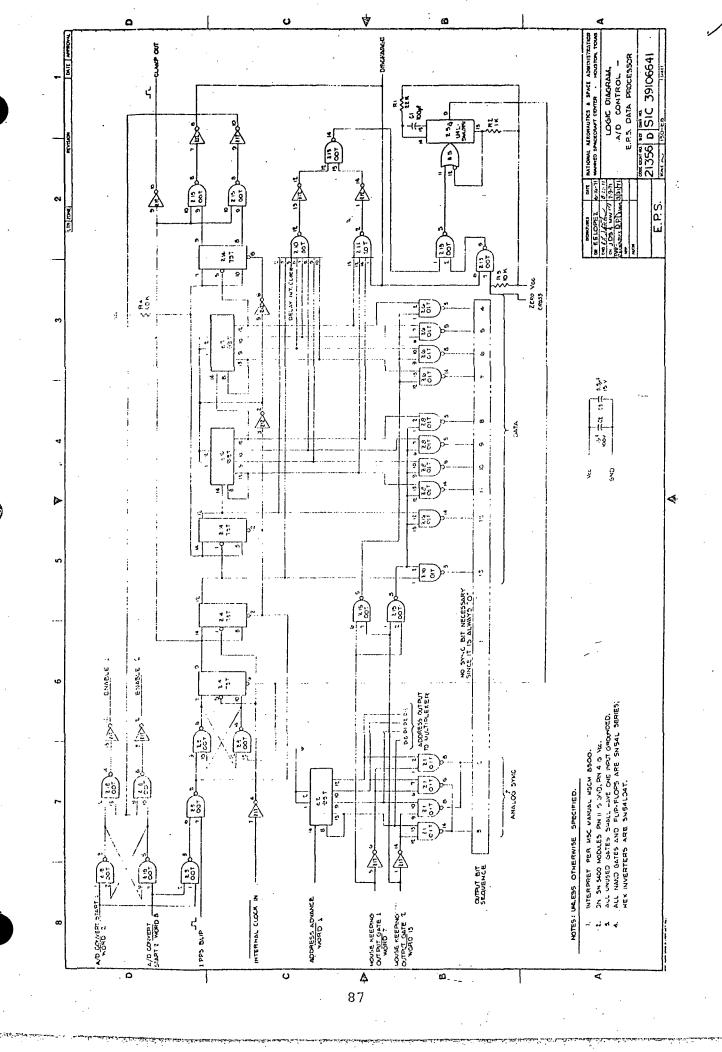

#### 3.4.5 A/D CONTROL (SCHEMATIC SIC39106641)

The A/D Control Module provides the control functions for the A/D converter, generates the 10 bit digital word plus two sync bits for the housekeeping data word, and provides four bits of address to the multiplexer. The A/D conversion occurs during intervals 2 and 8 and is initiated by the 1 The latch circuit is set and remains on until the end of the conversion. The gate that sets the latch resets all counters to zero. When the latch is set, the 11 bit counter starts, the clamp signal goes low, and enable 1 or enable 2 goes high. When the eleventh bit goes to a high state (1024 clock pulses), the enable line goes low, and the discharge line goes high. The counter continues to count until "Zero Cross" occurs, which resets the latch and stops the counter. The number in the counter is the digitized equivalent of the analog input to the A/D converter. data appears on the output gates and is read out during interval 7 or 13.

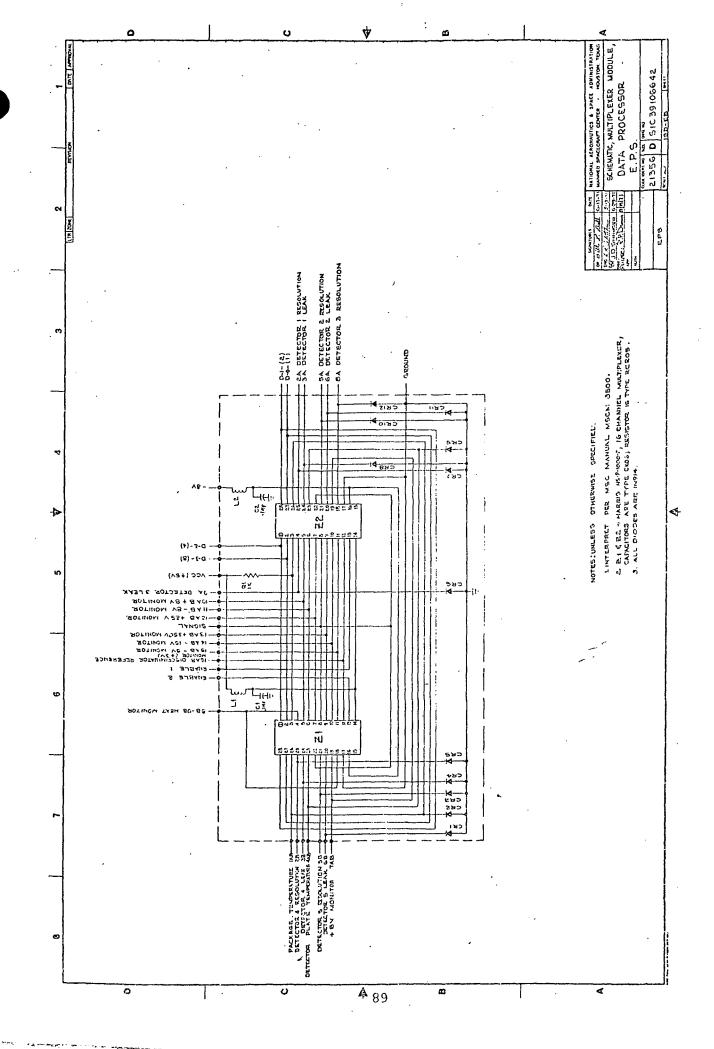

## 3.4.6 MULTIPLEXER MODULE (SCHEMATIC SIC39106642)

The Multiplexer Module consists of two integrated circuit packages each containing a 16-channel multiplexer. The two units are operated as a 32-channel unit. There are 21 sources of data fed through the multiplexer. However, all channels are used, which allows eleven channels of redundant data. The multiplexer package contains the decoding logic required for switching, so it can be operated by the binary outputs of a 4-bit counter. The multiplexer utilizes the J-FET device for switches. Diodes clamps are used to prevent negative bias being applied to the multiplexer.

#### MULTIPLEXER SPECIFICATION

The Multiplexer Specifications are outlined below.

The multiplexer serves as a switching device to route various analog voltages to the analog-to-digital converter (ADC). The individual channel switches must have an "ON" resistance small such that the analog voltage being switched is not lowered significantly. The "OFF" resistance must be sufficiently high to avoid "cross-talk" or leakage from the "OFF" channels to the channel being measured.

Number of Channels Power Requirement, Total

"ON" Resistance

"OFF" Leakage Current

Channel Addressing

Cross Talk with Vin

Environmental

Analog Voltage Range Input

16 x 2 = 32

(+5 Volts @ 9.6 ma) x 2 = 96 mw

(-8 Volts @ 16 ma) x 2 = 256 mw

1200 ohms maximum

< 250 Picoamps

Compatible to TTL Logic

20 VP-P, 100 kHz - - - -80 dB

MIL-STD 883, Condition B

0.0 to +5.0 Volts

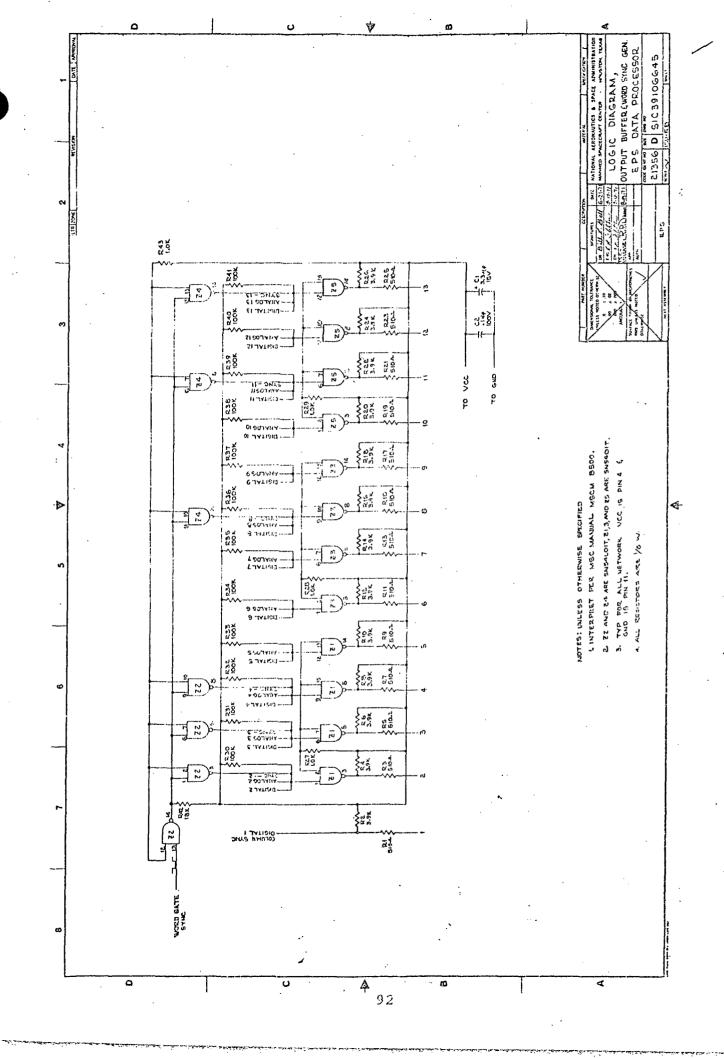

## 3.4.7 OUTPUT BUFFER AND WORD SYNC GENERATOR ( SCHEMATIC SIC39106645)

The Output Buffer and Word Sync Generator interfaces all data from the EPS to the CSM telemetry. The sync word is also generated in this module. During Word 1 time interval the word sync gate is enabled and the sync word (0111000100101) is fed out on the data lines. The output buffers are standard power T<sup>2</sup>L logic chosen to special parameters so that they may be driven by derated low power logic. The inputs to the output buffer are connected in the WIRED-OR configuration, and input data originates in the Data Compressor Module (digital data), the A/D control module (analog data) and the word sync generator circuit. The output of the buffer is designed to meet the interface requirements as specified in the Electrical ICD MH04-02110-234.

The output bits are required to reach their sampled voltage level within 20 milliseconds after the positive going edge of the 1 Hertz clock pulse (Section 3.4.1). This allows approximately 9 charging time constants for the output positive going pulse. The pulse will rise to 3.5 volts in 5 time constants, giving a large safety margin. The discharge time constant for a data bit "0" is approximately 10 times shorter, so no timing problems occur for the "0" bit data. All output data lines are fed out through filters.

### 3.5 POWER SYSTEMS

The EPS Power System was designed to receive the +28 V available from the spacecraft and provide the proper output voltages to both the EPS detectors and the electronic subsystems. The design criteria for the EPS power subsystems were partially specified in the EPS Electrical ICD NR #MH04-02119-234 and in the Electromagnetic Compatibility Design Criteria NR Document #MH04-0257-234.

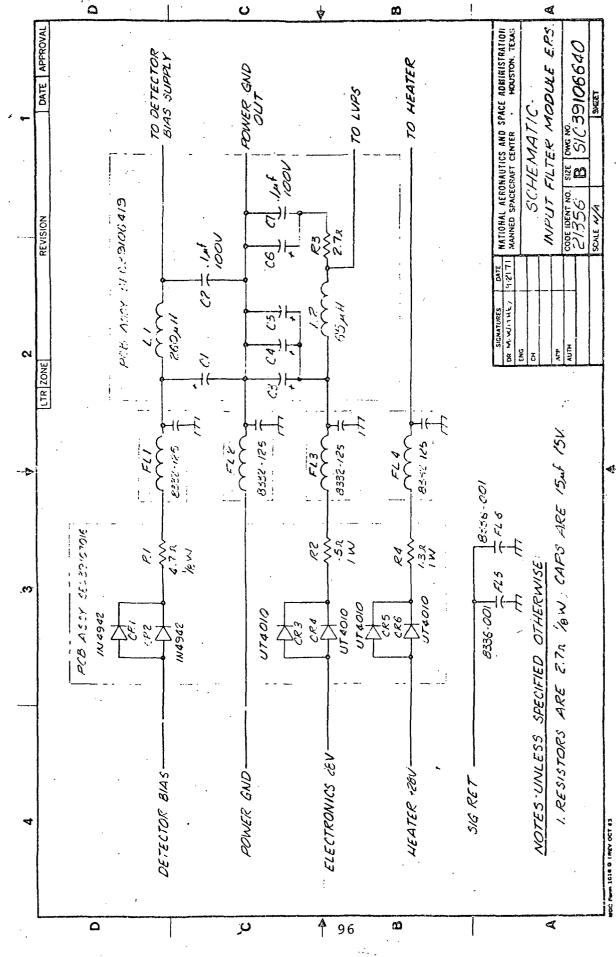

#### 3.5.1 INPUT FILTER

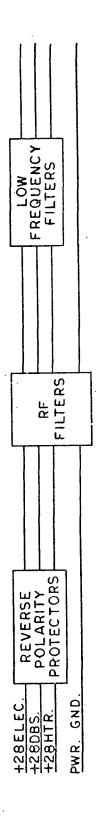

The three plus 28 Vdc power inputs and power ground from the CSM are routed to the EPS power input filter (see Block Diagram and Schematic SIC39106640). Within the Input Filter, all four lines are routed through circuits that protect the EPS from voltages of reverse polarity and from noise and interferences conducted into the EPS. The Input Filter also provides filtering for interference generated within the EPS and conducted out the power lines. The three power lines are then routed to the individual subassemblies.

INPUF FILTER MODULE BLOCK DIAGRAM

## ELECTRON-PROTON SPECTROMETER INPUT FILTER MODULE SPECIFICATIONS

- A. <u>Inputs</u>: The EPS Input Filter Module shall accept four separate inputs. These inputs are:

- 1. Electronics Power Input: 27.5 Vdc ± 2.5 Vdc

- 2. Detector Bias Power Input: 27.5 Vdc ± 2.5 Vdc

- 3. Heater Power Input: 27.5 Vdc ± 2.5 Vdc

- 4. Power Ground

- B. Outputs: The Input Filter Module shall provide four separate filtered power outputs to the EPS. These outputs are:

- Electronics Power (filtered)

- 2. Detector Bias Power (filtered)

- Heater Power (filtered)

- 4. Power Ground (filtered)

- C. RFI: The Input Filter Module shall provide the necessary electronic circuits to meet or exceed the requirements of North American Rockwell Corp., Space Division Document MH04-02057-234, Electromagnetic Compatibility Design Criteria.

- D. Operating Temperature Range: -25°C to +50°C

- E. Survival Temperature Range: -50°C to +65°C

F. Ground Isolation: There shall be a minimum of 1 megohm resistance between the power ground and the EPS external structure (chassis ground).

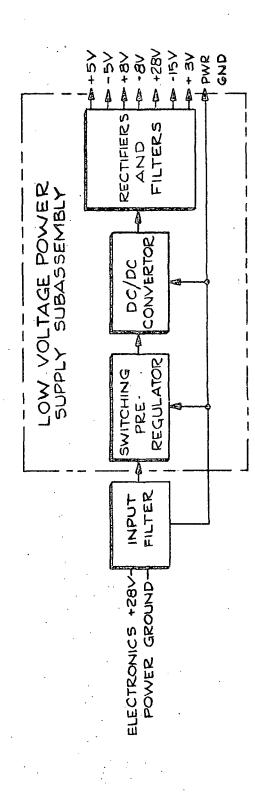

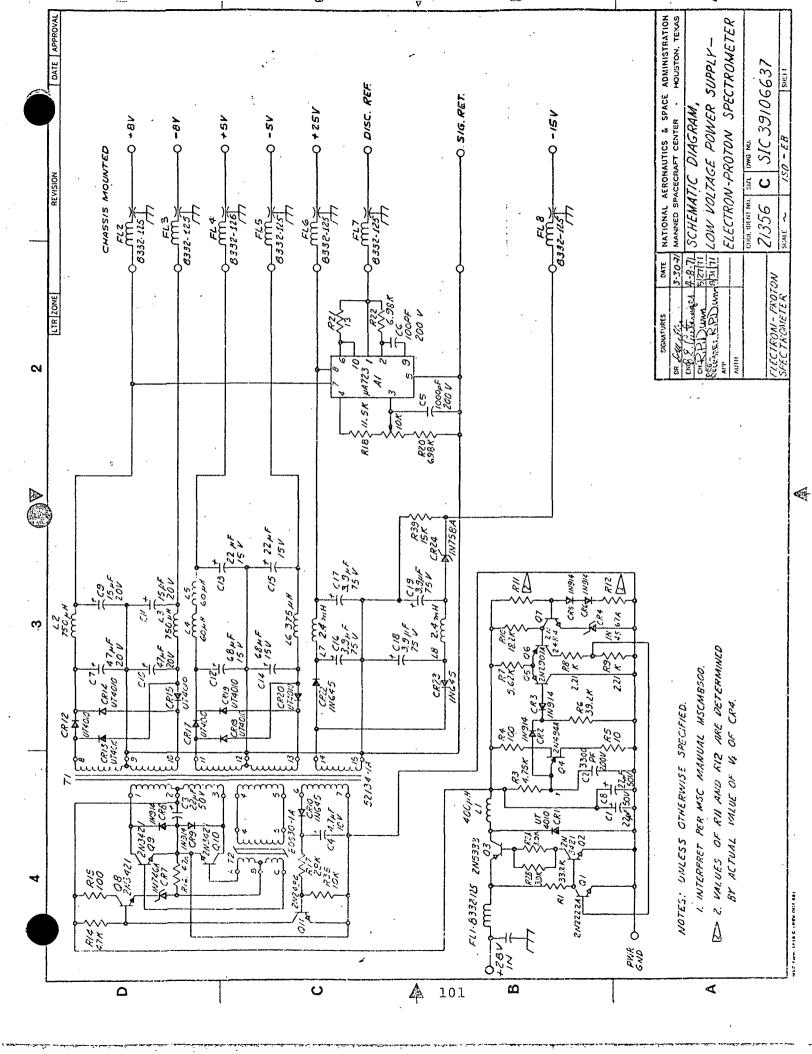

#### 3.5.2 LOW VOLTAGE POWER SUPPLY

The Low Voltage Power Supply (see Block Diagram and Schematic SIC39106637) receives filtered +28 V which is regulated down to +20 Vdc by utilizing a switching regulator. A switching regulator was used because of the efficiency required. The regulator output is then utilized by the dc/dc converter. There are three separate output windings on the dc/dc converter transformer. These windings produce six different output voltages. One of these outputs (the +8V) is also regulated down to +3.0 V to provide a stable reference voltage for the pulse-height discriminator subassemblies.

LOW VOLTAGE POWER SUPPLY BLOCK DIAGRAM

# LOW VOLTAGE POWER SUPPLY SPECIFICATIONS

A. Input Voltage: 27.5 ± 2.5 Vdc

B. Input Current:  $I_{in}(max) \leq 557 \text{ ma @ 28 Vdc}$

C. RFI: Must meet or exceed the requirements of North American Rockwell Corp., Space Division Document MH04-02057-234, Electromagnetic Compatibility, Design Criteria.

D. Operating Temperature Range: -25°C < Topp < +50°C

E. Survival Temperature Range: -50°C ≤ T<sub>Surv</sub> ≤ +65°C

F. Outputs: The LVPS must provide the following outputs (with the given specifications):

| Volt            | age | Current  | Regulation           | Maxim<br>Rippl | -    | Max<br>Spi | kimum<br>ke |

|-----------------|-----|----------|----------------------|----------------|------|------------|-------------|

| +8              | Vdc | 175 mamp | +0.2 Vdc<br>-0.0 Vdc | 25             | mvpp | 50         | mvpp        |

| -8              | Vdc | 150 mamp | +0.2 Vdc<br>-0.0 Vdc | 25             | mvpp | 50         | mvpp        |

| +5              | Vdc | 900 mamp | ±0.3 Vdc             | 50             | mvpp | 50         | mvpp        |

| <del>-</del> 5  | Vdc | 115 mamp | ±0.3 Vdc             | 50             | mvpp | 50         | mvpp        |

| +25             | Vdc | 10 mamp  | ±2.0 Vdc             | 150            | mvpp | 50         | mvpp        |

| <del>-</del> 15 | Vdc | 1 mamp   | ±2.0 Vdc             | 150            | mvpp | 50         | mvpp        |

| +3.0            | Vdc | 20 mamp  | ±0.01 Vdc            | 1.0            | mvpp | 5          | mvpp        |

### 3.5.3 DETECTOR BIAS SUPPLY

The +28 Vdc for the Detector Bias Supply (see Block Diagram and Schematic SIC3910638) is regulated down to +21 Vdc in order that the bias applied to the EPS detectors will not be affected by fluctuations in the spacecraft power lines. This regulated +21 Vdc is then fed to the dc/dc converter which generates a 350 volt square wave. This is rectified, filtered and applied to the detectors cathode thru the bias filter subassembly.

DETECTOR BIAS SUPPLY BLOCK DIAGRAM

## DETECTOR BIAS SUPPLY SPECIFICATIONS

- A. Input Voltage: 27.5 ± 2.5 Vdc

- B. Input Current: Maximum < 50 ma @ 28 Vdc

- C. <u>RFI</u>: Must meet or exceed the requirements of North American Rockwell Corp., Space Division Document MH04-02057-234, Electromagnetic Compatibility, Design Criteria.

- D. Operating Temperature Range: -25°C to +50°C

- E. Survival Temperature Range: -50°C to +65°C

- F. Output: The Detector Bias Supply must provide the following output:

| Voltage  | Current | Regulation | Maximum<br>Ripple | Maximum<br>Spike |

|----------|---------|------------|-------------------|------------------|

| +350 Vdc | 10 μa   | ±17.5 Vdc  | 500 mvpp          | 10 mypp          |

G. Monitor Output: The detector bias supply must provide an analog output voltage that is directly proportional to the bias voltage. The monitor output must have the following characteristics:

|            | Output     |  |  |  |  |  |  |  |

|------------|------------|--|--|--|--|--|--|--|

| Amplitude  | Impedance  |  |  |  |  |  |  |  |

|            |            |  |  |  |  |  |  |  |

| 0 to 5 Vdc | < 1 Megohm |  |  |  |  |  |  |  |

### 3.6 HEATER CONTROL SYSTEM

The Heater Power +28 Vdc line and power ground are routed to the Heater Control (see Block Diagram and Schematic SIC39106639) subassembly. The +28 Vdc is regulated to +10 Vdc for use as a stable reference for the temperature sensing circuit. The temperature sensing circuit consists of a thermistor and schmitt trigger, with the trip points set at 0° C (heater turn-on) and 10° C (heater turn-off). The output of the schmitt trigger is amplified and utilized to apply power, as necessary, to four individual skin heaters bonded to the electronics assembly housing. In addition to controlling the 6 watt heater, the schmitt output is also buffered and routed to the EPS Data Processor to provide the status of the EPS heaters (i.e., whether on or off).

HEATER CONTROL BLOCK DIAGRAM

. . ÷

*.*:

## HEATER CONTROL SPECIFICATIONS

- A. Input Voltage: 27.5 ± 2.5 Vdc

- B. Input Current: I in (Max) = 214 ma @ 28 Vdc

- C. <u>RFI</u>: Must meet or exceed the requirements of North American Rockwell Corp. Document MH04-02057-234, Electromagnetic Compatibility, Design Criteria.

- D. Operating Temperature Range:

$$-25^{\circ}C \leq T_{opp} \leq +50^{\circ}C$$

E. Survival Temperature Range:

$$-50$$

°C  $\leq$  T<sub>surv</sub>  $\leq$   $+65$ °C

- F. Operation: The Heater Control will sense the temperature of the EPS electronics package and provide 6 watts of heater power when the temperature drops below 0° C. When the temperature of the electronics package rises to 10° C, the Heater Control shall remove the 6 watts of heater power.

- G. <u>Outputs</u>: The Heater Control shall provide a bi-level output to the EPS Data Processor indicating whether the heater is on or off.

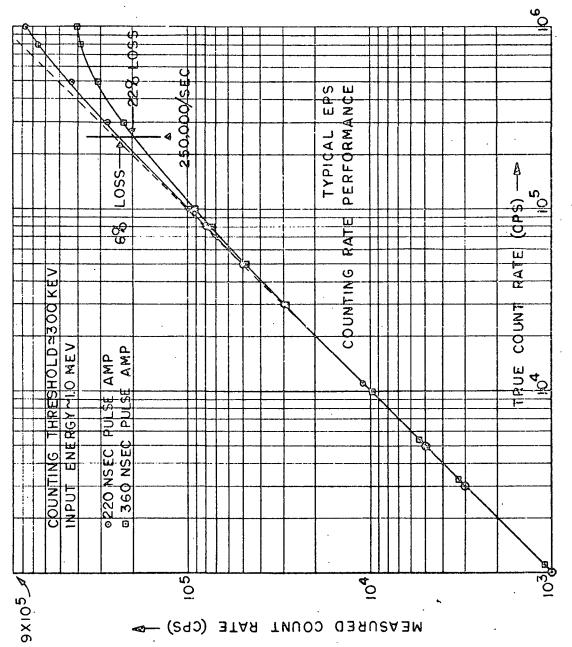

## 3.7 PERFORMANCE OF THE EPS SCIENTIFIC DATA ACQUISITION SYSTEM

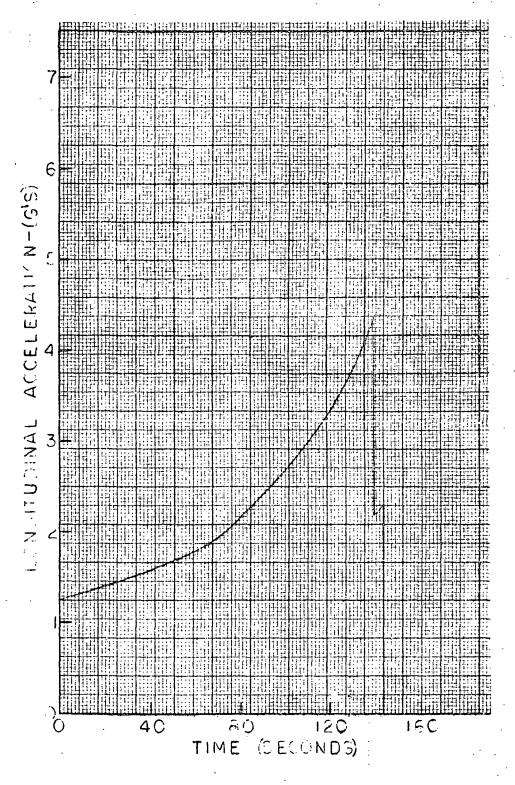

Errors, introduced by the EPS Scientific Analog and Data Processor Systems fall into two catagories, those errors affecting counting rate measurements and those errors affecting spectrum shape measurements. The following quantitative analysis is limited by the accuracy of measurements made to date.

#### 3.7.1 ERRORS AFFECTING COUNTING RATE ACCURACY

### 3.7.1.1 Data Roundoff