# NASA CONTRACTOR REPORT

N13-19225 NASA CR-2159

# CASE FILE COPY

# ILLIAC IV SYSTEMS CHARACTERISTICS AND PROGRAMMING MANUAL

Prepared by

BURROUGHS CORPORATION

Paoli, Pa. 19201

for Ames Research Center

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION • WASHINGTON, D. C. • FEBRUARY 1973

| 1. Report No. NASA CR-2159                                                  | 2. Government Access     | ion No.                                 | 3. Recipient's Catalog No.       |                  |  |  |  |  |  |

|-----------------------------------------------------------------------------|--------------------------|-----------------------------------------|----------------------------------|------------------|--|--|--|--|--|

| 4. Title and Subtitle                                                       |                          |                                         | 5. Report Date                   |                  |  |  |  |  |  |

|                                                                             |                          |                                         | February 197                     | 13               |  |  |  |  |  |

| ILLIAC IV Systems Characteristic                                            | cs and Programming       | Manual -                                |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         | 6. Performing Organization Code  |                  |  |  |  |  |  |

| 7. Author(s)                                                                |                          |                                         | 8. Performing Organiza           | ation Report No. |  |  |  |  |  |

|                                                                             |                          |                                         | 0. 10.10.1g = 13ce               |                  |  |  |  |  |  |

|                                                                             |                          | F                                       | 10. Work Unit No.                |                  |  |  |  |  |  |

| 9. Performing Organization Name and Address                                 |                          |                                         | TO. WORK OME NO.                 |                  |  |  |  |  |  |

| Burroughs Corporation                                                       |                          | <b> -</b>                               | 11. Contract or Grant            | NI-              |  |  |  |  |  |

| Defense, Space and Special Syst                                             | tems Group               | 1                                       |                                  | NO.              |  |  |  |  |  |

| Paoli, PA 19201                                                             |                          |                                         | AF 30(602)4144                   |                  |  |  |  |  |  |

| ,                                                                           | •                        | F                                       | 13. Type of Report an            | d Period Covered |  |  |  |  |  |

| 12. Sponsoring Agency Name and Address                                      |                          |                                         |                                  |                  |  |  |  |  |  |

| National Aeronautics and Space Ad                                           | ministration             |                                         | Contractor Repo                  | )1 L             |  |  |  |  |  |

| Washington, D.C. and                                                        | •                        | Γ                                       | 14. Sponsoring Agency            | Code             |  |  |  |  |  |

| Advanced Research Projects Agency                                           |                          |                                         |                                  |                  |  |  |  |  |  |

| Arlington, Va.                                                              |                          |                                         |                                  |                  |  |  |  |  |  |

| 15. Supplementary Notes                                                     |                          |                                         |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

| 16. Abstract                                                                |                          | , - · · · · · · · · · · · · · · · · · · |                                  |                  |  |  |  |  |  |

| 10. Abstract                                                                |                          |                                         |                                  |                  |  |  |  |  |  |

| This is the leave alive of the                                              |                          | 1.7                                     |                                  |                  |  |  |  |  |  |

| This is the latest edition of the                                           | Systems Characte         | ristics and Program                     | ning Manual to be                | supplied by      |  |  |  |  |  |

| the manufacturer of the ILLIAC IV                                           | Array and parall         | el disc memory syste                    | em. The ILLIAC                   | lV Array, a      |  |  |  |  |  |

| control unit and sixty-four arith                                           | metic processing         | units, is part of a                     | large digital co                 | omputing         |  |  |  |  |  |

| system that employes a variety of                                           | processors and r         | otating storage devi                    | ices. Inis docum                 | ent covers       |  |  |  |  |  |

| the major aspects of the Array.                                             | section 1 is devo        | ted primarily to the                    | Array systems of                 | naracteristics.  |  |  |  |  |  |

| Section 2 concerns programming ch                                           | maracteristics tha       | t include a descrip                     | tion of the word                 | formats. The     |  |  |  |  |  |

| next three sections, 3, 4, and 5                                            | provide a definit        | ion and flow chart (                    | or each of the 29                | 22 instructions. |  |  |  |  |  |

| Sections 6 and 7 concern timing. tion index. This manual remains            | mere are two ap          | pendices: (a) Gloss                     | sary or terms, ar                | id (b) Instruc-  |  |  |  |  |  |

| readers who anticipate learning                                             | to use the custom        | references when property                | granming for thi.                | IAC IV but       |  |  |  |  |  |

| readers who difference rearring                                             | o use the system         | will require other t                    | iocuments.                       |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  | :                |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         | •                                |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         | •                                |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

|                                                                             | ·                        |                                         |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

|                                                                             |                          |                                         |                                  |                  |  |  |  |  |  |

| 17. Key Words (Suggested by Author(s))                                      |                          | 18. Distribution Statement              |                                  |                  |  |  |  |  |  |

|                                                                             |                          | 18. Distribution Statement              |                                  |                  |  |  |  |  |  |

| ILLIAC IV                                                                   |                          |                                         | )-UNCLASSIFIED                   |                  |  |  |  |  |  |

| ILLIAC IV<br>Array Processor                                                |                          |                                         | O-UNCLASSIFIED                   |                  |  |  |  |  |  |

| ILLIAC IV Array Processor Parallel Processing                               |                          |                                         | O-UNCLASSIFIED                   |                  |  |  |  |  |  |

| ILLIAC IV<br>Array Processor                                                |                          |                                         | O-UNCLASSIFIED                   |                  |  |  |  |  |  |

| ILLIAC IV<br>Array Processor<br>Parallel Processing<br>Large Scale Computer |                          |                                         | O-UNCLASSIFIED                   |                  |  |  |  |  |  |

| ILLIAC IV Array Processor Parallel Processing                               | 20. Security Classif. (o | UNLIMITE                                | O-UNCLASSIFIED  21. No. of Pages | 22. Price*       |  |  |  |  |  |

| ILLIAC IV<br>Array Processor<br>Parallel Processing<br>Large Scale Computer | 20. Security Classif. (o | UNLIMITEI<br>f this page)               |                                  | 22. Price* 6.00  |  |  |  |  |  |

$<sup>^{*}</sup>$  For sale by the National Technical Information Service, Springfield, Virginia 22151

#### **EXPLANATORY NOTE**

This is the latest edition of the ILLIAC IV Systems Characteristics and Programming Manual to be supplied by the manufacturer of ILLIAC IV. It differs from the previous edition (IL4-PM1), Revision A, 30 January 1970 and Change No. 1, 30 June 1970) in four sections. The sections and pages significantly affected are:

Section II, page 2-28, 2-40 and 2-47

Section III, pages 3-7 and 3-44

Section IV, pages divider overleaf, 4-2, 4-4, 4-16, 4-18, 4-42, 4-67, 4-69, 4-82, 4-91, 4-92,

4-93, 4-95, and 4-105

Section V, page 5-10 up to the instruction set, now page 5-14, also instruction EFA now page 5-16.

All known errors have been corrected in this manual, the changes noted below not withstanding.

There is an important change which is not noted in this document. The control computer for the ILLIAC IV will not be a B6700. Instead, control will reside in a large central memory to which multiple processors and secondary storage devices will be attached. This configuration will obviate the functions of the Buffer I/O Memory and B6700 that are described herein.

Although these changes will make obsolete some of the information in this manual, most of it is accurate and stable. This manual remains one of the basic references when programming for the ILLIAC IV. Readers who anticipate learning to use the ILLIAC IV will require other documents.

Staff

Institute for Advanced Computation

Ames Research Center

National Aeronautics & Space Administration

Moffett Field, California 94035

Mel W. Pirtle, Director

Institute for Advanced Computation

|     |                                           | COI    | NIE  | NI  | 5   | •       |     |     |     | •  | • • |     |                  | Page         |

|-----|-------------------------------------------|--------|------|-----|-----|---------|-----|-----|-----|----|-----|-----|------------------|--------------|

|     |                                           |        |      |     |     |         | ٠   |     |     |    |     |     |                  | 1 age        |

| I.  | SYSTEM CHARACTERISTIC                     | S.     | • .  | • . | à   | .•      | •   | . • | •   | •  | ٠   | •   | •                | 1-1          |

|     | System                                    |        |      |     |     |         |     |     |     |    |     | ·.· | • '              | 1-1          |

|     | System Elements Control Unit Functions    | •      |      | •   | •   | •       | 2.  |     |     | •  |     |     |                  | 1-3<br>1-7   |

|     | Control Units                             | •      | •    |     | •   | •       |     | •   | • . |    | •   | •   |                  | 1-11         |

|     | Control Unit Structure                    | •      | • •  |     |     | •       |     |     |     |    |     |     | •                | 1-14         |

|     | Timing Considerations                     |        |      |     | • . |         |     |     |     |    |     |     | •                | 1-16         |

|     | Sequence of Operations                    | •      | • •  | • . | •   | ,<br>[] | • ` | •   | •   | •  | :   | •   | ÷.               | 1-16         |

|     | Processing Units                          | .•     | • •  |     | •   | •       | •   | •   | •   | •• |     |     | •                | 1 - 20       |

|     | Processing Element .                      |        |      |     |     |         | •   |     |     |    |     |     | •                | 1-21         |

|     | Processing Element Me Memory Logic Unit . |        |      |     |     | •       |     | •   |     | •  | •   | •.  | . <b>.</b><br>•. | 1-26<br>1-26 |

|     | I/O System                                | •      | • •  | ٠   | •   | •       | •   | •   |     |    | •   | •   | •                | 1-27         |

|     | B6700 I/O Control Com                     |        |      |     |     |         |     |     |     |    | •.  | •   |                  | 1-27         |

|     | ILLIAC IV Disk File Sul                   | -      |      |     |     |         |     |     |     | •  | ٠   | ٠   | •                | 1-29         |

|     | ILLIAC IV I/O Subsyste                    | erii , | • •  | •   | •   | •       | •   | •   | •   | •  | •   | •   | •                | 1-30         |

| II. | PROGRAMMING CHARACTI                      | ERIST  | ricș | . • | •   | •.      |     | •   | •   | •  | •   | • . |                  | 2-1          |

|     | Word Formats                              | •      |      | •   | •   | •       | •   |     | •   | •  | •   | •   |                  | 2-1          |

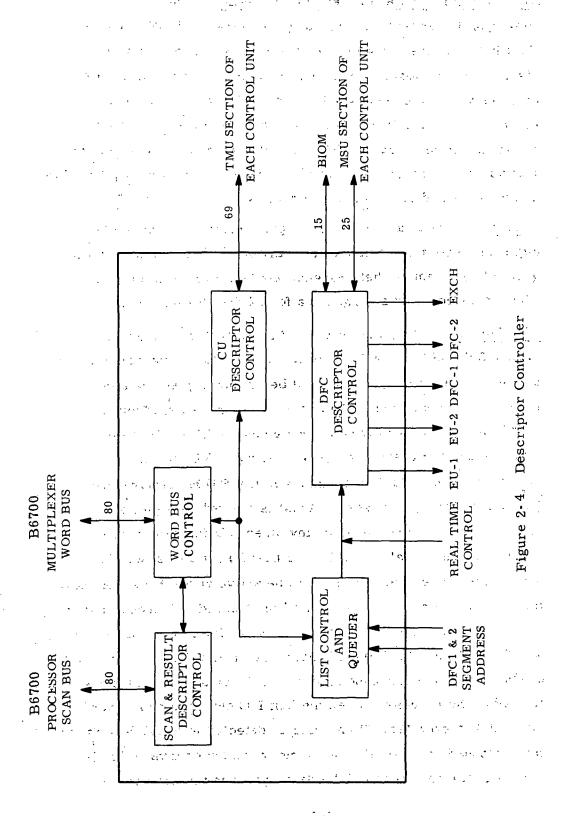

|     | Instruction Word Forms                    | ats .  |      |     |     | •       |     |     |     |    | •   |     | •                | 2-1          |

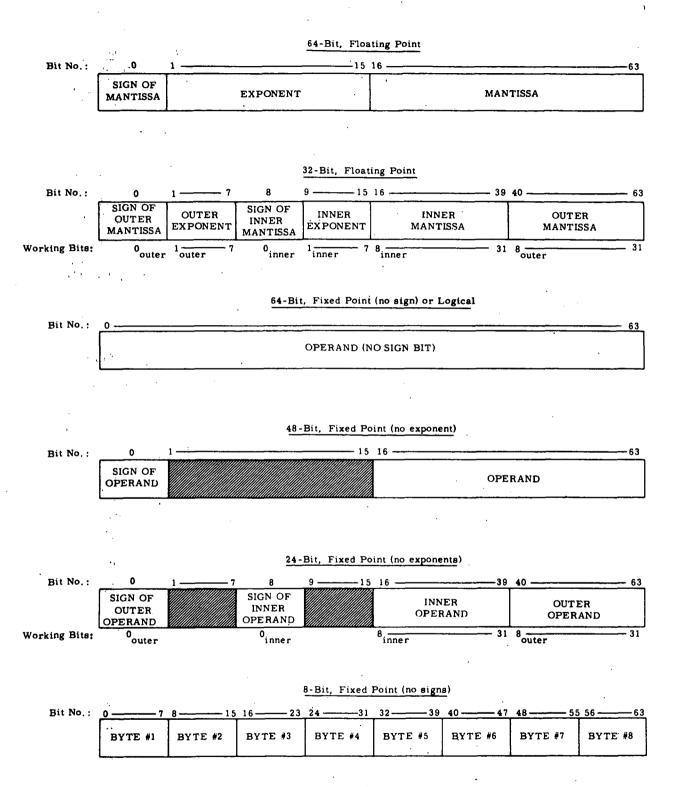

|     | Data Word Formats .                       |        |      | •   | •   | •       | •   | •   | •   | •  | •   | •   | •                | 2-2          |

|     | Notation Conventions .                    |        |      | •   |     |         |     |     | •   |    |     |     | •                | 2-4          |

# CONTENTS (CONT'D)

|      |                                                 | Page |

|------|-------------------------------------------------|------|

|      | Configuration Control Logic                     | 2-5  |

| . ~  | Forking and Joining                             | 2-11 |

|      | Basic CU Registers                              | 2-12 |

| ٠.   | Operational Control                             | 2-12 |

|      | Interrupt Handling                              | 2-13 |

|      | Interrupt, Mask, and Control Register Functions | 2-17 |

| *    | Illegal Instruction/Address Handling            | 2-20 |

|      | Input-Output Control                            | 2-23 |

| ٠,   | De la Galler Nov                                | 2-23 |

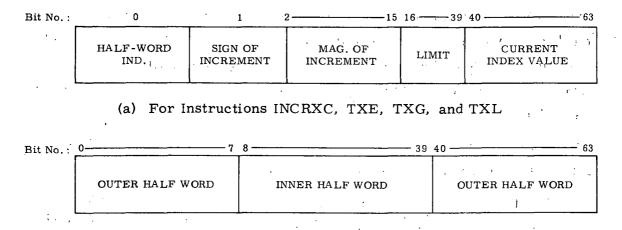

|      | Descriptor Controller                           | 2-44 |

|      | Ruffer I/O Memory                               | 2-46 |

|      | I/O Switch                                      | 2-51 |

| III. | ADVAST INSTRUCTIONS                             | 3-1  |

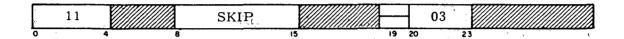

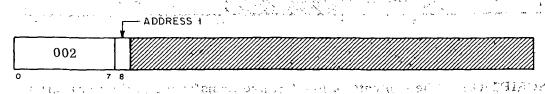

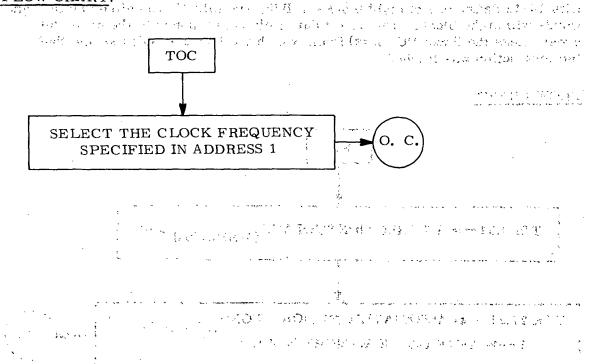

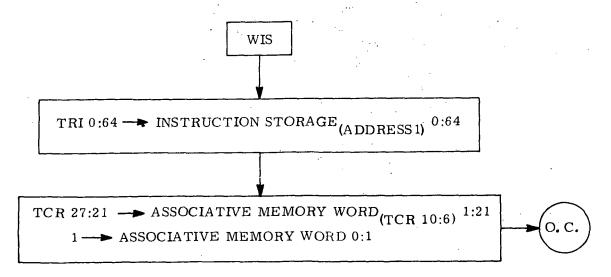

|      | Instruction Format and Field Usage              | 3-1  |

|      | ILLIAC IV Addressing                            | 3-4  |

|      | ADVAST Instruction Repertoire                   | 3-8  |

|      | ADVAST Instruction Descriptions                 | 3-11 |

| īv.  | FINST/PE INSTRUCTIONS                           | 4-1  |

| ,    | Instruction Format and Field Usage              | 4-1  |

|      | FINST/ PE Instruction Repertoire                | 4-5  |

|      | FINST/PE Instruction Descriptions               | 4-12 |

# CONTENTS (CONT'D)

计数据数据 化二氯酚 医乳腺管炎

|       |                                          | Page |

|-------|------------------------------------------|------|

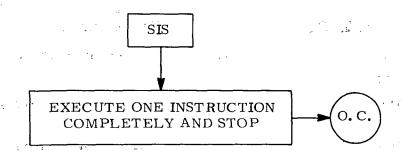

| v.    | TEST MAINTENANCE UNIT                    | 5-1  |

| ,     | Word Formats                             | 5-3  |

|       | B6700-TMU Communication                  | 5-5  |

|       | Register Address Codes and Accessibility | 5-7  |

|       | Operation of the TMU                     | 5-7  |

|       | Diagnostic Features                      | 5-9  |

|       | TMU Display                              | 5-10 |

|       | TMU Instruction Set                      | 5-15 |

| VI.   | INSTRUCTION TIMING                       | 6-1  |

| VII.  | PERIPHERAL TIMING                        | 7-1  |

|       | I/O Subsystem Timing                     | 7-1  |

|       | B6790 Peripheral Device Timing           | 7-7  |

| Appen | dix A. GLOSSARY                          | A-1  |

| Appen | dix B. INSTRUCTION INDEX                 | B-1  |

## ILLUSTRATIONS

| Figure |                                                                                            | Page |

|--------|--------------------------------------------------------------------------------------------|------|

| 1-1    | Development of Parallelism Toward Improving Program Throughput                             | 1-2  |

| 1-2    | ILLIAC IV System Configuration                                                             | 1-4  |

| 1-3    | Array Connectivity                                                                         | 1-4  |

| 1-4    | Control Unit                                                                               | 1-6  |

| 1-5    | Processing Element                                                                         | 1-10 |

| 1-6    | Control Unit Block Diagram                                                                 | 1-12 |

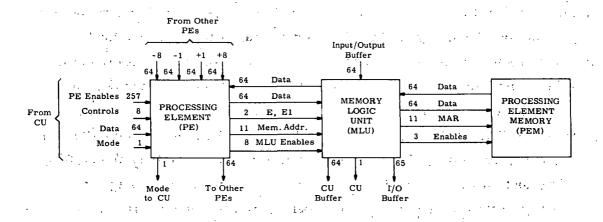

| 1-7    | Processing Unit Data Inputs and Outputs                                                    | 1-20 |

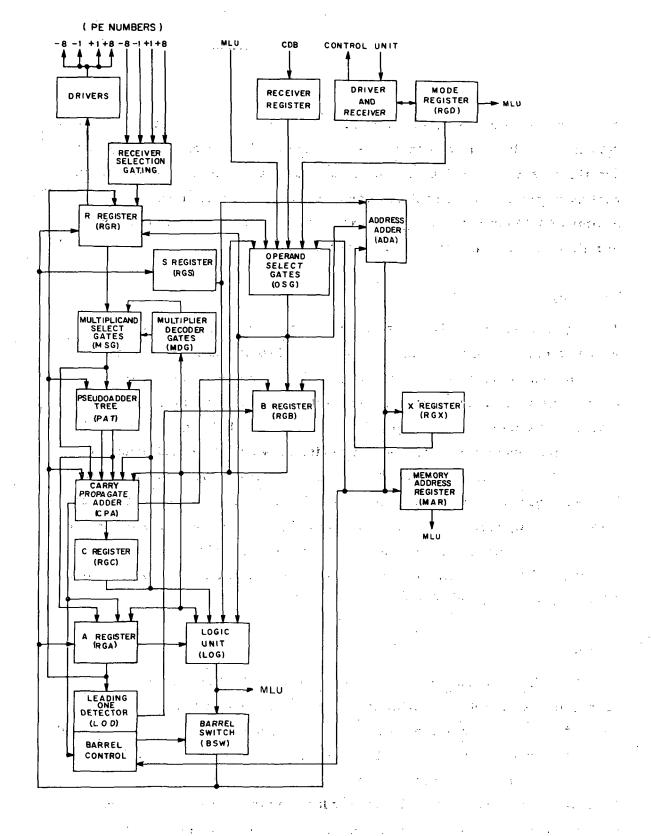

| 1-8    | Processing Element Block Diagram                                                           | 1-22 |

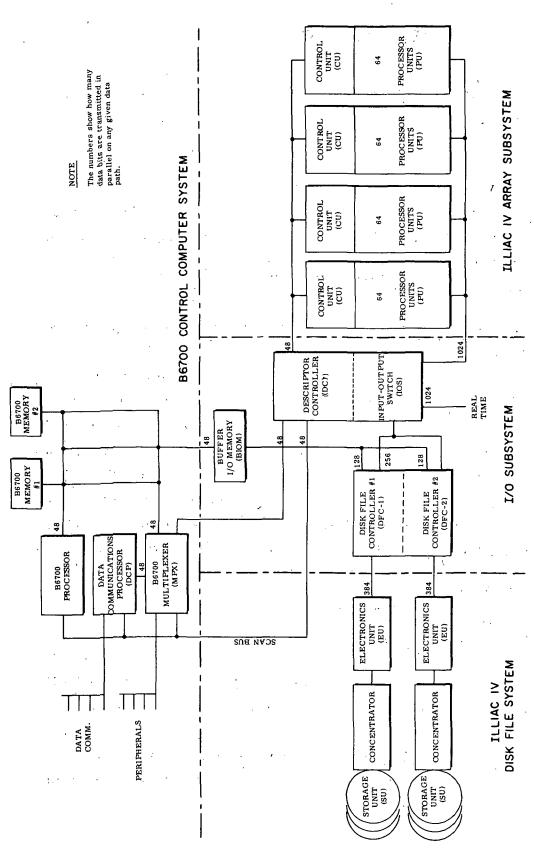

| 1-9    | ILLIAC IV Interface Diagram                                                                | 1-28 |

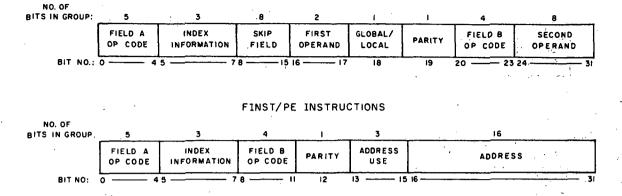

| 2-1    | Instruction Word Formats                                                                   | 2-2  |

| 2-2    | FINST/PE Data Word Formats                                                                 | 2-3  |

| 2-3    | ADVAST Data Word Formats                                                                   | 2-4  |

| 2-4    | Descriptor Controller                                                                      | 2-24 |

| 2-5    | Disk File Control                                                                          | 2-45 |

| 2-6    | Buffer I/O Memory                                                                          | 2-48 |

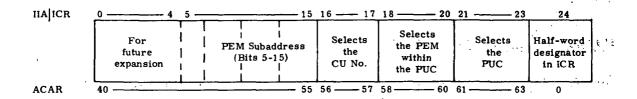

| 2-7    | PEM 32-Bit Mode Format                                                                     | 2-48 |

| 2-8    | PEM 48-Bit Mode Format                                                                     | 2-49 |

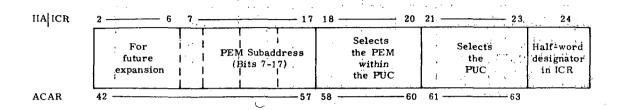

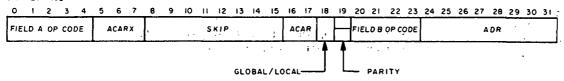

| 2-9    | 48-Bit Mode PEM Address Modification                                                       | 2-49 |

| 2-10   | I/O Switch Configuration for 1024-Bit Transfer Capability                                  | 2-50 |

| 2-11   | Possible Expansion Elements to Basic IOS<br>Configuration for 4096-Bit Transfer Capability | 2-50 |

| 5-1    | Test Maintenance Unit                                                                      | 5-2  |

| 5-2    | TMU Display Keyboard Character Set                                                         | 5-13 |

| 6-1    | FINST Overlay Structure                                                                    | 6-2  |

### TABLES

| Table |                                                                                     | Page   |

|-------|-------------------------------------------------------------------------------------|--------|

| 2-1   | Functions of Bits in Interrupt (AIN) and Mask (AMR) Registers                       | . 2-18 |

| 2-2   | Functions of Bits in CU Control Register (ACR)                                      | 2-19   |

| 2-3   | Legal/Illegal CU Addresses                                                          | 2-22   |

| 2-4   | Valid Registers for ADVAST Instructions                                             | 2-22   |

| 2-5   | Operations Specified by Instruction Field of I/O Descriptor                         | 2-34   |

| 3-1   | ADVAST Instruction Op Codes                                                         | 3-2    |

| 3-2   | CU Determination Chart                                                              | 3-4    |

| 4-1   | FINST/PE Instruction Op Codes                                                       | 4-4    |

| 5-1   | Address Codes for CU Registers                                                      | 5-6    |

| 5-2   | Bit Configurations of TCC Register and SRT Instruction<br>Data for Diagnostic Usage | 5-8    |

| 6-1   | ADVAST Instruction Timing                                                           | 6-8    |

| 6-2   | FINST/PE Instruction Timing                                                         | 6-11   |

| 7_1   | Perinheral Device Timing                                                            | 7-8    |

#### INTRODUCTION

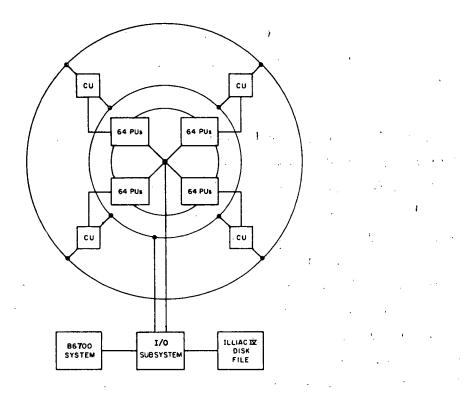

The ILLIAC IV is a large digital computing system that employs an advanced concept of parallel design to achieve a major increase in processing capacity. The nucleus of the system is the ILLIAC IV array, a matrix of 256 identical processing units and four identical control units, configured into four identical quadrants, each having 64 processing units under the direction of a control unit. These array elements perform the computational tasks for the system.

Although the user of this manual will be concerned mainly with operations internal to the array elements, he should have a working knowledge of the ILLIAC IV system as a whole. To provide this coverage, Section I is devoted in its entirety to a general discussion of the system organization and of the major units within this organization. Emphasis has been given especially to interactions between the major subsystems - ILLIAC IV array and I/O subsystem - and the disk file and B6700 control computer. Section II presents detailed information pertaining to programming characteristics. This section includes bit allocation in the internal word formats, the implementation of the configuration control logic, and the basic registers of the CU. It also includes descriptions of the Interrupt Control (including Interrupt Handling) and Input-Output Control. Section III provides a discourse and flow chart for each of the machine instructions executed by ADVAST of the Control Unit. Section IV similarly treats FINST/PE instructions executed by the array processing elements. A detailed description of the functional characteristics and instructions executed by the Test and Maintenance Unit is presented in Section V. Section VI is devoted to a discussion of instruction timing. Section VII presents a discussion on peripheral timing. A glossary of terms which includes abbreviations

frequently used throughout this manual, and a quick reference table for ADVAST, array processing element, and TMU instructions are presented in the Appendices. These quick reference tables have also been included on the inside tabs of sections III, IV, and V respectively.

17.0

#### CONTENTS

|     |         |       |       |      |      |    |     |     |   |   |     |   |   |   |   |    |   | Page |

|-----|---------|-------|-------|------|------|----|-----|-----|---|---|-----|---|---|---|---|----|---|------|

| SYS | TEM     |       |       |      |      |    |     | •   |   | • |     |   |   | • | • | •  | • | 1-1  |

|     | Syste   | m El  | .eme  | ents |      | •  |     |     |   | • |     |   |   |   | • |    |   | 1-3  |

|     | Contr   | ol U  | nit l | Fun  | etic | ns | •   | •   | • | • |     | • | • | • | • | •  | • | 1-7  |

| COI | VTROI   | L UN  | ITS   |      |      | •  |     | •   | • | • |     | • | • |   | ٠ | •  |   | 1-11 |

|     | Contr   | ol U  | nit S | Stru | c tu | re |     |     |   |   |     |   |   |   |   | ١. | • | 1-14 |

|     | Timir   |       |       |      |      |    |     |     |   |   |     |   |   |   |   |    |   | 1-16 |

|     | Seque   |       |       |      |      |    |     |     |   |   |     |   |   |   |   |    |   | 1-16 |

| PRO | CESS    | ING   | UNI'  | TS   |      | •. | •   |     |   |   |     |   | • |   |   | •  | ٠ | 1-20 |

|     | Proce   | essin | g E   | lem  | ent  |    |     |     |   |   |     |   |   |   |   |    |   | 1-21 |

|     | Proce   | essin | g E   | lem  | ent  | Me | eme | ory |   |   | ١.  |   |   |   |   | ٠. |   | 1-26 |

|     | Memo    |       |       |      |      |    |     |     |   |   |     |   |   |   |   |    |   | 1-26 |

| I/O | SYSTI   | ΞM .  |       | •    |      |    | •   | •   |   |   |     | • | ٠ | • |   | •  | • | 1-27 |

|     | B6700   | ) I/O | Co    | ntro | 1 C  | om | pu  | ter |   |   |     |   |   |   |   |    | : | 1-27 |

|     | ILLIA   | C IV  | Di:   | sk I | ile  | Sy | ste | em  |   | • | . • |   |   |   |   |    | • | 1-29 |

|     | II.I.IA |       |       |      |      |    |     |     |   |   |     |   |   |   |   |    |   | 1-30 |

# SECTION I SYSTEM CHARACTERISTICS

#### SYSTEM

ILLIAC IV is a milestone in computer development in that it provides a level of parallel processing many times that of conventional designs. To achieve this, a new and fundamentally different approach is used. For important classes of problems many repetitive loops of the same instruction string are executed with different and independent data blocks for each loop. Parallelism may be applied here by using N computers, each executing the identical program concurrently on separate data blocks. This improves execution time by a factor of N for that program. Similarly, since each computer is executing the identical program, much of the control logic of the computers could be made common. This is the fundamental proposition of the ILLIAC IV computer.

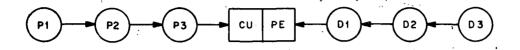

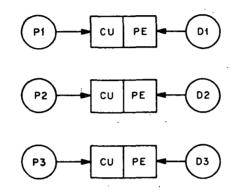

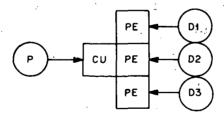

Figure 1-1 shows a three-step evolution from conventional design to the ILLIAC IV. The top schematic (Figure 1-1a) shows three identical program loops (P1, P2, P3) operating on three different data blocks (D1, D2, D3) in series. The block element shown is a computer, without input-output or memory, that is functionally separated into a control part (CU) and an execution part (PE). Figure 1-1b shows a simple application of parallelism that produces a threefold increase in throughput. The final schematic, Figure 1-1c, shows the ILLIAC IV approach with its simplifications and economies over the above method.

a. Conventional Computer

b. Improved Throughput by Paralleling

Identical Processors

c. ILLIAC IV Approach, Using Common Control Logic and Parallel Identical Processors

Figure 1-2. Development of Parallelism Toward Improving Program Throughput

The ILLIAC IV has a distributed memory system which allows each execution element uninhibited access to an assigned data block within its own memory. If a conventional, centralized memory were used, much time would be wasted in routing data to and from such a memory.

#### SYSTEM ELEMENTS

The five major elements of the ILLIAC IV are the Control Unit (CU), the Processing Unit (PU), the Input-Output (I/O) Subsystem, the Disk File, and the B6700 Control Computer. Each PU is a combination of a Processing Element (PE), Memory Logic Unit (MLU), and Processing Element Memory (PEM). A CU directly governs 64 PUs configured in an array as illustrated in Figure 1-2. In the ILLIAC IV system there are four such identical arrays called quadrants, making a total of four CUs and 256 PUs. Quadrants may function separately or in combination with one another.

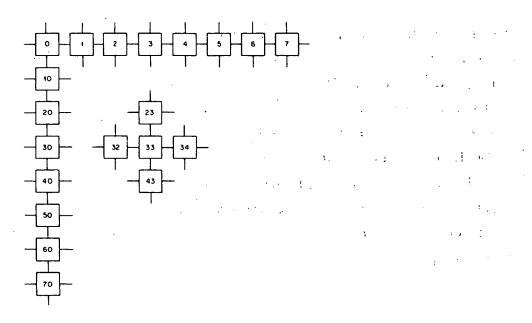

Each PU is labeled with a unique three-digit octal number, the first octal position identifying the quadrant number and the second two positions the PU number within a quadrant. The four "nearest neighbor" connections within the array are defined in terms of direct, parallel, word transfer paths between one PU and others having assigned labels differing by plus and minus eight, and plus and minus one, from the value of the connected PU's label (Figure 1-3). Thus for example, PU 033 can transfer directly to PUs 023, 032, 034, and 043. This connectivity is maintained for both separate and joined quadrants, and enables a variety of physical images to be modeled – for instance, weather maps – by means of a combination of these transfer paths. All CUs have full-word data interconnections for programs that operate in a multiquadrant mode.

The Burroughs parallel disk file is the principal secondary storage element, the main storage being furnished by the PEMs. The disk file provides a storage capacity of  $79 \times 10^6$  bits per Storage Unit and has a transfer rate of  $502 \times 10^6$  bits per second. Data is routed in and out of the disk files through

Figure 1-2. ILLIAC IV System Configuration

Figure 1-3. Array Connectivity

the Input-Output (I/O) Subsystem which includes the Descriptor Controller (DC), the I/O Switch (IOS), the Buffer I/O Memory (BIOM), and the Disk File Controller (DFC).

The final unit of ILLIAC IV is a B6700 control computer system which serves as the principal managing element for ILLIAC IV. Resident in this system are executive control, facility allocation, peripheral-equipment control, I/O processing and initialization, fault recovery, and program assembly. The linkage between the B6700 system and the Control Units is via the I/O subsystem, as shown in Figure 1-2. It is this link that the B6700 uses to initialize the state word in each CU, that is, setting the initial value of the program counter, the control state, and array configuration. The array configuration identifies the quadrants that are working jointly on the same program and the quadrants, if any, that are operating independently. The B6700 also generates controls to initiate the transfer of program and operands from disk to array memory before allowing the CUs to proceed with program execution.

To effect a data transfer, the B6700 supplies the DC with a start address and the number of words to be transferred. The DC then sends an intermediate memory address to the CU and the disk file to initiate the transfer. Data transfers are made directly between disk and the PEMs. Once the required number of instructions and operands have been transferred from disk, the CU will begin program execution by sending an instruction fetch to the PEMs. Operation then proceeds in the conventional manner, under control of the program stored in the PEMs. Instructions as well as operands may be transferred across quadrant boundaries, so they need be stored only once, regardless of the configuration.

Figure 1-4. Control Unit

#### CONTROL UNIT FUNCTIONS

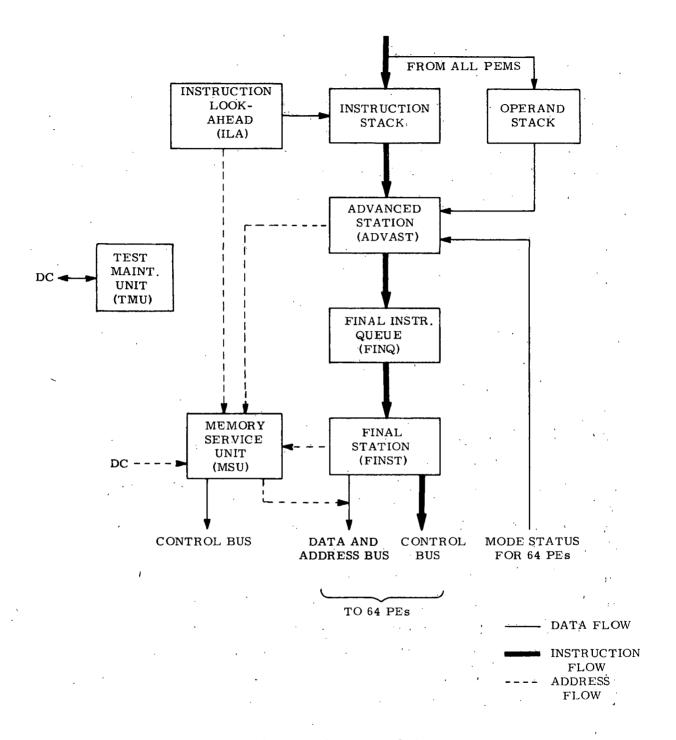

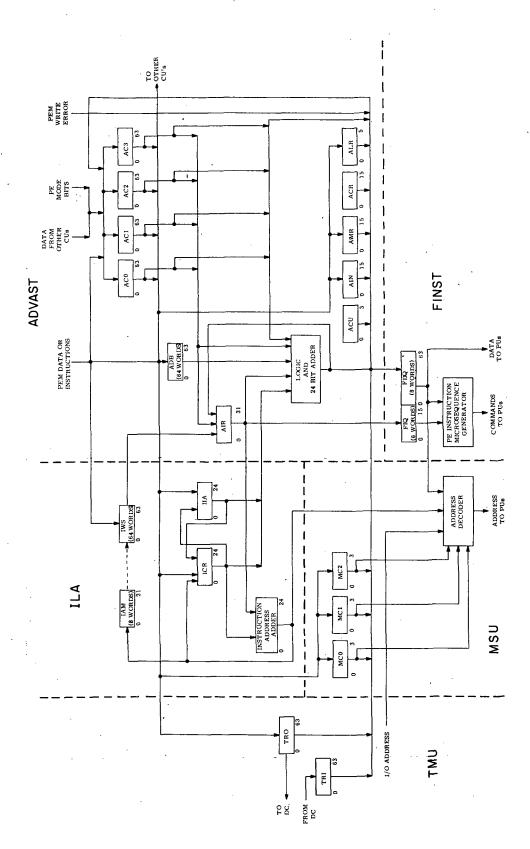

The Control Unit is that portion of the computer system which performs the initial processing of instructions up to and including the generation of instruction microsequences for a step-by-step control of the Processing Element. Figure 1-4 is a general block diagram of this single cabinet unit. Contained within the CU are five operating sections which perform specialized processing tasks on a semi-independent basis: Instruction Look-Ahead (ILA), Advanced Station (ADVAST), Final Station (FINST), Memory Service Unit (MSU), and Test Maintenance Unit (TMU).

The Instruction Look-Ahead (ILA) fetches instruction words in 8-word blocks from array memory, placing them in a 64-word content-addressable memory which serves as an instruction word stack. Individual instruction blocks are assigned locations by an associative memory which holds all but the four low-order bits of the instruction addresses. To access a word in the stack, the instruction counter in ILA sends the instruction address to the associative memory to locate the proper 8-word group in the instruction stack, and then the four low-order bits will select the appropriate instruction. Program loops of up to 128 instructions can be contained within the instruction stack.

From the instruction stack, instructions are fed in turn to the Advanced Station (ADVAST), which is the principal housekeeper of the system. Such functions as address arithmetic, loop control, mode control, interrupt processing, and configuration control are performed here. The hardware complement of ADVAST consists of a 64-word operand stack, four full-word accumulators, and a combinatorial logic unit, the latter used to perform functions such as adds, compares, shifts, bit testing, etc. ADVAST permits all those functions generally associated with program control to be performed concurrently with, but in advance of and separate from, the main processing activity.

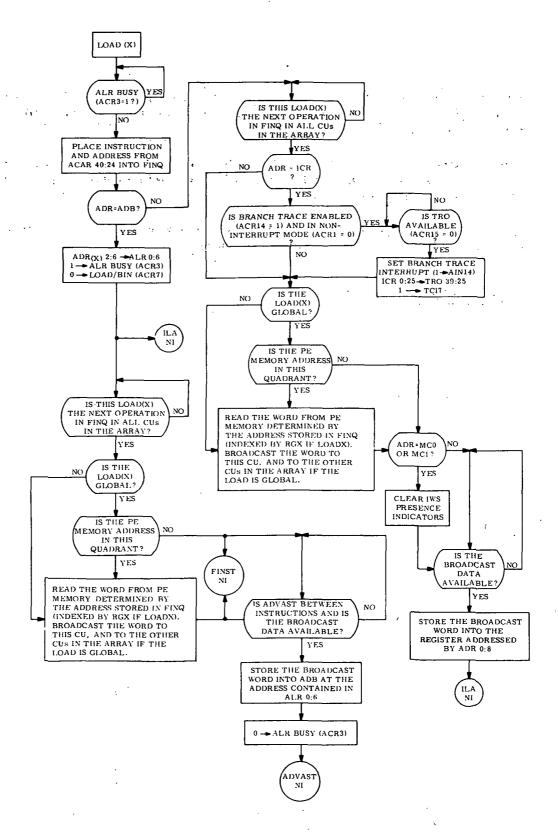

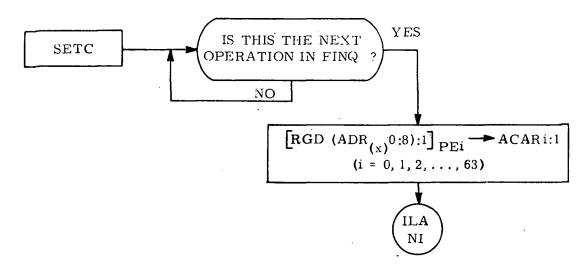

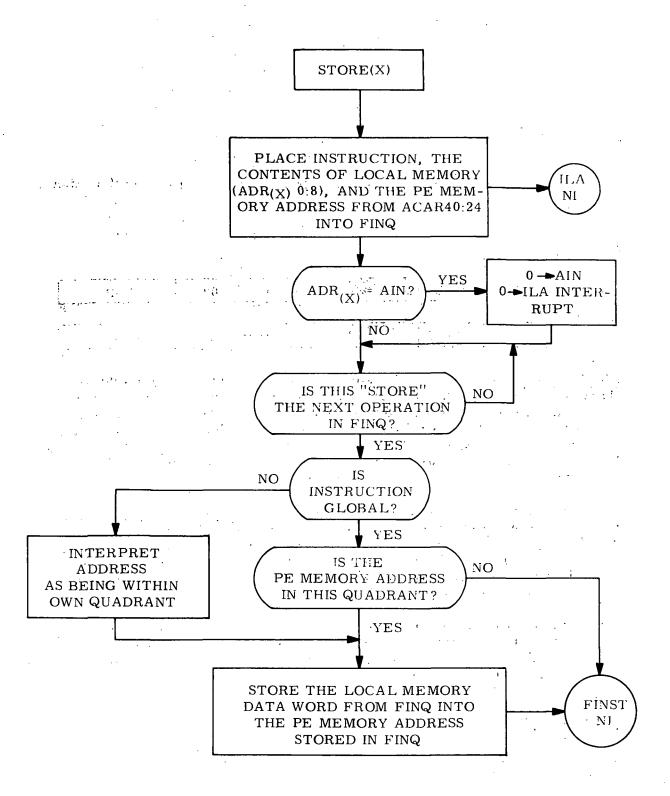

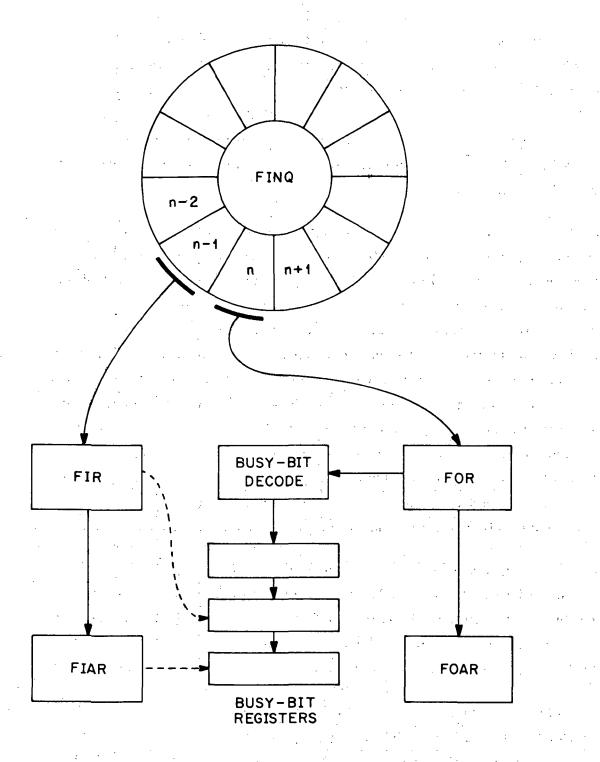

The primary function of the Final Station (FINST) is to act as an intermediary between the main control, in ADVAST, and the 64 array elements, called Processing Elements (PEs). The repertoire for ILLIAC IV has two general categories of instructions: those executed at ADVAST and those executed in the array elements but controlled by FINST. Since all instructions are first at ADVAST, those instructions intended for execution at FINST are transferred to FINST through the Final Queue (FINQ). This latter element is composed of eight instruction storage positions, which perform a time-smoothing function between ADVAST and FINST. FINST decodes each instruction into control microsequences, which are then broadcast to 64 array elements over a common control bus. FINST also broadcasts full-word operands, shift counts, test values, and other common array parameters on a data bus. In actual operation, the timing sequences of FINST and the 64 array elements are lock-stepped, except for the fixed transmission delay of the intervening control bus.

The Memory Service Unit (MSU) resolves the conflicts of the three users of array memory: I/O, FINST, and ILA. It also transmits the appropriate address to memory and exercises control over the memory cycle. As a hardware expedient, the addresses are transmitted over the same common data bus mentioned above.

The Test Maintenance Unit (TMU) provides the control channel to the Control Unit from the B6700 and the manual maintenance panel.

The array element, or PE, is the execution portion of the configuration depicted in Figure 1-1c. This unit is devoid of all independent control with the exception of mode and some data-dependent conditions. Mode control permits a PE to accept or ignore a broadcast control sequence from the CU, dependent on its current status. The PE is essentially a four-register

arithmetic unit, as shown in Figure 1-5, capable of executing a full repertoire of instructions having 64-bit, 32-bit, or 8-bit operands. Further, operations involving 64-bit and 32-bit words can be done in either fixed-point or floating-point representation.

An arithmetic unit in the PE combines a carry-save adder tree and parallel adder with carry look-ahead logic to give a floating-point multiply time on the order of 450 nanoseconds and a floating-point add time of 250 nanoseconds. Both times include post-normalization. Other logic elements include a barrel switch for rapid data-shifting, a leading-one's detector, and a logic unit for Boolean operations. Instruction operands may originate in any of the PE registers, the common data bus, the nearest orthogonal neighboring PEs, or the array memory.

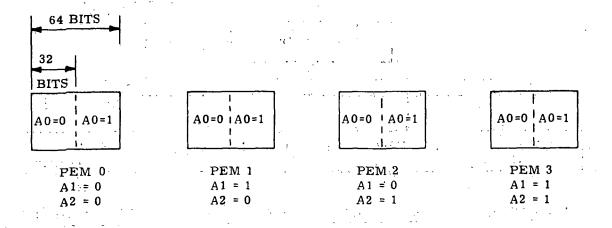

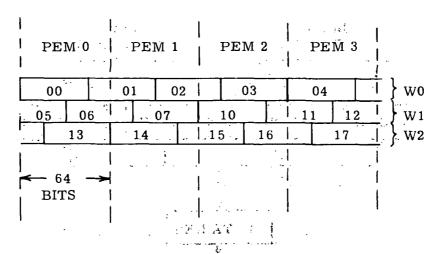

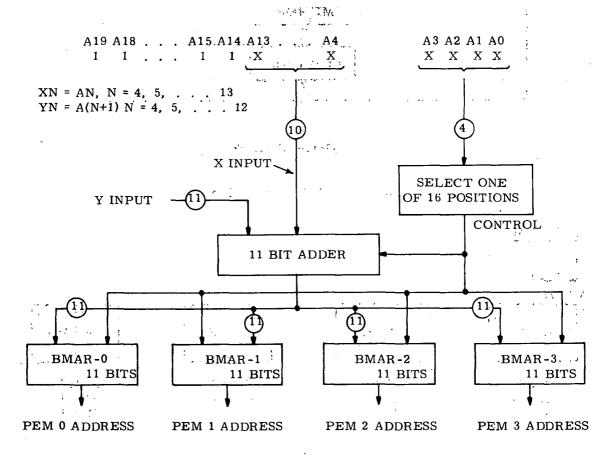

The array memory consists of 64 independent memory modules, called the Processing Element Memory (PEM). Each PEM is collocated with and assigned to a specific PE, providing storage for 2048 words of 64 bits each. The memory is designed for a 250-nanosecond read or write cycle. Memory addresses are supplied to the PEM from the memory address register located in the PE. An address adder and an index register within the PE permit memory indexing and addressing independent of FINST control. Such independence provides important flexibility for addressing data stored in a variety of ordered forms.

Figure 1-5. Processing Element

#### CONTROL UNITS

Each Control Unit (CU) directly controls a subarray of 64 Processing Units (PU) in a quadrant. Four identical quadrants, or a total of four CUs and 256 PUs, comprise the ILLIAC IV system. Associated with each subarray of 64 PUs are certain common registers and logical elements which can be manipulated by instructions; decoding of instructions for the Processing Elements (PE) of the PUs is also common. Both the decoding functions and the common registers and logic are contained within the CU. In the performance of its primary task the CU manipulates two types of instructions in the instruction stream: those which it decodes for specifying commands to the PEs – called FINST/PE instructions – and those which control the internal operation of the CU – called ADVAST instructions. A block diagram showing the principal logic elements of the CU is given in Figure 1-6. A block diagram of the CU showing the general relationships of its main functional areas appeared previously as Figure 1-4.

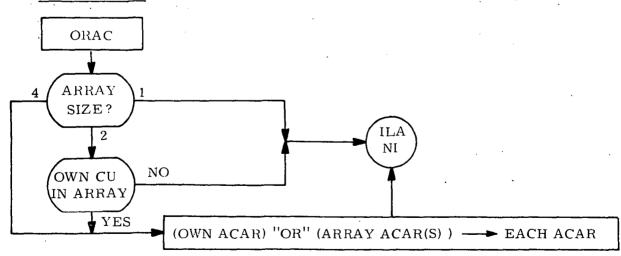

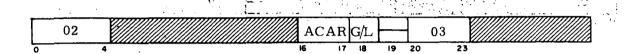

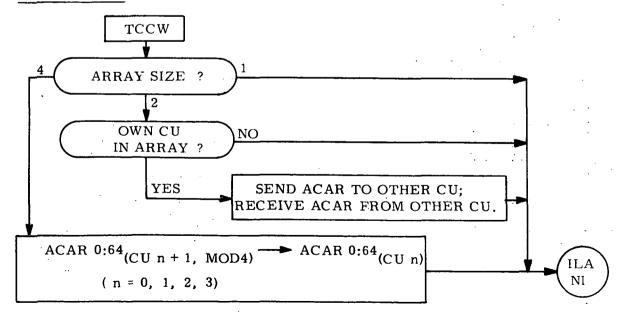

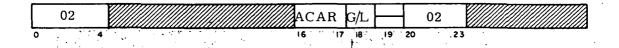

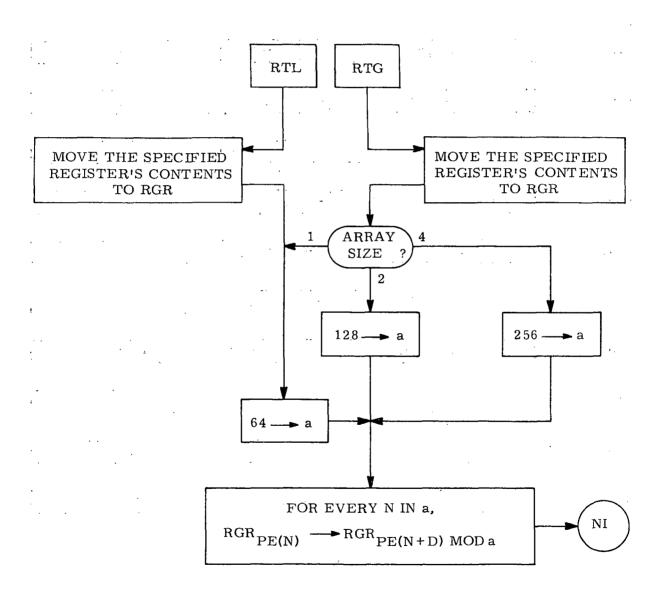

CUs may function individually to control single quadrants (64PUs) or in arrays of two (128 PUs), three (192 PUs), or four (256 PUs) quadrants. When operating in parallel, the CUs specified by the array size control register (MC0) will receive identical program instructions during fetches from array memory. The program instructions will be fetched from that portion of array memory controlled by the CUs specified by the instruction fetch register (MC1). Program instructions which are independent of array size, such as COR, CADD, ADD, CHSA, etc., will be executed by all of the CUs specified by MC0. However, program instructions which are array size dependent, such as LOAD, TCW, RTG, etc., will be executed by the array whose CUs are specified by the instruction execution register (MC2). Thus, the individual CUs will execute identical instructions in parallel, but in combination will appear indistinguishable from a single control unit having 64, 128, 192, or 256 processing units assigned to it. Note that three-quadrant operation is restricted by the MC1 and MC2 control bits, which may not specify three quadrants.

Figure 1-6. Control Unit Block Diagram

A CU shares the same physical array memory (PEMs) with the PEs in its quadrant. The Memory Service Unit (MSU) of the CU determines which PEMs shall be addressed for various memory operations according to the type of memory request received. For example, FINST/PE instructions which involve memory access require that all 64 PEMs of the quadrant must be addressed, whereas the ADVAST instruction BIN requires that only eight specific PEMs of the quadrant be addressed (see Section III, ILLIAC IV Addressing). The various users of array memory include in their memory request to the MSU the following number of bits to identify which PEMs are to be addressed:

| FINST/PE           | - | non€ |  |  |

|--------------------|---|------|--|--|

| I/O                | - | 2    |  |  |

| ILA                | - | 3    |  |  |

| ADVAST (via FINST) | - | 6    |  |  |

Program steps are fetched in blocks from memory, and executed one at a time. Although there is rather extensive machinery in the CU to reduce the actual number of memory fetches from one fetch per program step, as in conventional machines, to 0.0025 or 0.015 fetch per instruction, this machinery requires no attention on the part of the user programmer.

The registers in the CU which can be manipulated by the program are as follows:

ACO, AC1, AC2, AC3 - A set of 4 registers, 64-bits each, general purpose accumulators (ACARs)

<u>ACR</u> - ADVAST control register, which contains CU status information (read only)

ACU - Own quadrant number register (read only)

$\overline{\text{ADB}}$  - A set of 64 registers of 64 bits each, used as a scratch-pad  $\overline{\text{memory}}$

AIN - ADVAST interrupt register

AMR - ADVAST interrupt mask register

ALR - A register which holds the address of pending memory fetches

MC0, MC1, MC2 - Array configuration control registers

IIA - ILA interrupt storage for ICR

ICR - ILA instruction counter

TRI - TMU input register (read only)

TRO - TMU output register.

#### CONTROL UNIT STRUCTURE

As noted previously, the order code has two general types of instructions, those used primarily to control the internal operations of the CU, called ADVAST instructions, and those that are used primarily to control PU operation, called FINST/PE instructions. Since there is almost no interaction between the two instruction types, they can be viewed as two interlaced but distinct instruction streams. The hardware of the CU takes advantage of this partial independence to execute the two streams independently but concurrently with one another. The CU has five main functional areas, as follows:

Instruction Look Ahead (ILA). The instructions are fetched, in 8-word blocks of contiguous code, to a section of the CU called the instruction look-ahead (ILA). An associative memory (IAM) detects which blocks of instruction are currently in ILA storage. The instruction counter (ICR) is also contained in ILA.

Advanced Station (ADVAST). Each instruction is passed in sequence to the instruction register (AIR) of ADVAST. In ADVAST, each instruction is first examined to determine whether it is an ADVAST instruction (to be executed exclusively in ADVAST) or a FINST/PE instruction (to be executed by the PEs). FINST/PE instructions

will be indexed, if required, within ADVAST and then placed in the final queue (FINQ) for execution by the PEs. Some instructions (e.g., BIN, LOAD) may require additional processing in ADVAST after they have been executed by the PEs.

Final Station (FINST). Instructions from ADVAST enter a section of the CU called the final station (FINST), the outputs of which manipulate the Processing Units. Instructions enter FINST through a final queue (FINQ) so that the instruction execution time at FINST is decoupled from that at ADVAST. Some instructions (e.g., LOAD) are executed partially at ADVAST and partially at FINST because of the need for PU operations to complete instruction execution. In general, the programmer need not be aware of overlap operation between the two sections, if it occurs.

Memory Service Unit (MSU). The memory service unit (MSU) receives requests for access to memory from three sources: from FINST, from ILA, and from the Descriptor Controller (DC) of the I/O subsystem. The MSU resolves conflicts among the three sources as well as conflicts concerned with other FINST uses of the common paths from CU to memory. ADVAST memory requests are serviced through FINST.

e, Not origined for

Test Maintenance Unit (TMU). The Test Maintenance Unit (TMU) of the CU contains registers TRI and TRO (which are addressable by instructions in ADVAST) and provides paths to the maintenance panel, the display, and the B6700 (via the DC). The display will, on external command, indicate the state of certain CU registers. A portion of TMU serves as a "test instruction" register for diagnostics, testing, and initialization.

#### TIMING CONSIDERATIONS

Potential program difficulties are introduced by the asynchrony between ADVAST and FINST since ADVAST may be executing instructions which occur later in the instruction stream than those which are in FINQ awaiting execution. The hardware automatically detects this potential problem and introduces the necessary synchronism to prevent any difficulty. The only exceptions are bits ACR(09) and ACR(13). A change in either of these bits is effective immediately, even on any previous instructions which may remain unexecuted in FINST. If this presents a problem, an instruction "FINQ" may precede the CACRB which changes ACR(09) or ACR(13). On the other hand, changes in ACR(10), word size, are synchronized; only those FINST/PE instructions which follow a CACRB(10) instruction will be executed with the new word size. Other cases of asynchronism are also found. For instance, the effects of some interrupts, such as arithmetic fault interrupts, are somewhat delayed in reaching the interrupt register, AIN; they may halt the program several instructions after the one which cause the interrupt. Also, STORE instruction, whose address is in the program area, will not change the execution of the program if the instruction in ILA were fetched before the STORE was effective in memory.

#### SEQUENCE OF OPERATIONS

The operation of the ILLIAC IV system is somewhat complex due to the close coupling of intraquadrant operations and the largely decoupled operation of interquadrant functions. Superimposed on this structure are communications with the B6700 and the DC, which can be considered as being asynchronous with the ILLIAC IV system itself. The program flow described here traces the actions of the various system components during the execution of a program.

#### System Start-Up

Upon receipt of a job request, the B6700 transfers the program and data base to the ILLIAC IV disk system. The quadrants of the system which will be used by the program are than selected, and a command issued to the TMU section of the selected CU(s) causing operation to halt and initialization for the new program to proceed. Then, by issuing commands to the DC, the B6700

initiates the loading of the disk-held program and data to the appropriate array memory locations. Following the loading operation, the B6500 sends commands to the TMU(s) which will start program execution after setting the instruction counter (ICR) in the ILA section to the address of the first program instruction.

#### Fetching the Program

During initialization, the instruction look-ahead unit (ILA) is set to indicate that there are no instructions in its instruction word storage (IWS). Immediately upon start-up, the ILA will recognize this condition and request a block of instructions – via the MSU'- from the PE memories that contain the instruction addressed by the ICR.

The IWS acts as an instruction queue for ADVAST. It holds up to 128 instructions which are fetched in blocks of eight words, two instructions per word (16 instructions per block). Eight of these blocks are stored in IWS.

The conditions for initiating the fetch of a new block of instructions are, either ICR has changed or the instruction currently being executed is one of the last eight instructions in the block and the next block of instructions to be executed is not found in IWS. A ring-of-eight counter is used to implement a first-in-first-out discipline on the eight blocks of instructions in IWS. Thus, the instruction block which will be overlayed by the newly fetched instruction block is the oldest block in terms of the time at which the blocks were fetched from array memory. If, however, the block presently being executed is the oldest block (an exceptional case), the ring-of-eight counter is incremented a second time such that the next oldest instruction block will be overlayed.

#### ADVAST Processing

As noted previously the primary function of ADVAST is to handle the house-keeping tasks for the quadrant. From a programming point of view, FINST and the PEs perform the "inner-loops" of a program while ADVAST handles most of the "outer-loop" and control functions. Included in its tasks are the processing of exception conditions, decision-making for interquadrant transfers, and the handling of interrupts.

When ILA holds the instruction addressed by the ICR, the instruction is sent to the ADVAST instruction register (AIR) which determines whether it is a FINST/PE instruction or one that ADVAST will process. FINST/PE instructions are passed on to the final queue (FINQ) to await execution by FINST and the PEs, whereas ADVAST instructions remain in the AIR while they are being executed.

The ADVAST registers ACAR are primarily index/limit/increment registers that are used to supply addresses for PE instructions, but can also be used as accumulators for performing logical functions such as decision making and data formatting. The ADVAST data buffer (ADB) is used in conjunction with the ACARs in data formatting and information broadcasting to the PEs. The other registers controlled by ADVAST are manipulated to effect program sequencing and control.

#### Final Station Processing

FINST accepts instructions from ADVAST and places them in the final queue (FINQ), which is composed of an instruction queue (FIQ) and a data queue (FDQ). FDQ holds the address values or data associated with the instruction in FIQ. The eight locations in FINQ are serviced on a first-in, first-out basis. It is FINQ that permits the concurrent operation of ADVAST and FINST.

Instructions are taken from FINQ in largely undecoded form, for execution in the PE. FINST decodes these instructions into sets of microsequence commands for the array of 64 PUs. In some cases synchronism with other quadrants in an array is required and is also accomplished in this process. The generated microsequences contain the individual enable signals that control the information flow – both in direction (register to register) and in time – within the PUs. The generated microsequences are then broadcast to all of the PUs selected to accomplish the execution of the instruction.

#### Communication and Input-Output

Following the completion of processing on a block of data, additional data and/or program, or the output of the processed data, may be required for subsequent operations. Since the system has no input-output commands of its own, the CU can place a request code in its TMU output register (TRO) to interrupt the B6700 for servicing. This may be accomplished in either of two ways.

- 1. TRO loaded interrupt TCI 04: occurs when a word is loaded into the TRO. The word is generated and loaded into the TRO programmatically.

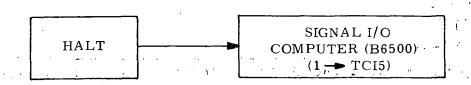

- 2. CU halted interrupt TCI 05: occurs when the CU has processed a HALT instruction. The HALT instruction causes the CU to complete current operations and then wait for further instructions.

In either case, the B6700 reads the interrupt, via the DC, and interprets its meaning. Numerous methods are available to the B6700 control program to assume control of the array (see Section V, B6700-TMU Communications).

#### Other CU Functions

Other CU functions are largely ADVAST controlled. Synchronism requirements are delineated in the individual instruction descriptions and are accomplished at either ADVAST or FINST, depending on the instruction set. The Configuration Control description in Section II details the grouping of quadrants into arrays and the synchronism that this implies. The interrupt system is described under Operational Control in Section II, which explains in more detail the uses and effects of the associated registers. The content of the control registers is also described so that the features for programming utility and service routines are available to the systems programmer.

#### PROCESSING UNITS

The Processing Unit (PU) functions as a general purpose computer under the direction of an ILLIAC IV Control Unit (CU). All of the 256 Processing Units in the ILLIAC IV system are electrically, mechanically, and functionally identical, each PU consisting of a Processing Element (PE), a Memory Logic Unit (MLU), and a Processing Element Memory (PEM). Data inputs to and outputs from the PE and PEM are shown in Figure 1-7.

٠,

Figure 1-7. Processing Unit Data Inputs and Outputs

For control, the PE and PEM receive enable signals from the CU for the sequential enabling of data paths and logic during instruction execution and for controlling the reading and writing in the PEM. In addition, the CU

monitors the control status of the PE by using one input and one output of the PE mode logic. Similarly, it monitors the memory protect error status of the PEM by using one input and one output of the MLU.

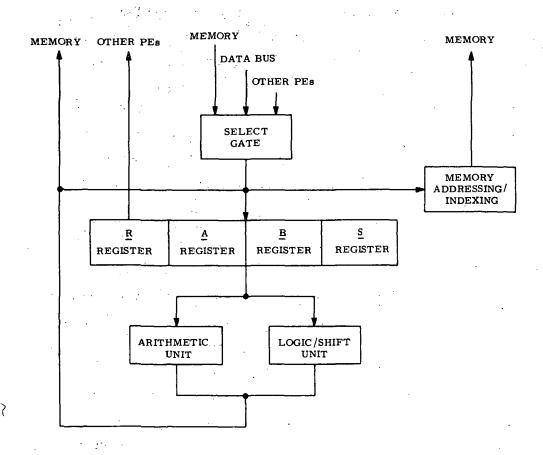

#### PROCESSING ELEMENT (PE)

The portion of the PE in which data manipulation is carried out is shown in Figure 1-8. The principal registers are the five 64-bit data registers, called the A, B, C, R, and S registers, the 16-bit indexing register, called the X register, and the 16-bit memory address register. For speed in addition, multiplication, and shifting, the logic gating is structured for register-length parallel operation. Although devoid of many of the controls usually associated with the conventional processing unit, the PE, under main control of the FINST portion of the CU, can execute a full complement of instructions involving arithmetic and data manipulations. Various instructions allow the use of 64-bit or 32-bit word sizes, in fixed-point or floating-point representation, or combinations of 8-bit bytes using unsigned notation. All operations are fully synchronized in the PE using a clock supplied to it from the CU. A receiver-retiming register accomplishes this function, synchronizing the controls with this clock before they are buffered for distribution within the PE. Although most of the controls originate externally to the PE, some data-dependent controls, such as used in normalization and signed-arithmetic operations, are generated within the PE.

#### Registers and Logic

#### Data Registers

The five 64-bit data registers are A, B, C, R, and S. The A register functions as an accumulator, holding one of the operands in arithmetic operations and receiving the output of the adder at the conclusion of the operation. The B register holds the second operand in arithmetic

Figure 1-8. Processing Element Block Diagram

operations (with the exception of multiply) and communicates most directly with external data via the operand select gates. The C register is used in certain instructions to save carries from the adder. The R register is the routing register, used principally for communications with other PEs, and at times for temporary storage of operands. The S register is used for programmatic storage of an operand within the PE.

#### Mode Register

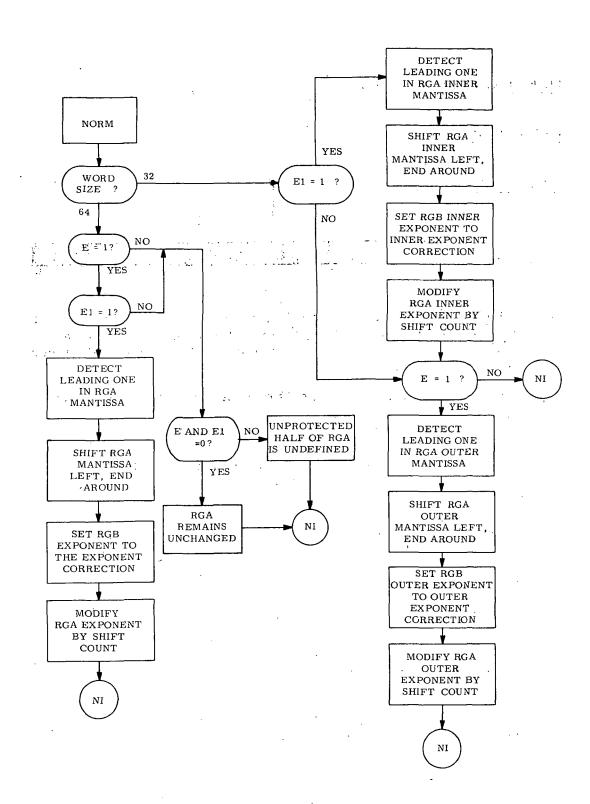

This register contains eight bits which control some of the operations in the PE and store the PE faults and test results. Two of these bits, E and E1, called enable bits, are used to protect the A register, the S register, and the memory information register (MIR) by controlling the gating of clocks to the outer (bits 0-7, 40-63), and inner (bits 8-39) half-words. The E bit alone also protects the 16-bit X register, which is the PE index register. In 32-bit mode, E and E1 are independent; however, in 64-bit mode, E should equal E1. The two F bits (F and F1) are used to store faults (underflow, overflow, etc.). The other four bits (G, H, I, and J) are used primarily for temporary storage of test results and can be manipulated in conjunction with the E's and F's. By instruction, any one mode bit may be sent from the CU or any one mode bit may be sent to the CU.

#### Shifting

A 64-bit, right shifting, end-around shift network, called the barrel switch (BSW), is used in the PE. With the logic unit to select the input and with full distribution of the output, the BSW allows generalized, one-clock-period shifting of registers in the PE. BSW control is extensive to allow 64-bit or 32-bit words to be shifted left, right, end-off or end-around. Inputs to the BSW control include shift amounts calculated by the address adder (ADA), fixed amounts required in certain instructions, and variable amounts derived

from operands to be normalized or aligned. The normalization amount is generated in a fast, parallel logic network, called the leading one detector (LOD). From the output of the A register, the LOD finds the position of the most significant nonzero bit in the 48-bit or 24-bit mantissa and generates both the shift controls for the BSW and a binary number to be used for exponent correction.

#### Adding and Multiplying

The requirements for the utmost speed in the addition and multiplication instructions demand a fast parallel adder. The one chosen can function as either a carry propagating adder using three levels of look-ahead, four bits in the first group, four groups in the second section, and four sections in the final level (achieving a 64-bit sum in a single clock period), or as a carry save adder. To distinguish this adder from the other adders, it is called the carry propagating adder (CPA) in spite of its dual purpose.

Eight-bit byte gating allows the interruption of carry propagation for 8-bit mode, and a carry register allows the saving of carries for use in the multiplication sequence.

For speed in multiplication, the eight least significant bits of the multiplier are decoded for each iteration and the proper multiples of the multiplicand are generated by the multiplicand select gates (MSG) which are added in a quadruple layer of parallel carry save adders (CSA) with the CPA acting as the fourth CSA. This logic accomplishes a single multiplication iteration, but without full carry propagation, in one clock time.

#### Addressing

The 16-bit address adder (ADA) has inputs selected from among the X register, the S register, and the operand select gates (OSG). Sums may be sent to the X register, to the 16-bit memory address register (MAR), and to the BSW controls. The sum output is also sent to the OSG, but is used only for transfers from the X register. With these data paths, all shift

counts and memory addresses are indexable by either the X or S register, and the X register may be modified with the ADA.

Figure 1-8 shows that the portion of the PE used for memory addressing is largely separated from the remainder of the PE. The sending of a memory address over the common data bus through the OSG and the ADA (where it may be indexed) into the MAR may be overlapped with any instruction not using this part of the PE. This feature is valuable in decreasing PE or CU idle time caused by waiting for information from memory, which takes approximately seven clock times to complete one memory cycle.

#### Instructions

The instruction set of the PE is that of a large scale, general purpose digital computer. Floating point arithmetic in both 64-bit and 32-bit words is provided with options for rounding and normalization. Full word operations, 8-bit byte operations, operations ignoring exponents, operations using exponents only, and operations ignoring the signs are provided in the arithmetic group. A full set of tests is generated by making all registers addressable and providing all possible comparisons. Test results are set into a mode bit which may then be used to programmatically direct the flow of the instructions. Swaps of parts of 32-bit words, bit manipulation, shifts and logical operations complete the instruction set.

#### Control

The PE is driven by a control unit to execute the instruction string contained in the CU. The PE does not receive the raw instructions but rather the fully decoded controls for the enabling of data paths and internal control of the PE as in a microprogrammed computer. While many of these external control inputs are used directly, some must be modified according to the data in the PE. Extensively used modifiers include the mode bits E and E1, the signs of the A and B registers, and the output of the LOD.

There are a few internal control signals of the PE which are generated in conjunction with data dependent operations such as multiplier decoding and mantissa normalization. These will be formed in the PE and are timed to coincide with external controls.

## PROCESSING ELEMENT MEMORY (PEM)

Contract Contract

The PEM provides a high speed random access storage function for the ILLIAC IV Processing Unit (PU), of which it is a subunit. The other subunits of the PU are the Processing Element (PE) and the Memory Logic Unit (MLU). The PEM provides storage for 2048 words, each word being 64 bits in length. The memory operates with a read cycle time of 250 nanoseconds (maximum), a write cycle time of 250 nanoseconds (maximum), and a data access time of 188 nanoseconds (maximum). The PEM interfaces with, and is directly controlled by, the MLU.

The first 128 words of the PEM can be write-protected by setting the control bit ACR 13. If a write is attempted in any of the word locations 0 through 127 when ACR 13 is set, the memory write cycle will not occur.

## MEMORY LOGIC UNIT (MLU)

The MLU controls and effects the transfer of data between the PEM, the Control Unit Buffer (CUB), the PE, and I/O Subsystem. The MLU also enables non-memory data transfers between the CUB and the PE. In addition to the control and timing circuitry for PEM operations, the MLU contains a memory information register (MIR) used for the temporary storage of data to be written into or read from the PEM.

. ! . ,

The transfer of the

San Carlotte Commence

garaga kan dan kan dan kanan dan kanan dan kanan dan dan kanan dan dan kanan dan dan dan dan dan dan dan dan d

Acres 1984

# I/O SYSTEM

The three elements which perform the I/O function are:

- 1. A Burroughs B6700 data processing system which, together with its peripherals, performs all the functions of the control computer;

- 2. A Model II disk file system providing approximately one billion bits of storage;

- 3. An ILLIAC IV I/O subsystem which interfaces between the above elements and the ILLIAC IV array subsystem.

The relationship of these elements to one another and to the array is illustrated in Figure 1-9 and described in the following paragraphs.

# B6700 I/O CONTROL COMPUTER

The primary functions of the I/O control computer are to execute the supervisory program for the ILLIAC IV complex and prepare programs for ILLIAC IV. The supervisory program controls the operation of ILLIAC IV; schedules jobs for the array; maintains the Model II disks; transmits control words (descriptors) to the I/O Descriptor Controller, which directs the I/O transactions in and out of the array; responds to interrupt conditions from the array or elsewhere; and communicates with the operator.

The initial B6700 data processing system\* necessary to run the supervisory program and prepare user programs consists of: one processor, 32 K words of memory, an I/O multiplexer with one peripheral control cabinet, and suitable peripherals including a disk file with 10<sup>7</sup> bytes of storage. Associated with the multiplexer are controller units which interface with the various peripherals. These are Burroughs units for the standard peripherals: magnetic tape, disk file, line printer, card reader, card punch, and console printer/keyboard. The B6700 can be expanded from this initial complement

<sup>\*</sup>Refer to B6700/B7700 Characteristics Manual.

Figure 1-9. ILLIAC IV Interface Diagram

of equipment to include an additional processor and multiplexer as well as additional memory (up to 512 K words). On-line communication may be added by including a Datacom processor, multiline controls, and line adapters.

The interface between the I/O subsystem and the I/O control computer is designed to take advantage of the existing properties of the B6700, while keeping simple the interface to the ILLIAC IV array. Control words are received over the scan bus interface provided from the B6700 processor, and results are described in words transmitted back over this same interface.

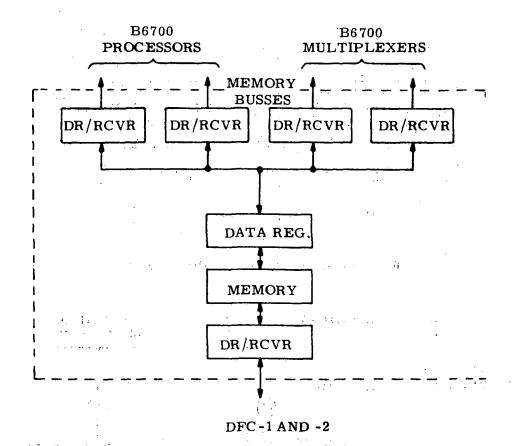

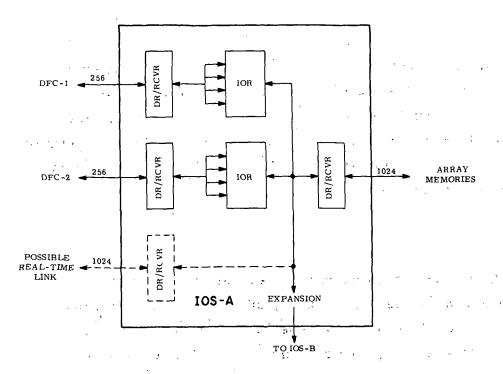

Two data paths exist between the B6700 subsystem and the I/O subsystem, one being the Buffer I/O Memory (BIOM), and the other being directly into the Descriptor Controller (DC). The BIOM functions as a module of B6700 memory, as seen from the B6700 side, handling data transfers from the B6700 into the ILLIAC IV I/O subsystem. On the ILLIAC IV side, the BIOM can transfer either into the disk file, or directly into array memory. The data path to the DC uses the 48-bit word interface of the multiplexer, being a connection into the multiplexer's memory bus whenever the multiplexer is not using it. All interfaces between B6700 and I/O subsystem use bidirectional cables; 20 lines for address, 48 bits for data, 3 bits for tag bits accompanying the data, 8 bits of control, and 1 bit of parity.

#### ILLIAC IV DISK FILE SYSTEM

The ILLIAC IV disk file system (not to be confused with disk file which is part of the B6700 control computer equipment) will initially consist of two Model II disk files with thirteen storage units. Each Model II disk file includes an electronics unit, a concentrator, and Burroughs Model II mechanisms, with sufficient electronic circuitry for reading or writing simultaneously on 128 tracks of one disk. Each disk has a capacity of 79, 257, 600 bits and a maximum

of sixteen such disks may be connected to an electronics unit and its associated concentrator. The electronics unit houses certain common electronics, registers for providing conversion of information from disk-serial to control-unit-parallel form, control logic, power, motor control, and the air pressure system. Read amplifiers are housed in the concentrator. Approximate transfer rate to and from the Disk File Controller is  $502 \times 10^6$  bits per second and the average access time is 19.6 milliseconds. The interface between each electronics unit and its controller in the DFC is 384 bidirectional data lines and 25 control-address lines. The track layout consists of 256 active information tracks per disk face, arranged in one zone.

#### ILLIAC IV I/O SUBSYSTEM

The I/O subsystem is shown in Figure 1-9 as consisting of the I/O Descriptor Controller (DC), I/O Switch (IOS), Buffer I/O Memory (BIOM), and Disk File Controller (DFC). The functions performed by these elements are briefly described below.

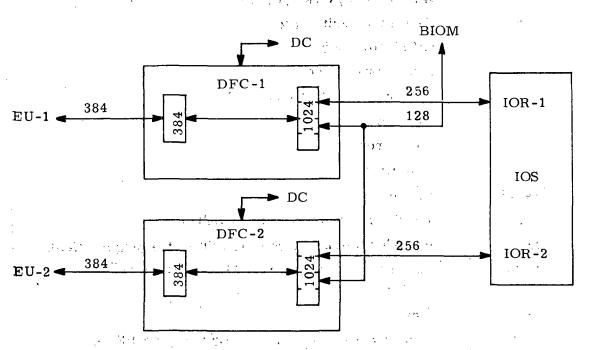

The DFC consists of two controllers which execute descriptors held in DC for transfers between disk and array, disk and BIOM, BIOM and array, and real-time link and array. All transfers involving the array are via the IOS.

As previously noted, the BIOM acts as a memory module for the B6700 system. Within the I/O subsystem, the BIOM has a 128-bit bidirectional interface with each of the two DFC units. All transfers through this interface are under the control of DFC descriptors.

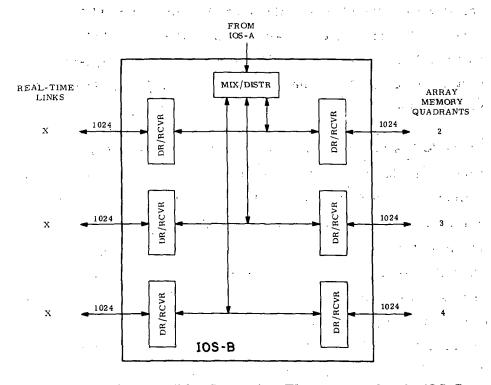

The IOS unit buffers and distributes data between the DFC and the ILLIAC IV array. The DC is also located in the IOS cabinet. The IOS has a 256-bit bidirectional interface with each of the two DFC units and initially a 1024-bit bidirectional interface with the ILLIAC IV array. The IOS design provides for possible future expansion of the real-time link with the array to 4096 bits.

The DC receives pairs of control words, called "scan descriptor, area descriptor", over the scan bus interface. The DC fetches I/O descriptors over the multiplexer word interface in response to the control words; sometimes an entire sequence of I/O descriptors will be initiated by one pair of control words. The DC sends result descriptors back over the scan bus upon the completion of I/O transactions. Certain I/O descriptors cause the DC to send words of data, fetched over the multiplexer word interface, to the CU, where they are treated as instructions by the TMU. There is a 48-bit bidirectional interface between DC and TMU for these transfers.

and the state of t

The second of the second of the second

Control of the Control of the Control

Brown and the first the second of the

and the second of the second o

Application of the second of the sec

The state of the s

# CONTENTS

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |      |     |     |            |     |     |     |     |    |      |      |   |     |   |   | Page |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|-----|-----|------------|-----|-----|-----|-----|----|------|------|---|-----|---|---|------|

| WORD  | FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                | •    | •   | •   | •          | •   | •   | •   |     |    |      | •    |   | •   | • |   | 2-1  |

|       | Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Word           | Fo   | rm  | ats | 3 <b>.</b> |     |     |     |     |    |      | •    |   |     |   |   | 2-1  |

|       | Data Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Form           | ats  |     |     |            |     |     |     |     |    | •    |      |   |     |   |   | 2-2  |

|       | Notation Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nvent          | ions | S . | •   | •          | •   | •   | •   | •   | •  | •    | •    | • | •   | • |   | 2-4  |

| CONFI | Instruction Word Formats   2-1     Data Word Formats   2-2     Notation Conventions   2-4     CONFIGURATION CONTROL LOGIC   2-5     Forking and Joining   2-1     Basic CU Registers   2-1     DPERATIONAL CONTROL   2-1     Interrupt Handling   2-1     Interrupt, Mask, and Control Register Functions   2-1     Illegal Instruction/Address Handling   2-2     NPUT-OUTPUT CONTROL   2-2     Descriptor Controller   2-2     Scan Bus   2-2     Scan Descriptor Usage   2-3     Result Descriptor Usage   2-3     Result Descriptor Usage   2-3     Disk File Control   2-4     Buffer I/O Memory   2-4 |                |      |     |     |            |     |     |     |     |    |      |      |   |     |   |   |      |

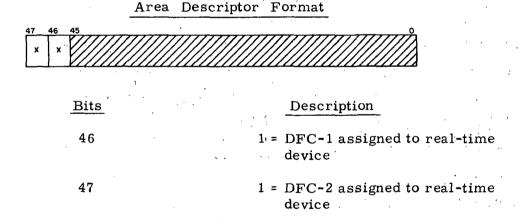

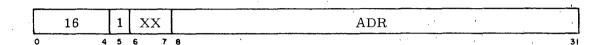

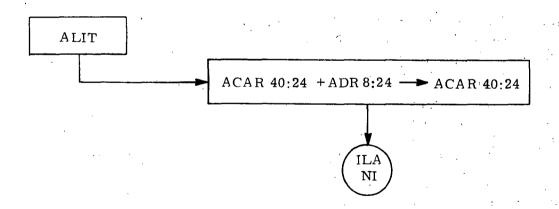

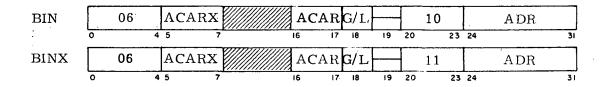

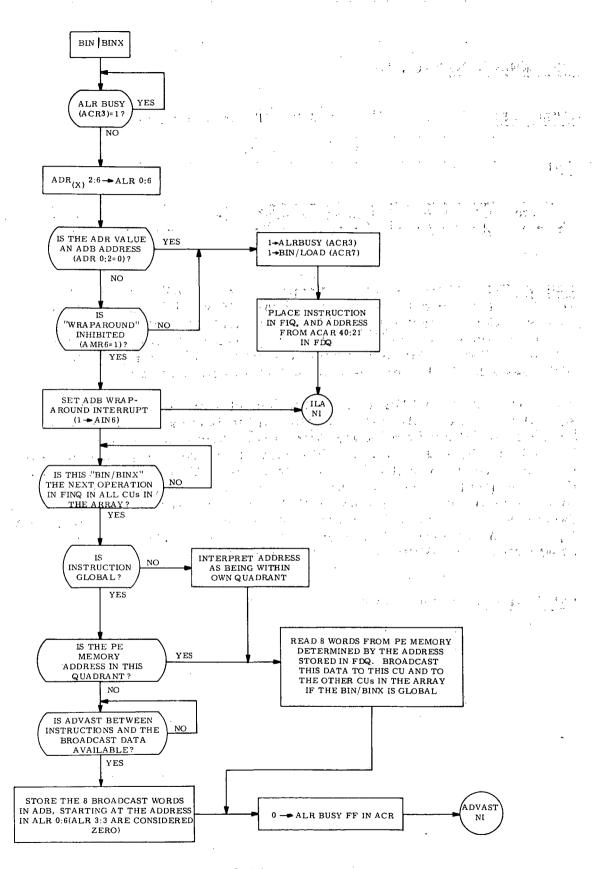

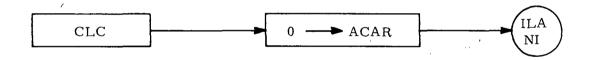

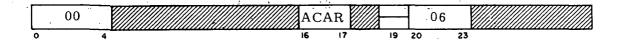

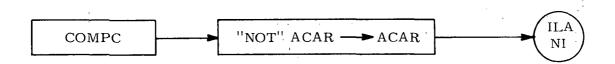

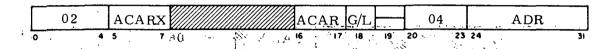

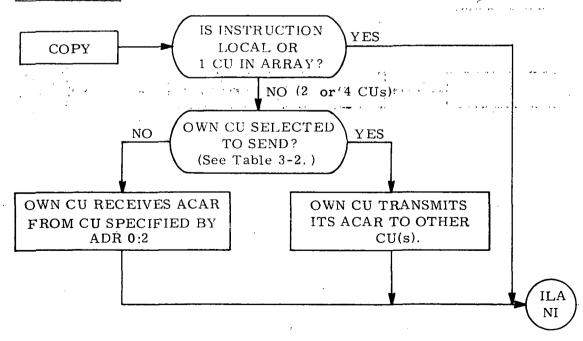

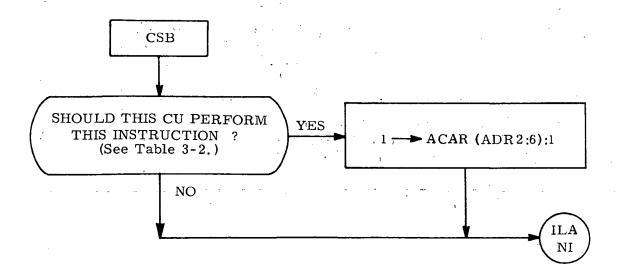

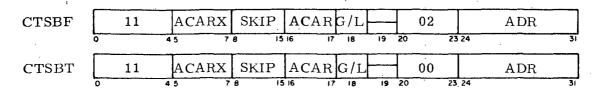

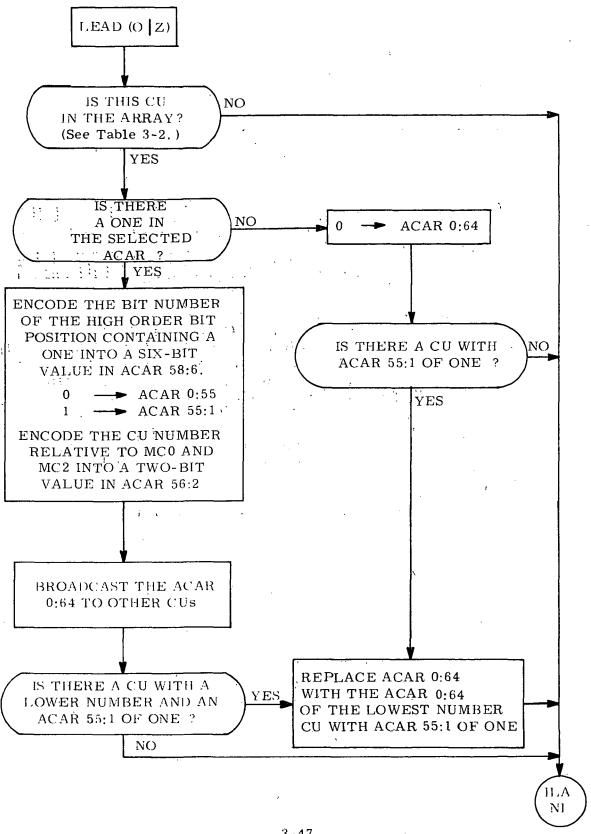

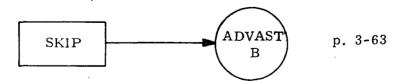

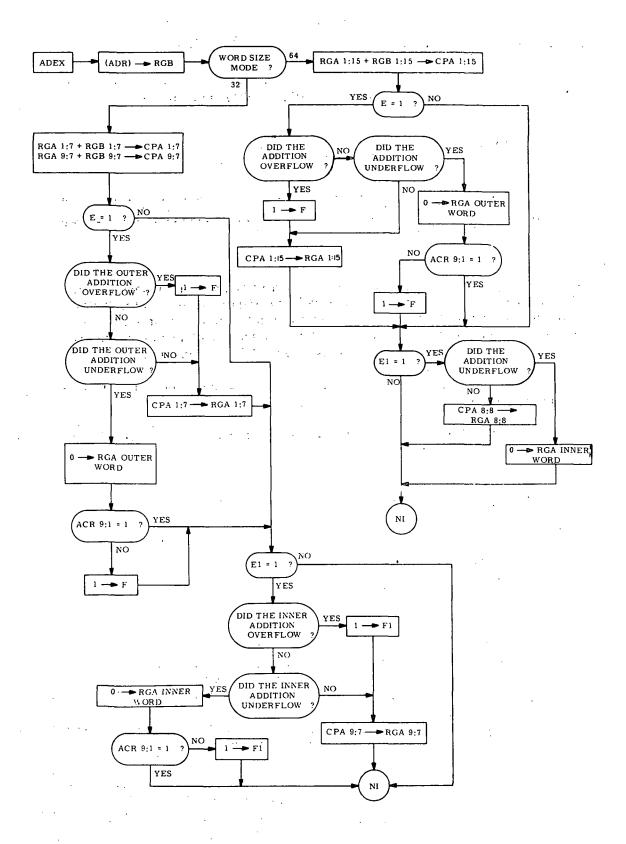

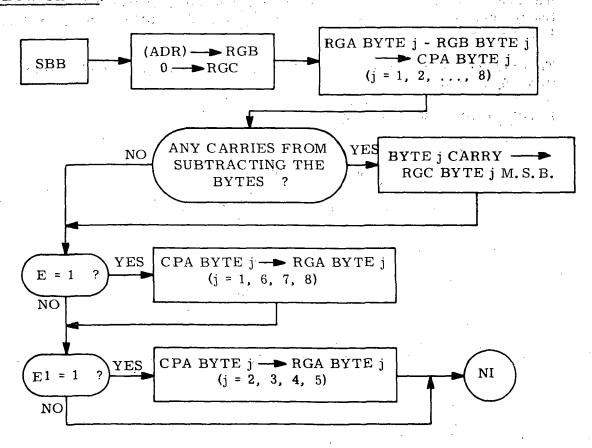

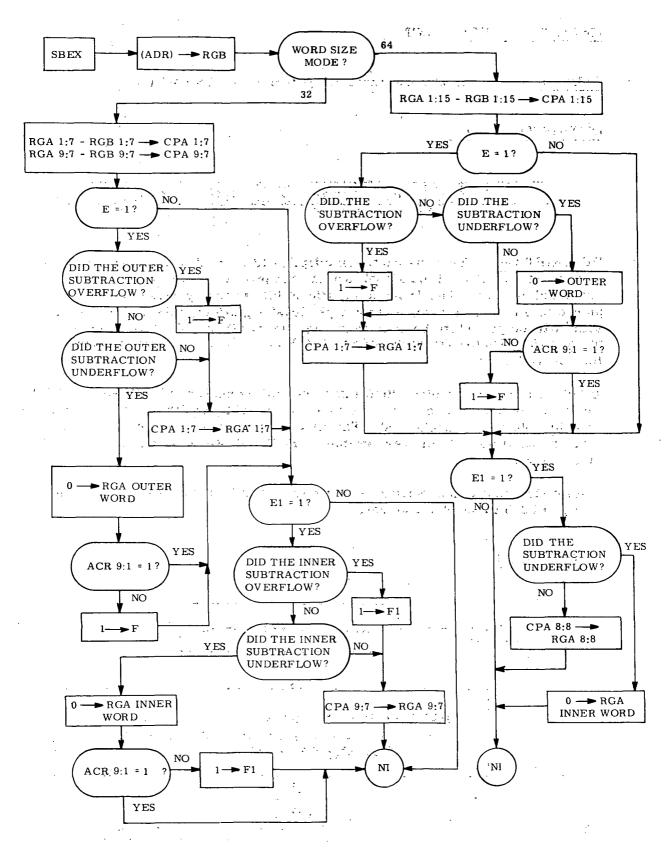

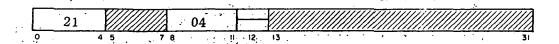

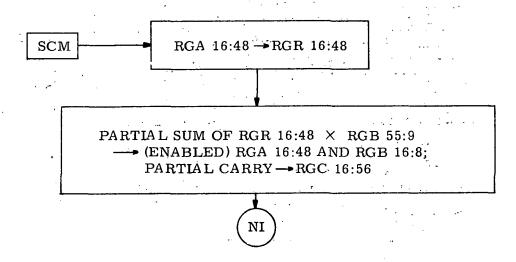

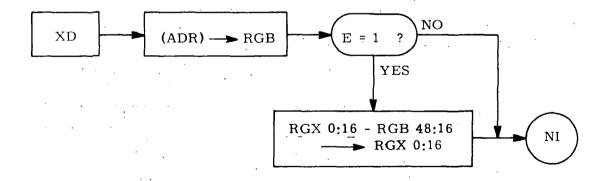

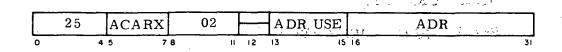

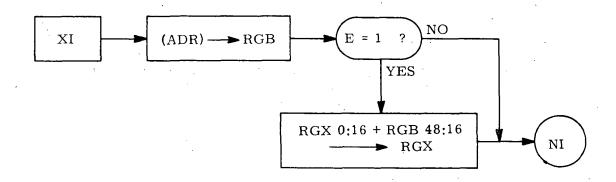

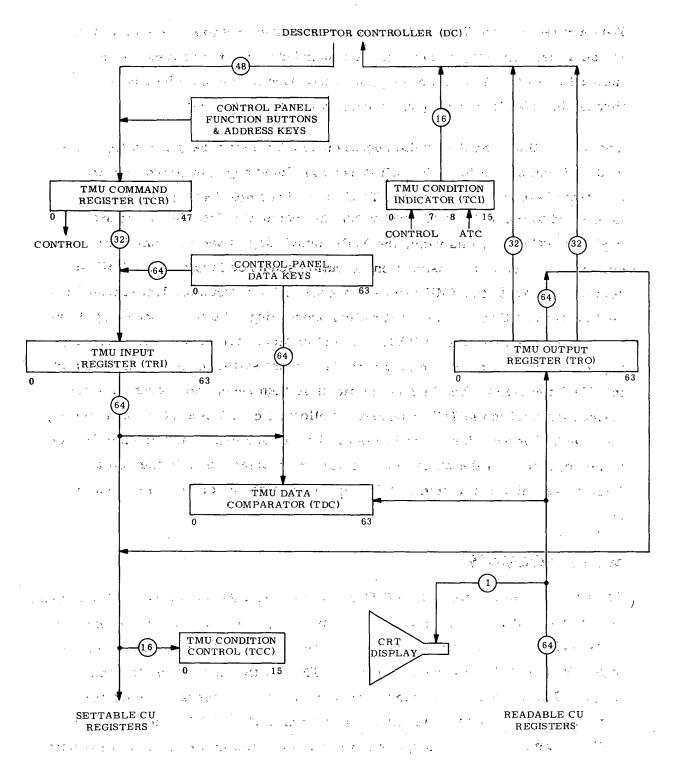

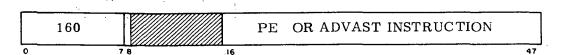

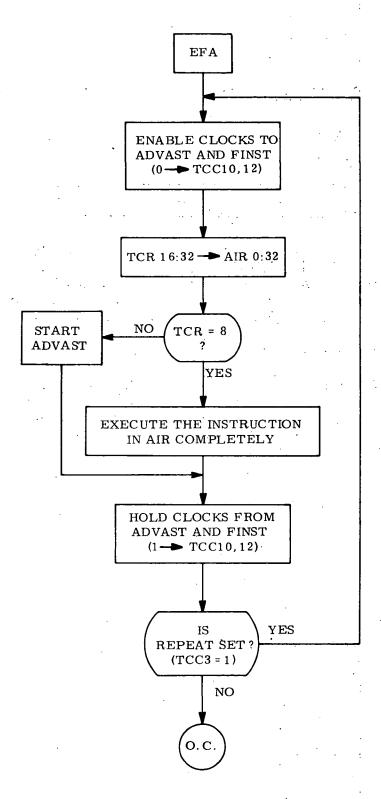

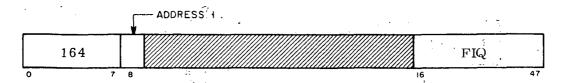

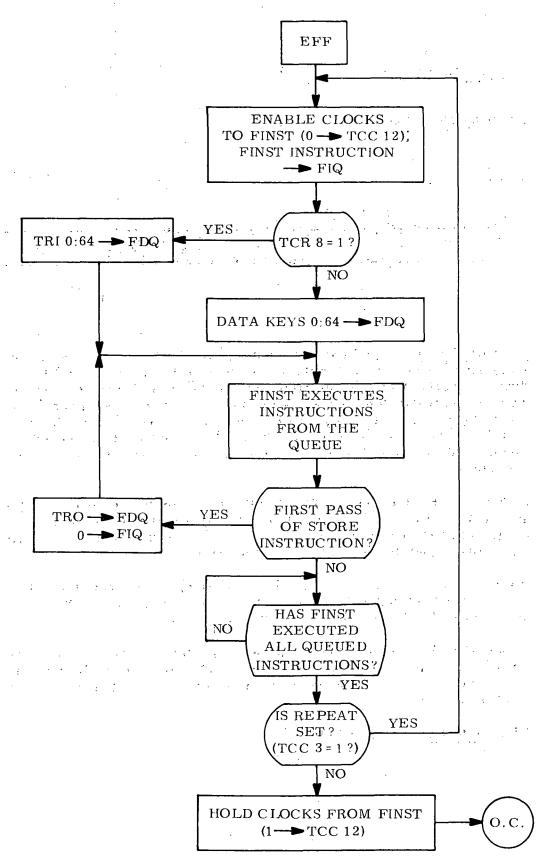

|       | Forking an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | d J <b>oin</b> | ing  |     | •   |            |     |     | •   | •   |    | •    |      |   |     |   | , | 2-13 |