# Final Report

## MULTIPROCESSOR ARCHITECTURAL STUDY

By:

# Alex L. Kosmala, Saul F. Stanten, Woodrow H. Vandever

November 1972

Prepared for the George C. Marshall Space Flight Center, Huntsville, Alabama 35812, under Contract NAS8-28605

by: Intermetrics, Incorporated 701 Concord Avenue Cambridge, Massachusetts 02138

Intermetrics Technical Report #01-73

-

-

\_\_\_\_

# TABLE OF CONTENTS

| FOREWORD             |                                                                           |                                                                                                | i                               |

|----------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------|

| ABSTRACT             | ii                                                                        |                                                                                                |                                 |

| Chapter 1:           | Introdu                                                                   | action                                                                                         | 1-1                             |

| l.l<br>l.2<br>Refere | Scope and Objectives<br>Overview of Intermetrics' Multiprocessor<br>ences |                                                                                                | 1-1<br>1-2<br>1-8               |

| Chapter 2:           | Multipr                                                                   | cocessor Operating System Design                                                               | 2-1                             |

| 2.1<br>2.2           | Introdu<br>Problem                                                        | action<br>ns of Multiprocessing                                                                | 2-1<br>2-3                      |

|                      | 2.2.2<br>2.2.3<br>2.2.4                                                   | Parallelism<br>Exclusive Sections<br>Shared Data<br>Conflict Over System Resources<br>Overhead | 2-4<br>2-5<br>2-6<br>2-7<br>2-8 |

| 2.3                  | Exclus                                                                    | ion and Synchronization                                                                        | 2-8                             |

|                      | 2.3.1<br>2.3.2                                                            | Exclusion Primitives<br>Synchronization                                                        | 2-8<br>2-12                     |

| 2.4                  | Schedu                                                                    | ling                                                                                           | 2-15                            |

|                      | 2:4.1<br>2.4.2                                                            | Space and Time Allocation<br>Deadlock Prevention                                               | 2-15<br>2-18                    |

| 2.5                  | Memory                                                                    | Management                                                                                     | 2-20                            |

|                      | 2.5.1                                                                     | Operating Memory Multiplexing                                                                  | 2-21                            |

| 2.6                  | Implem                                                                    | entational Aspects                                                                             | 2-24                            |

|                      | 2.6.1<br>2.6.2<br>2.6.3                                                   | System Specification<br>Structure<br>Systems Programming Language                              | 2-24<br>2-24<br>2-25            |

| Refere               | ences                                                                     |                                                                                                | 2-27                            |

- --

Table of Contents (continued)

| Chapter 3: | Interru                 | apt Structure                                                                                                              | 3-1                             |

|------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 3.1<br>3.2 | Assumpt<br>Interru      | ions<br>upt Categorization                                                                                                 | 3-1<br>3-1                      |

|            | 3,2.2                   | Process Oriented<br>System Oriented<br>Processor Oriented                                                                  | 3-2<br>3-2<br>3-2               |

| 3.3        | Multip                  | cocessor Interrupt Problem Areas                                                                                           | 3-3                             |

|            | 3.3.3<br>3.3.4          | Which Processor to Interrupt?<br>Response Time<br>Innovations<br>The Interrupt Sequence<br>Interrupt Functional Response   | 3-3<br>3-4<br>3-4<br>3-6<br>3-6 |

| Chapter 4: | Memory                  | Hierarchy                                                                                                                  | 4-1                             |

| 4.1        | Basic I                 | Hierarchy Description                                                                                                      | 4-1                             |

|            | 4.1.2<br>4.1.3<br>4.1.4 | MO - Micro Level Control Memory<br>Ml - Local Memory<br>M2 - Operating Memory<br>M3 - Mass Memory<br>M4 - Archival Storage | 4-1<br>4-1<br>4-2<br>4-2        |

| 4.2        | Local                   | Storage                                                                                                                    | 4-2                             |

| •          |                         | The Problem - Memory Contention vs.<br>Performance<br>Two Approaches to an Implementation                                  | 4-2<br>4-11                     |

| 4.3        | Operat                  | ing Memory and Memory Management                                                                                           | 4-15                            |

|            | 4.3.2<br>4.3.3          | Background<br>Segmentation<br>Paging<br>Implementing Virtual Memory                                                        | 4-15<br>4-18<br>4-20<br>4-21    |

| Refere     | ences                   |                                                                                                                            | 4-23                            |

| Chapter 5: | Addres                  | sing                                                                                                                       | 5-1                             |

| 5.1        | Addres                  | sing and Instruction Architecture                                                                                          | 5-1                             |

|            | 5.1.1                   | The Number of Operands in an<br>Instruction                                                                                | 5-1                             |

Page

# Table of Contents (continued)

|                                        | 5.1.2 Single Accumulator and General                                                                                                                                                                                                                                                                          | 5-3                                                                               |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|

|                                        | Registers<br>5.1.3 How to Address Operating Memory                                                                                                                                                                                                                                                            | 5-5                                                                               |  |

| 5.2                                    | The IBM 360 and Burroughs B6700                                                                                                                                                                                                                                                                               | 5-7                                                                               |  |

|                                        | <ul> <li>5.2.1 Two Dimensional Addressing (Static<br/>and Dynamic)</li> <li>5.2.2 Implicit Addressing</li> <li>5.2.3 Descriptors</li> <li>5.2.4 Type Differences</li> <li>5.2.5 Semantic Conciseness</li> </ul>                                                                                               | 5-7<br>5-9<br>5-10<br>5-11<br>5-12                                                |  |

| 5.3                                    | Implementation Aspects of a Stack Machine                                                                                                                                                                                                                                                                     |                                                                                   |  |

|                                        | 5.3.1 Definitions<br>5.3.2 PUSH<br>5.3.3 POP                                                                                                                                                                                                                                                                  | 5-13<br>5-14<br>5-14                                                              |  |

| 5.4                                    | Effective Address Generation (EA).<br>(Lexical Level Offset Addressing)                                                                                                                                                                                                                                       |                                                                                   |  |

| 5.5<br>Referen                         | Stack Fetch<br>ences                                                                                                                                                                                                                                                                                          |                                                                                   |  |

| Chapter 6: I/O Considerations          |                                                                                                                                                                                                                                                                                                               | <b>C D</b>                                                                        |  |

| Chapter 6:                             | I/O Considerations                                                                                                                                                                                                                                                                                            | 6-1                                                                               |  |

| Chapter 6:<br>6.1<br>6.2<br>6.3<br>6.4 | I/O Considerations<br>Space Station System Requirements<br>Data Bus I/O<br>Mass Storage I/O<br>I/O Controller Design                                                                                                                                                                                          | 6-1<br>6-2<br>6-8<br>6-10                                                         |  |

| 6.1<br>6.2<br>6.3                      | Space Station System Requirements<br>Data Bus I/O<br>Mass Storage I/O                                                                                                                                                                                                                                         | 6-1<br>6-2<br>6-8                                                                 |  |

| 6.1<br>6.2<br>6.3                      | <pre>Space Station System Requirements Data Bus I/O Mass Storage I/O I/O Controller Design 6.4.1 Central Control (CC) 6.4.2 Interprocessor Communication Interfaces (IPCI) 6.4.3 Operating Memory Interface 6.4.4 Channels 6.4.5 Interrupt Handler 6.4.6 Timer I/O Configuration Organized for Recovery</pre> | 6-1<br>6-2<br>6-8<br>6-10<br>6-10<br>6-10<br>6-12<br>6-13<br>6-13                 |  |

| 6.1<br>6.2<br>6.3<br>6.4               | <pre>Space Station System Requirements Data Bus I/O Mass Storage I/O I/O Controller Design 6.4.1 Central Control (CC) 6.4.2 Interprocessor Communication Interfaces (IPCI) 6.4.3 Operating Memory Interface 6.4.4 Channels 6.4.5 Interrupt Handler 6.4.6 Timer I/O Configuration Organized for Recovery</pre> | 6-1<br>6-2<br>6-8<br>6-10<br>6-10<br>6-10<br>6-12<br>6-13<br>6-13<br>6-13<br>6-13 |  |

Table of Contents (continued)

|            | 7.2.1                                                                                                                                       | Implementing Hardware Error Detection              | 7-3          |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------|

| 7.3        | Recovery                                                                                                                                    |                                                    |              |

|            | 7.3.1                                                                                                                                       | Processing Unit (P-M1)                             | 7-7          |

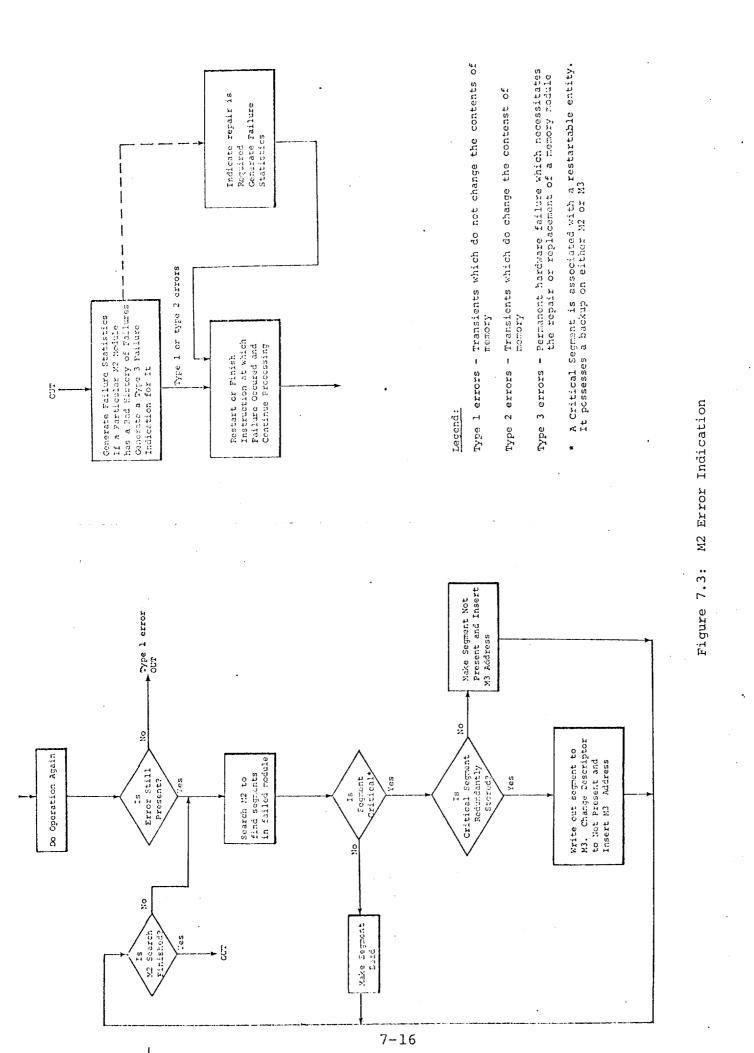

|            | 7.3.2 Recovery from an Operating Memory<br>(M2) Failure                                                                                     |                                                    | 7-11         |

|            | 7.3.3                                                                                                                                       | Fault Tolerant Aspects of the I/OC,<br>Channel     | 7-17         |

| 7.4        | The Imp                                                                                                                                     | plications of Fail Safe                            | 7-26         |

| Chapter 8: | Concept Verification                                                                                                                        |                                                    | 8-1          |

| 8.1        | Background<br>Phase 1 - Initial Analysis and High-Level<br>Simulation                                                                       |                                                    | 8-1          |

| 8.2        |                                                                                                                                             |                                                    | 8-2          |

|            | 8.2.1                                                                                                                                       | Objectives<br>Tools for High-Level Simulation      | 8-2<br>8-3   |

| 8.3        | Phase<br>Simula                                                                                                                             | 2 - Low-Level, Detailed, Mixed<br>tion             | 8-6          |

|            | 8.3.1<br>8.3.2                                                                                                                              | The Simulation Process<br>Simulation Design Issues | 8-6<br>8-11  |

| Refere     | nces                                                                                                                                        |                                                    | 8-16         |

| Chapter 9: |                                                                                                                                             | ue of SUMC's Architectural<br>teristics            | 9-1          |

| 9.1        | Design                                                                                                                                      | Goals                                              | 9-1<br>9-2   |

| 9.2<br>9.3 | Micro Instruction Sequencing<br>Choosing Functions to Optimize<br>Field Manipulation - Maskings - Shifting -<br>Bit Addressing and Shifting |                                                    |              |

| 9.4        |                                                                                                                                             |                                                    |              |

| 9.5        | Limite                                                                                                                                      | d Scratch Pad Addressing                           | 9-7<br>9-9   |

| 9.6        | Micro                                                                                                                                       | and Main Memory Speed Ratio                        | 9-9<br>9-9   |

| 9.7<br>9.8 | Maln M                                                                                                                                      | lemory Synchronization<br>d Modularity Concept     | 9-10         |

| 9.8        | The "U                                                                                                                                      | " in SUMC - Ultra Reliability                      | 9-12         |

| 9.10       | Confus                                                                                                                                      | ion Between Design Levels                          | 9-12<br>9-13 |

| References |                                                                                                                                             |                                                    |              |

Page

`

### FOREWORD

This document is the Final Report of a multiprocessor architectural design study, whose objective was to establish a baseline design for a central multiprocessor for a Space Station Data Management System exploiting the NASA/MSFC developed SUMC hardware where possible. The study was sponsored by the NASA Marshall Space Flight Center, Huntsville, Alabama, under contract NAS8-28605, entitled, Research Study on Memory Hierarchy. It was performed by Intermetrics, Inc, Cambridge, Massachusetts, over the period June to October 1972, under the direction of Alex L. Kosmala. Technical monitors for MSFC were Mr. Gerald L. Turner and Mr. James L. Lewis.

Publication of this report does not constitute approval by NASA of the findings or conclusions contained therein.

### ABSTRACT

This is an architectural design study of a multiprocessor computing system intended to meet functional and performance specifications appropriate to a manned space station application as defined by NASA's Marshall Space Flight Center. Intermetrics previous experience and accumulated knowledge of the multiprocessor field is used to generate a baseline philosophy for the design of a future SUMC\* multiprocessor.

The operating system design problem for multiprocessors is to approach the theoretical performance without sacrificing fault tolerance, flexibility, and expandability. Parallel tasking is described as a necessary operating capability in this regard, while exclusive operators are also needed to avoid critical section conflicts. Synchronization, scheduling, and deadlock prevention are other system design features which are discussed, along with memory management. Treatment of the topics of operating system specification and structuring, and the use of a higher order language complete the discussion of multiprocessor operating systems.

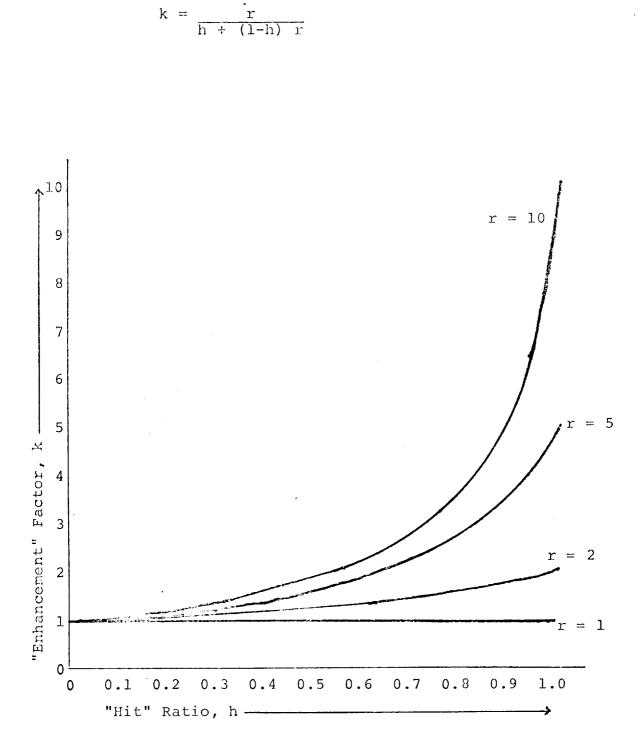

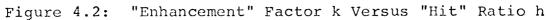

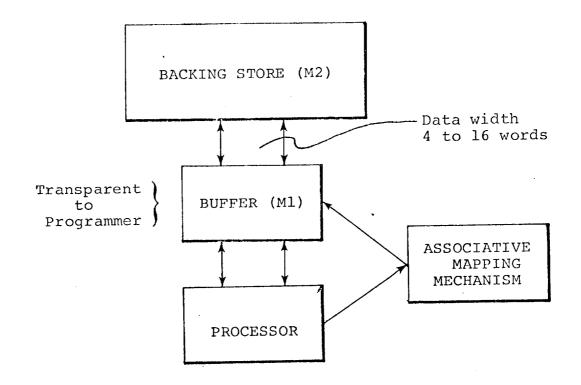

Interrupts are defined and the crucial questions of interrupt structure, such as processor selection and response time, are discussed. Memory hierarchy and performance is discussed extensively with particular attention to the design approach which utilizes a cache memory associated with each processor. The ability of an individual processor to approach its theoretical maximum performance is then analyzed in terms of a hit ratio, which is the proportion of time that a memory request can be supplied from cache only. Memory management is envisioned as a virtual memory system implemented either through segmentation or paging.

Addressing is discussed in terms of various register design adopted by current computers and those of advanced design. Using examples, two dimensional addressing, implicit addressing, and the use of descriptors are described. Implementation of a stack-oriented machine is explained, along with the generation of an Effective Address scheme. The overall I/O architecture set forth is upon a Data Bus I/O to service an

\* Space Ultra-reliable Modular Computer

-ii-

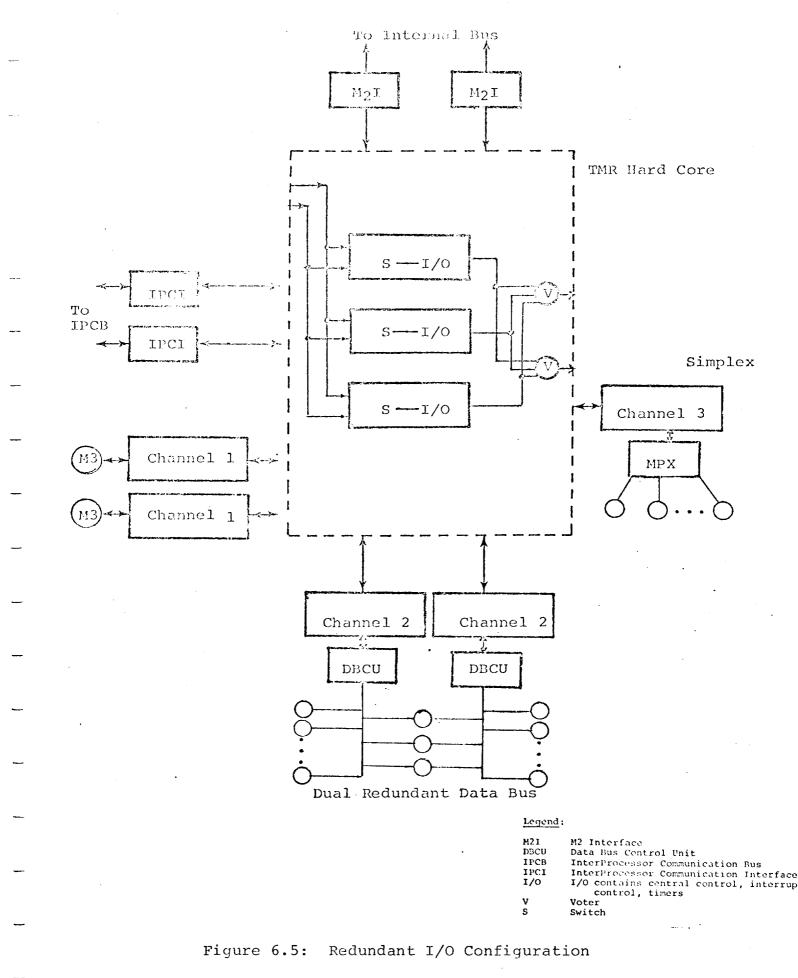

advanced data bus concept and a Mass Storage I/O. The I/O Controller design is then discussed in terms of interfaces to the processors and to the memories with special emphasis given to recovery from failure.

A complete chapter is devoted to error detection, fault isolation, and recovery philosophy as applied to a multiprocessor system. The important topic of concept verification is given careful scrutiny in terms of

a) analytical techniques and high-level computer simulation, and

b) detailed, low-level simulation.

Finally, the report concludes with a detailed critique of SUMC's architectural characteristics in relationship to the overall design objectives.

### Chapter 1

#### INTRODUCTION

#### 1.1 Scope and Objectives

The work described in this report is the result of a study of multiprocessing system design principles, performed in support of the MSFC in-house multiprocessor computer development. The initial objectives of the study were to achieve a top-level architectural design capable of meeting the functional and performance specifications established for the Phase B Space Station Information Management System Central Processor, and in doing so to exploit as much as possible the current MSFCdeveloped SUMC processor design. However, during the early phases of the study it became apparent that in order to preserve the value of an independently derived evaluation of multiprocessor design features by Intermetrics, some deviation from these objectives would be necessary. The basic philosophies of multiprocessor design and operation espoused by Intermetrics in defining an architecture appropriate to the Space Station requirements were found to be incompatible with those already adopted by MSFC in arriving at the current SUMC design. Consequently it was mutually agreed that rather than using the existing SUMC design as the basis for the study, Intermetrics should apply the results of their previous experience and accumulated knowledge of the multiprocessor field to establishing a SUMC architecture from an entirely independent point of view. Much of that point of view was gathered in the performance of a previous design study [1] with very similar objectives to those expressed for the SUMC multiprocessor. Although some of the philosophies which are embodied in that design were directly applicable, it was decided not to tailor the complete design to the SUMC application by adopting some features and discarding others. Instead, it was decided to select certain multiprocessor design areas and hardware features and perform an in-depth analysis, review and evaluation for each, in order to establish the philosophies and the rationale developed by Intermetrics in their approach to a multiprocessor design. The objective was to provide a baseline philosophy for the design of a future version of the SUMC multiprocessor, radically different from the one proposed in the present MSFC in-house development program.

In Intermetrics opinion the design of a multiprocessor for a Space Station application should be guided by the following considerations:

1-1

- a) The performance potentially achievable through the use of multiple processors (often quoted as the main motivation of multiprocessing but, as will be explained in Chapter 2, very difficult to achieve) should not be compromised by implementational incompatibilities, especially in the executive system, nor sacrificed to achieve other MP objectives such as fault tolerance, flexibility, and expandability.

- b) Since the overall cost of providing computational capabilities (especially in a difficult environment like a Space Station) may be dominated by software costs rather than hardware, the architecture and operating characteristics of the computer must reflect the needs, desires and techniques of the programmer rather than those of the logic designer.

- c) The outstanding advantage of a multiprocessor is its potential tolerance to failures of its components. This capability should be realized in the initial architectural design, and not provided as a final touch after most design decisions have been made.

The detailed analysis of the areas of multiprocessor design which were selected for this study reflect the above basic attitude. They form most of the chapters in the remainder of this report, and include the following topics: Operating System design (Chapter 2); Interrupt Structure (Chapter 3); Memory Hierarchy (Chapter 4); Addressing (Chapter 5); I/O Considerations (Chapter 6); Fault Tolerance (Chapter 7). Additional chapters cover Concept Verification (Chapter 8), since it was of some concern to MSFC how any given multiprocessor design could be given a quantitative evaluation without incurring the initial investment of a hardware build phase, and a critique of the SUMC processor internal architecture (Chapter 9).

Much of the description and terminology found in this report assumes a familiarity with Intermetrics' previous multiprocessor design. To prevent unnecessary (and probably inadequate) repetition of the details of that design, the reader is referred to reference [1]. However, to provide an introduction to at least some of the terms used we present the following overview of the configuration of hardware and software elements of the design, as extracted from sections of reference [1].

# 1.2 <u>Overview of Intermetrics' Multiprocessor</u>

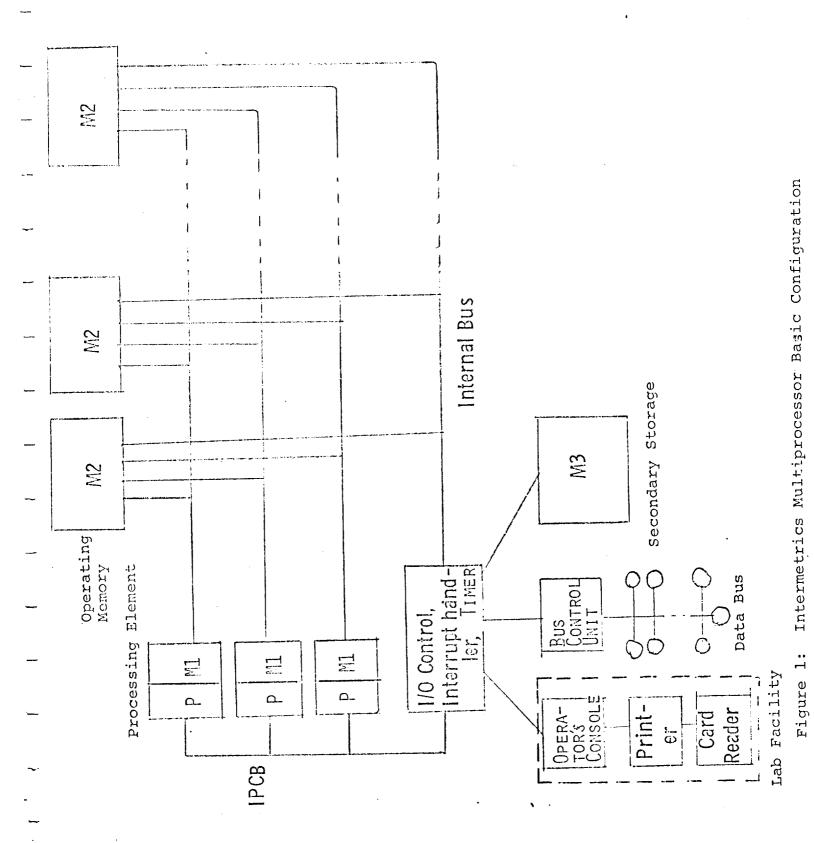

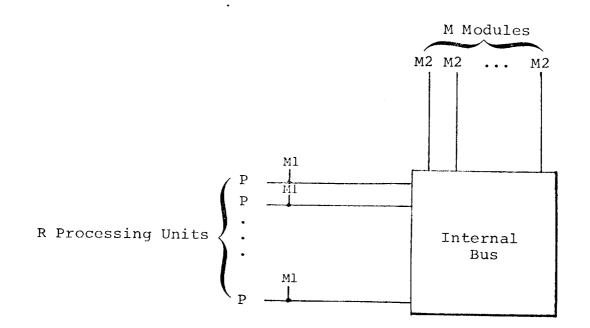

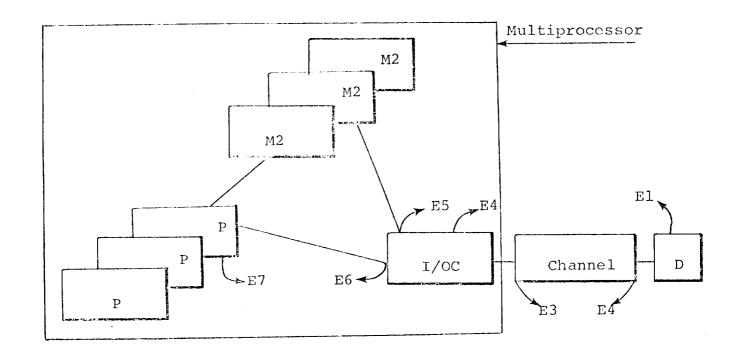

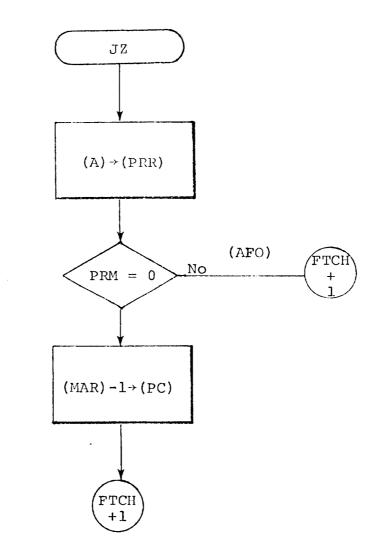

The basic configuration of the multiprocessor is shown in Figure 1. The MP was specified to consist of a number of

identical, interchangeable processing elements which would execute the major processing workload, and a single, more specialized processor to handle I/O processing and a number of other unique func-These functions include interrupt handling, interprocessor tions. communication control, and the central timer. The executive was specified to be non-dedicated (to any given processor), and its functions are performed by any of the processors. The choice of which processor is made on the basis of status (e.g., by having completed its current assignment), or by reason of its greatest interruptibility as determined by the priority of its current The number of computational processors was specified process. as three, because the resulting configuration represents the simplest which possesses completely all the characteristics (and problems) of the n-processor case. The two processor system which has received the greatest amount of development and operational experience of all configurations, represents a degenerate form of multiprocessor: while certainly exhibiting true concurrency of processes, nevertheless the dual processor allows certain simplifications of executive functions to be made because of the binary number of active elements in the system. The memory terminology in the figure is used in parts of this report, and is defined as follows:

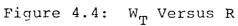

- M1: Local memory, dedicated to, and only for use by a processor. This is a general term and refers to all aspects of buffer, scratchpad, control and associative memory, required by a processing element. The contents of any M1 storage cell are available only to the processor of which M1 is an intimate component. Only in case of recovery after a P and/or M1 failure are these contents made available to another processor. In this MP design M1 is not, strictly, a member of the memory hierarchy.

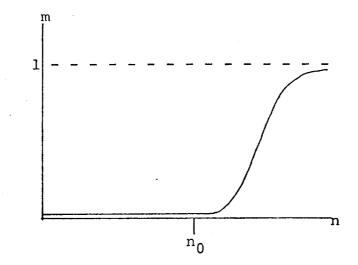

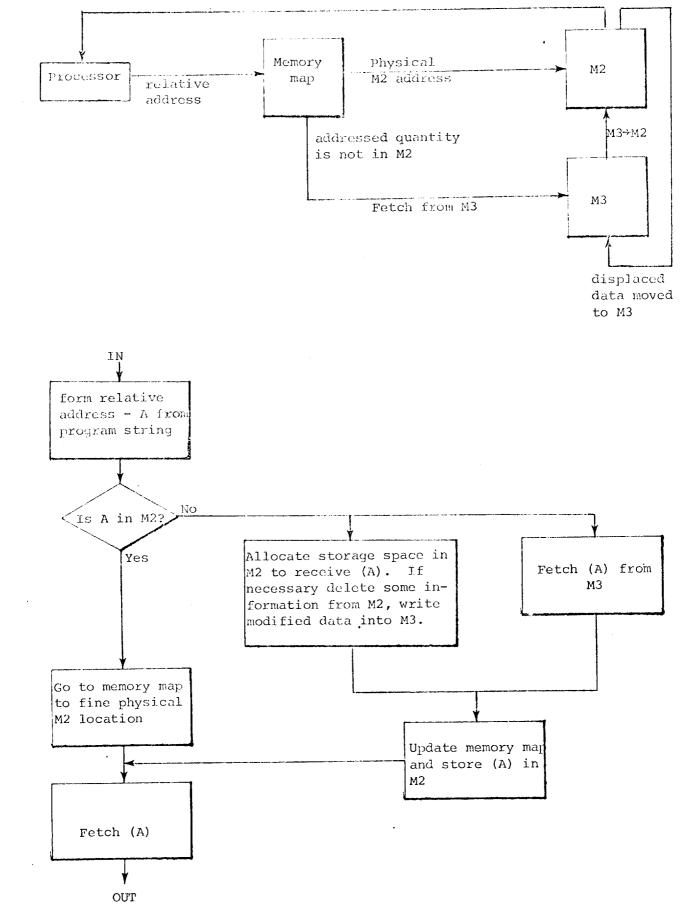

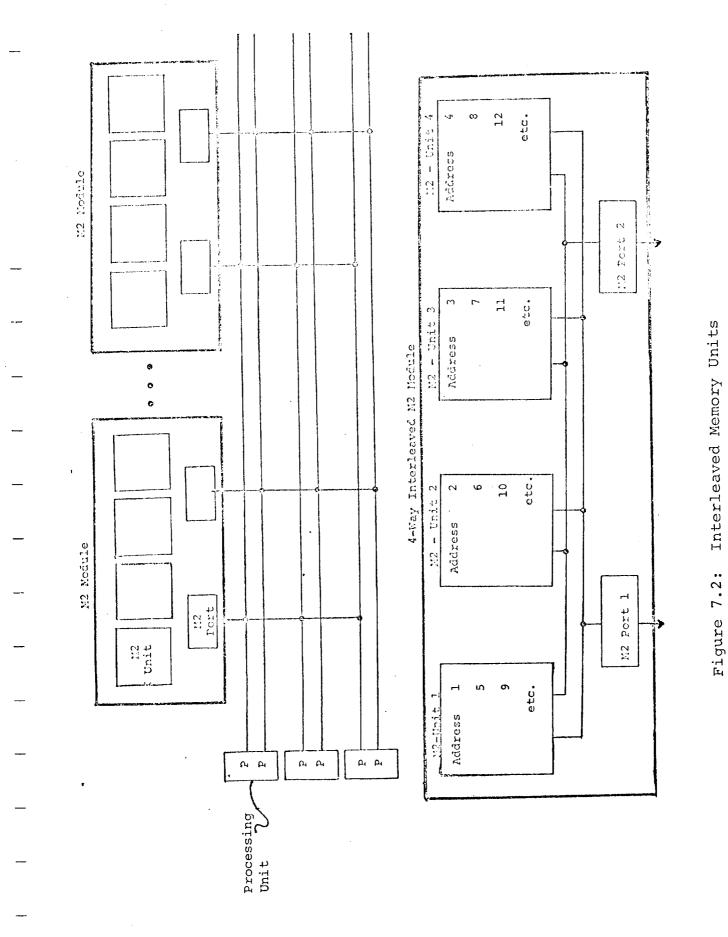

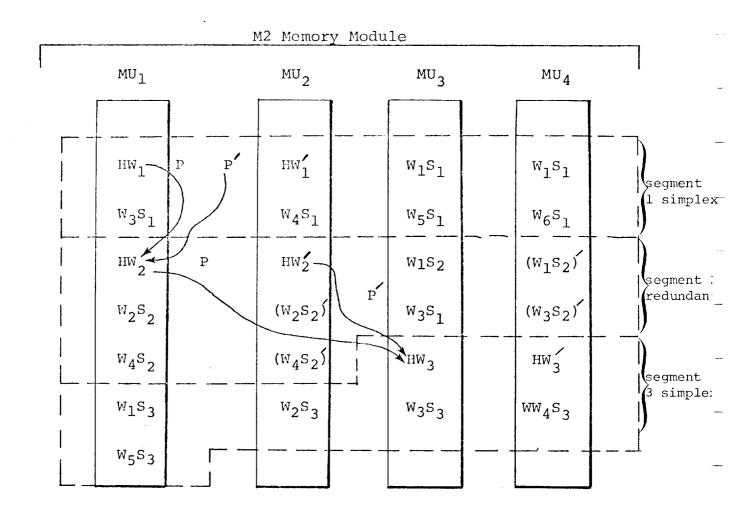

- M2: Operating memory (main memory, or, in popular terms, "core"). M2 consists of several individual memory modules, all of which are accessible to all processors, including the I/O controller. Each access takes place via a data path dedicated to each processing element, through a port in each M2 module. The basic MP configuration, therefore, requires four ports per M2 module. Each module is fourway interleaved, for purposes of speed, access, conflict resolution, and fault recovery.

- c)

a)

b)

- M3: Secondary storage (backup or Mass Memory). Being a conventional drum or disk, it was decided to interface this level of the memory hierarchy with the rest of the computer system in the more conventional manner, via an I/O channel. The use of

- 1-4

M3 to implement the concept of virtual memory then places the heaviest requirement on the design of the I/O controller and the I/O executive routines.

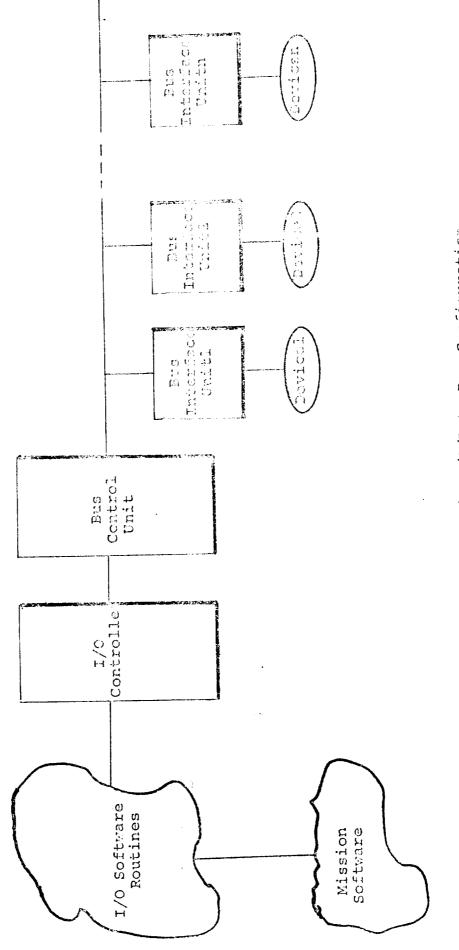

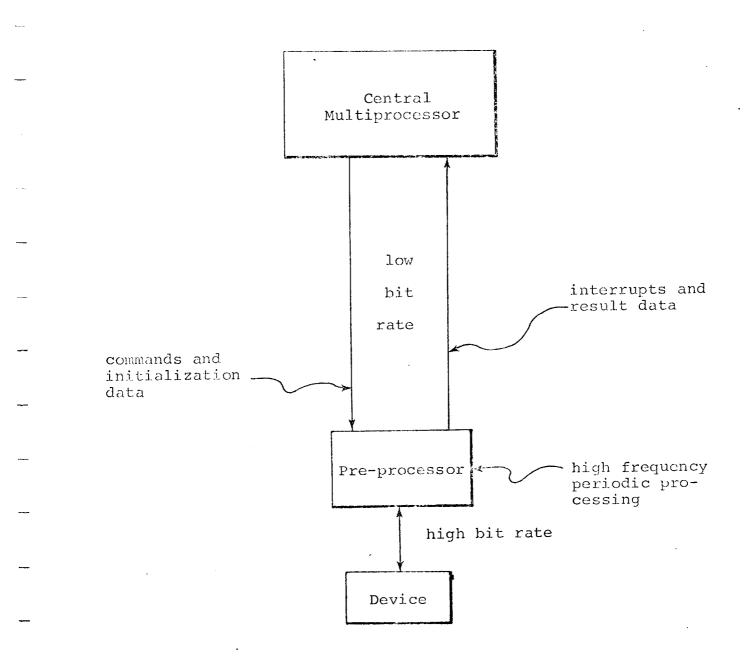

As mentioned above, several unique functions were gathered together into one, unique module, which is (for convenience) termed the I/O controller (IOC). All interfaces to the outside world were handled via the IOC.

Communication between the processing elements of the MP system (the P's and IOC) were handled by a separate interprocessor bus (IPCB).

(It should be emphasized that the basic configuration of Figure 1 does not indicate the levels of redundancy specified for fault detection and/or recovery. For a discussion of these aspects, refer to Chapter 7.)

The terminology used in this report refers to the way in which information was organized and handled in the previous Intermetrics work. The key terms and their assumed definition are as follows:

- a) <u>Program</u>: This is an independently compilable section of code containing pure procedures and/or data.

- b)  $\frac{Procedure}{can}$  A section of code to which execution control can be passed, with or without the passage of parameters.

- 1) Internal, not known outside of process (see below)

- 2) External, known to name manager and declared in the Process Information Area (see below)

- c) <u>Segment</u>: A contiguous block of words defined by a descriptor, which is the unit of memory management.

- d) <u>Process</u>: The unit of work as recognized by the operating system. A process is represented by a stack.

- e) <u>Stack</u>: Although strictly a LIFO list, the definition of a stack is less rigorous when used to represent a process.

- f) Level: A demarcation in the addressing hierarchy. Derived from the concept of lexicographical level in block structured language (such as ALGOL or HAL), but extended to provide convenient addressing by the operating system.

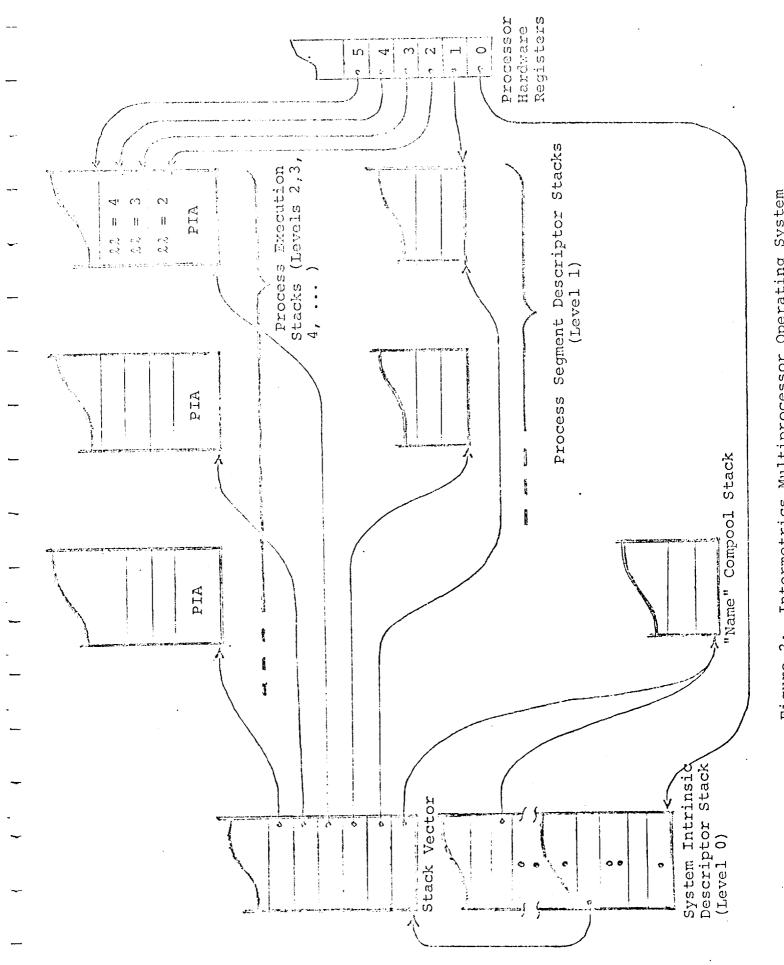

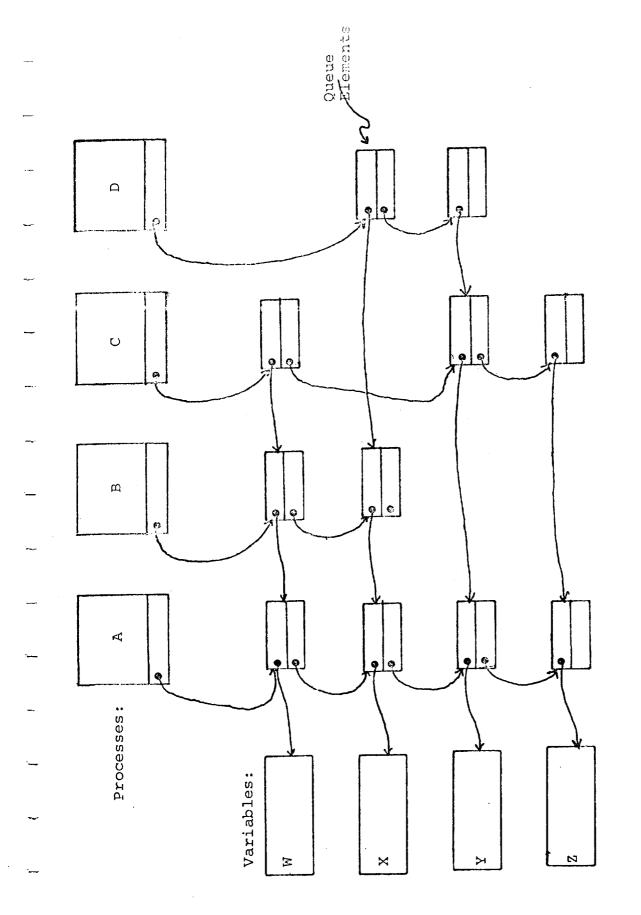

Figure 2 illustrates the relationship and use of some of these terms. Each process is represented by an execution stack. The initial hierarchical level for process execution, and therefore the lowest numerical level for any process stack, is level 2. Subsequent procedure nesting varies the lexical level of each process stack to 3, 4, 5, etc. The portion of a process stack that is below level 2 contains a collection of data termed the Process Information Area (PIA) containing names, priorities, counters, for bookkeeping, etc., specific to each process. Above the PIA the stack behaves more strictly as a LIFO list.

Each process has associated with it a vector of descriptors defining the segments containing the procedures to be executed by the process. These descriptors are addressed as if the vector were a stack: by stack number and offset from the base of the stack. For convenience, this collection of segment descriptors is termed Level 1, since it exists at a more global level than the individual processes, and each such vector will be referred to as a stack (even though, strictly, it is not).

At the most fundamental level there is a single collection of basic system descriptors, variables, etc., which is termed the Level 0 stack, again for convenience of addressing. One descriptor at level 0 points to the stack vector, which contains descriptors of all the stacks in the system including the "pseudo-stacks" of levels 1 and 0.

Each processor contained a set of hardware registers which indicated the actual M2 addresses of the start of each of the system levels, i.e., the base address of the corresponding stack. Figure 2 also shows the linkages that tie the Compool mechanism into the system.

The operating system design philosophy reflected an emphasis on the achievement of reliable operation of both hardware and software. It was assumed that only higher order language(s) would be used in the programming of application software. The exclusive use of HOLs allows secure system operation to be realized without exhaustive runtime verification of each request for OS functions. An intimate and well-defined interface between OS and the compiler(s) was assumed achievable, so that an optimal division between static (pre-run) and dynamic (runtime) diagnosis could be made.

It was assumed that the language/compiler to be used in programming the Space Station application software would possess the facility of handling common data pools (Compools). The MP design provided a Compool implementation.

1-7

Intermetrics Multiprocessor Operating System Figure 2:

# Reference for Chapter 1

1. Miller, J.S., et. al., "Engineering Study for the Functional Design of a Multiprocessor Design", Intermetrics/NASA Contract NAS9-11745, September, 1972.

#### Chapter 2

# MULTIPROCESSOR OPERATING SYSTEM DESIGN

#### 2.1 Introduction

This chapter will discuss the special problems facing the designer of an operating system for a multiprocessor computer. The scope of the task which is summarized here did not encompass all aspects of OS design. Emphasis is placed on the more important functions and on those aspects of OS which are unique to, or at least more significant for, multiprocessors as compared with simplex computers.

An operating system for a space station multiprocessor will be capable of supporting a wide variety of functions. Although some of these may be unique to the application, it is very probable that the following standard functions will always be required in some measure:

#### a) Initialization

This deals with the initial introduction of information into the computing system and its preparation for eventual execution. It includes bootstrapping from a cold start, establishing the minimum state from which the complete system structure can be created, the problems associated with loading and linking of programs and data for execution, etc. This topic is not a trivial one: a real-time MP/OS is a complex structure and the problem of establishing it as a working entity from scratch should be considered at the time its initial design is undertaken. Initialization will not be discussed further.

b) Process State Controller

The basic element of computational work will be termed a Process. Processes can exist in various states: execution, readiness, stall or suspension. This function of the OS controls the orderly progression of processes between these states in response to various stimuli, such as voluntary process state changes, I/O interrupts, priority changes, interprocess communication, etc.

#### c) Interrupt Servicing

A real time, general purpose, central computer for a space station will almost certainly be required to handle system-originated external interrupts in addition to interruptions due to arithmetic traps and other error conditions. This OS function implements the desired responses to randomly occurring events of this nature.

d) Timing and Synchronization

This function provides the basic mechanism for controlling the time dependent execution, and the synchronization of parallel, concurrent processes in a real-time, multiprogrammed environment.

e) Resource Management

This is the basic function of an operating system. The resources required by a computational process are various. First, there are the basic hardware elements: the processors, memory modules, and interconnecting data paths which must be available to allow the process to Then there are the less tangible items such as run. common programs and data over which conflict of access by several concurrent processes is possible. Lastly, there is external device availability: sensors, avionics data buses, disks, tapes, etc. The resource management function is usually divided into processor allocation, memory allocation, compool and shared data management, I/O and file management. It is the function of resource allocation to ensure that each scheduled process is granted a sufficient share of the available resources to execute in a timely fashion without adverse effect on other processes.

f) Configuration Control

In a fault tolerant computer, the current status and the configuration of all elements of the computer must be continuously monitored and controlled by the operating system.

g) Operator and User Interfaces

The OS must provide facilities to interface with the operator and/or user. For a complex system this is not a simple task, especially when a major mode of operation is interactive usage, by the crew members in controlling the progress of a mission.

2-2

INTERMETRICS INCORPORATED • 701 CONCORD AVENUE • CAMBRIDGE, MASSACHUSETTS 02138 • (617) 661-1840

#### Performance Monitoring

This is an often under-emphasized function of an operating system, but it is an especially important one in a new or novel application such as a space station MP. The more sophisticated a system is the greater is the need to measure, evaluate and influence its performance.

Some of these functions will be reviewed again in the light of the following discussion of problems facing the multi-processing operating system designer.

# 2.2 Problems of Multiprocessing

The multiprocessing environment does not pose any difficulties that the designer of an operating system for a multiprogrammed, single processor system has not also had to face and overcome. The MP adds new facets to familiar problems, however, by reason of the concurrent, rather than sequential, execution of the multiple processes within the system. This requires that greater care be taken to prevent damaging interaction between processes at a point of commonality, especially with regard to shared data. Measures taken to protect processes against each other usually affect performance unfavorably. The maintenance of performance near the theoretical limit is, in any case, more difficult for a multiprocessor than for an equivalent simplex computer.

An attractive feature of the multiprocessor is the prospect of increased performance achieved by means other than advances in processor technology, i.e., n similar processors doing the work of one n times as fast. In practice several factors prevent this promise from being fulfilled. If we define "throughput" as the integral over time of the rate of "useful" computation C, then it can be shown that:

$^{\mathrm{T}}\int_{0}^{\mathrm{Cdt}} \geq \frac{^{\mathrm{T}}}{\int_{0}^{\mathrm{n}} (\underline{C}) \, \mathrm{dt}}$

where n is the number of processors. C is a discontinuous function of time, and as n increases, it becomes increasingly difficult for C to remain non-zero for long periods of time. Computation lost whenever C falls to zero may not be made up in time, and the right hand (multiprocessor) integral continuously loses ground to the left hand (simplex computer) integral. The reasons for this are enumerated below.

2-3

h)

### 2.2.1 Parallelism

In order for all n processors to be kept usefully at work, their load must be capable of being organized into n or more tasks which can be executed in parallel, continuously and simultaneously. The degree to which this can be done depends on the parallelism inherent in the work load. Certain types of computation exhibit natural parallelism, e.g., signal processing, where the same operation is applied to multiple sets of input data (promoting the design of so-called Single Instruction Multiple Data (SIMD) computers, for example the Goodyear Associative Processor [1]). But, in general, parallelism must be sought out, identified and utilized. It exists potentially on several levels:

- a) On the "job" level. In a general purpose computer facility, the submitted jobs are normally completely independent of one another, even if they share resources.

- b) Within a job, at the task level.

- c) Within a task, most of the statements are independent of one another.

- d) Within a single statement some computations can be done in parallel.

Parallelism of types c) and d) is not visible to the operating system, because the basic unit of OS is the process (or task). For the type of application being considered for the SUMC multiprocessor, it is not likely that the work load will totally resemble that of a ground based general purpose facility, although it will exhibit more of its aspects than will a simple flight control computer. Parallelism of type a) will probably not be present in sufficient proportion to provide the sole guarantee of full employment for two or more processors. It becomes necessary to deal, additionally, with parallelism at the task The trouble is that problem solving with a computer is, level. in general, a serial process: programmers do not naturally think in terms of concurrent parallel processes in arriving at their solutions, unless such a structure is inherent in the problem. A real time control function may conists of several, more or less independent, activities going on in parallel, e.g., system monitoring, navigation, display processing, and vehicle control. Even so, it is anticipated that there will not be sufficient functions of this type to keep two or more processors fully occupied, all the time.

It is necessary, therefore, to uncover task parallelism that may not be apparent, and even to create parallelism if none

INTERMETRICS INCORPORATED • 701 CONCORD AVENUE • CAMBRIDGE, MASSACHUSETTS 02138 • (617) 661-184C

exists. This imposes a constraint on the programmer, which must be considered deleterious because it is not natural. So it is necessary to assist the programmer with a programming language and a compatible operating system that contain features, attractive to use, that encourage the creation of multiple, independent processes. The use of a block-structured language encourages programs to be written as collections of small, closed subroutines. ALGOL, PL/I and HAL are among the languages that possess this property. In addition to structure, a language can provide a convenient and natural way to interface with the executive by recognizing tasks as syntactical entities. The multi-tasking features of PL/I and HAL encourage the programmer to think as he programs in terms of processes which are amenable to scheduling.

The multiprocessor operating system must support the requirements of parallel tasking by providing adequate communication and synchronization primitives, and by protecting shared data against conflicting concurrent accesses. These requirements are discussed in more detail later.

## 2.2.2 Exclusive Sections

In a general purpose multiprocessor certain operations are concerned with the manipulation of unique system data such as, for example, information maintained by the Process State Controller, which contains the current dynamic state of all proces-Execution of the Process State Controller is an exclusive ses. operation: only one process may perform it at a time. In a simplex computer this is achieved trivially: it is only necessary to inhibit interruption of the single processor by external happenings to assure exclusive execution of the Process State Controller. A multiprocessor requires a more elaborate mechanism to prevent the simultaneous execution of such critical functions by two or more processors. Such mechanisms cause the conflicting processes to become serialized in time, each being admitted to the critical section through interlocking turn-stiles (a generalized mechanism is described later). The net effect is that whenever two or more processes wish to enter an exclusive section, only one may do so and continue executing: the other(s) must If the exclusive section is designed to inhibit the alterwait. nate assignment of the processor (e.g., if it is the Process State Controller), then throughput temporarily falls until the other processor is through with the exclusive section. This loss of throughput cannot be made up again. Note that in a batch environment conflicts of this type are rare, but in a real time system of short tasks, with frequent process state changes, the probability of conflict may become significant. This precipitates the following quandary: to encourage parallelism a multiprocessor program should consist of many concurrent tasks, but to

avoid critical section conflict it should be organized into as large a serially-executable piece as possible!

#### 2.2.3 Shared Data

There is a problem with shared data, aside from the need to protect it from simultaneous modification. It is associated with the creation of copies of shared data. In many computer designs, performance improvements have been achieved by localizing lengthy sequences of operations within the fast logic of the processor, rather than executing out of main memory. (The cache memories of the IBM 370 series [2] and the task memory of the Navy's AADC [All Applications Digital Computer][3] are examples of localized processing.) The problem arises because data is maintained local to the processor. If the data is shared with other processes, changes in the original or any of the copies must be reflected in all. Some means must be found either

a) to allow one process access to another's local storage,

- b) to update all copies of shared data at the same time or

- c) to prevent old values from being used by other processes until updating is performed.

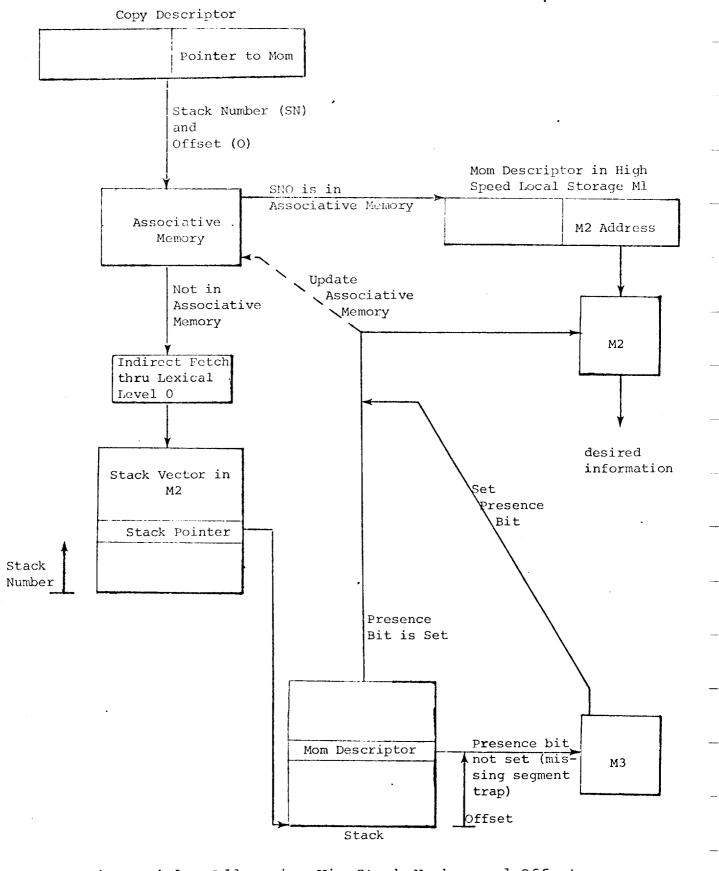

It should be pointed out that this phenomenon is encountered whenever copies of shared data are created in any sysin the Burroughs B6700 series the problem arises through tem: its use of descriptors. These are maintained in the stacks of individual processes. Whenever a descriptor needs to be changed (it is a common occurrence in a virtual memory system for a descriptored item to be transferred to back-up storage: the address field of its descriptor most be modified to reflect this change of whereabouts), all processors in the B6700 are stopped, and all process stacks in main memory are searched for copies of the particular descriptor. The B6700 was not designed as a real time controller so the ensuing loss of processing time was not considered objectionable by the designers. It is a different matter for a space station computer, however. The Multiprocessor design developed by Intermetrics [4] employs a unique approach to a similar problem. The copy of a descriptor may be maintained in an associative memory local to a processor. This avoids accessing the descriptor through three levels of indirection each involving main memory references. Changes in the descriptor are very quickly signalled by the provision of a specific machine instruction which cancels the appropriate entry in the associa-The Intermetrics multiprocessor avoids local copies tive memory. of the data itself, and thereby foregoes the potential performance advantages of local buffer or cache-type processing.

INTERMETRICS INCORPORATED • 701 CONCORD AVENUE • CAMBRIDGE, MASSACHUSETTS 02138 • (617) 661-1840

#### 2.2.4 Conflict Over System Resources

The most critical resource is main memory. As the number of processors increases, the possibility of conflict between them over the use of memory increases. As in the case of shared data, a resolution of conflict results in one or more processors losing processing time, and the right hand integral of the expression for throughput given earlier again loses to the left hand. The device of interleaving the modules of a memory system can be used to minimize the delays incurred by conflict, but it exacts a cost in added hardware complexity. Its effect is to randomize memory usage and thus to obtain stationary behavior. Another approach is to partition memory amoung the various processes so that processors tend to execute out of physically separate modules: i.e., much the memory usage very deterministic. This technique implies a sophistication of the operating system, a well-known job stream, and a memory system of sufficient modularity.

The network interconnecting processors, memories and I/O units is a more critical element in a multiprocessor than in a simplex system. With more than one processor requesting memory at a time, this bus itself becomes a source of conflict. It would seem that a technique that lowers the frequency of use of the bus would lessen the probability of such conflict. For example, the use of a cache memory, by encouraging local execution, would appear to make bus use less frequent. However, analysis shows that the probability of bus conflict actually increases with increasing speed of the cache, thereby defeating any performance advantage.

In summary, techniques devised to minimize conflict in a multiprocessor are susceptible to the following drawbacks, any or all of which combine to prevent the multiprocessor throughput from equalling that of the equivalent simplex processor:

- a) Increased hardware complexity and cost,

- b) Increasing operating system sophistication, usually accompanied by increased overhead in space and time.

- c) Reduced throughput due to delays introduced to resolve conflict.

The more processors in the system, the more marked is this effect. Only in a particular application, for which the characteristics of the work load can be anticipated, is it possible to deduce the number of processors required to achieve a given performance cost effectively. In the absence of such information about the environment of the multiprocessor, this

limit is very difficult to determine. As a result, almost all practical designs of multiprocessors to date have been limited to the degenerate case of two processors. Some designs have even dedicated functions or resources to each processor in order to avoid some of the above problems, resulting in configurations of dual computers rather than dual processors.

#### 2.2.5 Overhead

The preceeding sections have cited several factors that contribute to the complexity of functions that a multiprocessor operating system is required to perform. Each factor contributes to the overhead of computational time and memory space consumed by the operating system. Matters are further aggravated because the many activities going on simultaneously in a multiprocessing environment take on the characteristics of a queueing problem: their deleterious effects are in general worse than additive, i.e., the loss in real throughput is a non-linear function of the number of contributing overhead mechanisms.

But to end this section on a positive note, it should be realized that this depressing parade of multiprocessing difficulties has a corollary: small efforts to limit the damaging effects of each of the mechanisms discussed in this section can yield dramatic improvements in throughput because of the exponential nature of their interaction.

## 2.3 Exclusion and Synchronization

Any multiprogrammed system requires operating system primitives for the communication and mutual protection of the concurrent processes. In a multiprocessor, these activities can be actually time-concurrent and these primitives must be implemented in a combination of hardware and software. The problem of protection against unwanted interactions will be reviewed first, followed by a discussion of synchronization.

#### 2.3.1 Exclusion Primitives

In a simplex computer a basic exclusive operation may be implemented in software, but a multiprocessor needs hardware assistance for such an operation, because of the true timeconcurrency of execution of two or more processes. The hardware must be capable of reading the value of a variable, and then rewriting the variable with a new value in one uninterruptible operation. An example of such an instruction is the TS (Test and Set) of the IBM 360 series, which writes all ones into a specified byte and sets a condition code with the original

contents. The Burroughs B6700 RDLK (Read with Lock) instruction, which stores the contents of the B register into the location whose address is contained in the A register, but leaves the previous contents of the location in the B register, is closer to a generalized non-divisible read and write operation.

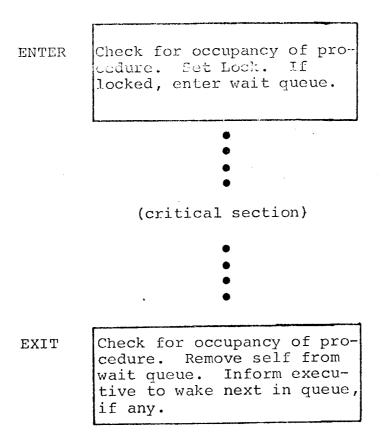

The actions of a set of general operating system procedures designed to provide the exclusion primitive are as follows:

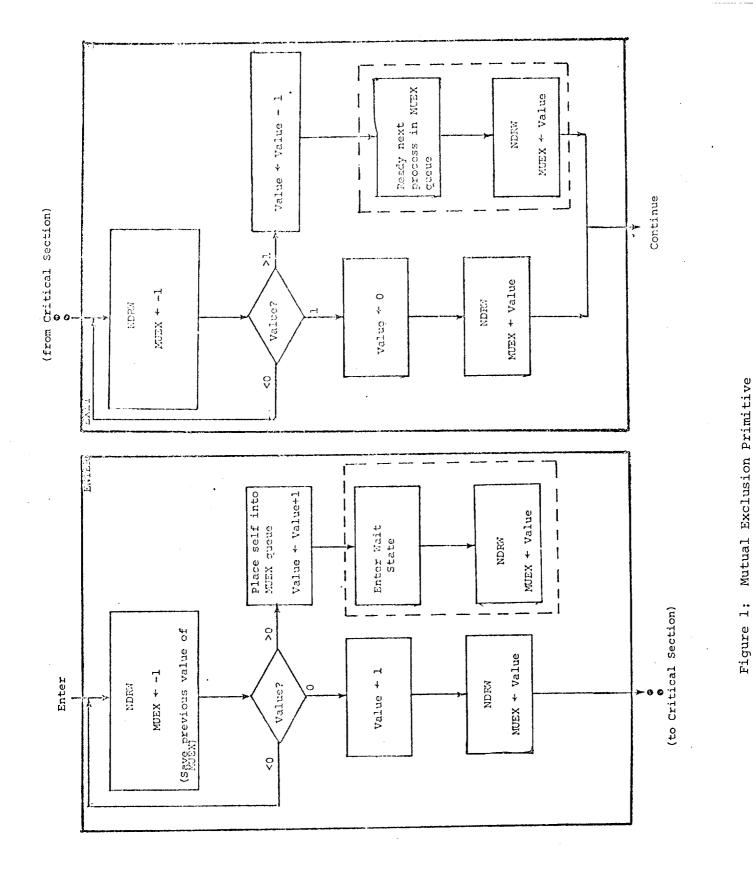

How these actions are implemented using a fictitious non-divisible read and write instruction NDRW is illustrated in Figure 1. Let the execution of NDRW exchange the contents of the operand, MUEX, with the contents of the accumulator. MUEX may contain the following values:

- 0 No process executing critical section (i.e., section is "free")

- Critical section is being executed by one process

2-9

-

1

# 2~10

- 2,3,...n Critical section is being executed by one process, and 1,2,...n-1 are waiting to gain access. Requires a MUEX queue structure to be maintained by OS.

- negative Procedures ENTER or EXIT are being executed by a process. (The OS primitive itself must be protected against multiple use.)

The actions surrounded by dotted lines indicate the execution of the Process State Controller function. Note that the final updating of MUEX in cases where a process is to be placed in the wait state, or readied to execute the critical section, must be done within the Process State Controller to prevent interruption of the sequence.

This exclusion mechanism must be expanded if it is required to accomodate the comprehensive Update Block capability, for controlling the accessing of common data, provided in the HAL language [5]. It is not always necessary to prevent all types of access to shared variables: a shared variable can be <u>read</u>, as long as it is not actually being changed. The ability to differentiate between types of access reduces the time for which a requesting process must be made to wait, with consequent improvement in throughput. The HAL Update Block is in effect a modified form of critical section. Every variable that is addressed within an Update Block has associated with it a "locktype" attribute. The lock can assume the following states:

a) Free: Unlocked

b) Read: Accessed for reading only

c) Copy: Accessed for modification

d) Write: Being modified

A variable that is to be modified is first copied, and all intermediate computations are performed on the copy. This is the meaning of the "Copy" state. Final values are written from the copy to the actual variable after the state of the lock has been raised to "Write". The testing and setting of the states of locked variables requires the use of the NDRW instruction. A requesting process is allowed into the Update Block only if the type of access requested is compatible with the current state of all locks within the block. For example, a request to read the variables is allowed if the current state of all locks is "Free", "Read", or "Copy", but is not allowed if any are in "Write".

An operating system mechanism to implement Update Blocks involves the maintenance of linked queues (see Figure 2). Every locked variable has associated with it a queue of requesting processes, each identified with its individual access type. All queue elements associated with a given process are also linked, to facilitate the response to changes of state of the processes.

The Intermetrics design of a multiprocessing operating system [4], defined a pair of generalized primitives, ACQUIRE and RELEASE, of the form: ACQUIRE (Mode, Category, Name, Access) where each of the terms has the following meaning:

- a) Mode: The calling process is placed in the Wait state if access is not immediately possible, or an immediate return may be specified with an indication of why access could not be allowed. b) Data, code or device. The ACQUIRE primi-Category: tive is applicable to the protection of shared data, the implementaiton of exclusive sections, or the use of a shared device such as a printer. c) Identifies the item in the category, e.g., Name:

- d) Access: Shared, update or exclusive access request.

- These are analogous to HAL's Read, Copy, and Write lock type states.

It is possible to define any type of required exclusive operation in a given system with these two primitives.

# 2.3.2 Synchronization

In order to provide for communication between parallel processes of a multi-tasked environment it is convenient to invoke the concept of an "event". An event is a variable whose state reflects the occurrence of an activity within the system, e.g., the completion of a lengthy computation or the arrival in memory of a previously requested item of I/O. The process awaiting the activity is associated with the event. The "signalling" of the event results in the process being made ready to continue. For illustration, let Tasks A, B and C be three independent tasks, all scheduled during the execution of some master Program. Suppose it is appropriate to schedule Task C only when certain computations have been completed by Tasks A and B. Tasks A and B may be executing on separate processors, and thus be unaware of

one another. In which case, they cannot easily cooperate in the scheduling of Task C. However, if each were to signal an event on completion, e.g., EVENT\_A and EVENT\_B respectively, then the event mechanism can provide the synchronization that causes Task C to be scheduled as soon as both EVENT\_A and EVENT\_B have been signalled.

The language multi-tasking features that were advocated earlier to help keep a multiprocessor busy are supported in PL/I, ALGOL and HAL by event mechanisms of varying sophistication. The Intermetrics multiprocessor design [4] specified a very comprehensive event structure which enabled complex logical expressions to be evaluated as event signals. In this design events are controlled by primitives of the form

$$\begin{cases} \text{SET} \\ \text{RESET} \end{cases} \quad (\text{E, n, E}_1, \text{E}_2, \dots, \text{E}_m) \end{cases}$$

which is interpreted as "set (reset) event E when n of the events in the list  $E_1$  through  $E_m$ , are signalled." If n = m, this expression is the boolean "and" of all listed events, and if n = 1it is the "or". The primitives also have a simpler form

$$\left\{\begin{array}{c} \text{SET} \\ \text{RESET} \end{array}\right\} \quad (E)$$

Response to the signalling of events is basically of two forms:

WAIT(n,  $E_1, E_2, ..., E_m$ )

and

$$ON(n, E_1, E_2, ..., E_m) < code >$$

In the first, as the WAIT is executed the process is placed in the Wait state until the event expression becomes true. The second statement causes an interruption of the process as soon as the expression becomes true, to execute the procedure specified in the "code".

The implementation of an event structure involves multiply-linked queues of event elements which allow the associations between the processes involved in declaring, signalling and responding to events to be established, executed, and removed in a dynamic fashion. It is perhaps superfluous to point out that such a mechanism in a multiprocessor environment requires processors to be able to interrupt one another. This ability is provided, for example, in the Burroughs B6700 by the "HEYU", and in the RCA 215 by the "INTERRUPT CPU" instructions.

#### 2.4 Scheduling

The scheduling function of the operating system ensures that processes are prepared for timely execution with due regard to their relative importance. It involves some of the functions of Process State Control and Resource Allocation defined earlier. This section will discuss briefly the following aspects of this function:

- a) Ensuring that computation time and space are properly apportioned among the processes according to predetermined needs, while maintaining an optimal balance between the conflicting requirements of throughput, efficiency, and response. Throughput is defined as the amount of useful work accomplished by the total multiprocessor system, efficiency is the degree of utilization of the basic components of the system (e.g., processors, memory modules, I/O devices), and response is the ability to react to a given stimulus.

- b) Ensuring that competition between processes in their demands for resources do not produce catastrophic conditions, such as deadlock or thrashing.

- c) Preventing the resulting computational overhead, especially of time in a real-time control system, but also of space, from becoming excessive (the definition of "excessive" is not attempted here!).

# 2.4.1 Space and Time Allocation

The computational activities in a space station multiprocessor are expected to fall into the following categories:

| Category    | Characteristic<br>Response Range | Time<br>Criticality | Examples                                                                                      |  |  |

|-------------|----------------------------------|---------------------|-----------------------------------------------------------------------------------------------|--|--|

| Batch       | 10 secs-mins.                    | non-critical        | Lengthy computations. Off line experiment data processing                                     |  |  |

| Interactive | 0.l sec-10 secs.                 | non-critical        | Crew operational sequences.<br>Time sharing by scientific per-<br>sonnel.                     |  |  |

| Real Time   | 1 ms-100 ms                      | non-critical        | Control of scientific experi-<br>ments. Operational equipment<br>status monitoring            |  |  |

| Real Time   | l ms-100 ms                      | critical            | Operational equipment servicing:<br>strapdown IMU. Closed loop con-<br>trol: autopilots, etc. |  |  |

Processing tasks in the batch category can, to an extent, ignore the constraint of time. The allocation of memory space or other system resources such as common data, input file, I/O devices, processors, can be considered with more freedom. The presence of this category in the total work load can provide a measure of global optimization in the use of system resources to maximize efficiency.

The time-critical real-time tasks can not make such compromises. Resources <u>must</u> be ready when needed. The need is often (but not always) randomly determined. Unless it is composed of highly repetitive tasks, the real-time component of the work load prevents high values of throughput and efficiency from being attained.

A work load consisting of components from each category must be so arranged and presented to the computer system that all tasks can get sufficient cuts at the system's processing resources. Obviously, no amount of intelligence built into an operating system will supply enough computational resources to a work load whose demands exceed the capability of the machine. An operating system can be designed to contain features and to operate in a way that matches the characteristics of the work load. But it remains the responsibility of the user of the system to assign a given work load to the machine in such a way that it does not overload the system.

Task scheduling can be approached from two extremes:

a)

Synchronous, or time slot scheduling. Each task is allotted a different, but fixed, interval of time for

execution, which is available at multiples of fixed minor cycle intervals.

b) Demand Scheduling. Tasks are allocated processors and other resources on demand, at execution time, according to the needs and importance of the task and the availability of the resources. Tasks are differentiated in importance by a priority value which stays as initially assigned, or changes as a function of time or the tasks' status.

The advantages of the synchronous approach are:

- a) Minimal overhead, since scheduling is pre-determined;

- b) The scheduler is simpler, being essentially table driven;

- c) The fixed schedule of task execution eliminates problems associated with code and data sharing, and does not require re-entrant code;

- d) The load may be evenly distributed over the available time;

- e) The deterministic behavior makes system verification easier.

The difficulties associated with it are:

- a) It is difficult to structure programs so that they may be time-sliced;

- b) Each time slice must be sufficient to accomodate the worst case, so on the average will be under-utilized;

- c) It is difficult to accomodate response to random events such as crew inputs. Response to system failures is especially difficult, unless recovery from all classes of failures is pre-scheduled.

- d) The structure is inflexible to change.

These disadvantages are all overcome by the demand scheduling approach, which, however, suffers from an increased degree of difficulty because of its greater complexity, and because it is more difficult to verify.

In a functional design of an executive for the Space Shuttle central computer, Intermetrics has proposed a combined synchronous and demand scheduled approach [6]. The repetitive, time-critical functions which can be implemented in short,

complete sections of code are executed by a synchronous "foreground" scheduler driven by timer interrupt, at 40 ms intervals. The majority of the remaining tasks are scheduled on demand as a "background" activity according to pre-assigned priority values. Communication between foreground and background is by an event mechanism, in essence similar to that described in section 2.3.2.

# 2.4.2 Deadlock Prevention

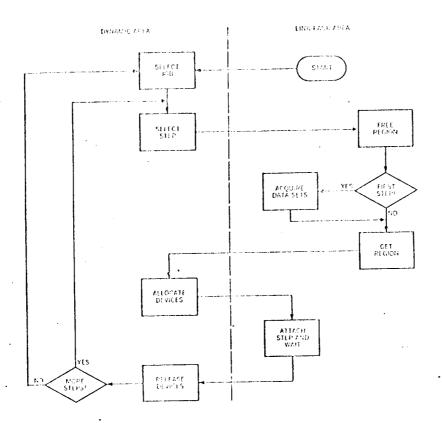

OS/360 has three resources to allocate to each job/step. These are core storage, data sets and peripheral devices. The allocation algorithm is summarized in Figure 3. Note that all data sets for the entire job are allocated at job initialization time and are bound for the duration of the job. In addition, all devices are allocated at step initialization time and are bound for the duration of the step. This approach may be costly since some of the resources allocated to a task may remain unused for long periods.

Alternatively, resources may be allocated dynamically, i.e., while the process is running. Unfortunately, now deadlock prevention becomes a more difficult problem. However, some practical solutions have been suggested [7], although a time overhead must be paid if they are implemented.

The suggested methods involve keeping track of the state of the system by means of state graphs or matrices. When a resource is requested by an executing process, the availability of the resource is checked. If it is presently unavailable, the algorithm must determine if it is safe to put the requesting task in the wait state. To determine this, it checks the state matrices of the system as they would be if the request were enqueued for the resource. When a safe condition results, the request is enqueued, and the task is placed in the wait state. On the other hand, if an unsafe condition results, the request must be denied and the task so notified. The task can then decide if it wishes to cease execution or it if can proceed without the resource. (Some subtle problems to be aware of, in implementing such an algorithm have been overlooked by several authors and are discussed by Holt [8].)

While it is easy to see that dynamic allocation is most economical in the amount of time system resources are unavailable, some time overhead must be paid each time a process requests a resource. The OS must check the state matrices to determine if safe states will result. This process can be lengthy for a system with many resources and many ready tasks. One must remember here that the overhead is really that time

used for dynamic allocation over and above that which would otherwise be spent for allocation at job and step initialization times as described above.

Unfortunately, no analytic studies or simulations of these algorithms have been done to evaluate overhead costs. However, with careful thought given to the implementation of a dynamic algorithm, its overhead can be held to a minimum. In any case, the advantages of dynamic allocation would seem to overshadow any time overhead that results.

# 2.5 Memory Management

Management of the use of memory is potentially the most critical activity of an operating system. It is very dependent on:

- a) the structure and characteristic behavior of the application software. If the work load is well known and dynamically predictable, especially with regard to its memory requirements, allocation of space can be predetermined, by pre-planned overlays for example.

- b) The system architecture. If sufficient operating memory is provided to accomodate all programs at all times, dynamic allocation problems are eliminated. If, however, a virtual memory design is adopted for its potential simplification of programming and its cost effectivity, the operating system becomes intimately involved in creating and allocating memory space, and its detailed design is further affected by the technique adopted for addressing the virtual memory system.

- c) Memory technology. The architecture of a virtual memory system and the functions of its operating system are significantly different for secondary storage with moving head disks, than for solid state block-oriented, random access devices such as the experimental magnetic bubble domain memory.

Although memory management can assume a critical role in determining operating system size and efficiency, its problems cannot be addressed in detail in the absence of a memory hierarchy definition. The following review of methods of operating memory utilization is presented to underscore some of the factors involved in providing increasing levels of operating memory utilization by multiplexing.

# 2.5.1 Operating Memory Multiplexing

The following examples describe practical applications of a number of techniques for increasing the utilization of operating memory.

2.5.1.1 <u>Non-multiplexed Memory</u>: In a non-multiplexed system the process of "assembly" of the program serves both to establish the mapping between names found in "subroutines" (which are simply separately maintained units of program code), and the mapping between names and physical locations in memory. At the conclusion of the assembly, the mapping information is completely distributed, and is saved and accessible only as a diagnostic aid, for the computer simulator, for example. Most flight control computers are of this design, usually because of their modest total memory requirements, typically 8K to 32K words.

2.5.1.2 Partitioned Memory: A simple form of memory multiplexing is used when the physical memory is large enough to support the requirements of more than a single program at a time. The OS/360 MFT and MVT systems implement fixed and variable partitions respectively. The normal objective of concurrently-loaded programs is to provide more efficient use of the processor by increasing the chances that some program can use the CPU when another is waiting for completion of I/O operations.

As in sequential execution, the mapping between names and locations is applied in all places at the time of loading, and the map is of no further use to the execution of the program.

To further increase processor efficiency, a high-speed secondary storage device may be used for "core-swapping". This involves writing the contents of a partition out to the device before its execution has been completed in order to make room to bring in some other program ready to run. Because the namelocation mapping is not dynamically applied, the information must be returned to its original location when its execution is to be resumed.

2.5.1.3 Partitioned Memory with Relocation Registers: Under the above mechanization, the application of the name-location map takes place at one time, but over many spatial places. This has the advantage of getting the mapping finished; however, it has the disadvantage that the mapping is not readily reversed or modified. Several systems (e.g., PDP-10, Univac 1108) use an alternate scheme which re-applies the mapping each time. This

is achieved by providing one or more relocation registers, whose function is transparent to the software, which supply offset values to be combined with logical or virtual addresses generated during the program's execution. A disadvantage of this approach is that it requires additional hardware to perform the combining as part of instruction execution. However, it has the valuable characteristic that the mapping remains available for modification, so that program and data sections may be relocated in the operating memory and only the relocation values need to be changed in the process. Thus, storage in use can be compacted to collect available space into one contiguous piece when necessary to find room to load an additional program.

As in the partitioned memory scheme, "core-swapping" may be used for additional multiplexing. However, the use of the relocation registers makes it possible to return the information to any convenient location, rather than the precise place from which it was written.

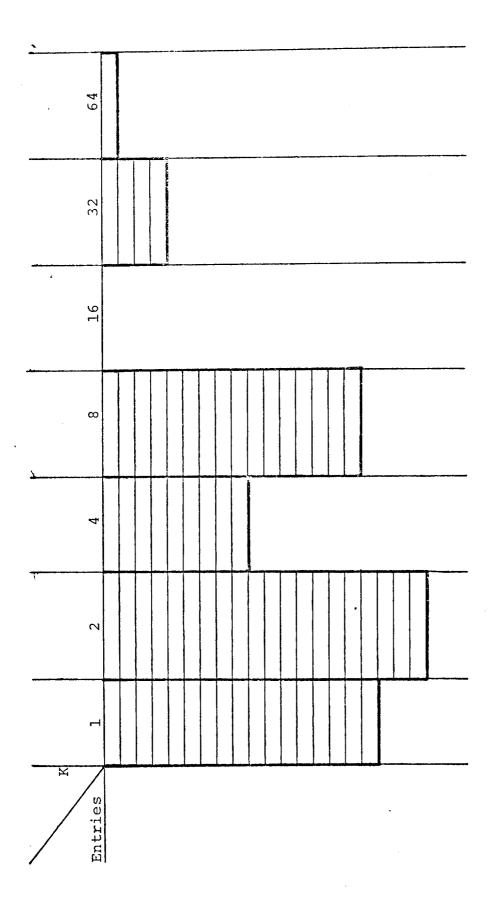

2.5.1.4 Paging: An alternate to the use of relocation registers is to divide the program and data space, linearly arranged, into a series of "pages" of a fixed size, ordinarily a power of 2 (e.g., XDS Sigma 7, CDC 3800). In address formation, a group of bits from the logical address is used to select a pagelocation word from an array called a page-table; this word contains the memory-address of the page if it is currently there. Otherwise, an indication of the absence of the page is provided, along with the secondary-storage location at which the page may be found. The physical storage space is thus divided into fixedsize page frames, and the mapping between names and physical location is dynamically applied. A strong advantage of this approach is that logically contiguous space need not be physically contiguous, nor need it even all be present. The relaxation of the pages for occupancy of storage space by implementing some measurement of page reference behavior (with hardware help). Pages appearing to be less needed may be overlaid with more lively ones.

Because all page frames are the same size, space management is simple, and requires only modest overhead at execution time. On the other hand, the page boundaries fall at arbitrary locations in code or data, rather than at logical divisions. The average usefulness of words in a page is therefore reduced, since a logical entity may occupy only a small part of a page, or cross a page boundary.

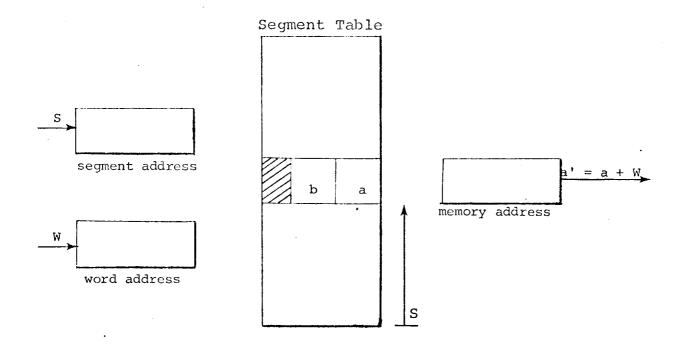

2.5.1.5 <u>Segmented Addressing</u>: The simplest segmentation on a logical (if not operational) basis is the scheme used in the Burroughs B6700 and its predecessors. Each program block is compiled into a virtual address space of its own, called a segment; locations may then be accessed by specifying a segment number and an offset from the beginning of the segment. In execution, the name-location mapping is applied dynamically. Each segment has a segment descriptor which contains the physical location of the beginning of the segment. However, this descriptor can also contain an indication that the segment is not in storage at the moment; in this case, the address in the descriptor is the secondary storage location at which the segment may be found.

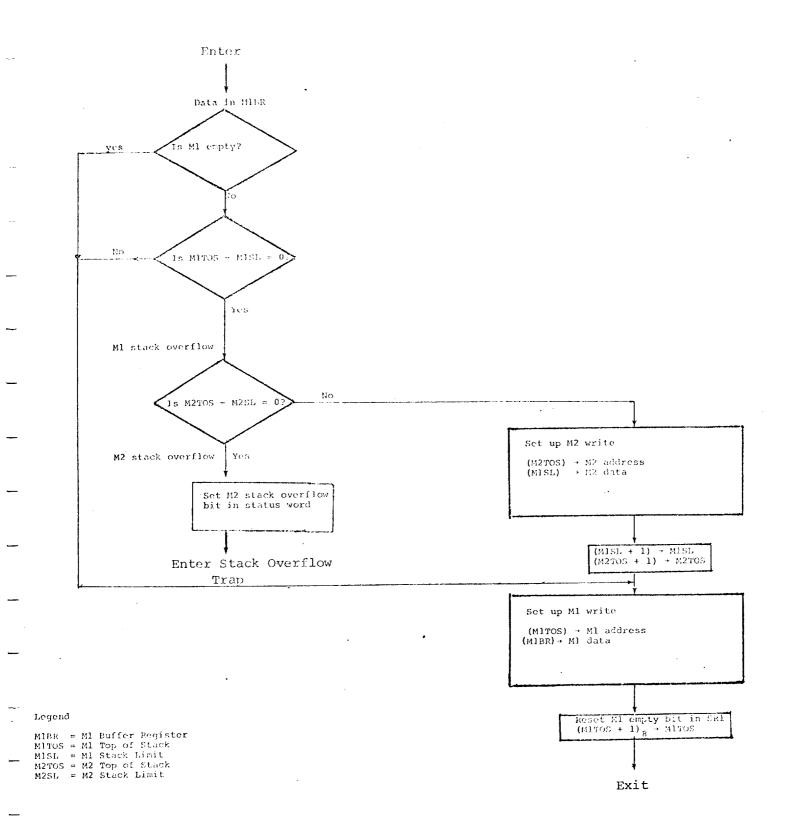

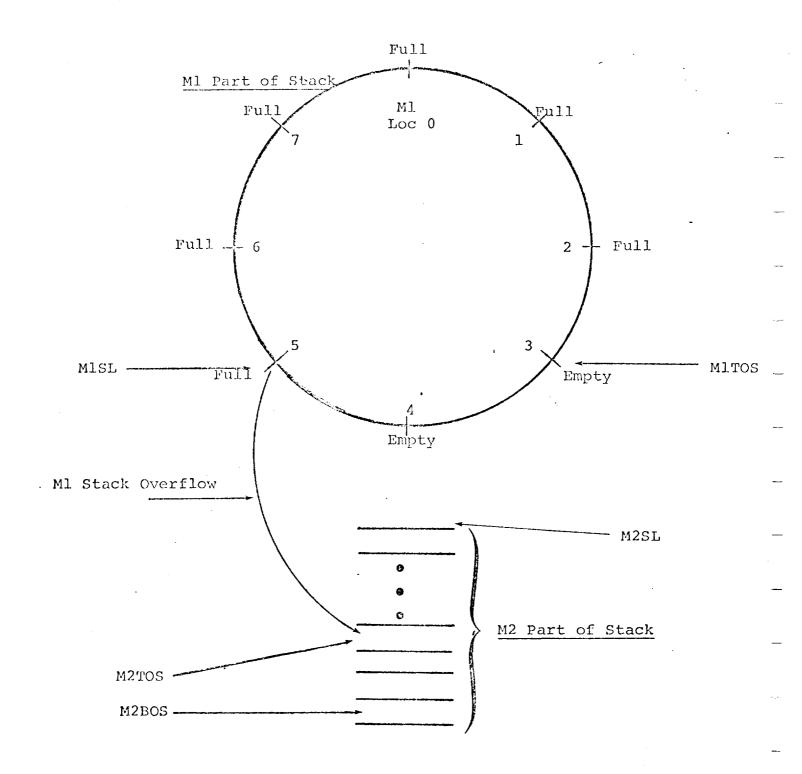

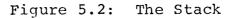

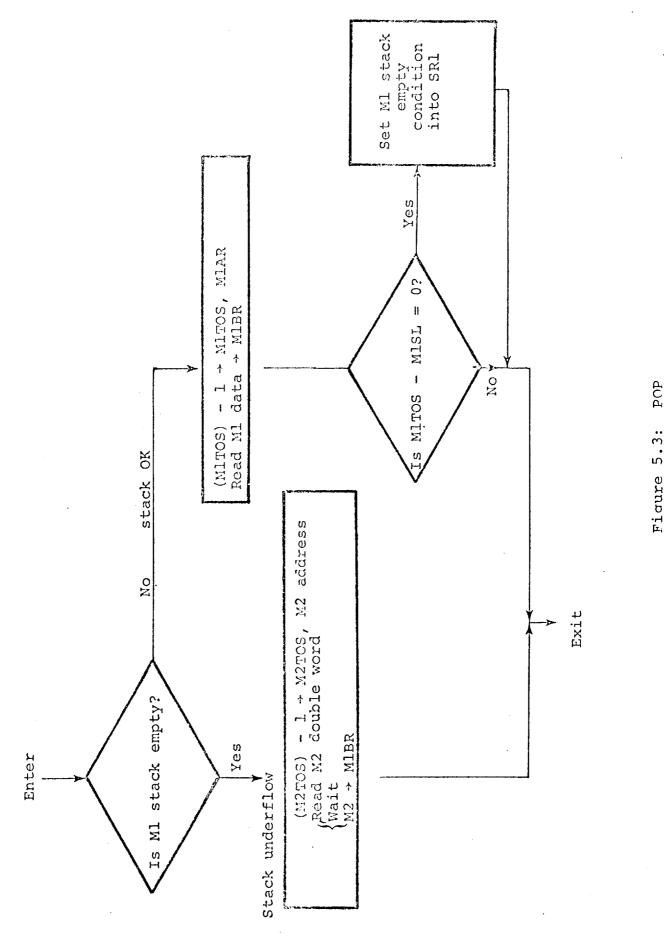

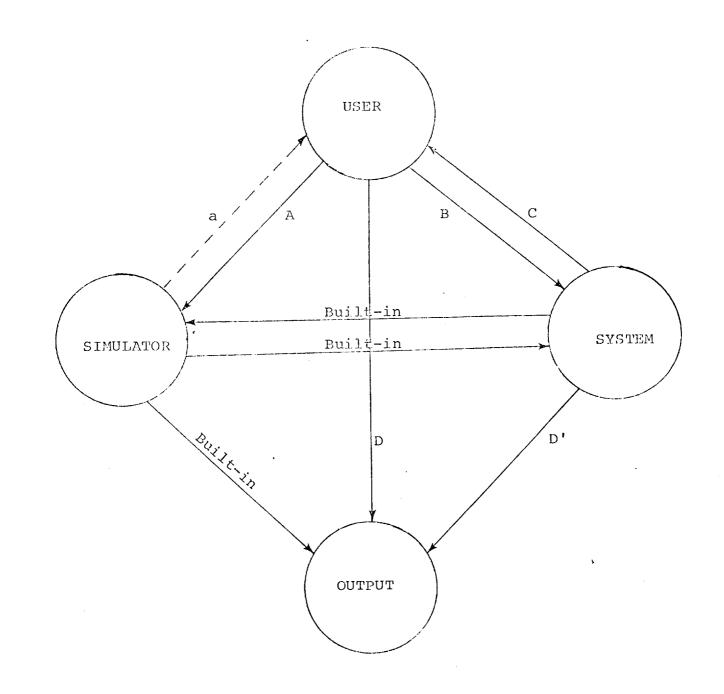

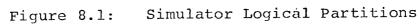

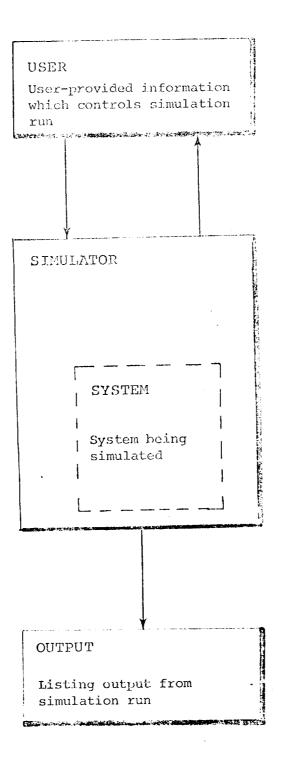

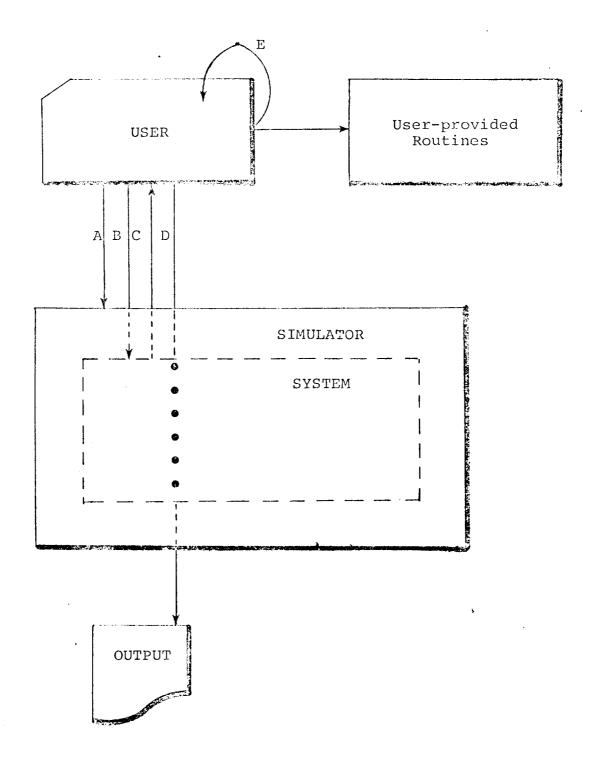

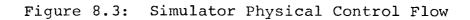

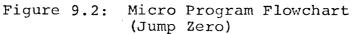

An advantage of this type of segmentation is the direct relationship between the segment size and the logical unit of program or data it contains. This characteristic increases the average usefulness of words transferred in a segment load.