STAR 4-B-73

# **OPTICAL MODULATOR SYSTEM**

## J. Brand

McDonnell Douglas Astronautics Company - East

Box 516

# St. Louis, Mo. 63166

(NASA-CR-130195) OPTICAL MODULATOR SYSTEM Final Report (McDonnell-Douglas

N73-20569

rinal Report (McDonnell-Douglas Astronautics Co.) 93 p HC \$6.75

CSCL 20E

Unclas 67496

October 1972 Final Report

Prepared for

GODDARD SPACE FLIGHT CENTER

Greenbelt, Maryland 20771

| 1. Report No.                                                                                                                                                                                                                                                                         | 2. Government Acces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | sion No.                                                                                                                                                                                                                                                                                                                                           | 3. Recipient's Catal                                                                                                                                                                                                      | og No.             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 4. Title and Subtitle                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                    | 5. Report Data Octo                                                                                                                                                                                                       | ber 1972           |

| OPTICAL MODU                                                                                                                                                                                                                                                                          | JLATOR SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                           |                    |

|                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ı                                                                                                                                                                                                                                                                                                                                                  | 6. Performing Organi                                                                                                                                                                                                      | zation Code        |

| 7. Author(s)  J. Brand                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                    | 8. Performing Organi                                                                                                                                                                                                      | zation Report No.  |

| 9. Performing Organization Name and Ac                                                                                                                                                                                                                                                | ldress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                    | 10. Work Unit No.                                                                                                                                                                                                         |                    |

| McDonnell Douglas Astr                                                                                                                                                                                                                                                                | ronautics Company                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <sup>,</sup> -East                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                           |                    |

| Box 516                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                    | 11. Contract or Grant                                                                                                                                                                                                     | , No. 2<br>5—11474 |

| St. Louis, Mo. 63166                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                    | 13. Type of Repair as                                                                                                                                                                                                     |                    |

| 12. Sponsoring Agency Name and Addres                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                           | Report             |

| Goddard Space F                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                           | Report             |

| Greenbelt, Mary                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                    | 14. Sponsoring Agend                                                                                                                                                                                                      | ry Code            |

| Attn: L. O. Cau                                                                                                                                                                                                                                                                       | dill, Code 524.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                           |                    |

| electrooptic a supply and signodulators convith MECL logs thermal environt compens use two lithin That is, the land then is reanalyzer.  The signate are capable of voits at a may The digital searrial NRZ dat is also include generates PN searrial NRZ for The worst was 15:1 with | ates at data rates up to modulator, a 1.06 mm elegnal processing electron ntain solid state driver ic levels, temperature comment for the modulator sation to maximize the eum tantalate crystals calaser beam enters the moeflected back through both all processing electronics digitizing analog signiximum rate of 80 megasam samples are serialized anta source for the modulated in the signal process sequences with lengths beformat at rates up to 400 to case dynamic extinction 727 transmission. The | etrooptic modulator ics with power suppl s which accept digit to trollers to mainta crystals, and autom xtinction ratio. The scaded in a double p dulator, passes throth crystals to the p s include encoding e als between the limit ples per second with d made available as tors. A pseudorando sing electronics. Tetween 31 bits and 3 D Mbps. | with power y. The al signals in a stable atic elec- e modulators ass configuration. ugh both crystals olarization  lectronics which t of + 0.75 5 bit resolution. a 400 Mbps (PN) generator his data source 2,767 bits in |                    |

|                                                                                                                                                                                                                                                                                       | s 13:1 with 50% transmiss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                           |                    |

| 17. Key Words (Selected by Author(s))  Optical Modulator Lithium Tantalate electrooptic of Pulsed Digital laser communicati Pseudorandom generator Encoding electronics                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18, Distribution S                                                                                                                                                                                                                                                                                                                                 | tatement                                                                                                                                                                                                                  |                    |

| 19. Security Classif (of this report)                                                                                                                                                                                                                                                 | 20. Security Classif. (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | of this page)                                                                                                                                                                                                                                                                                                                                      | 21. No. of Pages                                                                                                                                                                                                          | 22, Price*         |

| UNCLASSIFIED                                                                                                                                                                                                                                                                          | UNCLASS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IFIED                                                                                                                                                                                                                                                                                                                                              | 85                                                                                                                                                                                                                        |                    |

<sup>\*</sup>For sale by the Clearinghouse for Federal Scientific and Technical Information, Springfield, Va. 22151

#### ABSTRACT - OMS FINAL REPORT

This program included the fabrication, test, and delivery of an optical modulator system which will operate with a mode-locked Nd:YAG laser indicating at either 1.06 or 0.53 micrometers. The delivered hardware operates at data rates up to 400 Mbps and includes a  $0.53 \mu m$ electrooptic modulator, a 1.06 µm electrooptic modulator with power supply and signal processing electronics with power supply. modulators contain solid state drivers which accept digital signals with MECL logic levels, temperature controllers to maintain a stable thermal environment for the modulator crystals, and automatic electronic compensation to maximize the extinction ratio. The modulators use two lithium tantalate crystals cascaded in a double pass configuration. That is, the laser beam enters the modulator, passes through both crystals and then is reflected back through both crystals to the polarization analyzer.

The signal processing electronics include encoding electronics which are capable of digitizing analog signals between the limit of  $\pm$  0.75 volts at a maximum rate of 80 megasamples per second with 5 bit resolution. The digital samples are serialized and made available as a 400 Mbps serial NRZ data source for the modulators. A pseudorandom (PN) generator is also included in the signal processing electronics. This data source generates PN sequences with lengths between 31 bits and 32,767 bits in a serial NRZ format at rates up to 400 Mbps.

The worst case dynamic extinction ratio of the 0.53  $\mu$ m modulator was 15:1 with 72% transmission. The 1.06  $\mu$ m modulator worst case extinction ratio was 13:1 with 50% transmission.

### CONTENTS

|                       |              |                                              | Page |

|-----------------------|--------------|----------------------------------------------|------|

| 1.                    | INTRODUC     | TION                                         | 1    |

| 2.                    | PERFORMA     | NCE SUMMARY                                  | 5    |

| 3.                    | HARDWARE     | DESCRIPTION                                  | 9    |

| 3.1 0.53 µm Modulator |              |                                              | 9    |

|                       | 3.1.1        | Modulator Subassembly                        | 9    |

|                       | 3.1.1.1      | Crystal Material Selection                   | 16   |

|                       | 3.1.1.2      | Crystal Configuration                        | 18   |

|                       | 3.1.2        | Modulator Driver                             | 19   |

|                       | 3.1.3        | Temperature Controller                       | 20   |

|                       | 3.1.4        | Automatic Electronic Compensator             | 21   |

|                       | 3.1.5        | Manual Compensator                           |      |

|                       | 3.1.6        | Power Supply                                 | 22   |

| 3.2                   | 1.06 µm.     | Modulator                                    |      |

|                       | 3.2.1        | 1.06 µm Modulator Subassembly                | 22   |

|                       | 3.2.2        | Modulator Driver                             | 22   |

|                       | 3.2.3        | Temperature Controller                       | 24   |

|                       | 3.2.4        | Automatic Electronic Compensation            | 24   |

|                       | 3.2.5        | Manual Compensator                           | 26   |

|                       | 3.2.6        | Power Supply                                 | 26   |

| 3.3                   | Signal P     | rocessing Electronics                        | 26   |

|                       | 3.3.1        | Pseudorandom Generator                       | 27   |

|                       | 3.3.2        | Dual Sample Hold                             | 29   |

|                       | 3.3.3        | Analog/Digital Converter                     | 31   |

|                       | 3.3.4        | Parallel/Serial Converter                    | 31   |

|                       | 3.3.5        | Timing and Control/Multiplexer               | 33   |

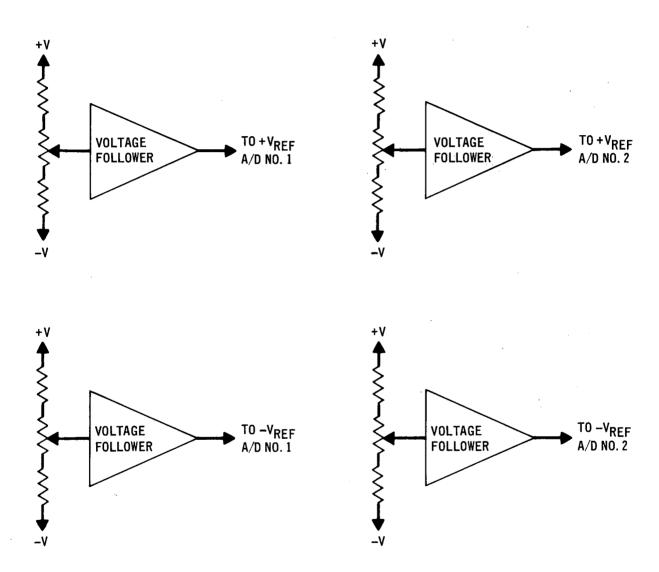

|                       | 3.3.6        | Reference Voltage Generator                  | 34   |

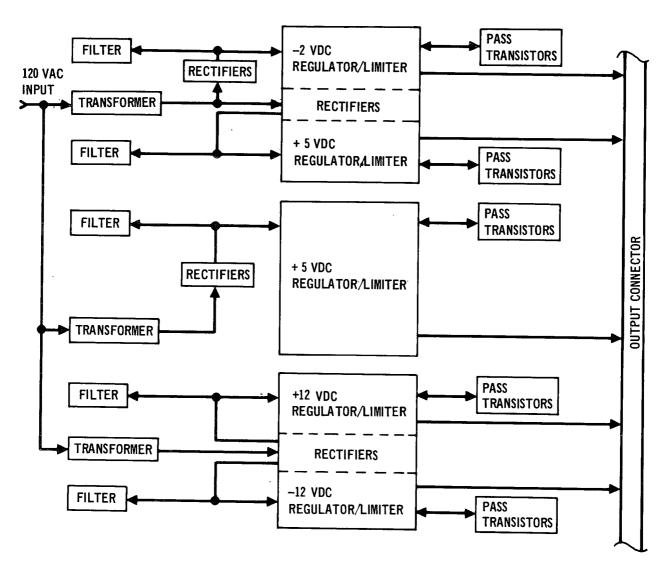

|                       | 3.3.7        | Signal Processing Electronics Power Supply   | 36   |

| 4.                    | OPERATIN     | IG INSTRUCTIONS                              | 39   |

| 4.1                   | Modulato     | or Optical Alignment                         | 39   |

| 4.2                   | 0.53 μm.     | Modulator Operating Instructions             | 44   |

| 4.3                   | 1.06 $\mu m$ | Modulator Operating Instructions             | 46   |

| 4.4.                  | Signal P     | rocessing Electronics Operating Instructions | 50   |

|                       | 4.4.1        | PN Generator                                 | 52   |

|                       | 4.4.2        | Analog/Digital Encoding Electronics          | 52   |

|     |          |                                                  | Page |

|-----|----------|--------------------------------------------------|------|

| 5.  | PERFORMA | NCE TESTS                                        | . 57 |

| 5.1 | 0.53 µm  | Modulator Tests                                  | . 57 |

|     | 5.1.1    | Modulator Unit Tests                             | . 57 |

|     | 5.1.2    | Driver Tests                                     | . 62 |

|     | 5.1.3    | AEC Tests                                        | . 62 |

|     | 5.1.4    | Temperature Controller Tests                     | . 65 |

|     | 5.1.5    | Modulator Power Supply Tests                     | . 65 |

| 5.2 | 1.06 µm  | Modulator Tests                                  | . 66 |

|     | 5.2.1    | Modulator Unit Tests                             | . 66 |

|     | 5.2.2    | Driver Tests                                     | . 67 |

|     | 5.2.3    | Other 1.06 µM Modulator Tests                    | . 67 |

| 5.3 | Signal P | rocessing Electronics Tests                      | . 67 |

| ,   | 5.3.1    | PN Generator                                     | . 67 |

|     | 5.3.2    | <pre>Dual Sample/Hold</pre>                      | . 71 |

|     | 5.3.3    | Analog/Digital Convertors                        | . 73 |

|     | 5.3.4    | Parallel/Serial Converters                       | . 80 |

|     | 5.3.5    | Timing and Control/Multiplexer                   | . 81 |

|     | 5.3.6    | Signal Processing Electronics Integration        | . 81 |

|     | 5.3.7    | Signal Processing Electronics Power Supply Tests | . 83 |

| 5.4 | Error Ra | te Tests                                         | . 83 |

| 6.  | CONCLUSI | ONS AND RECOMMENDATIONS                          | . 85 |

## LIST OF FIGURES

| <u>Figure</u> |                                                                            | Page |

|---------------|----------------------------------------------------------------------------|------|

| 1-1           | 400 Mbps 0.53 μm Modulator                                                 | 2    |

| 1-2           | 400 Mbps 1.06 μm Modulator and Power Supply                                | 3    |

| 1-3           | 400 Mbps Signal Processing Electronics and Power Supply                    | 4    |

| 3-1           | 400 Mbps 0.53 μm Modulator                                                 | 10   |

| 3-2           | Laser Modulator Functional Block Diagram                                   | 11   |

| 3-3           | Modulator Subassembly Cutaway                                              | 12   |

| 3-4           | Modulator Oven Assembly                                                    | 13   |

| 3-5           | Modulator Optics Head and Lens Holder                                      | 15   |

| 3–6           | Modulator Rear Mirror Holder                                               | 17   |

| 3-7           | Crossed-Axes Crystal Mounting Arrangement                                  | 19   |

| 3~8           | Power Supply                                                               | 23   |

| 3-9           | 400 Mbps 1.06 μm Modulator                                                 | 25   |

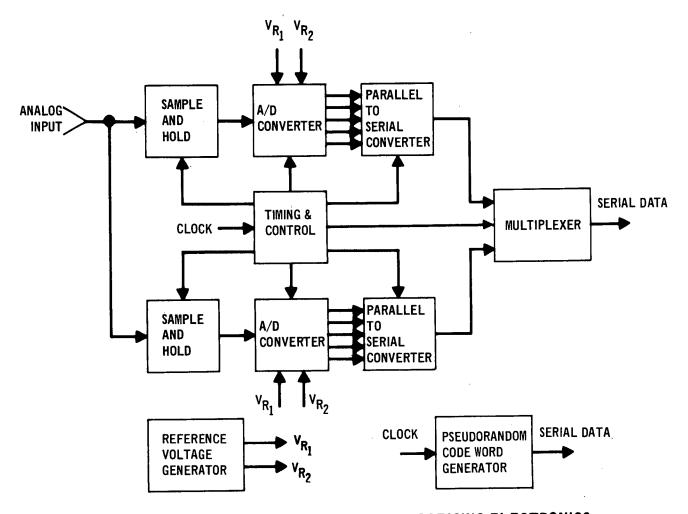

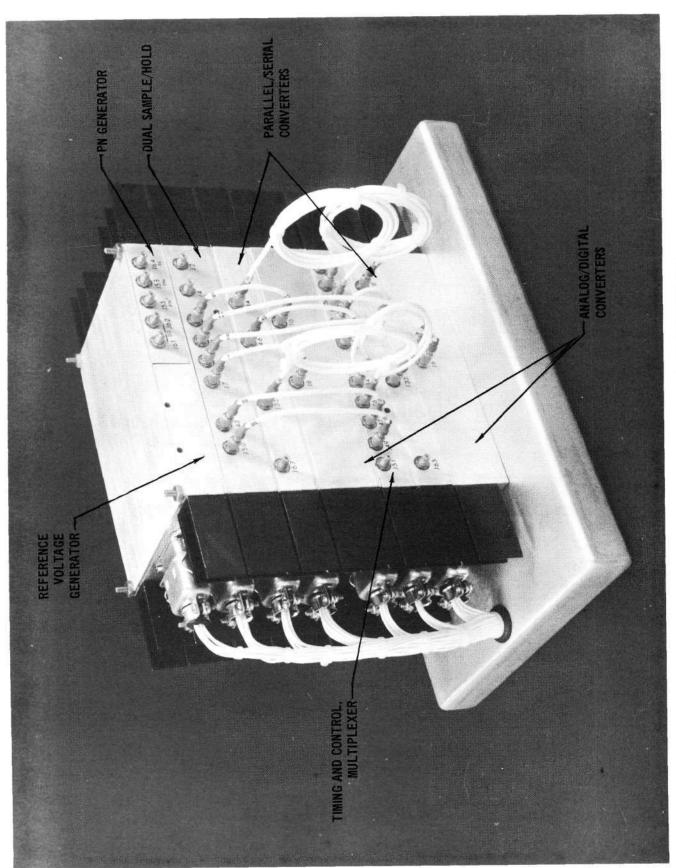

| 3-10          | Block Diagram of Signal Processing Electronics                             | 27   |

| 3-11          | Signal Processing Electronics                                              | 28   |

| 3-12          | Functional Diagram - PN Generator                                          | 29   |

| 3-13          | Dual Sample/Hold                                                           | 30   |

| 3-14          | A/D Converter Functional Diagram                                           | 32   |

| 3–15          | Parallel/Serial Converter Functional Diagram                               | 33   |

| 3-16          | Parallel/Serial Clock Waveforms                                            | 34   |

| 3-17          | Timing and Control/Multiplexer Functional Diagram                          | 35   |

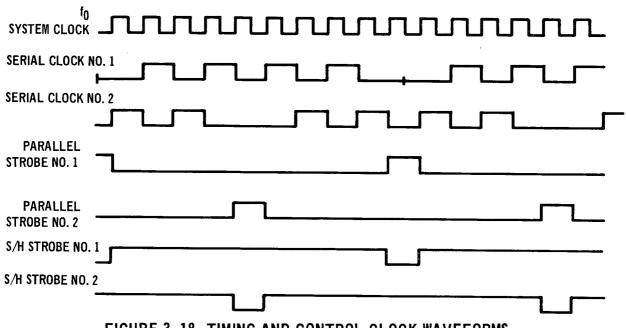

| 3-18          | Timing and Control Clock Waveforms                                         | 36   |

| 3-19          | A/D Reference Voltage Generators Functional Diagram                        | 37   |

| 3–20          | Power Supply                                                               | 38   |

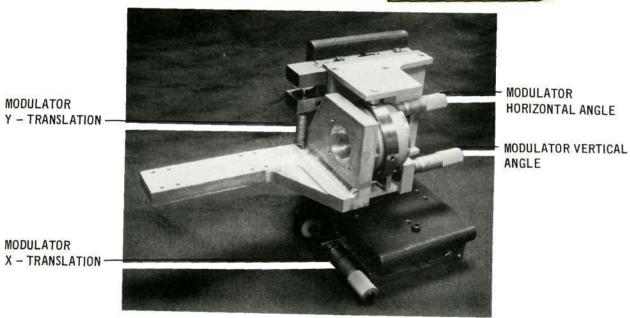

| 4-1           | Modulator Alignment Adjustment Locations                                   | 40   |

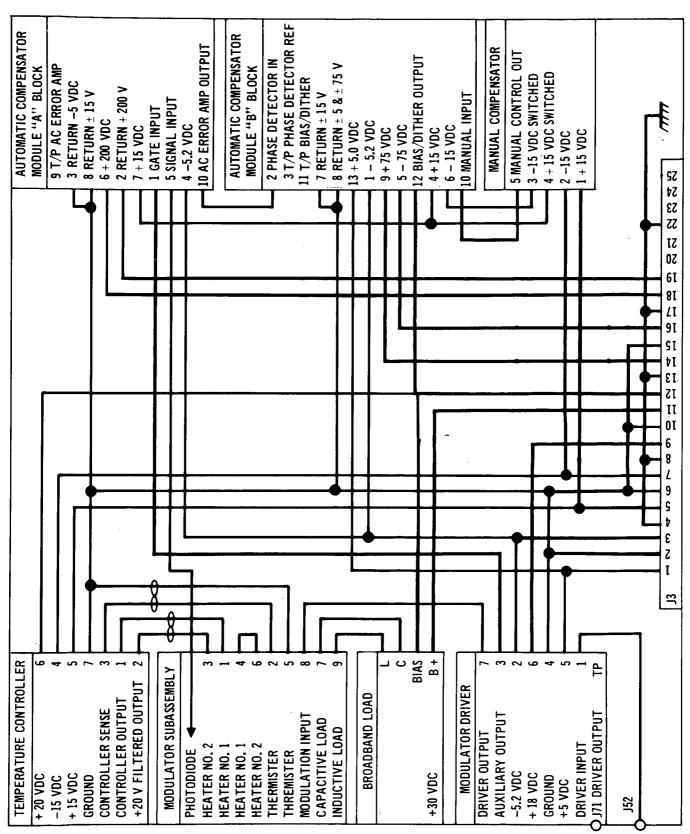

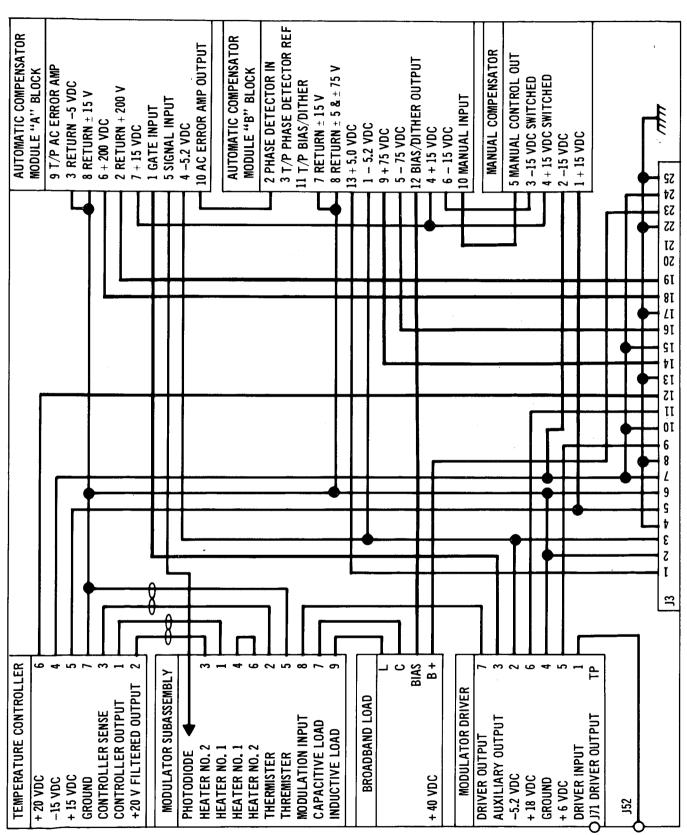

| 4-2           | 0.53 µm Modulator Wiring Diagram With Automatic Electronic Compensation    | 47   |

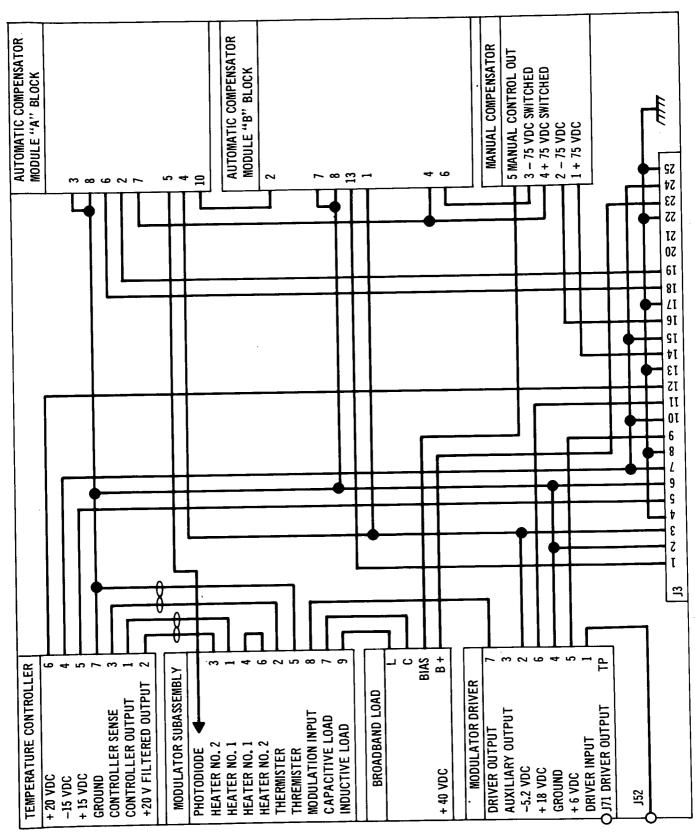

| 4-3           | 1.06 µm Modulator Wiring Diagram Without Automatic Electronic Compensation | 49   |

| 4-4           | 1.06 µm Modulator Wiring Diagram With Automatic Electronic Compensation    | 51   |

| 4-5           | Functional Diagram of PN Generator                                         | 53   |

| 4-6           | Block Diagram of Analog-To-Digital Encoding Electronics                    | 54   |

| Figure |                                                                                             | Page |

|--------|---------------------------------------------------------------------------------------------|------|

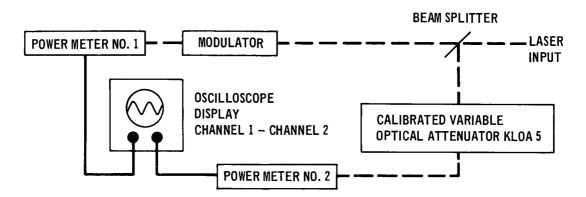

| 5-1    | Setup For Modulator Transmission Measurement                                                | 58   |

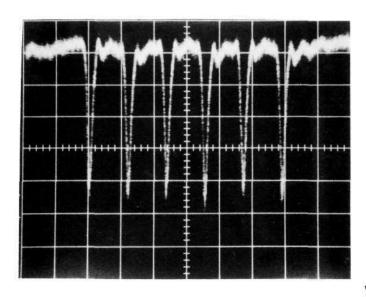

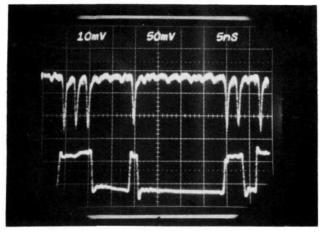

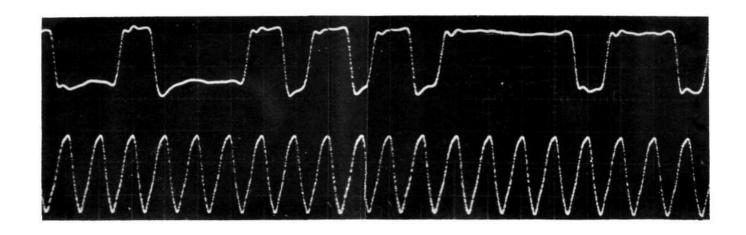

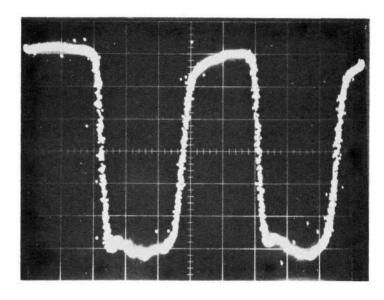

| 5-2    | Optical Response of 0.53 µm Modulator With 63 Bit Code                                      | 59   |

| 5-3    | Worst Case Bits 0.53 µm Modulator With 63 Bit Code                                          | 60   |

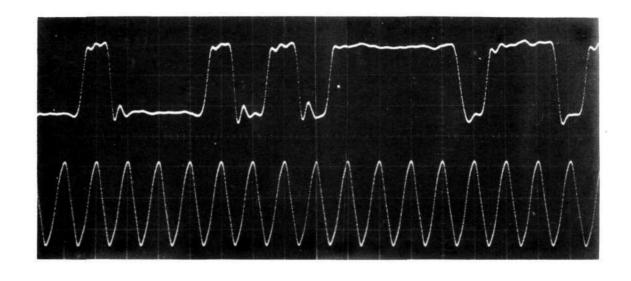

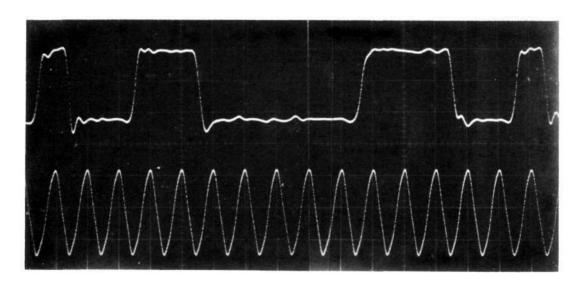

| 5-4    | 0.53 µm Modulator Optical Output And Driver Test Point Selected From A 1023 Bit PN Sequence | 61   |

| 5-5    | Typical Modulator Driver Input Used During Timing Bench Test                                | 62   |

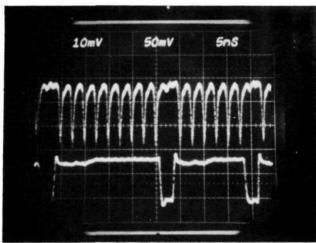

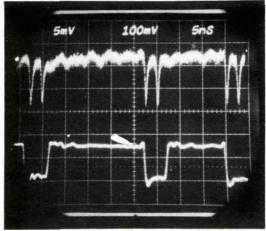

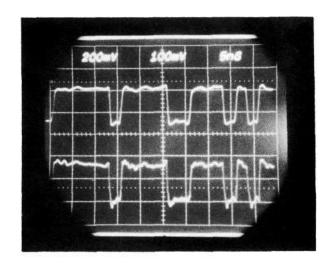

| 5-6    | 0.53 µm Modulator Driver Output vs PN Code Generator Clock 500 Mbps, 31 Bit Sequence        | 63   |

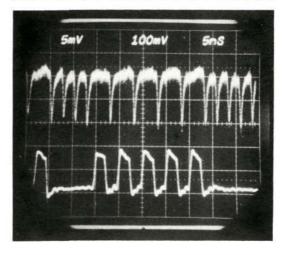

| 5-7    | Automatic Electronic Compensator Waveforms                                                  | 64   |

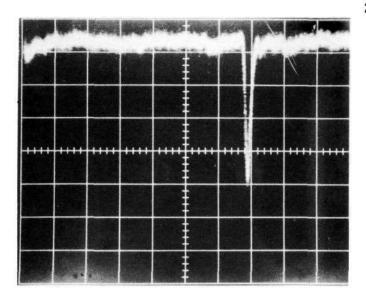

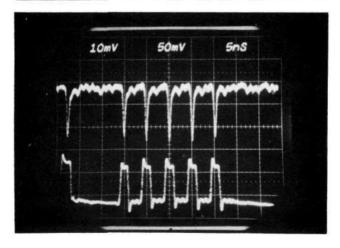

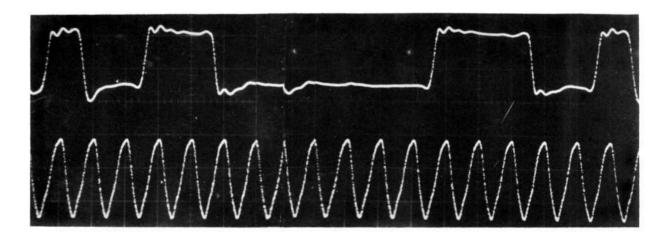

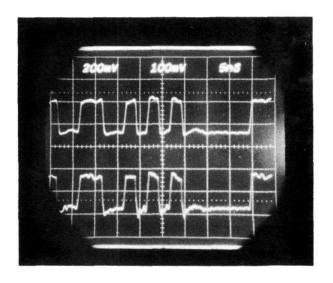

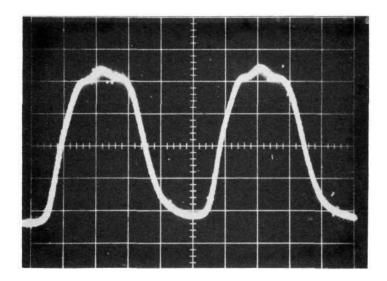

| 5-8    | 1.06 µm Modulator Optical Output And Driver Test Point Selected From A 1023 Bit PN Sequence | 68   |

| 5-9    | 1.06 µm Modulator Driver Output vs PN Code Generator Clock 500 Mbps, 31 Bit PN Sequence     | 69   |

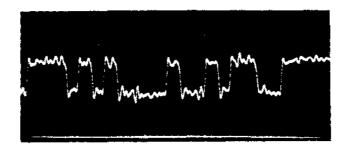

| 5-10   | Comparison of 1.06 µm Driver Test Point Versus Probed Output                                | 70   |

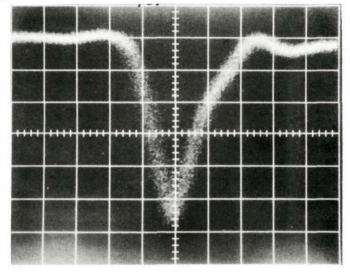

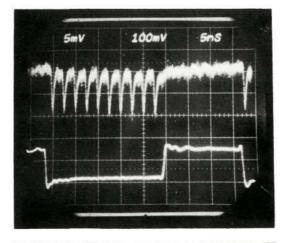

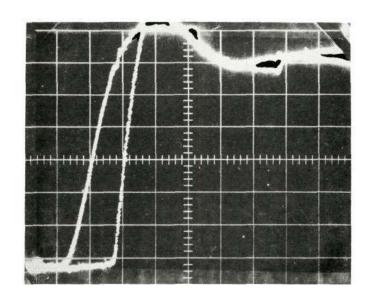

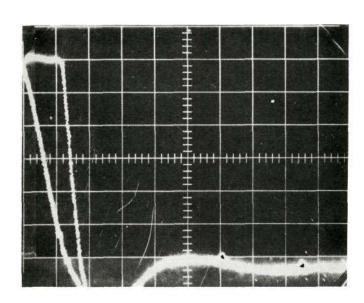

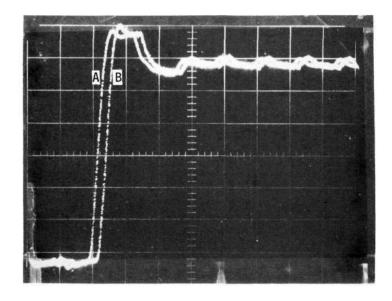

| 5-11   | Maximum Slewing Tests On Sample/Hold Circuit                                                | 72   |

| 5-12   | Relative Comparison Of Bridge Output And Postamplifier Output                               | 73   |

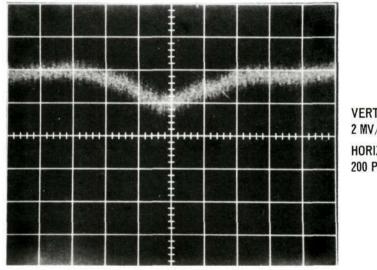

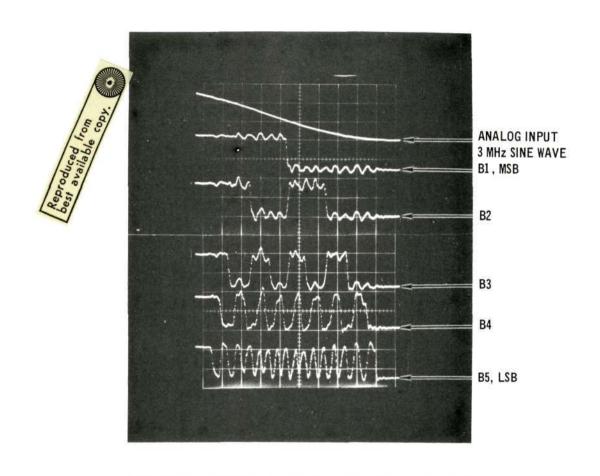

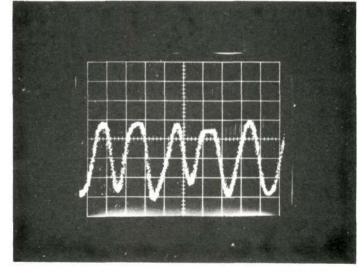

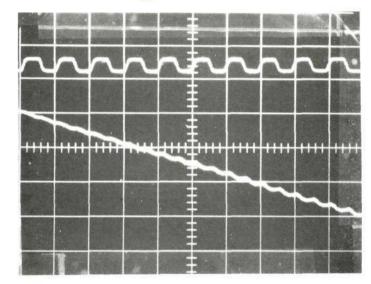

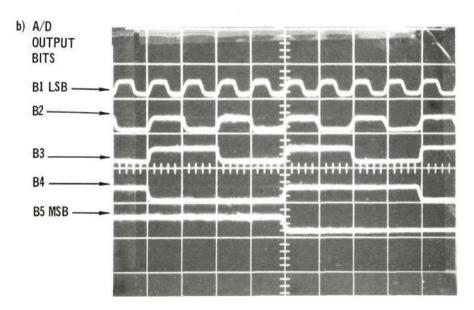

| 5-13   | Ripple Test On A/D Converter                                                                | 74   |

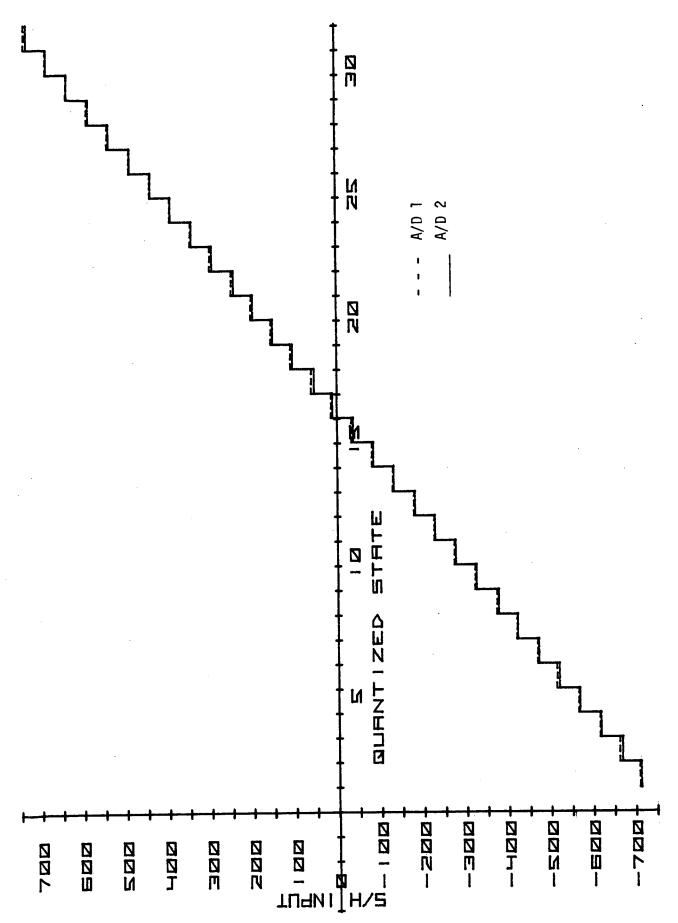

| 5-14   | A/D Converter Relative Tracking And Linearity Results                                       | 75   |

| 5-15   | A/D Output Bits With Ramp Input                                                             | 79   |

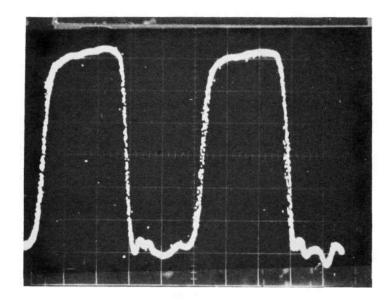

| 5-16   | Parallel/Serial Converter Outputs Illustrating Good "One Zero" Symmetry                     | 80   |

| 5-17   | Multiplexer Output Illustrating Good "One Zero" Symmetry                                    | 81   |

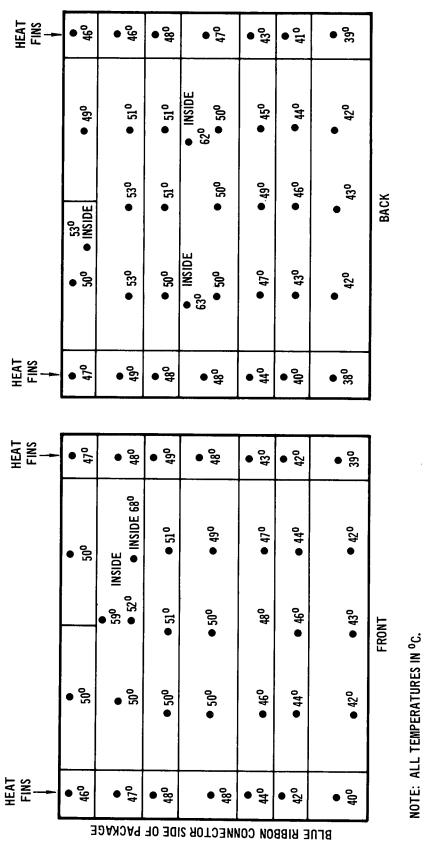

| 5-18   | OMS Signal Processing Package Temperature Test Results                                      | 82   |

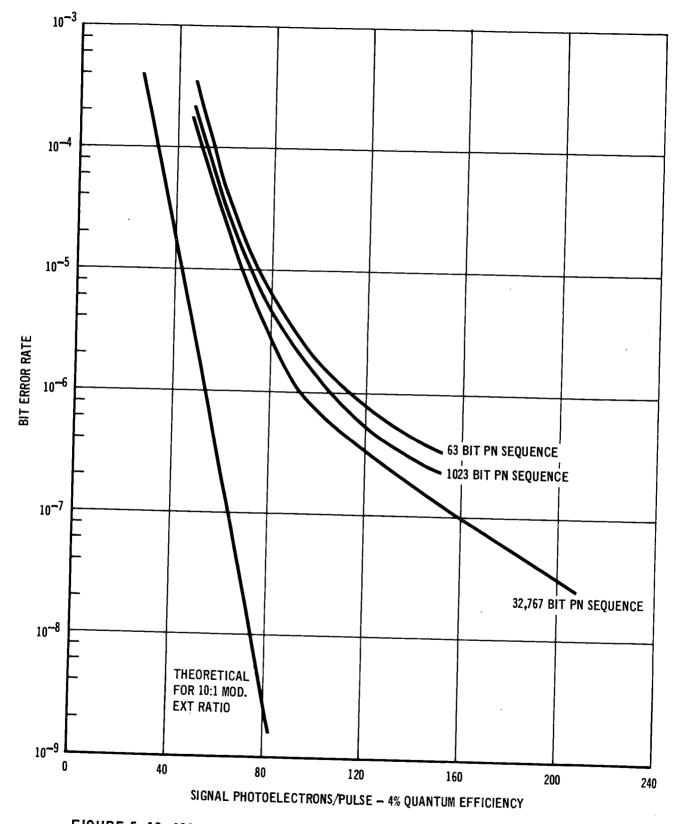

| 5-19   | 400 Mbps 0.53 μm Modulator/Receiver Error Rate Data                                         | 84   |

## TABLES

| Table |                                                                 | Page            |

|-------|-----------------------------------------------------------------|-----------------|

| 1     | 400 Mbps Laser Modulator Interface Specifications               | 6               |

| 2     | Signal Processing Electronics Interface Specifications          | 7.              |

| 3     | 400 Mbps Laser Modulator Performance Summary                    | 8               |

| 4     | Modulator Driver Input/Output Characteristics                   | 20              |

| 5     | Modulator Power Supply Voltages                                 | 24              |

| 6     | Signal Processing Electronics Power Supply Voltages             | 36              |

| 7     | Power Supply Adjustments - 0.53 µm Modulator                    | 45              |

| 8     | Power Supply Adjustments - 1.06 µm Modulator                    | 48              |

| 9     | 1.06 µm Modulator Rewiring For Automatic Electronic Compensator | 50              |

| 10    | PN Generator Cable Delay Lengths                                | 53              |

| 11    | Temperature Controller Test Results                             | 65              |

| 12    | Modulator Power Supply Test Data                                | 66              |

| 13    | DC Linearity Test Results A/D #1                                | 76              |

| 14    | DC Linearity Test Results A/D #2                                | 77              |

| 15    | S/H - A/D Tracking and Linearity Test Results                   | <sup>.</sup> 78 |

| 16    | Signal Processing Power Supply Tests                            | 83              |

#### OPTICAL MODULATOR SYSTEM

#### 1. INTRODUCTION

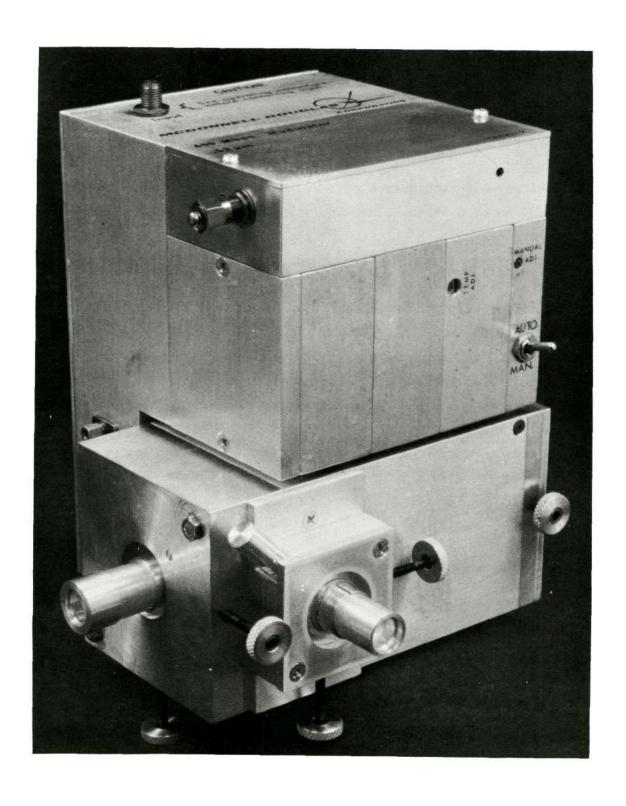

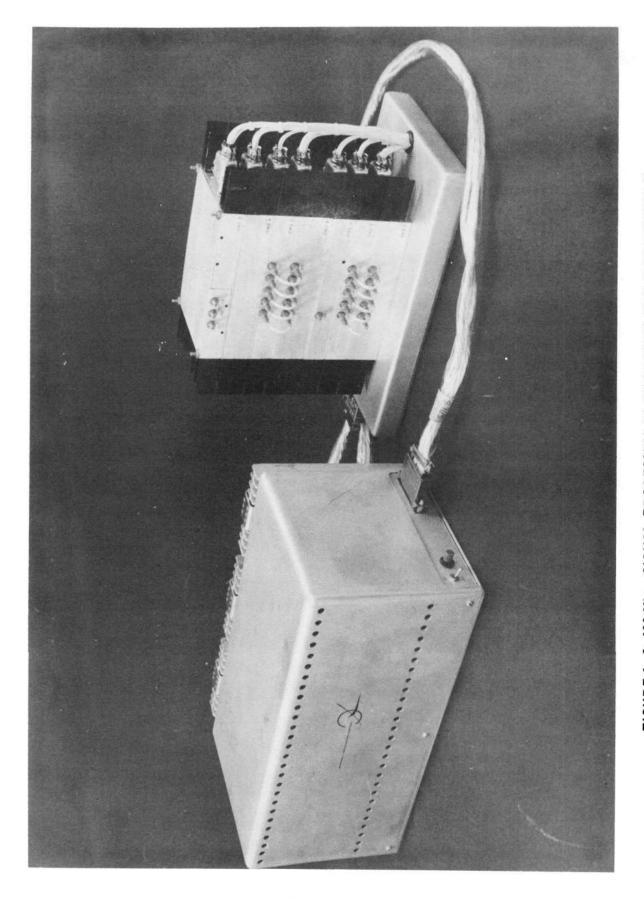

The optical modulator system hardware which was fabricated, tested, and delivered under this program included a 0.53 µm modulator (Figure 1-1), a 1.06  $\mu m$  modulator with power supply (Figure 1-2), and signal processing electronics with power supply (Figure 1-3). The electrooptic modulators function as high speed optical gates on the output of a 400 MHz mode locked Nd:YAG laser radiating at either 1.06 µm or 0.53 µm. The modulator units were designed to operate with digital signal sources with MECL logic levels. Each modulator unit contains the necessary amplifiers, thermal control, compensation circuits, and optics to provide stable, high quality optical gating. The signal processing electronics include encoding electronics which are capable of digitizing analog signals between the limits of + 0.75 volts at a maximum rate of 80 megasamples per second with 5 bit resolution. The digital samples are serialized and made available as a 400 Mbps serial NRZ data source for the modulators. A pseudorandom (PN) generator is also included in the signal processing electronics. This data source generates PN sequences with lengths between 31 bits and 32,767 bits in a serial NRZ format at rates up to 400 Mbps.

This report contains a functional description, operating instructions, and performance test results for the above mentioned hardware.

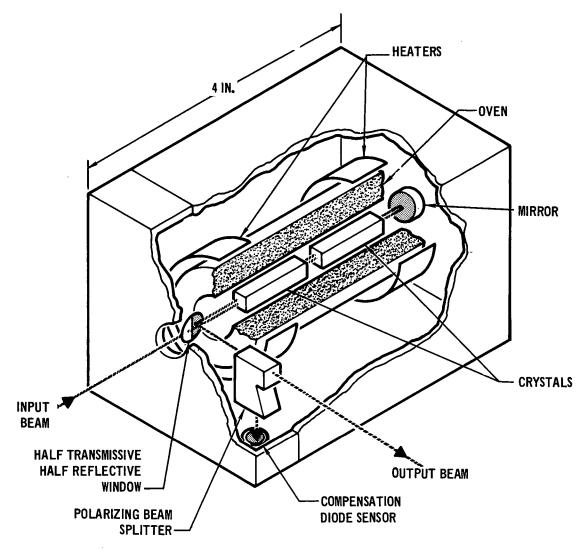

FIGURE 1-1 400 Mbps  $0.53 \mu \mathrm{M}$  MODULATOR

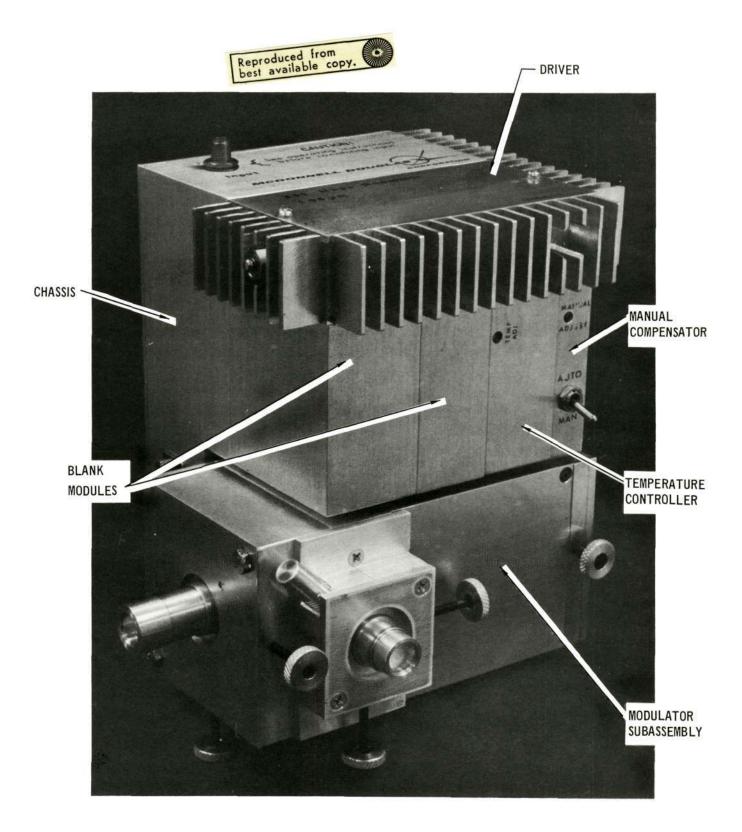

FIGURE 1–2  $\,400\,$  Mbps  $1.06\mu$ M MODULATOR AND POWER SUPPLY

FIGURE 1-3 400 Mbps SIGNAL PROCESSING ELECTRONICS AND POWER SUPPLY

## 2. PERFORMANCE SUMMARY

The modulators delivered in this program are intended for incorporation in a mode-locked Nd:YAG laser communication system. The important interface parameters for the modulators in such an application are given in Table 1. Likewise, the interface specifications for the signal processing electronics which serve as a data source for the modulators are given in Table 2.

Table 3 summarizes the measurement results for critical modulator parameters. These results are typical of measurements made during various modulator tests at different times. The results vary depending on the care taken in optically aligning the modulators when they are set up for a test. More detailed test results are given in Section 5 of this report.

TABLE 1

400 Mbps LASER MODULATOR INTERFACE SPECIFICATIONS

|              |                                                  | Specification      |                               |

|--------------|--------------------------------------------------|--------------------|-------------------------------|

|              | Characteristic                                   | 0.53 µm Modulator  | 1.06 μm Modulator             |

| Input Beam   | Wavelength                                       | 0.53 μm            | 1.06 µm                       |

|              | Average Power <sup>1</sup> (with compensator     | 0.5 mW-10 mW       | 0.5 mW-10 mW                  |

|              | Pulse Repetition Frequency                       | 400 Mpps max.      | 400 Mpps max.                 |

|              | Pulse Width (10% points)                         | 500 ps max.        | 500 ps max.                   |

|              | Beam Characteristics                             | Gaussian TEM       | Gaussian TEM                  |

|              | Beam Diameter                                    | 2mm nom.           | 2mm nom.                      |

|              | Beam Divergence (1/e points)                     | 0.3 mrad nom.      | 0.6 mrad nom.                 |

|              | Polarization                                     | Horizontal         | Horizontal                    |

| Driver Input | Waveform                                         | Bilevel, NRZ       | Bilevel, NRZ                  |

|              | Logical one level                                | $-0.8V \pm 0.1V$   | -0.8V + 0.1V                  |

|              | Inches I many 1 1                                | -1.7V + 0.1V       | ! =                           |

|              | Input Impedance (nominal)                        | 50 ohm             | -1.7V <u>+</u> 0.1V<br>50 ohm |

|              | Reflection coefficient (with lns risetime)       | < 0.2              | ≤ 0.2                         |

|              | Rise, Fall times (10-90%)                        | < 1.3 ns           | <1.3 ns                       |

|              | Data Jitter, Symmetry with respect to data clock | ≤ ± 100 ps         |                               |

| Output Beam  | Beam Characteristics                             | Gaussian TEM<br>oo | Gaussian TEM<br>oo            |

|              | Beam Diameter                                    | 2mm nom.           | 2mm nom.                      |

|              | Divergence                                       | 0.3 mrad nom.      | 0.6 mrad nom.                 |

|              | Polarization                                     | Horizontal         | Horizontal                    |

### NOTE:

1. Will operate with power levels exceeding this range when used with the manual compensator.

TABLE 2

SIGNAL PROCESSING ELECTRONICS INTERFACE SPECIFICATIONS

|                                     | Characteristic                                                                                                                         | Specification                                                                                                |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| PN Generator<br>Clock Input         | Waveform<br>Frequency <sup>l</sup><br>Amplitude<br>Load Impedance                                                                      | Sinusoidal<br>400 MHz +5 MHz<br>1V pp<br>50 ohms nominal                                                     |

| Data Output                         | Waveform Frequency  Logical one level Logical zero level Rise, Fall time (10-90%) Jitter Symmetry with respect to Clock Load Impedance | Bilevel, Serial NRZ Same as Clock Input Frequency -0.8V ±0.1V -1.7V ±0.1V < 1.3 ns  < ±100 ps 50 ohm nominal |

| Encoding Electronics<br>Clock Input | Waveform<br>Frequency<br>Amplitude<br>Load Impedance                                                                                   | Sinusoidal<br>10-400 MHz<br>3V pp<br>50 ohms nominal                                                         |

| Analog Input                        | Amplitude<br>Bandwidth <sup>2</sup><br>Load Impedance                                                                                  | <pre>&lt; +0.75V pp dc - 32 MHz 50 ohms nominal</pre>                                                        |

| Data Output                         | Waveform Frequency Logical one level Logical zero level Rise, Fall time (10-90%) Jitter, Symmetry with respect to Clock Load Impedance | Bilevel Same as Clock input -0.8V <u>+0.1V</u> -1.7V <u>+0.1V</u> < 1.3 ns  < 100 ps 50 ohms nominal         |

#### NOTES:

- 1. Cables are also furnished to allow operation at 200 MHz and 300 MHz with a 63 bit sequence. The generator can be made to operate at any frequency below 400 MHz if the proper cable lengths are used.

- 2. The analog signal bandwidth should be at least 2.5 times less than the sampling rate.

TABLE 3

400 Mbps LASER MODULATOR PERFORMANCE SUMMARY

| Characteristic      | 0.53 μm Modulator | 1.06 μm Modulator |

|---------------------|-------------------|-------------------|

| Transmission        | 72%               | 50%               |

| Depth of Modulation | >98%              | >97%              |

| Extinction Ratio    |                   |                   |

| Static              | >50:1             | >30:1             |

| Dynamic             | >15:1             | >13:1             |

| Power Dissipation   | 22 watts          | 30 watts          |

|                     |                   |                   |

### Definitions:

1) Transmission =

$$\frac{P_{\text{in ave.}} - P_{\text{out ave.}}}{P_{\text{in ave.}}} \times 100$$

2) Depth of Modulation =

$$\frac{\text{Maxium 1 level-Minimum 0 level}}{\text{Maximum 1 level}} \times 100 = (1 - \frac{1}{\text{Static Ext. Ratio}}) \times 100$$

3) Static Extinction Ratio =

$$\frac{P_{\text{out ave. (all 1's)}}}{P_{\text{out ave. (all 0's)}}}$$

4) Dynamic Extinction Ratio =

$$\frac{\text{Minimum 1 level in optical pulse train}}{\text{Maximum 0 level in optical pulse train}}$$

Dynamic extinction ratio is measured using a 63 bit pseudorandom code as a data source

#### NOTES:

- Optical alignment of the modulators are critical when attempting to measure the above performance parameters.

- Measurement of dynamic extinction ratio is limited by the ability to discern 0 levels down in the detector and oscilloscope noise levels.

#### 3. HARDWARE DESCRIPTION

### 3.1 0.53 µm MODULATOR.

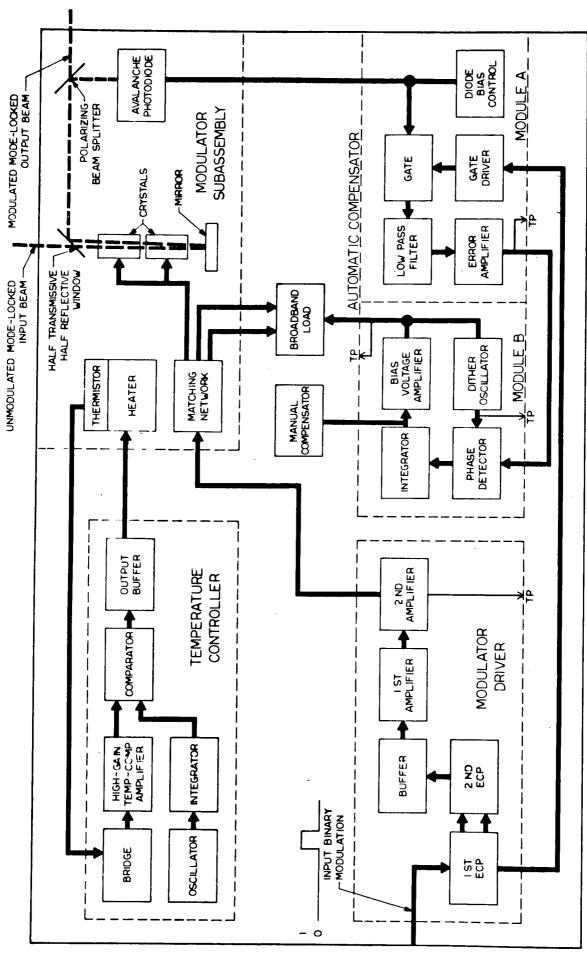

A photograph of the 0.53  $\mu m$  modulator is shown on Figure 3-1 and a functional diagram of the unit is given of Figure 3-2. The 0.53  $\mu m$  modulator consists of a 0.53  $\mu m$  modulator subassembly, modulator driver, temperature controller, automatic electronic compensator, manual compensator, and chassis. The chassis contains the wideband 50 ohm loads, power connector, and all the power and signal cables to the various modules. The dimensions of the 0.53  $\mu m$  modulator are 10.35 cm x 12.5 cm x 14.0 cm. It weighs 1.7 kilograms and dissipates 22 watts average.

The horizontally polarized, mode locked laser beam enters the modulator through the transparent half of a window as shown in Figure 3-3. It then passes through two cascaded crystals whose longitudinal axes are parallel to the light beam. The beam is then reflected from a mirror at the exit from the second crystal, such that it passes in the return direction again through both crystals. If the crystals are energized during the period that a pulse passes through, the pulse polarization is rotated by 90°. If the crystals are not energized, the polarization of a given pulse remains unchanged. After leaving the crystals, the beam is reflected by a second mirror to a polarized beam splitter. Here, the beam is split into two: 1) a modulated, horizontally polarized output beam, and 2) a modulated, vertically polarized beam which is detected by the compensator diode and used as the correction signal for the automatic compensator.

## 3.1.1 Modulator Subassembly

The modulator subassembly consists of the optics head, oven subassembly, and lens holders.

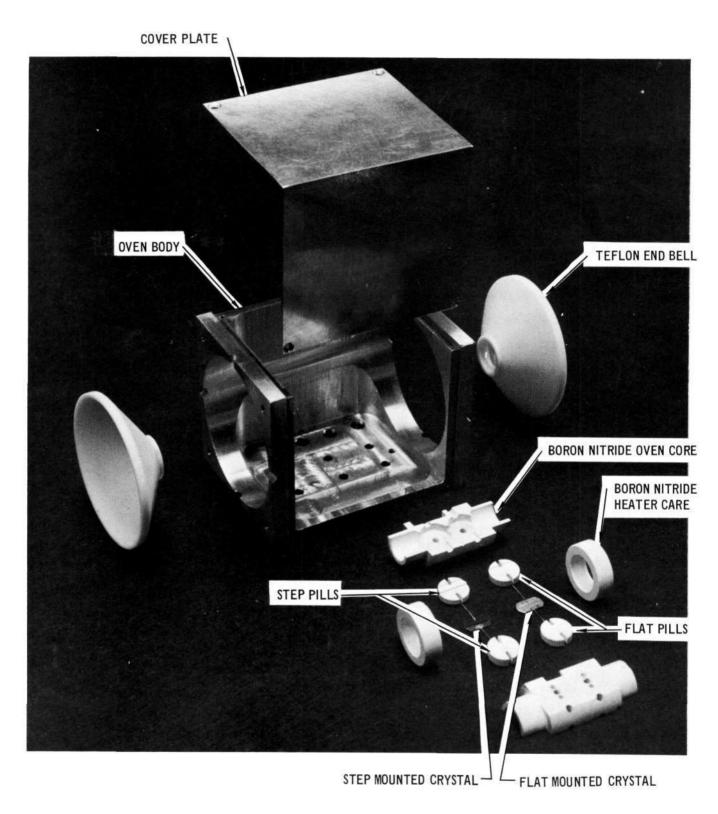

Figure 3-4 shows an exploded view of the oven subassembly. The oven is used for mechanical support and as an isothermal enclosure which thermally stabilizes the modulator interior with respect to the laboratory environment. The matching network cables, heater leads, and thermistor leads enter the oven through the base of the housing which acts as a ground plane for the high frequency signals. The unshielded leads are bypassed with feedthrough capacitors to this ground plane which prevents pickup of the several watts of circulating RF power from entering the control loop of the temperature controller. The oven core is held in place by the teflon end bells.

FIGURE 3-1 400 Mbps 0.53  $\mu$  M MODULATOR

FIGURE 3-2 LASER MODULATOR FUNCTIONAL BLOCK DIAGRAM

FIGURE 3-3 MODULATOR SUBASSEMBLY CUTAWAY

These end bells are shaped for maximum support of the oven core and also provide a minimal heat leak from the oven core to the oven housing. The end bells are made of teflon to minimize the reactive interaction with the matching network components.

The oven core is made of boron nitride. Boron nitride was chosen for its low dielectric loss tangent and high thermal conductivity. Only beryllium oxide would be better in this respect, but it is extremely difficult to machine and handle beryllium oxide because of its very toxic nature. The oven core holds the mounted crystals and heaters. It acts as the high temperature isothermal enclosure. The ends of the oven core are shaped to hold the heaters. The nichrome wire heaters are wound in grooves in

FIGURE 3-4 MODULATOR OVEN SUBASSEMBLY

boron nitride cylinders which fit snugly around the oven core. The length of the groove in the cylinders was chosen so that about 22 ohms of nichrome wire are used. This impedance was chosen to match the temperature controller output stage. The heaters were located away from the oven center so that there is as little electrical interaction as possible between the heaters and matching network.

The crystals are soldered to copper electrodes. One crystal is a flat configuration where the electrode comes in from the side. It mounts between two flat boron nitride pills. The other crystal is placed between two similar electrodes, one above and one below the crystal. The boron nitride pills used for mounting this crystal have a step of height equal to the crystal and electrode thickness. The pills are bonded to the electrodes with an RTV cement. The pills are then optically aligned in the oven core and bonded in place in the same manner.

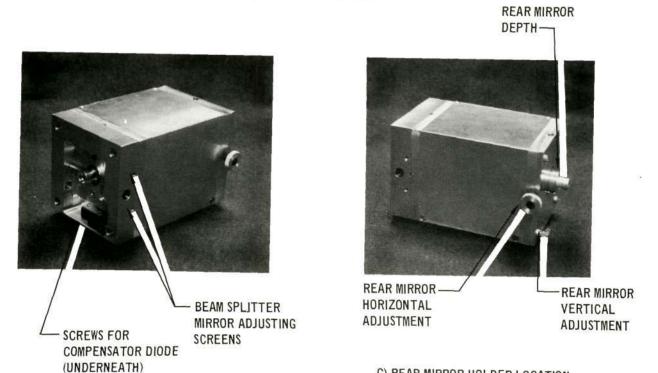

An exploded view of the optics head is shown in Figure 3-5. The body of the optics head is shaped to hold the component parts. Its back side is shaped to fit into the oven body to hold the teflon end bell in place. The beam splitter mirror holder fits into the optics head body from the back side; it slides between the body and a metal backup plate. Adjustment is accomplished by turning the two screws which push rods against the shoulders in the mirror holder. Back pressure is applied by the spring loaded plunger pressing against the cylindrical part of the mirror holder. The two screws which hold the plates together can be tightened for locking the mirror holder in place. The mirror is held in the mirror holder between two press fit  $45^{\circ}$  rings. The polarizing beam splitter prism sits in a recess in the optics head body. Its center aligns with the center of the beam splitter mirror. It is held in place by spring pressure from the metal retainer. The compensator diode is held in place beneath the polarizing beamsplitter by a plastic holder. The plastic holder is adjustable to position the diode in the compensator output beam by sliding it into place and clamping the holder by tightening the two screws which hold the diode holder. The output cable from the diode exits through the large hole in the left of the optics head body.

An exploded view of the front lens holder is shown on the right hand side of Figure 3-5. The adjustment motion is produced by a sliding

FIGURE 3-5 MODULATOR OPTICS HEAD AND LENS HOLDER

plate, as in the optics head. The difference here is that only X and Y degrees of freedom are required while restricting rotation. The horizontal adjustment is accomplished by a screw on one side of the sliding plate with a spring on the other side opposing it. The vertical adjustment works in a similar manner. The lens is held in a cylinder which is a close slip fit into the sliding plate with a spring loaded retainer. The lens can be pushed in and out for focusing adjustments.

An exploded view of the rear mirror holder is shown in Figure 3-6. The rear mirror holder is quite similar in design and function to the front lens holder. Its stability of position is more critical, however, because of the short focal length of the rear mirror. This requires spring loading of the sliding plate in all three directions. The helical spring holds the sliding plate against the rear mirror holder body. The rear mirror holder body has the same kind of shoulder as the optics head for holding the teflon end bell in place in the oven body. The mirror is mounted in the stainless steel post which extends into the oven interior for proper location of the rear mirror.

## 3.1.1.1 Crystal Material Selection

Each of the modulators delivered under this program use two high quality lithium tantalate crystals. Prior to this program, we had conducted a trade analysis of the available electrooptic crystals which might be useful for 400 Mbps modulation. At that time, based on the best data available, we concluded that strontium barium niobate, SBN ( $\mathrm{Sr_{05}^{Ba}_{0.5}^{Nb}_{20}^{0}_{6}}$ ) was the best crystal choice for this application. This decision was based upon its availability in good quality specimens, low half wave voltage, acceptable crystal capacitance, and immunity to optical damage at 0.53  $\mu m$ . We knew that the dielectric loss tangent was a few percent and the piezoelectric coupling was quite high. At the time, however, we considered SBN to be the best available material for use in this program.

During the course of this program we also conducted an extensive modulator materials evaluation study (under Air Force contract F33615-71-C-1909) of the current and readily achievable optical quality of several candidate modulator materials. The material that emerged from that study, and the study conducted under this program, as the choice for high data rate space data relay applications was lithium tantalate. This decision was partly

FIGURE 3-6 MODULATOR REAR MIRROR HOLDER

based upon the fact that we were never able to completely suppress the piezoelectric body resonance in the SBN modulators. Intersymbol interference always occurred when modulation codes containing low frequency components were used. The decision was also influenced by the increased availability of lithium tantalate during the course of this program. In fact, we were able to obtain usable samples of lithium tantalate from four separate sources, although only one source produces exceptionally good material.

The decision to use lithium tantalate was made early enough in the program that we were able to accomplish most of the program goals. The use of lithium tantalate required increasing the oven temperature from a nominal 50°C to 150°C for prevention of optical damage, with a corresponding increase in heater power. The increased switching voltage required more driver power than we had originally budgeted.

#### 3.1.1.2 Crystal Configuration

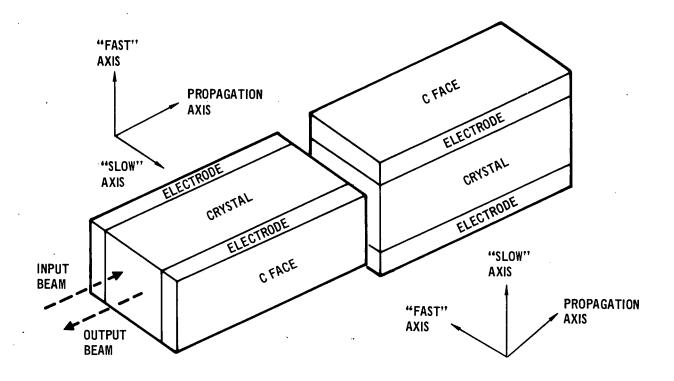

The lithium tantalate crystals are oriented so that the polarized laser light travels through the crystals in a direction parallel to the "C" faces. The light enters the crystals polarized at 45° with respect to the crystal axes. In this configuration, the input beam is divided equally into the two polarizations within the crystal, i.e., ordinary (0-wave) and extraordinary (E-wave). The two crystals are oriented so that their axes are crossed as shown in Figure 3-7. The light which travels as 0-wave light in the first crystal will travel as E-wave light in the second crystal. Similarly, light which travels as E-wave light in the first crystal will travel as O-wave light in the second crystal. One can see that, when the two crystals are identical in length as they are when cut from a single piece of material, the total optical length traversed by each polarization is identical, provided that each crystal is at the same temperature. This provides above two orders of magnitude of cancellation of thermal effects in a single crystal. Therefore, the control range required by the automatic electronic compensator and the accuracy of control required by the temperature controllers are greatly reduced.

The phase retardation induced by placing a voltage across the "C" faces is a field distance product. The crystals are therefore made as long and thin as practical so that the field distance product required to achieve half-wave switching is minimized. A factor of two is gained by operating

FIGURE 3-7 CROSSED AXES CRYSTAL MOUNTING ARRANGEMENT

the modulator in the double pass configuration so that the light passes through the crystals twice. The optimum size of the crystals for minimizing driver power in the 0.53  $\mu m$  unit is 0.3mm aperture with each crystal being 10mm long. The aperture was increased to 0.4mm to increase the extinction ratio because we were not able to eliminate the surface strain in the crystals. The crystal capacitance and rise time was not affected by this change but the switching voltage was increased to about 22 volts.

#### 3.1.2 Modulator Driver.

The Modulator Driver (Figure 3-2) amplifies the signal from the digital data source to drive the modulator crystals. The driver input and output signal characteristics are defined in Table 4.

The input section is made up of two emitter-coupled-pairs (ECP) which operate in the switching mode to isolate the driver output from noise and amplitude variation on the input signal. The first stage has an output which is used to gate the automatic electronic compensator. The second stage provides some power gain. The output of the second stage is buffered, and drives a two stage wideband output amplifier which drives the 50 ohm matched modulator load.

TABLE 4

MODULATOR DRIVE INPUT CHARACTERISTICS

| Load Impedance           | 50 ohm nominal        |

|--------------------------|-----------------------|

| Reflection Coefficient   | <0.2                  |

| Logical Zero Input Level | -1.7 <u>+</u> 0.1 Vdc |

| Logical One Input Level  | -0.8 <u>+</u> 0.1 Vdc |

| Rise & Fall Time         | <1.0 ns               |

### MODULATOR DRIVER OUTPUT CHARACTERISTICS

|                           | <u>0.53 μm</u>              | 1.06 μm                |

|---------------------------|-----------------------------|------------------------|

| Logical Zero Output Level | $+30.0 \pm 2.2 \text{ Vdc}$ | +40.0 <u>+</u> 3.0 Vdc |

| Logical One Output Level  | +8.0 <u>+</u> 2.2 Vdc       | +10.0 <u>+</u> 3.0 Vdc |

| Rise & Fall Times         | <0.7 ns                     | <1.0 ns                |

| Load Impedance            | 50 ohms nominal             | 50 ohms nominal        |

The 0.53  $\mu m$  driver is completely dc coupled. Under normal operating conditions (50% duty cycle) it furnishes 4.8 watts to the matched load while dissipating 6.2 watts internally.

### 3.1.3 Temperature Controller.

The Temperature Controller (Figure 3-2 ) provides slow-response, long-term temperature control of the modulator crystals. Crystal temperature is controlled at  $150^{\circ} \pm 1^{\circ}\text{C}$  by heaters that are supplied with electrical power from the Temperature Controller.

A temperature sensing thermistor is inserted into one leg of a bridge, and resistors are used in the other legs. The thermistor has a temperature coefficient of approximately 1% per degree Centigrade, and has a nominal impedance of 200 ohms at 150° Centigrade. The resistors are selected so that the bridge output is nulled at the desired operating temperature. Any

error in the bridge null is amplified by the high-gain temperature controlled amplifier and is used as a bias voltage for the comparator. A triangular waveform (the integrated square-wave-oscillator output) that has an average value of zero is used as the second signal to the comparator. The comparator switches on and off as the triangular waveform changes above and below the bias voltage developed from the bridge. Thus, the bridge controls the on-off ratio or duty cycle of the voltage applied to the heater. The output buffer switches the required amount of power to the heater.

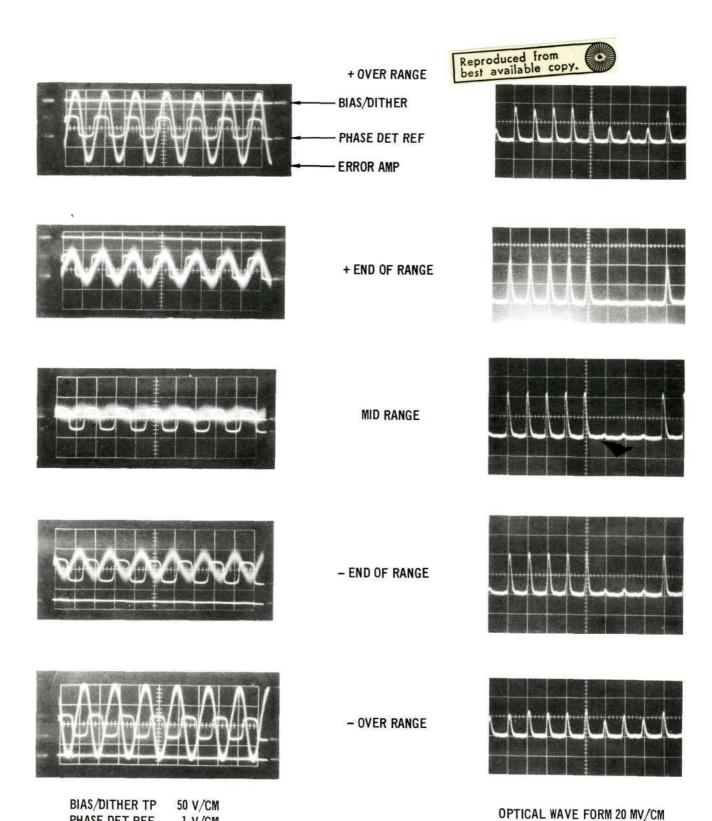

### 3.1.4 Automatic Electronic Compensator.

The function of the Automatic Electronic Compensator (Figure 3-2) is to compensate for thermal effects not compensated by the crossed axis crystals and to compensate for any dc bias level applied by the driver amplifier. Compensation is provided by adjustment of the dc bias that is applied to the crystals. A dither control system is used to automatically adjust the dc bias to maintain the electrooptic modulator at maximum extinction ratio.

The light rejected by the polarizing beam splitter is the complement of the light transmitted. The amplitude of the rejected zeros is maximum at the time when the transmitted zeros are minimum. This rejected light is monitored while a low amplitude dither signal is applied to the modulator bias. The The amplitude and phase of the recovered dither signal is used as an error signal to provide bias amplitude and polarity information for optimum operation.

An avalanche photodiode is used to monitor the rejected light. Diode bias voltage adjustment and current limiting are provided in Module "A". The detected light pulses pass through a gate which is synchronized with the modulator driver binary signal. The gate drive signal is delayed so that it coincides with the time of arrival of the detected signal at the gate. The gate is turned on for the rejected pulses and off for the transmitted pulses. The filter recovers the dither signal from the rejected pulses. The error amplifier increases the signal to the required level and automatically adjusts for a wide range of input signals via its AGC circuits. The amplified error signal is then compared with the phase of the dither oscillator. The phase detector output is a full-wave rectified waveform proportional to the amplitude of the error signal. The polarity is positive when the two signals are in-phase and negative when out-of-phase. The

rectified wave form is then integrated, amplified, summed with the dither signal, and applied to the crystals through the breadboard load.

### 3.1.5 Manual Compensator.

The Manual Compensator permits operation of the modulator exclusive of the Automatic Compensator electronics. The Manual Compensator provides a bias that is adjustable by setting a potentiometer. It switches off the plus and minus 15 Vdc supply voltages to the error amplifier and the dither oscillator/detector, and connects these voltage to an adjustable resistor which permits manual control of the dc signal to the bias amplifier.

### 3.1.6 Power Supply.

Figure 3-8 is a block diagram of the power supply. Eleven voltages are provided for the operation of the Modulator Driver, Automatic Electronic Compensator, and Temperature Controller. Each supply is voltage regulated and current limited, except the batteries. The function of the batteries is to supply stable, ripple-free power to the silicon photodiode at a very low current level. Table 5 lists the voltages provided.

#### 3.2 1.06 µm MODULATOR

The 1.06 µm modulator is shown in the photograph on Figure 3-9. This modulator is 12.5 cm x 11.55 cm x 14.9 cm, weighs 1.67 kilograms, and dissipates 30 watts average. It is very similar to the 0.53 µm modulator described in Section 3.1 except for the added fins which facilitate dissipation of the additional heat from this unit. This modulator does not contain an automatic electronic compensator, but provisions have been made to incorporate one by removing the two blank modules, inserting the compensator modules, and making the wiring changes noted in Section 4.3.

## 3.2.1 1.06 µm Modulator Subassembly

The 1.06  $\mu m$  modulator subassembly is identical to the 0.53  $\mu m$  modulator subassembly described in Section 3.1.1 except that the crystals are 0.3mm cross section and are coated for 1.06  $\mu m$  wavelength.

## 3.2.2 Modulator Driver

The 1.06  $\mu m$  driver is identical functionally to the 0.53  $\mu m$  driver described in Section 3.1.2. It differs only in that different transistors

FIGURE 3-8 POWER SUPPLY

#### TABLE 5

#### MODULATOR POWER SUPPLY VOLTAGES

- +5.0 Vdc Regulated, for Automatic Compensator

- -5.2 Vdc Regulated, for Modulator Driver, Automatic Compensator

- +15 Vdc Regulated, for Automatic Electronic Compensator and Temperature Controller

- -15 Vdc Regulated, for Automatic Electronic Compensator and Temperature Controller

- +6/19 Vdc Regulated, for Modulator Driver (6V for 1.06  $\mu$ m, 19V for 0.53  $\mu$ m driver)

- +18/30 Vdc Regulated, for Modulator Driver (21V for 1.06 μm, 30V for 0.53 μm driver)

- +40 Vdc Regulated, for Modulator Driver (1.06 μm Driver only)

- +24 Vdc Regulated, for Heater

- +75 Vdc Zener regulated, Filtered, for Automatic Compensator

- -75 Vdc Zener regulated, Filtered, for Automatic Compensator

- +200 Vdc Battery for Silicon Photodiode

are used in the power stages and different bias voltages are used. It operates with the same input signal characteristics (Table 1) as the 0.53  $\mu m$  drive. It delivers a 30 V pp signal (9 watts at 50% duty cycle) to the matched load while dissipating 9.5 watts internally.

#### 3.2.3 Temperature Controller

The Temperature Controller used in the 1.06  $\mu m$  modulator is identical to the 0.53  $\mu m$  modulator temperature controller described in Section 3.1.3.

#### 3.2.4 Automatic Electronic Compensator

The 1.06  $\mu m$  modulator does not contain an Automatic Electronic Compensator. The 0.53  $\mu m$  compensator described in Section 3.1.4 was designed to operate in the 1.06  $\mu m$  modulator when the proper bias voltages are supplied. Space has been allotted to insert the automatic compensator modules and the avalanche photodiode has been included in the optics head. Thus with the incorporation of minor chassis wiring changes the compensator can be incorporated in the 1.06  $\mu m$  modulator.

FIGURE 3-9 400 Mbps  $1.06 \mu$  M MODULATOR

## 3.2.5 Manual Compensator.

When the Automatic Electronic Compensator is not installed, the Manual Compensator connects directly to the broadband load and provides an adjustment range of plus and minus 75 volts. When the Automatic Electronic Compensator is installed, the Manual Compensator function is identical to that described in Section 3.1.5.

### 3.2.6 Power Supply.

The power supply is the same unit described in Section 3.1.6. The 40 volt supply is used for the 1.06  $\mu m$  system only. The 6/18 and 18/30 volt supplies which are set for the 0.53  $\mu m$  modulator require readjustment for use with the 1.06  $\mu m$  modulator. When the Automatic Electronic Compensator is not used the +5.0V,  $\pm$ 75V, and the 200 Vdc supplies are not used.

## 3.3 SIGNAL PROCESSING ELECTRONICS

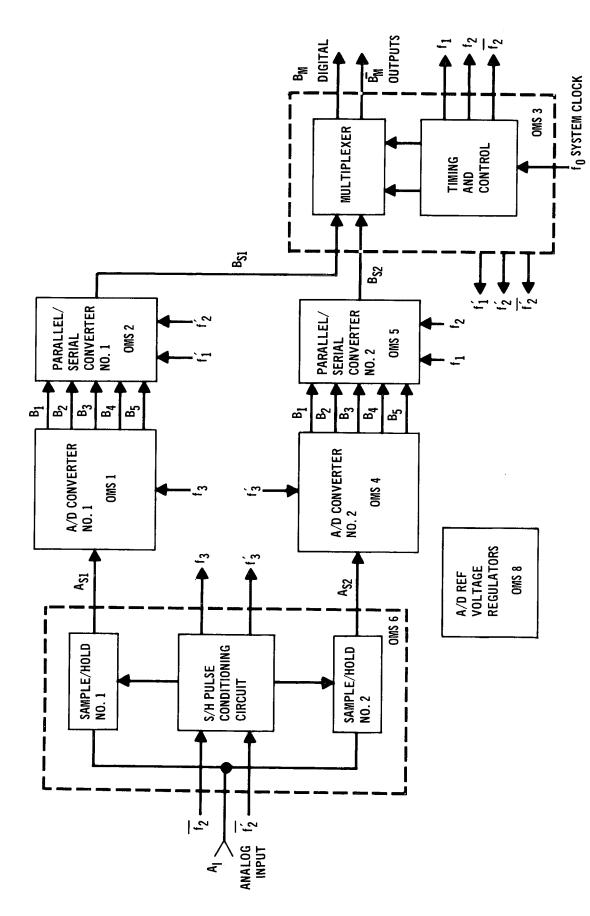

The block diagram of the Signal Processing Electronics is shown on Figure 3-10. The electronics supply digital data to the modulator in the form of pseudorandom codes or digitally encoded analog data. The Signal Processing Electronics consists of 8 modules in a 10.1 cm  $\times$  15.7 cm  $\times$  17.8 cm stack which dissipate approximately 50 watts. Figure 3-11 is a photograph of the electronics.

The pseudorandom code word generator outputs serial NRZ data (MECL levels) at bit rates up to 400 Mbps to the modulator driver. It operates from an external 1V pp clock source which is locked to the laser pulse frequency and can be connected to obtain several different code sequence lengths.

The encoding electronics digitizes analog signals within a ± 0.75V pp range into a serial NRZ digital train (MECL levels) which can be used as a data source for the modulator driver. The encoding is accomplished with two identical 200 Mbps prosessing chains whose outputs are interleaved to obtain the 400 Mbps serial data. Each chain contains a buffered sample/hold capable of 40 MHz sampling rates, a 5 bit simultaneous type analog/digital converter which quantizes the analog sample to 32 discrete levels, and a shift register to convert the 5 bit parallel samples into a serial bit stream. The timing and control module accepts a 1V pp clock signal (400 MHz maximum) which is locked to the laser pulse frequency and phase. The reference voltage generator supplies adjustable filtered bias voltages for the A/D converter comparator references.

FIGURE 3-10 BLOCK DIAGRAM OF SIGNAL PROCESSING ELECTRONICS

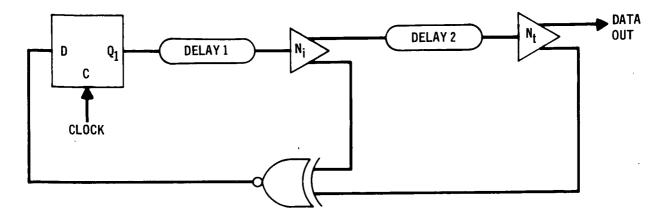

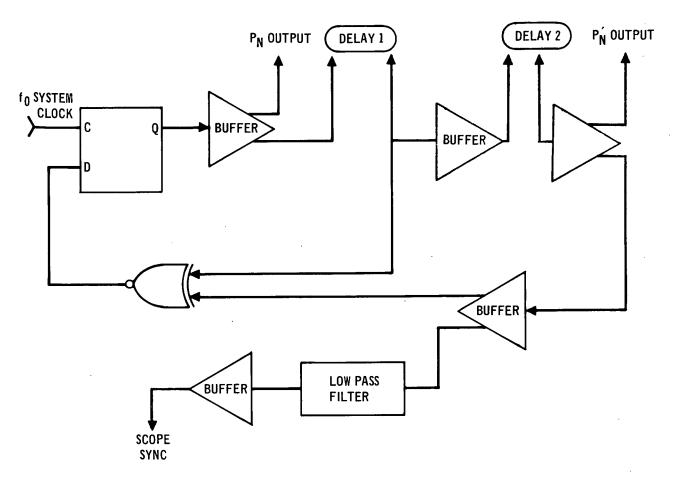

#### 3.3.1 Pseudorandom Generator

The pseudorandom (PN) generator was designed using passive delay lines in lieu of active elements in the shift register as shown in the functional diagram of Figure 3-12 . Any specific maximal length sequence can be obtained by modulo 2 feedback from the N $_{\rm i}$  and N $_{\rm t}$  stages of the generator. The desired feedback condition is obtained by selection of delay line cable lengths. Delay 1 sets up the proper delay for stage 2 through N $_{\rm i}$  and delay 2 gives the proper delay for stage N $_{\rm i+1}$  through N $_{\rm t}$ .

This approach has the following advantages relative to the conventional implementation of a PN generator with all active elements: 1) the maximum generator operating frequency is limited only by the maximum flip/flop toggle frequency, 2) Various code sequences can be obtained by proper selection of delay line cable length, 3) Power dissipation is minimized. The only disadvantage of this approach is that the clock frequency can only be varied

FIGURE 3-12 FUNCTIONAL DIAGRAM - PN GENERATOR

approximately 5% about the nominal for any given set of delay lines. This is not a restriction for normal operating conditions.

The delay lines to implement maximal length PN sequences of 31, 63, 127, 511, 1023, 2047, and 32,767 bits at 400 MHz and 63 bits at 200 MHz and 300 MHz are furnished with the unit.

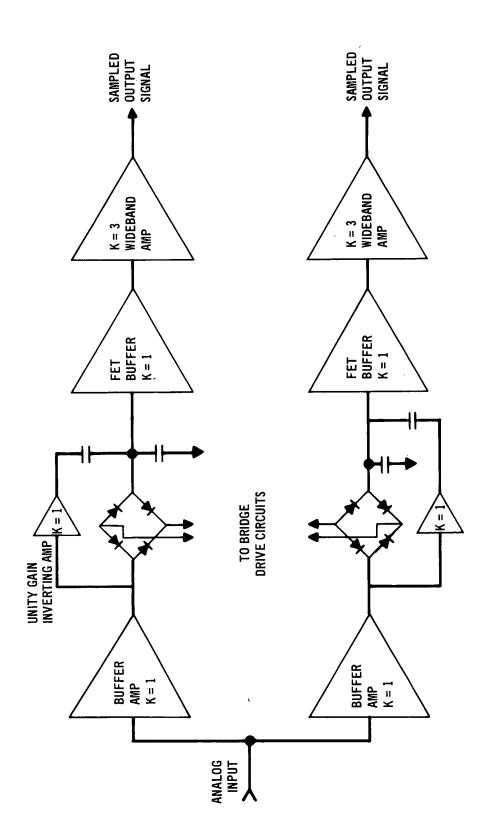

#### 3.3.2 Dual Sample Hold

The functional diagram of the dual sample/hold is shown on Figure 3-13. This unit samples analog data within the limits of  $\pm$  0.75V pp and holds each sample at a constant level for a sufficient time to allow the comparators in the A/D converter to reach a binary decision. The two sample/holds are strobed out of phase with each other at rates up to 40 MHz. This results in an effective maximum analog input sampling rate of 80 MHz. The bandwidth of the analog input signal should be restricted to approximately 2.5 times less than the sampling rate. The two sample/holds were matched and designed to minimize the contribution of aperture error, feedthrough, offsets, droop, and nonlinearity to the overall encoding system accuracy.

The diode bridges are driven from buffer amplifiers with low output impedance. Low impedance drive to the bridges is necessary to obtain maximum slewing capability for the circuit. The slewing is limited by a RC time constant composed of the output impedance of the buffer, the "on" resistance of the bridge, and the capacitance of the holding capacitor. The bridge is composed of four hot carrier diodes that are matched and mounted in hybrid form in a single package. This arrangement reduced parasitics and minimized

FIGURE 3-13 DUAL SAMPLE/HOLD

feedthrough. The size of the holding capacitor was determined by a tradeoff between slewing capability and holding droop. The unity gain inverting amplifier was used to cancel capacitive feedthrough of the analog input while the bridge is in its off condition. FET input unity gain buffers were used at the output of the bridges to maintain high impedance conditions at the holding capacitor. Wideband amplifiers having gains of 3 follow the FET input buffers. Amplification of the signal at this point minimizes the error contribution of the A/D converter comparator offset and hysteresis.

#### 3.3.3 Analog/Digital Converter

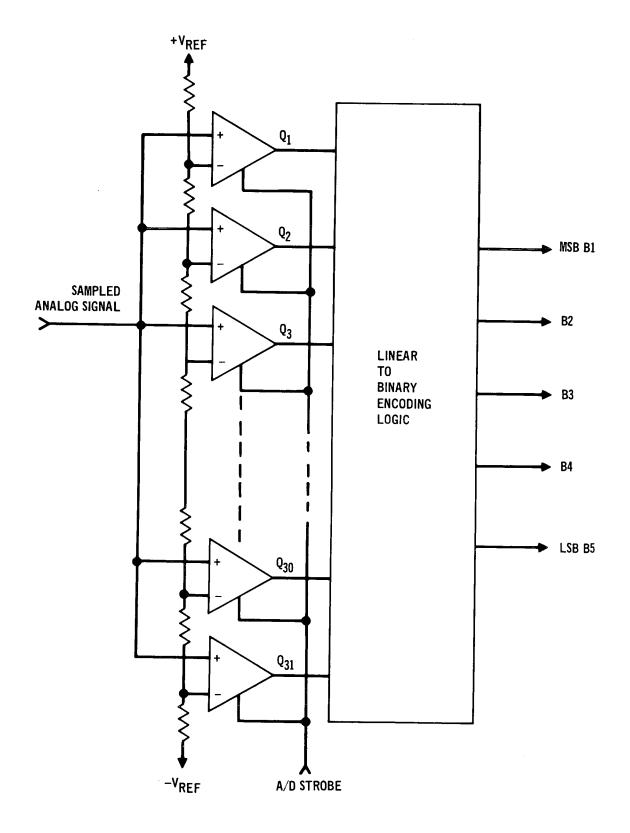

Figure 3-14 is a functional diagram of the A/D converter which was implemented using the parallel conversion technique. Thirty-one differential comparators were used in parallel. A divider chain composed of equal value resistors was used to set references at each comparator input. The analog sample is simultaneously compared to the 31 equally spaced reference levels. At this stage, the analog input is linearly related to the output states of the 31 comparators. A linear to binary converter was used to get the digital information into 5 bit binary format. Each differential comparator has a strobe input which is used to latch the data. This insures stable outputs during parallel to serial conversion.

The A/D converters were implemented using Mecl III type comparators and logic elements.

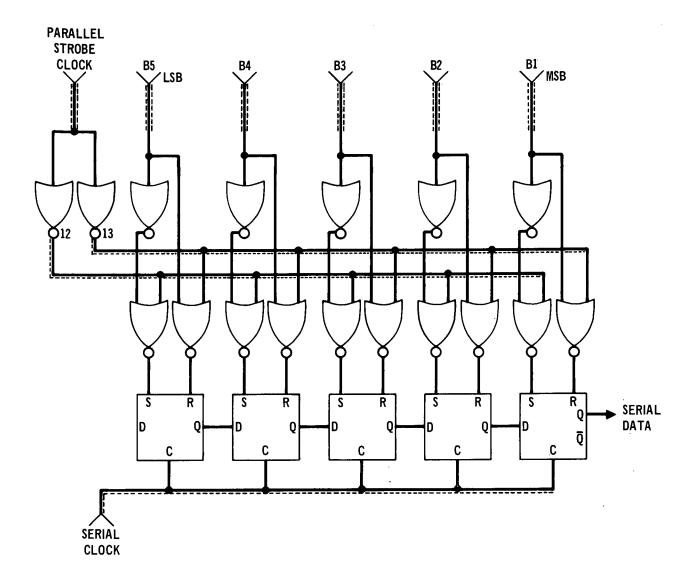

#### 3.3.4 Parallel/Serial Converter

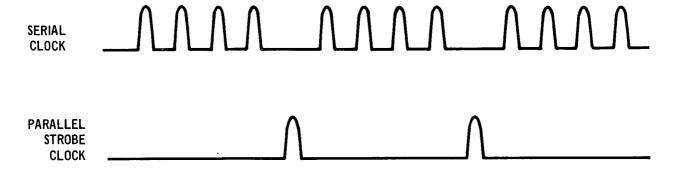

Figure 3-15 is a functional diagram of the parallel to serial converter. The 5 bit parallel words from the A/D converter are presented to the converter at inputs Bl through B5. These inputs are seen by the binary logic elements during the parallel strobe clock pulse at which time the binary logic element is either set or reset depending on whether a binary "1" or "0" is present at the respective B input. After this parallel strobing action the data is shifted to the right of the shift register at a rate that is equal to the frequency of the serial clock. Figure 3-16 shows the parallel strobe clock and the serial clock in the proper phase alignment. The serial clock has a pulse missing every five clock periods, this is to allow time for a new 5 bit parallel word to be strobed into the shift register. The input from B1 is present at the serial data output immediately after the parallel

FIGURE 3-14 A/D CONVERTER FUNCTIONAL DIAGRAM

FIGURE 3-15 PARALLEL/SERIAL CONVERTER FUNCTIONAL DIAGRAM

strobe. Thus the serial bit stream is not interrupted by the absence of the serial clock pulse.

The parallel/serial converter was implemented using Mecl III type integrated circuits and discrete clock and output drivers.

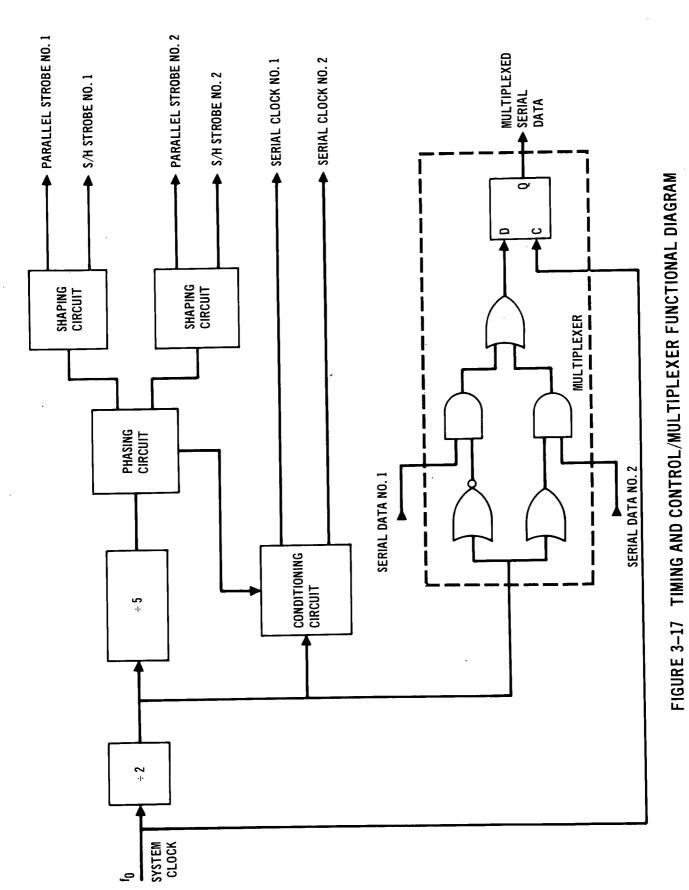

#### 3.3.5 <u>Timing and Control/Multiplexer</u>

The timing and control board contains circuits for clock countdown, clock conditioning, and clock driving necessary for proper operation of the entire signal processing electronics package. In addition it contains a digital

### FIGURE 3-16 PARALLEL/SERIAL CLOCK WAVEFORMS