# **NEW APPROACH TO TELEMETRY** DATA PROCESSING

NAS-

(NASA-TM-X-66248) A NEW APPROACH TO TELEMETRY DATA PROCESSING Ph.D. Thesis - Maryland Univ. (NASA) 170 p HC \$10.50

CSCL 09F

66248

Unclas G3/07 0.4314

N73-24183

X-522-73-135 PARTNER

# CARLO J. BROGLÍO

MAY 1973

GSFC

GREENBELT, MARYLAND

# A NEW APPROACH TO TELEMETRY DATA PROCESSING

by Carlo Joseph Broglio

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### ACKNOWLEDGEMENT

The author acknowledges a special debt of gratitude to his advisor, Dr. James Pugsley, for his numerous helpful suggestions and especially for his patience in the critical review of this thesis.

# PRECEDING PAGE BLANK NOT FILMED

iì

## ABSTRACT

Title of Thesis: A New Approach to Telemetry Data Processing Carlo Joseph Broglio, Doctor of Philosophy, 1973 Thesis directed by: Dr. James Pugsley, Associate Professor

A new approach for a preprocessing system for telemetry data processing has been developed. The philosophy of this approach is the development of a preprocessing system to interface with the main processor and relieve it of the burden of stripping information from a telemetry data stream. To accomplish this task, a telemetry preprocessing language has been developed. This higher level language contains statements designed using the jargon of telemetry data engineers and a set of simple but powerful operators for manipulating telemetry data. Also, a hardware device for implementing the operation of this language was designed using a cellular logic module concept.

In the development of the hardware device and the cellular logic module, a distributed form of control has been implemented. This is accomplished by a technique of one-to-one intermodule communications and a set of privileged communication operations. By creating a special state (called the control state), each module can direct the activities of the system. By transferring this control state from module to module, the control function is dispersed through the system.

A compiler for translating the preprocessing language statements into an operations table for the hardware device was also developed. This compiler uses a simple left to right single pass compilation algorithm. It can do so because the language is simple and has no operator precedence.

Finally, to complete the system design and verify it, a simulator for the collular logic module was written using the APL/360 system. This simulator

contains data sets which are images of the programs that are loaded into the various modules of the system. It then emulates the operations of the modules and produces timing data. The simulator was used to prove that the concepts and microcode loaded into the modules worked. The timing data gathered by it was used to form comparisons with a medium speed machine of the operations of a preprocessing program on the modular device with those on the medium speed machine. The results of this comparison show that the device compares very well, being a fraction of two to six slower on arithmetic operations, but two orders of magnitude better on the bit manipulation operations.

٩V

# LIST OF TABLES

| Table |                                         | Page |

|-------|-----------------------------------------|------|

| 2-1   | SET-UP SEGMENT RESERVE WORD LIST        | 14   |

| 2-2   | CONTROL INSTRUCTION GROUP               | 16   |

| 2-3   | DATA HANDLING INSTRUCTIONS              | 18   |

| 2-4   | OAO-A2 DIRECT DIGITAL FRAME FORMAT      | 22   |

| 2-5   | DIRECT DIGITAL DATA ELEMENTS            | 22   |

| 2-6   | DIRECT DIGITAL DATA PROCESSING PROGRAM  | 23   |

| 2-7   | OUTPUT DATA FORMAT                      | 24   |

| 2-8   | INPUT STRING PRECEDENCE                 | 26   |

| 2-9   | PARSER DECISION TABLE                   | 26   |

| 2-10  | FORMAT OUTPUT TABLE                     | 28   |

| 2-11  | ENCODED MODULATION CODE VALUES          | 28   |

| 2-12  | ENCODED TAPE PLAYBACK SPEEDS            | 28   |

| 2-13  | OPERATIONS TABLE                        | 29   |

| 3-1   | PROGRAM MEMORY LAYOUT                   | 38   |

| 3-2   | PROGRAM MEMORY WORD STRUCTURE           | 41   |

| 3-3   | ALU MODULE FUNCTIONS                    | 44   |

| 3-4   | ADDER ALGORITHM                         | 46   |

| 3-5   | SUBTRACTOR ALGORITHM                    | 48   |

| 3~6   | MULTIPLY ALGORITHM                      | 51   |

| 4-1   | SIMULATION RESULTS FOR THE ALU FUNCTION | 74   |

| 4-2   | SPECIAL FUNCTIONS SIMULATION RESULTS    | 78   |

| A-1   | INSTRUCTION SET                         | 110  |

# LIST OF ILLUSTRATIONS

| Figure      |                                                           | Page |

|-------------|-----------------------------------------------------------|------|

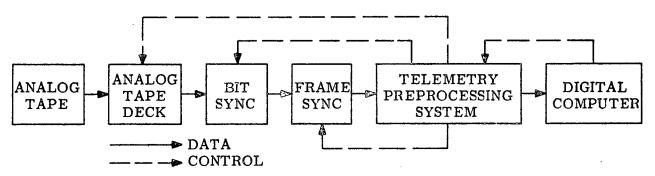

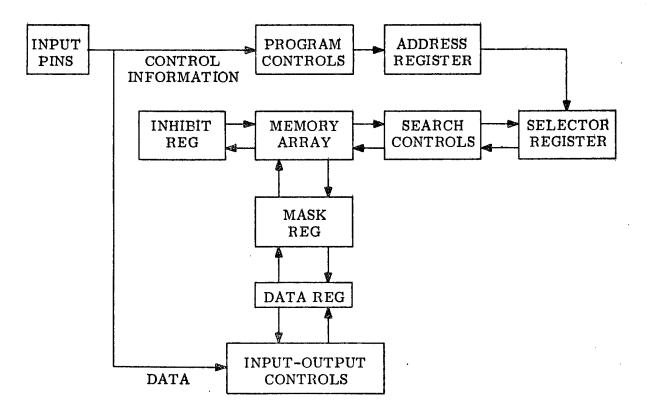

| 2-1         | PROPOSED TELEMETRY DATA ACQUISITION SYSTEM                | 9    |

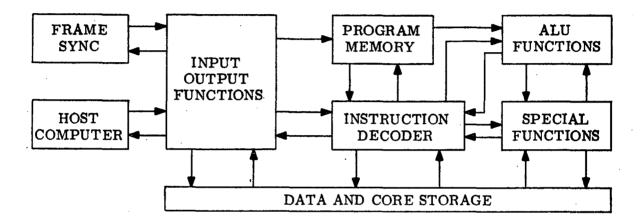

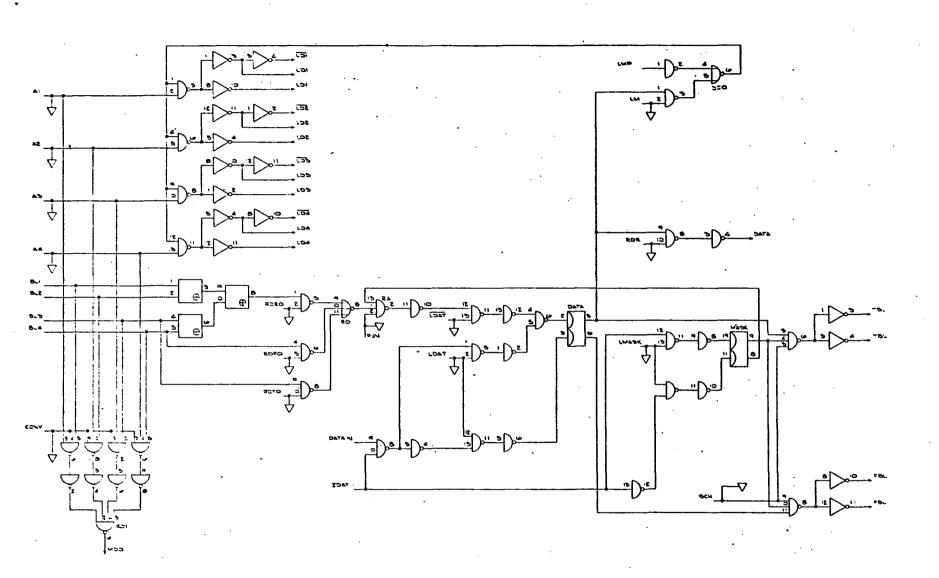

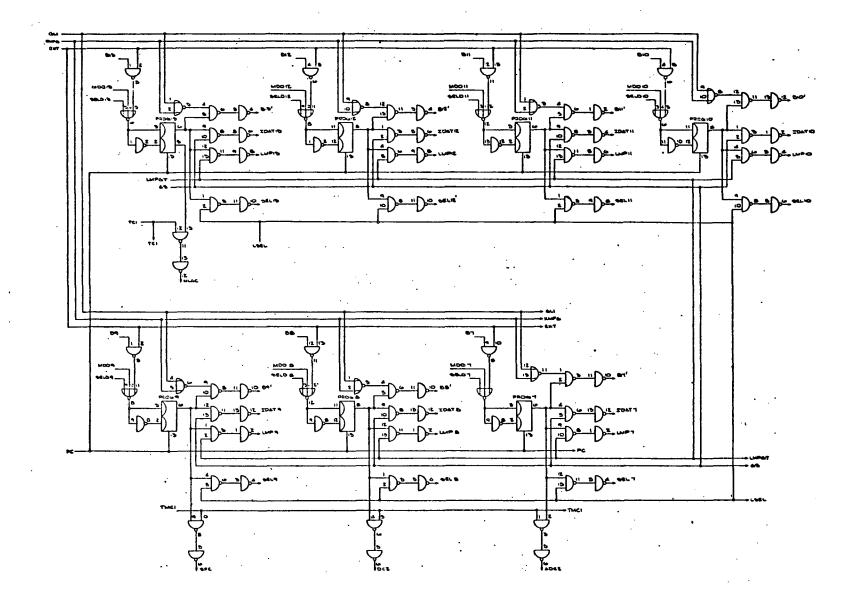

| 3-1         | PREPROCESSOR BLOCK DIAGRAM                                | 37   |

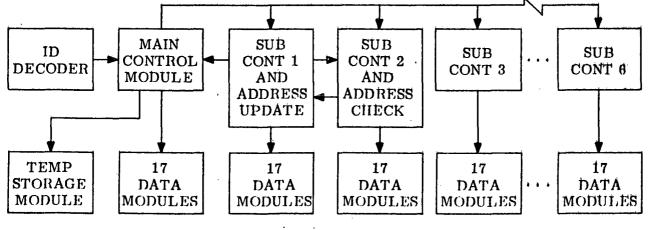

| 3-2         | PROGRAM MEMORY BLOCK DIAGRAM                              | 42   |

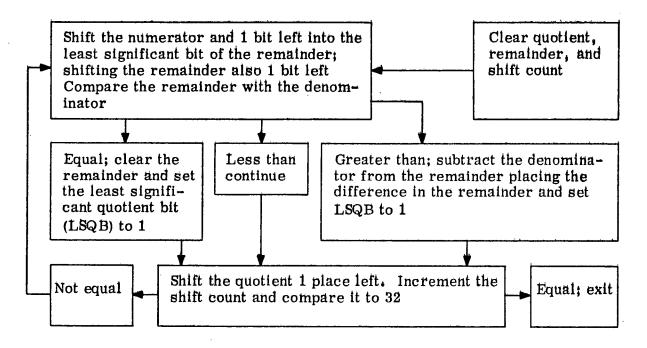

| 3-3         | DIVIDE ALGORITHM                                          | 53   |

| 4-1         | INFORMATION FLOW DIAGRAM OF A FUNCTIONAL<br>MEMORY MODULE | 68   |

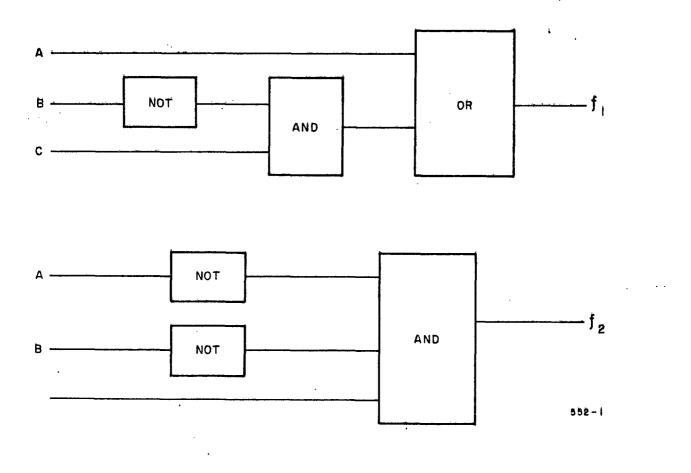

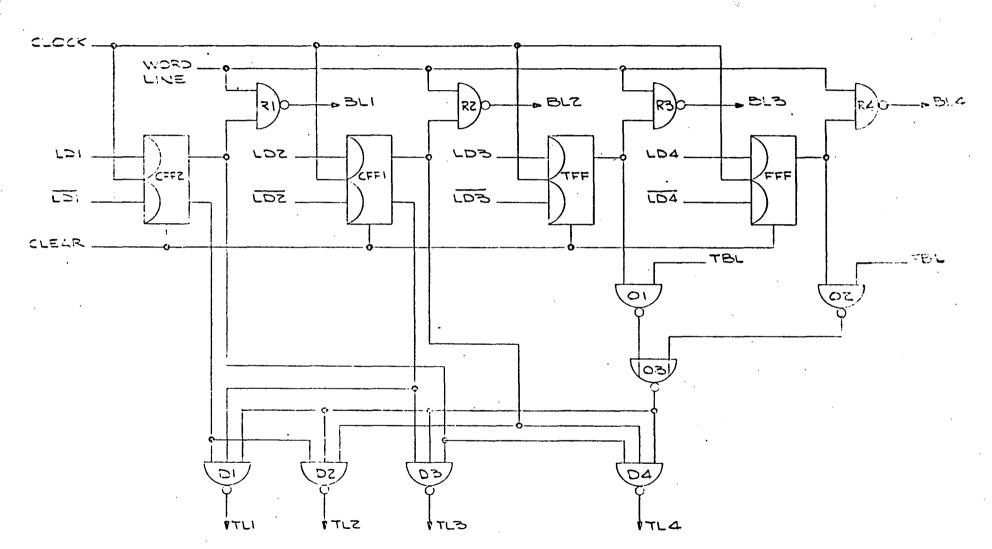

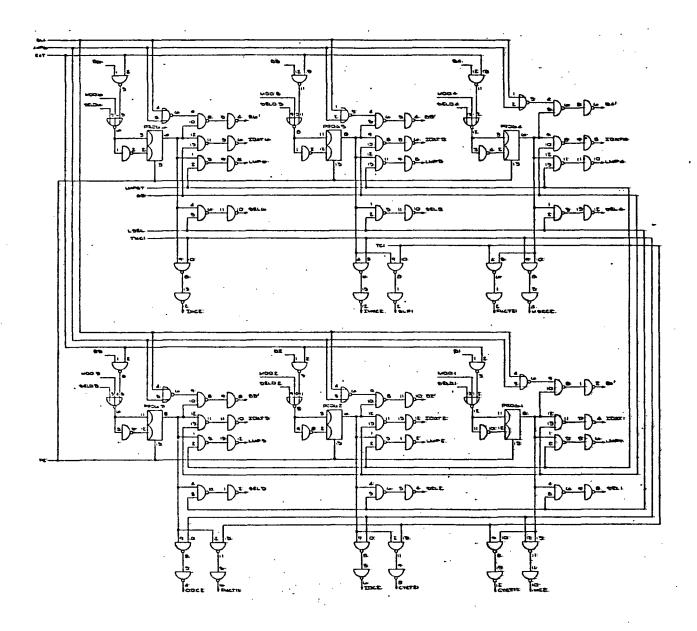

| A-1         | CLASSIC GATING STRUCTURE                                  | 86   |

| <b>A</b> -2 | MODIFIED GATING STRUCTURE                                 | 87   |

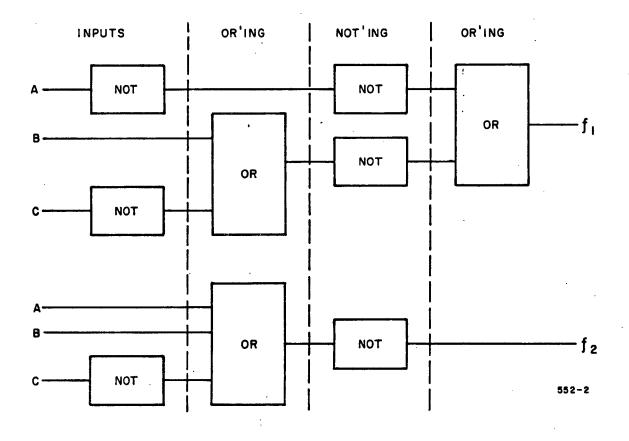

| A-3         | CONCEPTUAL FUNCTIONAL MEMORY CELL                         | 88   |

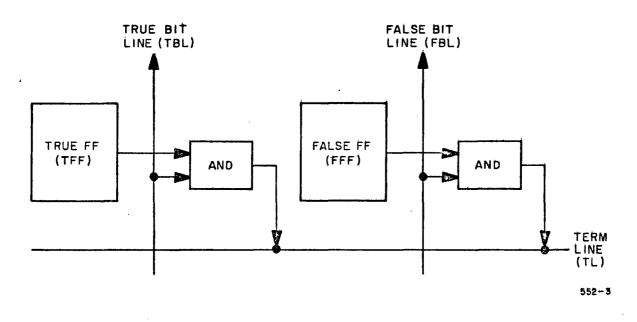

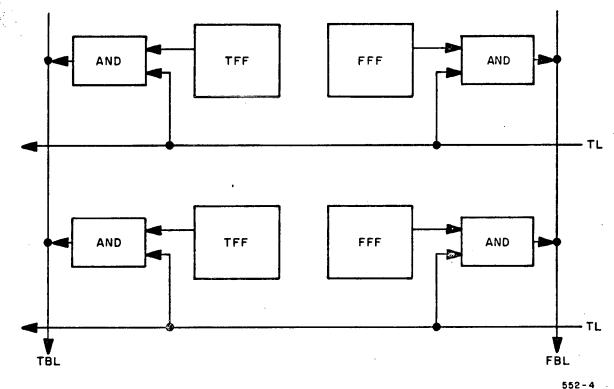

| A-4         | CELL INTERCONNECTION                                      | 89   |

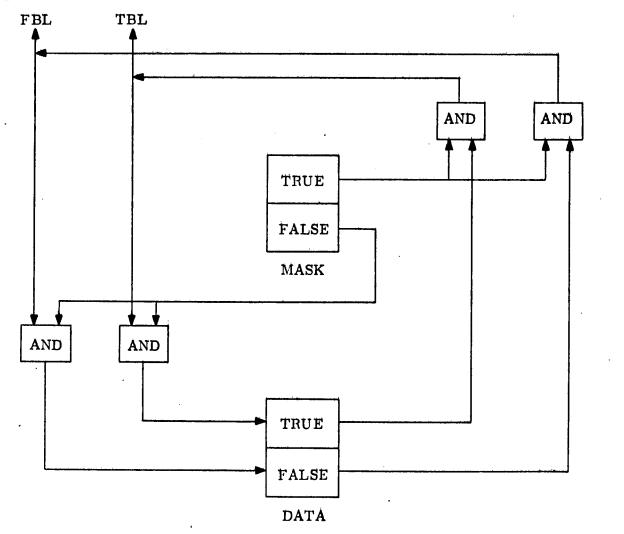

| A-5         | TYPICAL MASK AND DATA CELL INTERCONNECTION                | 90   |

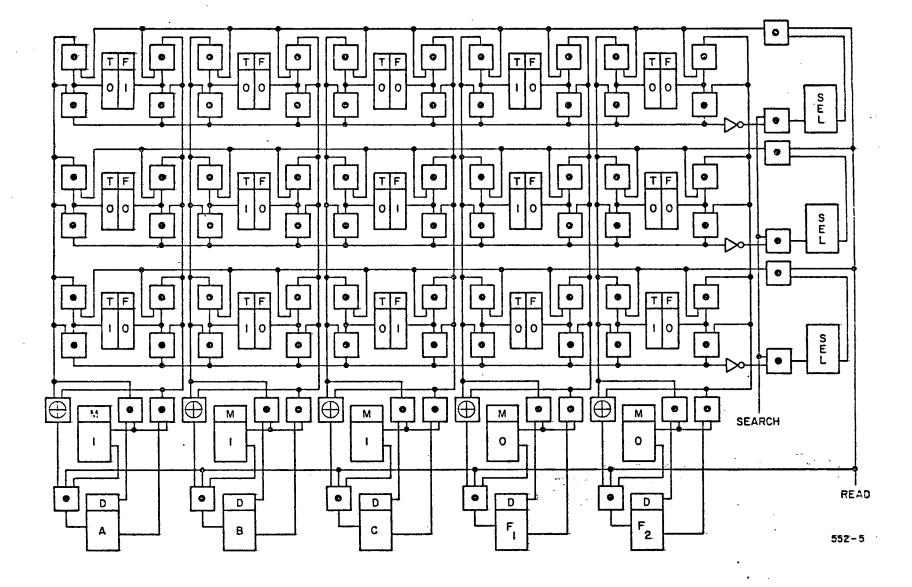

| <b>A-</b> 6 | PROGRAMMED FUNCTIONAL MEMORY UNIT                         | 92   |

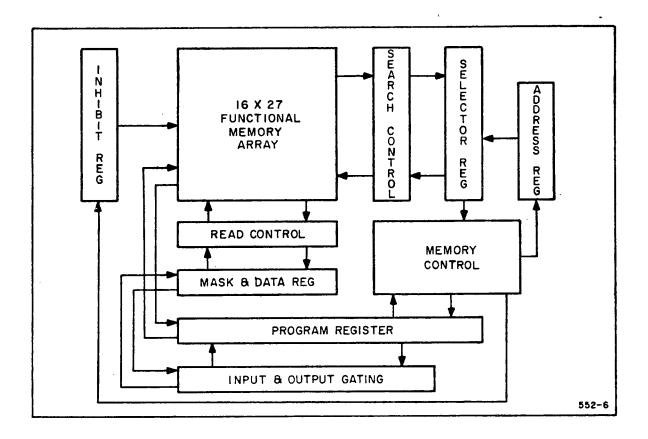

| A-7         | FUNCTIONAL MEMORY MODULE BLOCK DIAGRAM                    | 93   |

| <b>A-</b> 8 | FUNCTIONAL MEMORY CELL                                    | 95   |

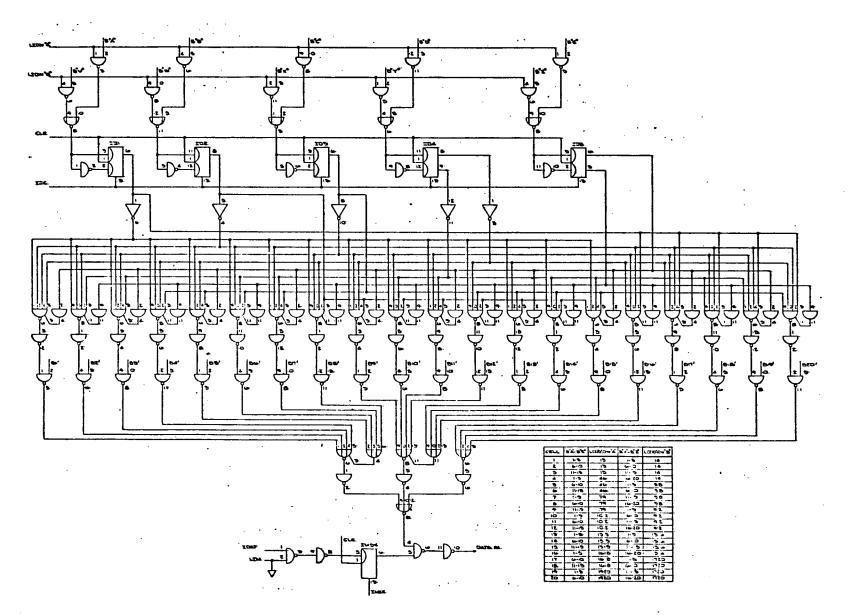

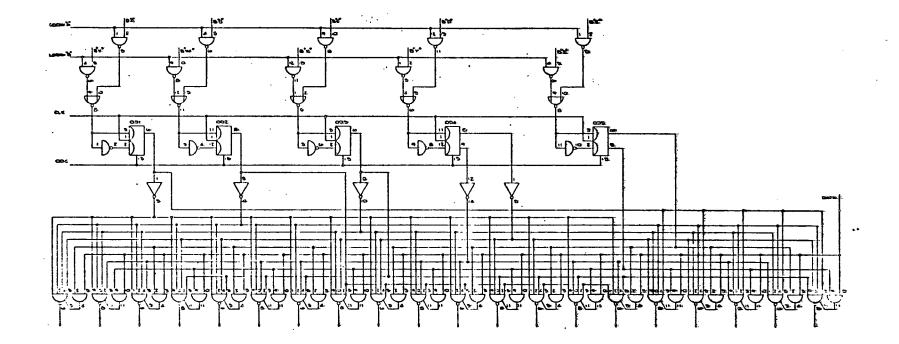

| A-9         | INHIBIT REGISTER                                          | 97   |

| A-10        | SEARCH CONTROL AND SELECTOR REGISTER CELL                 | 98   |

| A-11        | MASK AND DATA CELL                                        | 101  |

| A-12A       | INPUT GATING                                              | 103  |

| A-12B       | OUTPUT GATING                                             | 104  |

| A-13        | PROGRAM REGISTER (4 Sheets)                               | 106  |

| A-14        | ADDRESS REGISTER                                          | 116  |

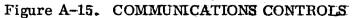

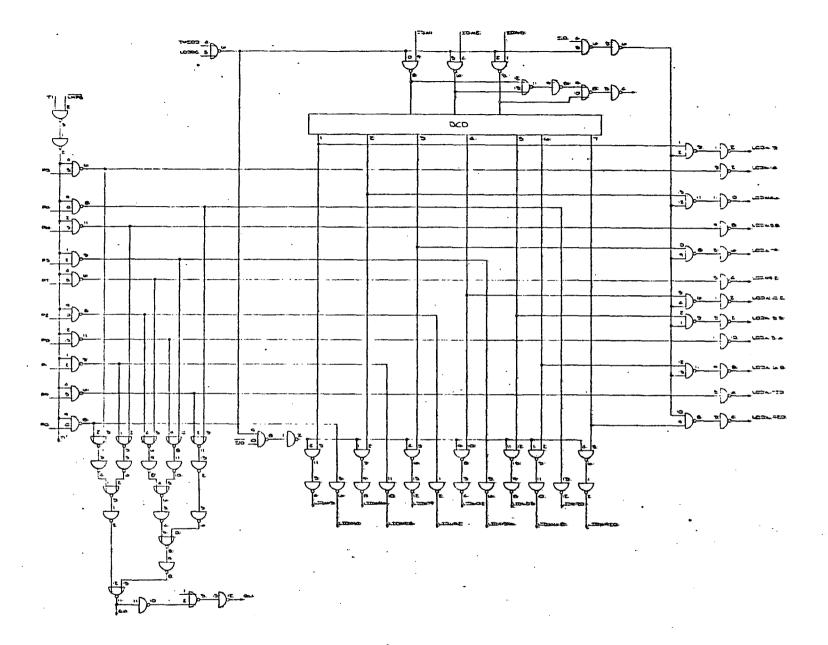

| A-15        | COMMUNICATIONS CONTROLS                                   | 118  |

| A-16        | I/O DECODER CONTROLS                                      | 122  |

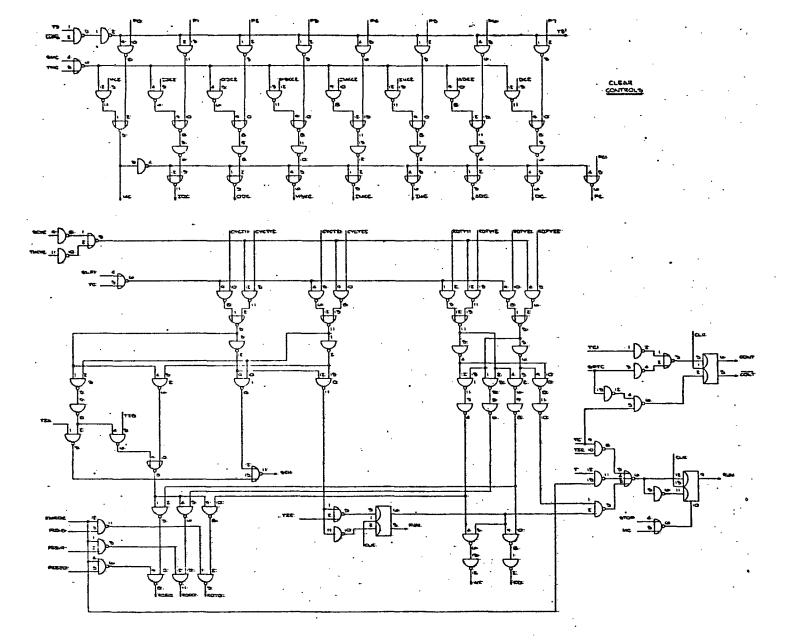

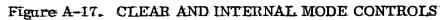

| A-17        | CLEAR AND INTERNAL MODE CONTROLS                          | 124  |

vi

#### CHAPTER I

#### INTRODUCTION

The action of telemetering data from spacecraft sensors to ground based processing equipment introduces a number of unique data manipulation problems. The basic cause of these problems is the need to combat noise in the space-toearth communications channel. Another cause of these problems is the use of spacecraft tape recorders. Since typically a tape cannot be changed while in flight, a method of recording in one direction and reading in the reverse direction is used. This, however, also causes the data to be transmitted backwards compared to non-recorded data.

The data under consideration in this thesis is strictly digital data. By this is meant, a sensor measurement value is coded into a set of ones and zeroes called binary digits. These binary digits (bits) are then telemetered to a ground based receiving station where they are recorded on an analog tape. This analog tape is transported to a processing facility. However, during the telemetering process the binary bits were encoded into one of several position-time sequences. These sequences are designed to combat a particular kind of noise which may be known or suspected to be present (reference 1). During the telemetering and recording process, the timing information necessary to reconstruct the sets of data bits has been lost. Hence, to reconstruct this information, special purpose equipment is required and various special techniques are used (reference 2).

First, the data bits must be reconstructed as accurately as possible. For this purpose a device known as a bit synchronizer is used. This device produces a "best estimate" of what the original bits were. It typically employs a maximum likelihood decision model. At this point in the processing, a stream of data bits is present. This data stream contains errors and must be regrouped into the

original sets of data values transmitted. These values are now called data words, each word being a known number of bits in length. But during the bit synchronization process, the starting bit position of the first word is lost and, thus, it is unknown where any data word begins or ends. Thus the technique of creating a special grouping of data bits into sets called data frames is used. These sets contain (usually as a prefix) a special known bit pattern called a frame synchronization pattern (FSP). A special device known as a frame synchronizer is used to "search" the data stream for this pattern. This is done typically by placing the desired FSP in a data register and shifting the data stream through another data register. A comparator is placed between the two registers and contains a preselected error tolerance. When a bit by bit match is obtained between the two registers that falls within the error tolerance, the pattern is considered found. At this point it is possible to separate the data bits into the specified data words and the telemetered data is considered to be recovered. Typically, the data is then transferred to a general purpose computer and the data processing phase begins.

At this point in the operation, several observations should be made. No spacecraft currently being flown contains only one sensor. In fact some contain hundreds of sensors. In the data frame scheme described, not all sensor outputs need to be in a single data frame because, such a scheme implies a fixed sampling rate. Furthermore, a standard governing the size (in bits) of data words and data frame (reference 3) exists. Hence, not all sensors can be placed in one data frame and, quite often, sensor values cannot be placed in single data words nor even in consecutive data words. Thus, some sensor data values may be distributed in words throughout the data frame. Other words of the data frame may contain a sequence of sensor values on consecutive data frames (a process called subcommutation). When subcommutation is used, a method for determining the start of the sequence must be present. Usually a data word is used for

this purpose. For example, a word may contain a binary counter which represents the sequence number of this data frame and identifies what sensor values are present.

In addition, many spacecraft use a method of parity generation to insure error detection capabilities. When this is present, the parity for the received data must be computed and compared with the received parity to determine if an error has occurred. As a further assurance of how well the system is operating, the bits contained in the FSP are compared with those expected and a count of the errors is maintained. This error count is used as a measure of the error level of the bit stream. Finally, to assist the bit synchronization process in cases where it is suspected that data values may not change for many bit times, certain bits of the data stream are complemented.

All of these observations noted here require a set of data processing functions to be implemented. These functions are needed to transform the data frames into data values that the computer can work with. However, these functions do not contribute directly to the data processing operation. Further, these functions are awkwardly handled in a large general purpose processor since most of these machines are designed for data computation and have limited bit manipulation capabilities. The problem is further compounded by the fact that most higher level programming languages are also designed to do computations and many are very inefficient at bit manipulation. Efficiency becomes important for two major factors. First, spacecraft generate a large volume of data; greatly reducing total run times can be accomplished by saving instructions in highly repetitive operations. Second, a need often exists to handle the data as it is received in real time and hence not much processing time is available. A final observation is that the data is transferred into the computer over one of its inputoutput channels. This means that the data words are stored consecutively in the

computer's internal data words. The size of these two different words is rarely identical and thus represents an unnatural data set to the computer because, data words are not on computer word boundaries.

Under the current method of telemetry data processing, these problems are handled by programs coded at the machine language level. Hence, if more than one type of computer is involved at the frame level of processing, as is typical, a costly duplication of programming effort is required. Further, any event which causes a change in the data format (e.g., a failure on the spacecraft while in orbit or, a design change in a family of spacecraft) requires extensive reprogramming to accommodate. Several attempts have been made in the past to generalize some of these functions (references 4, 5, and 6). These approaches, however, were either too specialized to a specific machine configuration or too cumbersome and complex to be used effectively.

The work of this thesis is directed toward the solution of these problems while overcoming the difficulties of the past approaches. In the context of this solution, it is assumed that a special-purpose device will be placed between the frame synchronizer and the host computer's input-output channel. This device will have the ability to pass the necessary parameters to the frame synchronizer subsystem to enable it to run. The device will then accept data from the frame synchronizer, and reformat this data into sensor values which will appear on the host computer's word boundaries. Finally, the functions of parity checking, word reversal, bit complementing, data counter continuity checking and FSP error measurements will also be done in this device, thereby allowing the host computer to concentrate on data processing.

To overcome the difficulties and costs encountered in programming the required bit manipulation functions, a special-purpose higher level telemetry preprocessing language has been designed. This language concentrates on bit

manipulation methods and has only a minimal set of computation instructions. The statements of this language are derived from telemetry data handling engineer's jargon and hence, programs in this language represent a concise description of the telemetry data frame. Perhaps the biggest advantage of this language is the ease with which the programmer can accommodate changes in the data format's structure.

Since the device which implements the language must be able to interface with a wide variety of host computers on one end and a number of different frame synchronizers on the other end, a microprogrammed (reference 7) approach was taken. Another factor influencing this decision was the wide variety of internal computer formats which must be accounted for, since this device must appear to be a standard device to the host machine. By appearing as a standard device, the host machine's operating system can be used with minor changes and hence the system integration costs are minimized.

Having decided to use a microprogrammed approach, the operations specified in the preprocessing language were examined to determine what microcoded functions were required. It was observed that: a) telemetry words vary in size from 6 to 32 bits, <sup>1</sup> b) bit for bit word reversal is a nontrivial function, and c) selective bit complementation is a special operation compared to all the other functions required to implement the preprocessor. Upon examining "off the shelf" microcoded machinery, these operations are not part of the standard functions offered. Further, many of the word sizes required are not compatible with the machines' internal data structures; hence, using one of these machines

J

<sup>1.</sup> The Standards (reference 3) claim larger word sizes, but in practice they are never used. In fact, the hardware currently in use will accommodate a maximum word size of 32 bits.

would represent a transferal of the problem from the conventional general purpose machine to the microcoded one and, many of the past difficulties would still be present. Thus the operations of the preprocessing system were examined to find the most uniform approach to the total system design. To accomplish this task, a design of an integrated circuit chip, implementing a concept known as a functional memory (reference 8), was completed. This module design offers the power of implementing all the required logical functions with a single chip structure. The interconnection between these chips is accomplished with another chip structure thereby yielding a system with only two basic parts.

The functional memory module is discussed in detail in Appendix A. The term functional memory denotes a device used to generate Boolean functionals in a memory device. Basically, it is a method of arranging a cellular memory array such that, each cell of the array can be either an associative memory cell or a conventional memory cell. Additional gating is provided at the array boundaries so that Boolean functions can be generated by using the above two memory types in combination. The associative nature of the memory is used to "search" for a set of preprogrammed Boolean expressions in the input data. Then the results of this search are used as a conventional address to "read" the function output from specified cells of the array.

In order to implement a system of this type the concept of distributed control was used. This concept treats each module as an independent processing station and represents a means of networking these stations.

The concept of distributed control was hinted at in an article by L. J. Koczela (reference 9). This is basically the replacement of the conventional single control unit by a transferable abstraction of the control function. This implies that each functional memory array of the system contains a flip-flop indicating whether or not it has system control. If it has system control, then it

is allowed to carry out certain privileged global operations. These operations primarily deal with the intermodule data communication system. Only a module in control is allowed to transfer data over the communication bus to other modules and initiate cycles within those modules. Further, control can be both transferred and retained by the issuing module, thus allowing independent control sequences to be simultaneously initiated. By the use of this concept, the data flow paths through the various functional elements are directed with the net result being that the data flow path through the system determines the total processing function to be performed.

A conventional control approach with one or more modules making up the control function could have been implemented, but this approach would represent a more complex design. With distributed control, no subsystem needs to know what functions are being executed at all parts of the machine. It merely needs to know what the data destination is and where to pass control. This simplifies the design by necessitating fewer system wide control lines and allowing independent functions to complete their tasks at the rate which the tasks require.

In summary, this system offers two advantages capable of overcoming the difficulties of past approaches. These advantages are a higher level telemetry preprocessing language and a peripheral device to implement that language in microcode. The language offers to the user the capability of specifying in nearly English terms, the transformations that he desires to perform on the telemetry data stream. These terms were derived from the jargon used by the handlers of telemetered data and hence, should be readily understood by workers in this area.

The microprogrammed peripheral device has the advantage of separating the operations to be performed from the main computer. This helps the problem solution in two ways. First, it simplifies the processing program in the main

computer by preparing a data set for it and hence, relieving this processor of many bookkeeping and manipulation functions which do not contribute to the processing operation directly. Further, many of these functions are not implemented in the standard instruction set and thus are inefficient to implement. Secondly, by being a microcoded device, it is adaptable to most commercially available computers since the microcode can be changed to suit the host computer and thus the device becomes installation independent.

The remainder of this thesis will describe the above problem solution in detail and develop in depth the concepts and techniques used. Chapter II presents the telemetry preprocessing language. The elements of this language are defined and explained by use of examples. A compiler for this language which was written in APL (references 10 and 11) is also described in this chapter.

Chapter III discusses the design and microcode sequences of the peripheral device developed to implement this language. Chapter IV describes an APL simulation of the system and presents a discussion of it. Chapter V presents the results, conclusions, and recommendations of this work. Appendix A is a detailed presentation of the functional memory module chip design. Appendix B is a metalanguage description of the telemetry processing language. Appendix C is a description and listing of the APL compiler. Finally, Appendix D is a description and listing of the APL simulation programs.

#### CHAPTER II

#### THE TELEMETRY PREPROCESSING LANGUAGE

#### A. The Problem Environment

In Chapter I, the various parts of a telemetry data acquisition system were introduced and the interfaces to this research were discussed. These concepts are shown again here in Figure 2-1. In this figure, the telemetry data is input to the system on what is called an analog tape. The name "analog" is somewhat misleading because the recorded signals are digital pulses (i.e., on-off type). It is called analog because the timing information needed to recover the data is not recorded on the tape and the techniques used to recover that information are analog in nature (e.g., a phase-locked loop).

As is shown in Figure 2-1, the proposed telemetry preprocessing system has two functions. First, its main task is to reformat the frame synchronized data into sensor values capable of being processed directly by the digital computer. Second, it is designed to distribute the necessary control parameters to the acquisition system to allow it to operate. While this capability is designed into the system, it is not necessary for its operation. Hence, the preprocessing system can operate in cases where other forms of control are desirable or in cases where other configurations are necessary (e.g., a digital tape could input directly to the telemetry preprocessing system in the figure).

Upon closer examination of the system of Figure 2-1, the parameters necessary for this systems operation are easily determined. The analog tape deck needs to know what speed is required to run the analog tape since these units are typically designed to run at several speeds. The bit synchronizers are designed, to run over a broad range of data rates (called bit rates) and also can handle several forms of modulation codes (called code types). Hence the desired bit rate and code type are necessary parameters. Finally, the frame sysnchronizers are typically generalized to handle all the standard types of formats (reference 13). The necessary parameters required to define these formats are the number of bits in a telemetry data word, the number of telemetry data words in a telemetry data frame, and the frame synchronization pattern.

The last three parameters (bits/word, words/frame and FSP) form part of the input constraints to the telemetry preprocessing system and are used by that system to locate data values and to perform some of the error measurement computations briefly discussed in Chapter I. These computations will be described in greater detail later.

The other input constraints were also briefly mentioned in Chapter I and consist primarily of data formatting and translation problems. The data formatting problems are: 1) reversed data where the least significant bit of the data value is transmitted last; this requires a bit for bit reversal of the data value; 2) dispersed data where parts of the data value are found in different telemetry data words; this requires a bit-by-bit assembly of the data value from several telemetry data words; and 3) complemented data bits; this requires selected bit complementation.

The data translation constraints consist primarily of error checking computations. Data parity checks can be generated by either the spacecraft telemetering system or by the experiment measuring system of the spacecraft. These

checks can be either even or odd parity. If the telemetering system imposes the parity, then the parity check must be done on the bits in the order which they were transmitted. If the experiment system imposes the parity, then the parity check must be done on the bits after the data value has been assembled.

Counters appearing in the data should be checked for the continuity of the count. These counters may be either forward counting or backward counting. The telemetry preprocessing system should be capable of establishing the correct count value, flagging counts that are received in error, and keeping a record of the number of counts that are received in error.

Finally, since the frame synchronization pattern is the primary measure of the received error rate and is used for data quality assurance purposes, the telemetry preprocessing system should be capable of performing all the necessary error computations on this pattern. These statistics are collected on a frame-by-frame basis, as well as in an overall cumulative form. The statistics to be collected are: 1) a bit-by-bit error distribution, 2) a one-to-zero error distribution, and 3) the total number of errors.

In addition to the input constraints on the preprocessing system, the host digital computer which receives the data imposes output constraints. Since the main purpose of the preprocessor system is to free the host computer from those functions that are not directly related to the processing of sensor data, care must be taken to avoid additional non-related processing tasks which would be required to accommodate the output of the preprocessor. Thus the preprocessor output must be compatible with the host computer's internal data format. If the preprocessor were to appear to the host computer as a standard peripheral device, the programming impact on its operating system to accommodate the preprocessor could be minimized. Further, the data storage scheme used by the telemetry preprocessing language should be compatible with the data retrieval scheme

used by the host computer's data processing program; i.e., an operation similar to a COMMON statement for FORTRAN programs should be implemented. While many of these functions are hardware related and are handled by the preprocessor hardware design (described in the next Chapter), the data storage allocations and contents are described in the telemetry preprocessing language.

Finally, as in any language, certain instructions are provided for programming convenience. These are computed branch instructions provided to alter the execution sequence of instructions, conditional branch instructions provided to alter the execution sequence dependent upon conditions in the data, and looping instructions provided to allow repetitive operations to be concisely stated.

All of the above constraints and conditions described in this introduction form the context within which the telemetry preprocessing language is intended to operate. To facilitate the coding of statements in this language a compiler was designed and coded in the APL language (references 10 and 11). For simplicity, this compiler assumes that the language statements are to be input on 80 column cards. Hence, general field delimiters are not used; instead, column positions and blank columns are used to delimit statement fields. The language is context dependent; hence, not all statements have the same number of fields. However, all cases are unique; thus no ambiguities can arise. The output of this compiler is an operations table which is a coded set of the operational steps that are required to implement the statement of the language. This table will be described later in this chapter.

The compiler contains an extensive set of error messages to assist the programmer in detecting and correcting syntax errors. It also allows the programmer to use symbolic addressing and symbolic address computation. Hence, by the use of descriptive names for the sensor value addresses, it is possible to

have the telemetry preprocessing language program appear to a knowledgeable reader as a shorthand English description of the telemetry data frame.

#### B. <u>The Language</u>

This section describes the syntax of the telemetry preprocessing language along with those compiler functions necessary to implement that syntax. The elements of the telemetry language consist of all the capital letters, the digits zero to nine, and the special characters:  $+ - \frac{1}{2}$  () / , . = and blank. These elements are then grouped to form variables which are used to either index data values, to form data destination addresses, or to specify the operations to be performed on the telemetry data. The telemetry language is logically divided into two segments: the set-up descriptors and the frame descriptors.

The set-up descriptors form a table which contains the parameters required to configure the frame synchronization data acquisition system discussed in the introduction. This segment of the language contains statements. Such statements, being the specifications of operations to be performed, consist of three fields: a location field, an instruction field, and a parameter field. The names given to these statements derive from the content of their instruction fields. The segment begins with a FORMAT statement and ends with an END statement. The location field contains the identifier of the telemetry data frame being described. The location fields of all other statements in this segment are ignored. The location field is considered to be nine elements long and is blank-filled to that size with the information being left-justified.

The identifier field is 10 elements long and begins in column 10 of the input card. Table 2-1 contains a list of the parameters identified in this segment.

FSP denotes the right-justified frame synchronization pattern. The pattern which appears in the parameter field of the statement may be an octal number which is prefixed by the letter "o", a binary number which is surrounded by

parentheses, or a combination of the two. In any case, the binary equivalent of this parameter must represent the exact pattern right-justified. In this manner the compiler can determine the number of bits to use in setting the preprocessing system for the required error calculations and also what pattern to send to the frame synchronizer.

| INSTRUCTION                                                                     | <u> </u> |

|---------------------------------------------------------------------------------|----------|

| FORMAT<br>FSP<br>CODE<br>BIT RATE<br>BITS/WORD<br>WORDS/FRAM<br>TAPE SPD<br>END |          |

| Table 2-1. | SET-UP | SEGMENT | RESERVE | WORD | LIST |

|------------|--------|---------|---------|------|------|

|            |        |         |         |      |      |

CODE specifies the telemetry modulation type to be used by the bit synchronizer and is an optional parameter. The legal modulation types are: SPPH, BIPH, RZ, NRZ, NRZM, NRZL, and NRZC. These codes are described in the standards (reference 3).

BIT RATE is the telemetry transfer rate at which the bit synchronizer is to run, and is an optional parameter. The value in the parameter field may be a decimal, octal, or binary number.

BITS/WORD specifies the number of bits in a telemetered data word. This parameter is required since the preprocessing system uses it to determine how to store the telemetry data in its internal structure.

WORDS/FRAM specifies the number of telemetered data words in a telemetry frame. This parameter is required so that the preprocessing system can allocate its internal resources.

TAPE SPD is the speed to be used in reading an analog tape and is an optional parameter. The legal speeds are: 120, 60, 30, 15, 7-1/2, 3-3/4, and 1-7/8 inches per second. All of the necessary parameters must be present when specifying the setup description segment; otherwise, an improper format syntax error is encountered.

The frame description segment contains the instructions which form the main working portion of the language. These instructions form three functional groups: a control group, a storage allocation group, and a data handling group. This segment begins with a FRAME statement and ends with an END statement. The location field of the FRAME statement identifies what data frame is being described. The name located here must match the name in the location field of the FORMAT statement defining the set-up table for this telemetry data frame.

All the statements of this segment except the END statement contain a nine element location field which may be blank. Further, with the exception of the FRAME statement, these location field variables may be subscripted. When subscripting is used, the assigned location of the variable is used as a base address to which the computed value of the subscript is added to yield a final storage address.

The storage allocation group of instructions contains three fields: a location field, a type field, and a parameter field. Since it is being assumed that there are two independent types of storage in the preprocessing system (a program store and a data store), and that the contents of these storages may not be mixed between program and data, two types of storage allocation instructions are required.

The storage allocation instruction that specifies addresses in the program memory is the CONTINUE statement. The location field of this statement contains a symbolic name of an address in the program memory. When this name is referred to by other statements in the language, its value will be the address of the statement following the CONTINUE statement in the program.

The storage allocation instruction that addresses only the data memory is the DIMENSION statement. This statement uses all three fields of this group. All variable names which reference the data memory must be dimensioned before they are used in a statement. The parameter field of this statement denotes how many consecutive data storage locations are to be assigned to this name.

The control group of instructions contains three fields: a location field, an instruction field, and a parameter field. This group of instructions deals primarily with bookkeeping, decision making, and order of execution types of operations. These instructions are used to compute and assign values to index registers to perform both conditional and unconditional branching operations, and to form program loops. Inclusion of these types of operations enables programs to be written in compact form and also allows conditions within the data to alter the program execution sequence. Table 2-2 lists the instructions included in this group.

|       | · · · · · · · · · · · · · · · · · · · |       |

|-------|---------------------------------------|-------|

| ATION | INSTRUCTION                           | PARAM |

Table 2-2. CONTROL INSTRUCTION GROUP

| LOCATION | INSTRUCTION | PARAMETER                                           |

|----------|-------------|-----------------------------------------------------|

| N        | <pre></pre> | <pre><location> F, V = I, E TRUE 0</location></pre> |

The first expression in the table is an index definition statement as delimited by the presence of the equal sign. The name to the left of the equal sign is the symbolic name of the index being defined. The arithmetic expression on the right may have any number of levels of parentheses, and any legal (to be defined when the compiler is discussed) combination of adds, subtracts, multiplies, and divides. The variables appearing on the right may be decimal numbers or the symbolic names of previously defined variables. This statement may have a

location symbol; if it does, the value of the index as computed from the arithmetic expression will be placed in the data memory location specified by the location field.

The GO TO, REPEAT, and IF instructions must have null location fields. The names in the GO TO and IF instructions must appear as a location expression of a CONTINUE statement. The GO TO instruction is an unconditioned branch to the specified location. The IF instruction is a conditional branch instruction. If the logical expression (to be defined) is true, then, the branch to the specified location is executed; otherwise, execution continues with the next instruction.

The REPEAT instruction is used to perform a looping operation. The loop index (V) is specified by name. The initial value of the index is the value of the first simple arithmetic expression (I). The final value which will cause the loop to be exited is the value of the second simple arithmetic expression (E). The REPEAT instruction is used to repeat the next F instruction in the program. The way in which the loop operates is as follows: the loop index is incremented by one and compared to the final loop value for the equality condition every time the end of the loop is reached. When equality occurs, the loop is exited at the next instruction beyond the end of the loop.

Two important restrictions must be remembered. First, if the variable is not a decimal number, it must be the name of a previously defined index. Second, the loop index may be altered within the loop, but care must be taken to insure that equality will result at the end of loop test.

The EQUATE statement must have a name in the location field. This name must match the name of a frame identifier. This statement is used to define a frame which is simply the reverse of another defined frame; a condition commonly prevalent when spacecraft recorders are used.

The index definition instruction may have a location symbol; if it does, the value of the index as computed by the definition of that index will be placed in the specified data memory location.

A note on the card formats for these instructions, the GO TO and REPEAT instructions have arguments which must begin in column 20. All others begin in column 10 and continue until a blank is encountered.

Logical expressions are formed by a set of arithmetic expressions whose values are either zero or one, and variables whose values are either zero or one connected by the logical relators: EQUAL, NOT EQUAL, LESS THAN, LESS THAN OR EQUAL TO, GREATER THAN, GREATER THAN OR EQUAL TO, AND, OR, and NOT. One important rule of operation must be remembered: the order of evaluation is left to right with no precedence among the operators. However, note that in both arithmetic and logical expressions, any level of parenthesis is allowed and here the evaluation sequence may be altered. Also, in logical operations, the unary operator NOT means complement the operand to its right. If that operand is a variable, the value of that variable will be complemented prior to comparison.

The data handling instructions form the main working section of the language. They are used to extract sensor data values from the telemetry data words and to perform all of the data manipulation functions that are required. These instructions contain two fields: a location field and an operation field. The location field contains a pointer to the data memory address where the assembled data value is to be stored. The instructions of this group are listed in Table 2-3.

| LOCATION | INSTRUCTION                                                                                                      |

|----------|------------------------------------------------------------------------------------------------------------------|

|          | SYNC, M (A, B, C)<br><location name="">, M (A, B, C)<br/>WORD, M (A, B, C)<br/>SUB, M, K, O (A, B, C)</location> |

#### Table 2-3. DATA HANDLING INSTRUCTIONS

In this table, M is a modifier operation which may be L (to indicate that the word has its least significant bit first and, an end for end bit reversal must be done) and/or one of the following: PET, PEA, POT, POA, or blank. The modifiers PET, PEA, POT, and POA specify that the associated data value is to be checked for a parity error. The parity bit to be used for comparison is the bit specified by the word control section of the instruction containing one of these modifiers. The type of check to be performed is specified by E for even parity or O for odd parity. The time that the check is to be performed is specified by either T for before manipulation or A for after manipulation. The result of the parity check is to set the sign bit of the specified data memory word to 1, if a parity error is detected and, to 0, if not.

The data value to be checked is specified by those instructions that are linked to the one containing the parity check modifier. Instructions may be linked by either plus or minus signs. The linkage symbols are fully distinguished from their arithmetic counterparts by their location in the instruction stream.

The plus linkage implies that the bits specified by the instruction immediately following will be appended to the right of the bits already extracted. The minus linkage implies that the complement of those bits will be appended. In this manner a new data value is formed from the input bit stream.

The bits to be manipulated in the above manner are specified by the parameter set (A, B, C). A is the telemetry word number to be processed. This parameter can be a number, a variable, or a simple two variable arithmetic operation. B is the number of the starting bit within the telemetry word. C is the number of bits to take from the telemetry word. Taken together these parameters define a new information word derived from the original stream.

SYNC is the instruction used to indicate the location of the frame sync pattern (FSP) in the telemetry data frame. The SYNC instruction doesn't place the

frame sync code in the data memory; instead, it retrieves the frame sync code from the format table word and compares it with the data value bit by bit. It then replaces this data value in the data memory by a set of words representing: 1) the total number of errors in the frame sync pattern, 2) the number of pattern ones in error, and 3) the "exclusive or" of the pattern and the received frame synchronization code. In addition to this, it keeps a cumulative set of registers containing the statistics of items 1 and 2 above.

In the location name operation, the name must be a defined data memory address. Hence the parameter set will operate on the data memory locations specified by name, whereas in the other data handling, the operations are performed on the input data set.

The WORD instruction is used to extract sensor data values from the telemetry data words.

SUB is the instruction used to indicate the presence of a subcommutation counter and initiates the accumulating of statistics and the smoothing of this counter; i.e., error flagging and a continuity check.

The SUB instruction and the SYNC instruction are the only two instructions which involve more than one data frame in their execution. The SUB instruction is designed to determine whether or not the sequence of values received for a data counter is correct. It also gathers error statistics concerning the condition of the data counter. In order to perform these functions, this instruction must determine what the expected count value should be. This is done by scarching for three consecutive received counts. The count mode (K) of the instruction specifies whether to look for forward (F) or backward (B) counting. Further, the counter modulus (O) in the instruction specifies the range of the data counter.

This instruction forms a value for entry into the data memory in the same way as the word instruction, but with two exceptions. While searching for three consecutive count values to establish the counting sequence, the sign bit of the stored data word is set. Then, once a sequence has been established, the expected count value will replace any count value received in error, with the sign bit being set to denote the replacement of the received data. A count sequence, once established, may be broken by the reception of three consecutive counts received in error.

This instruction maintains a set of error counters throughout the processing operation. These error counters are read out to the host machine upon request and represent: 1) the number of times a new sequence had to be established, 2) the number of counts in the search state, 3) the number of erroneous counts received while in a sequence, 4) the total number of counts received while in a sequence, and 5) the number of attempts made to establish a sequence.

Comments in the language, when punched on an 80 column card, can be entered either with an asterisk (\*) in column 1 or after a blank at the end of a language statement. Comments may appear anywhere within the telemetry language. A final note on card formats is that, if the linked data handling instructions or an index definition statement forms a character string too long to fit on one card, an asterisk (\*) in column 80 signifies that the entire next card is a continuation card. As many continuation cards as needed may be used. However, on a continuation card an \* in column 1 does not signify a comment card. In this case, the \* is interpreted as an operator.

As an example of the use of this language, consider the direct digital frame format of the OAO-A2 spacecraft (reference 14).

As is shown in Table 2-4, the set-up table indicates that the modulation code is NRZC. The 64 words of the telemetry frame are each 32 bits long and and are transmitted to the ground at a rate of 50,000 bits per second. Notice that in the FSP specification the "o" preceding the numbers indicates that the

octal number system is to be used. However, the "()" near the end indicates a switch to the binary system. The resulting bit string is the FSP right-justified; i.e., 11100010010000111011010001110110.

| LOCATION | INSTRUCTION                                                         | PARAMETER                                    |

|----------|---------------------------------------------------------------------|----------------------------------------------|

| DD       | FORMAT<br>FSP<br>CODE<br>BIT RATE<br>BITS/WORD<br>WORDS/FRAM<br>END | O7044166435(10)<br>NRZC<br>50000<br>32<br>64 |

Table 2-4. OAO-A2 DIRECT DIGITAL FRAME FORMAT

Table 2-5 indicates a further breakdown of the bit stream into 8-bit elements, where the first 4 elements are the FSP, the 5th element is the TV line number, and the 6th to 256th are the TV intensity elements. Further, notice that the data is least significant bit first and, in the case of the intensity elements, every odd number bit is complemented. Preparing this information for use in a general purpose computer requires a lengthy and complex program. However, as Table 2-6 shows, the telemetry preprocessing language makes it rather simple to describe the reconstruction of this data.

| ELEMENT | BIT<br>12345678                                                                                                                                                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | 11100010                                                                                                                                                                                |

| 2       | 0 1 0 0 0 1 1                                                                                                                                                                           |

| 3       | 10110100                                                                                                                                                                                |

| 4       | 0 1 1 1 0 1 1 0                                                                                                                                                                         |

| 5       | <sup>y</sup> 0 <sup>y</sup> 1 <sup>y</sup> 2 <sup>y</sup> 3 <sup>y</sup> 4 <sup>y</sup> 5 <sup>y</sup> 6 <sup>y</sup> 7                                                                 |

| 6-256   | $i_0 n_1 i_2 n_3 i_4 n_5 i_6 p$                                                                                                                                                         |

| where:  | $y_7y_6y_5y_4y_3y_2y_1y_0$ is a binary TV line number.<br>$n_x = i_x$ complemented.<br>$i_6i_5i_4i_3i_2i_1i_0$ is a binary intensity value.<br>p is the even parity as transmitted bit. |

Table 2-5. DIRECT DIGITAL DATA ELEMENTS

# Table 2-6. DIRECT DIGITAL DATA PROCESSING PROGRAM

| LOCATION  | INSTRUCTION                                                                                                                         | PARAMETER |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------|-----------|

| DD        | FRAME                                                                                                                               |           |

| STAT      | DIMENSION                                                                                                                           | 3         |

| LINE      | DIMENSION                                                                                                                           | 1         |

| ELMT      | DIMENSION                                                                                                                           | 251       |

| STAT      | SYNC (1)                                                                                                                            |           |

| LINE      | WORD, L(2,1,8)                                                                                                                      |           |

| ELMT(1)   | WORD, PET(2,16,1) + WORD(2,15,1) -<br>WORD(2,14,1) + WORD(2,13,1) -<br>WORD(2,12,1) + WORD(2,11,1) -<br>WORD(2,10,1) + WORD(2,9,1)  |           |

| ELMT(2)   | WORD, PET(2,24,1) + WORD(2,23,1) -<br>WORD(2,22,1) + WORD(2,21,1) -<br>WORD(2,20,1) + WORD(2,19,1) -<br>WORD(2,18,1) + WORD(2,17,1) |           |

| ELMT(3)   | WORD, PET(2,32,1) + WORD(2,31,1) -<br>WORD(2,30,1) + WORD(2,29,1) -<br>WORD(2,28,1) + WORD(2,27,1) -<br>WORD(2,26,1) + WORD(2,25,1) |           |

|           | I = 4                                                                                                                               |           |

|           | REPEAT                                                                                                                              | 5,X=3,64  |

| ELMT(I)   | WORD, PET(X,8,1) +WORD(X,7,1) -<br>WORD(X,6,1) + WORD(X,5,1) -<br>WORD(X,4,1) + WORD(X,3,1) -<br>WORD(X,2,1) + WORD(X,1,1)          |           |

| ELMT(I+1) | WORD, PET(X,16,1) +WORD(X,15,1) -<br>WORD(X,14,1) + WORD(X,13,1) -<br>WORD(X,12,1) + WORD(X,11,1) -<br>WORD(X,10,1) + WORD(X,9,1)   |           |

| ELMT(I+2) | WORD, PET(X,24,1) +WORD(X,23,1) -<br>WORD(X,22,1) + WORD(X,21,1) -<br>WORD(X,20,1) + WORD(X,19,1) -<br>WORD(X,18,1) + WORD(X,17,1)  |           |

| ELMT(I+3) | WORD, PET(X,32,1) + WORD(X,31,1) -<br>WORD(X,30,1) + WORD(X,29,1) -<br>WORD(X,28,1) + WORD(X,27,1) -<br>WORD(X,26,1) + WORD(X,25,1) |           |

|           | I = I + 4                                                                                                                           |           |

|           | HALT                                                                                                                                |           |

|           | END                                                                                                                                 |           |

Notice that the SYNC instruction refers to word 1. This causes the system to refer to the DD format BITS/WORD statement and take the first 32 bits of the bit stream. The system then compares these bits with those of the FSP statement and gathers its statistics.

Notice the statement LINE. This statement causes bits 1 to 8 of telemetry word 2 to be reversed and placed in a location (line) reserved for the TV line number.

Next, the intensity elements are dealt with. The first word instruction indicates that this is the even parity bit as transmitted and causes a parity check on this element. The rest of the WORD instructions in the statement cause the uncomplemented intensity element to be found in the appropriate element array location in most significant bit first integer format.

Note that the repeat loop and the index counter are used to save the programmer from the burden of specifying every element. This program would cause an array to be formed which, when output, would have the data storage allocations shown in Table 2-7.

| WORD NUMBER | CONTENT                                           |

|-------------|---------------------------------------------------|

| 1           | Frame Sync Error pattern                          |

| 2           | Number of FSP errors in this frame                |

| 3           | Number of FSP ones in error                       |

| 4           | TV line number in integer form                    |

| 5-256       | Parity error bit and 7-bit intensity values 1-251 |

Table 2-7. OUTPUT DATA FORMAT

The first 3 words generated result from the SYNC instruction. The rest are a result of the WORD instructions.

In summary, the telemetry preprocessing language described and illustrated above is proposed as a more natural means of manipulating telemetry

data streams. This is because the information content of these data streams is described by using the telemetry format specification to extract the data. A further benefit is that the code generated in this manner inherently contains the internal bookkeeping required to extract the data and, thus, is a much simpler code. Hence, it is easier to debug, maintain, and modify as opposed to either machine language coding or FORTRAN coding.

#### C. <u>The Compiler</u>

The telemetry preprocessing language compiler is a set of subroutines written in the APL language which converts a program input data stream into an operations table to be described.

The APL language was chosen for its availability, interpretive implementation, and its powerful set of operators. These features considerably shortened the development and debug times in designing and implementing the compiler and allowed compiler concepts to be explored without excessive concern for internal bookkeeping chores.

Because of the simple nature of the telemetry language, a simple left to right single pass compilation algorithm was able to be used. This algorithm is described in reference 17.

The main body of the compiler is driven by a reserve word list (reference 16) consisting of the instruction set and operators. This list drives the compiler to the appropriate subroutine, which parses the particular instruction being examined. Most of these routines are context sensitive (reference 15) since most of the instructions have a rigid format.

The most interesting of these routines is the arithmetic and logical parser. This routine is driven by two tables and is used to form a reverse Polish string (reference 12) of these expressions. The first of these tables (Table 2-8) is the Input String Precedence Table. This table represents an exhaustive listing of the allowed order of elements in the input string. If an error is detected here, an error message is generated and the entire expression is discarded.

|               |                                                           |                                | HEAD     | OF INP  | UT    |            |          |   |         |

|---------------|-----------------------------------------------------------|--------------------------------|----------|---------|-------|------------|----------|---|---------|

|               | SYMBOL                                                    | CLASS                          |          |         |       |            |          |   |         |

| SYMBOL        |                                                           |                                | relation | logical | .NOT. | arithmetic | variable | ( | )       |

| CLASS         | :                                                         |                                | 1        | 2       | 3     | 4          | 5        | 6 | 7       |

| last          | relation                                                  | 1                              | x        | x       | x     | +/-        |          |   | x       |

| input         | logical                                                   | 2                              | x        | x       |       | x          |          |   | x       |

|               | .NOT.                                                     | 3                              | x        | x       |       | x          |          |   | x       |

|               | arith-<br>metic                                           | 4                              | x        | x       | x     | X          |          |   | x       |

| ļ             | variable                                                  | 5                              |          |         | x     |            | x        | x |         |

|               | (                                                         | 6                              | х        | x       |       | +/-        |          |   |         |

|               | )                                                         | 7                              |          |         |       |            | x        | x |         |

| relat<br>logi | x = not all+/- = plus dion = .NE.cal = .ANIstic = +, -, * | or minus<br>,.EQ.,.<br>).,.OR. |          | E.,.LT. | ,.GT. | <b></b>    |          | L | <b></b> |

## Table 2-8. INPUT STRING PRECEDENCE

Table 2-9, the Parser Decision Table, is used by this routine to assign weight to the elements at both the top of the storage (TOS) string and the head of the input string (HIS).

| Table 2-9. | PARSER | DECISION | TABLE |

|------------|--------|----------|-------|

|------------|--------|----------|-------|

| SYMBOL          | TOS | HIS |

|-----------------|-----|-----|

| logical/relator | 2   | 1   |

| .NOT.           | 4   | 3   |

| arithmetic      | 6   | 5   |

| variable        | 8   | 7   |

| (               | 0   | 9   |

| )               |     | 0   |

Elements are then transferred to the output reverse Polish string according to the simple algorithm:

> HIS>TOS means HIS moved to TOS and drop HIS. HIS = TOS means drop both HIS and TOS. HIS<TOS means TOS moved to output and dropped.

This relatively simple system adequately parses all of the logical and arithmetic expressions found in this language.

The compiler is structured into two major divisions: the format parser and the frame parser. Both of these divisions accept card images as input and produce the above mentioned outputs. They scan the input character stream for illegal conditions and produce error messages when such conditions are found.

The format parser is entered upon recognition of a FORMAT statement. At this time the location field is placed in the format identifier table. During this process, it is checked for multiple entries. If a case of multiple identifiers is encountered, an error message is generated and the generated format table is discarded. Also in the error case, the input data stream is read and ignored until the END statement signifying the end of the format definition is found. The format identifier table is used to set up a linkage between the format table and the frame operations table.

The format parser reads and decodes the statements of the format segment. The output generated by the parser is the format table. This table is checked for multiple entries. If a multiple entry occurs, an error message is generated and the latest parameter replaces the old one. When an END statement is found, the output format table is checked for the presence of all necessary parameters. The necessary parameters are: BITS/WORD, WORDS/FRAM, and FSP. If any one of these is missing, an improper format specification message is generated and the format table is discarded. If all the parameters are present, then the error messages (if any) are output and the format table as shown in Table 2-10 is output. The word number column of the table refers to the nine words which comprise a format table.

| WORD NUMBER | CONTENT                                |

|-------------|----------------------------------------|

| 1           | Identifier                             |

| 2           | Number of bits in the FSP              |

| 3           | Number of bits in a telemetry word     |

| 4           | Number of telemetry words in a frame   |

| 5           | Right most 16 bits of the FSP in octal |

| 6           | Left most 16 bits of the FSP in octal  |

| 7           | Encoded telemetry modulation code      |

| 8           | Telemetry bit rate                     |

| 9           | Encoded tape playback speed            |

Table 2-10. FORMAT OUTPUT TABLE

The codes for the two encoded words are listed in tables 2-11 and 2-12.

The last 3 words of the format output table are optional parameters. If they are absent, a zero is inserted or, in the case of the codes, a seven.

Table 2-11. ENCODED MODULATION CODE VALUES

| INPUT        | ENCODED VALUE |

|--------------|---------------|

| SPPH<br>BIPH | 0 1           |

| RZ<br>NRZM   | 2<br>3        |

| NRZL<br>NRZ  | 4<br>5<br>2   |

| NRZC         | б             |

#### Table 2-12.ENCODED TAPE PLAYBACK SPEEDS

| INPUT | ENCODED VALUE |

|-------|---------------|

| 120   | 1             |

| 60    | 2             |

| 30    | 3             |

| 15    | 4             |

| 71/2  | 5             |

| 33/4  | 6             |

| 17/8  | 7             |

The frame parser scans the input program statements and produces an operations table of the format shown in Table 2-13. The parser is entered upon recognition of a FRAME statement. During this process, the location field is

checked for multiple entries. If such a case is found, an error message is generated and this entire segment of the program is disregarded.

The operation table being produced as output from the frame parser and the format table produced as output from the format parser represent the total output of the compiler. This output is a coded set of operations representing the input statements. The codes used are explained in Table 2-13. The form of this output is suitable for execution by a telemetry preprocessing system. It may be produced as a magnetic tape, a card deck, or directly inserted into the preprocessor depending on the configuration of the installation.

#### Table 2-13. OPERATIONS TABLE

| LOC V1 OP V2 I L A V1 OP V2 R V1 OP V2 V1 OP<br>XXX BXXX O BXXX X XXX BXXX OI BXXX XXXX BXXX O BXXX BXXX | V2<br>BXXX |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|------------|--|--|--|--|

| xxx is the numerical value defined as:                                                                   |            |  |  |  |  |

| - A symbol address if no prefix is present                                                               |            |  |  |  |  |

| - A value as specified by the prefix                                                                     |            |  |  |  |  |

| B is the prefix encoded as:                                                                              |            |  |  |  |  |

| - 1 means the value is a number                                                                          |            |  |  |  |  |

| - 2 means the value is a data address                                                                    |            |  |  |  |  |

| - 3 means the value is a program address                                                                 |            |  |  |  |  |

| 0 is a type 1 operation code meaning:                                                                    |            |  |  |  |  |

| - 1 means add                                                                                            |            |  |  |  |  |

| - 2 means subtract                                                                                       |            |  |  |  |  |

| - 3 means multiply                                                                                       |            |  |  |  |  |

| - 4 means divide                                                                                         |            |  |  |  |  |

| OI is a type 2 operation code meaning:                                                                   |            |  |  |  |  |

| - 1 means add                                                                                            |            |  |  |  |  |

| - 2 means subtract                                                                                       |            |  |  |  |  |

3 means multiply

Table 2-13. OPERATIONS TABLE (Cont)

- 4 means divide

- 5 means equal

- 6 means not equal

- 7 means less than or equal to

- 8 means greater than or equal to

- 9 means less than

- 10 means greater than

- 11 means or

- 12 means and

- 13 means not

- I is the instruction operation code:

- 0 means HALT

- 1 means GO TO

- 2 means REPEAT

- 3 means IF

- 4 means equation

- 5 means location expression

- 6 means SYNC

- 7 means SUB

- 8 means WORD

L is the linkage flag defined by:

- 0 means no linkage

- 1 means + linkage to the next instruction

- 2 means linkage to the next instruction

| · ·                            |                                |

|--------------------------------|--------------------------------|

| A is an address field used as: |                                |

| instruction                    | meaning                        |

| GO TO                          | branch address                 |

| REPEAT                         | loop index address             |

| IF                             | branch address                 |

| equation                       | address of index being defined |

| location expression            | address of old location symbol |

R is either the result of an arithmetic expression or a modifier code as:

| Code | Modifier         |

|------|------------------|

| . 0  | end of modifiers |

| 1    | PET              |

| 2    | POT              |

| 3    | PEA              |

| 4    | POA              |

| 5    | L                |

| 6    | F                |

| 7    | В                |

Table 2-13. OPERATIONS TABLE (Cont)

#### CHAPTER III

## THE TELEMETRY PREPROCESSING SYSTEM

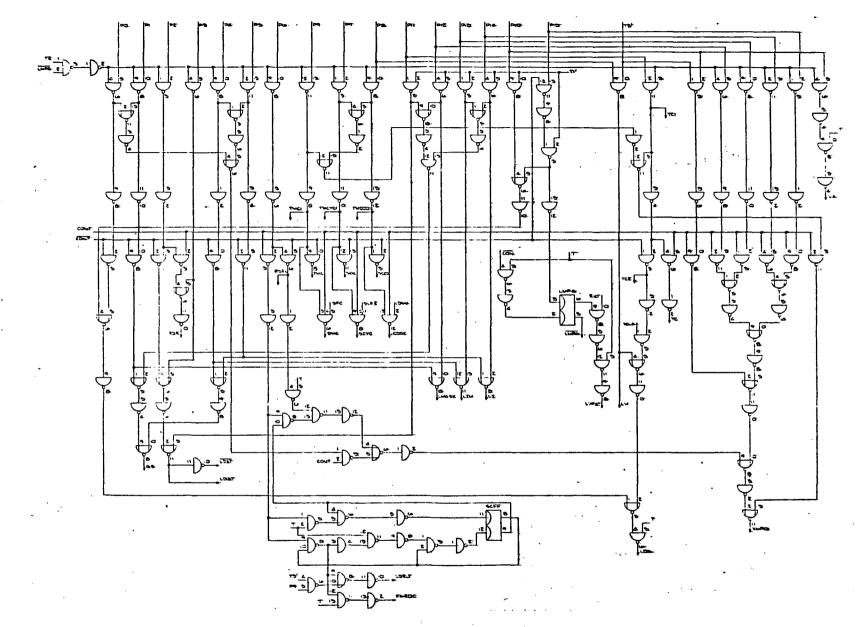

This chapter contains a functional description of a machine designed to process the statements of the telemetry preprocessing language described in Chapter II. The design of the machine is a natural development based upon the format of the language, as will be demonstrated when the system block diagram is derived in a later section. However, the method used to implement this design is a new and powerful approach to system implementation. This method, known as a functional memory, will be described in this chapter. A hardware design of a functional memory device is presented in Appendix A.

The present chapter has nine sections. The first section describes the functional memory device. Next the telemetry preprocessing system block diagram is derived. Sections three to eight describe the six subsystems derived in the block diagram. Finally, section nine presents a summary of this approach, discussing the advantages and disadvantages of the functional memory module and the telemetry preprocessing system.

## A. The Functional Memory Module

The telemetry preprocessing language described in Chapter II will be used to define a hardware system. In using the language to guide the hardware design, many approaches could be taken. The main consideration in choosing an approach is that the system should have a minimum impact on its operating environment. As was pointed out in Chapter I, this environment is highly variable in that it depends on what host computer is chosen and on what telemetry data acquisition system is being used. To accommodate this variability with minimum impact, a microprogrammed approach shows the most promise. Further, when considering the various microprogrammed approaches available and matching them

with the requirements of the preprocessing system, the most promising method is a cellular logic array. This method offers the required flexibility to accommodate the various environments envisioned for the preprocessing system, while simultaneously taking advantage of the lower implementation costs that large scale integration offers.

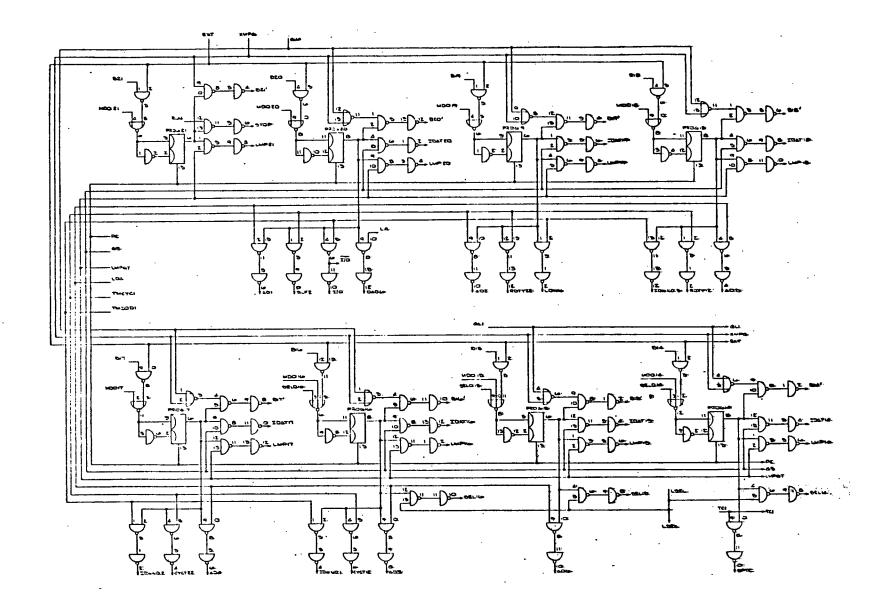

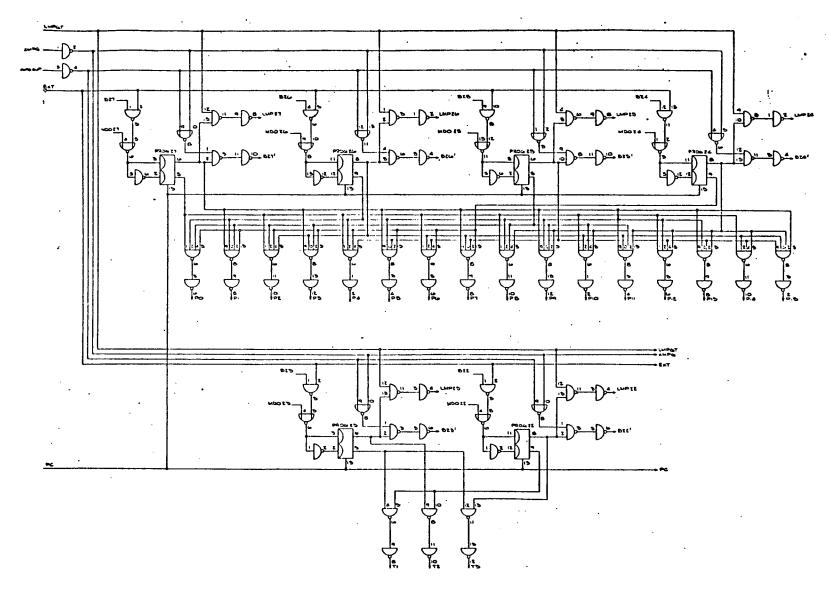

The hardware technique chosen to implement this cellular logic array method consists of a basic building block called a functional memory module. The term functional memory denotes a device used to generate Boolean functions in a memory system. In this device, a cellular memory array is arranged so that each cell of the array can be either an associative memory cell or a conventional memory cell. In order to generate Boolean functions, the value of the input variables is gated into the memory array. The cells of the array are preprogrammed with the value of the variables required for each term of the function. During this phase of the operation (called a search), the value of the input variables is "associated" with the value of the terms and, for every match that is found, a register latch is set. Then the contents of this register are used as a driving signal to read all the addresses of the memory that were selected. The data at these locations is preprogrammed to represent the bit pattern of the function's output when the corresponding input variables are present. In this way a Boolean function can be created by programming a memory device rather than by wiring a combination of logic devices as is normally done.

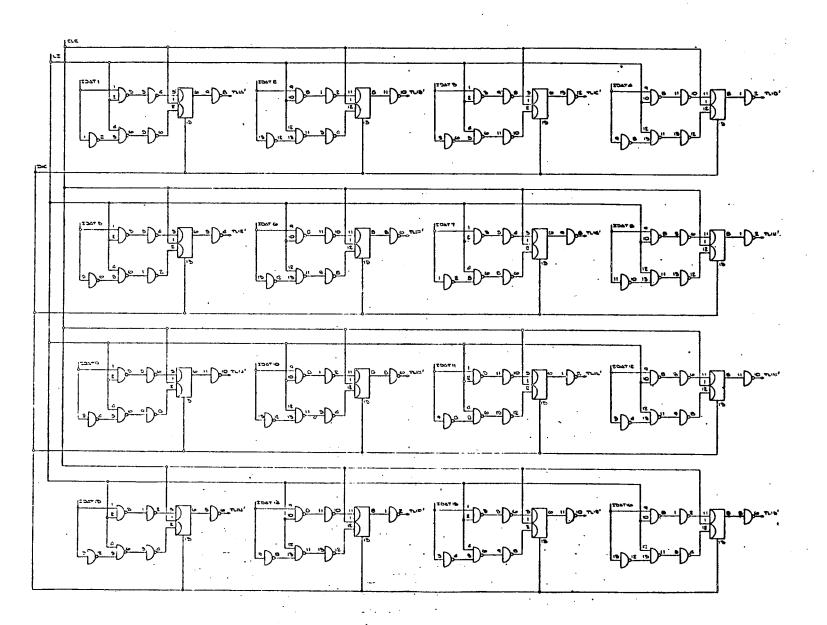

The module that was designed in this work has 16 associative functional words of the type described above, each of which is 20 bits wide. Hence, functions with 16 or less terms and with a total number of input and output bits less than or equal to 20 can be implemented in a single module. As is explained in detail in Appendix A, the terms selected during a search phase can be logically combined prior to setting the register latch. Further by appropriate programming,

აა

use can be made of "don't care terms", and carry terms (from one word to the next) can be generated to reduce the Boolean functions. Thus by using a combination of the above operations, functions with more than 16 terms can be readily reduced to fit in the memory module.

The module is 27 bits wide and contains 64 conventional addresses. The upper 7 bits are not used for function generation, but are operation codes for the 45 microinstructions implemented in the module. These microinstructions are used to clear the various registers of the module, shift data, selectively move data from the module to several other modules, connect other modules to this one, transfer control to another module, and other housekeeping functions.

This module is designed to be suitable for construction using large scale integrated circuit technology. In order to implement this design on a single chip, a constraint must be imposed on the number of input-output pins available. Hence, the number of signals used for communications is restricted. To overcome this restriction during the generation of the various required functions, two powerful techniques were employed.

The first is the method of connecting functional memory modules to the communications bus for the purpose of cooperating in function execution. Since it is the intent of this method of design that most functions be implemented on a small number of modules, an instruction is provided which is capable of forming a connection between 16 modules and the one sending the command at one time. However, this method only leaves three bits available for addressing purposes because of the pin constraint on the modules. Thus, a maximum of 128 modules are available for function generation.

The second technique is the distribution of the control function. A module whose control flip-flop is set is in the control state. In this state, the module is able to control the five communication buses. Hence, it may start instruction

sequences in other modules, initiate functional cycles, transfer data, etc. The most important thing it can do is transfer this control state to all other modules connected to the bus and simultaneously retain control or relinquish it. In this manner, many independent control sequences may be established.

These independent control sequences group the modules under their direction into disjoint sets. When the results of several independent operations have to be merged into a common sequence, the designer who is coding the control sequences must carefully avoid conflicting operations (e.g., separate data transfers to a common destination). Further, when several control sequences are being reduced to one control sequence, only one of the original control states is allowed to be transferred to the new sequence. The others must be terminated by transferring their control state to an empty bus.

B. The Preprocessor Block Diagram

It will be shown how the device described in the previous section can be used to implement a telemetry preprocessing system. This example will demonstrate a very effective usage of LSI technology, since a single chip design is used to implement all the functions of the system.

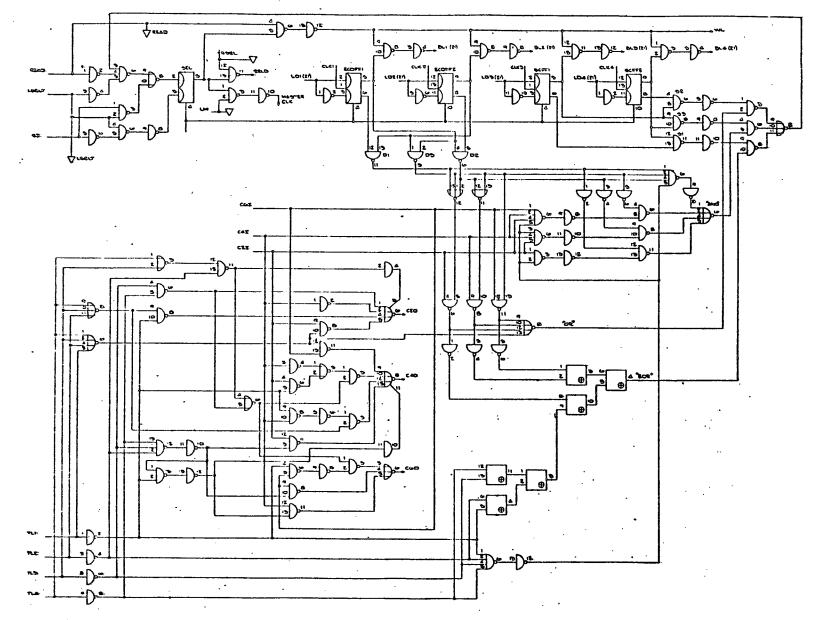

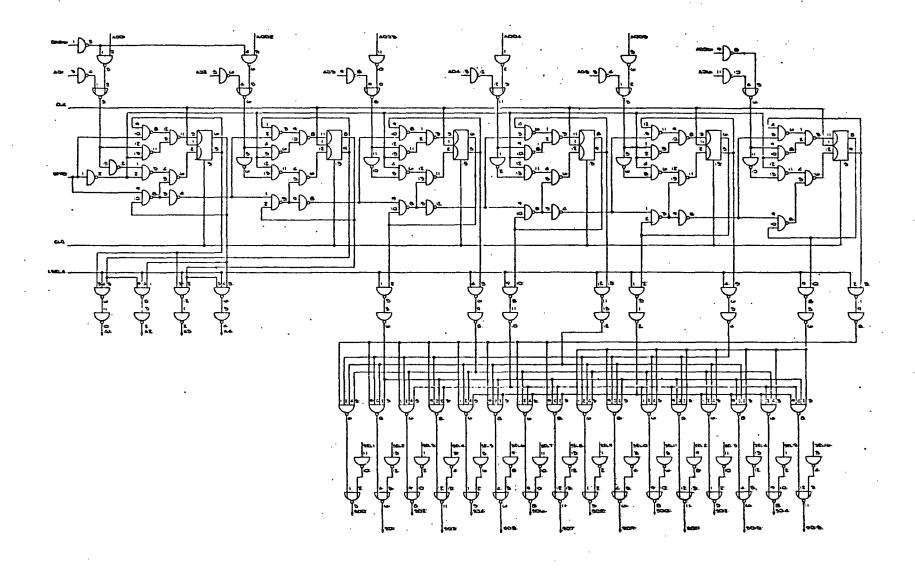

The language described in Chapter II, particularly as shown in Table 2-13, will now be used as a guide to derive the major subsystems which make up the telemetry preprocessor.

The heading of the operation table (Table 2-13 of Chapter II) is repeated here for convenience.

#### LOC V1 OP V2 I L A V1 OP V2 R V1 OP V2 V1 OP V2

This heading identifies the various operation fields that an instruction of the telemetry preprocessing language contains. Upon examination of these fields, desirable simultaneous operations are noted. Obviously, the instruction must be decoded. Further, the four fields under the headings V1 OP V2 can be

evaluated separately at the same time. While this requirement is not strictly necessary, it does serve to reduce the instruction execution time and further it represents a natural environment of the language. Consequently, it will be shown that the combination of direct and indirect implications of this table will lead to a block diagram of the desired preprocessing system.

The direct implications considered thus far show the need for an instruction decoder and for an arithmetic unit consisting of four arithmetic and logical units (ALU's). Another direct implication of the table is contained in the R field. As was described in Chapter II, this field contains several parameters which require that specialized functions be performed (e.g., parity checking, error statistics, etc.). Hence, a special functions unit to implement all those functions which are not inherently handled by an ALU is a characteristic of the language.