# **NASA TECH BRIEF**

## NASA Pasadena Office

NASA Tech Briefs announce new technology derived from the U.S. space program. They are issued to encourage commercial application. Tech Briefs are available on a subscription basis from the National Technical Information Service, Springfield, Virginia 22151. Requests for individual copies or questions relating to the Tech Brief program may be directed to the Technology Utilization Office, NASA, Code KT, Washington, D.C. 20546.

### Improved Capacitance Multiplier Circuit

### The problem:

Capacitance-multiplier circuits create a much larger capacitance than is possible with capacitors of an equivalent physical size. They have many applications in miniature circuits, such as in integrators, sample-and-hold circuits, and phase-locked loops. However, their use has been restricted because of their limited dynamic range. Conventional capacitance-multipliers amplify signal voltage by approximately the same factor as they increase capacitance. The output-voltage rating of amplifiers in the capacitance-multiplier circuit therefore limits the maximum input voltages.

#### The solution:

An improved circuit multiplies capacitance without increasing the overall circuit gain. In addition, the circuit

may be designed to include a lag or a lead/lag transfer function and an independent gain adjustment.

#### How it's done:

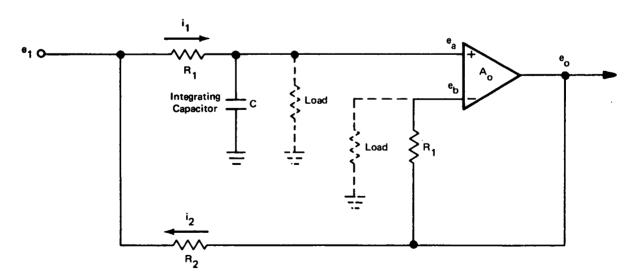

The basic circuit for the improved capacitance-multiplier is shown in Figure 1. An operational amplifier is connected in a differential configuration. One terminal, with an integrating capacitor C, receives the input signal through a resistor. The other terminal is connected to the input signal across two resistors,  $R_1$  and  $R_2$ ; the junction between these is connected to the amplifier output. The effective capacitance  $C_0$  of the circuit is

$$C_0 = C \frac{(R_1 + R_2)}{R_2}$$

Figure 1. Basic Capacitance-Multiplier Circuit

(continued overleaf)

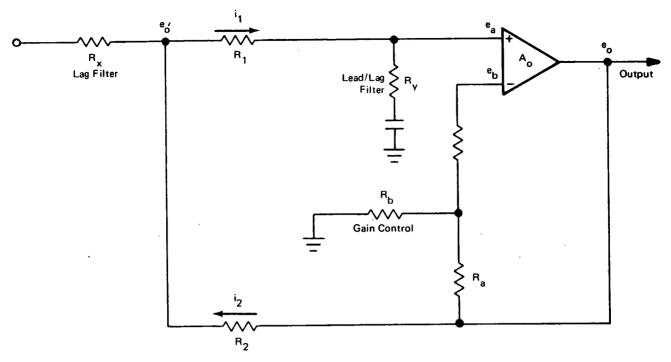

Figure 2. Capacitance-Multiplier Circuit With Additional Features

In Figure 2 the circuit has been modified to include a lag filter  $(R_x)$  and a lead/lag filter  $(R_y)$ . Resistors  $R_a$  and  $R_b$  have been added to allow independent control of the circuit gain. This circuit has been used in a phase-locked loop filter that required a long time constant. It has allowed the capacitance to be increased by a considerable factor of 5 without amplifying the signal voltage.

#### Note:

Requests for further information may be directed to:

Technology Utilization Officer NASA Pasadena Office 4800 Oak Grove Drive Pasadena, California 91103 Reference: TSP74-10162

#### Patent status:

This invention is owned by NASA, and a patent application has been filed. Inquiries concerning non-exclusive or exclusive license for its commercial development should be addressed to:

Patent Counsel NASA Pasadena Office 4800 Oak Grove Drive Pasadena, California 91103

> Source: Arthur J. Kline, Jr., of Motorola, Inc. under contract to NASA Pasadena Office (NPO-11948)