NASA CR-121106 TRW 21083-6001-RU-00

ASDTIC CONTROL

AND

STANDARDIZED INTERFACE CIRCUITS

APPLIED TO

BUCK, PARALLEL AND BUCK-BOOST

DC TO DC POWER CONVERTERS

by A. D. Schoenfeld and Y. Yu

ED INTERFACE CIRCUITS APPLIED TO LILEL AND BUCK-BOOST dc TO dc ERTERS Final Report, (TRW oup) 128 p HC \$9.50 CSCL 10A

TRW SYSTEMS

LE SUBJECT TO COLLEGE

Prepared for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

NASA Lewis Research Center Contract NAS3-14392

# ASDTIC CONTROL AND STANDARDIZED INTERFACE CIRCUITS APPLIED TO BUCK, PARALLEL AND BUCK-BOOST DC TO DC POWER CONVERTERS

by A. D. Schoenfeld and Y. Yu

TRW SYSTEMS

Prepared for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

NASA Lewis Research Center

Contract NAS3-14392

|                              |                                                                                                                                                                                                                                                                                                               |                                          |                                            |                                       | _                  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------|---------------------------------------|--------------------|

| 1                            | . Report No.<br>NASA CR121106                                                                                                                                                                                                                                                                                 | 2. Government Acce                       | ssion No.                                  | 3. Recipient's Catalo<br>TRW21083-600 | <del>-</del>       |

| 4                            | . Title and Subtitle                                                                                                                                                                                                                                                                                          | LATERSTAN CLERK                          |                                            | 5. Report Date<br>February 1973       | 3                  |

|                              | ASDTIC CONTROL AND STANDARDIZE<br>TO BUCK, PARALLEL, AND BUCK-BOO                                                                                                                                                                                                                                             |                                          |                                            | 6. Performing Organ                   |                    |

| 7                            | . Author(s) A. D. Schoenfeld and Y. Yu                                                                                                                                                                                                                                                                        |                                          |                                            | 8. Performing Organi                  | ization Report No. |

| <u>_</u>                     | Profession Committee N                                                                                                                                                                                                                                                                                        |                                          |                                            | 10. Work Unit No.                     |                    |

| "                            | Performing Organization Name and Address TRW Systems Group                                                                                                                                                                                                                                                    |                                          |                                            |                                       |                    |

|                              | Redondo Beach, California 90278  Control and Power Electronics D                                                                                                                                                                                                                                              |                                          |                                            | 11. Contract or Gran<br>NAS3-14392    | t No.              |

| 13. Type of Report and Perio |                                                                                                                                                                                                                                                                                                               |                                          | and Period Covered                         |                                       |                    |

| 12                           | Sponsoring Agency Name and Address National Aeronautics and Space                                                                                                                                                                                                                                             | Administration                           |                                            | FINAL REPORT Aug 1971 thro            | ough Nov 1972      |

|                              | Lewis Research Center<br>Cleveland, Ohio 44135                                                                                                                                                                                                                                                                |                                          | 14. Sponsoring Agenc                       | y Code                                |                    |

| 15.                          | Supplementary Notes                                                                                                                                                                                                                                                                                           |                                          |                                            |                                       |                    |

|                              | Project Manager, Vincent R. Lal<br>NASA Lewis Research Center<br>Cleveland, Ohio 44135                                                                                                                                                                                                                        | 11                                       |                                            |                                       |                    |

| 16.                          | Abstract                                                                                                                                                                                                                                                                                                      |                                          |                                            |                                       |                    |

|                              | Versatile standardized pulse modulation nondissipatively regulated control and control signal processing circuits were applied to three most commonly used dc to dc power converter configurations: the series switching buck-regulator, the pulse modulated parallel inverter, and the buck-boost converter. |                                          |                                            |                                       |                    |

|                              | The unique control concept and the commonality of control functions for all switching regulators have resulted in improved static and dynamic performance and control circuit standardization.                                                                                                                |                                          |                                            |                                       |                    |

|                              | New power-circuit technology was also applied to enhance reliability and to achieve optimum weight and efficiency.                                                                                                                                                                                            |                                          |                                            |                                       |                    |

|                              | Three demonstration models for each of the three types of dc to dc converters were built, tested, and delivered to NASA/LeRC. $\it f$                                                                                                                                                                         |                                          |                                            |                                       |                    |

|                              |                                                                                                                                                                                                                                                                                                               |                                          |                                            |                                       | ***                |

|                              |                                                                                                                                                                                                                                                                                                               |                                          |                                            |                                       |                    |

|                              |                                                                                                                                                                                                                                                                                                               |                                          |                                            |                                       |                    |

|                              |                                                                                                                                                                                                                                                                                                               |                                          |                                            |                                       |                    |

|                              |                                                                                                                                                                                                                                                                                                               |                                          |                                            |                                       |                    |

|                              |                                                                                                                                                                                                                                                                                                               |                                          |                                            |                                       |                    |

|                              |                                                                                                                                                                                                                                                                                                               |                                          |                                            |                                       |                    |

|                              |                                                                                                                                                                                                                                                                                                               |                                          |                                            |                                       |                    |

| 17.                          | Key Words (Suggested by Author(s)) Buck-Boost Converter Series Switching Buck-Regulator Pulse Moidulated Parallel-Invert Standardized Regulation Control                                                                                                                                                      | ter Converter<br>(ASDTIC), and           | 18. Distribution Statement Unclassified-un | •                                     |                    |

|                              | Digital Control Signal Processor DC-DC Converters                                                                                                                                                                                                                                                             | (BCSF)                                   | 1/1/                                       |                                       |                    |

| 19.                          | Security Classif, (of this report) Unclassified                                                                                                                                                                                                                                                               | 20. Security Classif. (c<br>Unclassified | f this page)                               | 21. No. of Pages                      | 22. Price*         |

|                              |                                                                                                                                                                                                                                                                                                               | <u> </u>                                 |                                            | L                                     | L                  |

#### **FOREWORD**

This development project was sponsored under contract NAS3-14392 from the National Aeronautics and Space Administration. For the support and technical interface provided by NASA, we would like to acknowledge Mr. V. R. Lalli of the Lewis Research Center, the NASA Project Manager.

Our appreciation also goes to Dr. F. C. Schwarz, formerly of NASA/LeRC, who laid the foundation for this development and provided technical monitoring at the early contract stage.

Special thanks are due Mr. J. J. Biess of TRW Systems, whose invaluable advice at the beginning of the contract on overall system design concepts contributed significantly to the success of this development.

# TABLE OF CONTENTS

|    |       |                                                                        | Page |

|----|-------|------------------------------------------------------------------------|------|

| ۱. | SUMMA | ARY                                                                    | 1    |

| 2. | INTRO | DDUCTION                                                               | 2    |

| 3. | SWIT  | CHING REGULATOR CONTROL PHILOSOPHY                                     | 6    |

|    | 3.1   | General Switching-Regulator Control System  Block Diagram              | 6    |

|    | 3.2   | Category of Single-Loop Control Methods and Their Inherent Limitations | 8    |

|    | 3.3   | History of Two-Loop Control                                            | 10   |

| 4. | STANI | DARDIZED ANALOG CONTROL SIGNAL PROCESSOR (ACSP)                        | 12   |

|    | 4.1   | Original ASDTIC Implementation                                         | 12   |

|    | 4.2   | ASDTIC Concept Used to Implement a Standardized ACSP                   | 13   |

|    | 4.3   | Inherent Merits of the Standardized ACSP                               | 15   |

| 5. | STAN  | DARDIZED DIGITAL CONTROL SIGNAL PROCESSOR (DCSP)                       | 19   |

| 6. | ASDT  | IC-CONTROLLED POWER CONVERTER DESIGN GUIDELINES                        | 22   |

|    | 6.1   | Power Circuit Design Guidelines                                        | 22   |

|    | 6.2   | Control Circuit Design Guidelines                                      | 24   |

|    | 6.3   | Brassboard Converter Package Design Guidelines                         | 25   |

| 7. | CONV  | ERTER SPECIFICATIONS AND BLOCK DIAGRAMS                                | 26   |

|    | 7.1   | Converter Specifications                                               | 26   |

|    | 7.2   | Converter Block Diagram                                                | 29   |

| 8. | POWE  | R AND CONTROL CIRCUIT DESCRIPTIONS                                     | 33   |

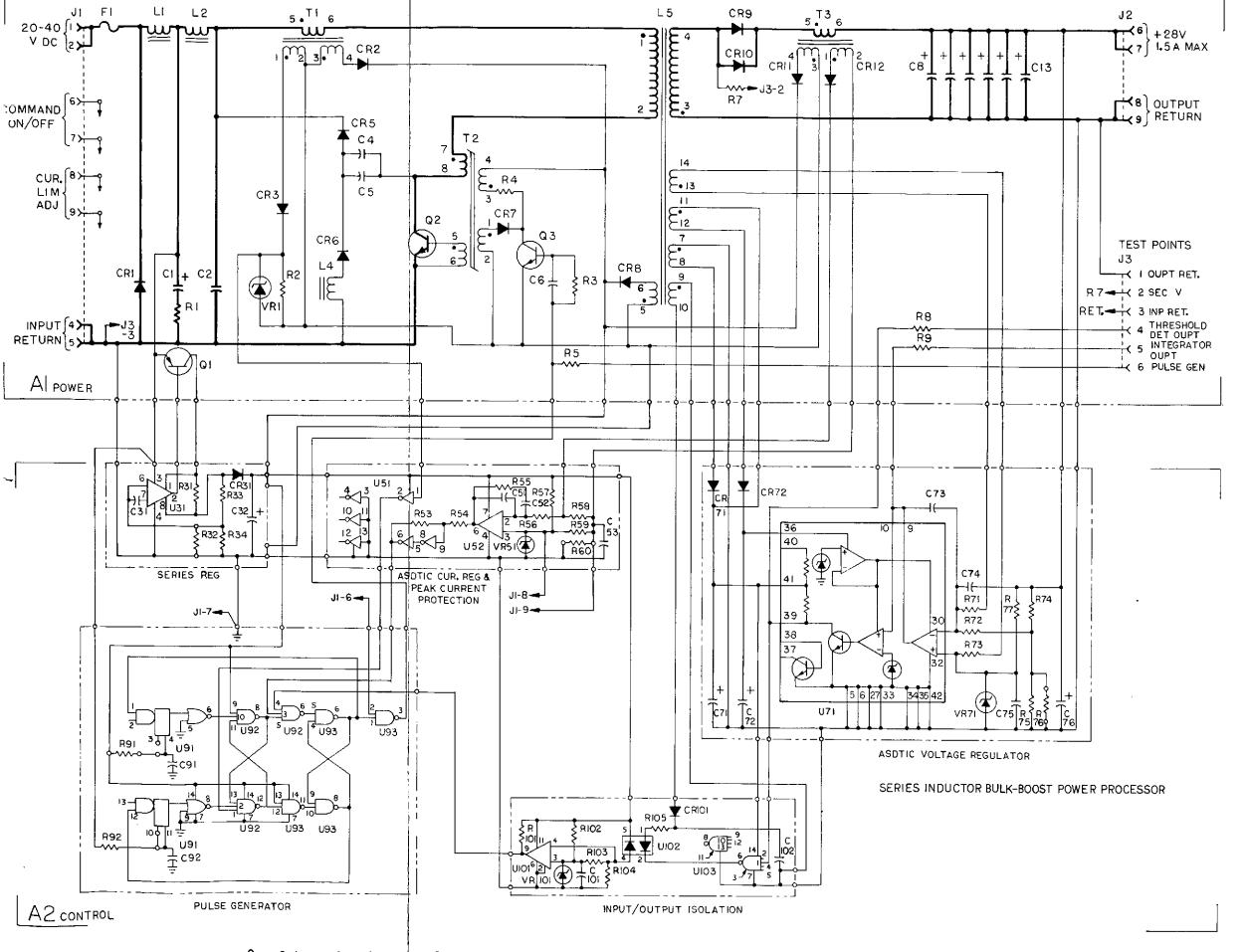

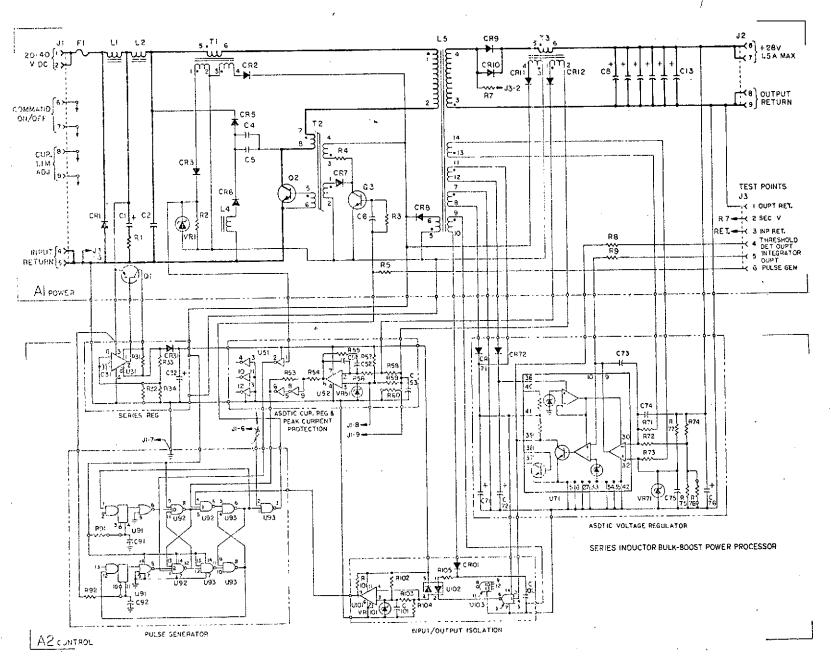

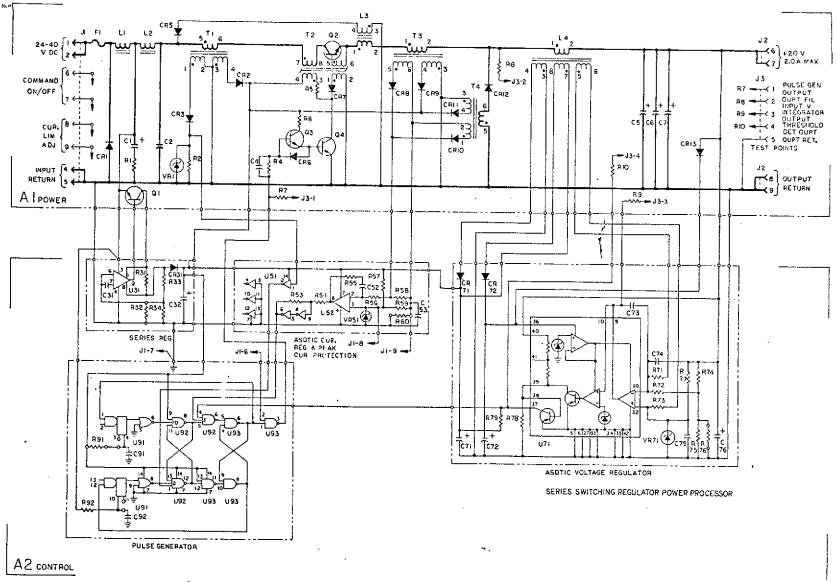

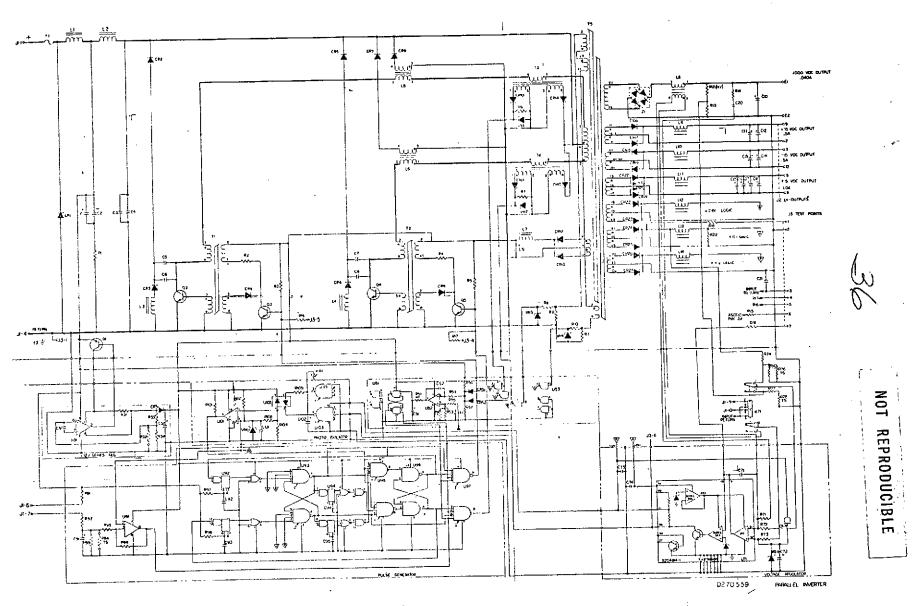

|    | 8.1   | Converter Schematics                                                   | 33   |

|    | 8.2   | Power Circuit Description                                              | 33   |

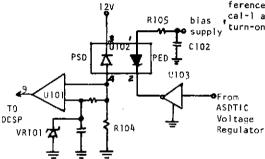

|    | 8.3   | Control Circuit Description                                            | 33   |

Preceding page blank

# TABLE OF CONTENTS (Cont'd)

|     |       |                                                            | Page     |

|-----|-------|------------------------------------------------------------|----------|

| 9.  | CONV  | ERTER FABRICATION                                          | 43       |

|     | 9.1   | General Mechanical Design Features                         | 43       |

|     | 9.2   | Converter Outline, Interface, and Weight                   | 45       |

|     | 9.3   | Converter Assembly and Subassembly                         | 46       |

|     | 9.4   | Test Points                                                | 50       |

| 10. | CONVE | ERTER STEADY-STATE PERFORMANCE                             | 51       |

|     | 10.1  | Output Voltage Regulation                                  | 56       |

|     | 10.2  | Efficiency                                                 | 57       |

|     | 10.3  | Output Current Regulation                                  | 57       |

|     | 10.4  | Output Voltage Ripple                                      | 58       |

|     | 10.5  | Source-Current Ripple                                      | 58       |

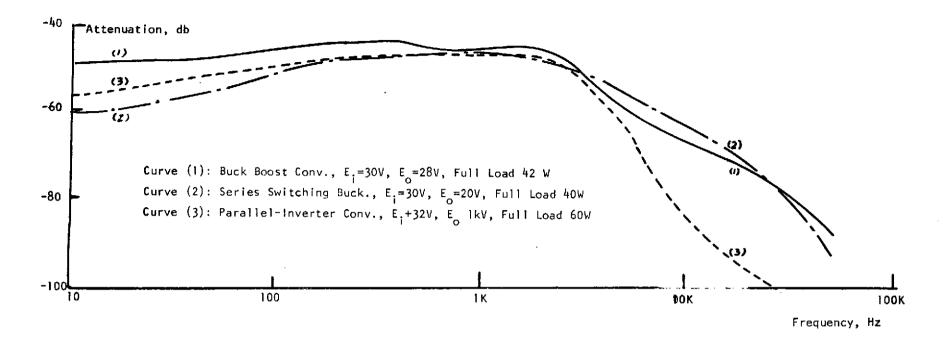

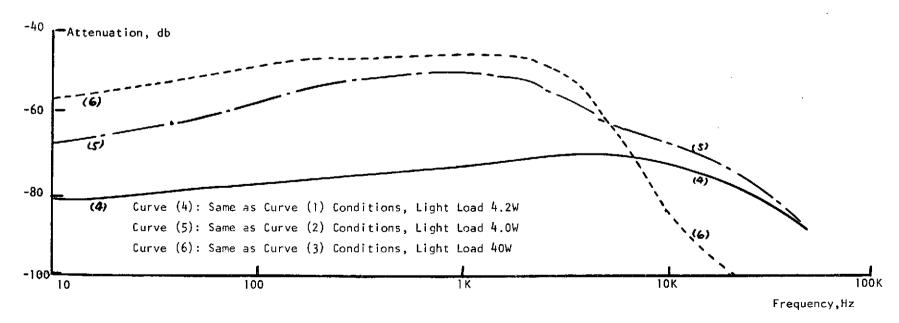

|     | 10.6  | Audio Susceptibility                                       | 59       |

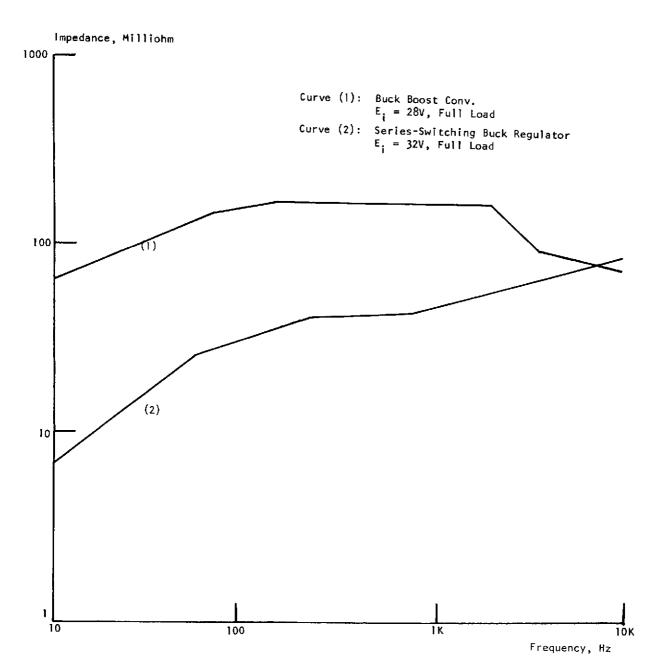

|     | 10.7  | Output Impedance                                           | 61       |

|     | 10.8  | Input/Output Isolation                                     | 63       |

|     | 10.9  | Summary of Comparison Between Performance and Requirements | 63       |

|     | 10.10 | Discussion of Results                                      | 63       |

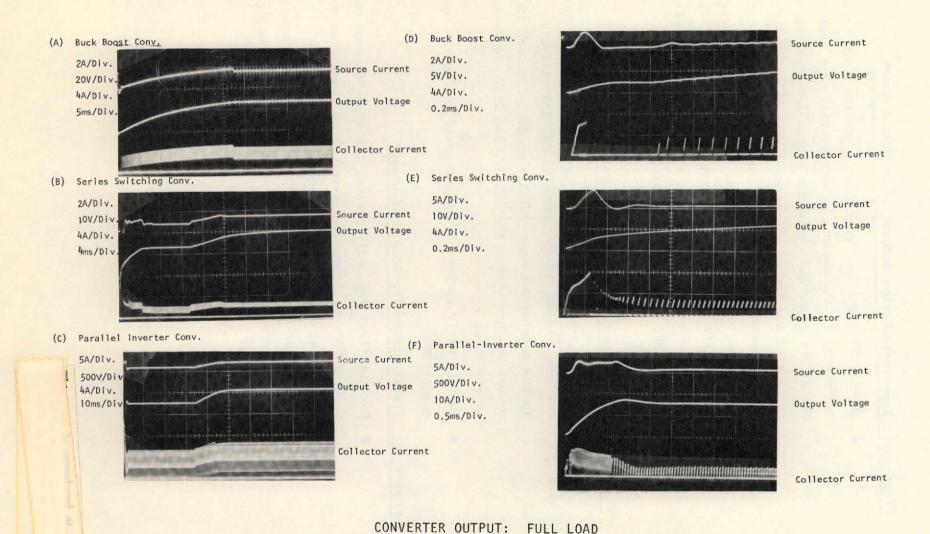

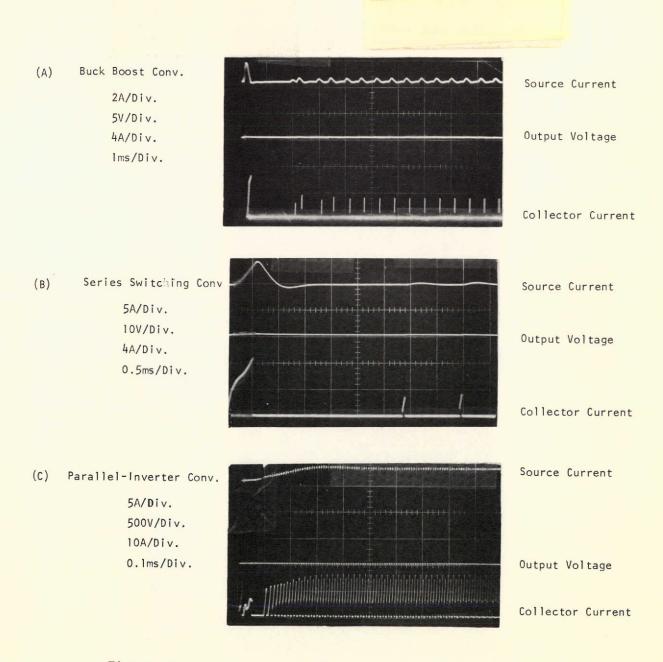

| 11. |       | RTER TRANSIENT PERFORMANCE                                 | 66       |

| 12. |       | MENDATION FOR FUTURE WORK                                  | 77       |

| 13. |       | USIONS                                                     | 77<br>79 |

|     | 13.1  | Power Circuit Technology Improvement                       | 79       |

|     | 13.2  | Control Circuit Standardization                            | 80       |

|     | 13.3  | Performances                                               |          |

|     | -     |                                                            | 80       |

# TABLE OF CONTENTS (Cont'd)

|            |   |                                                                      | Page |

|------------|---|----------------------------------------------------------------------|------|

| APPENDIX   | Α | SMALL SIGNAL ASDTIC OPEN-LOOP FREQUENCY RESPONSE                     | 82   |

| APPENDIX   | В | MINIMUM-WEIGHT TOROID-CORE INDUCTOR DESIGN EQUATIONS                 | 86   |

| APPENDIX   | С | PARALLEL INVERTER TWO-CORE TRANSFÖRMER DESIGN                        | 93   |

| APPENDIX   | D | A TWO-STAGE INPUT FILTER WITH NONDISSIPATIVELY- CONTROLLED DAMPING   | 96   |

| APPENDIX   | E | POWER AND CONTROL CIRCUIT COMPONENTS AND PARAMETERS                  | 103  |

|            |   | El POWER CIRCUIT COMPONENTS AND PARAMETERS                           | 103  |

|            |   | E2 CONTROL CIRCUIT COMPONENTS AND PARAMETERS                         | 104  |

| APPENDIX   | F | DESIGN CRITERIA AND DESCRIPTION OF POWER CIRCUIT FUNCTIONAL BLOCKS   | 105  |

| APPENDIX   | G | DESIGN CRITERIA AND DESCRIPTION OF CONTROL CIRCUIT FUNCTIONAL BLOCKS | 111  |

|            |   | G1 ASDTIC VOLTAGE REGULATOR                                          | 111  |

|            |   | G2 ASDTIC CURRENT REGULATOR                                          | 113  |

|            |   | G3 INPUT/OUTPUT ISOLATION AND SERIES REGULATOR                       | 115  |

| •          |   | G4 DIGITAL CONTROL SIGNAL PROCESSOR (DCSP)                           | 116  |

|            |   | G5 PARALLEL-INVERTER CONVERTER PROTECTION CIRCUIT                    | 121  |

| APPENDIX   | Н | NOMENCLATURES                                                        | 123  |

| REFERENCE: | S |                                                                      | 125  |

## LIST OF FIGURES

|            | •                                                                      | Page |

|------------|------------------------------------------------------------------------|------|

| Figure 1.  | A Generalized Converter Control Circuit Block Diagram                  | . 7  |

| Figure 2.  | Original ASDTIC Implementation                                         | 14   |

| Figure 3.  | Modified ASDTIC Implementation                                         | 14   |

| Figure 4.  | Adaptive Duty-Cycle Control Waveform                                   | 16   |

| Figure 5.  | Standardized Digital Control Signal Processor (DCSP)                   | 20   |

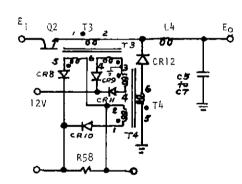

| Figure 6.  | Power Configurations of the Three<br>Demonstration Converter Models    | 27   |

| Figure 7.  | A Common Block Diagram for All Three Converters                        | 30   |

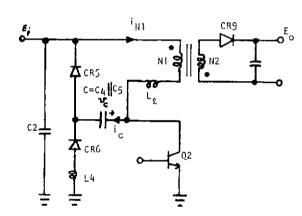

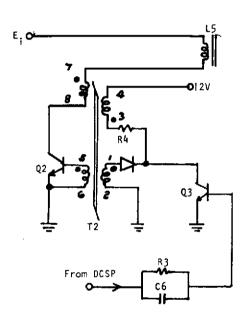

| Figure 8.  | Schematic Diagram of the Buck-Boost Converter                          | . 34 |

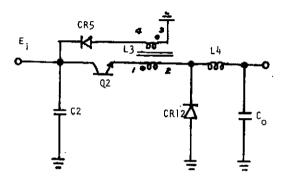

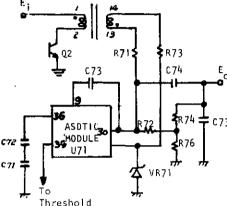

| Figure 9.  | Schematic Diagram of the Series-Switching Buck Regulator               | .35  |

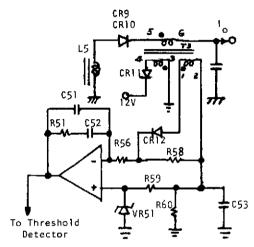

| Figure 10  | . Schematic Diagram of the Pulse-Modulated Parallel-Inverter Converter | . 36 |

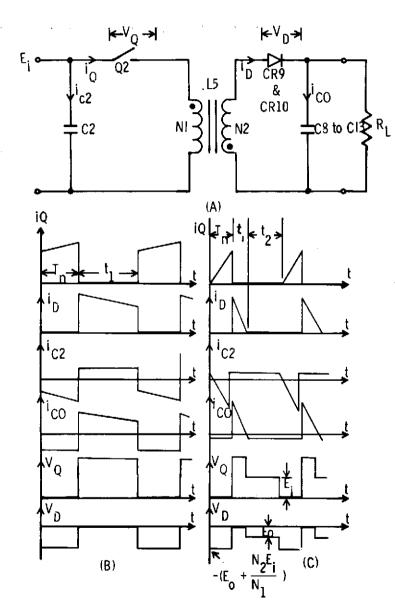

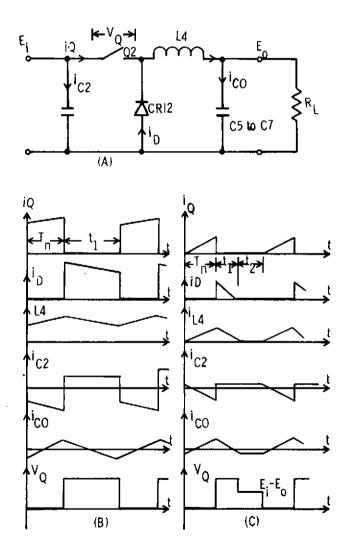

| Figure 11  | . Buck-Boost Converter Configuration and Waveform                      | 37   |

| Figure 12  | . Series Switching Regulator Configuration and Waveform                | 38   |

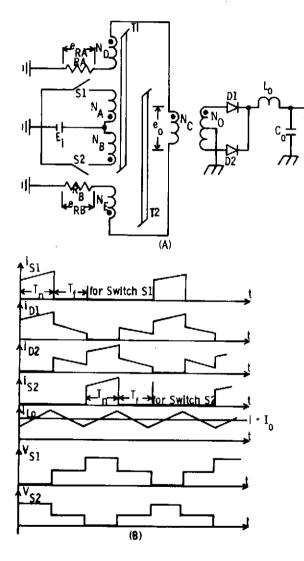

| Figure 13  | . Parallel-Inverter Converter Configuration and Waveform               | 41   |

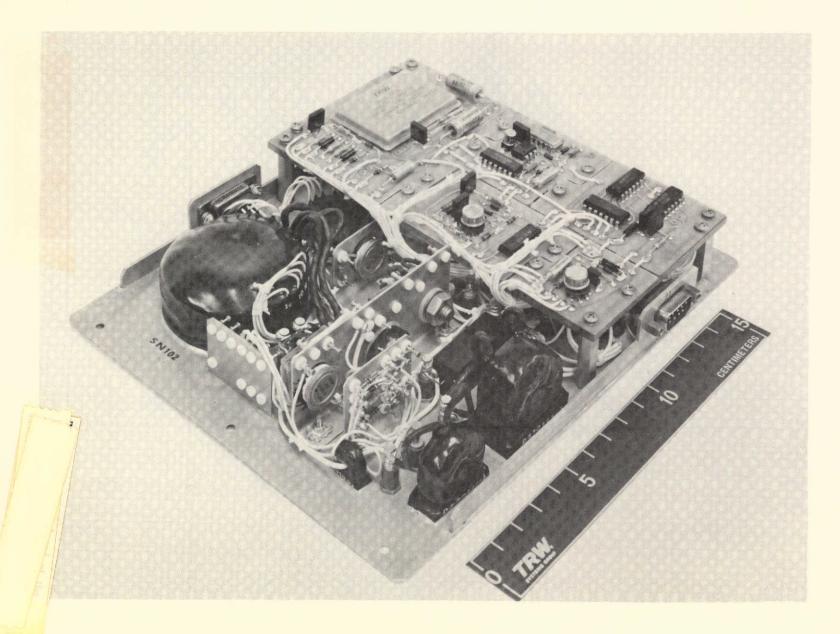

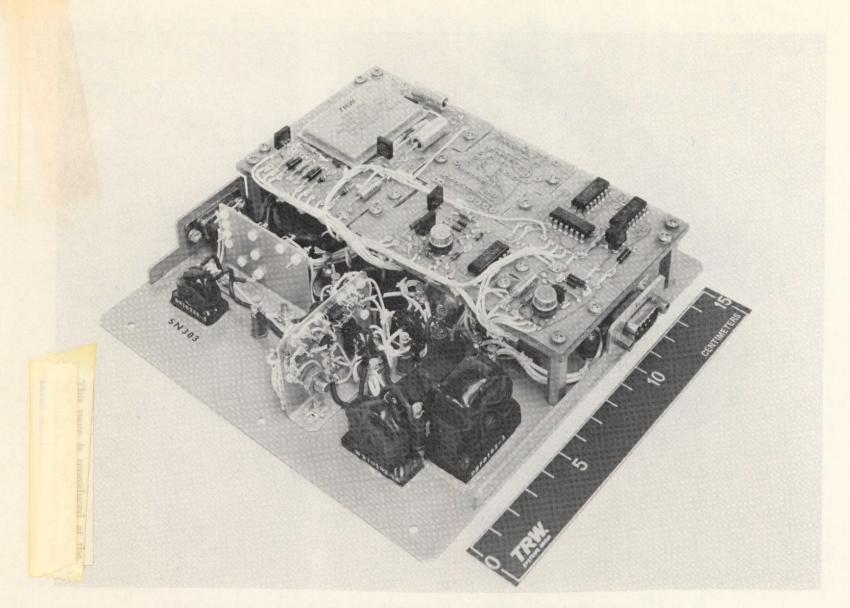

| Figure 14  | . Buck-Boost Converter Brassboard Configuration                        | . 47 |

| Figure 15. | Series Switching Regulator Brassboard Configuration                    | 48   |

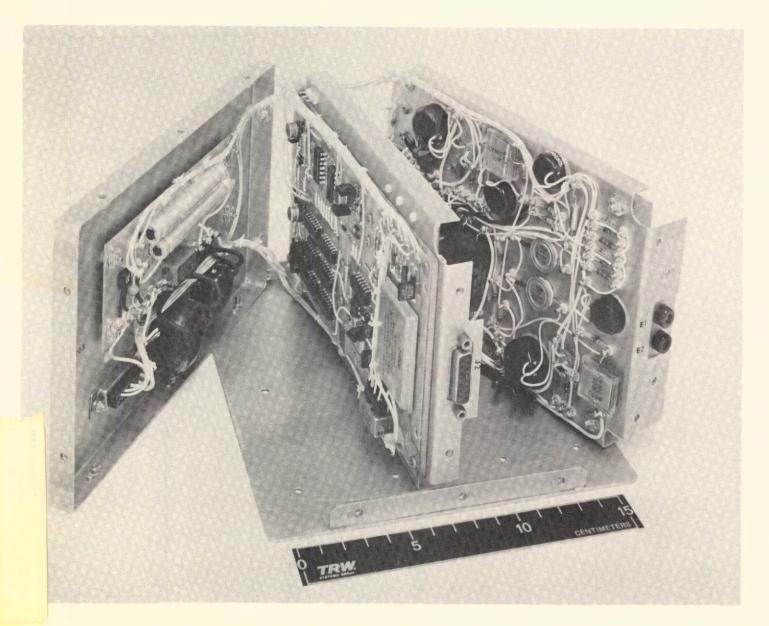

| Figure 16  | Parallel-Inverter Converter Brassboard Configuration                   | 49   |

|            | <u>Page</u>                                                                                                           |

|------------|-----------------------------------------------------------------------------------------------------------------------|

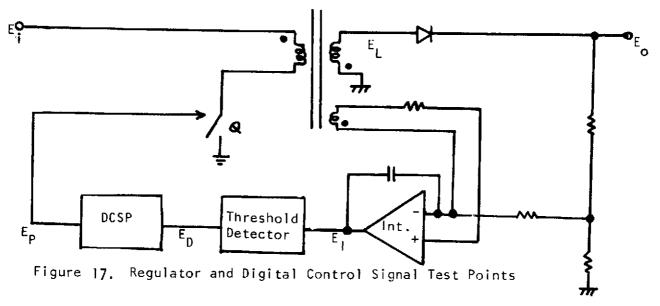

| Figure 17. | Regulator and Digital Control Signal Test Points                                                                      |

| Figure 18. | Measured Audio-Susceptibility Performance 60                                                                          |

| Figure 19. | Measured Output Impedance                                                                                             |

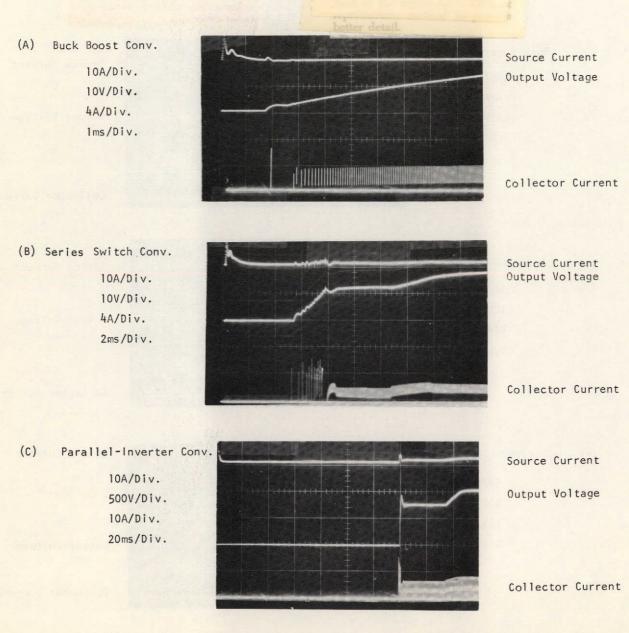

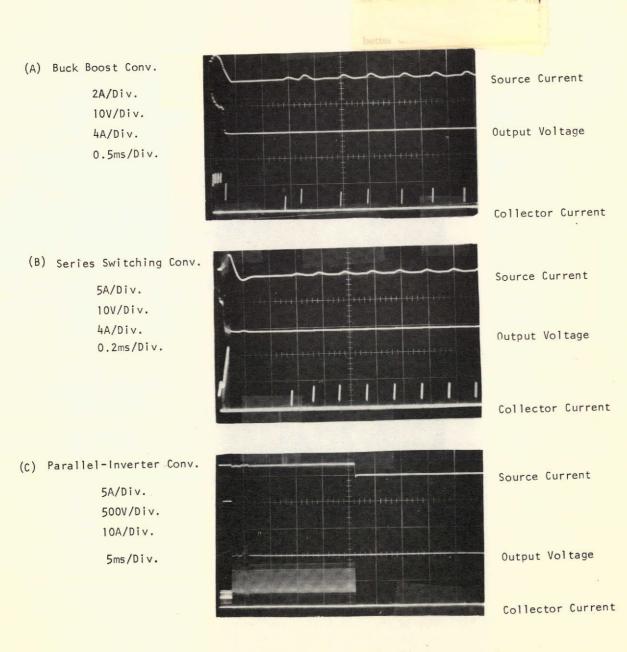

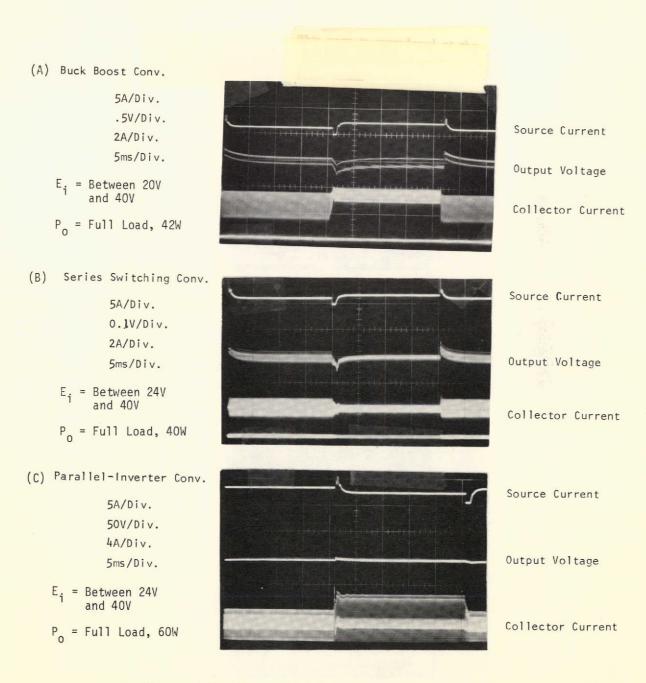

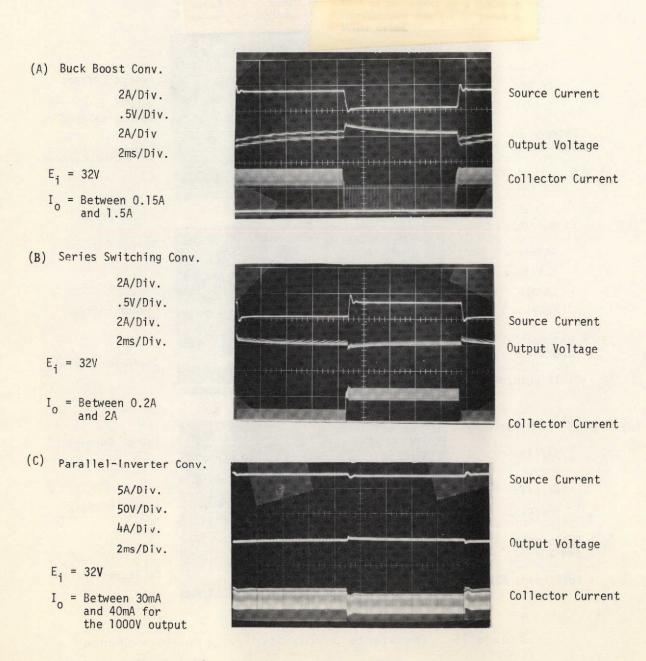

| Figure 20. | Transients During Converter Command On                                                                                |

| Figure 21. | Transients During Converter Command On                                                                                |

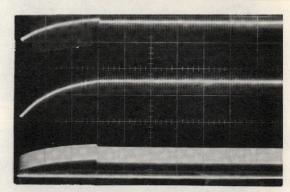

| Figure 22. | Transients During Converter Turn-On By a Step Application of Input Voltage                                            |

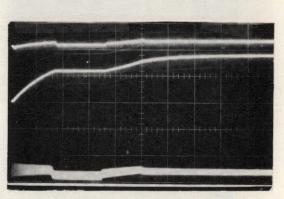

| Figure 23. | Transients During Sudden Converter Output<br>Short Circuit                                                            |

| Figure 24. | Transients During Removal of an Output Short                                                                          |

| Figure 25. | Transients During Step Input Voltage Change                                                                           |

| Figure 26. | Transients During Step Load Change                                                                                    |

| Figure 27. | Block Diagram of ASDTIC-Controlled Series Switching Buck Regulator                                                    |

| Figure 28. | Open-Loop Frequency Response of the ASDTIC Control                                                                    |

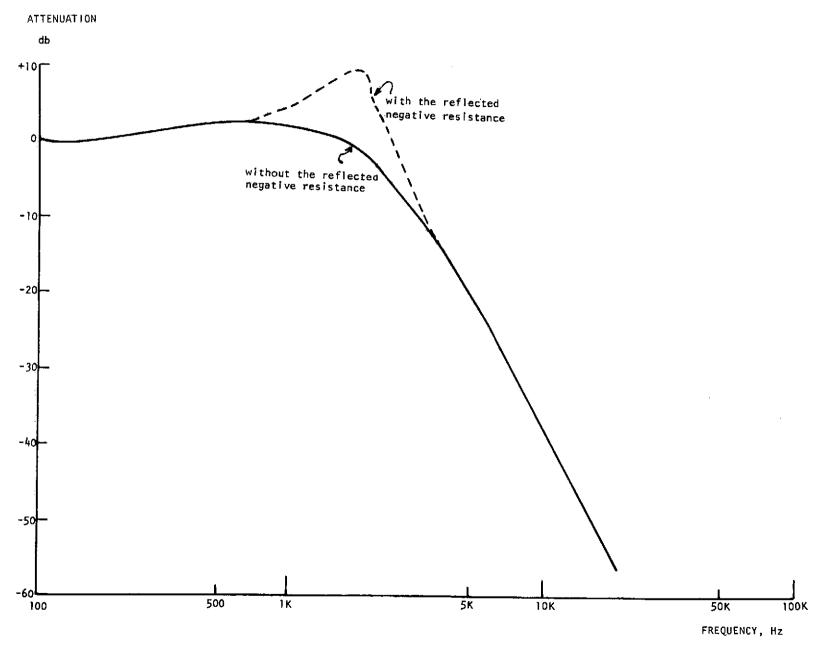

| Figure 29. | Input-Filter Frequency Response With and Without the Reflected Negative Resistance From the Converter Regulator       |

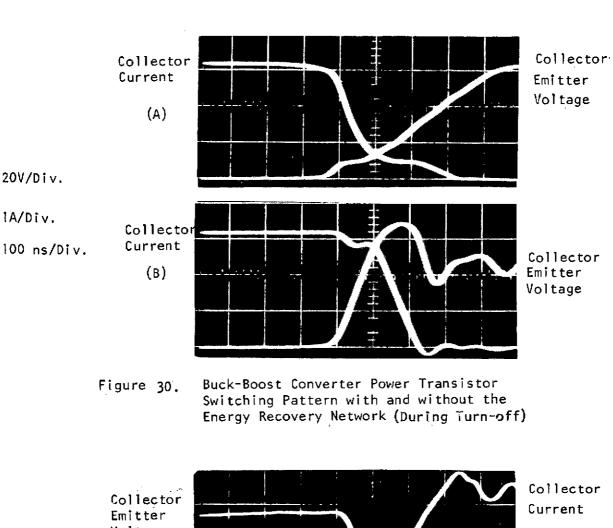

| Figure 30. | Buck-Boost Converter Power Transistor Switching Patterns With and Without the Energy Recovery Network                 |

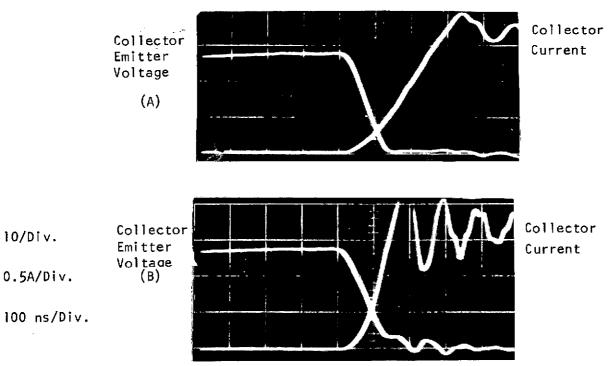

| Figure 31. | Series Switching Buck Regulator Power<br>Transistor Switching Pattern With and<br>Without the Energy Recovery Network |

## LIST OF TABLES

|           |                                                                                   | Page |

|-----------|-----------------------------------------------------------------------------------|------|

| Table 1.  | Summary of DC to DC Convertor Specification                                       | 20   |

|           | Summary of DC to DC Converter Specifications                                      |      |

| Table 2.  | Summary of Power Circuit Functions                                                | 31   |

| Table 3.  | Summary of Control Circuit Functions                                              | 32   |

| Table 4.  | Basic Buck-Boost Power Configuration                                              | 37   |

| Table 5.  | Basic Series Switching Buck Regulator Configuration                               | 39   |

| Table 6.  | Basic Parallel-Inverter Converter Configuration                                   | 41   |

| Table 7.  | Summary of Converter Size, Interface and Weight                                   | . 45 |

| Table 8.  | Steady-State Performance Data for Buck-<br>Boost Converter                        | .52  |

| Table 9.  | Steady-State Performance Data for Series-<br>Switching Buck Regulator             | .53  |

| Table 10. | Steady-State Performance Data for Pulse-<br>Modulated Parallel-Inverter Converter | . 54 |

| Table 11. | Summary of Output Voltage Regulation                                              | .56  |

| Table 12. | Summary of Converter Efficiency at full Load and Room Temperature                 | . 57 |

| Table 13. | Summary of Output Regulation                                                      | .58  |

| Table 14. | Summary of Output Voltage Ripple                                                  | . 58 |

| Table 15. | Requirements Versus Capabilities of Prototype Converters                          | .64  |

| Table 16. | Power Circuit Components and Parameters                                           | 103  |

| Table 17. | Control Circuit Components and Parameters                                         | 104  |

#### SUMMARY

The application of versatile pulse modulation control and control signal processing circuits to the three most commonly used nondissipatively regulated dc to dc converter power circuit configurations: the series switching buck regulator, the pulsewidth modulated parallel inverter, and the buck-boost converter, is discussed in detail.

The Analog Signal to Discrete Time Interval Converter (ASDTIC), conceived originally within NASA, was utilized as the Standardized Analog Control Signal Processor (ACSP) of the three dc to dc converter regulators. The application has resulted in uniformly superior static and dynamic performance for all three types of dc to dc converters.

Commonality of control signal functions for all switching regulators, made possible by the ASDTIC and the newly developed Digital Control Signal Processor (DCSP) circuits, has resulted in control-circuit standardization of the three dc to dc converters.

New power-circuit technology, including component stress control and recovery of power transistor switching loss, was applied to improve reliability and to optimize weight and efficiency.

Three demonstration models for each of the three types of dc to dc converters were built, tested, and delivered to NASA LeRC. The static and dynamic performance of the demonstration models, as well as the power component stress control philosophy implemented in their design, has greatly advanced the state-of-the-art in the design of dc to dc converters.

#### 2. INTRODUCTION

A nondissipatively-regulated dc to dc converter generally achieves efficient voltage transformation and regulation through cyclic operation of its power switch in alternate conduction and nonconduction states. Consequently, the converter control system must be able to converter analog signals derived from the converter output and the control reference, through an A-to-D process, into discrete time intervals in controlling the on-off duty cycle of the power switch. The modulated pulse train derived from the cyclic operation of the power switch is then converted back, through a D-to-A process, to analog form at the converter output by a low-pass filter. Converter output regulation can be achieved through modulation of the power switch on-time  $(T_p)$  and/or off-time  $(T_f)$ .

A pulse modulation for voltage or current regulation of dc to dc converters can be implemented through numerable control circuits proposed and in use today. Generally speaking, they can be categorized into two types of feedback control mechanization: (1) single-loop feedback control and (2) multiple loop feedback control.

The electrical performance of a dc to dc converter depends, to a large extent, on the quality of its control system. Unfortunately, most single-loop approaches suffer from many inherent limitations:

- Due to the presence of a second-order LC filter for output ripple reduction, the utilization of a high gain and wider band width amplifier necessary for good static regulation, high audio-susceptibility reduction, and fast dynamic response is usually accompanied by an increasing risk of dynamic instability induced by line or load changes and variations in component characteristics due to component tolerances, environmental effects, and aging.

- The long time constant associated with the low-pass filter delays the rate of power-switch-modulation adjustment responding to a dynamic line and/or load disturbance, thus compromising the converter dynamic response.

- Due to the many transport delays including the power transistor storage time, additional loop gain is needed to reduce the error, which again leads to an increasing risk of instability.

The stringent demands of space and military programs have served to promote considerable research effort toward the development of an electronic control system capable of mitigating these limitations. One such system was conceived and disclosed through a NASA Internal Research Program.  $^{[1,2]}$  The system utilizes a multiple-loop control mechanization. The controlling element is basically an Analog-Signal-to-Discrete-Time-Interval-Converter (ASDTIC), which was subsequently reduced to a microminiaturized thin film hybrid module.  $^{[3,4]}$  Since then, the ASDTIC module has been employed in different types of nondissipative regulator applications, with the static regulation and dynamic performances approaching those generally exhibited only by dissipative regulators.

The basic objectives of this program were to develop and demonstrate the application of ASDTIC to the three most commonly used dc to dc converter power circuit configurations and to develop the associated control signal processing circuits. The successful performance of this program did lead to the following achievements:

Verify and demonstrate the application of the ASDTIC control system to three distinct and functionally different types of dc to dc converter power circuit configurations:

> Buck-Boost Converter Series Switching Buck-Regulator Pulse Modulated Parallel-Inverter

- Design and development of interface circuitry between the ASDTIC control element and the power circuits of the respective dc to dc converters. These control signal processing circuits should exhibit commonality among different converters to further standardization.

- Accomplishment of superior performance characteristics including superb static and dynamic output characteristics and input current inrush limiting (for the prevention of the collapse of current limited primary power sources).

- Construction, testing, and delivery of one breadboard and two brassboard demonstration models for each of the three types of dc to dc converters.

In accordance with the contract, the program proceeded sequentially through the following phases:

Task 1: Technical Plan

Task 2: Converter Development and Design

Task 3: Converter Fabrication and Test

A Technical Plan summarizing results of Task 1, [5] was used to guide the efforts of Task 2. A report, [6] prepared at the conclusion of Task 2 served as a construction plan for the three regulator converters. One breadboard and two brassboard demonstration models of each converter type were subsequently built and tested to establish their compliance with the technical specifications. The demonstration models were delivered to NASA/LeRC.

This report presents the pertinent information generated in the course of the three tasks performed over a period of one year starting in September 1971.

The presentation starts with a general switching-regulator converter control block diagram presented in Section 3, from which ASDTIC concept is evolved. Using ASDTIC as the standardized Analog Control Signal Processor, a qualitative discussion of ASDTIC then follows in Section 4, which highlights its salient features. To complete the control-circuit standardization, a Digital Control Signal Processor (DCSP) is described in Section 5. The design guidelines for the power and control circuits of the three aforementioned dc to dc converters are presented in Section 6. The three converter block diagrams, featuring the commonality of functional blocks, are given in Section 7, followed by circuit descriptions in Section 8. The construction of the demonstration models of the three types of dc to dc converters is discussed in Section 9. The static and transient performance data are included in Sections 10 and 11, respectively. Recommendation for future tasks is presented in Section 12, and the report ends with conclusions in Section 13.

To anyone working with nondissipatively regulated dc to dc converters, certain design intricacies inevitably make themselves felt throughout the converter design and development stage. While by no means intended as a

final solution to an optimum converter design, the work described herein nevertheless represents a step forward in an effort to bring into sharp focus the converter system design philosophy as well as its functional standardization. Specifically, the effort resulted in the following key achievements:

- (1) The control system implementation through standardized control and interface circuits including both standardized analog and digital-control signal processors. These circuits can be applied to all types of switching regulators using either transistors or SCR's as power switches.

- (2) The successful application of the standardized control system to the three most commonly used dc to dc converters:

(A) the energy-storage buck-boost converter, (B) the series-switching buck regulator, and (C) the pulse-modulated parallel-inverter converter. The static regulation and dynamic performance of each converter were demonstrated to approach the high levels generally exhibited only by dissipative regulators.

- (3) Active power-component stress control under all conceivable transient operations was facilitated by a peak-current sensor and the standardized digital control signal processor, thus enhancing the reliable operation of each converter.

- (4) Optimum weight-efficiency was made possible by: (A) energyrecovery networks to minimize the switching losses in the

power switch, (B) an active magnetics-saturation sensor to

eliminate saturation current in the parallel-inverter transformer, (C) a set of well-conceived power magnetics design

equations, and (D) a proportional power switch base current

drive.

#### SWITCHING REGULATOR CONTROL PHILOSOPHY

As stated in Section 2, the analog signal at the output of a switching-regulator, after comparison with a reference, must be transformed into a digital signal to control the on-off duty cycle of the power switch. The controlled digital pulse train at the power switch output is averaged by an energy storage element, and the analog control signal is derived from the regulated dc output of the dc to dc converter.

The objective of this section is twofold. One is to present a general switching-regulator control system block diagram, from which the various conventional single-loop control methods are categorized, and their relative drawbacks reviewed. The second is to provide a brief history of two-loop control, from which the specific control system used in this program is evolved.

### 3.1 General Switching-Regulator Control System Block Diagram

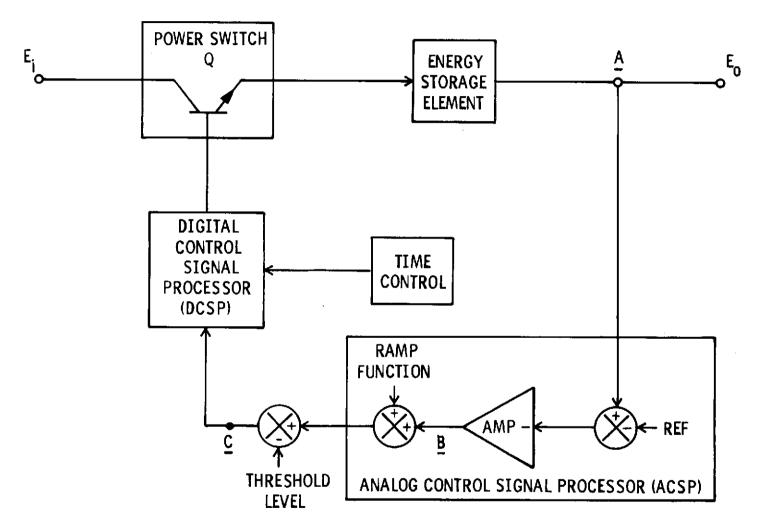

Generally speaking, the A-to-D-to-A process is accomplished, as shown in the block diagram of Figure 1, where a series switching converter is used for illustration purpose

Starting with a signal at the converter output, i.e., point A of Figure 1 and tracing clockwise, the signal is processed by an Analog Control Signal Processor (ACSP) composed of a reference, an error amplifier, and a ramp function generator. After comparing the sensed signal to the reference, the error is amplified by a properly-compensated amplifier, which results in a signal at point B. The amplified output is then either:

(1) combined with, or (2) transformed into, a ramp function. The ramp can be a flux ramp via a magnetic device, or it can be a voltage ramp obtained, for example, by charging a capacitor. When the instantaneous ramp voltage reaches a threshold level, it causes the threshold detector output, point C of Figure 1, to change state. This change of state, in turn, actuates a Digital Control Signal Processor (DCSP) to control the turn-on or the turn-off of the power switch Q. Voltage pulses with an amplitude

Figure 1. A Generalized Converter Control Circuit

Block Diagram

corresponding to the input voltages E, are averaged by the energy storage element, thus closing the loop at its starting point, i.e., point A. This general control concept can be implemented through numerous circuits. The variations are primarily due to the different means through which the ramp function and the threshold level are mechanized.

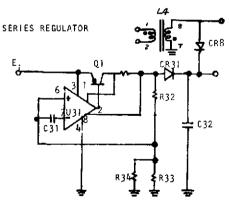

Notice the necessity of a ramp function intersecting a threshold level, for without it the transformation from the analog error at point B to a digital pulse train at point C and at the power switch output is impossible to initiate. Notice, also, the significance of the DCSP. Depending on how it is mechanized, the duty-cycle of the power switch can be controlled by the following combinations of on-time  $T_n$  and off-time  $T_f$ : (1) constant  $T_n$ , variable  $T_f$ , (2) constant  $T_f$ , variable  $T_n$ , (3) constant  $T_f$ , variable  $T_n$  and  $T_f$ , and (4) variable  $T_n$ , variable  $T_n$  and  $T_f$ .

## 3.2 Category of Single-Loop Control Methods and Their Inherent Limitations

Generally speaking, the intersection of the ramp and the threshold level in classical, single feedback loop control is achieved through either one of the three following implementations:

- (1) The ramp (or, the threshold level) at the ACSP output, generated from the amplified error, intersects a fixed threshold level (or, a fixed ramp) to actuate the DCSP [7, 8, 9, 10, 11, 12]

- (2) The ramp or the threshold level is generated as an exclusive function of converter input voltage E<sub>i</sub>. When the ramp is line dependent, the threshold level is fixed. Likewise, a line dependent threshold level is complemented by a fixed ramp. The composite analog error and the ramp are compared to the threshold level to actuate the DCSP [13, 14]

- (3) The ramp is simply the ac ripple of the converter output voltage, E<sub>O</sub>. The error amplifier is essentially unity gain and there are two threshold levels corresponding to the peak and valley of the output ripple. The two threshold levels are combined with the DCSP to form a bistable hysteretic trigger. [15, 16, 17, 18]

Converters of category (1) derive the ramp or the threshold level from the output error exclusively. This method suffers from the following inherent limitations:

- o Due to the presence of a second-order LC energy storage element for output ripple reduction, the utilization of a higher gain and wider bandwidth ACSP amplifier necessary for good static regulation, high audio-susceptibility reduction, and fast dynamic response is usually accompanied by an increasing risk of dynamic instability. The instability can be induced by line or load changes and variations in component characteristics due to component rating tolerances, environmental effects, and aging.

- o The long time constant associated with the low-pass output filter delays the rate of power-switch-modulation adjustment responding to a dynamic line and/or load disturbance, thus compromising the converter dynamic response.

- o Due to the many transport delays including the power transistor storage time for all converters and power transistor on time T for certain types of converters, converter instability becomes imminent when a high gain, large bandwidth control is attempted.

Consequently, the performance for converters of category (1) are inevitably compromised by the stability criterion. These inherent limitations are partially alleviated in converters of category (2). The static and dynamic regulation against line change is improved, in an open-loop fashion, by the line dependent ramp or threshold-level generation. However, static line regulation and converter stability are still degraded by transport delays, and the dynamic performance against load changes is again hampered by the output energy storage element.

Converters of category (3) represent a classical application involving a second-order system with hysteresis. Generally, their dynamic performances are superior to those of categories (1) and (2). The output ripple itself is used as the ramp between two hysteretic levels, within which the dynamics against line and load distrubances are bounded. The simplicity and unconditional stability of the nonlinear control has lent itself to extensive

modeling and analysis [15,17,19,20]. Its known functional subtleties include: (A) the heavy dependence of converter performance on the amount of equivalent series resistance (ESR) in the output filter capacitor, (B) the dc output voltage is a function of the transistor storage time and the output ripple waveform; its average value within the boundary of two hysteretic levels is not precisely controlled, (3) although its operating frequency range can be made small [21], it is still unable to engage in a constant frequency operation, which may be mandatory for applications involving frequency synchronization, and (4) thus far, the control has been applied only to the buck type switching regulators and their equivalent [21].

Up to this juncture, the common denominator of the three control categories discussed above is the utilization of a single feedback loop.

#### 3.3 History of Two-Loop Control

Confronted with such inherent limitations of the single feedback-loop switching regulator, multi feedback-loop regulation-control concepts were advanced. As early as 1964, patents [22,23] were filed in which a second feedback signal was applied to effectively reduce the hysteresis width of the bistable trigger, thus allowing a higher frequency of operation than otherwise feasible. A converter where both dc and ac information were included in its feedback loop by sensing the voltage in front of the filter inductor was reported [24], which resulted in stable operation of the converter over a relatively large change in output-filter capacitance.

Another two-loop regulation control concept was developed in which the ramp is generated by reproducing the current in the output filter inductor [25]. The ramp is then summed with the output of the error amplifier and is used in a closed loop fashion to control the on-off of the power switch through a bistable hysteretic trigger. Basically, this system closely resembles converters of category (3) in principle. The ramp generated from the inductor current is identical in waveform to the ripple across the output filter capacitor having a sufficient ESR. The converter, therefore, possesses the performance advantages of control category (3). However, by using the inductor current to replace the capacitor voltage as the ramp function, the converter operation no longer depends heavily on the capacitor ESR. Furthermore, the use of the additional feedback permits

the design of a high-gain dc loop for precision output voltage regulation. The technique also provides inherent current limiting. However, due to its two-state modulation, it is limited to performing duty cycle control at a constant off time,  $T_{\mathbf{f}}$ .

Still another regulation control concept employing an additional feedback loop was conceived within a NASA Internal Research Program [1, 2]. Here the ramp function is generated by integrating the rectangular ac voltage at the power switch output. A modified version of this concept derives the ramp function by integrating the ac voltage across the filter inductor. The additional ac loop is responsible for improvements in static and dynamic converter performances. In conjunction with a fixed threshold level and the DCSP, the triangular integrator output is used as the ramp function to accomplish power switch duty-cycle control. This concept uses an Analog to Discrete Time Interval Converter (ASDTIC) for the ACSP and threshold detector functional blocks of Figure 1 [3, 4, 26]. The control is flexible, as it can be accomplished through either a constant  $T_n$ , a constant  $T_n$ , a constant  $T_n$ , a line dependent  $T_n$ , or a two-state modulation.

## 4. STANDARDIZED ANALOG CONTROL SIGNAL PROCESSOR (ACSP)

As described in Section 3, the modified ASDTIC derives the necessary ramp function by integrating the voltage across the filter inductor. In this section, the original implementation of the control concept is first described, which then leads to the modified version used in the present program. The inherent merits of ASDTIC are discussed with regard to its dynamic capability and stability, thus laying the foundation for a qualitative understanding of the high performance exhibited by the ASDTIC-controlled dc to dc converter-regulator.

## 4.1 Original ASDTIC Implementation.

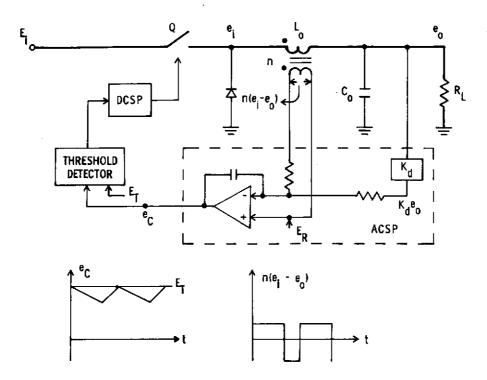

The ASDTIC control concept, originally conceived within NASA, [2] can be represented in Figure 2, where a series-switching converter is utilized for illustration. The filter inductor  $L_o$  is shown to have a dc resistance.  $R_{dc}$ . Voltages  $e_i$  and  $e_o$  at either end of the inductor are divided down by a factor  $K_d$ , and compared with reference  $E_R$ . Thus, the integrator input voltage contains error signals  $e_{dc}$  and  $e_{ac}$ , where  $e_{dc} = K_d e_o - E_R$ , and  $e_{ac} = K_d e_i - E_R$ . The integrator is, in reality, a high gain dc amplifier with capacitor feedback. Consequently,  $e_{dc}$  is extremely small and  $e_{ac}/>>e_{dc}$  holds, leaving the integrator input voltage, x, as that shown in Figure 2. The triangular integrator ac output, serving as the ramp function, is superimposed on the amplified dc error to intersect a threshold level,  $E_T$ . The intersection actuates the DCSP to perform the proper control of the power switch.

This implementation was tested and found to yield excellent regulation against input-voltage variation. However, its performance against load change was hampered by resistance  $R_{dc}$  in the inductor winding. Qualitatively, the detrimental effect of  $R_{dc}$  to load regulation is understandable. Voltages  $e_i$  and  $e_o$  differ by a voltage drop across  $R_{dc}$ , yet both voltages are compared with the same reference  $E_R$  to establish the dc error. The inner loop sensing  $e_i$  is,therefore,interferring with the proper function of the outer loop sensing  $e_o$ , which prevents a precision regulation for  $e_o$ . In the worst-case limit, when only the inner loop exists, the load regulation against a load-current change  $\Delta I_o$  is  $R_{dc}\Delta I_o$ .

## 4.2 ASDTIC Concept Used to Implement a Standardized ACSP.

The modified ASDTIC concept was used in this program for the regulation control of three different types of dc to dc converters. The commonality facilitated the use and demonstrated the practicality of the standardized Analog Control Signal Processor (ACSP).

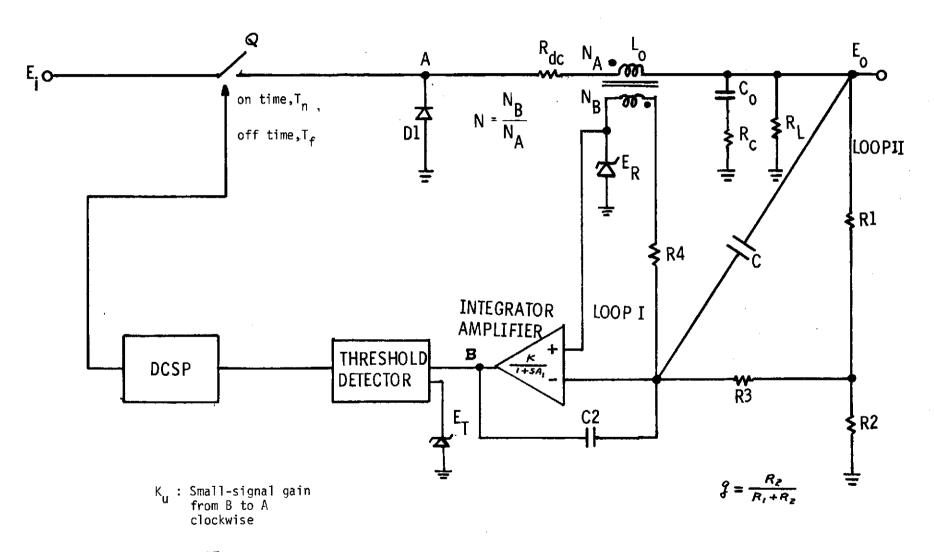

The modified ASDTIC concept is represented in Figure 3. The errorprocessing component of the standardized ACSP is a high-gain error amplifier with a capacitor feedback, i.e., an integrator. Two input signals are applied to the integrator-amplifier through two feedback control loops. The first loop senses the dc output voltage  $e_0$  of the converter, divides it by a factor  $K_d \stackrel{\leq}{=} 1$ , and compares  $K_{d \circ}$  to the amplifier reference  $E_R$ . The difference  $e_{dc} = K_d e_o - E_R$  becomes the dc error input. In conjunction with a threshold-detector level  $\mathbf{E}_{\mathsf{T}}$ , the dc output level of the integratoramplifier is determined by  $e_{\mathrm{dc}}$ . The second loop senses the ac component of  $(e_i - e_j)$  across the filter inductor  $L_i$ , transforms it by a factor  $n \ge 1$ , and feeds  $e_{ac} = n (e_i - e_o)$  differentially to the integrator-amplifier. The rectangular ac voltage e ac, along with the much smaller dc error e dc, are integrated. The integrator triangular output, serving as the ramp function, is superimposed on the amplified dc error to intersect the threshold-level  $E_{\tau}$ . The threshold detector actuates the Digital Control Signal Processor (DCSP) to control the duty cycle of power switch Q.

Notice that, unlike Figure 2 in which the inner loop sensing e handles both dc and ac information, the second loop of Figure 3 processes only the ac information for the purpose of ramp generation. It, therefore, no longer interferes with the dc regulating function of the first loop sensing e. Experimentally, the modified ASDTIC of Figure 3 exhibited an order of magnitude improvement over that of Figure 2 insofar as the load regulation was concerned. As for the regulation against line change, the two systems offer essentially identical performances. Consequently, the system of Figure 3 was utilized in the present program. An additional feature not to be overlooked in the system concept of Figure 3 is its universal adaptability to all switching regulators. For as long as there exists within the regulator an inherent ac waveform suitable for rampfunction generation, the standardized ACSP can be conveniently applied to sense a dc voltage signal at any point in the converter.

Figure 2. Original ASDTIC implementation

Figure 3. Modified ASDT1C Implementation

#### 4.3 Inherent Merits of the Standardized ACSP

As stated previously, the long time constant of the output energy—storage elements and the various transport lags often make it impossible to achieve simultaneously fast transient response, stability, and precistion regulation for a dc to dc converter employing a single-loop control.

In this regard, the two-loop standardized ACSP using the ASDTIC regulation control concept offers the following merits:

(1) Owing to the additional ac loop, the rate of change of the regulator duty cycle in responding to line disturbances is not limited by the relatively slow dc loop.

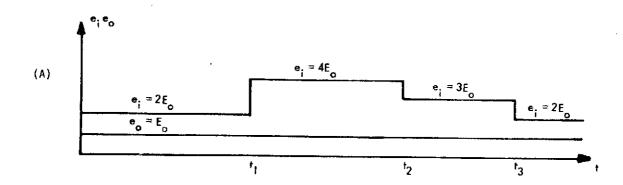

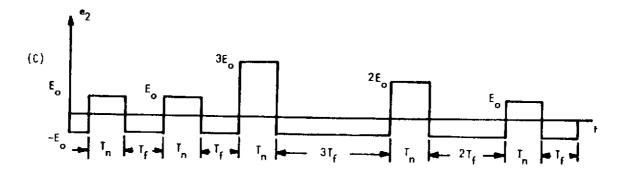

The fast reaction can be verified by considering Figure 4 (A), in which the converter output voltage is regulated at  $e_0 = E_0$ , and sudden changes in input voltage are indicated to occur at  $t_1$ ,  $t_2$ , and  $t_3$ . For clarification, the following conditions are assumed: (A) The DCSP is programmed for a constant  ${}^{11}T_{n}^{-11}$ operation. Each time an increasing ramp intersects the threshold level, it initiates the conduction of the power switch for a fixed time interval  $\boldsymbol{T}_{n}$ , and the output voltage is regulated by controlling  $T_f$ . (B) The time constant of the output filter is much longer than a switching period  $(T_n + T_f)$ , thus maintaining an essentially constant  $\mathbf{E}_{\mathbf{O}}$  within a switching period independent of any step change in e. (C) All components are ideal and lossless. Under these assumptions, the integrator and inductor voltages for Figure 4(A) are shown in Figure 4(B) and Figure 4(C), where  $T_n$  is constant as assumed. During  $T_n$ , the voltage across the inductor is  $e_i - e_0$ , where  $e_i$  is the step waveform of Figure 4(A) and  $e_0 = E_0$  is the regulated output voltage. The slope of the integrator ramp during  $T_n$  is thus proportional to  $e_i$  -  $e_o$ , while during  $T_f$  the slope is constant determined by  $E_0$ .

Between t = 0 and t =  $t_1$ , when  $e_i$  =  $2E_o$ , the steady-state operation results in equal  $T_n$  and  $T_f$ , giving a duty cycle  $T_n/(T_n+T_f)=0.5$ . When  $e_i$  is suddenly increased from  $2E_o$  to  $4E_o$  at  $t_1$ , which for clarity was made to coincide with the start of a new  $T_n$ , the steeper ramp slope proporational to  $3E_o$  during  $T_n$  now causes the ramp amplitude to be three times larger at the

Figure 4. Adaptive Duty-Cycle Control Waveform

end of  $T_n$ . It therefore takes a time interval of  $3T_f$  before the positive ramp can intersect the threshold again to start the next  $T_n$ , giving a new duty cycle of 0.25. Since the required steady-state duty cycle is  $e_0/e_i$  for this converter, the duty cycle becomes 0.5 and 0.25 when  $e_i = 2e_0$  and  $e_i = 4e_0$ , respectively.

The correct duty cycle is adaptively achieved on an instantaneous basis without being delayed by the time constant of the output filter. Similarly, the auto-compensation effect for step input changes at  $t_2$  and  $t_3$  can be easily verified.

# (2) The regulator stability is immune to control component parameter Changes.

The small-signal open-loop frequency response of this standardized ACSP is given in Appendix A. The analytical results show that the converter stability is not effected by changes in the output-filter configuration, the output loading, the error amplifier gain, the threshold level, the integrator time constant, and all other critical control parameters. The immunity reduces significantly the effort normally required in performing the worst-cast stability analysis. Such an analysis would be time consuming, as all parameter changes due to initial tolerances, temperature variation, and aging must be considered collectively. The immunity also provides a highly desirable feature for specific applications such as nuclear-hardening electronics, in which critical component parameters are known to undergo drastic changes.

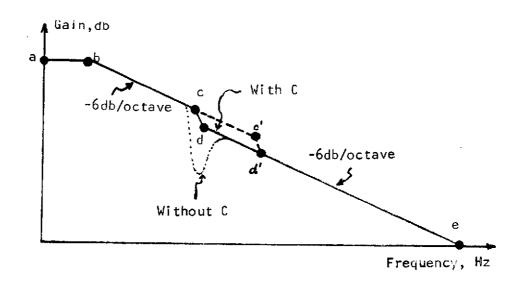

# (3) High gain, wide bandwidth, and precision regulation against line and load changes.

Analysis has also shown that the two-loop standardized ACSP can achieve high gain and stable operation concurrently. The open-loop dc gain is essentially that of the ACSP operational error amplifier, which is in the order of 100 db. The ac loop can be designed to eliminate the roll-off effect of the output filter, thus significantly increasing the bandwidth of the converter operating at a given switching frequency. These combined features are responsible for the good line and load regulation exhibited by the converters controlled by the standardized ACSP.

# (4) Elimination of the detrimental effects of transport lags and other functional subtleties.

Since the auto-compensation between  $T_n$  and  $T_f$  is achieved by sensing the inductor voltage, in which the power-switch storage time is treated as part of on-time,  $T_n$ , the effect of the storage time on the output regulation and line rejection is minimized.

More important, the functional subtlety of certain converter types such as the buck-boost converter and the boost converter has made them most vulnerable to limitations of the single-loop control. The outputs of each of these converters are decoupled from the control-signal path during power-transistor on time  $T_n$ . The consequences are: (1) As far as its feedback control loop sensing the output error is concerned, the entire on-time interval  $T_n$  is equivalent to a transport lag, and (2) A low-frequency characterization of these converters has revealed a novel "positive-zero" term [27] in the frequency response of these converters. The two factors significantly limit the bandwidth of these converters when controlled by a single-loop sensing only the output error.

# (5) <u>Capability of controlling all switching regulators operated in different duty-cycle control modes.</u>

The standardized ACSP is applicable to all switching regulators capable of providing an ac waveform for ramp generation. The ramp at the output of the standardized ACSP can be used in conjunction with a single threshold level or a bistable hysteresis level so that the DCSP can be configured to achieve duty-cycle control using either a constant  $\mathbf{T}_n$ , a constant  $\mathbf{T}_f$ , a variable  $\mathbf{T}_n$  and  $\mathbf{T}_f$  with  $(\mathbf{T}_n+\mathbf{T}_f)$  constant, or a variable  $\mathbf{T}_n$  and  $\mathbf{T}_f$  with  $(\mathbf{T}_n+\mathbf{T}_f)$  also variable.

The aforementioned advantages have been verified by the performance of the three different types of dc to dc converter demonstration models using the standardized ACSP.

The application of the standardized ACSP was complemented by a standardized Digital Control Signal Processor (DCSP), which is discussed in the next section.

## 5. STANDARDIZED DIGITAL CONTROL SIGNAL PROCESSOR (DCSP)

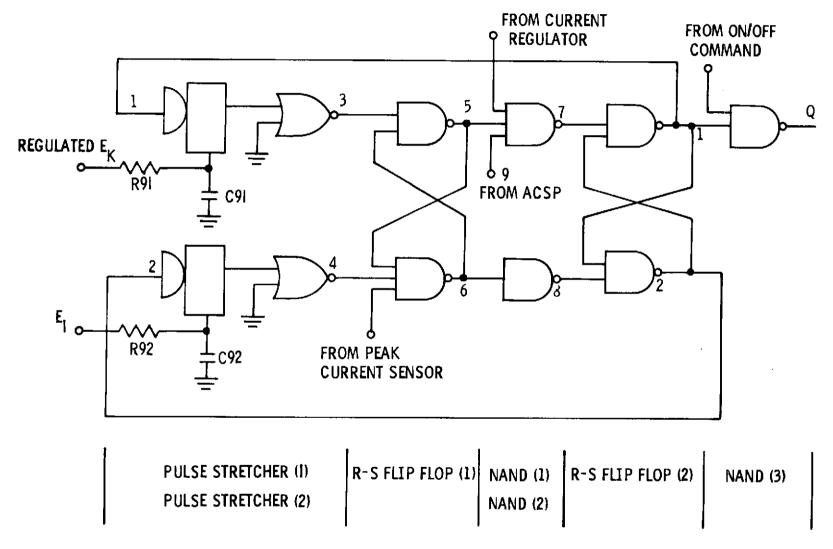

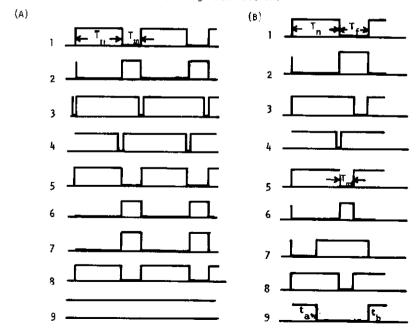

Presented in this section is a novel DCSP which, in conjunction with the standardized ACSP described in Section 4, could form a universal control circuit for all dc to dc converters.

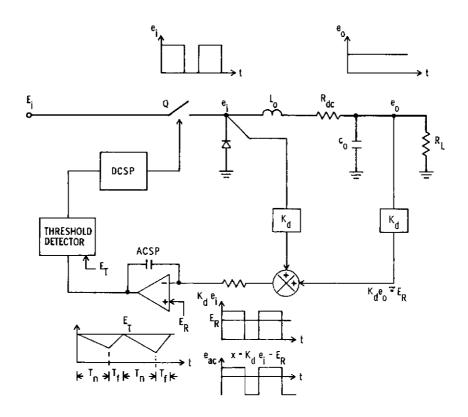

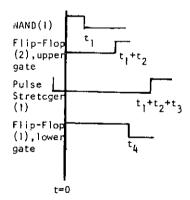

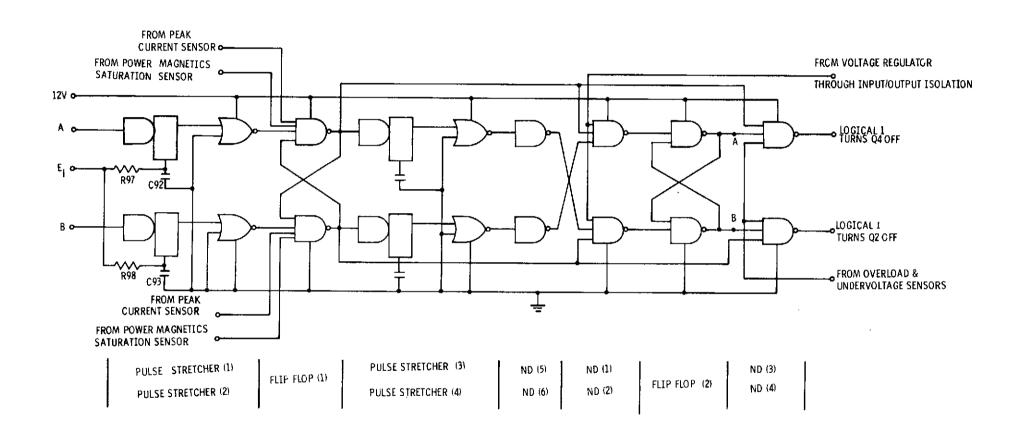

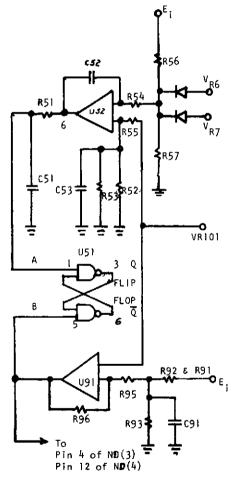

The implementation of the standardized DCSP is shown in Figure 5. It is composed of two pulse stretchers, three NAND gates, and two R-S flipflops. Each pulse stretcher gives an output pulsewidth equal to the sum of the input pulsewidth and a stretched time interval determined by external RC time constants. The digital outputs from flip-flop #2 are fed back directly as inputs to the respective pulse stretcher. The output at point Q is used to control the on-off times of the power switch through a driver whose output is proportional to the current in the power switch.

The DCSP receives the following signals:

- (1) Converter Input Voltage Applied to R92. The converter voltage,  $E_i$ , along with R92, C92, and the internal-threshold level of pulse stretcher (2), determines the on-time interval  $T_n$  for the power switch.

- (2) Regulated Voltage Applied to R91. This voltage, along with R91, C91, and the threshold level inside pulse stretcher (1), determines the minimum off-time  $T_{\rm m}$  during transient operations.

- (3) ACSP and Current Regulator Signals. By applying these regulator signals from the respective threshold detectors to NAND (1), digital signals in series with NAND (2) are not affected. Consequently, on time T<sub>n</sub>, is not altered by the regulator function. The regulating signals applied to NAND (1) therefore serve only to inhibit the turn-on of the power switch by extending the off-time interval beyond the programmed minimum off time, T<sub>m</sub>, to achieve the required duty-cycle control.

- (4) ON-OFF Command Applied to NAND (3). A logical-0 applied to NAND (3) causes its output to be logical-1; this condition corresponds to the off condition for the power switch. A logical-1 applied to NAND (3) allows the DCSP to start the converter at a free-running frequency  $1/(T_n + T_m)$  until the output regulation level is reached.

Figure 5. Standardized Digital Control Signal Processor (DCSP)

(5) Peak-Current Sensor Signal Applied to NAND (2). To limit the peak transient current in the power transistor switch requires that it be turned off before the normal  $T_n$  is timed out. The early termination of  $T_n$  is accomplished by a logical-0 input to R-S flip-flop #1 before the pulse-stretcher (2) output changes state. The signal is obtained from the peak-current sensor.

The new standardized DCSP was developed with a total of only seven parts including three IC's, two capacitors, and two resistors. Furthermore, it is readily adaptable to different methods of duty-cycle control. The DCSP shown here, with converter input voltage E applied to R92, is configured for a converter duty-cycle control based on a constant E.T., i.e., a line-dependent variable on time  $T_n$  and a variable off time  $T_f$ . However, if an externally-generated constant voltage independent of varying E, were applied to R92, the DCSP would then produce a constant  $T_n$  and a variable  $T_f$ . If the feedback signals to the pulse stretchers were not from the outputs of the R-S flip-flop (2), but were from the flip-flop (1), then both  $T_n$  and  $T_{\mathbf{f}}$  would vary, yet the sum of  $T_{\mathbf{n}}$  and  $T_{\mathbf{f}}$  would be kept constant, resulting in constant-frequency operation. An external clock (with a frequency higher than the free-running frequency of the DCSP) applied to flip-flop (1) would result in synchronization of the converter switching frequency with the clock frequency. From these descriptions, the following advantages offered by this standardized DCSP become evident: (1) circuit simplicity, (2) performance of multiple functions and ease of interfacing including control, command, protection and orderly converter startup, (3) flexibility of adapting to various switching regulators, and (4) versatility of the circuit to perform duty-cycle control at either constant  $T_n$ , constant  $T_f$ , constant  $T_n + T_f$ , or a line-dependent  $T_n$ .

#### ASDTIC-CONTROLLED POWER CONVERTER DESIGN GUIDELINES

The objectives of this program were to demonstrate the application of the standardized Analog Control Signal Processor (ACSP) to three most used do to do converter configurations, and to develop a Digital Control Signal Processor (DCSP) which, in conjunction with the ACSP, would be used as a universal control circuit for the regulation and control of any do to do converter.

In the process of the design and development of the demonstration models for the three types of dc to dc converters, new power circuit technology was applied to improve reliability and to optimize weight and efficiency.

To achieve these objectives, certain guidelines were established. The design guidelines used in this program and their rationale are discussed below.

#### 6.1 Power Circuit Design Guidelines

- (1) High Reliability through Component Stress Control. One of the most lagging aspects of power processing technology at present is that of reliability. By this is meant the failure to consistently achieve in operational equipment the reliability that one might anticipate from consideration of the reliability of the components themselves. The reliability of the power converters can be greatly enhanced by controlling the power component stresses during steady state and, more important, during dynamic operations such as step line and/or load changes, sudden output short circuit, and converter starting. The power switch is the single most vulnerable and important power component, whose operation also determines the stress level of essentially all other power components. For this reason, a peak current sensor, which turns off the switch as soon as the switch current exceeds a certain limit, and an energy-recovery network, which minimizes the stresses and the switching loss in the power switch, shall be implemented for each converter [28].

- (2) Optimum Weight Efficiency Tradeoff. Aside from reliability, weight and efficiency are the two other major concerns in the designing of power converters. To achieve a balance between weight and efficiency, the following guidelines were adopted:

- (A) Converters processing large line and load variations should be designed to pass a trapezoidal power-switch current at heavy load, and a triangular current at light load. In other words, the power inductor should be designed to exhibit a critical inductance at an intermediate load.

- (B) The power magnetics contribute to a majority of the total converter weight as well as significant portions of the total converter loss. Their design must be guided by a set of carefully derived design equations. See Appendix B.

- (c) To maintain high efficiency at light load, the utilization of a proportional base-collector current drive is necessary.

- (D) The aforementioned energy-recovery networks should be used to prevent the overlap of high voltage and high current associated with the power switch during its switching intervals, thus improving the efficiency and eliminating the possibility of secondary breakdown.

- (E) High current spikes resulting from saturation of power magnetics of the pulse modulated parallel-inverter should be eliminated through active means. See Appendix C.

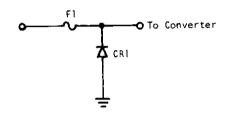

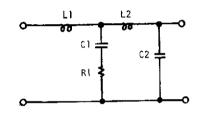

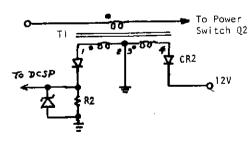

- (3) Source EMI Control without High Resonant Peaking. Due to the audio-frequency line disturbance (i.e., 2.8V rms), the resonant peaking of the input filter must be controlled to prevent (A) the regulation limits of the power processors from being exceeded due to low voltage resonant valleys, and (B) the filter and the converter components from being over-stressed due to peak resonance. The filter must be designed with a large damping factor, yet without a significant efficiency penalty. The two-stage input filter which represents such a design shall be used. The optimum filter design shall be enhanced by an essentially constant switching frequency independent of input line voltage at full-load operation. See Appendix D for detailed filter design.

- (4) <u>Fool-proof Design</u>. The converter must be designed to protect itself against a polarity reversal of the input line and a shorted or open converter output.

#### 6.2 Control Circuit Design Guidelines

- (1) <u>Commonality of Regulation Control-Signal Functions</u>. Adoption of the standardized ACSP to all three converters shall lead to the commonality in performing the basic analog to digital control-signal functions.

- (2) Commonality of Control Circuits. In addition to the ASDTIC control elements in the voltage and current regulators, commonality should be achieved for all the interface and peripheral circuits. The realization of this design goal shall be achieved by the design of a novel Digital Control Signal Processor (DCSP).adaptable to all converters. The DCSP shall accommodate all control signal requirements including (A) interface with the digital signals from ASDTIC control elements, (B) provisions for duty-cycle control with either a constant on time, a constant off time, a line-dependent variable on time, or a constant frequency, (C) processing of the peak current protection of the power switch, (D) response to on/off command and enforcing an orderly converter starting, and (E) synchronization to an external clock frequency, if needed.

- (3) Application of Digital Control Logic. The very nature of pulse modulation control in switching regulators has paced the present trend of increasingly incorporating more digital functions in regulator and control circuits. Realizing that noise immunity is the key to reliable digital IC application in switching regulators, the High Threshold Logic (HTL) family of IC's shall be used in the design of the DCSP. It has a high input threshold, a large logic swing, and a relatively long propagation delay (100 nanoseconds). These characteristics make the HTL most attractive for use where electrical noise rejection is an important consideration, as well as for applications where interfacing with various discrete components is required.

In addition, the following two guidelines were imposed on the digital control circuits: (A) all low-level control signals shall be dc coupled, with no ac or capacitive coupling for digital pulses; thus minimizing noise-generated false triggering, and (B) controlled time intervals wherever possible whall be mechanized using passive parts instead of regenerative one-shots to minimize noise susceptibility.

(4) Meeting Ripple Requirement during Dynamic Operations. To accommodate critical instrumentation and equipment loads aboard the space-craft, it is desirable to limit the converter output voltage excursion to within the ripple specification limits during dynamic input line voltage and load changes. This design goal of containing the converter transient response within the limits of the ripple specification shall be achieved through the integrated design of the power and control circuits.

## 6.3 <u>Brassboard Converter Package Design Guidelines</u>

- (1) <u>Division of Power and Control Circuit Modules</u>. The power and control circuits shall be separated to facilitate the demonstration of control circuit commonality among different converters. Furthermore, this separation shall isolate from the low-level control-circuit boards interference-prone power components and leads carrying high switching currents.

- (2) <u>Division of Control Circuit Board into Submodules</u>. To further standardization and to enhance maintainability, interchangeability, and functional block identification, the control circuit shall be divided into submodules of control and protection functions.

- (3) <u>Separation of High Voltage (HV) and Low Voltage (LV) Circuits</u>. The circuit design should enable a simple division between HV and LV circuits to aid in the packaging of components. Sufficient separation of HV and LV circuits must be established to ensure reliable converter operation. To ensure personnel safety, HV components and terminals shall be totally enclosed.

- (4) <u>Provision of Test Points for Control Signal Tracing</u>. Since one of the program objectives is to introduce to design engineers the ASDTIC control system concept, selected points which permit observation of control signal flow shall be made available through a test connector. The test points shall be protected against external shorts.

#### CONVERTER SPECIFICATIONS AND BLOCK DIAGRAMS

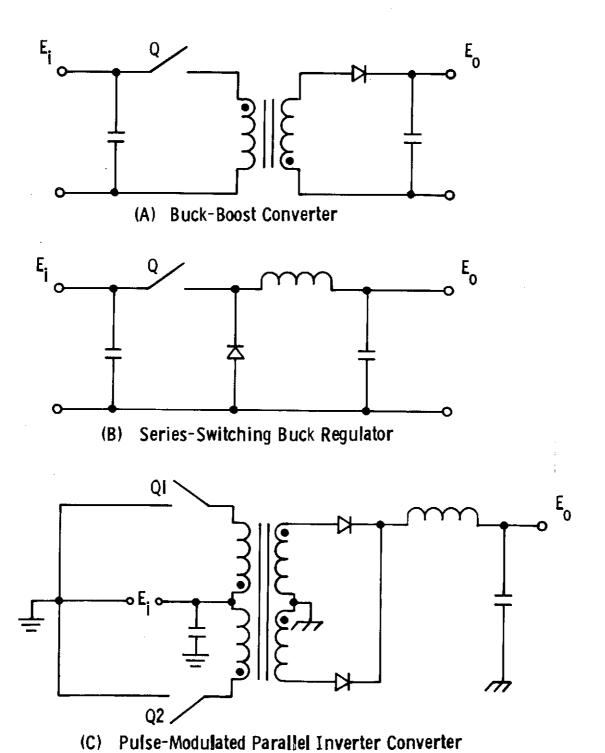

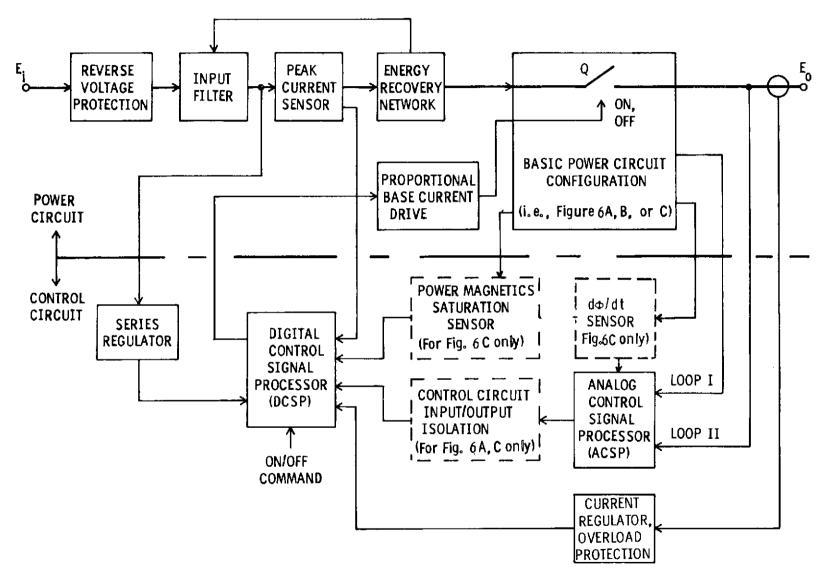

The program provided for the demonstration of standardized control on three types of dc to dc converters. The three most commonly used dc to dc converter configurations, shown in Figure 6, were selected for demonstrating the applicability of the ASDTIC control and of the newly developed interface and peripheral circuits: (1) the buck-boost converter, (2) the series switching buck-regulator, and (3) the pulse modulated parallel-inverter.

The buck-boost converter is usually used for low part count, high efficiency applications. This circuit can achieve voltage transformation with one power switch, and by duty cycle control of the same power switch, output regulation control is also achieved. The buck-boost converter has added advantages in high output voltage applications, as the number of secondary turns in the step-up magnetics can be reduced through the use of power switch on to off time ratios greater than one.

The series switching buck-regulator is the highest efficiency, lowest part count, lightest dc to dc converter. It is used where there are no input to output isolation requirements and where the single output voltage is lower than the lowest input voltage. It is also used as a pre-regulator to square wave parallel inverters where efficiency is less critical or for converter applications having multiple output voltages with wide load variations.

The pulse modulated parallel inverter is used for high efficiency multiple output applications. Power inversion and regulation is accomplished in the same power stage as in the switching-buck regulator, however, there are two power switches required, operating alternatively to effect voltage transformation. On the other hand, the separate LC filters in each output provide a degree of load isolation.

#### 7.1 Converter Specifications

The equipment specifications for the three dc to dc converters are summarized in Table 1. Test data showing compliance by the deliverable converter units with these requirements are provided in Section 10.

Figure 6. Power Configurations of the Three Demonstration Converter Models

Table 1. SUMMARY OF DC TO DC CONVERTER SPECIFICATIONS

| PERFORMANCE PARAMETERS                        | BUCK BOOST<br>CONVERTER       | SERIES SWITCHING BUCK-REGULATOR | G PULSE MODULATED PARALLEL-INVERTER                                                                      | REQUIREMENT OBJECTIVE                                                                                                   |

|-----------------------------------------------|-------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Audio Susceptibility Test                     | 2.8V RMS                      | 2.8V RMS                        | 2.8V RMS                                                                                                 | Demonstrate ASDTIC line<br>rejection                                                                                    |

| Source Current Ripple                         | MIL-STD-461 (N3)              | M1L-STD-461 (N3                 | ) MIL-STD-461 (N3)                                                                                       | Typical Space Requirement                                                                                               |

| Reverse Input Protection                      | yes                           | yes                             | yes                                                                                                      | Fool-proof                                                                                                              |

| Temperature Range                             | -25°C to 85°C                 | -25°C to 85°C                   | -25°C to 85°C                                                                                            | Abnormal space environment                                                                                              |

| Input Voltage Range                           | 20 to 40V                     | 24 to 40V                       | 24 to 40V                                                                                                | Demonstrate wide input<br>voltage range                                                                                 |

| Output Power Rating                           | 42W                           | 40W                             | 60W                                                                                                      | Typical equipment converter                                                                                             |

| Full-Load Efficiency                          | 90%                           | 92%                             | 85%                                                                                                      | Efficient Power Circuit<br>Design                                                                                       |