(NASA-CF-132702) FEASIBILITY STUDY FOR THE N75-30604 IMPLEMENTATION OF NASTRAN ON THE ILLIAC 4 PARALLEL PROCESSOR (McDonnell-Douglas Astronautics Co.) 75 p HC \$4.25 CSCL 20K Unclas G3/39 33997

# FEASIBILITY STUDY FOR THE IMPLEMENTATION OF NASTRAN ON THE ILLIAC IV PARALLEL PROCESSOR

by Eric I. Field

Prepared under Contract No. NAS1-12436 by UNIVERSAL ANALYTICS, INC. 7740 West Manchester Boulevard Playa Del Rey, California 90291

Subcontractor to McDONNELL DOUGLAS ASTRONAUTICS COMPANY Huntington Beach, California 92647

for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

## FOREWORD

This document presents the Final Report on the feasibility study of modifying the NASTRAN (NASA Structural Analysis) computer program to make it execute efficiently utilizing the new ILLIAC IV "parallel" processing computer. This effort was sponsored by the NASTRAN Systems Management Office (NSMO) of the National Aeronautics and Space Administration, Langley Research Center under contract with and monitored by McDonnell Douglas Astronautics Company - West (MDAC).

Universal Analytics, Inc. (UAI) performed this effort under MDAC Contract No. 6-74-489 H, supported by the MDAC prime contract with NASA, No. NAS1-12436. The principal investigation was performed by Dr. E. I. Field with the able technical support of Mr. R. L. Hoesly and Mr. S. E. Johnson and clerical support of Ms. C. Lassen. UAI extends its appreciation to MDAC's Dr. E. L. Stanton for his welcomed critique and to Mr. H. P. Adam for his support and contract monitoring efforts. Also, UAI thanks Mr. J. L. Rogers, Jr. of NSMO for his and the many helpful comments and suggestions offered by the NASA - LRC reviewing team.

This activity, however, could not have succeeded without the over two years of contract support provided UAI by the Advanced Research Projects Agency (ARPA) and supervised by the Defense Nuclear Agency (DNA001-72-C-0108) to develop ILSA, a general purpose finite element structural analysis program for the ILLIAC IV.

This report contains only unclassified material.

## ABSTRACT

The ILLIAC IV, a fourth generation multiprocessor using "parallel" processing hardware concepts, is now operational at Moffett Field, California. Its capability to excell at matrix manipulation, makes the ILLIAC particularly well suited for performing structural analyses using the finite element displacement method. The NASTRAN Systems Management Office (NSMO), therefore, contracted with Universal Analytics, Inc. (UAI) to study the feasibility of modifying the NASTRAN (NASA Structural Analysis) computer program to make effective use of the ILLIAC IV.

This report summarizes the characteristics of the ILLIAC and the ARPANET, a telecommunications network which spans the continent making the ILLIAC accessible to nearly all major industrial centers in the United States. Two distinct approaches are studied: (1) Retaining NASTRAN as it now operates on many of the host computers of the ARPANET to process the input and output while using the ILLIAC only for the major computational tasks, and (2) Installing NASTRAN to operate entirely in the ILLIAC environment.

Though both alternatives offer similar and very significant increases in computational speed over modern third generation processors, the full installation of NASTRAN on the ILLIAC is recommended. Specifications are presented for performing that task with manpower estimates and schedules to correspond.

## TABLE OF CONTENTS

|          | I                                          | Page |

|----------|--------------------------------------------|------|

| FOREWORI | )                                          | i    |

| ABSTRAC  | Γ                                          | ii   |

| LIST OF  | FIGURES AND TABLES                         | v    |

| CHAPTER  | I - INTRODUCTION                           | 1    |

| CHAPTER  | II - ILLIAC IV SYSTEM BACKGROUND           | 4    |

| COM      | PUTER AND NETWORK HARDWARE                 | 9    |

|          | The ARPA Network                           | 10   |

|          | The ILLIAC IV System Hardware              | 12   |

|          | System Hardware Constraints                | 16   |

| SYST     | TEM SOFTWARE                               | 19   |

|          | Process Control Languages                  | 19   |

|          | FTP (File Transfer Protocol)               | 20   |

|          | Application Languages                      | 21   |

|          | Key Language Features                      | 23   |

|          | Language Comparison and Selection Criteria | 26   |

| CHAPTER  | III - DESIGN CRITERIA                      | 28   |

| SYST     | TEMS AND MAINTENANCE                       | 33   |

|          | Compiler Development                       | 33   |

|          | Required Code Modifications                | 33   |

|          | Linkage Editor and Overlays                | 33   |

|          | Operating System Interfaces                | 33   |

|          | Maintenance                                | 34   |

|          | Implementation of Future Capabilities      | 34   |

| EXEC     | CUTIVE                                     | 34   |

|          | Operations Sequence Control                | 35   |

|          | File Allocation                            | 35   |

|          | Checkpoint/Restart                         | 35   |

| UTII     |                                            | 36   |

|          | I/Ø Routines                               | 36   |

|          | String Notation and Matrix Packing         | 36   |

|          | Open Core                                  | 36   |

|          | Miscellaneous Utilities                    | 36   |

| ENGI     | NEERING COMPUTATIONS                       | 37   |

|          | Matrix Operations                          | 37   |

|          | Functional Modules                         | 37   |

| SELE     | CTION CRITERIA                             | 38   |

|          | Level of Effort                            | 38   |

|          | Efficiency                                 | 38   |

|          | User Convenience                           |   | • | • | 42<br>42             |

|----------|--------------------------------------------|---|---|---|----------------------|

| CHAPTER  | IV - DESIGN SPECIFICATIONS                 | • | • | • | 44                   |

| PROC     | GRAM ORGANIZATION                          | • | • | • | 46                   |

| SYSI     | TEM INTERFACE REQUIREMENTS                 | • | • | • | 49                   |

|          | User Interface Requirements                |   |   | - | 49<br>51             |

| EXEC     | CUTIVE SEQUENCE MONITOR                    | • | • | • | 53                   |

|          | Checkpoint/Restart                         | • | • | • | 53<br>54<br>54<br>54 |

| UTIL     |                                            | • | • | • | 55                   |

|          | Input/Output                               | • | • | • | 55<br>56<br>57       |

| ENGI     | INEERING COMPUTATION MODULES               | • | • | • | 59                   |

| SUMP     | 1ARY                                       | • | • | • | 60                   |

| CHAPTER  | V - TASK DEFINITIONS                       | • | • | • | 61                   |

| TASK     | CI - MAINTENANCE AND SUPPORT FACILITIES    | • | • | • | 61                   |

| TASK     | C II - UTILITY ROUTINES                    | • | • | • | 61                   |

|          | General Purpose Input/Output               | • | • | • | 61<br>61<br>62       |

|          | CIII - EXECUTIVE SEQUENCE MONITOR          |   |   |   | 62                   |

| TASK     | C IV - ENGINEERING COMPUTATION ROUTINES    | • |   | • | 62                   |

| TASK     | <b>V - DOCUMENTATION AND DEMONSTRATION</b> | • | • | • | 63                   |

| TASK     | VI - PERFORMANCE EVALUATION                | • | • | • | 63                   |

| TASK     | VII - MODULE OPTIMIZATION                  | • | • | • | 63                   |

| CHAPTER  | VI - ESTIMATED COST AND SCHEDULE           | • | • | • | 64                   |

| CHAPTER  | VII - SUMMARY AND CONCLUSIONS              | • | • | • | 67                   |

| REFERENC | CES                                        | • | • | • | 68                   |

| BIBLIOGE | RAPHY                                      | • | • | • | 69                   |

iv

## LIST OF FIGURES

|      |                                                                 | Page |

|------|-----------------------------------------------------------------|------|

| 2.1. | Structure of the ILLIAC IV Hardware                             | 5    |

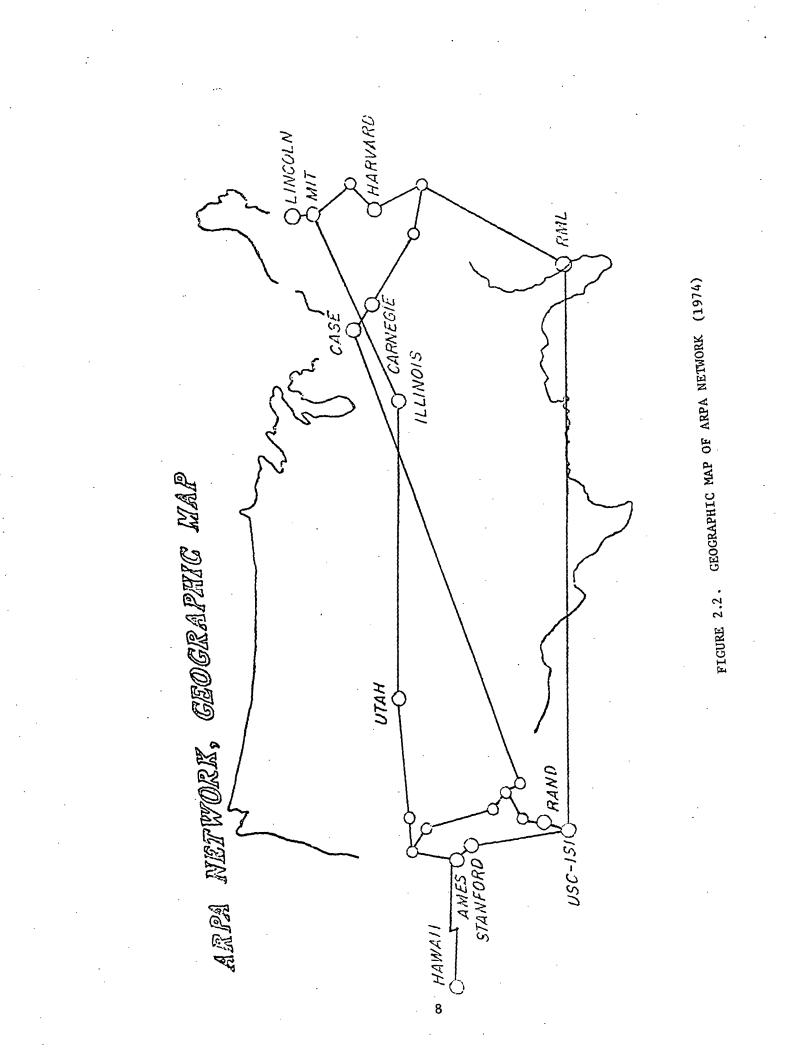

| 2.2. | Geographic Map of ARPA Network (1974)                           | 8    |

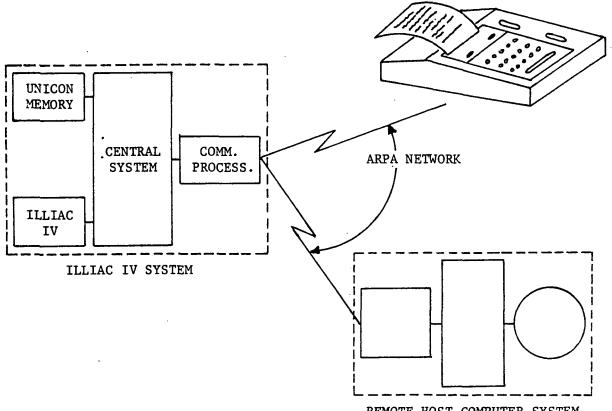

| 2.3. | System Access Via ARPANET                                       | 9    |

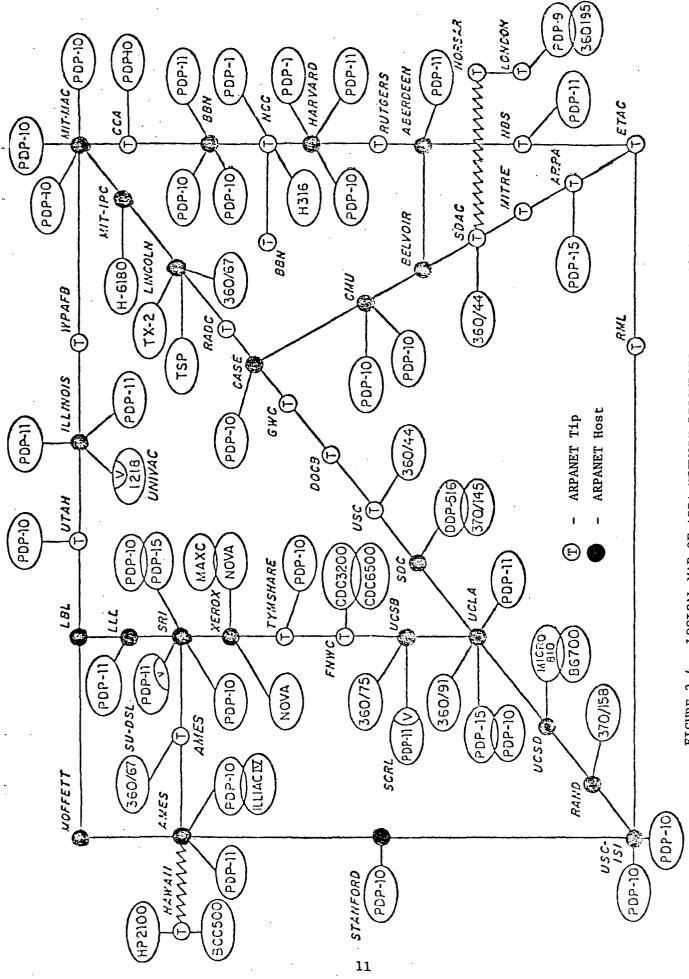

| 2.4. | Logical Map of ARPA Network Resources, January 1974             | 11   |

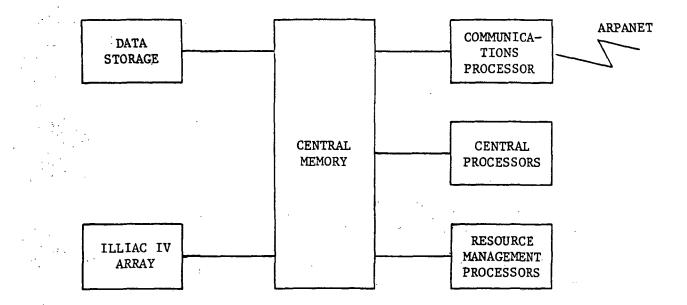

| 2.5. | Major Functional Elements of the System                         | 13   |

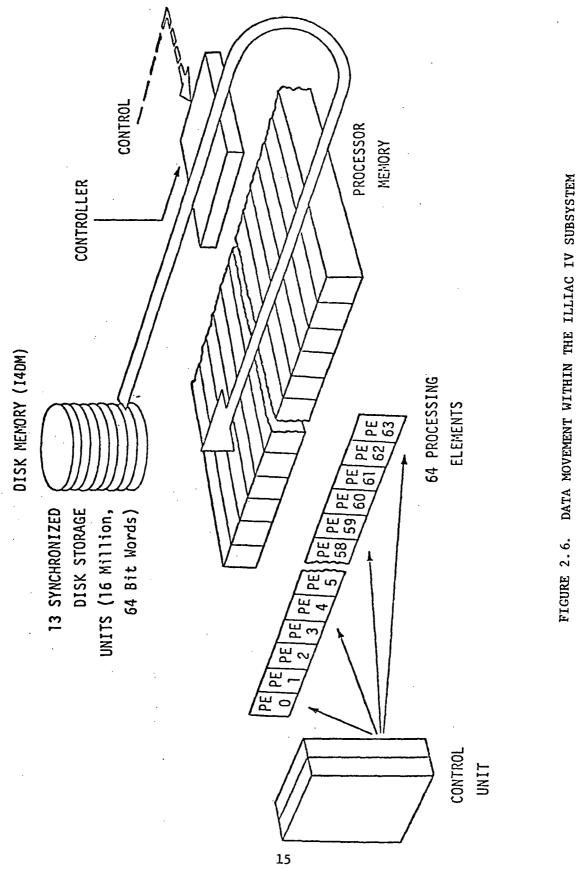

| 2.6. | Data Movement Within the ILLIAC IV Subsystem                    | 15   |

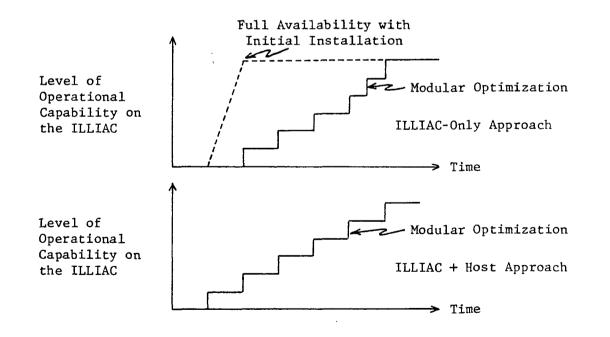

| 3.1. | Time Phasing of Available NASTRAN Capability on the ILLIAC $$ . | 29   |

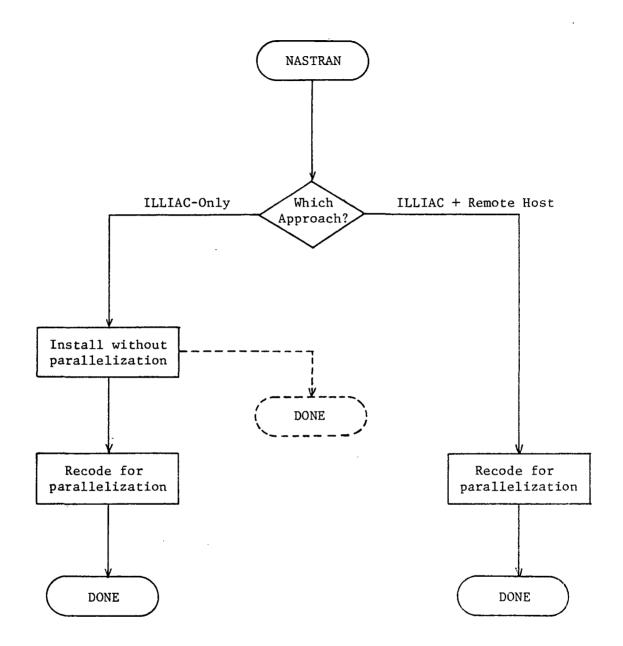

| 3.2. | Installation Approach Decision Tree                             | 39   |

| 4.1. | NASTRAN Program Organization on the ILLIAC                      | 47   |

| 4.2. | User Interface to ILLIAC NASTRAN                                | 50   |

## LIST OF TABLES

| 2.1. | Comparative Speeds of Execution                 | 6  |

|------|-------------------------------------------------|----|

| 2.2. | Comparison of Language Features                 | 24 |

| 3.1. | NASTRAN Module Characteristics                  | 30 |

| 3.2. | NASTRAN Installation Estimate for the ILLIAC IV | 32 |

| 3.3. | Timing Comparison                               | 40 |

| 3.4. | Timing Constants (Microseconds)                 | 41 |

| 3.5. | Performance Improvement Ratios                  | 41 |

| 6.1. | Detail Man-Time and Schedule Estimates          | 65 |

### CHAPTER I

## INTRODUCTION

The potential speed and power of fourth generation computers is being realized. Though the electronics of computers has now reached a capacity to perform up to 1.6 millions of arithmetic operations per second, the architecture of existing computers has organized these electronics using multiprocessing techniques to overlap these operations and effectively magnify this capacity to provide up to 50 million such operations per second. These fourth generation computers, such as the ILLIAC IV with "parallel" processing and the STAR with "pipeline" processing, also introduce the opportunity and necessity for developing new computational algorithms. This opportunity has stimulated government agencies, such as NASA, to initiate studies to determine the feasibility of performing finite element structural analyses with these new fourth generation multiporcessor computers.

In response to this challenge, the NASTRAN Systems Management Office of NASA (NSMO) requested an evaluation study to determine the requirements for possibly installing NASTRAN (NASA Structural Analysis), a finite element analysis program, on the ILLIAC parallel processor. In response to this request, Universal Analytics, Inc. (UAI) has prepared the following feasibility study under the direction of McDonnell Douglas Astronautics Company - West (MDAC). This study has been performed under MDAC Subcontract No. 6-74-489 H as part of MDAC's overall contract NAS1-12436 with the NASA Langley Research Center.

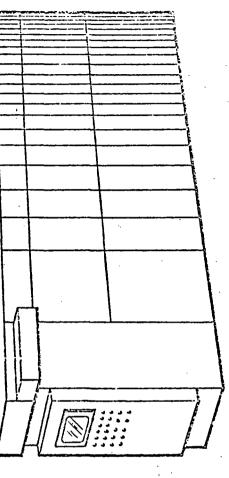

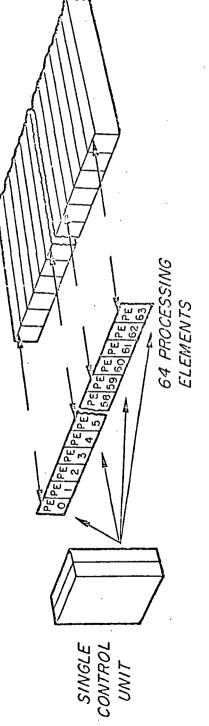

The ILLIAC, which is now operational at Ames Research Center, Moffett Field, California, provides unique capabilities already demonstrated [Ref. 1,2,3,5] to be eminently suited to the matrix processing constructs of finite element analyses as currently executed with the NASTRAN program. The multiprocessing capabilities of the ILLIAC are achieved using parallel processing hardware concepts. Very simply, the ILLIAC physically consists of 64 small computers or Processing Elements (PE) directed by a single Control Unit (CU): (1) to execute a common instruction sequence (2) simultaneously (3) on independent sets of data. These three key phrases contain the essense of parallel processing. In other terms, related to structural analysis, these 64 PEs can be used to compute 64 beam element stiffness matrices <u>simultaneously</u> or they can be programmed to decompose a matrix by <u>simultaneously</u> processing 64 columns of that matrix. Thus, with parallel processing, the ILLIAC can provide 64 times the effective speed of a single series processing computer.

Installation of NASTRAN on the ILLIAC would provide a centralized, efficient, and sophisticated analytical tool to potential users in nearly every major industrial center in the United States. Not only does the ILLIAC provide its users with a significant increase in computer efficiency, it is now accessible to many government and university users throughout the nation via the highspeed communications ARPA Network (ARPANET) of small, medium, and large computers. In the future, the ILLIAC will be available to a broader spectrum of users for government-related and/or government sponsored projects. So far, however, specific provisions have not been made for a charging algorithm designed for individual job accounting.

Based on the working knowledge gained by the UAI staff in developing structural analysis software for the ILLIAC under contract with the Defense Nuclear Agency (DNA) and sponsored by the Advanced Research Projects Agency (ARPA), two basic approaches were studied for installing NASTRAN on the ILLIAC. One approach would be to utilize the large CDC, UNIVAC, and IBM computers of the ARPANET as host processors to perform selected NASTRAN input and output processing and to use the ILLIAC for the major computational tasks of NASTRAN. This "ILLIAC + Host" approach is compared to an "ILLIAC-Only" approach which assumes NASTRAN would be installed in its entirety on the ILLIAC. The results of this study provide the basis for the following conclusions:

- 1. Installation of NASTRAN using the "ILLIAC-Only" alternative is feasible and the preferred approach.

- 2. A complete NASTRAN system could be installed and available for execution in approximately 18 months. Full optimization would require an additional 18 to 24 months.

- 3. User access to NASTRAN on the ILLIAC would be possible via ARPANET from nearly every major industrial center throughout the United States.

The justification for expending the estimated 60 man-months for initial installation and an additional 50 to 75 man-months for full optimization of NASTRAN on the ILLIAC can be summarized as follows:

- 1. Major computational activity, such as matrix decomposition, can be performed 25 to 130 times faster on the ILLIAC as compared to current third generation serial processors.

- 2. The ILLIAC is ideally suited to processing large static, dynamic and nonlinear analyses involving highly iterative techniques which heretofore have not been practical on conventional serial processors.

- 3. Finally, the centralization of maintenance and development efforts on the ILLIAC would reduce future costs of maintenance and would provide ILLIAC users immediate access to all such improvements.

Also presented in this study are the justifications for selecting the ILLIAC over other multiprocessing computers. These may be summarized as follows:

- 1. The ILLIAC is now operational and has been demonstrated to be highly suited for the matrix processing operations of NASTRAN.

- 2. The ILLIAC can perform from 1 to 1.7 times more arithmetic operations per second compared to the most efficient alternative, the CDC STAR pipeline processor.

- 3. The ILLIAC is currently available via the ARPANET from nearly all parts of the nation.

To achieve these significant advantages, however, care must be exercised during program design in order to overcome certain limitations of the

ILLIAC System hardware. These limitations, which are fully described in Chapter II of this study, are as follows:

- 1. The ILLIAC System is dedicated to the execution of only one job at a time. Therefore, the effective total time of execution must include all phases of processing.

- 2. Data transfers from Central Memory to the ILLIAC disk is slow compared with the transfer rates from that disk to ILLIAC memory. This imposes practical limits on the size of problems to be solved.

- 3. The total space available on the ILLIAC disk is also limited, thereby accentuating the problems of slow data transfer to and from Central Memory which would be required during execution of very large problems.

These limitations, when properly accounted for, do not discount the impact the ILLIAC can have in providing the structural analysis community with a new increase in computer capability.

The background information for this study, from which each of the above conclusions was derived, is presented below. The current Level 15.7.7 [Ref. A, B, C], a precursor to the upcoming Level 16 release of NASTRAN, was assumed throughout. The following chapters are organized to present first the background information on the ILLIAC hardware and available software, and the design criteria for selecting the best approach to installing NASTRAN. Then, based on the selection of the "ILLIAC-Only" approach, the design specifications, the task identification, and the cost and schedule estimates for implementation are presented. The last chapter presents an overall summary and the conclusions derived from this feasibility study.

## CHAPTER II

## ILLIAC IV SYSTEM BACKGROUND

Background information relating to the ILLIAC computer, its supporting hardware and available software is presented here. Historical perspective is also provided to illustrate the magnitude and complexity of the tasks involved in developing a fourth generation computer system with the power and capacity of the ILLIAC [Ref. 6,7,9-13].

ILLIAC, which is now operational, offers an exceptionally high computational throughput compared to current third generation computers. This high rate is achieved principally through the parallel structure of its processor. This structure is pictured in Figure 2.1. It consists of 64 small computers called processing elements, or PEs. These 64 PEs are managed by a single control unit, or CU, which directs the execution of the same instruction sequence in each of the 64 PEs <u>simultaneously</u>. However, because the actual data in each PE may be different, the effect is to achieve a computational power as much as 64 times more effective than that of a conventional serial processor.

For example, in terms related to finite element analyses as performed by NASTRAN, the power of the ILLIAC can be achieved by:

- 1. Generating 64 beam element stiffness matrices at the same time.

- 2. Decomposing 64 columns of a stiffness matrix simultaneously.

- 3. Performing forward and backward substitution on 64 sets of righthand sides simultaneously.

These examples of efficiency illustrate the optimum potential of the ILLIAC. The significance of the ILLIAC's parallel processing power is magnified when compared with other modern serial and multiprocessing computer systems such as the new CDC STAR pipeline processor, CDC 7600, IBM 360/95, and IBM 360/75<sup>\*</sup> as shown below in Table 2.1 [Ref. 3]. This table compares the number of operations (in millions per second) that can be achieved by each of these computer systems. Two extremes are shown: one for serial operations (N = 1), and one for multiple processing with optimum efficiency (N =  $\infty$ ), Assuming optimum efficiency, the ILLIAC would be

- 1. 180 to 300 times faster than the IBM 360/75

- 2. 10 times faster than the IBM 360/95

- 3. 8 to 9 times faster than the CDC 7600

- 4. 1 to 1.7 times faster than the CDC STAR

These same comparisons, assuming now a serial mode of operation (N = 1), show that the ILLIAC in its least efficient mode is still faster than all but the CDC 7600. Therefore, if only modest utilization of its parallel processing capability is achieved, the resulting increase in efficiency over that of current third generation computers would be quite significant.

<sup>\*</sup>Of these, only the IBM 360/75 does not have some form of multiprocessing capability.

CONCEPTUAL

5

128 K WOFDS (2048 OR 4096 WORDS /PE)

FIGURE 2.1. STRUCTURE OF THE ILLIAC IV HARDWARE

•

· • • •

TABLE 2.1. COMPARATIVE SPEEDS OF EXECUTION

•

| Operation      | Steps<br>per<br>stage | IBM<br>360/75 | IBM<br>360/95 | CDC<br>7600 | CDC<br>STAR | ILLIAC IV |

|----------------|-----------------------|---------------|---------------|-------------|-------------|-----------|

| Addition       | 8<br>11<br>N          | 0.24          | 4.6           | 5.2         | 50          | 50        |

|                | N = 1                 | 0.24          | 0.55          | 1.6         | 0.57        | 0.78      |

| Multiplication | 8<br>II<br>N          | 0.14          | 4.6           | 5.2         | 25          | 77        |

|                | N = 1                 | 0.14          | 0.53          | 1.5         | 0.57        | 0.69      |

| Division       | 8 = N                 | 0.096         | 1.7           | 2.0         | 12.5        | 17        |

|                | N = 1                 | 0.096         | 0.43          | 0.93        | 0.56        | 0.27      |

|                |                       |               |               |             |             |           |

64-bit precision computation speeds (memory to memory) in millions of operations per second.

For the ILLIAC IV and STAR, the figures are preliminary and for illustrative purposes only. For the 360/195 and 7600, the numbers are sensitive to the way the smaller, faster memories are used. ----

;

The ILLIAC processor, however, is only one component of an entire complex of computer systems accessible via the ARPA Communications Network (ARPANET) shown in Figure 2.2. As can be seen in Figure 2.2, the ARPANET offers the user access to the ILLIAC from many parts of the United States. This accessibility is one of the major justifications for implementing a nationally recognized applications package, such as NASTRAN, on the ILLIAC.

The first of the two major sections to follow includes a more detailed view of the ARPANET facilities followed by a detailed description of the ILLIAC and its supporting hardware. This discussion of the ILLIAC hardware focusses on the central system of PDP-10 computers that support and control the ILLIAC, the specific requirements and facilities for data storage, the data file transfers capabilities, and the major hardware constraints which would affect installation of NASTRAN on the ILLIAC. These constraints, which affect the specific design criteria and program specifications discussed later in Chapters 3 and 4 respectively, may be summarized as follows:

- 1. The ILLIAC is a system dedicated to processing of a single job at a time without overlap.

- 2. The rate of data transfer from the central system to the ILLIAC IV Disk Memory (I4DM) is from 10 to 50 times slower than from the I4DM to ILLIAC memory.

- 3. The rotational speed of the I4DM is relatively slow compared to execution time on the ILLIAC which tends to cause processing to be I/O bound.

- 4. Data transferred from one PE to disk may be read back only into the core memory of that same PE.

This section on the system hardware is then followed by a discussion of the software packages available for process control and applications program development. The best of the application languages are compared and a tabulation of their key features is presented. This is followed by a summary comparison and identifying the selection criteria. The major language section criteria involve:

- 1. Access to unique hardware features of the ILLIAC

- 2. Variety of I/O capability

- 3. Future of maintenance and support

The eventual choice of language to be used depends on which alternative approach is selected for implementing NASTRAN. Therefore, the final selection is made part of the specifications for implementation presented in Chapter 4.

#### COMPUTER AND NETWORK HARDWARE

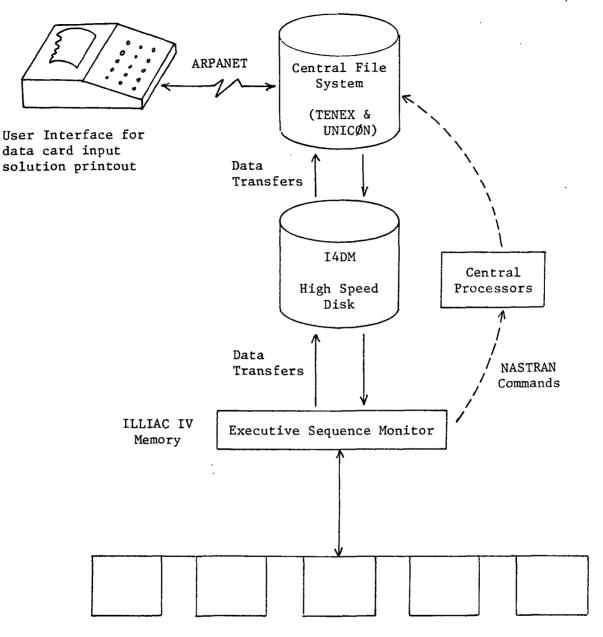

The system that includes the ILLIAC IV processor is an integrated system of data processing, information storage, and communications equipment located at NASA Ames Research Center, Moffett Field, California. The system is accessed, as shown in Figure 2.3, via a high-speed communications network (ARPANET) which provides large-scale computational and file management services to a growing community of users located throughout the nation. Through ARPANET, specialized analysis and research groups seeking solutions to a range of contemporary problems have access to required computational power not otherwise available to them, and not economically feasible on an individual or regional basis.

The ILLIAC system is being developed at Ames Research Center by the NASA Institute for Advanced Computation (IAC). The Advanced Research Projects Agency, ARPA, of the Department of Defense underwrote the research and production that were required in the early phases of development. Since 1971, the system at Ames has been sponsored and managed by a multi-agency board of owners, and today IAC receives its technical direction from this board. The board currently includes representatives of NASA, ARPA, and IAC.

REMOTE HOST COMPUTER SYSTEM

## FIGURE 2.3. SYSTEM ACCESS VIA ARPANET

The system being developed by IAC is the largest of several systems of computing resources available to users through ARPANET. Other resources, see Figure 2.4, vary from small interactive systems to large conventional processors. This network approach to the distribution of computer system services is one of the principal economic justifications for the development and operation of large systems - on the scale of the IAC System - for users whose applications require such systems but who cannot economically justify a dedicated system. The small systems on the network are used for communications and for program and data preparation tasks, allowing larger resources to be applied to tasks commensurate with their special capabilities.

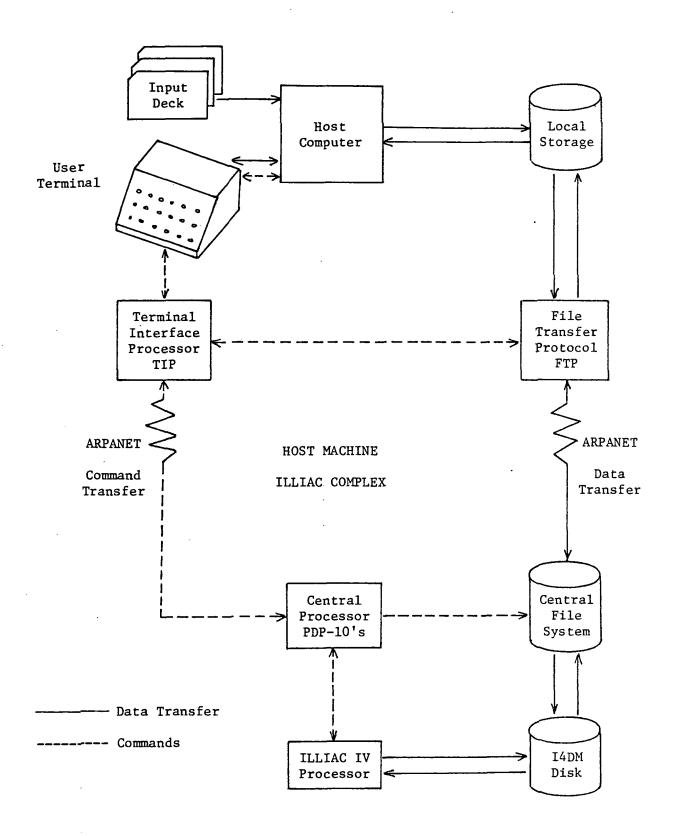

The potential value of the system at Ames is greatly enhanced by its accessibility to a large number of disparate and geographically remote users through the ARPA communications network. All users, wherever located, access the system remotely via ARPANET for both data transfer and interactive submission of processing requests. Therefore, the ARPANET is described first, followed by a summary of the ILLIAC System design specifications and a summary of the critical hardware features which will affect the implementation of NASTRAN.

#### The ARPA Network

ARPANET is a wide-band (currently 50,000 bits per second) [Ref. 8] communications network linking together computing centers and terminal access points throughout the country. The network has been constantly growing, both in the number of computing facilities available through it and in its geographic extent, since its inception in 1969. It should be noted that the participating institutions are primarily universities, with a sprinkling of public and private research organizations.

A primary purpose underlying ARPA's sponsorship of the network is to establish the feasibility and to develop the technical and management basis for computer system networks on a large scale. In the future, data rates in excess of one million bits per second are expected over the ARPANET.

ARPANET not only represents a linking together of equipment, but also includes a standard set of management procedures and communications protocol. For example, network procedures include a file transfer facility that allows the easy transfer of files to and from virtually any computing center in the network. There is also a high degree of standardization in the control languages of the various network systems.

Network users of any of the available computing and data storage services interact with the resources of their choice, either directly through data terminal devices tied into the network, or indirectly through interaction with local computer centers which are in turn tied into the network. A set of geographically dispersed network resources can be readily combined, and each applied to an appropriate part of the solution of a single problem. Regardless of how the resources of the system are intended to be used, the procedures for access and interaction are generally the same. The potential of the network as a resource for servicing and making available the multitude of current and yet-to-be-developed structural mechanics programs is obvious.

FIGURE 2.4. LOGICAL MAP OF ARPA NETWORK RESOURCES, JANUARY 1974

The major centers available to the ARPANET, which are shown in Figure 2.4, illustrate the generality of inter-system communication capabilities. For example, the current development efforts at UAI have utilized several components of this system. These include the IBM 360/91 at the University of California at Los Angeles (UCLA), the Burroughs B6700 at the UC San Diego (UCSD), and of course, the ILLIAC IV System at Ames, Moffett Field, California. The IBM 360/91 at UCLA provides the host computer facilities on which NASTRAN has been installed and modified to transmit basic structural data and the control files for execution on the ILLIAC. Once a solution is obtained, the results are communicated back to the IBM 360/91 host for the selective output processing as requested by the user. Also, the B6700 at UCSD was used via ARPANET during initial code development and testing via the SSK ILLIAC System simulator. This effort, however, is no longer required as the ILLIAC is now available directly for code development and testing.

The TIP (Terminal Interface Processor) at USC is used as the local resource for interaction with the ARPANET. Any other TIP (marked by T in Figure 2.4) could be used interchangeably for dial-up typewriter terminal activities. Via the TIP, a user can remotely control files and execution on any host to which he is given access on the ARPANET. This feature allows a user in Boston, for example, to initiate computations on the UCLA IBM 360/91 for creation of his input files for the ILLIAC, to transfer these files to Ames and to process them on the ILLIAC, to return the results to UCLA for output processing, and finally to interrogate these files selectively or have them shipped to a local site in Boston for volume printout.

The hardware facilities of the ILLIAC IV System at Ames are described next.

## The ILLIAC IV System Hardware

The ILLIAC IV System at Ames, which consists of a number of computing elements, is a remotely accessible facility available to a variety of user groups as described above. Figure 2.5 is a high-level block diagram showing the major functional elements of the system as it is now in operation. Looking at these elements first from a user's point of view, the <u>communications processor</u> ties the system to ARPANET. It provides data error checking and performs the necessary communications protocol.

The <u>central processors</u> (PDP 10 and 11, and one Burroughs 6700) control the user job sequences and execute all of the utility programs provided to users by the system. These processors interpret service requests from users and either execute the necessary utility programs or pass on the requests when they are for services provided by other resources in the system. The <u>resource</u> <u>management processors</u> control and allocate the major resources in the system; they do not directly execute user programs. The resources they control include the data storage devices and the ILLIAC processor itself which was pictured earlier in Figure 2.1.

All of the system processors communicate with each other through central memory. Central memory also functions both as a program and data store for the processors, and as an intermediate buffer for data transfers between any two storage devices in the system and between the system and ARPANET. Central memory is thus pictured as the central device in the system in Figure 2.5.

The major devices in the system are the UNICON laser memory and the ILLIAC processor. The UNICON laser memory, with an on-line capacity of 700 billion bits, is the largest storage device in a central file system which also includes a large buffer disk and magnetic tapes. Users do not directly address or specify the UNICON memory for data storage; rather, the location of all data files in the system is controlled by the central file system.

The block labeled "ILLIAC IV" in Figure 2.5 represents both the ILLIAC processor and the large ILLIAC disk memory system, which has a capacity of over 32 million 32-bit words. The ILLIAC processor, which is the major processor in the system, is totally dedicated to the execution of user code. It is seen by the central system as a large peripheral device providing a special user service, namely, very high-speed parallel processing on large data volumes. These services can be used independently or in combination in the solution of a single problem. The separate nature of these services is a result of the architecture of the system. Although fully integrated, it can be functionally utilized as three independent subsystems, namely, the ILLIAC, the information storage subsystem, and the central system.

## FIGURE 2.5. MAJOR FUNCTIONAL ELEMENTS OF THE SYSTEM

Once the program and data have been stored on the system at Ames, the user defines the general processing tasks to be performed, including those steps to be done on the ILLIAC. This definition can be done interactively or in a batch sequence. The central system then initiates the movement of the data files from the UNICON memory to the ILLIAC memory system. The transfer takes place in a series of steps under control of resource management processors. Once a sufficient quantity of data has been transferred to the ILLIAC disk memory, the program itself is moved from the UNICON to the processor memory, which functions as working storage for the ILLIAC. Execution then begins. Refer to Figure 2.6 for an illustration of data movement within the ILLIAC IV subsystem.

The ILLIAC subsystem, which is distinct from the central system but controlled by it, includes the ILLIAC processor, a 256K (32-bit word) processor memory, and a 32-million-word main disk memory device (see Figure 2.6). The high execution rate of the ILLIAC is achieved principally through the parallel structure of its processor, presented here in general terms.

The ILLIAC processor executes a common instruction sequence simultaneously on a large number of otherwise independent sets of data. This simple description contains the three key phrases in understanding the parallelism implemented in the ILLIAC: (1) "a common instruction sequence", (2) "simultaneously", and (3) "independent sets of data".

The instruction sequence is similar to that of any modern large-scale processor. "Simultaneously" means literally that each instruction in the program sequence executes on every one of the independent data sets at the same time. The number of independent data sets can vary from one up to 512, depending on the required word size of each data item and the skill of the implementing programmer. With a single data stream, the ILLIAC is functionally identical to a conventional, nonparallel processor. The machine architecture, as seen in Figure 2.6, facilitates 64, 128, or 512 parallel data streams which are 64, 32, or eight bits wide, respectively. Both 64-bit and 32-bit words are standard ILLIAC word sizes and are fully implemented in parallel in the hardware and in the programming languages. Eight-bit wide parallelism may be thought of as a byte mode with more limited implementation in the hardware and software.

To achieve this high degree of parallelism, the processor structure consists of a single Control Unit (CU) that performs instruction decoding and program control and 64 arithmetic and logic units referred to as Processing Elements (PEs). The CU reads the instruction sequence stored in processor memory, decodes each instruction, and generates identical control signals for each of the PEs. The entire set of PEs (or any subset within it) executes the same instruction simultaneously, under CU control, each on different sets of data. Under program control, any subset of PEs can be selected <u>not</u> to execute the current instruction.

The instruction set and instruction execution times of each individual PE in the ILLIAC processor equal or exceed those of existing conventional processors. For example, a full 64-bit, floating point, normalized ADD takes approximately 300 nanoseconds. A MULTIPLY under the same conditions executes in about 600 nanoseconds.

There is a single instruction sequence, stored in processor memory. Interleaved in this instruction sequence, normally, are computational steps

executed by the PEs, and program control instructions executed by the CU itself. Thus the CU, in addition to controlling the PEs, executes instructions such as branching, loop counting, and the generation of external system calls. In order to provide a sophisticated control capacity (for example, complex loop indexing), the CU has a complete instruction set including arithmetic and logic, byte and bit, and special control instructions. The CU is, if viewed as a stand-alone device, a full-scale processor.

Another vital function of the CU is to direct the transfer of data from one PE to another. Each PE memory segment is hard-wired to four neighboring PEs to provide high-speed, core-to-core transfer rates. Two methods of transfer are available to the program user. One is <u>broadcasting</u>, which takes a single word from one PE and broadcasts it to all PEs. The second provides for <u>routing</u> of one word from each PE(i) the same distance j to PE(i + j) for all PEs simultaneously.

The high execution rate of the ILLIAC is achieved not only through the parallel structure of the PEs but also through execution overlap. The execution of instructions within the CU is overlapped in time with the execution of instructions by the PEs. The accessing of instructions from processor memory is overlapped with the execution of these instructions. Finally, PE operand fetches are overlapped with PE instruction execution.

The processor memory is working storage for both instructions and data for the ILLIAC processor. This memory may be thought of as an array of 64 columns and 2048 rows. Each column (which is either two 32-bit words or one 64-bit word in width) is associated with an individual PE. The CU can access the entire processor memory, while each PE accesses only its associated column. As described earlier, however, data can also be moved from one PE to another under control of the CU.

The main memory storage for the ILLIAC is the disk memory, the I4DM. This device is a fixed-head rotating disk system with a capacity of about 32 million 32-bit words. The system is composed physically of 13 disks which rotate synchronously with a 40-millisecond rotation period and which provide a maximum data transfer rate of about  $10^9$  bits per second. The entire processor memory can be written out to disk or loaded from disk in just one revolution. That is, 256K 32-bit words can be transferred in 40 milliseconds.

#### System Hardware Constraints

Though the hardware facilities described above offer significant computational speed, massive storage capabilities and unique inter-computer communication features, certain of these facilities impose constraints which must be mentioned. These constraints may be divided into four basic categories which effect the design of any applications program to be implemented. These are:

- 1. Data transferred from one PE to disk may be read back only into the core memory of that same PE.

- 2. The rotational speed of the disk is relatively slow compared to the speed of execution so that the system tends to be  $I/\emptyset$  bound for programs that require significant temporary data storage on disk.

- 3. The relatively slow transfer rates from central memory to the I4DM and the restricted number of I4DM disk drives (compared with current IBM 3330 capacities) place limits on the size of problems to be solved.

- 4. The ILLIAC is a dedicated machine restricted to the processing of a single job at a time without overlap.

Specifically, the first constraint requires that primary consideration must be given to design of the data structures to be implemented. Files must be organized to avoid as much as possible the necessity to transfer data from one PE memory to another. For example, matrix generation and matrix assembly modules need to be coordinated so that data output from one module is input to the other module in such a manner as to minimize the time required to route the data for assembly. Also, the storage of assembled matrix data should be designed to anticipate the specific PE into which it must be read for subsequent processing. In anticipation of these objectives, attention must be given to the selection of internal numbering schemes, to the design of solution algorithms, to take advantage of numbering conventions in order to minimize storage of pointer data and to the interfacing between modules which operate on these data. Those modules responsible for the major computational efforts probably should be specially coded to account for this constraint.

The second and third constraints impose a design requirement to optimize the allocation of disk space to storage of matrix data. The software facilities are provided, as described later, to "map" or assign data block storage on the disk. Careful attention to estimates for execution time relative to data transfer times is required to design "mapping" algorithms which will avoid potentially lengthy wait periods for disk I/O to take place. Practical considerations, however, dictate that this type of "tuning" of the application software be limited only to the interfaces between major time consuming modules. The relative overall speed of the ILLIAC will compensate for some inefficiencies of less critical modules.

The fourth constraint imposes more global considerations on the design of a large applications software package. The major concerns involved with current serial processors for checkpointing and restarting to protect the user during long running computations should be modified. An examination of the time required to regenerate data versus the time required to checkpoint and then restore that data will be required to establish new checkpointing criteria. The speed and capacity of the ILLIAC and its I4DM will generally show less time is required to regenerate matrices to insure cost effective utilization of the system. The overriding criteria will be to selectively checkpoint only the minimum size data blocks needed for restart rather than to implement the practice of arbitrarily checkpointing nearly every item as is done now in NASTRAN.

These hardware constraints apply primarily to the initial efforts of selecting a basic approach and design methodology for implementing any large application software package. The size of NASTRAN and the generality of its current capability also present major considerations. By retaining its original organization as a modular program, installation of NASTRAN on the ILLIAC can be accomplished utilizing either of two basic approaches:

1. The current NASTRAN system which now can operate on several of the remote host computers on the ARPANET can be modified to extend its

capabilities linking it to the ILLIAC for the execution of selected modules specifically designed for optimal utilization of the power and speed of the ILLIAC.

2. Directly implement all modules of NASTRAN on the ILLIAC first, and then selectively redesign the major modules for optimum utilization of the ILLIAC.

The first option would soon provide powerful and efficient code for a limited set of capabilities. The second option would allow execution of <u>all</u> current capabilities on the ILLIAC but at far from optimal efficiency. However, both options eventually would reach a commensurate level of efficiency, thus providing the NASTRAN user community with access to the most powerful computational facility now available.

The final selection of an approach for installing NASTRAN obviously depends heavily on the available software for its implementation and eventual optimization. The next section, therefore, is devoted to an analysis of the available software.

#### SYSTEM SOFTWARE

The system software available on the ILLIAC IV is divided into two categories: that used for producing application programs and that used for providing the job control and file control utilities.

There are four suitable application languages presently implemented for use on the ILLIAC:

GLYPNIR CFD IVTRAN

ASK Assembly language

Of these four, all but IVTRAN have seen extensive use on the ILLIAC. CFD is a FORTRAN-based language. It has been used in a wide variety of climatic and fluid dynamics problems. GLYPNIR, one of the first available languages for the ILLIAC, is based on ALGOL. It is being used now for structural analysis with the UAI-ILSA system and by several others who are performing earthquake studies. Many of the ILLIAC users also use ASK in certain applications where more efficient coding is desirable. IVTRAN, which is currently under development, is also a FORTRAN-based language. Though it has not yet seen much use, current studies indicate it is to be highly regarded as a major candidate for major software development on the ILLIAC.

Several additional languages such as COCKROACH and TRANQUIL have received some attention in recent years, but none has reached an operational state.

Two control languages are available to the user. These provide utility services for file editing and job control. The two systems are:

ACL - Job control language FTP - File transfer services

Both of these languages operate under the TENEX operating system of the central system's PDP-10 computers. These are summarized in the first section to follow. Next to be presented are the four application languages, along with a summary of the key features of the three higher level alternatives. The final section of this chapter presents an overall comparison of the three languages, GLYPNIR, CFD and IVTRAN, to be used later in selecting the language for implementing the NASTRAN capabilities on the ILLIAC.

Process Control Languages

ACL (A Control Language)

ACL is the general control language for the ILLIAC System. It provides linkage between the ILLIAC IV, the central file system, and the PDP-10 system process controllers. The language operates in two modes, batch and interactive, with several subsystems being restricted to only one mode. The language is sequential in nature with only simple error tests and jumps allowed.

A summary of services supplied is listed below:

1. Compile and Assembly Steps:

Subsystems are provided to support the GLYPNIR and ASK languages. IVTRAN will be available in the future. No services are available for CFD. These must be obtained through host computers over the ARPANET.

2. Program Execution Steps:

The normal services exist for submitting and monitoring the execution of user programs on the ILLIAC. Subsystems are also provided for the transfer of data to and from the I4DM and central memory.

3. Linkedit and Map Steps:

Linking of relocatable code and formatting of the I4DM working disk storage for the ILLIAC are provided with these subsystems:

Linkedit - Only simple linking procedures are supported. No overlay structures are allowed. Commands are also provided to control the manner in which unsatisfied external references are supplied.

<u>Map</u> - The map subsystem allows the user to format his areas on the I4DM for use during execution. A utility is also available to produce a printed picture of the resultant disk layout.

4. File Utilities:

Several subsystems are available for the editing and listing of files stored in the central file system. Three file types are supported, 7 or 8 bit ASCII formatted files, binary files, and ILLIAC Dump files.

The file editor used primarily for maintenance of source code and output viewing provides very good searching and updating facilities combined with ease of use.

## FTP (File Transfer Protocol)

The File Transfer Protocol is a processor for data transfers between host computers on the ARPA network. The primary function is to transfer data efficiently and reliably among hosts and to allow the convenient use of remote file storage facilities.

FTP provides for only limited data representation. Four data formats are

- 1. 8-bit ASCII formatted

- 2. 8-bit EBCDIC formatted

3. Image - continuous stream of binary data

4. Local - data is stored on logical bytes of a size specified by the user

The conversion of data between internal storage representations and the FTP representation is handled by the host computer before or after transfer. The system also provides access controls to prevent unauthorized or accidental use of files.

The following section describes the four primary application languages and summarizes their key features.

## Application Languages

### GLYPNIR

GLYPNIR is an ALGOL-based language for the ILLIAC with extensions to provide parallel processing capabilities. The GLYPNIR compiler runs on the B6700 computer and generates ASK code to be assembled and executed on the ILLIAC. A simulator (SSK) which runs on a B6700 also exists which does a bit-for-bit ILLIAC simulation of the GLYPNIR-generated machine code.

Being ALGOL-based, the language is quite flexible. Good capabilities exist for string-and-bit manipulation and partial word operations. Sufficient capabilities have been included to make efficient use of hardware capabilities. Direct operations on hardware registers and several routing capabilities are provided. ASK code may be inserted at any point in the GLYPNIR code and may use any GLYPNIR-defined variables. Good storage management facilities exist for assigning data to either PE or CU memory and to hardware registers. No provision is included for code overlaying.

Sufficient I/O capabilities exist for transferring data to and from the I4DM. A crude display feature is provided to format data for later output. The major drawbacks of the language come from its lack of formal support for maintenance and improvement. The language, though it is advanced, also tends to be difficult to program because of the large variety of constructs available to the user. That is, the existing FORTRAN code of NASTRAN could not readily be converted, and a major rewrite would be required for every module to be coded in GLYPNIR.

#### CFD

CFD is a FORTRAN-based language extended to include access to the parallel processing of the ILLIAC. The CFD code can be either compiled directly into ASK for execution on the ILLIAC, or it may be translated into equivalent FORTRAN for execution on any of the larger IBM computers. This allows a CFD program to be debugged externally from the ILLIAC. The language is actively supported and used at NASA Ames. Being FORTRAN-based, the language is restricted in its flexibility such as limited string-and-bit manipulation. Also, no provisions are available to use some of the hardware features of the ILLIAC. This includes no direct access to registers and limited routing capabilities. It is possible to include ASK code at any location in the CFD source statements. Good data assignment facilities are provided for storing data in either PE or CU memory. The language does not allow any type of mixed mode arithmatic.

Sufficient I/O capabilities exist for transferring data to and from the I4DM. No display feature is provided for formatted I/O and, if desired, must be accomplished with ASK.

Although easy to use, CFD is not as flexible or sophisticated as the GLYPNIR language. Unnecessary syntax restrictions also have been imposed to include parallel processing capabilities. These include the \* in Column 6 on most cards and a required (\*) subscript on all variables assigned to PE memory.

## IVTRAN

IVTRAN is a FORTRAN-based language for use on the ILLIAC. The language syntax is very similar to standard FORTRAN, making conversion from existing code a minimal effort. A major feature of the IVTRAN system is the "paralyzer", a compiler option for use in this conversion effort. The paralyzer examines DØ loops of standard FORTRAN programs and converts them into more efficient DØ FØR ALL loops for use on the ILLIAC.

IVTRAN is being actively developed by Massachusetts Computer Associates. Although it is not available to users at this time, recent benchmarks give encouraging results. The compiler appears to generate very efficient code and has extensive optimization facilities. The user can also aid the compiler in optimization by specifying expected execution frequencies through the FREQUENCY statement:

The I/O facilities of IVTRAN are quite different from those of the other languages. The biggest difference exists in formatted I/O. IVTRAN has very good display features derived from the full implementation of the FORTRAN FØRMAT statement. Binary I/O is of a buffered variety which does not allow for asynchronous processing. A non-buffered bulk I/O is also available for transferring whole IVTRAN arrays. This technique takes better advantage of the I4 hardware and does allow asynchronous processing.

IVTRAN contains all the normal restrictions of a FORTRAN-based language. These include poor string-and-bit manipulation facilities and no partial word operations. However, good debugging facilities and a mixed mode arithmetic feature are included.

One of the principal disadvantages of IVTRAN appears to be its limited utilization of the unique characteristics of the ILLIAC. Although little actual experience with the language is available, to produce code which fully utilizes this parallel processing feature could be difficult. Only one language construct, the DØ FØR ALL clause, deals with this important concept. No direct control is available over PE modes (on or off) or use of CU registers or CU memory. Also, no provision is available for inserting ASK code directly within the IVTRAN code, although separate ASK subroutines may be coded. The IVTRAN language attempts to relieve the programmer of many of the idiosyncrasies and difficulties of working in a parallel processing environment. The efficient use of parallel processing is highly dependent on the alignment of data in each PE memory. The facility for this in IVTRAN gives the programmer only limited control while the compiler attempts to do the majority of the work. Unfortunately, these attempts appear to have restricted the efficient use by the programmer of these important ILLIAC features.

### ASK

ASK is the assembly language for the ILLIAC and is fully supported by the Institute for Advanced Computations. It allows full use of the hardware configuration of the machine. While powerful, coding is difficult and time consuming, as with any assembly language.

I/O capabilities are very good for assembly language programming. Macros are available that provide disk and formatted I/O similar to that of GLYPNIR.

Its major advantage is for use in optimizing selected sections of code. It may be used as direct inserts into GLYPNIR and CFD program code and as a macro language for subroutine constructs.

#### Key Language Features

There are many features that determine the suitability of a language for any application. Table 2.2 summarizes the basic features for easy comparison of the three best higher level languages available on the ILLIAC: GLYPNIR, CFD, and IVTRAN. The more important of these features are identified below.

The user should have direct access to and control over the hardware functions unique to the parallel processing environment for optimal program design. These include:

- 1. Routing of data between PEs.

- 2. Access to the hardware registers.

- 3. Access to the small, high-speed memory of the CU.

- 4. Direct control over the operational mode of each PE (on or off).

- 5. Access to asynchronous I/O capability.

- 6. Ability to insert ASK code where needed to gain efficiency for computation and I/O.

- 7. Access to central file system from the ILLIAC.

Other important features to be considered are:

- 1. Available data types, including string and complex.

- 2. Communication facilities between subroutines, including calling parameters and common.

## TABLE 2.2. COMPARISON OF LANGUAGE FEATURES

|                      | GLYPNIR       | CFD              | IVTRAN            |

|----------------------|---------------|------------------|-------------------|

| Base language        | ALGOL         | FORTRAN          | FORTRAN           |

| Support -            |               |                  |                   |

| maintenance          | very little   | good             | good              |

| documentation        | poor          | good             | under development |

| improvement          | none          | fair             | good              |

| Syntax -             |               |                  |                   |

| readability          | good          | good             | good              |

| programability       | difficult     | difficult        | good              |

| reserve words        | ≈ 120         | ≈ 25             | none              |

| loops                | several types | DØ loop          | DØ loop           |

| mode control         | several types | logical IF       | DØ FØR ALL        |

| branches             | GØ TØ's       | several types    | several types     |

|                      | 00 10 5       | severar cypes    |                   |

| Code generation -    |               |                  | 1                 |

| efficiency           | poor          | fair             | good              |

| optimization         | none          | none             | good              |

| ASK inserts          | yes           | yes              | no                |

| Debugging -          |               |                  |                   |

| bound checking       | yes           | no               | yes               |

| subroutine call      | ,             |                  |                   |

| traces               | yes           | no               | yes               |

| conditional com-     | <i>J</i> = 0  |                  | , ,               |

| pilation             | yes           | no               | no                |

| variable displays    | no            | no               | yes               |

|                      |               |                  | ,                 |

| Hardware-related     |               |                  | -                 |

| features -           |               |                  |                   |

| routing functions    | yes           | no               | no                |

| register avail-      |               |                  |                   |

| ability              | yes           | no               | no                |

| ADB* usages          | yes           | some             | no                |

| mode control         | yes           | direct control   | no                |

| Macros               | DEFINE        | no               | no                |

| Subroutines and      |               |                  |                   |

| functions -          |               |                  |                   |

| separately compiled  | yes           | yes              | yes               |

| in-line              | yes           | no               | no                |

| -                    | ,             |                  | _                 |

| Built-in functions - |               |                  |                   |

| trig                 | yes           | yes              | yes               |

| log and exp          | yes           | yes              | yes               |

| type conversion      | yes           | yes              | yes               |

| bit manipulation     | shifts &      | shifts & rotates | shifts            |

|                      | rotates       |                  |                   |

|                      |               |                  |                   |

\*ADVAST, DATA, BUFFER

# TABLE 2.2. COMPARISON OF LANGUAGE FEATURES (cont'd)

|                                                                                 | GLYPNIR                                               | CFD                                                 | IVTRAN                                                                |

|---------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------|

| Data types -<br>real<br>integer<br>alphanumeric<br>logical<br>complex<br>string | 32 & 64 bit<br>32 & 64 bit<br>yes<br>yes<br>no<br>yes | 32 & 64 bit<br>32 & 64 bit<br>no<br>yes<br>no<br>no | 32 & 64 bit<br>32 bit<br>no<br>yes<br>no<br>yes                       |

| Implicit declaration                                                            | no                                                    | FORTRAN conventions                                 | FORTRAN conventions                                                   |

| Allowable bases                                                                 | betw'n 2 & 36                                         | base 10 only                                        | 8, 10, & 16                                                           |

| Data initialization                                                             | yes                                                   | some                                                | yes                                                                   |

| Subscripted<br>variables                                                        | l subscript                                           | 3 subscripts                                        | unlimited<br>subscripts                                               |

| Dynamic storage<br>allocation                                                   | yes                                                   | yes                                                 | no                                                                    |

| Data alignment -<br>by row<br>by column<br>equivalencing                        | PE variables<br>PE vectors<br>AS construct            | (*) construct<br>vectors<br>EQUIVALENCE             | physical skewing<br>aligned index<br>EQUIVALENCE,<br>OVERLAY & DEFINE |

| Common/global<br>data areas                                                     | Limited no. of global areas                           | COMMON                                              | COMMON                                                                |

| Mixed mode<br>arithmetic<br>Partial word                                        | yes                                                   | no                                                  | yes                                                                   |

| operations                                                                      | yes                                                   | no                                                  | no                                                                    |

| Relational operators                                                            | complete                                              | complete                                            | complete                                                              |

| Logical operators                                                               | complete                                              | AND, NØT, ØR                                        | complete                                                              |

| I/Ø to I4DM disk -<br>full row<br>half row<br>quarter row                       | yes<br>yes<br>yes                                     | yes<br>yes<br>yes                                   | yes<br>no<br>no                                                       |

| Formatted display                                                               | no                                                    | no                                                  | yes                                                                   |

| Asynchronous I/Ø                                                                | yes                                                   | yes                                                 | yes                                                                   |

| I/Ø to Tenex disk                                                               | yes                                                   | no                                                  | no                                                                    |

25

÷

- 3. Available compiler-provided functions, including logical, mathematical, and bit manipulative functions.

- 4. Compiler ability to utilize temporary storage, including dynamic array allocation.

- 5. Ability to allocate data across PE memories and within the memory of one PE.

- 6. Adequacy of debugging facilities, including checks on bounds of array subscripts, temporary debug output, and subroutine call tracebacks.

- 7. Compiler efficiency and code optimization.

- 8. Code checking facilities (simulators) external to the ILLIAC.

- 9. Appearance and readability of code syntax.

- 10. The level of support the language will receive, including error correction and future enhancements.

The remaining features listed in Table 2.2 refer to specific technical items important to the implementation of any major application package on the ILLIAC. The following section presents a summary comparison of all three languages.

## Language Comparison and Selection Criteria

In order to make the final selection, as will be done later in Chapter IV, this section presents a summary comparison of the four available application languages: ASK, GLYPNIR, CFD, and IVTRAN. The basic merits of these languages are compared to determine their relative suitability for use in the implementation of large application software systems on the ILLIAC.

The first and foremost criteria for selecting any ILLIAC language is its ability to utilize the parallel processing features of the ILLIAC Array. The language best suited for this purpose is ASK, the assembly language for the ILLIAC. Its drawback, of course, is the same difficulty inherent in using any assembly language. However difficult that may be, ASK must be used selectively to optimize both the inner computational loops and I/O processing.

Of the three higher level languages, GLYPNIR offers the greatest flexibility to the programmer in accessing the unique hardware features of the ILLIAC. CFD also provides ample access to these features but is constrained by limitations inherent in its FORTRAN-like constructs. Both, however, allow for direct insertion of ASK code for optimal efficiency. IVTRAN provides only for minimal utilization of the parallel processing features. Its major advantage is easy application to program conversion of existing code. If IVTRAN is used, together with selected subroutines coded in ASK, the overall conversion of an existing FORTRAN code can be performed efficiently, and effective utilization of the ILLIAC can be achieved.

The second major criteria for selecting a language is its I/O capability. The two basic types of I/O required are binary and formatted. Only IVTRAN provides formatted I/O comparable with standard FORTRAN. GLYPNIR provides -

very limited formatting and CFD provides none. Again, ASK may be used to provide this capability for both GLYPNIR and CFD. GLYPNIR, CFD, and ASK provide the best binary I/O capabilities. IVTRAN is limited to buffered binary I/O with no asynchronous capability.

The capacity to utilize the asynchronous I/O feature of the ILLIAC will be extremely important to avoid potentially severe I/O bound operations. Though GLYPNIR and CFD do provide for this capability, any large applications system should include a general purpose I/O package to manage these activities. This package should be written in ASK to best utilize the sophisticated I/O features of the ILLIAC.

A third criteria for selecting a language is the support it will be given in the future. Only GLYPNIR is not actively being maintained. CFD and IVTRAN will both be provided with ongoing maintenance for both error correction and improvements by their respective developers. ASK, of course, will be actively maintained, as it is the basic assembly language for the ILLIAC. CFD and GLYPNIR code can be tested outside the ILLIAC environment as an aid to debugging. This is important for the near future while the ILLIAC is in the checkout phase and turn-around remains a problem. IVTRAN is provided with a "paralyzer" to assist in the conversion of existing FORTRAN code, but checkout can only be performed on the ILLIAC Array itself.

The process of combining relocatable code produced by any of the compilers into an executable program is similar for all the languages. The code produced by each compiler can be processed by the LINKEDITOR provided on the ILLIAC system. What is lacking at present is an adequate overlay facility for managing large application programs. Necessarily, therefore, a manual overlay capability will have to be developed.

In summary, the selection of a language on overall capabilities is largely dependent on the tasks to be performed. For coding a new program for operation on the ILLIAC, most likely CFD or GLYPNIR would be the best choice. Both these languages allow the user the greatest flexibility to access the unique features of the ILLIAC. Thus, optimizing the code for full utilization of the parallel processing is possible. Of these two languages, CFD offers the distinct advantage of a more familiar syntax, and initial checkout of the code can be performed efficiently outside of the ILLIAC environment. This approach would be recommended if only selected NASTRAN modules were to be developed for optimal utilization of the ILLIAC. These selected modules then could be accessed via the ARPANET from any remote host on which NASTRAN is already operational.

If an entire application package such as NASTRAN, which has already been programmed in FORTRAN, were to be implemented on the ILLIAC, then IVTRAN would be the logical choice. The close resemblance of IVTRAN to FORTRAN and the availability of a "paralyzer" to assist in code conversion, minimizes the initial installation task. However, because the resulting code would make inefficient use of the ILLIAC, the more time-consuming modules would have to be recoded to fully utilize parallel processing. The singular advantage of this approach would be that a functioning integrated system could be available early in the process and immediate gains would be realized as each new optimized module is completed.

## CHAPTER III

### DESIGN CRITERIA

This chapter presents the fundamental design criteria for implementing NASTRAN on the ILLIAC System. Pros and cons of the two alternative approachs for installation are discussed. The technical feasibility of these approaches is related to the basic design items or building blocks of the NASTRAN System. The relationship between the possible installation approaches and installation effort, program efficiency, and user convenience are explored. Finally, a basic design for the installation of NASTRAN on the ILLIAC is selected.

The main purpose for this design would be to provide a user-oriented system, commensurate with current NASTRAN standards, which minimizes the need for user interaction with the ILLIAC IV System. There are two feasible approaches to be considered for installing NASTRAN on the ILLIAC. These are:

- 1. The "ILLIAC-Only" approach wherein 100% of the NASTRAN program is implemented directly on the ILLIAC.

- The "ILLIAC + Host" approach wherein selected NASTRAN operations are implemented on the ILLIAC so as to be accessible via the ARPANET from an extended version of standard NASTRAN operating on a remote host computer.

The first approach would involve taking the machine-independent code of current NASTRAN and processing it by a FORTRAN compiler, translator, or other source conversion program. Thus, installation of NASTRAN could proceed in a "normal" manner even though the ILLIAC is not a "normal" machine. However, object code as initially generated by this method would probably not make efficient use of the ILLIAC hardware. As noted in Chapter II, this code still would execute on current third generation computers. Also, once installed and operational, the full power of the ILLIAC could be exploited by selectively optimizing the resulting source code to take full advantage of the unique parallel processing features of the ILLIAC.

The ILLIAC + Host approach is not so much the installation of NASTRAN on the ILLIAC as it is the extension of current NASTRAN to access the ILLIAC. In this approach NASTRAN could be installed on one or more of the conventional host computers (IBM, CDC, or UNIVAC) on the ARPANET. Functional modules which perform heavy computational chores would be specially coded and installed on Thus, the input card processing, geometry processing, output the ILLIAC. file processing, etc. would continue to be performed by a conventional NASTRAN computer. The real "number-crunching" portion of an analysis would be performed by the ILLIAC. This approach has the advantage that the ILLIAC programming effort would be concentrated on relatively few modules. The ILLIAC part of NASTRAN could be specifically tailored to fully utilize the power of the ILLIAC. Problems with source code conversions and inefficient utilization of the ILLIAC could be avoided. However, the user will have to expend more effort to make a NASTRAN run. For example, a scenario for solving a problem with this approach might be as follows:

- 1. Run NASTRAN on a conventional host computer to process input.

- 2. Log on to the ARPANET system to direct data files from the host to the ILLIAC IV System.

- 3. Run NASTRAN on the ILLIAC to obtain solution.

- 4. Log on to the ARPANET system to direct data files from the ILLIAC IV System to the host computer.

- 5. Restart NASTRAN on the host computer to obtain printed output.

As will be shown later, the end result of both approaches would provide the user with a highly efficient code for executing structural analyses on the ILLIAC. The time phasing of its availability would be different as shown below in Figure 3.1. The solid line shows the sequence in which full optimization is achieved as each increment of capability is added. Note that for the ILLIAC-Only approach, the process of optimization accelerates in time while for the ILLIAC + Host, the time for implementation of each new capability remains relatively constant. This difference reflects the fact that with the ILLIAC-Only approach, the code to be implemented with optimization is derived from existing tested capability and needs only to be modified, as opposed to being developed especially for and tested entirely on the ILLIAC. Table 3.1 has been prepared to help identify those modules which would be prime candidates for optimization. The heavy computational modules shown are the prime candidates for recoding under either approach. Conversely, those modules which might be modified frequently for future developments would not be prime candidates. Those modules with both characteristics would require the exercise of engineering and programming judgment before a decision could be made.

FIGURE 3.1. TIME PHASING OF AVAILABLE NASTRAN CAPABILITY ON THE ILLIAC.

|        |     |   | · · ·   |   |   |         |   |   |         |   |   |

|--------|-----|---|---------|---|---|---------|---|---|---------|---|---|

| MODULE | С   | M | MODULE  | С | M | MODULE  | С | М | MODULE  | С | м |

| ADD    | x   |   | GPWG    |   |   | PLA2    | x |   | SMA3    |   |   |

| ADD5   | x   |   | IFP     |   | x | PLA3    | x | x | SMP1    | x |   |

| BMG    |     |   | IFP1    |   | x | PLA4    | x | x | SMP2    | x |   |

| CASE   |     |   | IFP3    |   |   | PLØT    |   | x | SMPYAD  | x |   |

| CEAD   | x   |   | IFP4    |   |   | PLTSET  |   | x | SØLVE   | X |   |

| CHKPNT |     |   | IFP5    |   | 1 | PLTTRAN |   |   | SSG1    |   | x |

| CØND   |     |   | INPUT   |   |   | PRTMSG  |   |   | SSG2    |   |   |

| DDR1   |     |   | INPUTT1 |   |   | PRTPARM |   |   | SSG3    | x |   |

| DDR2   |     |   | INPUTT2 |   |   | PURGE   |   |   | SSG4    |   | . |

| DECØMP | x   |   | JUMP    |   |   | RANDØM  |   |   | TA1     |   | x |

| DPD    |     |   | MATGPR  |   |   | RBMG1   |   |   | TABPRT  |   |   |

| DSMG1  | x   | X | MATPRN  |   |   | RBMG2   | x |   | TABPT   |   |   |

| DSMG2  |     |   | MATPRT  |   |   | RBMG3   |   |   | TRD     | x |   |

| END    |     |   | MCE1    |   |   | RBMG4   |   |   | TRNSP   | x |   |

| EQUIV  |     |   | MCE2    | x |   | READ    | x |   | UMERGE  | x |   |

| EXIT   |     |   | MERGE   | x |   | REPT    |   |   | UMFEDIT |   |   |