Contract No. NASA 9-14757 DRL #: T-1207

Item No. 4 DRD #: MA-599T

CR 151093

(NASA-CR-151093) SOLID STATE TELEVISION

N77-10396

CAMERA (CID) Final Technical Report, Aug. 1975 - Aug. 1976 (General Electric Co.)

CSCL 17B

Unclas

G3/32 07710

SOLID STATE TELEVISION CAMERA (CID)

August 1976

FINAL TECHNICAL REPORT

**OPTOELECTRONIC SYSTEMS OPERATION**

**ELECTRONIC SYSTEMS DIVISION**

Syracuse, N.Y.

SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered)

| REPORT DOCUMENTATION PAGE                                                  |                            | READ INSTRUCTIONS BEFORE COMPLETING FORM.                      |  |  |

|----------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------|--|--|

| 1. REPORT NUMBER . 2.                                                      | GOVT ACCESSION, NO.        | 3. RECIPIENT'S CATALOG NUMBER                                  |  |  |

| •.                                                                         |                            | •                                                              |  |  |

| 4. TITLE (and Subtitle)                                                    |                            | 5. TYPE OF REPORT & PERIOD COVERED                             |  |  |

| COLTE OF AND METERITOTON GAMED & (O'                                       | /                          | Final Report                                                   |  |  |

| SOLID STATE TELEVISION CAMERA (C:                                          | , ער אדי.<br>אריד          | August 1975-August 1976                                        |  |  |

|                                                                            |                            | 6. PERFORMING ORG. REPORT NUMBER                               |  |  |

| 7. AUTHOR(a)                                                               |                            | 8. CONTRACT OR GRANT NUMBER(s)                                 |  |  |

| Daniel W. Steele                                                           | ,                          | NAS9-14757                                                     |  |  |

| Wayne T. Green                                                             |                            | NAD9-14737                                                     |  |  |

| 9. PERFORMING ORGANIZATION NAME AND ADDRESS                                |                            | ID DOGEDAN EL EUENT DOGISCT TASK                               |  |  |

| General Electric Company                                                   | ***                        | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS |  |  |

| Optoelectronic Systems Operation                                           |                            |                                                                |  |  |

| Electronics Park, Bldg. #3-201<br>Syracuse, New York 13201                 | •                          |                                                                |  |  |

| III. CONTROLLING OFFICE NAME AND ADDRESS                                   |                            | 12. REPORT DATE                                                |  |  |

| NASA Lyndon B. Johnson Space Cent                                          | ter                        | July 1976 -                                                    |  |  |

| R&T Procurement Branch                                                     |                            | 13. NUr ŞS                                                     |  |  |

| Houston, Texas 77058 14. MONITORING AGENCY NAME & ADDRESS(If different f.  | from Controlling Office)   | 15. SEC (of this report)                                       |  |  |

|                                                                            |                            | Unclassified                                                   |  |  |

| ,                                                                          |                            |                                                                |  |  |

| . ,                                                                        |                            | 15a, DECLASSIFICATION/DOWNGRADING<br>SCHEDULE                  |  |  |

| 16. DISTRIBUTION STATEMENT (of this Report)                                |                            | -                                                              |  |  |

| ' SID HIS HOLD ON THE MENT OF THE PROPERTY                                 | •                          | _                                                              |  |  |

|                                                                            |                            | •                                                              |  |  |

|                                                                            |                            |                                                                |  |  |

|                                                                            |                            |                                                                |  |  |

|                                                                            |                            |                                                                |  |  |

| 17. DISTRIBUTION STATEMENT (of the abstract entered in                     | Block 20, if different tro | m Report)                                                      |  |  |

| *                                                                          |                            | ,                                                              |  |  |

|                                                                            |                            |                                                                |  |  |

|                                                                            |                            |                                                                |  |  |

| 18. SUPPLEMENTARY NOTES                                                    |                            |                                                                |  |  |

|                                                                            |                            |                                                                |  |  |

|                                                                            |                            |                                                                |  |  |

|                                                                            |                            | _                                                              |  |  |

| 19. KEY WORDS (Continue on reverse side if necessary and                   | identily by block number)  |                                                                |  |  |

| CID                                                                        |                            |                                                                |  |  |

| Charge Injection Device                                                    |                            |                                                                |  |  |

| Solid State Imager                                                         |                            |                                                                |  |  |

| Camera                                                                     |                            |                                                                |  |  |

| 20. ABSTRACT (Continue on reverse side if necessary and i                  | dentify by block number)   |                                                                |  |  |

| This report describes the design, development and test of a Charge         |                            |                                                                |  |  |

| Injection Device (CID) camera using a 244x248 element array. The resulting |                            |                                                                |  |  |

| camera was delivered to NASA.                                              |                            | 1                                                              |  |  |

|                                                                            |                            |                                                                |  |  |

| The end product of this contr                                              | actual effort v            | was a CID camera employing                                     |  |  |

scanning techniques which allow the CID to be used with conventional monitor displays meeting EIA standards. The camera was designed to provide state-of-

## SECURITY CLASSIFICATION OF THIS PAGE(When Date Referred)

the-art performance in CTD technology. The 244x248 element array is presently the highest resolution CTD array that can be produced. A number of video signal processing functions are included which maximize the output video dynamic range while retaining the inherently good resolution response of the CTD. In addition, the camera provides two switchable scanning options, two switchable readout options and various internal video and timing signals at the back panel of the camera. The combination of options and externally provided signals will allow this camera to become a valuable evaluation tool for determining future design goals. The following is a summary of some of the unique features of this CTD camera.

| Low | light | leve1 | performance | - | NDRO  | readou  | ut  | mode   | with   | built  | in   | thermo |

|-----|-------|-------|-------------|---|-------|---------|-----|--------|--------|--------|------|--------|

|     | _     |       | •           |   | e1ec  | tric co | 001 | ing a  | at .13 | } ft c | and] | Le     |

|     | •     |       |             |   | scene | e illu  | nir | ıatioı | ns.    |        |      |        |

| High S/N Ratio | - In excess of 50 DB for both pattern |

|----------------|---------------------------------------|

|                | and random noise components.          |

| Anti-Blooming | - | Inherently | excellent | optical | overload |

|---------------|---|------------|-----------|---------|----------|

|               |   | response.  |           |         |          |

| Geometric Distortion | - | Inherently | excellent | geometric |

|----------------------|---|------------|-----------|-----------|

|                      |   | linearity. |           |           |

| Sequential | Scanning | - | Sequent | :ial | scan  | mode, | all  | lines | in |

|------------|----------|---|---------|------|-------|-------|------|-------|----|

|            |          |   | proper  | vert | cical | seque | nce. |       |    |

AGC - The first utilization of AGC in a CID camera.

Contract No. NASA 9-14757 DRL #: T-1207 Item No. 4 DRD #: MA-599T

SOLID STATE TELEVISION CAMERA (CID)

August 1976

FINAL TECHNICAL REPORT

# OPTOELECTRONIC SYSTEMS OPERATION ELECTRONIC SYSTEMS DIVISION

Syracuse, N.Y.

# TABLE OF CONTENTS

| <u>Paragraph</u> | <u>Title</u>                               | Page No. |

|------------------|--------------------------------------------|----------|

| 1.0              | Purpose                                    | 1        |

| 1.1              | Objective                                  | . 1      |

| 1.2              | End Product                                | 1        |

| 2.0              | Scope                                      | 1        |

| 3.0              | Technical Requirements                     | 2        |

| 3.1              | Study, Design and Development Requirements | 2        |

| 3.2              | Scanning Technique                         | 3        |

| 3.2.1            | Resolution                                 | 3        |

| 3.2.2.           | Formatting                                 | 4        |

| 3.3              | Design                                     | 6        |

| 3.3.1            | Resolution                                 | 6        |

| 3.3.2            | Interlace Ratio                            | 6        |

| 3.3.3            | Aspect Ratio                               | 6        |

| 3.3.4            | Vertical Scan                              | 7        |

| 3.3.5            | Operating Light Ranges                     | , 7      |

| 3.3.5.1          | Gray Scale Response                        | 7        |

| 3.3.5.2          | Dynamic Light Range                        | 8        |

| 3.3.6            | Operating Voltage                          | 9        |

| 3.3.7            | Power Consumption                          | 9        |

| 3.3.8            | Output Video Format                        | 9        |

| 3.3.8.1          | Standard Load Impedance                    | 10       |

| 3.3.8.2          | Composite Picture Signal                   | 10       |

| 3.3.8.2.1        | Polarity                                   | 10       |

| 3.3.8.2.2        | Signal Levels                              | . 10     |

| 3.3.8.3          | Sync Signal Waveform                       | 11       |

| 3.3.9            | Output Resolution                          | 11       |

| 3.3.10           | Output Video Voltage                       | 12       |

| 3.3.10.1         | Blanked Output Video Voltage               | 12       |

| 3.3.10.2         | Synchronozing Signal                       | 12       |

| 3.3.10.3         | Setup Levels                               | 13       |

| 3.3.11           | Signal-to-Noise Ratio S/N                  | 13       |

| 3.3.12           | Ceometric Distortion                       | 13       |

## Table of Contents (contd)

| Paragraph | <u>Title</u> <u>Page</u>                | No. |

|-----------|-----------------------------------------|-----|

| 3.3.13    | Spots and Blemishes                     | .4  |

| 3.3.14    | Blooming 1                              | .5  |

| 3.3.15    | Camera Optics                           | _5  |

| 3.3.16    | Camera Controls                         | .5  |

| 3.3.17    | Camera Interfaces 1                     | .6  |

| 3.3.18    | Non-Destruct Readout Mode               | .6  |

| 3.4       | Prototype Development and Test 1        | .6  |

| 3.5       | Design Reviews                          | .6  |

| 4.0       | Camera Operation                        | 20  |

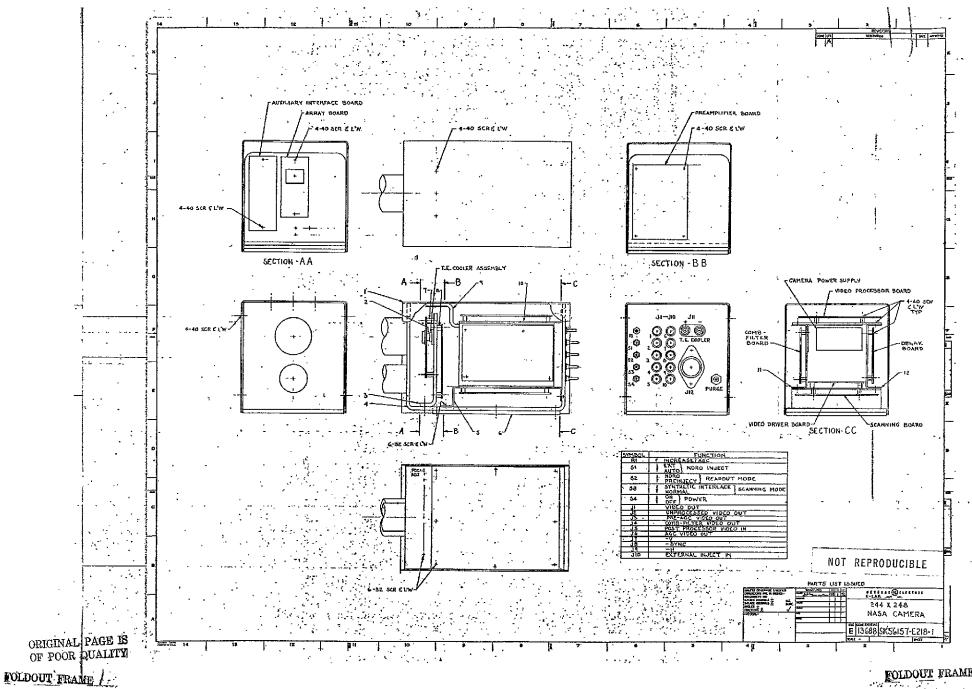

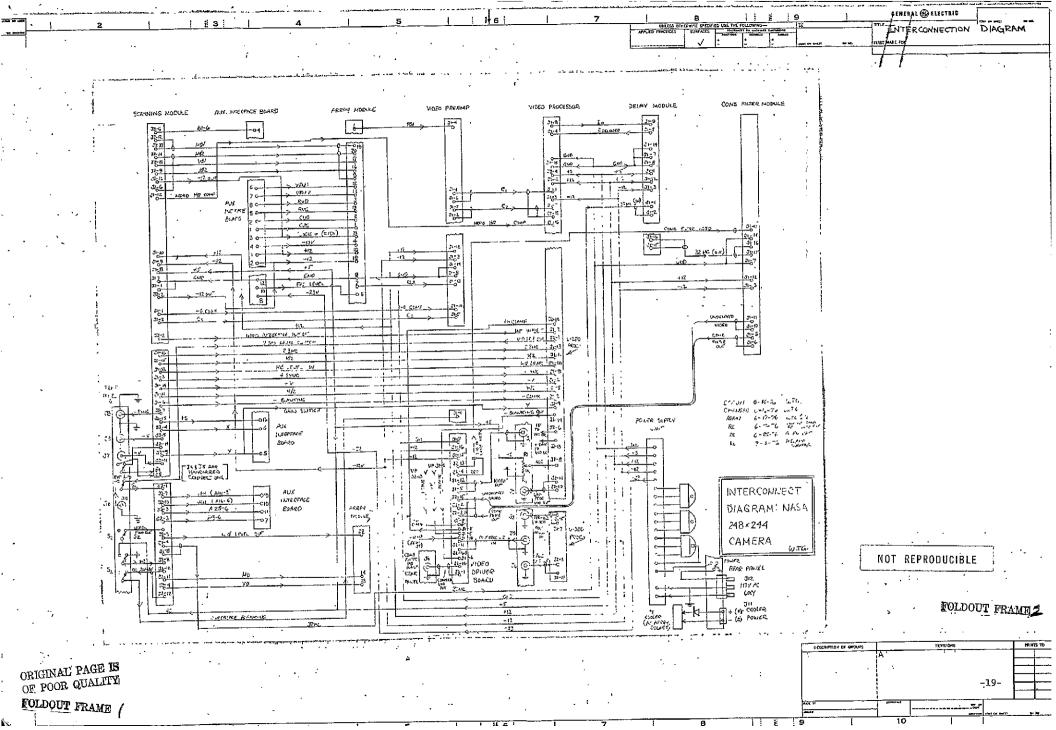

| 4.1       | Preamplifier Board 2                    | .0  |

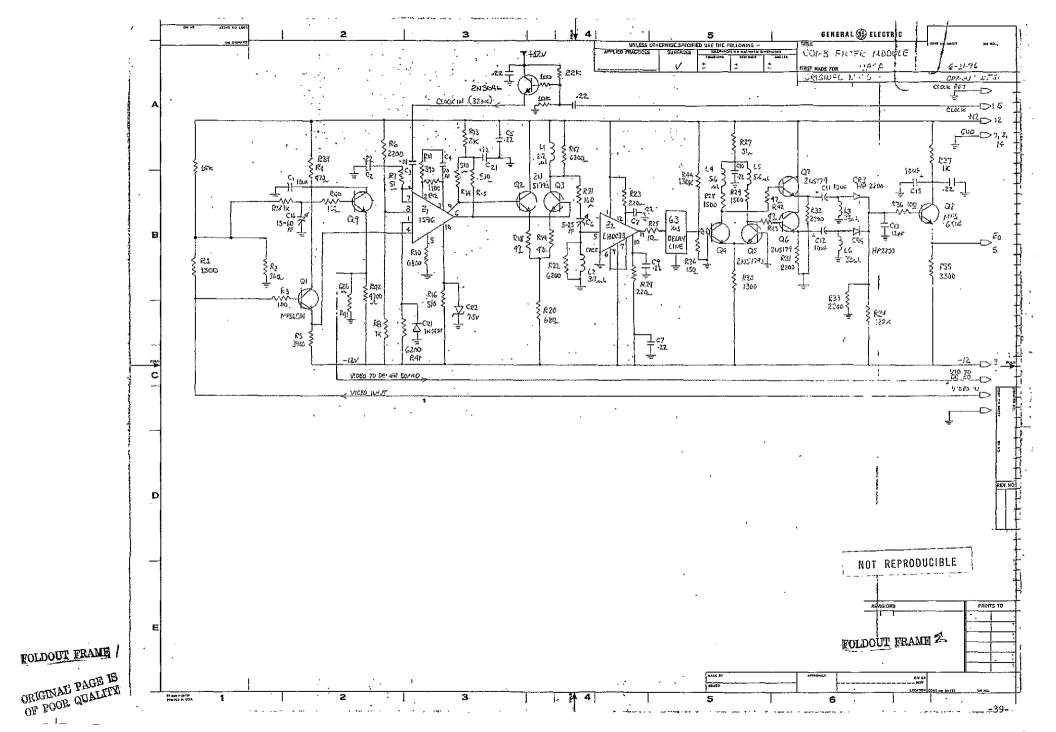

| 4.2       | Video Processor                         | .3  |

| 4.3       | Video Driver Board                      | 32  |

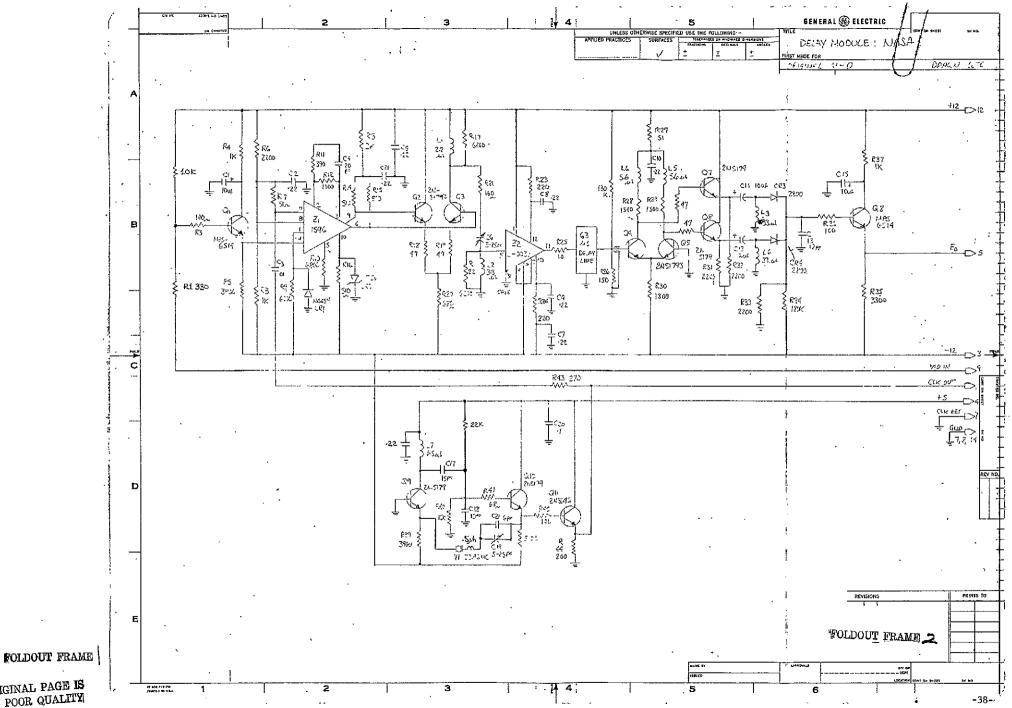

| 4.4       | Delay and Comb Filter Boards 3          | 35  |

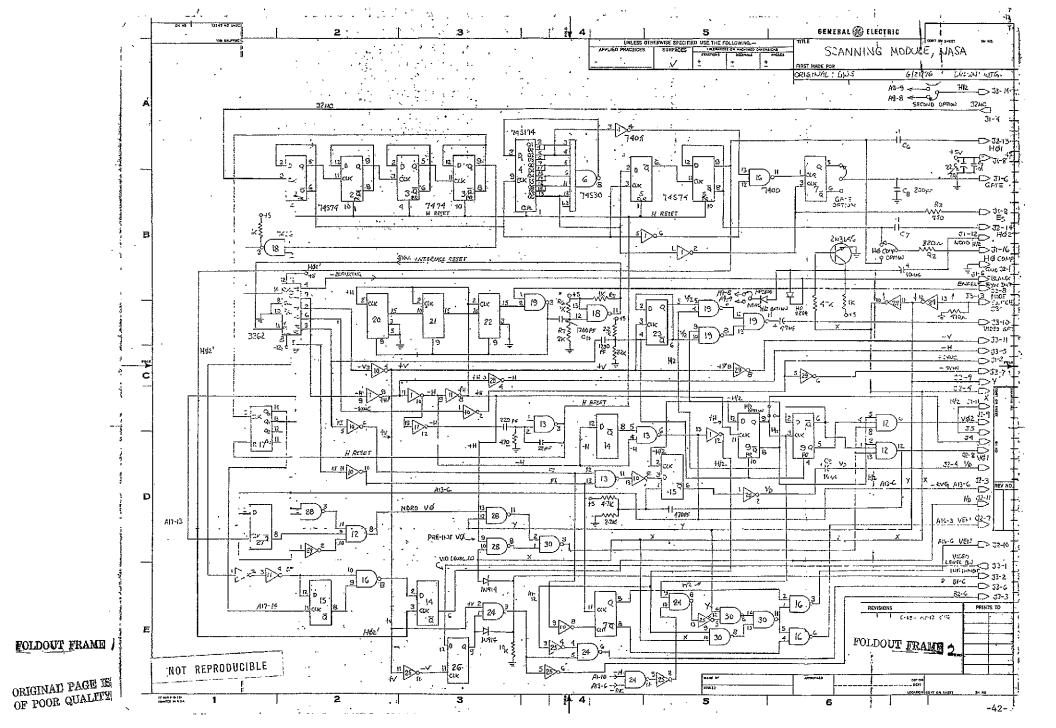

| 4.5       | Scanning Board 4                        | 0   |

| 4.6       | Auxiliary Interface and Array Boards 4  | -3  |

| 4.7       | Camera Power Supply                     | 7   |

| 4.8       | Thermoelectric Cooler                   | .9  |

| 5.0       | Controls and Their Function 5           | 51  |

| 6.0       | Predelivery Acceptance Test Procedure 6 | 0   |

| 6.1       | Camera Interfaces 6                     | 0   |

| 6.2       | Power Consumption 6                     | 1   |

| 6.3       | Output Video Format 6                   | 2   |

| 6.3.1     | Standard Load Impedance 6               | 2   |

| 6.3.2     | Composite Picture Signal Measurements 6 | 3   |

| 6.4       | Spots and Blemishes 6                   | 4   |

| 6.5       | Output Resolution 6                     | 5   |

| 6.6       | Operating Light Ranges 6                | 6   |

| 6.6.1     | Grav Scale Response                     | 6   |

## Table of Contents (contd)

| <u>Paragraph</u> | <u>Title</u> <u>Page</u>                 | No.         |

|------------------|------------------------------------------|-------------|

| 6.6.2            | Dynamic Light Range 67                   |             |

| 6.6.3            | Signal-to-Noise Ratio (S/N) 68           |             |

| 6.6.4            | Blooming                                 |             |

| 6.7              | Data Photos (1-20)                       | <b>-</b> 76 |

| 7.0              | New Directions for CID Camera Design 77  |             |

| 7.1              | Higher Resolution                        |             |

| 7.2              | Greater Sensitivity                      |             |

| 7.3              | Color Performance                        |             |

| 7.4              | Stereo                                   | ı           |

| 7 <b>.</b> 5 ,   | Smart Cameras                            |             |

| Appendix         | Charge Injection Device (CID) Concept 82 | -92         |

#### 1.0 Purpose

#### 1.1 Objective

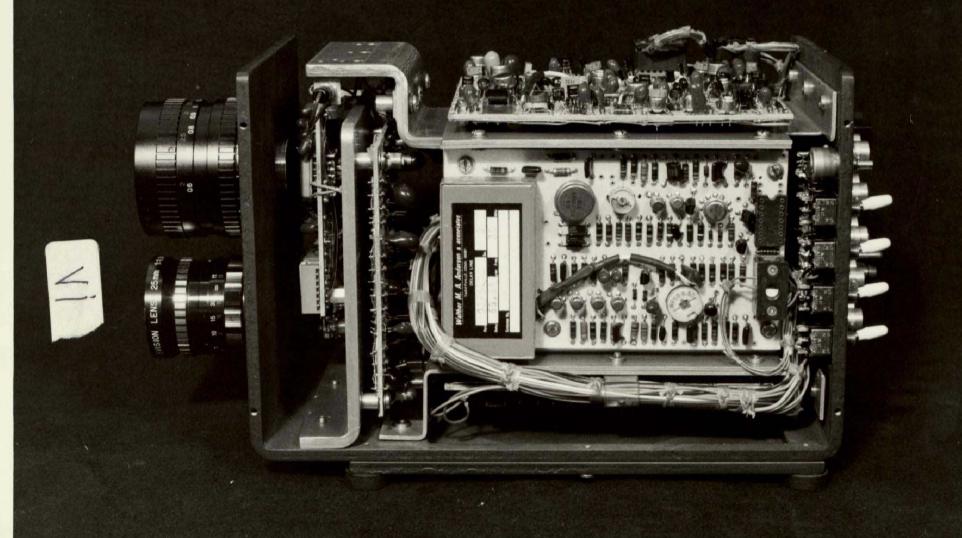

The objective of this Final Report is to summarize, in a detailed manner the effort required to perform the engineering design, development and test of a totally solid-state television camera.

#### 1.2 End Product

The end product of this contractual effort is a solid state television camera which uses a CID (Charge Injection Device) as the image sensor. The camera employs scanning techniques which allow the CID to be used with conventional monitor displays meeting EIA standards. A number of significant options have been incorporated in the product design to facilitate experimental study of CID camera technology.

## 2.0 Scope

General Electric has provided the necessary resources to perform engineering design, development and test of a solid state television camera using a CID for the image sensor. A large number of diverse tasks were performed in building the end product. A study of scanning techniques and subsequent experimental evaluation resulted in the choice of the two present CID camera scanning modes, normal RS170 and synthetic interlace. A study of readout alternatives and their experimental evaluation resulted in the choice of two selectable readout modes, normal pre-inject, and NDRO. A thermoelectric cooler study initiated in support of the NDRO readout mode, resulted in the incorporation of a thermoelectric cooler, heatsink and nitrogen purging capability. Investigations, which had occurred during the progress of an in-house program running parallel to this effort, resulted in the valuable addition of a comb filter option. In an effort to provide as much versatility as reasonably possible, several video and digital interfaces were made available externally. A detailed discussion of the work performed is described in Section 3 of this report.

## 3.0 Technical Requirements

## 3.1 Study, Design and Development Requirements

Purpose: To study, design and develop a number of alternate approaches and concepts that are applicable to the design of a CID camera having state-of-the-art performance.

Scope: To perform engineering study, design and development the areas of CID array size, camera scanning techniques, readout modes and video processing.

#### Performance:

- 1. Evaluated various array sizes for state-of-the-art resolution and reasonable availability consistent with the timing of the program. A 244 line x 248 array was chosen for use in the camera.

- 2. Evaluated several scanning schemes in an effort to find techniques which provide video lines in proper vertical sequence. The difficulty being to both satisfy the readout constraints imposed by the pattern noise rejection techniques utilized in CID video processing, and to meet the video output specifications imposed by EIA standards. As a compromise, two scanning schemes were provided, individually selectable via switching on the rear panel of the camera. The "normal" scanning mode is one which has greater vertical aberration however supplying the full compliment of lines (none blanked) and satisfying EIA standards for total number of lines (525 with 488 being visable) and interlace. The "synthetic interlace" mode (outerlace) provides fully sequential video information, however, supplies only 244 visable vertical lines per frame (every other line is blanked), and non-interlaced fields. An additional video processor was added, a comb filter, which corrects to some extent the vertical distortion incurred during the "normal" scanning mode. This scheme also augments pattern noise rejection as an additional benefit.

- 3. Evaluated various readout modes for the CID imager from the standpoint of providing a maximum of versatility for a reasonable amount of hardware. Two readout modes, the normal "pre-inject" mode

and the NDRO (Non Destruct Readout) were provided, individually selectable via rear panel switches. The pre-inject mode has the best signal to pattern noise ratio of any of the studied CID readout schemes, however, it has a conventional fixed 33 millisecond optical integration time for each element.

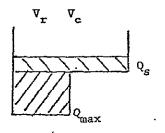

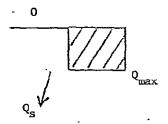

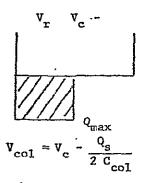

The NDRO mode provides for a variable amount of optical integration time (up to several seconds) while maintaining a continuous readout of the image signal charges being accumulated by the CTD at standard TV video rates. The incorporation of this mode was augmented by the addition of three significant hardware elements, a thermo-electric cooler, video threshold detector, and AGC. The thermo-electric cooler is used to cool the CID, thus maintaining dark current integration at a reasonably low value during the three second maximum integration period. Thermal electric cooling involved a thermal design study and an iterative mechanical design to achieve a compromise between dark current levels (proportional to CID temperature) and the size and weight of the camera package. The video threshold detector determines when the accumulated signal charge is near saturation in the array and subsequently injects that charge starting a new integration period. (The threshold detector can be bypassed and a manual inject signal via a rear panel BNC connector can be utilized to control injection). The video AGC is utilized to maintain a constant video envelope. (peak to peak video swing during the scene integration/readout time.) (Note: The AGC can be used for both readout modes).

## 3.2 Scanning Technique

## 3.2.1 Resolution

Purpose: To develop a CID camera which simulates the resolution required by the EIA standards. To maximize the resolution available from the CID array.

Scope: To utilize various scanning and video processing techniques that significantly enhance the resolution of the CID array limited by reasonable hardware size.

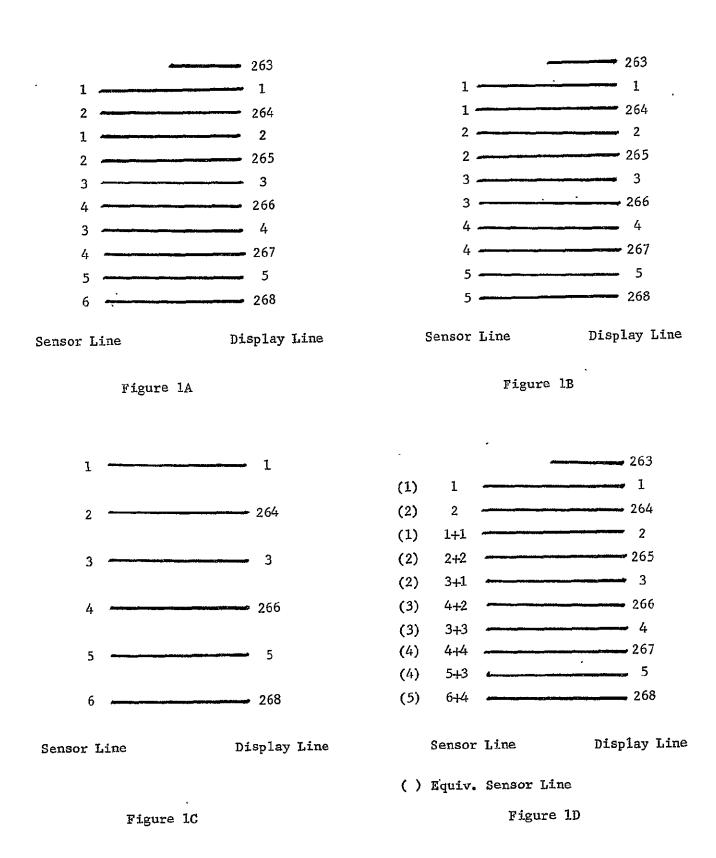

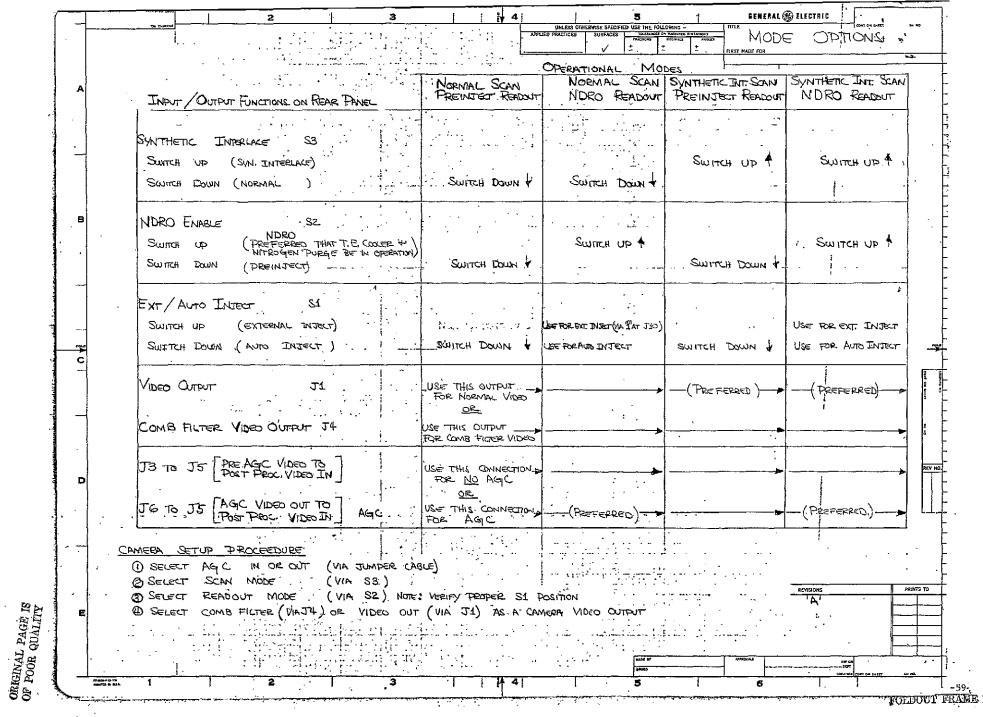

Performance: Two selectable scanning modes are provided by the camera, "normal" and "synthetic interlace". A switch (S3), on the rear panel of the camera is used to determine which is used by the camera, the "normal" scanning mode produces the vertical scanning sequence as described by Figure 1A. The out of sequence line format for this mode comes about by the use of redundant data (which is available from the pattern noise rejection circuitry) for every other line in each field in combination with the standard interlaced TV display format. One would prefer to use a scheme (assuming a 244 line CID) which produced the vertical scanning sequence as described by Figure 1B. It is not practical to achieve this at the present time as evidenced in the results of our preliminary study. The practical alternate to this is the synthetic interlace mode (outerlace) which has the scanning sequence as in Figure 1C. Simply put, this mode is accomplished by elimination of the interlaced TV format (by not allowing the extra 1/2 line/field to occur) and by blanking out the out of sequence redundant information which is available from the pattern noise rejection circuitry. The result is a sequential presentation with no loss of unique video lines , information (244 unique visable lines available/frame) and direct compatibility with standard TV monitors. For the "normal" scanning mode, video processing by the comb filter changes the video line sequence to that shown in Figure 1D. The effect on the "normal" scanning mode is that of interpolation and smoothness of the video information vertically from line to line. This results in a more subtle vertical aberration along with, as an added benefit, better pattern noise rejection.

#### 3.2.2 Formatting

Purpose: To maintain EIA video standards assuring that the camera will be compatible with conventional TV monitors and video transmission characteristics.

Scope: To develop camera modes and circuitry with the intent of meeting EIA video standards for sync and video levels, interlacing, and scan rates.

Performance: The camera accomplishes the intent outlined in "scope" taking a small liberty in the way in which the sequential scan mode is accomplished. This particular mode poses no problem in compatibility with conventional equipment (.1% change in scanning frequency).

### 3.3 Design

#### 3.3.1 · Resolution

Purpose: To specify minimum resolution requirement for the CID matrix and to assure that EIA standards are met.

Scope: To maintain a nominal array size no smaller than 250x250 elements. To maintain compatibility of synthesized lines with EIA positive interlace format.

Performance: An array size of 244 lines x 248 elements/line was chosen as the only reasonable alternative which could meet or exceed the minimum nominal requirement of 250x250 elements. This array selection resulted from a best fit between required resolution, array availability and baseline circuit design availability. The EIA positive interlace format is met where possible, the intent of this standard (i.e. compatibility) being met for all modes of the camera.

## 3.3.2 Interlace Ratio

Purpose: To assure interlace compatibility.

Scope: Specify interlace ratio of 2 to 1.

Performance: Interlace ratio is 2 to 1 with the exceptions as outlined previously.

#### 3.3.3 Aspect Ratio

Purpose/Scope: Specify an aspect ratio of 4 horizontally by 3 vertically.

Performance: The 244x248 CID array is designed with and provides an aspect ratio of 4 horizontally by 3 vertically.

## 3.3.4 Vertical Scan

Purpose/Scope: To specify that the vertical scan be nominal - 60 fields/second, 30 frames/second, and 525 lines/frame.

Performance: The vertical scan is nominal - 60 fields/second, 30 frames/second, and 525 lines/frame. A minor exception being the "sequential" scan mode where there are 524 lines/field.

## 3.3.5 Operating Light Ranges

#### 3.3.5.1 Gray Scale Response

Purpose: To define the camera's ability to resolve scene contrast ratio and generate a proportional voltage to display same on a television monitor.

Scope: When the camera is activated under nominal conditions and a logarithmic gray scale with 10 steps (32:1 contrast ratio) is imaged onto the sensor faceplate with a highlight illumination as indicated below (via a standard reflectance-type gray scale chart), the camera shall resolve the 10 steps when its output is displayed on a suitable television monitor and shall exhibit a signal/noise ratio as defined in Section 3.3.11 and is indicated below:

| Camera        | Highlight<br>Illumination<br>(faceplate) | S/N R<br>(rand | atio<br>om noise) | (fixed | S/N Ratio<br>(fixed<br>pattern noise) |  |

|---------------|------------------------------------------|----------------|-------------------|--------|---------------------------------------|--|

|               |                                          | Min            | Design<br>_Goal   | Min    | Design<br>Goal                        |  |

| 244x248 Array | 0.13 ft-c*                               | 38db           | 48db              | 33db   | 43db                                  |  |

The illumination source shall be a standard tungsten lamp at 2854 K color temperature. \*The highlight illumination shown corresponds to 1/2 the amount required for array saturation.

#### Performance:

| Readout Mode      | S/N Ratio<br>(Random Noise) | S/N Ratio (Fixed<br>Pattern Noise) |

|-------------------|-----------------------------|------------------------------------|

| Normal pre-inject | 39.6 db                     | 33.6 db                            |

| NDRO              | > 30 db                     | 32 db                              |

(Commentary on comparisons between specified and achieved. Great difficulty in making accurate NDRO measurements).

## 3.3.5.2 Dynamic Light Range

Purpose: To define the camera's ability to respond to varying light levels with a fixed lens iris setting. It must still retain the ability to resolve the 10 logarithmic gray scale steps (as described in 3.3.5.1) when the camera output is displayed on a suitable television monitor, over a range of illumination levels.

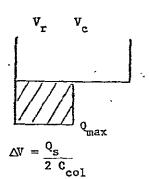

Scope: The test procedure is defined to be: 1) adjust lens iris setting to obtain maximum signal/noise ratio without exceeding array saturation; i.e., the highlight illumination reflected from the gray scale chart shall be within 10% of array saturation; 2) adjust lens iris setting until the 2 blackest shades of the 10 step gray-scale chart are no longer resolved on the monitor display (camera AGC functions to maintain constant signal output over this range); 3) calculate dynamic light range from the relationship:

Dynamic Light Range =

$$\frac{f\# \text{ (loss of }}{f\# \text{ (saturation)}}$$

Dynamic Light Range specifications are as follows:

|               | <u>Dynamic</u> | Light Range |

|---------------|----------------|-------------|

| Camera        | Min.           | Des.Goal    |

| 244x248 Array | ".7 <b>:</b> 1 | 14:1        |

This specification may be interpreted to mean that as a minimum, one can always adjust the lens iris one f stop in either direction without losing the ability to resolve any of the 10 logarithmic gray shades (with proper light level adjustment for nominal operating conditions).

Performance:

| Camera            | Dynamic Light | Dynamic Light Range |  |  |

|-------------------|---------------|---------------------|--|--|

| Normal pre-inject | 30.25:1       | (F4-F22)            |  |  |

(Commentary on comparisons between specified and achieved).

(AGC performed extremely well - refer to photos 8 through 15).

## 3.3.6. Operating Voltage

Purpose: To assure primary power capability. To assure I/O control logic compatibility.

Scope: The camera shall operate with a nominal input voltage that is buffered such that standard TTL logic drive circuits can be interfaced with the CID sensor electronics.

The camera circuits shall be so isolated as to prevent noise from the power line or other circuits from appearing on the video output.

Performance: The primary power requirements for the camera and associated thermoelectric cooler power supply are nominal 115V AC 50/60 Hz. Electronic regulation is used to derive DC voltages used to power electronic devices internal to the camera. The distribution lines are additionally bypassed at each circuit card within the camera electronics assembly. Each circuit card has a ground plane in close proximity to its bottom side.

## 3.3.7 Power Consumption

Purpose/Scope: The design of this camera shall be such that power consumption shall be minimized.

Performance: (see 6.2)

| Voltage                                       | Power (watts) |

|-----------------------------------------------|---------------|

| 115V AC Primary input to camera 50/60 Hz      | 27            |

| 115V AC Primary input TE cooler P.S. 50.60 Hz | <u>≈20</u>    |

| +12V DC Camera electronics                    | 4.5           |

| -12V DC Camera eléctronics                    | 4.2           |

| +5V DC Camera electronics                     | 3.3           |

## 3.3.8 Output Video Format

Sections 3.3.8.1 through 3 define the standard output video load impedance, composite picture signal, polarity, and signal levels required by EIA television broadcast standards. The current 244x188 prototype camera meets all these standards, and the proposed cameras will not deviate from them other than in the area of

Sync Signal Waveform (3.3.8.3). The timing relationships of the sync signals will depend upon the choice of scan format developed during the course of this program. There could be slight deviations from the RS-170 Standards; however, the deviations will not be sufficient to result in incompatibility with conventional TV monitors and transmission characteristics.

#### 3.3.8.1 Standard Load Impedance

Purpose: To define and specify the video output impedance of the camera.

Scope: The standard load impedance is defined as the complex ratio of voltage to current in a two-terminal network, expressed in ohms. The output impedance shall be 75 ohms <u>+5%</u> over the frequency range of the camera and shall be connected for single-ended operation.

Performance: The measured impedance = 72.0 at J1, 75.6 at J4

#### 3.3.8.2 Composite Picture Signal

The composite picture signal is the signal which results from combining a blanked picture signal (the result of the scanning process) with the synchronizing (sync) signal.

#### 3.3.7.2.1 Polarity

Purpose/Scope: The picture signal polarity is defined as the sense of the potential of a portion of the signal representing a dark area of a scene relative to the potential of a portion of the signal representing a light area. Polarity of the composite is thus stated as "black-negative" or "black-positive". The standard polarity of the output of the camera shall be black-negative.

Performance: The camera is black-negative.

## 3.3.8.2.2 Signal Levels

Purpose/Scope: The levels of the composite picture signal shall be defined in terms of Institute of Radio Engineers (IRE) units. Reference white level shall be +100 IRE units; blanking level shall be 0 IRE units; sync level shall be -40 IRE units.

Thus, the peak-to-peak level of signal extending from reference. white to sync tip shall be 140 IRE units.

The subject level shall be measured by means of an oscilloscope capable of measuring such a signal with the accuracy of  $\pm$  2% of the actual value over the voltage range of -0.5 to +1.5 volts. Some means of calibration shall be provided so that signal level measurements can be made in volts as well as in IRE units.

Measurements of signal levels shall be made in accordance with appropriate portions of 58 IRE 23.51 IRE Standards on Television: Measurement of Luminance Signal Levels, 1958, or latest revision thereof.

Performance: Composite picture levels 138 at J1, 142 at J4 IRE units/volts (see 6.3.2)

#### 3.3.8.3 Sync Signal Waveform

The timing relationships of the sync signals shall depend upon the choice of scan format developed during this program as discussed above. Slight deviations from the RS-170 standard in the area of syn sync signal waveform are acceptable; however, these deviations shall not be sufficient to result in incompatability with conventional TV monitors and transmission characteristics.

## 3.3.9 Output Resolution Response

Purpose/Scope: In television systems, a measure of ability to delineate picture detail is resolution expressed in terms of the maximum number of TV lines (alternate black and white lines) per picture height discriminated on a standard test chart. The ratio of (1) the peak-to-peak signal amplitude, given by a test pattern consisting of alternate black and white bars corresponding to a specified line number (resolution), to (2) the peak-to-peak signal amplitude, given by large area blacks and large area whites having eh same luminance as the test pattern, is defined as the resolution response.

The methods of measurement shall be as specified in Institute of Electrical and Electronic Engineers (IEEE) 208, 60 IRE 23.52, Standards on Video Techniques: Measurement of Resolution of Camera

Systems, 1961 or latest revision thereof, be used. For the measurement of resolution response, the picture signal shall be applied to a picture monitor properly adjusted per the IEEE standard above. The limiting horizontal and vertical resolution response is determined by observing the point at which the individual lines of the graduated wedges are no longer distinguishable as separately defined images.

The horizontal resolution response shall not be degraded by the video processing chain of the camera systems, at least to an upper limit defined by the number of CID elements. The limiting resolution shall be no less than 70% of the number of TV elements - for example, for a camera system employing 250 horizontal elements, the limiting resolution shall be better than 175 TV lines per picture width.

Performance: Limiting resolution >175 elements. (See 6.5)

## 3.3.10 Output Video Voltage (Unblanked) .

Purpose/Scope: The composite picture signal, as measured from the sync tip to reference white level across the standard load impedance (see Section 3.3.8.1), shall be nominally 1 volt peak-topeak with the following component signal levels and tolerances comprising the total signal level.

Performance: Composite picture signal .990 at J1, .960 at J4 (see 6.3.2)

#### 3.3.10.1 Blanked Output Video Voltage

Purpose/Scope: The blanked picture signal with setup (i.e., noncomposite), as measured from blanking level to reference white level, shall be 0.714 ±0.1 volt (nominally 100 IRE units).

Performance: .738 at J1, .705 at J4

#### 3.3.10.2 Synchronizing Signal

Purpose/Scope: The synchronizing signal, as measured from 0 voits dc shall be +0.286 +0.05 voits (nominally 40 IRE units).

Performance: .236 at J1, .240 at J4 (see 6.3.2).

#### 3.3.10.3 Setup Levels

Purpose/Scope: The standard setup shall be 7.5 ±5 IRE units as measured across the standard impedance from blanking level to reference black level.

Performance: 7.5

## 3.3.11 Signal-to-Noise Ratio S/N

Purpose: To determine the S/N for nominal camera operation (i.e., highlight illumination at 1/2 that required for array saturation) shall be as outlined below. S/N for temporal noise sources (random noise) shall be determined by measurement on an oscilloscope, at the camera output, (across the standard load impedance) of the peak-peak noncomposite picture signal voltage and the peak-peak random noise voltage. S/N is the ratio of peak-peak signal voltage to rms (\frac{peak-peak}{5.6}) random noise voltage. S/N for fixed pattern noise sources shall be determined by measurement on an oscilloscope, at the camera output, (across the standard load impedance) of the peak-peak noncomposite picture signal voltage and the peak-peak fixed-pattern noise voltage across any one selected line of video. S/N is the ratio of peak-peak signal voltage to peak-peak fixed pattern noise voltage.

Scope:

| •             | S/N (R: | andom Noise) | S/N (Fix | ed Pattern Noise) |

|---------------|---------|--------------|----------|-------------------|

| Camera        | Min.    | Des. Goal    | Min.     | Des. Goal         |

| 244x248 Array | 38ф     | 48dЪ         | 33dЪ     | 43 db             |

Performance:

| Camera Mode      | S/N (Random Noise) | S/N (Fix.Pat.Noise) |

|------------------|--------------------|---------------------|

| Normal Preinject | 3 <u>9.6</u> db    | <u>33.6</u> db      |

| NDRO · ·         | > <u>30</u> db     | >32db               |

## 3.3.12 Geometric Distortion

Purpose/Scope: The TV camera geometric distortion exclusive of the lens shall not exceed a displacement of any picture element from its true position in the object being viewed by more than +2% of the picture height within Zones 1 and 2 and ±5% of the picture height within Zone 3. For any increment of 5% of the picture height, the rate of change of displacement of any picture element shall not be greater than 0.5% of the picture height. Zone 1 shall be defined as the area within an inscribed circule centered within the scanned area, the diameter of which is one-half the picture height. Zone 2 shall be the area included within an inscribed circle centered within the scanned area with a diameter equal to the picture height, but excluding the area of Zone 1. Zone 3 shall be the remaining area of the scanned picture outside of or excluding Zones 1 and 2.

#### 3.3.13 Spots and Blemishes

Purpose/Scope: A spot or blemish shall be defined as a video signal transition of 7 IRE units or more in the output picture signal not present in the original scene, and which is the direct result of a sensor defect. The difference in sensitivity between any two adjacent CID elements in any direction shall be no more than 10%. Also, the difference in sensitivity from raster edge to edge (horizontally and vertically) shall be no more than 10%. No horizontal or vertical black lines resulting from a failed CID element shall be allowed. The size of a spot shall be determined by counting the number of scan lines on which the transition occurs; i.e., the number of lines per frame on which the transition is greater than 7 IRE units. The total of white and dark spots shall be less than or equal to:

10 spots ≤ 4 TV lines per frame

2 spots < 8 TV lines per frame.</pre>

To determine the presence of spots, smudges, etc., a uniform grey background shall be observed which is illuminated by light source(s) of the appropriate color temperature and of the intensity to allow nominal camera operation (i.e., S/N shall not be such that spots and blemishes are masked by noise). Any gain operation by the camera shall also be considered.

Performance: See photograph #7

# white spots 3 # black spots 6

## 3.3.14 Blooming

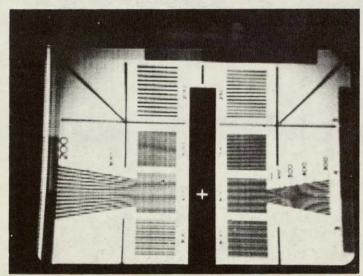

The solid-state image sensor is particularly susceptible to "blooming" - the spreading of an optical overload-generated charge into adjacent regions. The contractor shall propose various solutions to minimizing the blooming problem, incorporate the most acceptable solution into the camera, and include in the final report a detailed discussion of the solutions proposed and further work that may be done in this area.

Performance: See photographs #16 and #17

## 3.3.15 Camera Optics

Purpose/Scope: The camera shall be equipped with a lens with a fixed focal length between 25 mm and 50 mm with manual aperture and focus controls. The aperture control range shall be between f/2.2 to f/16 or better. The lens shall be mounted to the camera such that it will be interchangeable with other lenses. The lens shall be considered a part of the camera for all specifications herein. No development is intended in the optics area.

Performance: The camera has been equipped with two interchangeable lenses each optimized for a specific area of experimentation. A large F.85 to F11,25 mm lens is provided for experimentation at low light levels, especially suitable where the camera is operated in the NDRO readout mode. A small F1.9 to F22 lens is provided for experimentation at high light levels. The recessed objective of this lens makes it suitable in applications of extreme side light intensities such as produced from large areas of high reflectance scene material.

## 3.3.16 Camera Controls

The camera shall be equipped with external controls that are accessible to the operator. The controls shall be so located, positioned, and labeled with sufficient size and contrast to allow ease of reading and operation.

Performance: See outline drawing

# 3.3.17 Camera Interfaces

Purpose Scope: The camera shall include two connectors so as to facilitate the provision of camera power from one source and camera video to a standard commercial-type TV monitor. The contractor shall select the appropriate connectors to meet all the requirements of this specification. They shall be small with a minimum number of pins and and have a positive locking mechanism. Pin assignments are to be determined by the contractor.

Performance: A standard 115V AC chassis mount, 3 pronged male plug, J12, serves as the primary power input to the camera. All input and output signal interfaces are provided with standard female BNC chassis mount connectors (see 6.1).

#### 3.3.18 Non-Destruct Readout Mode

A non-destruct readout (NDRO) mode shall be provided such that a video output signal meeting with requirements of this specification shall be atainable for all scene integration times up to and including 3 seconds for scene highlight illuminations of 0.1 foot-candle or greater. A selectable capability shall be provided that will allow either automatic integration cutoff at saturation or continuous integration (the minimum S/N specification shall not apply for the latter). To achieve the necessary low noise level for proper NDRO mode operation, a thermoelectric cooling device shall be incorporated which shall maintain the CID operating temperature at  $0^{\circ}\text{C} \pm 5^{\circ}\text{C}$ .

Performance: A measured temperature of 40°C was obtained with the CID and cooler exposed to room temperature and humidity. Refer to 6.1 for electrical performance.

## 3.4 Prototype Development and Test

One prototype solid-state TV camera employing CID's as the image sensor which meets the design requirements of Section 3.3 shall be developed, tested and delivered to NASA/JSC.

Performance: Delivered 8/6/76.

## 3.5 Design Reviews

There shall be at least two (2) design reviews with the presentations to be held at the contractor site.

Performance: Design Review #1 - 12/75

Design Review #2 - 4/76

FOLDOUT FRAME 2\_17-

#### 4.0 Camera Operation

## 4.1 Preamplifier Board

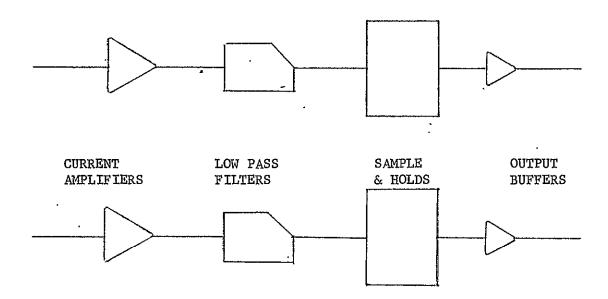

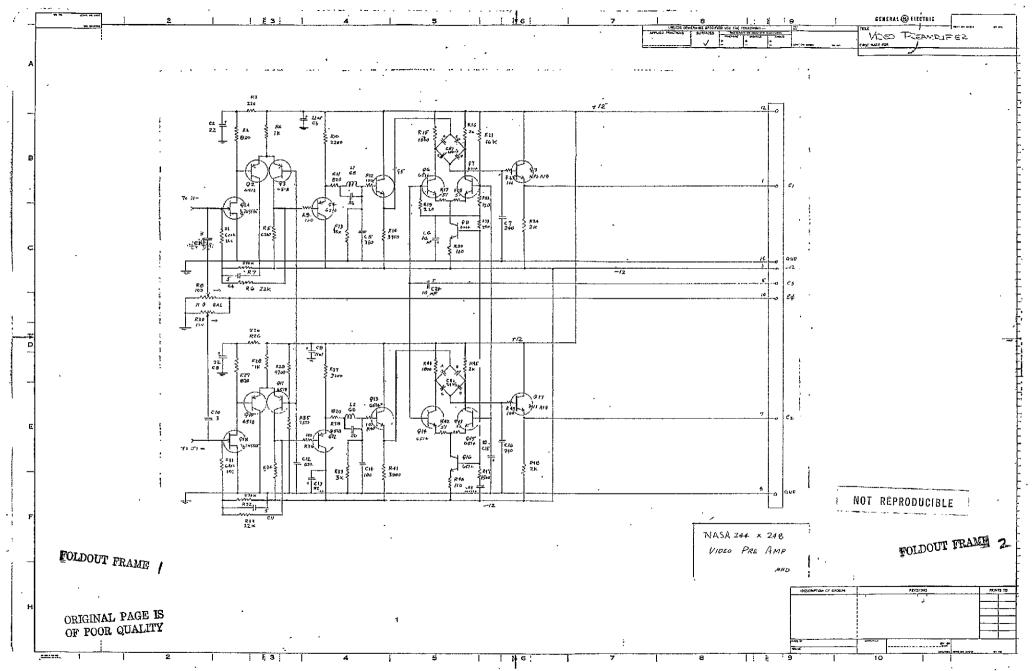

The preamplifier board contains two channels. One channel is connected to the "odd" columns of the array; the other to the "even" columns. Each channel is identical to the other. A pre-amp channel consists of a low-noise feedback type input stage, a filter section with buffers, and a sample-and-hold circuit. The input stage has a gain of approximately 0.67 V/ $\mu$ A. The equivalent RMS input noise is 0.62 nanoamps (measured with a 2 MC sharp-cutoff filter and a 39 pF capacitor to simulate the CID array capacitance).

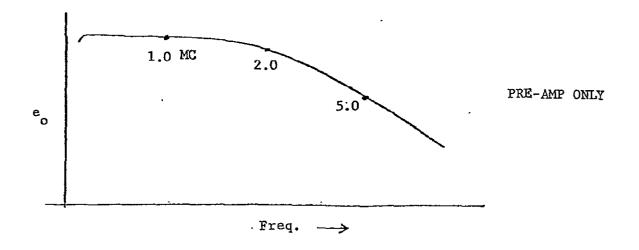

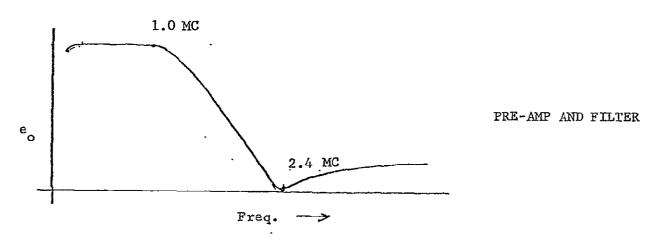

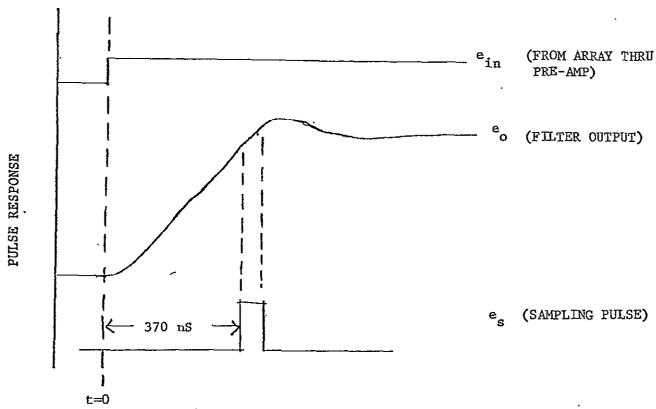

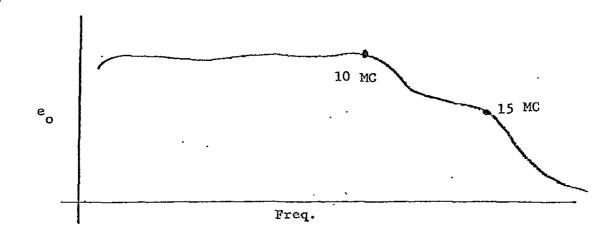

The input amplifier is followed by the filter section. Without this filter, the sampling wave at 2.3 MC will alias with noise voltages in the region of 2.3 MC and low frequency "difference" signals will appear in the output of the samples. These noise voltages, being low frequency, are very objectionable when viewed on a display monitor. To minimize this "conversion noise", a filter with the response shown in Figure 1 is used which has high attenuation at the sample frequency. As seen in Figure 1, a step wave passed through such a filter has rather slow rise time. It is necessary, therefore, to delay the sample pulse almost the full element period so that the full MTF of the CID can be realized.

The filter has about 10% overshoot but the time delay of the sampling pulse is chosen to occur as the signal is just passing through the 100% point. As a result, the overshoot is not reproduced in the sampled output.

The sampling circuit is designed to provide fast acquisition time (60 nanoseconds) and with minimum feedthrough of the sampling gate pulse. The feedthrough spikes are + 8 MV in amplitude and are about 10 nanoseconds wide. These spikes, although small to begin with, are filtered out by the 3 MC low-pass filter in the processor.

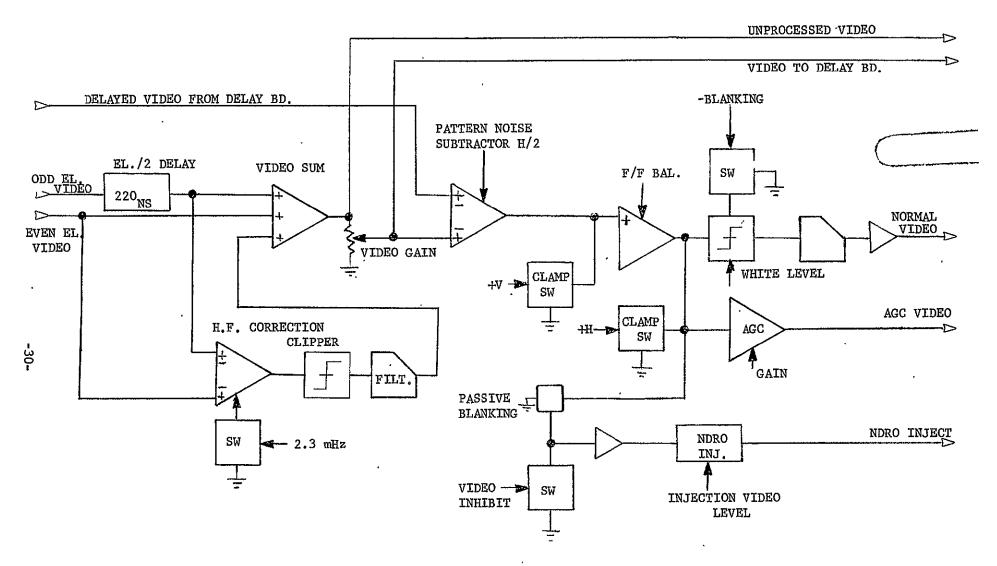

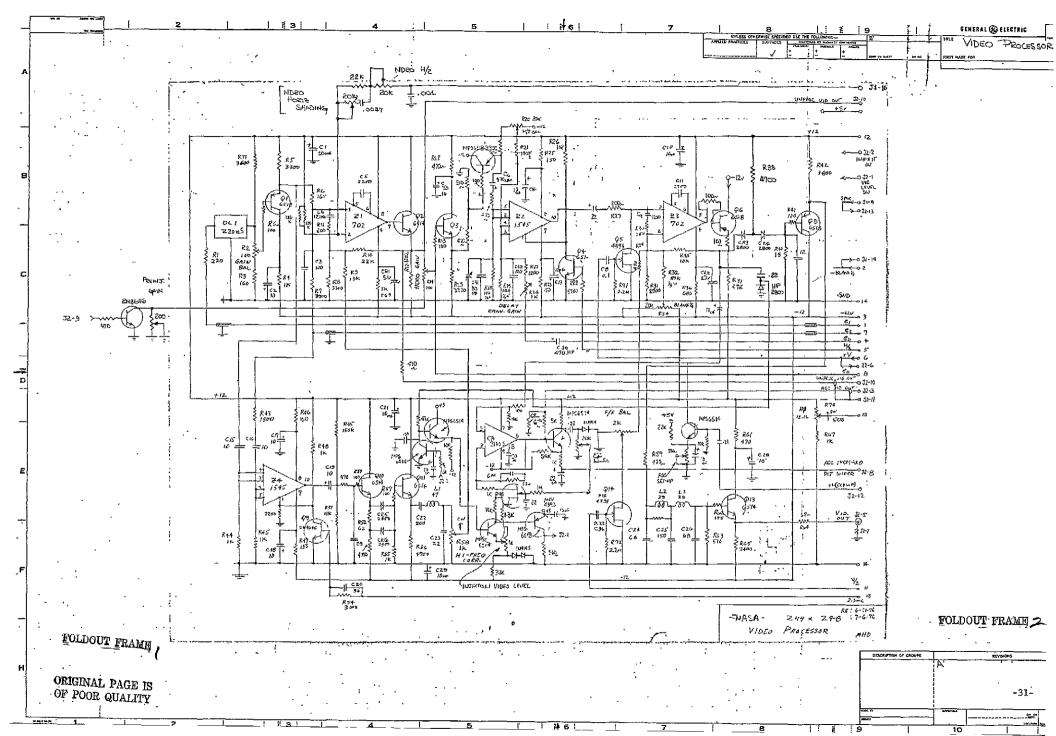

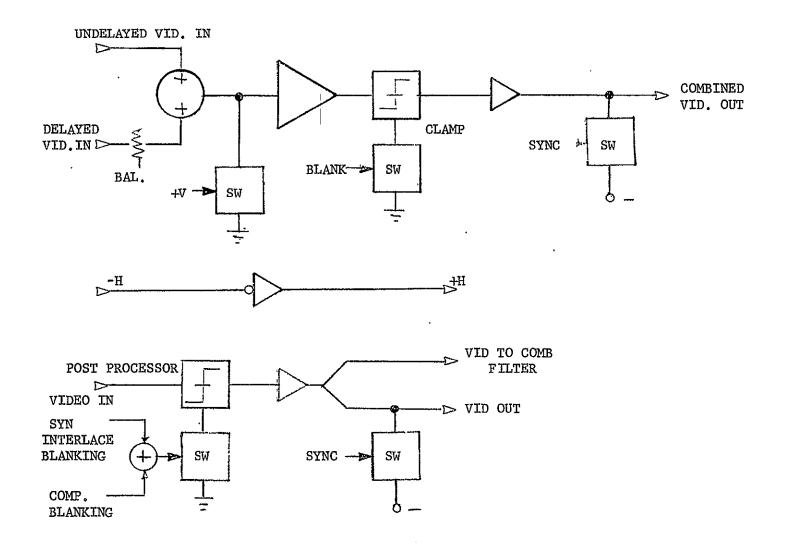

#### 4.2 Video Processor

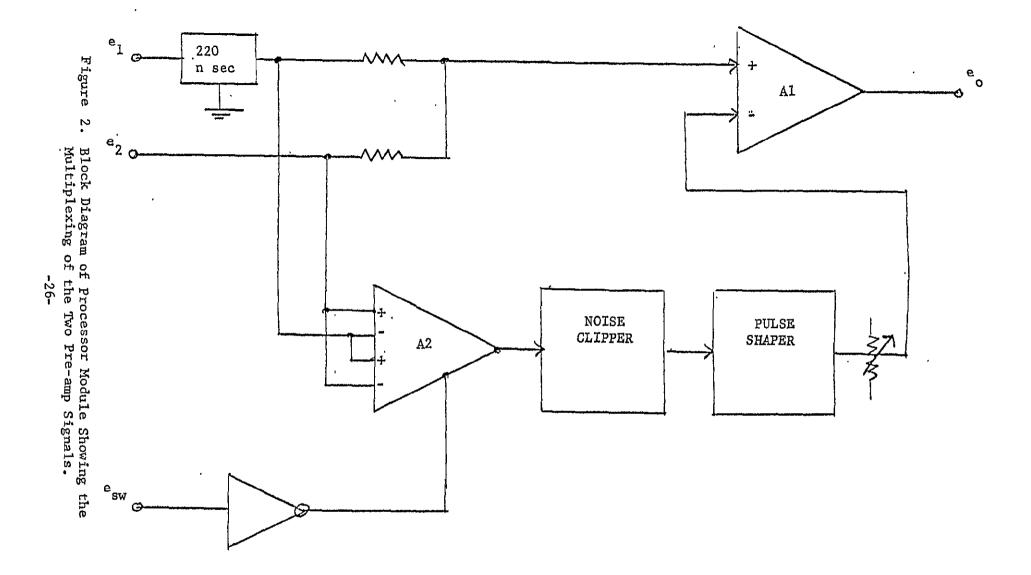

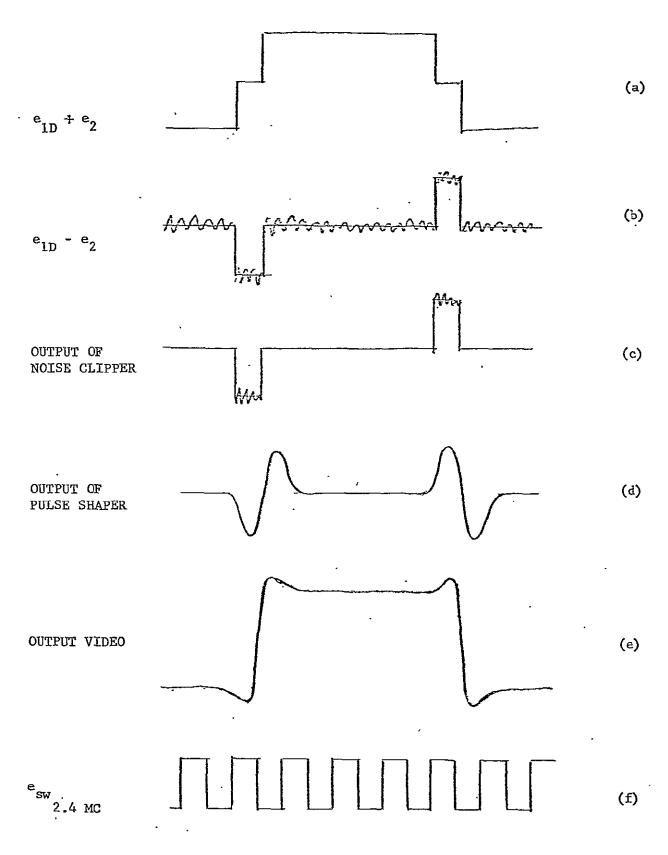

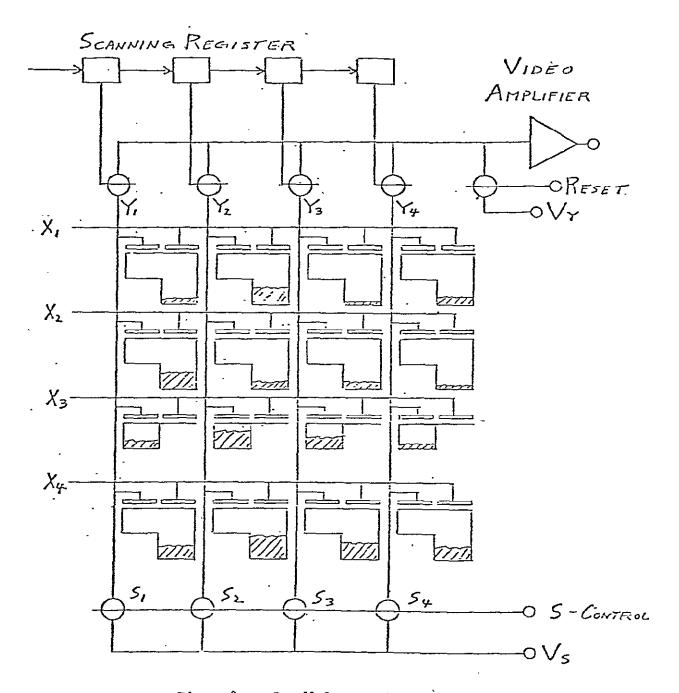

The two pre-amp signals e<sub>1</sub> and e<sub>2</sub> are fed to the processor module where they are multiplexed together in a way that provides the lowest possible noise. A block diagram is shown in Figure 2 and the signal waveforms in Figure 3. Signal e<sub>1</sub> is delayed for a 220 nanosecond delay line - the period of an element. This delayed signal, e<sub>1D</sub>, is then added to e<sub>2</sub> to form the signal shown in Figure 3a. The waveform used, indicates the output of a vertical white bar or window scene. The two singals add directly whereas the noise voltages, from 2 separate preamps, add inquadrature. The S/N of the combined signal is therefore 3 db better than each preamp by itself.

Referring again to Figure 2, e<sub>1D</sub> and e<sub>2</sub> are subtracted, yielding the waveform of 3b. In this case the low frequency video is cancelled leaving only edges or transitions as shown. Noise is not cancelled, however, so this "edge" signal is fed through a base-line clipper which removes the noise (random noise and pattern noise) except during edges or transitions (see Figure 3c). The result is that large flat areas of the TV image, where there is no detail, will have little or no added noise.

The wave of Figure 3c could be used directly to correct the rise time of 3a. Instead, additional pulse shaping with an R-L-C circuit forms the wave of 3d which is then added to 3a as shown. A pot controls the amount of correction and the picture may be slightly over-corrected if desired to optimize subjective sharpness in the final picture.

A 2.4 mc switching voltage, in phase with the sampling pulse, is required to keep the HF correction wave polarized properly when the image transition moves from an odd to an even column, or vice versa:

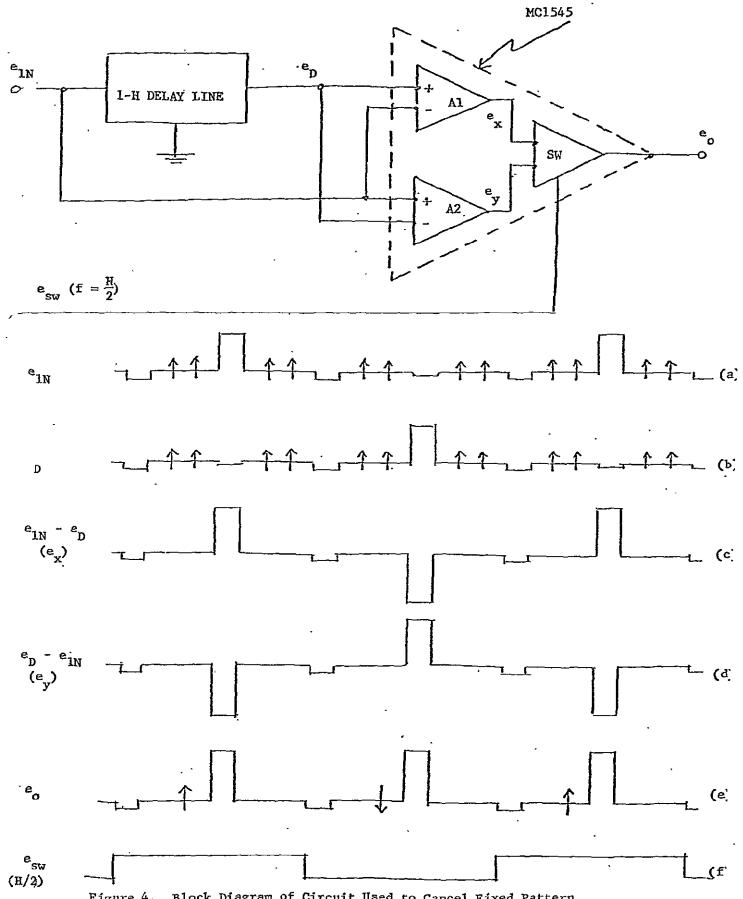

The combined signal of Figure 3e is amplified and routed to a 1-H delay circuit which is used to cancel pattern noise. A block

The video crosstalk term which appears with pre-inject readout is also cancelled by the delay line circuit.

diagram is shown in Figure 4 along with the pertinent waveforms. Each line of the imager is read twice. The first "read" contains the signal plus pattern noise as indicated by the arrows in Figure 4. The second read contains only pattern noise. The input signal is delayed by exactly one horizontal line period and is subtracted from the undelayed signal. Since the pattern noise is the same on each line, it is cancelled out. The video signal is not cancelled since it only appears on alternate lines. The delayed video at this point could be thrown away or, as in this case, inverted again and added to the real-time video as shown in Figure 4e. A subtle advantage of doing this is as follows: any residual pattern noise not completely cancelled by the delay line appears in opposite phase on alternate horizontal lines and provides additional optical cancellation of the pattern noise. This has been indicated by the single arrows of Figure 4e.

The remaining video processor functions are DC level setting via keyed clamps, video gain, blanking addition, blanking clipping, white level clipping, sync addition and a 75 ohm output for the normal video output. Additionally, three other functions are provided. An analog switch is employed to blank redundant video lines for the synthetic interlace scan mode. An AGC function is provided which, via back panel connections, can be used or bypassed for all modes. The mean value of the AGCed video signal may be controlled via the AGC threshold control, also located on the back panel. An NDRO inject circuit is provided to control image charge injection during the NDRO readout mode. It is essentially a video level detector which produces a logic "1" level when the average video level reaches a certain presettable value (on inject). When used, the AGC output from the video processor board is routed, via rear panel connections (J6 to J5), to the video driver board where white level clipping, blanking and sync addition is incorporated into the video waveform.

Figure 1. Response of Pre-amp With and Without Filter.

Figure 3. Waveforms in the Processor Module

Figure 4. Block Diagram of Circuit Used to Cancel Fixed Pattern Noise Along with Pertinent Waveforms.

DELAY CHANNEL FREQ RESPONSE

DIFFERENTIAL GAIN + PHASE TEST SIGNAL

Figure 5. Delay Channel Frequency Response.

VIDEO PROCESSOR BOARD

#### 4.3 Video Driver Board

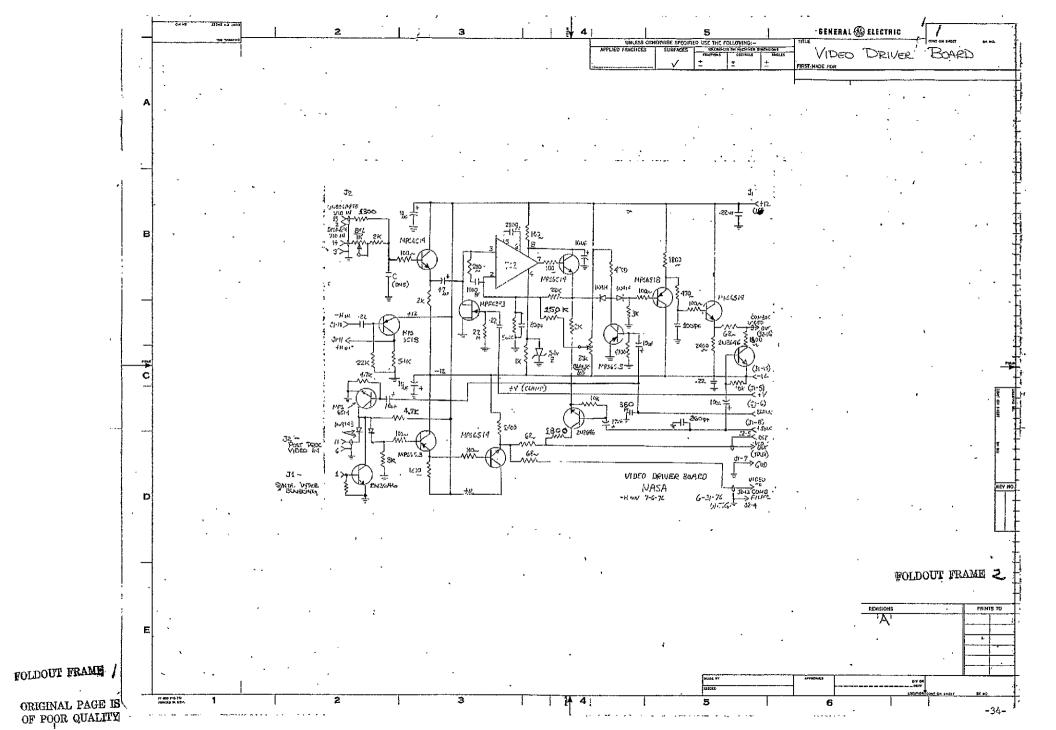

The video driver board has the functions of video buffering and comb filter processing. The two primary video output signals provided at the rear of the camera, J1 - "Video Out" and J4 - "Comb Filter Video Out", are buffered on this board.

Sync and blanking is incorporated into these waveforms along with a 75 OHM driver for each output. Also located on this board is a buffer for the video sent to the comb filter board. The comb filter processor operates by summing the 1H delayed video from the comb filter board with undelayed video, thereby adding together alternate video lines within each field. There are two benefits in using the comb filter. During the normal scanning mode of operation, it softens the vertical aberration due to out of sequence lines. This is due to the averaging function that occurs which smoothes and interpolates line information in a nearly proper sequence. The other benefit lies in the fact that the residual pattern noise not removed by the video processor has the characteristic of having opposite phase (180°) on alternate lines. When the alternate lines are summed together, this residual pattern noise is considerably reduced.

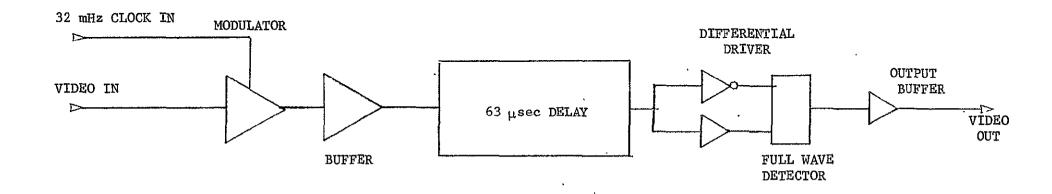

#### 4.4 Delay and Comb Filter Boards

The delay and comb filter boards are identical with the exception of the 32 MHz crystal oscillator which is contained on the delay board and not on the comb filter board. To achieve the performance necessary for good noise cancellation, the following requirements are critical:

Exact 1 H delay

Stable delay time

Faithful impulse response

Very low amplitude distortion (differential gain)

Very low differential phase distortion

Low self-generated random noise.

These requirements are most nearly fulfilled by a zero T. C. glass delay line. The video signal is AM modulated onto a 32 MC carrier which is generated by a crystal oscillator. This same frequency is divided down and used to generate the various voltages required to scan the CID. In this way, any possibility of beat-frequencies is eliminated.

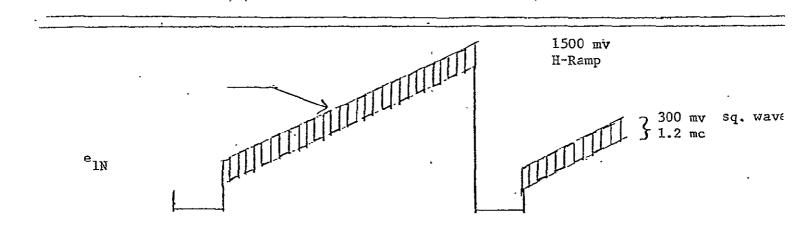

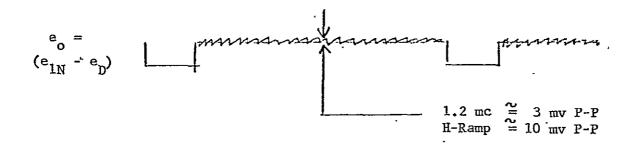

The modulated carrier is then amplified and fed to the delay line. The line has about 30 db of loss so that additional amplification is required before demodulation. The demodulator is a full-wave type using hot-carrier diodes. This circuit was found to have lower differential gain and phase distortion than some integrated circuit types. The response of the entire delay channel is shown in Figure 5. It is flat to 10 MC; down to less than 6 db at 16 MC. This response is considerably broader than the 2-1/2 or 3 MC needed for the video information. However, to faithfully reproduce the shape of the pattern noise, which is needed for maximum cancellation, a wide bandwidth is required. Figure 2 also protrays a differential gain and phase test signal similar to that used in standard television systems. In this case, the H-ramp simulates a low frequency

video signal which covers the full amplitude range. The 1.2 MC square wave, which is added to the ramp, simulates the pattern noise from the imager.

Such a signal was fed through the delayed channel and subtracted from the undelayed signal. The pattern noise cancellation over the entire amplitude range was 100:1. In earlier camera designs, this ratio was 15:1.

# COMB FILTER/\*DELAY BOARD

\*(DELAY BOARD CONTAINS CLOCK GENERATOR, BELOW, IN ADDITION TO ABOVE DELAY)

XTAL OSC. 32.760

ORIGINAL PAGE IS OF POOR QUALITY

## 4.5 Scanning Board

The scanning module consolidates circuitry used to generate scanning logic required by the CID imager, clamp, sample and other pulses required by the analog signal processing loop, and synchronizing and blanking pulses applicable to closed circuit TV systems.

Essentially, the scanning module consists of three sections:

- a) A counter and multiplex circuitry which generates the imager horizontal phase (Ø) pulses, processor loop sample pulses, a 2.4 MC switching voltage, and a 2 MC sync generator clock.

- b) The TV horizontal and vertical rate section, employing a 3262 ADC MOS sync generator chip and appropriate processing logic to produce imager H and V data pulses, vertical phase (0) pulses, vertical enable pulses, and a row load device gate signal as well as synchronizing, blanking, and field and line rate pulses required by the Camera Video Processing System.

- c) Assorted logic for performing readout and scanning mode changes, and for controlling injection during the NDRO mode.

- A) The counter section is comprised of devices A2, A3, A4, A5, A6, A7 and portions of A1 and A12. 32 MC clock pulses generated on the delay board are applied to cascaded sections of A2 and A3 (divide by 16). The resulting 2 MC square wave is applied to the sync generator chip (discussed later). A 16 MC square wave (clock divided by 2) is brought out from A2a and is applied to a divide by 7 counter consisting of A4, A5, and A6. The Q1 through Q6 outputs of A4, and the Q(7) output of A5 have a duration of 61 ns and are delayed from the previous Q output by a 61 ns period (see Figure 6). A6 multiplexes the outputs to derive a data pulse which resets the counter at the end of the 7th interval.

The Q7 output of the counter (2.4 MC) is applied to A5b (divide by 2) deriving the 1.2 MC square wave and its complement which become the HØ pulses. Note that counter output Q7 "times" the HØ interval (Figure 6). The Q6 output of the counter occurring at the end of the

HØ pulse, is inverted in Ala, becoming the system sample pulse. A7a, in conjunction with Alb, and Al, generates the 2.4 MC high frequency gate signal used in the video processor module. The sample pulse rise initiates the sync wave; the inverted output of Al2 which represents Q1-1/2, ends the period (see Figure 6).

B) The horizontal and vertical rate section of the scanning module processes various A8 (sync generator) outputs to obtain additional imager scanning pulses, and video processor signals.

Horizontal data pulses are obtained by sampling and delaying, at Al5 and Al4, a portion of the burst flag output of A8.

Vertical data pulses are obtained by sampling and delaying, at A15, a portion of the "ov'ed" field index outputs of A8 which are available at A13.

Vertical phase (0) pulses result from gating, at Al2, divided down horizontal drive pulses, A9, produced by A8.

Vertical enable pulses result from gating a field index counter, A7, with a multiplexed signal which is readout mode dependent. This multiplexed signal is a function of  $V\emptyset$ , H, and  $R_{VG}$ ,  $V\emptyset$  being readout mode dependent.

The  $R_{\mbox{VG}}$  pulse is derived from a sampled and delayed -H pulse available from A8.

Horizontal reset pulses required by various counter sections, are derived from differentiated and inverted horizontal drive pulses, 48, at Al3.

C) The A20, 21, 22 counter sections comprise a 262 line counter which is used to reset the sync generator A8 at the beginning of each field during the "synthetic interlace" scan mode. A19, 23 generate the video gate signal which is also required for the synthetic interlace scan mode. The purpose of this gate signal is to blank alternate (redundant but out of spatial sequence) video lines from each field. Even lines are blanked for field #1 and odd lines are blanked for field #2. A26, 24, 25 utilize the video level switch output from the video processor board to generate signals to control the injection of charge at the CID during the NDRO readout mode.

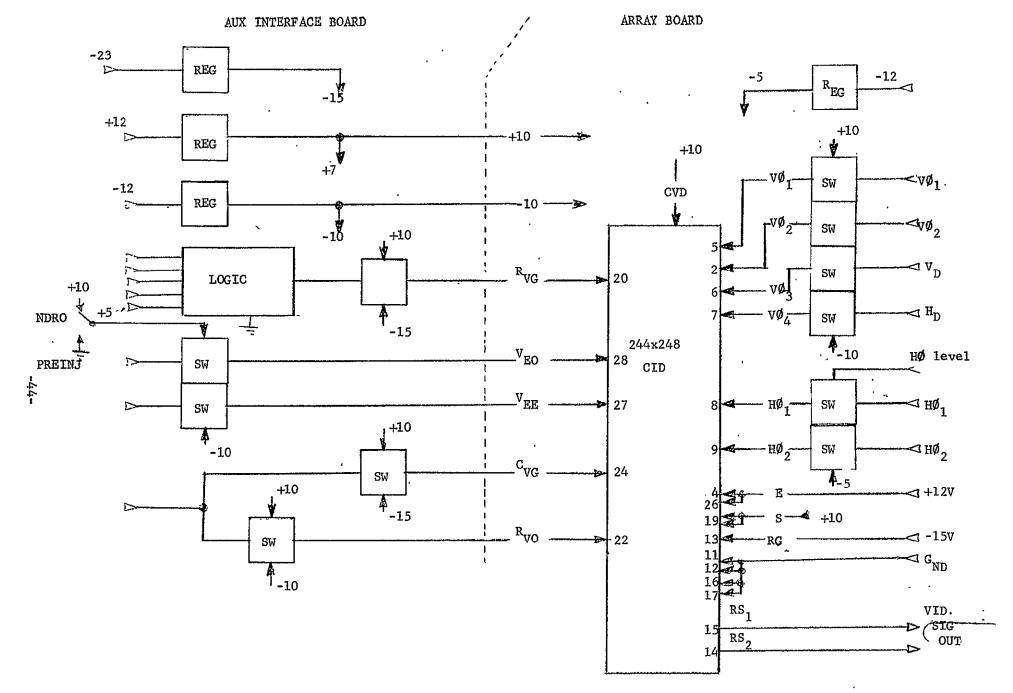

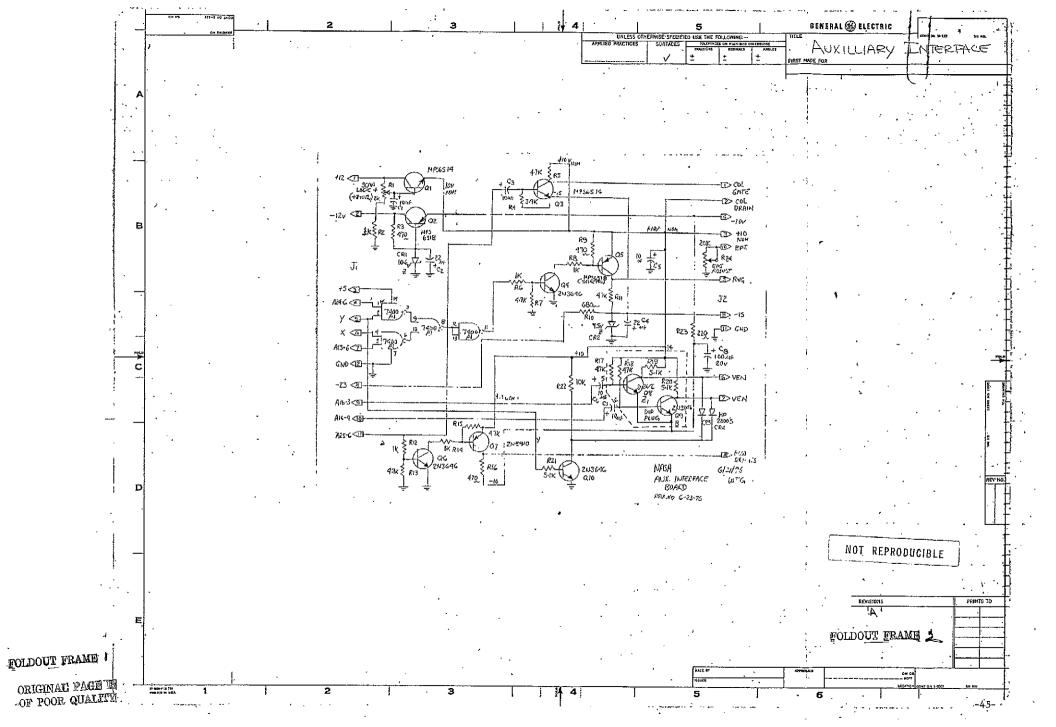

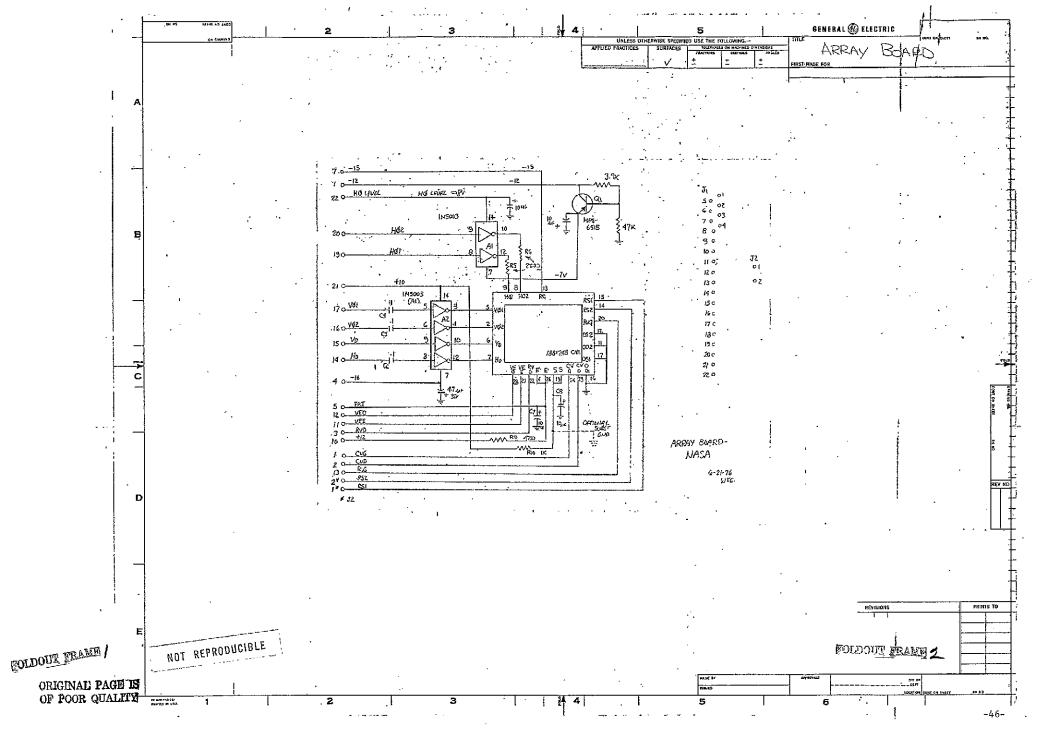

Figure 6. Auxiliary Interface and Array Boards

# 4:6 Auxiliary Interface and Array Boards

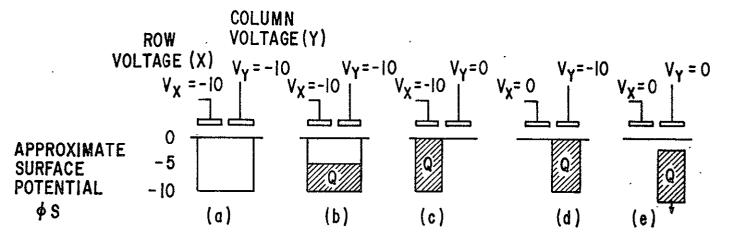

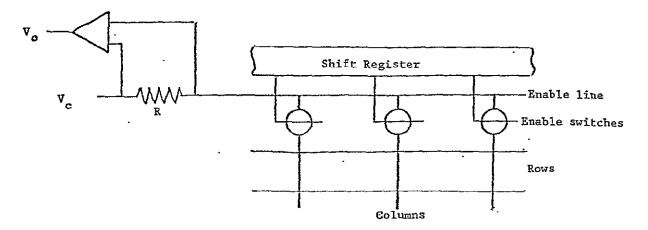

The CID array requires several DC and switching voltages to operate properly. The non-standard DC voltages (i.e., not directly available from the DC power supply) and the non TTL level, switching voltages are provided by the auxiliary and array boards. The array board also serves to provide mounting for the CID. Figure 6 describes the major functions performed on these boards and their relationship to the CID. It is important to note that the switches denoted SW on the diagram are essentially digital level translators. They accept standard TTL input signals and provide switching voltages that swing nearly to the limits of the DC voltages provided to them. In addition, the R<sub>VG</sub> generation, provided on the auxiliary interface board, takes into account the selected readout mode (preinject-NDRO). The required logic for readout mode switching is included on this board.

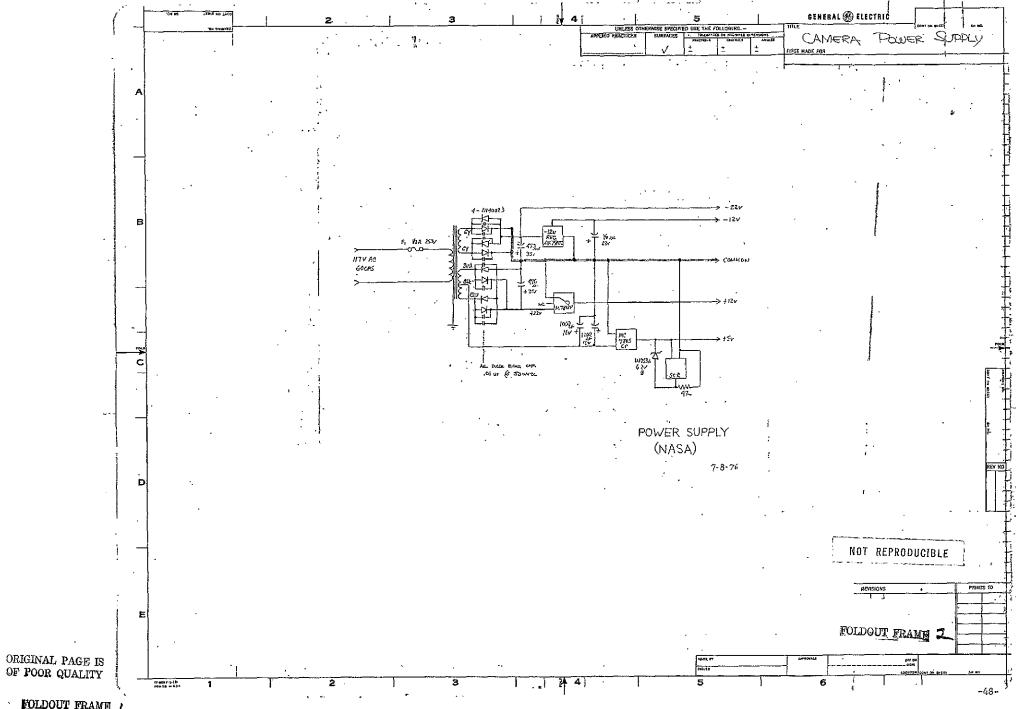

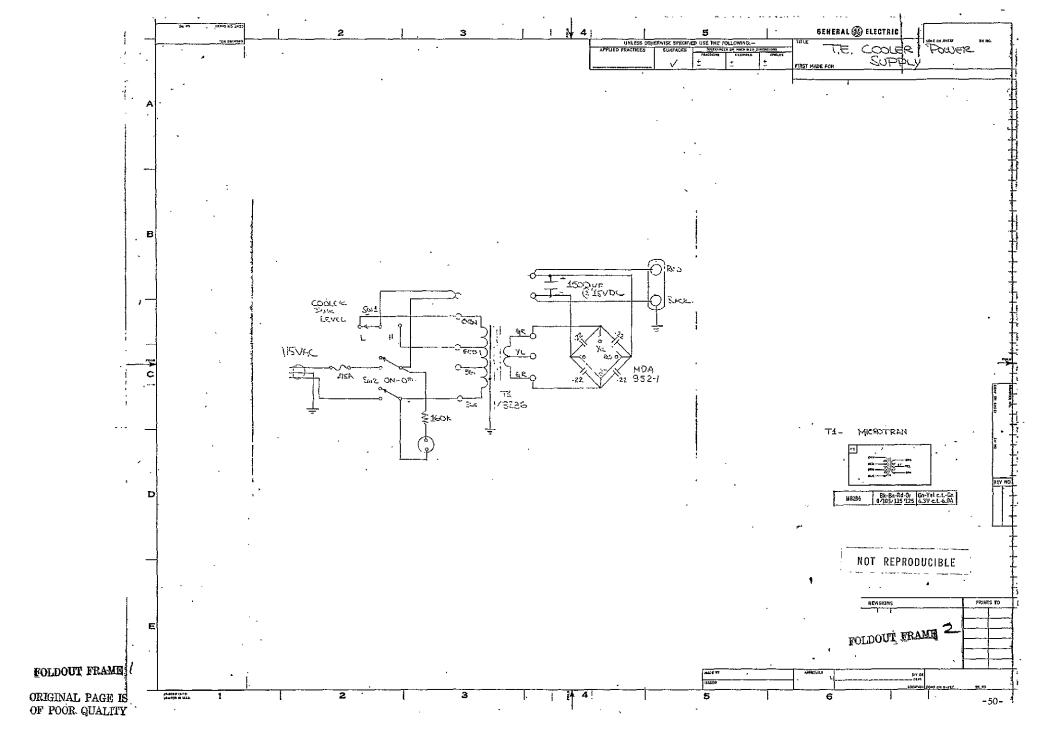

# 4.7 Camera Power Supply

The camera power supply is mounted internally to the camera. It supplies three regulated voltages, +12V (.25A), -12V (.25A) and +5V (1A). Regulation is performed by three series pass IC regulators mounted on a heat sink which is in thermal contact with the top cover of the camera. All regulated outputs are over current protected and in addition, the +5V output is over voltage protected. An unregulated +23V is also supplied. This voltage is subsequently regulated to -15V with a Zener diode on the auxiliary interface board.

#### 4.8 Thermoelectric Cooler

A provision is made for cooling the CID thermoelectrically for use in the NDRO readout mode. A two stage thermoelectric cooler (Nuclear Systems, Inc. 5HF2) is mounted to a heat sink plate which is in thermal contact with the bottom of the camera chassis (hot surface). The cold end of the cooler is in thermal contact with the back of the CID via an intermediary copper block cold finger. A separate thermoelectric cooler power supply is provided which connects to J11 on the rear of the camera. Proper polarity must be observed in this connection. A protective diode mounted on the T.E. cooler heat sink prevents inadvertent current flow in the wrong direction. The power supply has a high and a low power switch. The high switch position should be used only for rapid cooldown of the CID and subsequently, the unit should be placed in the low position for continuous running. It should be noted that it is extremely important that the heat sink be in good thermal contact with the camera chassis, i.e. thermal grease at this junction and fully tightened focus adjustment screws (which mechanically mount the heat sink to the camera chassis). Failure to note this may cause permanent damage to both the thermoelectric cooler and the CID. Additionally, it is important that a moderate rate of dry nitrogen flow be maintained into the "purge" connection while the camera is being thermoelectrically cooled. This will prevent excessive condensation in the area of the CID which will cause a slow but reversable deterioration in performance.

#### 5.0 Controls and Their Function

#### Video Processor:

HØ Level Controls positive excursion of HØ pulses and is

adjusted for minimum patterning consistent with

reliable horizontal scan.

Blanking: Controls "setup"; the level between the most positive

excursion of camera sync and the most negative (black)

video component.

F to F: (Field to Field) compensates where necessary for

differing array sensitivity field to field.

H/2: Compensates for line to line DC level variation.

Delay Channel Adjusts gain of the delay channel such that it matches Gain:

exactly that of the undelayed channel thus optimizing

pattern noise cancellation.

Delay Bal: Balances undelayed channel time delay such that it

matches exactly that of the delay line channel for

optimum pattern noise cancellation.

High Freq: Aperture corrects video signal to re-constitute

element rate MTF (may be adjusted to exceed 100%).

AGC Level: Controls DC feedback in the AGC loop. Control should

be, left in the fully CW position.

PI Gain: Sets processor gain when camera system is in the pre-

inject mode.

NDRO Gain: Sets processor gain when camera system is in the NDRO

mode. This control and the PI gain control tend to

interact.

Vid Lev SW

Th'1d:

(Video level switch threshold) controls integration time when camera is in the NDRO mode and determines the video level at which injection of the array occurs. Control is adjusted (when the cooler has

stabilized) such that array is injected just short of

•

saturation on low light level scene material.

Gain Bal: Compensates for possible pre-amp channel gain imbal-

ance. Control is adjusted for minimum element rate

patterning in scene highlight (PI mode).

NDRO H Shade: Compensates for possible horizontal shade due to dark

current effect in CID.

NDRO H/2: Compensates for H/2 offset characteristic of preamp

video in the NDRO mode.

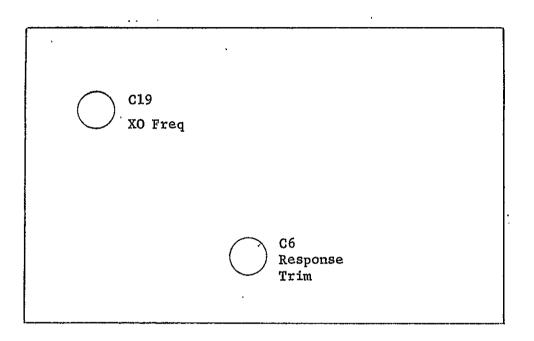

Delay Module:

XO Frequency: Allows for trimming crystal oscillator frequency.

Control is adjusted along with processor delay channel

gain and delay balance for minimum pattern noise.

Response Trim: Adjusts 1 H delay channel RF bandpass for optimum

response. (Sweep generator required).

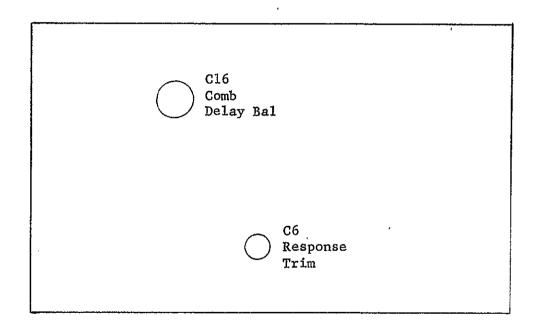

Comb Filter:

Comb Delay Bal: Trims undelayed channel time delay to match that of

of the 1 H delay channel.

Response Trim: Adjusts 1 H delay channel RF bandpass for optimum

response (sweep generator required).

Video Driver Board:

Comb Gain

Adjusts 1 H delayed channel gain such that it matches

Balance:

exactly that of the undelayed channel.

Comb Blanking: Controls setup in the comb filter video channel (see

video processor "blanking").

Video Preamp: .

HØ Comp

Compensates for HØ crosstalk in odd and even preamp

(R8, R30):

channels. Controls are adjusted for minimum

element/2 rate square wave at each preamp output.

Aux Interface:

Scan Logic: Controls positive excursion of scan logic. Control

is adjusted for nominal level of ≈ +7V.

Epi Adjust: Controls array epitaxial layer bias. Control is set

for epi level of  $\approx 8.1$ V.

DELAY MODULE CONTROL LOCATION

<sup>&#</sup>x27;COMB FILTER CONTROL LOCATION

| Comb<br>Gain Bal<br>R1 | 0 | Comb<br>Blanking<br>R2 |

|------------------------|---|------------------------|

|                        |   | ·<br>-                 |

|                        |   |                        |

| 0 | HØ<br>Comp<br>R8  |  |  |  |

|---|-------------------|--|--|--|

| 0 | HØ<br>Comp<br>R30 |  |  |  |

AUX; 'INTERFACE .

CONTROL LOCATION

## 6.0 Predelivery Acceptance Test Procedure

# 6.1 Camera Interfaces

The following outputs will be appropriately terminated and monitored by a scope to verify proper signal levels.

| Location | Description            | <u>Verified</u> |

|----------|------------------------|-----------------|

| J1       | Video Output           | x ´             |

| J2       | Undelayed Video        | . X             |

| J3       | Pre AGC Video          | Х .             |

| J4       | Comb. Filter Video Out | X               |

| Ј6       | AGC Video Out          | X               |

| J7       | -V (1 U.L.)            | X               |

| ј8 .     | -Sync (1 U.L.)         | X               |

| J9       | -H (1 U.L.)            | . X             |

The following input functions will be exercised to verify proper operation.

| Location | Description                | Verified |

|----------|----------------------------|----------|

| TE       | Dock Dungages Wides To     | v        |

| J5       | Post Processor Video In    | X        |

| J10      | External Inject            | X        |

| S1       | Ext/Auto Inject            | · X      |

| . S2     | NDRO Enable                | X        |

| S3       | Synthetic Interlace Enable | X        |

| S4       | Power                      | X        |

| R1       | Video Gain                 | X        |

# 6.2 Power Consumption

Camera power consumptions external and internal to unit:

| Nominal Voltage     | Description                     | Power (Watts)                                   |

|---------------------|---------------------------------|-------------------------------------------------|

| 115V AC             | Total Primary Input to Camera   | 27                                              |

| 4.8/5.15V DC(a)     | TE Cooler (Input to Camera)     | 13 <u>.92/16.</u> 99                            |

| +12V DC             | Camera Electronics              | 4.50                                            |

| -12V DC             | Camera Electronics              | 4.21                                            |

| +5V DC              | Camera Electronics              | 3.26                                            |

|                     |                                 |                                                 |

|                     | independent of cooler and power |                                                 |

| supply inefficiency | •                               | <u>11.97                                   </u> |

## 6.3 Output Video Format

### 6.3.1 Standard Load Impedance

The standard load impedance is defined as the complex ratio of voltage to current in a two-terminal network, expressed in ohms.

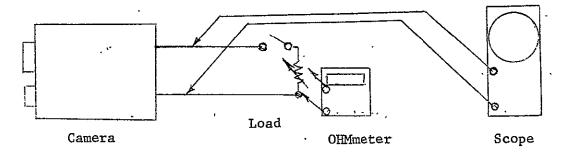

#### Procedure:

The following test circuit will be used: .

The open circuit output video voltage will be measured with a scope. The pot will then be used to terminate the output and be subsequently adjusted to yield an output voltage of 1/2 the previously measured open circuit voltage. The pot will then be removed from the output circuit and measured with a digital ohmmeter.

The output impedance shall be 75 ohms <u>+</u>5% over the frequency range of the camera and shall be connected for single-ended operation.

J1 Measured impedance  $72.0 \Omega$

J4 Measured impedance  $75.6 \Omega$

## 6.3.2 Composite Picture Signal Measurements

The composite picture signal is the signal which results from combining a blanked picture signal (the result of the scanning process) with the synchronizing (sync) signal.

The subject level will be measured by means of an oscilloscope capable of measuring such a signal with the accuracy of  $\pm 2\%$  of the actual value over the voltage range of -0.5 to +1.5 volts. Some means of calibration shall be provided so that signal level measurements can be made in volts as well as in IRE units.

The following composite signal measurements were made in accordance with appropriate portions of 58 IRE 23.51 IRE Standards on Television: Measurement of Luminance Signal Levels, 1958, or latest revision thereof:

|                                                 | Required                 | <u>J1</u><br>Verified | <u>J4</u><br>Verified |

|-------------------------------------------------|--------------------------|-----------------------|-----------------------|

| Polarity                                        | Black Negative           | X                     | X                     |

| Signal Levels                                   |                          |                       |                       |

| White                                           | 100 IRE units            | 100                   | 100                   |

| Blanking                                        | O TRE units              | . 0                   | 0.                    |

| Sync                                            | -40 IRE units            | -38                   | 42                    |

| Setup                                           | 7.5 <u>+</u> 5 TRE units | 7.5                   | 7.5                   |

| Output Video Voltage . (with 75                 | ohm termination)         | 1                     |                       |

| Composite                                       | 1V p-p                   | 990 MV                | 960 MV                |

| Blanked Picture Signal with set (non composite) | up .714 <u>+</u> .1V p-p | 738 MV                | 705 MV                |

| Synchronizing Signal                            | +.286 <u>+</u> 05V p-p   | 236 MV                | 240 MV                |

# 6.4 Spots and Blemishes

A spot or blemish shall be defined as a video signal transition of 7 IRE units or more in the output picture signal not present in the original scene, and which is the direct result of a sensor defect. The difference in sensitivity between any two adjacent CID elements in any direction shall be no more than 10%. Also, the difference in sensitivity from raster edge to edge (horizontally and vertically) shall be no more than 10%. No horizontal or vertical black lines resulting from a failed CID element will be allowed. The size of a spot shall be determined by counting the number of scan lines on which the transition occurs; i.e., the number of lines per frame on which the transition is greater than 7 IRE units.

To determine the presence of spots, smudges, etc., a uniform grey background shall be observed which is illuminated by light source(s) of the appropriate color temperature and of the intensity to allow nominal camera operation (i.e., S/N shall not be such that spots and blemishes are masked by noise). Any gain operation by the camera shall also be considered.

The total of white and dark spots shall be less than or equal to:

10 spots ≤ 4 TV lines per frame 2 spots < 8 TV lines per frame

The total of white and dark spots measured: 9 6 significant black

Measured at room temperature (white spots halve in intensity for approximately each 8°C reduction in CID temperature)

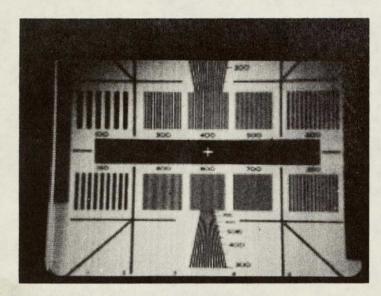

# 6.5 Output Resolution

In television systems, a measure of ability to delineate picture detail is resolution expressed in terms of the maximum number of TV lines (alternate black and white lines) per picutre height discriminated on a standard test chart. The ratio of (1) the peak-to-peak signal amplitude, given by a test pattern consisting of alternate black and white bars corresponding to a specified line number (resolution), to (2) the peak-to-peak signal amplitude, given by large area blacks and large area whites having the same luminance as the test pattern is defined as the resolution response.

The methods of measurement are as specified in Institute of Electrical and Electronic Engineers (IEEE) 208, 60 IRE 23.52, Standards on Video Techniques: Measurement of Resolution of Camera Systems.

Resolution: The limiting horizontal and vertical resolution response is determined by observing the point at which the individual lines of the graduated wedges are no longer distinguishable as separately defined images. For the measurement of resolution response, the picture signal shall be applied to a picture monitor properly adjusted per the IEEE standard above.

The horizontal resoltuion response shall not be degraded by the video processing chain of the camera systems, at least to an upper limit defined by the number of CID elements. The limiting resolution shall be no less than 70% of the number of TV elements.

|                     | <u>Desired</u>    |                 | Measured           |                  |  |

|---------------------|-------------------|-----------------|--------------------|------------------|--|

| Scanning Mode       | <u>Horizontal</u> | <u>Vertical</u> | <u>Horizontal</u>  | Vertical         |  |

| Normal '            | 174 lines         | 171 lines       | > <u>200</u> lines | <u>175</u> lines |  |

| Synthetic Interlace | 174 lines         | 171 lines       | >200 lines         | >200 lines       |  |

# Resolution Response

Measured Resolution Response > 175 lines (See photographs #1 through #6)

#### 6.6 Operating Light Ranges

## 6.6.1 Gray Scale Response

The gray scale response is defined as the camera's ability to resolve scene contrast ratio and generate a proportional voltage to display same on a television monitor.

When the camera is activated under nominal conditions and a logarithmic gray scale with 10 steps (32:1 contrast ratio) is imaged onto the sensor faceplate with a highlight illumination as indicated below (via a standard reflectance-type gray scale chart), the camera shall resolve the 10 steps when its output is displayed on a suitable television monitor and shall exhibit a signal/noise ratio as defined and indicated below:

The S/N for temporal noise sources (random noise) shall be determined by measurement on an oscilloscope, at the camera output, (across the standard load impedance) of the peak-peak noncomposite picture signal voltage and the peak-peak random noise voltage. S/N is the ratio of peak-peak signal voltage to rms (\frac{peak-peak}{5.6}) random noise voltage. S/N for fixed pattern noise sources shall be determined by measurement on an oscilloscope, at the camera output, (across the standard load impedance) of the peak-peak fixed-pattern noise voltage across any one selected line of video. S/N is the ratio of peak-peak signal voltage to peak-peak fixed pattern noise voltage.

| Mode      | Highlight Illumination ode (Faceplate)                                              |           | S/N Ratio<br>(Random) |           | S/N Ratio<br>(Fixed Pattern) |   |  |

|-----------|-------------------------------------------------------------------------------------|-----------|-----------------------|-----------|------------------------------|---|--|

| Normal ·  | 1/2 amount required for array saturation (.4 ft-c)                                  | Min<br>NR | Meas<br>>50 DB        | Min<br>NR | Meas<br>46 DB                | , |  |

| Preinject | (.13 ft-c nominal)                                                                  | 38DB      | 39 <u>.6</u> DB       | 33DB      | 33.6 DB                      | ' |  |

|           | 1/2 amount required for array saturation with a scene integration time of 3 seconds |           |                       |           | ,                            |   |  |