#### **UNCLASSIFIED**

# FINAL REPORT

# NUMERICAL AERODYNAMIC SIMULATION FACILITY

#### PRELIMINARY STUDY EXTENSION

February 1978

Distribution of this report is provided in the interest of information exchange. Responsibility for the contents resides in the author or organization that prepared it.

(NASA-CR-152107) NUMERICAL AERODYNAMIC N78-19051

SIMULATION FACILITY. PRELIMINARY STUDY

EXTENSION Final Report (Burroughs Corp.)

273 p HC A12/MF A01 CSCL 01A Unclas

G3/02 08629

Prepared under Contract No. NAS2-9456 by Burroughs Corporation Paoli, Pa.

for

AMES RESEARCH CENTER

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

UNCLASSIFIED.

#### UNCLASSIFIED

#### FINAL REPORT

#### NUMERICAL AERODYNAMIC SIMULATION FACILITY

#### PRELIMINARY STUDY EXTENSION

February 1978

Distribution of this report is provided in the interest of information exchange. Responsibility for the contents resides in the author or organization that prepared it.

Prepared under Contract No. NAS2-9456 by Burroughs Corporation Paoli, Pa.

for

AMES RESEARCH CENTER

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

## CONTENTS

| Chapter/Paragraph |                                        | Page             |

|-------------------|----------------------------------------|------------------|

| 1                 | INTRODUCTION AND SUMMARY               | 1-1              |

| 1.1               | Introduction                           | 1-1              |

| 1. 2              | Functional Design                      | 1-3              |

| 1. 3              | Software                               | 1-4              |

| 1. 4              | Simulation                             | 1-4              |

| 1.5               | Reliability .                          | 1-5              |

| 1.6               | Tradeoffs                              | 1-5              |

| 2                 | FUNCTIONAL DESCRIPTION OF NSS HARDWARE | 2-1              |

| 2.1               | Introduction                           | 2-1              |

| 2.2               | Basic System Parameters                | 2-2              |

| 2.3               | Overview of Functional Description     | 2-5              |

| 2.4               | Individual Blocks                      | 2-10             |

| 2.5               | Instruction Set and Instruction Timing | 2-43             |

| 3                 | SOFTWARE ISSUES                        | 3-1              |

| <b>3.</b> 1       | Extended FORTRAN for the FMP           | 3-1              |

| 3. 2              | Hand Compilation for SAM               | 3-16             |

| 4                 | SIMULATION                             | 4-1              |

| 4. 1              | Simulation Goals                       | 4-1              |

| 4.2               | Selection of Metrics                   | 4-2              |

| 4.3               | Simulation Models                      | 4-4              |

| 4. 4              | BOSS Simulator                         | 4-6              |

| 4.5               | Simulation Model for the Current Study | 4-11             |

| 4.6               | Simulation Results                     | 4-20             |

| 5                 | RELIABILITY                            | 5-1              |

| 5. 1              | Introduction                           | 5 <del>-</del> 1 |

| 5. 2              | Availability Prediction                | 5-2              |

| 5. 3              | Error Detection and Correction         | 5-1-7            |

# CONTENTS (Cont'd)

| Chapter/Paragraph  |                                               | Page              |

|--------------------|-----------------------------------------------|-------------------|

| 6                  | TRADEOFFS DELINEATED                          | ,<br>6 <b>-</b> 1 |

| 6. 1               | Introduction                                  | 6-1               |

| 6 <b>.</b> 2       | Language Definition                           | 6-2               |

| 6. 3               | Matching the Compiler and the Instruction Set | 6-2               |

| 6 <b>.</b> 4'      | Word Format                                   | 6-3               |

| 6 <b>.</b> 5       | Instruction Formats                           | 6-4               |

| 6. 6               | SECDED                                        | 6-4               |

| 6. 7               | Trustworthiness vs. Throughput                | 6-5               |

| 6 <b>.</b> 8       | Parity within Processors                      | 6-7               |

| 6 <b>.</b> 9       | Instruction Fetching Mechanism                | 6-7               |

| 6. 10 <sup>-</sup> | LOADEM and STOREM Block Fetching              | 6-9               |

| 6. 11              | Overlappable Extended Memory Access           | 6-10              |

| 6. 12              | Single Processor Memory                       | 6-11              |

| 6.13               | Processor Program Memory Size, Control        |                   |

|                    | Unit Memory Size .                            | 6-12              |

| 6.14               | Extended Memory Speed and Transposition       |                   |

|                    | Network Speed                                 | 6-12              |

| 6. 15              | Control Unit Speed                            | 6-13              |

| 6.16               | Scalar Processor                              | 6-14              |

| 6. 17              | Marginal Checking                             | 6-18              |

| 6. 18              | Component Technologies                        | 6-18              |

| 6.19               | Expansibility                                 | 6-19              |

| A' a 35            |                                               | ;                 |

| Appendix           |                                               |                   |

| A                  | PRELIMINARY COMPILER ALGORITHMS FOR           | •                 |

| A                  | SETTING THE TRANSPOSITION NETWORK             | A-1               |

| В                  | SECDED RELIABILITY IMPROVEMENT MODELS         | B <b>-</b> 1      |

| С                  | SPARE PROCESSOR                               | C-1               |

#### CHAPTER ONE

#### INTRODUCTION AND SUMMARY

#### 1.1 INTRODUCTION

Burroughs Corporation is pleased to present this report which is the result of work carried on under an extension to contract No. NAS2-9456, a preliminary study for a Numerical Aerodynamic Simulation Facility. The primary objective of this extension is to produce an optimized functional design of key elements of the candidate facility defined in the Final Report (1) of the basic contract. This is accomplished by effort in the following tasks:

- To further develop, optimize and describe the function description of the custom hardware.

- To delineate trade-off areas between performance, reliability, availability, serviceability and programmability.

- To develop metrics and models for validation of the candidate systems performance.

- To conduct a functional simulation of the system design.

- To perform a reliability analysis of the system design.

- To develop the software specifications to include a user level high level programming language, a correspondence between the programming language and instruction set and outline the operation system requirements.

The results of this effort are presented in five separate chapters:

Chapter 2. Functional Description includes a summary of the system parameters, block diagrams, descriptions, of the major elements and the instruction set with detailed timing.

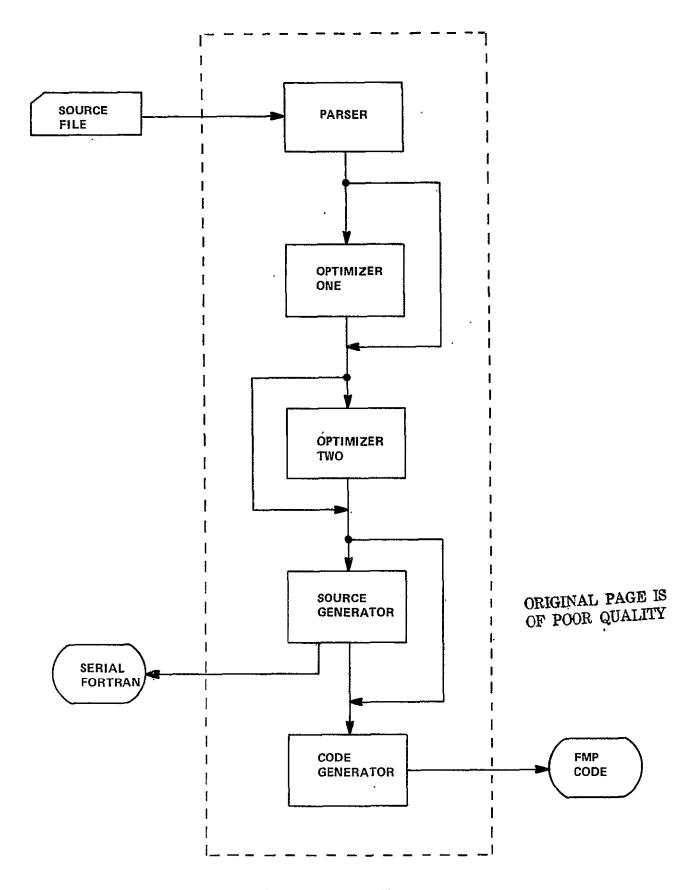

Chapter 3. Software Issues describes the extensions and restrictions on the FORTRAN language and compiler at the functional level a discussion of converting statements in extended FORTRAN into machine language and a statement regarding the operating system.

<u>Chapter 4. Simulations</u> presents the models, metrics and methodology for conducting the simulation along with preliminary results.

Chapter 5. Reliability includes two sections. The first presents the results of an availability analysis of the systems and the second present further discussion of the error detection, correction and control to be employed.

Chater 6. Trade-offs delineates and discusses a large number of design and operating factors for which reasonable alternatives exist.

While the information in this report is designed to stand alone, it is also considered to be a supplement to the Final Report (Ref. 2) of the basic NAS2-9456 contract where appropriate, reference is made to this report rather than to unnecessarily repeat previously reported information.

In addition, it should be pointed out that certain terminology used in the previous report have been revised. The new terms are:

• Flow Model Processor (FMP). This is the portion of the system previously called the Navier-Stokes Solver (NSS).

- Processor Data Memory (PDM) was previously called Processing

Element Memory (PEM)

- Processor Program Memory (PPM) was previously called

Processing Element Program Memory (PEPM)

- Execution Unit (EU), the logic portion of the array processor, formerly called Processor Element (PE).

The following sections summarize the chapters in additional detail.

#### 1.2 FUNCTIONAL DESIGN

The FMP is an array processor of 512 processors, a control unit, and 521 modules of extended memory, as described in Reference 1. The major additions found in Chapter 2, to the description of reference 1, are, first, the provision of SECDED, instead of parity-plus-retry, as the expected means of error control in the processors' memory, second, the addition of four on-line spare processors as definitely a part of the design (they are mentioned briefly as a possibility in reference 1); third, significant revisions and additions to the instruction set; fourth, the restriction of the extended memory instructions to fetching 512 words (one per processor) per instruction, (the earlier description had EM instructions fetching 512 × N words per instruction); and fifth, provision for special hardware for computing any floating-point variables that are not members of a vector.

Chapter 2 includes diagrams and figures of every element of the FMP.

ì

#### 1.3 SOFTWARE

The software chapter covers the FORTRAN language, to a depth necessary to cover simple test cases, discusses hand compiling, and is charged with the task of reporting on progress in defining the operating system during this contract extension. Three and only three extensions are visualized for the initial FORTRAN language. First, the DOALL construct declares to the compiler that the iterations of a particular loop can be done in any sequence, or all in parallel, without affecting the result; second, declarations of several types of use of variables are used to allocate those variables among the different types of memory; third, certain system library functions are required, because of the parallel nature of the machine, that would not be required in serial FORTRAN.

None of these library functions are required for the initial benchmarks.

The operating system is extensively described in reference 1. The level of detail in that document is such that the effort of the contract extension was spent more fruitfully on language definition, compiler considerations, and hand compilation procedures. Thus, the operating system discussion in reference 1 still stands as the best description so far produced of the operating system of the FMP. No attempt has been made to update that description for this report.

#### 1.4 SIMULATION

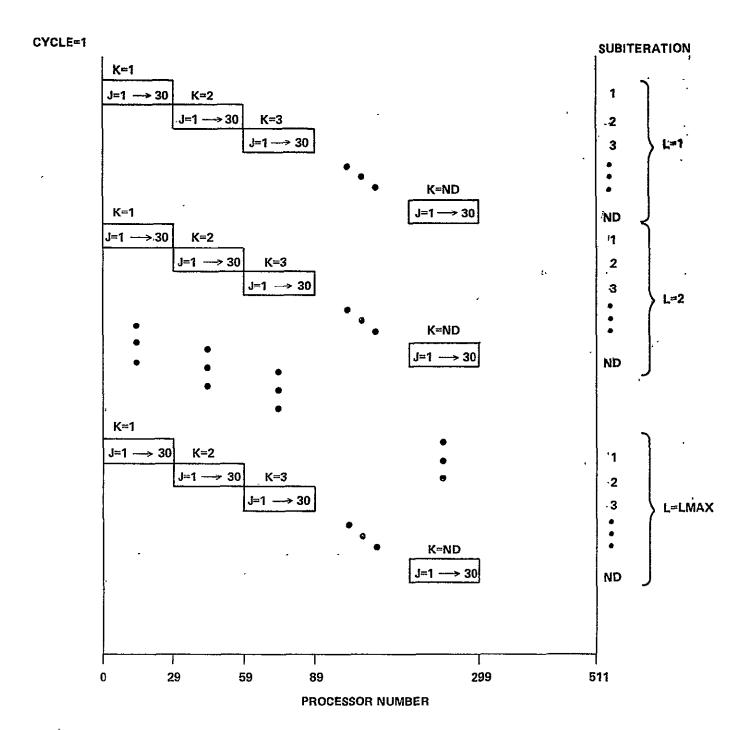

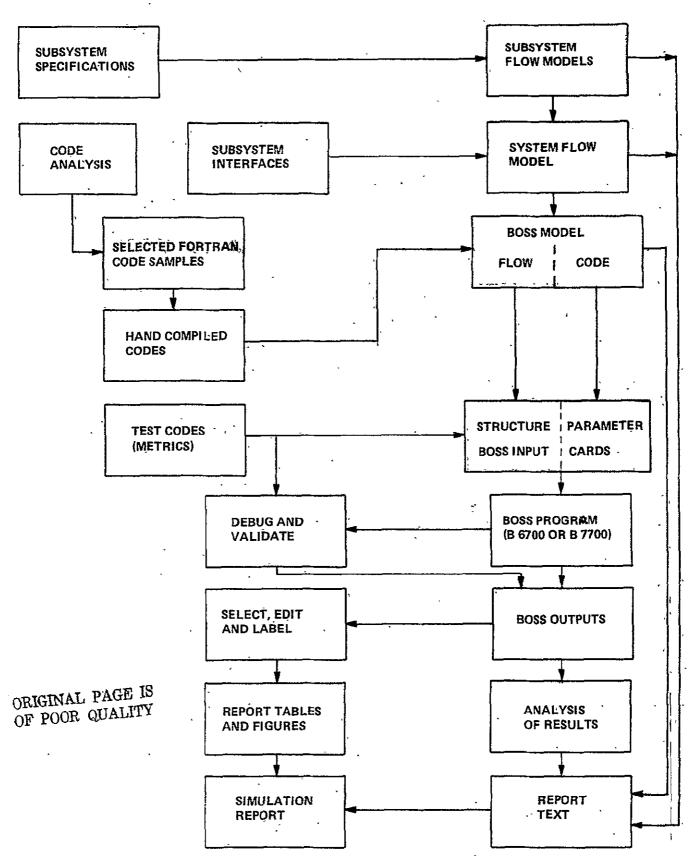

Chapter 4 discusses the separation of the simulation effort into two levels, instruction and FMP level, and the system level. Metrics for each level are discussed, and SUBROUTINE TURBDA has been selected as the metric for the simulation done in this extension also given. The BOSS simulator, in which our simulation is being done, is described briefly in chapter 4.

#### 1.5 RELIABILITY

A detailed computer model for the reliability of the FMP was run. The results of this model bound the availability at 96 percent being the lower limit of availability using pessimistic assumptions, and better than 99 percent availability being achieved under the most optimistic assumptions. The use of spare processors with operating system automatic restart (assumed successful for some fraction of all attempts) produces a very significant improvement over the model that has no spare processors.

The reliability section also includes a discussion of the use of SECDED in all memory, of the process of "scrubbing" out the errors that spontaneously arise in CCD storage (DBM), and of other error control strategems that are used in the FMP.

#### 1.6 TRADEOFFS

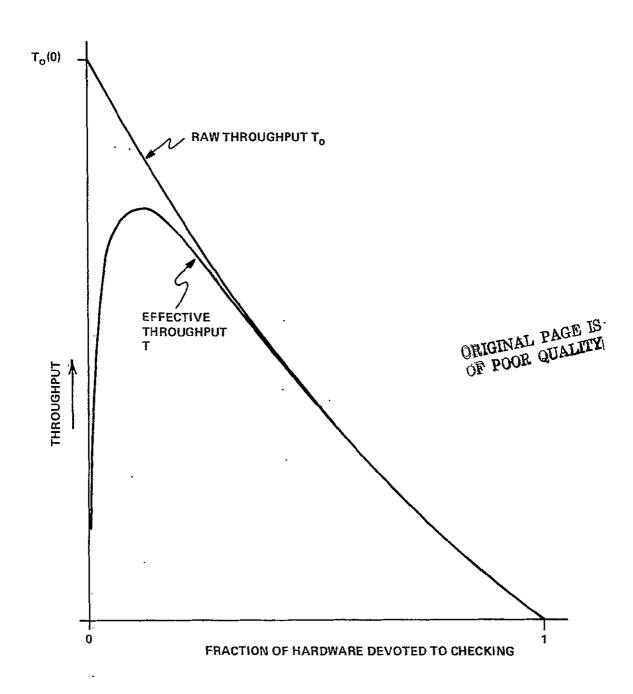

Chapter 6 discusses tradeoffs in many areas. These include ease of programming versus execution efficiency, where one wishes to have most of both, word and instruction formats, error control methods versus their cost in reduced throughput, several specific design issues, relative speeds of specific blocks of the system, alternate methods of supplying the floating-point scalar capability, and other topics, with a final section on the expansibility of both the specific FMP, once built, and the expansibility of the design from which it was built.

# CHAPTER 2 FUNCTIONAL DESCRIPTION OF NSS HARDWARE

#### 2.1 INTRODUCTION

This functional description is arranged in several successive sections. First, a brief system description of the SAM that is the baseline system for FMP is given. Second, a brief list of system parameters is provided. Third, the elements of the system block diagram are each described in turn. Fourth, the instruction set of the FMPis given, together with its timings.

In all of this, it has not been felt necessary to repeat material that is found in the final report of contract NAS2-9456, except very briefly to refresh the reader's recollection. It is presumed that the reader has first read that report.

No design should be considered to be necessarily final if further investigation should show that the machine performs better with the feature modified. Chapter 6, "Tradeoffs", is a discussion of many of the features that will be studied in simulation during phase 2 (time permitting), and which are therefore likely to be modified in the direction of higher throughput if the baseline system is found wanting.

This functional description is intended to provide the base for the information input to a performance simulation of the SAM of the FMP. Some of the information, such as error correction capabilities, is included for completeness in spite of the fact that it has no apparent involvement in a performance simulation.

#### 2.2 BASIC SYSTEM PARAMETERS

Most of the basic system parameters were covered in some detail in the final report Ref. 1. They are summarized here along with additional information of specific interest.

- 2.2.1 Logic Family ECL is the preferred logic family. Final selection of circuits for implementation at this time would only lock us into choices that will become obsolete by 1979-1980 when the design is completed. We do not wish to preclude the use of up-to-date technology in the actual design. If the final design were being implemented at this time, Fairchild's 100K series would be chosen, together with compatible memory circuits. The chip count projected for 1979-1980 is the one assigned to the baseline system. Confidence in this package count is supported in most cases by the very similar chip count, of circuit types already available in 1977 (usually ECL 100K), which are also given.

- 2.2.2 <u>Clock Rate</u> The clock has been assigned a 40 ns period. The instruction times, given below in terms of this clock period, are compatible with the instruction times derived from a preliminary processor design using ECL 100K.

- 2.2.3 <u>Cabling Methods</u> The same flat belts used successfully in prior projects in Burroughs for transmitting high-speed signals with fast rise time and low crosstalk will be used for most of the interunit cabels. Reference 1 discusses this choice.

- 2.2.4 <u>Power</u> While a number of comments on power were included in reference 1, certain detailed information was not. These details are provided in the following statements.

- Switching regulators will be used for the sake of efficiency. A net efficiency of 65% is expected from the total power supply.

- DBM is provided with whatever power is required to make it nonvolatile against glitches and short power outages.

Since CCD is proposed for DBM, battery backup would be highly desirable.

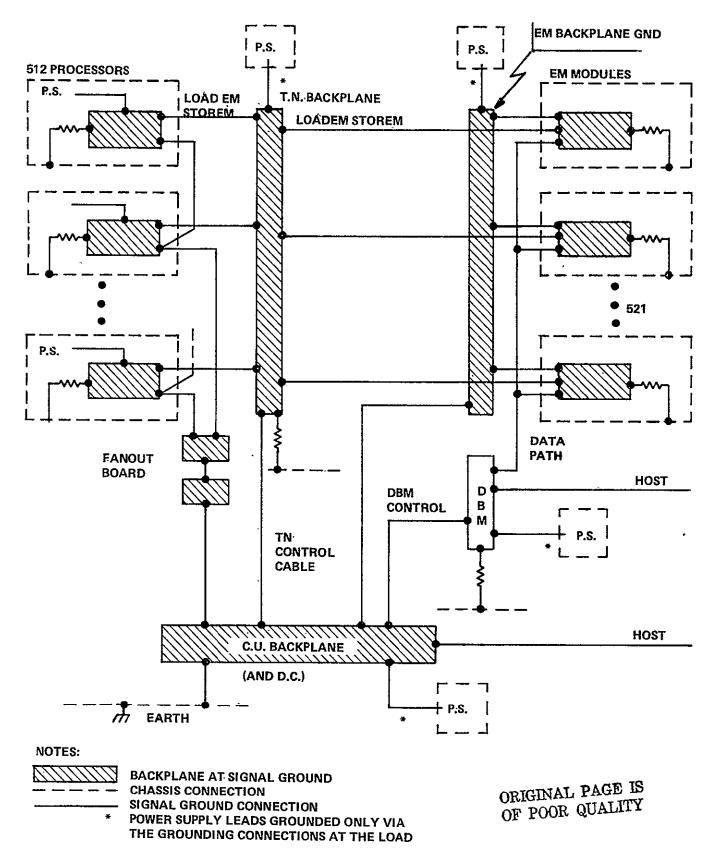

Figure 2-1. Grounding

- The ground return from backplane to power supply is never used as part of the path that connects one backplane ground to another backplane ground. Figure 2-1 shows the grounding arrangements expected

- . Total power for the FMPis estimated (very approximately) at 250 kw, based on an average of 0.8w for each of the 200,000 circuit packages, and 65% efficiency in the power supply. These are for the 1980 projected circuit counts.

- . Every module has its signal ground tied to chassis so that' there will be no floating grounds when the modules are tested as stand-alone modules. In Figure 2-1 these ties are shown as resistors.

A requirement on power supplies employed at NASA AMES is that they must ride through the undervoltage transients produced by wind tunnel motor startup, and not pass voltage spikes. In addition, they should be reasonably respectful to the source. Requaid upwer supply configurations satisfy this requirement.

- . Motor-generator set. Inertia enables an M-G set to ride through large transients. The inefficiency of the M-G set is multiplied into the inefficiency of the system power supplies. The advantage of an M-G set is that it can be added to a system after the fact, without impacting any existing design.

- Transformerless rectifiers, like the old AC-DC radio, require a filter capacitor, which suppresses spikes, and if large enough, will ride through undervoltage transisents. The unregulated DC (about 280v) is distributed around the equipment and used as input to individual switching regulators. SCR rectifiers are to be avoided, since they inject noise back into the line.

. Battery back-up Uninterruptible Power Supply (UPS).

Of the three schemes, the transformerless rectifier is most efficient, and takes the least space. It also has the advantage that back-up batteries can be supplied to a selected subset of the equipment (DBM, in this case). It is also easy to make the rectification redundant. Three-phase full wave rectifiers are actually six-phase for ripple characteristics. They often need no chokes, and have wide conduction angles in the rectifier diodes.

2.2.5 <u>Number of Processors</u> - A key decision in the design of the FMP is the choice of the number of processors to be implemented. The design presented here is based on using the fastest processor that is consistent with the speed of memory built of 16k-bit static RAM chips. Projecting 100 ns speed for such chips, we arrive at a 360 ns floating point multiply as being approximately in balance. A faster processor would yield increased speed only if the memory were changed to the faster 4k-bit chips, implying a four-fold increase in the number of components in memory. Reliability, even more than cost, tells us to keep the parts count down, and therefore to design a system consistent with 16k-bit memory chips. It takes about 512 processors, at these speeds, to yield the desired billion floating point operands per second with sufficient margin for inefficiencies.

#### 2.3 OVERVIEW OF FUNCTIONAL DESCRIPTION

#### 2.3.1 Block Diagram

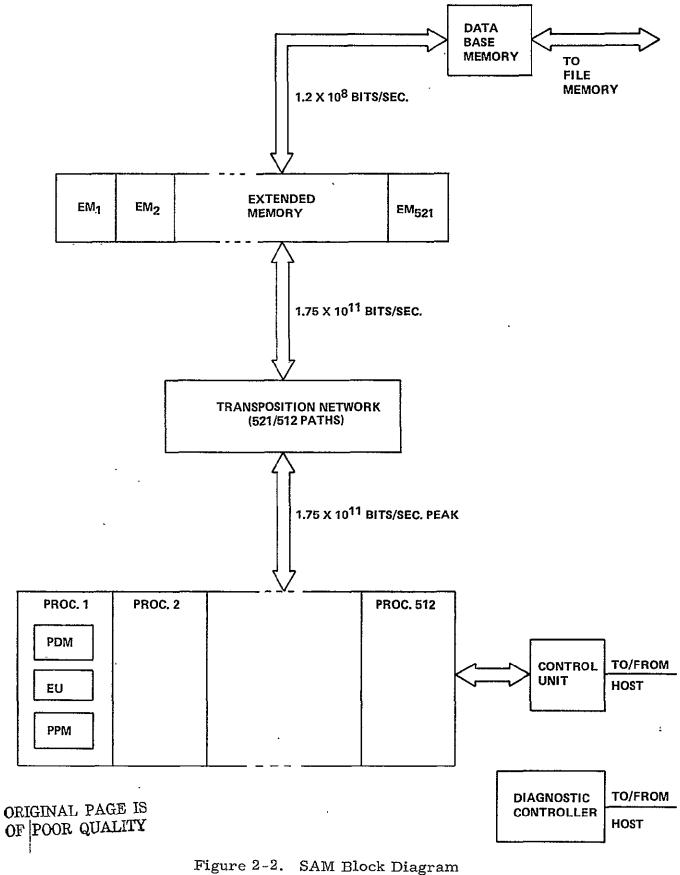

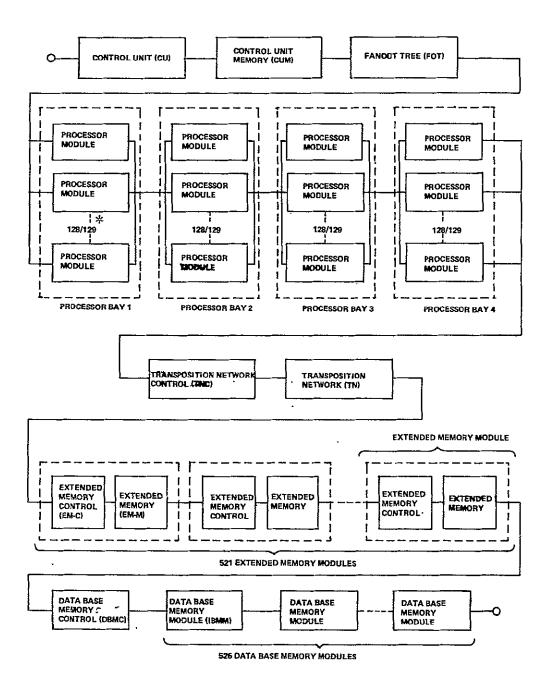

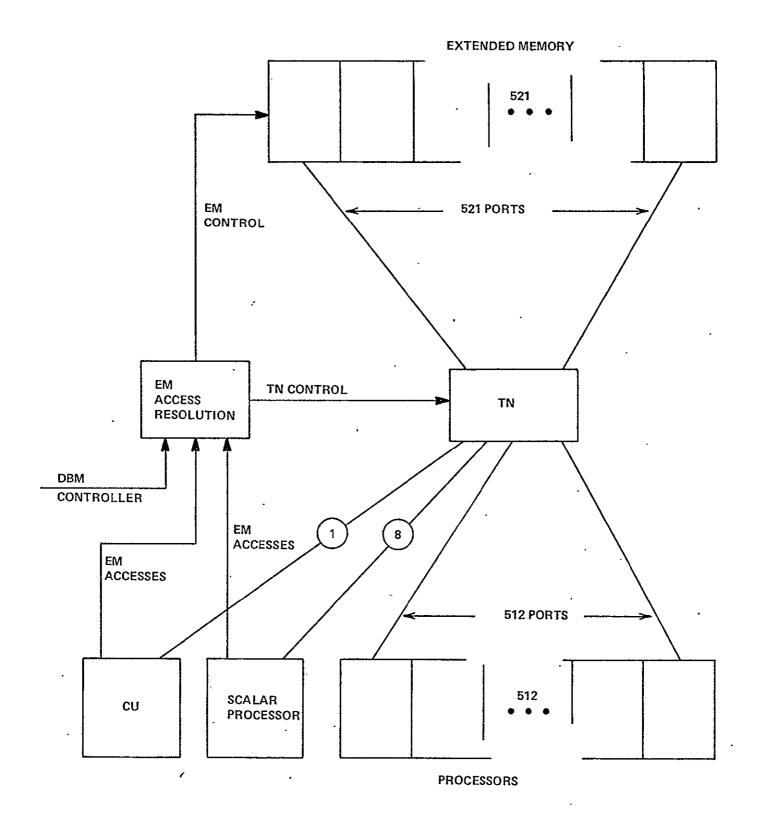

Figure 2-2 (a slightly expanded copy of Figure 1-2 of the Ref. 1) shows the array processor consisting mostly of 512 processors attached by a switch, the Transposition Network, to 521 Extended Memory modules which hold the main data base of the program. Used

ORIGINAL PAGE IS OF POOR QUALITY

as a staging area for jobs not yet started, and as the output area for jobs in process or completed, is Data Base Memory. A Control Unit synchronizes the action and controls the transposition network and the transfers in and out on both faces of the extended memory. The controller for the Data Base Memory also accepts requests from the host processor to transfer to and from the host disk pack file system. The Data Base Memory controller resolves access conflicts to and from data base memory. The Control Unit resolves accesses to and from Extended Memory. There is also a Diagnostic Controller used for maintenance and cold starts.

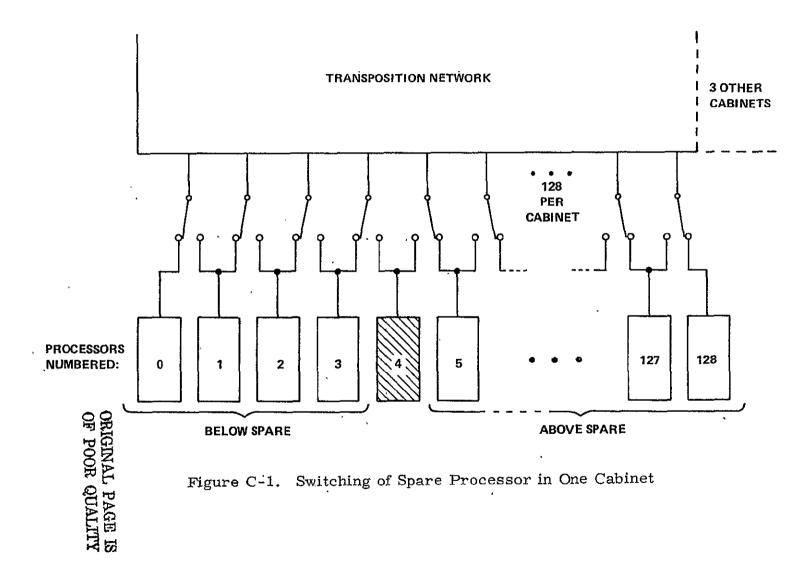

Each processor is self-contained, with integer and floating-point arithmetic units, its own instruction decoder, its own program memory, and its own data memory. In addition to the 512 processors, four processors are included as on line spares to help achieve system availability requirements. The use of these on-line spare processors is discussed in Chapter Five.

### 2.3.2 <u>Instruction Streams</u>

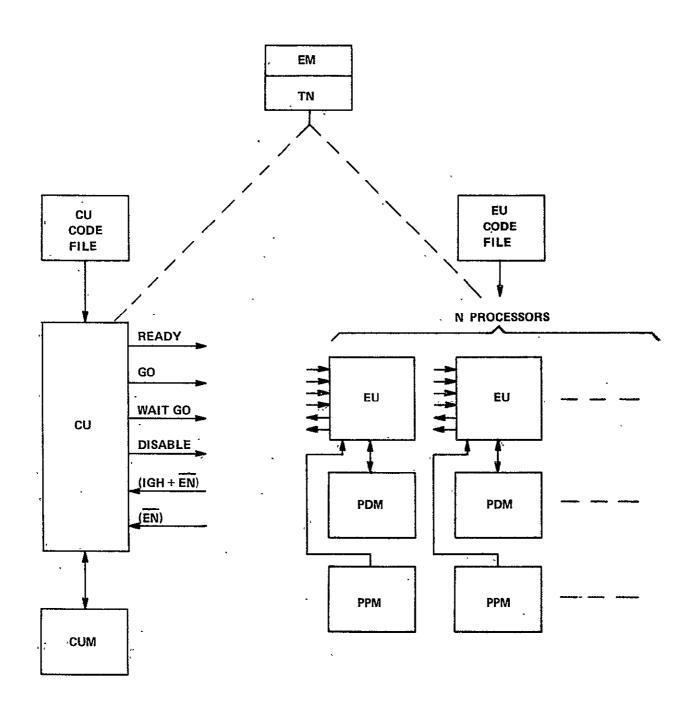

As described in Ref. 1, the FMP is controlled by two instruction streams, which are created in parallel by the compiler from a single sequence of source statements. One instruction stream is being executed in the control unit; the other is being executed by all processors asynchronously of each other. Some statements in the source code result in instructions in both instruction streams. Examples are "CALL subroutine", or an arithmetic statement using an EM variable, and therefore requiring a fetch to all processors from the EM. Some of these joint instructions require that the control unit and the processors synchronize themselves. It has been observed that reference 1 does not seem to be clear in explaining synchronization, nor in explicating the means of accomplishing it. Therefore, the discussion digresses here to a detailed discussion of the synchronization mechanism.

#### 2.3.3 Synchronization

The process of synchronization occurs within instructions. It involves two signal lines which go from the control unit to all processors, namely "CUready" and "go". "CUready" is a level, "Go" is a pulse that arrives at all processors simultaneously. From each processor there are two lines, "Enabled" is a copy of the "enabled" flipflop that exists in each processor; "I got here" is a signal, a level, which is raised during the execution of some instructions.

To explain the process, consider the example of a LOADEM instruction fetching N words from EM. In the control unit, the LOADEM causes the raising of the "CUready" line as soon as the TN controls have been set to the proper value. In each processor where "enabled" is true, "I got here" is raised as soon as the processor starts executing the LOADEM instruction.

When any processor executing LOADEM sees "CUready" true, the processor sends the address through the TN to the EM module that is connected to this processor. The strobe accompanying the address causes the loading of the address within the EM module.

An "all processors ready" signal, marking the time at which the last enabled processor arrives at the LOADEM instruction is created for the CU (The logic creating this signal is actually contained within the fanout tree). Using  $E_n$  as the "enable" bit of the nth processor, and  $H_n$  as the "I got here" line of the nth processor, the "all Processors ready" signal is given by the formula

All-processors-ready = (H<sub>1</sub> OR

$$\overline{E_1}$$

) AND (H<sub>2</sub> OR  $\overline{E_2}$ ) AND ...

AND (H<sub>512</sub> OR  $\overline{E_{512}}$ )

There is also "any processor enabled", the OR of all the "enable" bits.

When the CU sees "all processors ready", the CU issues, after an appropriate delay to let addresses be loaded, a series of N "read" commands to the EM module and also issues, appropriately timed with respect to the last such command, a "go" pulse to the processors. In the processor, we load N words under control of the N strobes coming from EM module through the TN. The "go" signals the end of the instruction.

As a second example, consider the instruction WAIT. Here no processor action timed to the "CUready" is required, so the CU sends no "CUready". When the CU sees the "all processors ready" signal formed from the "I got here"s and the "enable"s, it issues a "go" to all processors, who have refrained from executing their next instruction until the "go" is received.

When the processor has raised its "I got here" line, but before it has received a "go" signal, it is said to be "¡waiting". The "I got here" line is dropped upon receipt of the "go" pulse.

In addition to the above synchronization, the CU also has the power to transmit commands. The commands are carried on a 4-bit-wide bus accompanied by a strobe line. Many of these commands are used in the diagnostic programs. Ref. 1, p 4-27, has a tentative list of operations called forth by these commands. Some of these commands will be conditional on the "enable" bit of the processor, some are unconditional independent of the enable bit. The only such command that is used in user-generated FORTRAN programs is the command that simultaneously loads the program counter and sets the enable bit.

The control unit's command power is exerted over all processors at once, not over individual processors. Processors that do not join in some array-wide operation avoid it by a) jumping around the operation, if it is local to each processor, b) executing certain

instructions (LOADEM, STOREM, SHIFTN) as noops conditional on the last bit of an integer register in the processor, or c) executing the STOP instruction, which turns off the "enable" bit until the CU reaches some point in its instruction stream that turns it back on.

There is also an interrupt line from processor to CU.

# 2.3.4 Starting a Run

During normal operation, all data and program for the next run will be loaded into data base memory prior to the beginning of the run. When the run starts, system software in the CU loads program from data base memory to the memory of the control unit (via extended memory). The initialization phase of the program then transfers necessary data to extended memory, and transmits the processors' program to them. These actions are automatically inserted by the compiler and the linker. With data in place in extended memory, and allocated space initialized to "invalid" and with code files in place in control unit and processors, user execution starts.

#### 2.3.5 FMP Hardware Summary

The Flow Model Processor therefore consists of

- One Control Unit (CU) with its own memory (CUM) with optional scalar processor capability.

- 512 Processors, (plus 4 spares) each with its own Processor Data Memory (PDM) and Processor Program Memory (PPM)

- One Transposition Network

- 521 Extended Memory modules

- One Data Base Memory and Controller

- · One Diagnostic Controller

All of the above is shown in Figure 2-2 except for the optional scalar processor and the four spare processors. The scalar processor is an ingredient of the design which was not needed in order to successfully match the SAM to the aerodynamic flow models. Since the scalar processor was not discussed in reference 1, further discussion thereon is found in Chapter 6.

#### 2.4 INDIVIDUAL BLOCKS

Following is a brief description of each of the elements of the FMPtogether with a formatted tabulation of pertinent features and a block diagram of each.

#### 2.4.1 Description of Tables

For each element of the FMP, there is a table of characteristics given. A very short narrative description gives the intended function of the element in user programs. Source of control is identified, and the storage capabilities, both capacity and speed, are also given. Connectivity to other elements is broken down to a rather detailed level, with each group of signals that has an identifiably different function being so identified. In some cases, such as CU to processor, signals in the same belt are identified as a different group in order to more clearly identify their use.

The table also discusses the mode of error control built into the design. Some mechanisms of error control were included in the baseline system design in the final report. Some further mechanisms of error control are proposed in Chapter 5. This section represents a particular state of the design, not the final state.

Two chip counts are given. The 1979-1980 projected chip count is the one projected for the baseline system. The second chip count, using parts now existing in 1977, is given only for corroboration, to indicate the reasonableness of that projection. It also represents the chip count of the FMP if design were frozen now. There are also in some cases estimates of the power drain. All these are included only for interest. These are preliminary. They have no direct bearing on the performance evaluation simulation.

"TBD" means "to be determined".

2.4.2 <u>Processor</u> The array of 512 processors is charged with the task of executing the user computations in the program, namely the floating-point operations on the problem variables.

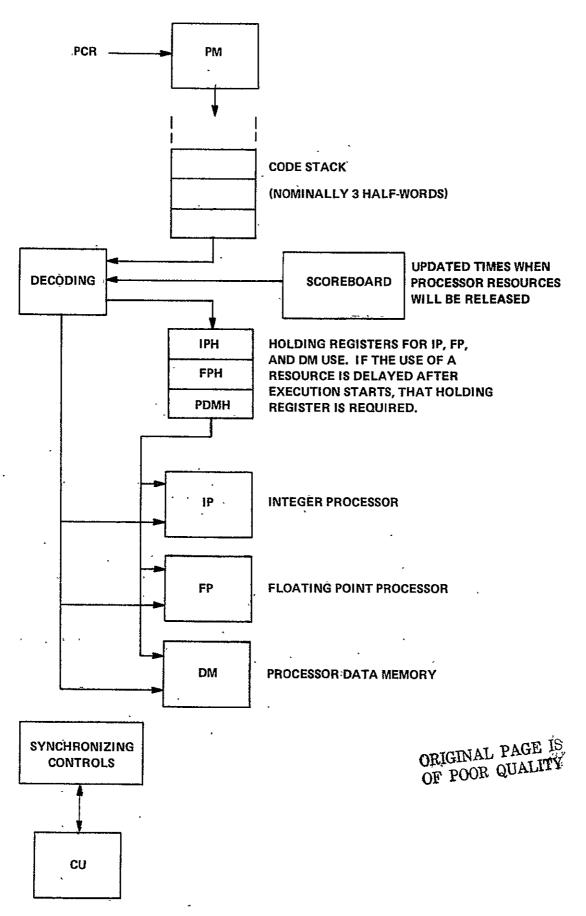

The processor executes code contained in its own program memory, and accepts commands from the control unit. Certain instructions (see Table 2-13) are executed in synchronism with the control unit (and hence, by implication, in synchronism with the entire array, since the control unit expects cooperation from all processors.)

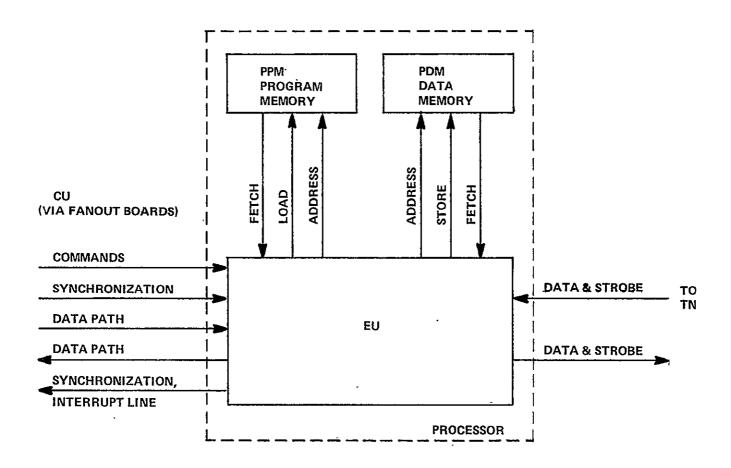

The actions of the processor are delineated by the instruction set in the next section. Figure 2-3 shows pictorially the division of the processor into and execution unit, a data memory, and a

ORIGINAL PAGE IS OF POOR QUALITY

Figure 2-3. Processor Block Diagram

ORIGINAL PAGE IS OF POOR QUALITY

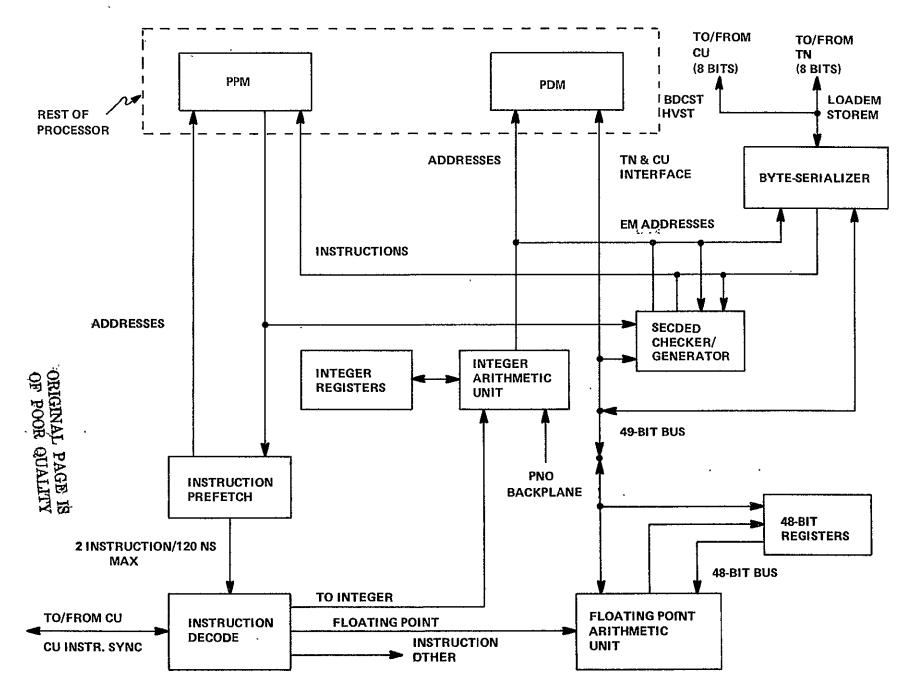

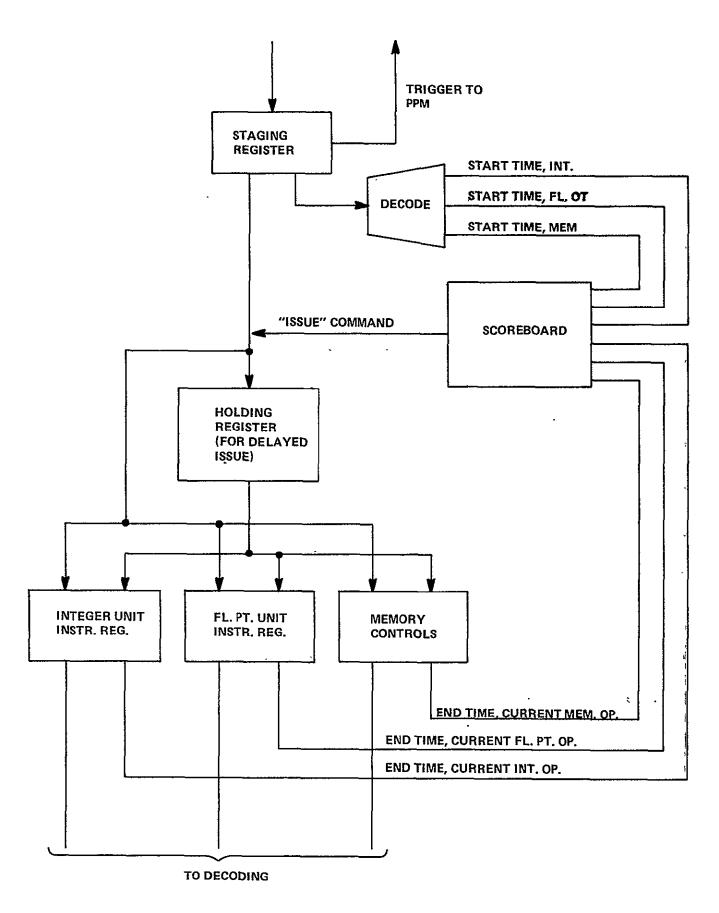

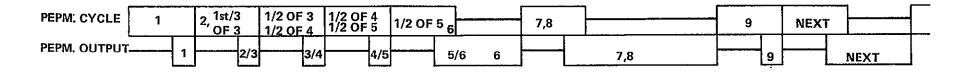

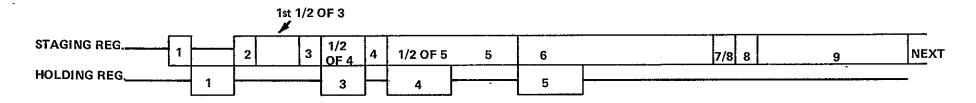

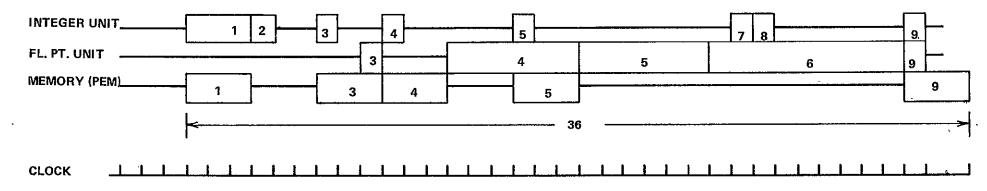

program memory. Figure 2-4 is a block diagram of the logic part of the processor, showing the independent integer and floating point units, with separate register files for each. Figure 2-5 is a diagram of the instruction fetching and overlap machinery, which is explained at length below in connection with the timing of instruction execution. The logic portion of the processor has been named the "execution unit." Table 2-1 provides data on the EU.

Connections to the processor come from the control unit and the transposition network. A byte-wide (8-bit) data path is found both from (BDCST) and to (HVST) the control unit. synchronization signals discussed previously also come from the control unit. The 4-bit wide command path, and its strobe, also come from the control unit. The data paths to (STOREM) and from (LOADEM) the transposition network are each accompanied by a In addition, each processor is connected to backplane strobe. wiring that expresses its own number. Of the 129 processors in a cabinet, any one may be the spare processor. Suppose processor no. N is the spare processor. Then the backplane number for processors 0 through N-1 is correct, but the backplane number for processors N1 through 128 must be shifted own by one, to N through 127, in order that the processors being used by the program be consecutively numbered. Therefore, there is a one-bit signal coming from the switching machinery which tells the processor whether or not to subtract 1 from its hard-wired processor number to correct for the location of the spare.

Error control within the processor consists of bounds checks, reasonableness checks, and consistency checks, as listed in Ref. 1. See Sections 6.7 and 6.8 for further checks that may be implemented but at some cost in throughput.

For justification of the 1977 component count, see appendix E of volume II of reference 1.

Figure 2-4. Internal Block Diagram of EU

Figure 2-5. Instruction Fetching and Overlap

ORIGINAL PAGE IS OF POOR QUALITY

# TABLE 2-1 EXECUTION UNIT CHARACTERISTICS

UNIT: Execution Unit (EU) No. In System: 512 + 4 on-line spares

FUNCTIONAL CHARACTERISTICS

Function: This is the logic portion of the processor, all the processor except memory. It executes code that has been written by the FMP FORTRAN compiler, including EM address computations, index calculations and floating point operations.

Source of Control; During User Program: Program stored in PPM, sync's from the CU. During System Startup and Diagnostics: Same plus CU commands

Storages; Capacity: 16 16-bit integer registers

16 48-bit floating point registers

Other registers (see text)

Speed: Multiple accesses each 40 ns clock

#### Connectivity to Other Elements:

| # | Path    | To or From            | No.<br>Sig | Timing     | Primary Use                      |

|---|---------|-----------------------|------------|------------|----------------------------------|

| 1 | BDCST   | From CU               | 8          | byte/20ns  | Receive global variables from CU |

| 2 | HVST    | To CU                 | 8          | byte/20ns  | Transmit result to CU (global)   |

| 3 | LOADEM  | From TN               | 9          | byte/20ns  | Receive data from EM             |

| 4 | STOREM  | To TN                 | 9          | byte/20ns  | Transmit data to EM              |

| 5 | CUinstr | From CU               | 4          | TBD        | Primarily for diagnostics        |

| 6 | sync    | To CU                 | 4          | edge       | Synchronization                  |

| 7 | sync    | From CU               | 4          | edge       | Synchronization                  |

| 8 | PEno    | Wired to<br>backplane | 9          | D.C. level | Processor's own number           |

#### RELIABILITY/REPAIRABILITY/TRUSTWORTHINESS

Error Control Methods: TBD. Modulo 3 check on arithmetic is being evaluated. Error cases are detected (see text).

Repair Methods: Replace and restart from restart point. On-line replacement (with manual pull-and-replace at a later convenience of the repairman) is very feasible. MTBF of Unit: See Chapter 5.

Degraded Modes Available: Programs can be compiled to use less than all the processors available, thereby bypassing any failed processors. On-line switching of spare processors.

PHYSICAL

Chip Count; 1980 Projection: 100 If use 1977 parts: 160 (100K ECL etc.)

(based on preliminary logic design using 100K)

Pysical Size: 1980: One large pc. sized module. 1977: Single removable module

Power Drain: 1980: 150 w 1977: 300 w

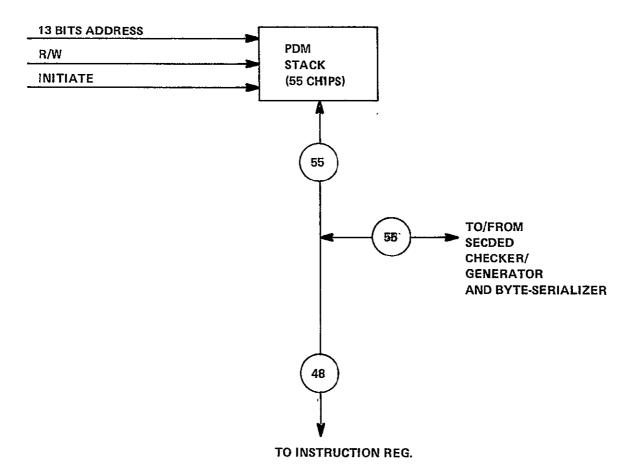

- 2.4.3 Processor Data Memory The processor data memory (PDM) contains work space for each processor. It is also used to hold local copies of global information, to facilitate their being fetched by the processor's program. It can be used to window data from EM. Control is from the memory address register in the processor. There are 16384 words of 55 bits, consisting of 48 bits data and 7 bits of single-error correcting, double-error-detecting code. Data address, and control connections are solely to the processor. 16k-bit static RAM chips are used. Figure 2-6 shows some of the logic in the processor associated with the port into PDM. Table 2-2 describes major characteristics of the PDM. See sections 6.6, 6.12, 6.13 for discussion of tradeoffs in PDM design.

- 2.4.4 <u>Processor Program Memory</u>. Processor Program Memory (PPM) contains the code file from which the processor executes. It is addressed directly by the program counter. Overlay comes from the CU via the "broadcast" (BDCST) path. Except for the size of 8192 words, design is identical with that of PDM.

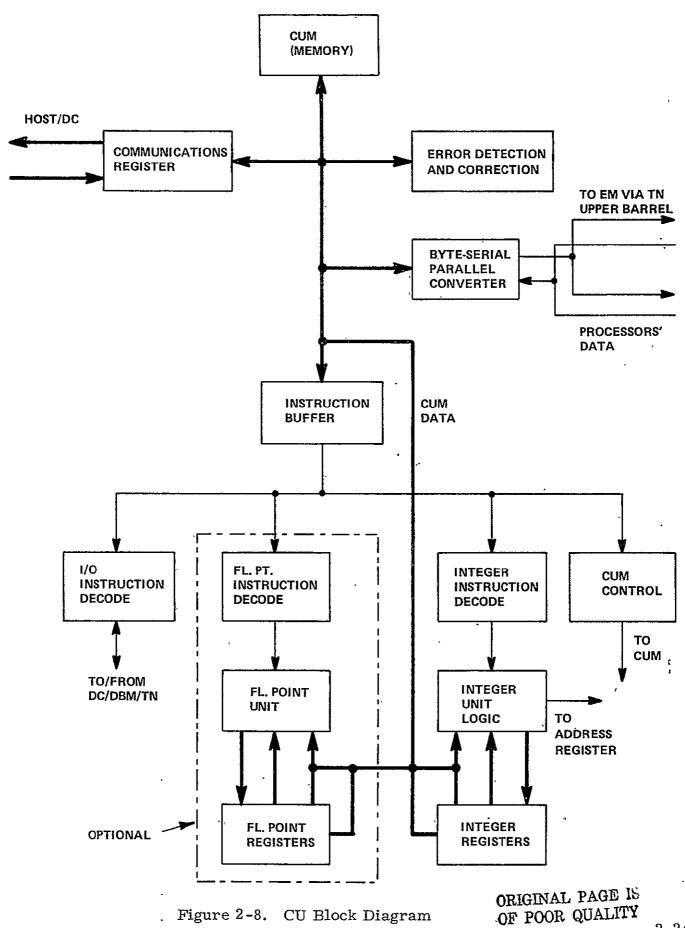

#### 2.4.5 Control Unit (CU)

#### 2.4.5.1 Basic Control Unit

The control unit, during user programs, is in charge of synchronizing the array for those instructions that require a synchronized array; it issues the "go" signal. It also handles those portions of the address computation that must be issued from a central point. The control unit executes the FMP-resident portion of the system software. It has a single shared memory (CUM) for both program and data.

# **FROM EU** 14 BITS ADDRESS PDM R/W STACK INITIATE (55 CHIPS) 55 TO/FROM T.N. TO/FROM 55 (LOADEM, **SECDED** STOREM) CHECKER/ **GENERATOR PARALLEL** TO 55 BITE-SERIAL CONVERSION TO/FROM CU (BDCST, HVST) **EU DATA BUS**

Figure 2-6. PDM Logic

ORIGINAL PAGE IS OF POOR QUALITY

#### TABLE 2-2 CHARACTERISTICS OF PROCESSOR DATA MEMORY

UNIT: Processor Data Memory (PDM) No. In System: 512 + 4 spares with spare processor (formerly processing element memory PEM)

FUNCTIONAL CHARACTERISTICS

Function: Stores temporary variables generated by the processor during computation.

Work space. Subroutine return information. Windows EM data.

Source of Control; During User Program: EU command lines

During System Startup and Diagnostics: Same

Storages; Capacity: 16,384 words.

Speed: 120 ns cycle

#### Connectivity to Other Elements:

| #           | Path                       | To or From                       | No.<br>Sig.   | Timing                                | Primary Use                                |

|-------------|----------------------------|----------------------------------|---------------|---------------------------------------|--------------------------------------------|

| 1<br>2<br>3 | data<br>address<br>control | To/from EU<br>From EU<br>From EU | 55<br>16<br>2 | static<br>static<br>edge or<br>static | Fetch and store data<br>Address<br>Command |

# RELIABILITY/REPAIRABILITY/TRUSTWORTHINESS

Error Control Methods: SECDED

Repair Method: Removed with entire processor. Not a separate entity.

MTBF of Unit: Dominated by control chips because of SECDED.

Degraded Modes Available: Programs compiled to less than 512 processors bypass failed 'PDM's. Error correction allows program to continue, but with reduced reliability, in single-bit failure cases. On-line switching of failed processors.

#### PHYSICAL

Chip Count: 1980 Projection: 70 (55 16k-bit mem + 15 control)

Physical Size; 1980: Part of processor assy.

Power Drain; 1980:

If use 1977 Parts: 250

(100K ECL, etc.) (220 4k-bit mem.

+ 30 control)

1977: Part of processor assy.

1977:

ORIGINAL PAGE IS OF POOR QUALITY.

#### FROM EU

Figure 2-7. PPM Logic

# TABLE 2-3 PROCESSOR PROGRAM MEMORY CHARACTERISTICS

UNIT: Processor Program Memory (PPM) No. In System: 512 + 4 spares with

spare processor FUNCTIONAL CHARACTERISTICS Function: Contains program for the processor. Is loaded using the BDCST path from the CU. Source of Control; During User Program: Processor's program counter. During System Startup and Diagnostics: Same Storages; Capacity: 8,192 words Speed: 120 ns Connectivity to Other Elements: No. Path To or From Sig. Timing Primary Use Fetch and load program program To/From EU 55 static Address 2 address From EU 16 static Command control From EU 2 edge or static RELIABILITY/REPAIRABILITY/TRUSTWORTHINESS Error Control Methods: SECDED Repair Method: Remove with entire processor. Not a separate entity. MTBF of Unit: See Chapter 5 Degraded Modes Available: Program compiled to less than 512 processors bypass failed PPM's. Error correction allows program to continue at reduced reliability, in single bit failure cases. On-line switching of failed processors. PHYSICAL Chip Count; 1980 Projection 43 If use 1977 parts: 140 (28 mem + 15 control) (100K ECL, etc.) (110 mem +30 control) Physical Size; 1980: Part of processor assy. 1977: Part of processor assy. Power Drain: 1980: 1977:

The control unit can also be controlled by commands from the host computer issued via the Diagnostic Controller (DC). This mode of operation is supplied for the purpose of performing diangostics.

The control unit is at once the most complex, in terms of variety of functions performed, and the most pedestrian, in terms of the demands it makes on the logic designer, of all the units in the FMP. Such hand analysis as has been done indicates that for the aerodynamic flow problems, the control unit will most of the time be waiting on the processors. One of the aims of the simulation is to find out if this statement is really true, or whether an investment in a faster control unit will pay off.

The frequency with which the CU executes system software upon interrupt, in the middle of user executions, will affect the required speed of the CU. The present plan is to so allocate the tasks in the system that during normal executions no interrupts either from host or resulting from FMP code are expected.

The host initiates file-system-to-DBM transfers using its copy of the DBM allocation map and issuing I/O commands directly to the DBM controller. No FMP-resident routine is involved in the initiation or completion of these transfers. The DBM controller resolves any potential conflict between these host transfers and a CU-initiated DBM-EM transfer.

Figure 2-7 is the block diagram of a control unit built around a single bus for transferring all data to and from memory, and using this same bus for one of the register file outputs. Such a structure defeats overlap but simplifies design. If simulation were to show that a faster CU is needed, a faster CU would be built.

2-24

In addition to the portion shown in Figure 2-8, the control unit also contains a section which resolves conflicts for EM between the instructions of the NSS and the needs of the DBM controller.

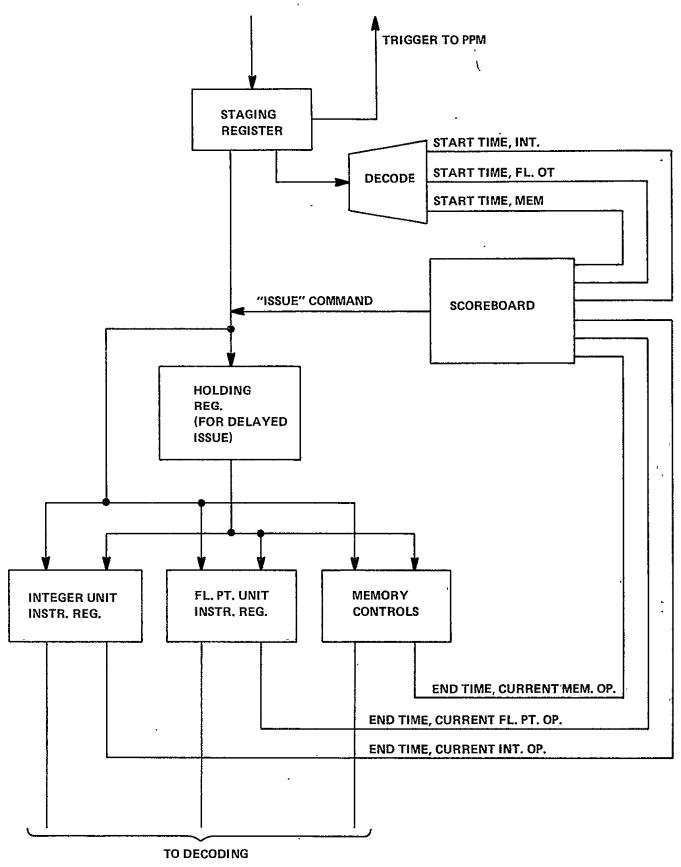

The control unit has four semi-independent execution stations, just as the processor has three. The degree to which the execution of the independent sections is to be overlapped is a subject for study during simulations in future work. Using the two aerodynamic flow models as benchmarks tells us that no overlap is required, therefore specifying an exact mechanism of overlap has been deferred. The four units are:

- \* Integer Unit

- \* Memory Control

- \* Floating Point Unit (optional, can be omitted if it is determined that so called scalar processor capability is not required for the contemplated applications. See Section 6.5)

- \* Interface to host and DBM controller

Instruction timing is given in the next section, 2.5. Table 2-4 lists the features of the CU.

#### 2.4.5.2 Scalar Processor

Floating point scalars are an item of concern in some applications. In the baseline system, an optional design feature to handle floating-point scalars is a floating-point arithmetic capability in the control unit. For a discussion of other options for attaching scalar capability to the FMP, see section 6.16. Scalar floating point capability is not be be confused with the "scalar unit" found in some other designs. The addressing and control functions of such a "scalar unit" are included in the control unit here whether or not the floating-point option is included.

# TABLE 2-4 CONTROL UNIT CHARACTERISTICS

| UNIT                                                                                                                                                                                                                    | : Contr                                                                               | l Unit: (CU) No. In System: 1 |                                                     |                                                                           |                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FUNC                                                                                                                                                                                                                    | TIONAL C                                                                              | HARACTERISTICS:               |                                                     |                                                                           |                                                                                                                                                                                                                                                                                                                          |

| Function: Executes the non-array portion of the FMP program. Executes the FMP resident portion of the system software.                                                                                                  |                                                                                       |                               |                                                     |                                                                           |                                                                                                                                                                                                                                                                                                                          |

| Source of Control; During User Program: Program stream contained in Control Unit Memory During System Startup and Diagnostics: Same plus commands issued from Diagnostic Controller                                     |                                                                                       |                               |                                                     |                                                                           |                                                                                                                                                                                                                                                                                                                          |

| Storages; Capacity: Integer Register file, perhaps 16 words, exact number to be determined by simulation. Floating point register file of 16 words.  Speed: Single-clock access to two registers per file. 40 ns clock. |                                                                                       |                               |                                                     |                                                                           |                                                                                                                                                                                                                                                                                                                          |

| Conn                                                                                                                                                                                                                    | ectivity                                                                              | to Other Elements:            |                                                     |                                                                           |                                                                                                                                                                                                                                                                                                                          |

| #                                                                                                                                                                                                                       | Path                                                                                  | To or From                    | Sig.                                                | Timing                                                                    | Primary Use                                                                                                                                                                                                                                                                                                              |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12                                                                                                                                                                  | control return control return control STORCU LOADCU command sync sync SYNC BDCST HVST | TO TN<br>From TN              | TBD<br>TBD<br>13<br>9<br>9<br>4<br>4<br>4<br>8<br>8 | TBD TBD TBD TBD TBD byte/20ns byte/20ns TBD edge edge byte/20ns byte/20ns | Control of DEM-EM transfers Completion, error, EM conflict resolution Control of EM Monitoring, errors, interrupt Control of TN Data to be stored in EM Data fetched from EM to CU Diagnostic commands to the processor Synchronization of array Synchronization of array Broadcast data Data (such as global max) to CU |

| Error Control Methods: TBD  Repair Method: TBD. Repair in place; FMP is down until CU repaired  MTBF of Unit: See Chapter 5  Degraded Modes Available: None.                                                            |                                                                                       |                               |                                                     |                                                                           |                                                                                                                                                                                                                                                                                                                          |

| PHYSICAL                                                                                                                                                                                                                |                                                                                       |                               |                                                     |                                                                           |                                                                                                                                                                                                                                                                                                                          |

| Chip Count; 1980 Projection: 3,000 chips (a coarse estimate)  Physical Size: 1980  Power Drain: 1980  If use 1977 parts: 4,000 chips (100k ECL, etc.)  1977:  1977:                                                     |                                                                                       |                               |                                                     |                                                                           |                                                                                                                                                                                                                                                                                                                          |

The FORTRAN language and compiler of chapter 3 makes no use of the floating-point option in the CU, as there was no use for it in the four codes used for benchmarking.

#### 2.4.6 Control Unit Memory (CUM)

The control unit memory holds both program and data for the control unit. It is addressible only from the control unit, and sends all data into the central data bus of the control unit.

The control unit memory is identical in electrical design and uses the same 16k-bit RAM chips as the processor memories. Its size is subject to verification via simulation. The size resulting from considerations of the flow-model matching study is 32,768 words.

The control unit memory is initially loaded from DBM at the beginning of each run using a routine which is itself resident in CUM and executes on the CU. The routine transfers data and program from DBM to CUM via EM.

Data on the control unit memory is found in Table 2-5.

# 2.4.7 Extended Memory Module

Extended memory (EM) is the "main" memory of the FMP, in that it holds the data base for the program during program execution. Temporary variables, or work space, can be held in either EM or PDM, as appropriate to the problem. All I/O to and from the FMP is to and from EM via DBM. Control of the EM is from two sources, the first is instructions executed in the CU, the second is the DBM controller which handles the DBM-EM transfers. In the baseline system design, the DBM-EM rate is such that the CU can be given first priority into EM without losing any of the DBM-EM transfers, therefore, the CU instructions have priority in the EM.

#### TABLE 2-5 CHARACTERISTICS OF CONTROL UNIT MEMORY

UNIT: Control Unit Memory (CUM) No. In System: 1 FUNCTIONAL CHARACTERISTICS Function: Contains data local to the CU, and CU's program. Also contains processor program as source for overlay during runs. Holds mailbox for host-FMP communication. Holds copy of DBM allocation map. Source of Control; During User Program: CU During System Startup and Diagnostics: Same plus may be accessed by DC if CU not running Storages; Capacity: 32,768 words. Speed: 120 ns cycle Connectivity to Other Elements: No. Path To or From Siq. Timing Primary Use To/from CU static Fetch and store data data 55 static 2 · address From CU 16 Address 2 command From CU edge or Command static RELIABILITY/REPAIRABILITY/TRUSTWORTHINESS Error Control Methods: SECDED Repair Method: FMP is down while CUM is down. Must replace failed modules for FMP to recover. MTBF of Unit: Dominated by control logic because of SECDED Degraded Modes Available: Error correction allows program to continue at reduced reliability; in single-bit failure cases.

PHYSTCAL

Chip Count; 1980 Projection: 175 chips

(110 mem + 15 control)

Power Drain; 1980:

Physical Size; 1980: TBD

2 - 28

If use 1977 parts: 470

1977: TBD

1977:

(100 ECL, etc.) 440 mem + 30 control)

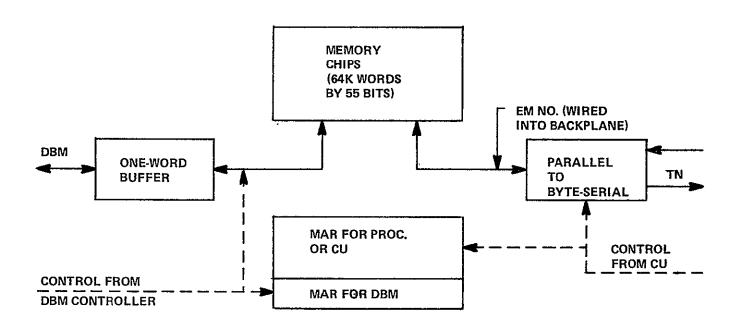

EM consists of 521 identical modules, which are accessed in parallel. 521 is a prime number for the sake of allowing efficient parallel fetching for all vectors of any length (with the minor exception of any vectors that happen to have elements spaced apart in memory by exactly 521).

From each EM module we need a transfer rate and access time consistent with the most economical implementation. For the baseline system, an implementation in 64k-bit dynamic RAM was chosen, as being the most economical implementation available by 1980. The low chip count also enhances reliability. Projections say that a 64k-bit chip will have 250 ns cycle time by that date. The 280 ns cycle time of the memory is compatible with the 140 ns per word transfer rate through the transposition network. Each word carries single- error-correction-double-error-detection code, which is generated at the source (DBM, CU, or processor) and also checked there, so that transfer paths are covered by the same error control as the contents of EM.

Having decided on a TN that is almost twice as fast as the EM module, it would be possible to build the EM module in two interlaced submodules, if it the streaming mode of fetching were to see much use. Section 6.10 discusses the tradeoff between implementing or not implementing this streaming mode of access. The baseline system as described in this document avoids the complexities of a design suitable for streaming, which includes among other things, a capability of incrementing the address in the EM module by nonunity increments. The chip count of table 2-6 does not include any incrementer.

Figure 2-9. EM Module

ORIGINAL PAGE IS OF POOR QUALITY

#### TABLE 2-6 EM MODULE CHARACTERISTICS

UNIT: EM Module No. in System: 521

FUNCTIONAL CHARACTERISTICS \_\_\_\_\_

Function: Stores problem data base during program executions. Most nearly corresponds

to "core" of conventional processor.

Source of Control; During User Program: Receives commands from CU

During System Startup and Diagnostics: Same

Storages; Capacity: 65,536 words

Speed: Access time 200-250 ns, interlaced for 140 ns/word block transfer

#### Connectivity to Other Elements:

| #           | Path             | To or From                 | No.<br>Sig. | Timing                                           | Primary Use                                                                                      |

|-------------|------------------|----------------------------|-------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 1<br>2<br>3 | LOADEM<br>STOREM | To TN<br>From TN<br>To DBM | 9<br>9<br>9 | byte/20ns<br>byte/20ns<br>full word<br>in 400 ns | Fetching data to processors and CU<br>Storing data from processors and CU<br>Results back to DBM |

| 4           |                  | From DBM                   | 9           | full word<br>in 400 ns                           | Initial data (and eventually, overlay) from DBM                                                  |

| 5           | No               | From<br>backplane          | 10          | D.C. level                                       | Module's own number                                                                              |

| 6           | Control          | From CU                    | TBD         | TBD                                              | Controls EM operations                                                                           |

## RELIABILITY/REPAIRABILITY/TRUSTWORTHINESS

Error Control Methods: SECDED (providing acceptable error rates are demonstrated)

Repair Method: Remove and replace

MTBF of Unit: Control dominates failure modes because of SECDED.

Degraded Modes Available: Data continues to be corrected even when there is one hard error, allowing the current program to complete before repairs are undertaken.

## PHYSICAL

Chip Count; 1980 Projection: 86 (55 memory + 30 control)

Physical Size; 1980: One medium sized

p.c. board

Power Drain: 1980

If use 1977 parts: 274

(100K ECL, etc.) (224 mem. + 50 control)

1977:

1977:

ORIGINAL PAGE IS OF POOR QUALITY

Figure 2-8 shows the EM module, including two address registers, a one-word buffer for DBM transfers, and an access path to the EM modules own number, wired into the backplane. Table 2-6 gives the data on the EM module.

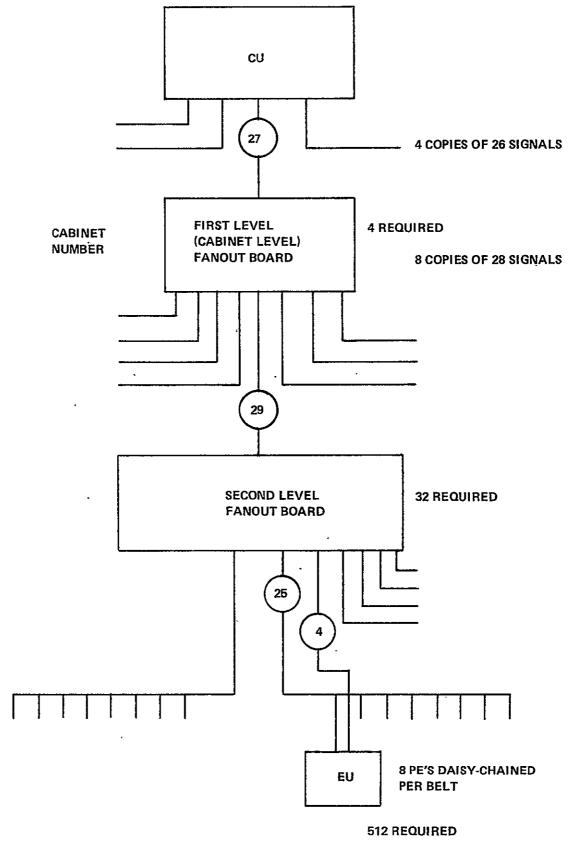

### 2.4.8 Fanout Tree

A series of fanout boards is supplied to provide the CU to processor connection. From CU to processor, signals fan out to a final 512 destinations. From the processors, the signals are combined, so that, within the CU, a single result appears in response to 512 signals emitted by the processors. For example, the "all processors ready" signal becomes true at the clock that the last enabled processor emits "I got here". Another such signal is the 512-input OR of "enabled".

At the processor, some signals are wired per-processor directly to the last level of fanout board; others are daisy-chained to eight processors from a single signal pin on the last board. The fanout boards are pin-limited. Simple buffers with one input pin and one output pin per signal dominate the circuit count, so hex buffers, easily available today, will not be improved upon by 1979-1980.

Data on the famout tree is in Table 2-7. The figure demonstrating the famout tree is Figure 2-10.

#### 2.4.9 Transposition Network

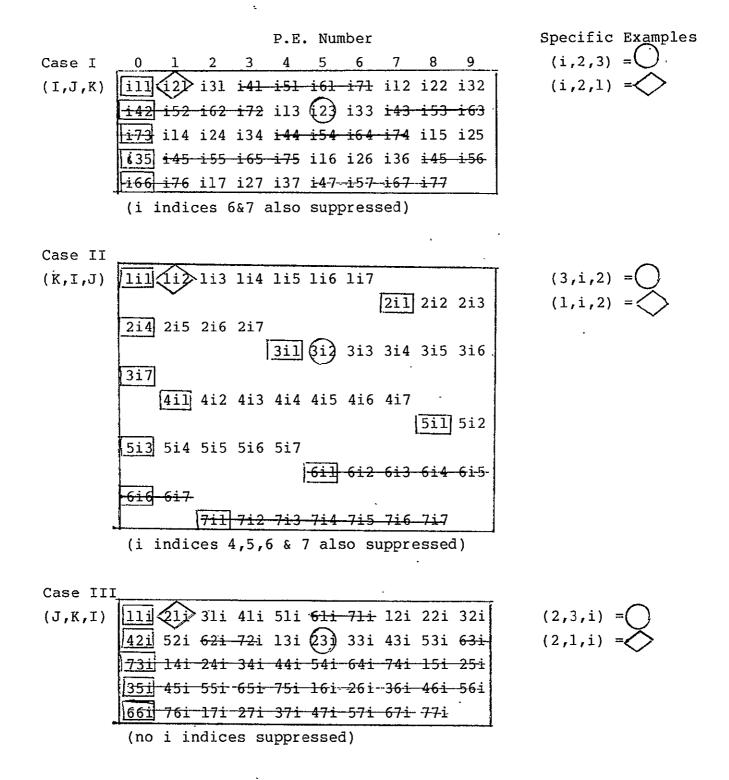

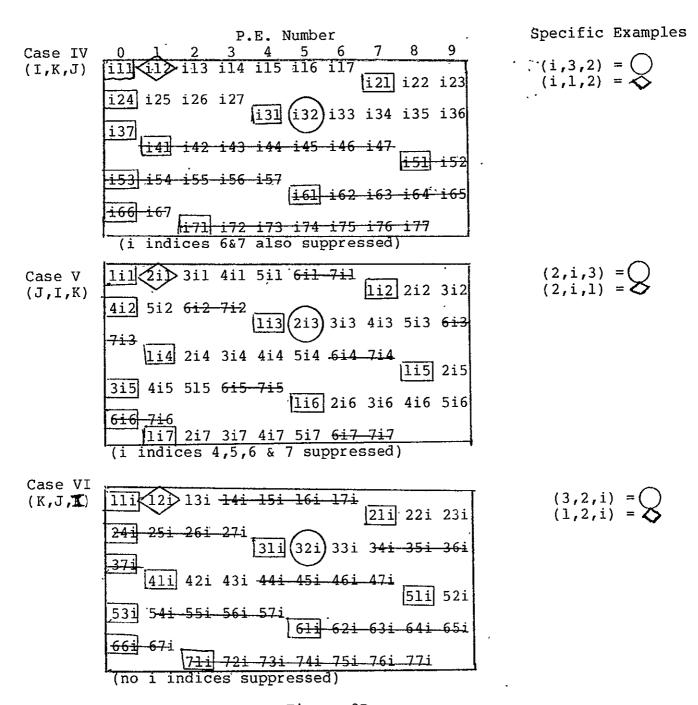

The transposition network allows the fully parallel, 512-wide, fetching of sets of variables that are to be processed in parallel. Up to 512 elements in one-dimensional vectors of any type can be fetched at full speed in parallel. When DOALL loops have two index variables, two-dimensional subsets of multidimentional arrays can also be fetched in parallel. For details, see Ref 1, and Chapter Three.

Figure 2-10. Fanout Tree

ORIGINAL PAGE IS OF POOR QUALITY

#### TABLE 2-7 FANOUT TREE CHARACTERISTICS

UNIT: Fanout Tree, CU to Processors No. In System: 1

FUNCTIONAL CHARACTERISTICS

Function: Provides famout for signals from CU to the 512 processors; accepts signals from the 512 processors and combines them appropriately for the CU. Consists of 36 boards.

Source of Control; During User Program: No control; all passive logic.

During System Startup and Diagnostics: Same

#### Connectivity to Other Elements:

| #  | Path    | To or From     | No.<br>Sig. | Timing    | Primary Use                                                                  |

|----|---------|----------------|-------------|-----------|------------------------------------------------------------------------------|

| 1  | command | From CU        | 4           | TBD       | Diagnostic                                                                   |

| 2  | sync    | From CU        | . 4         | edge      | Synchronization of array                                                     |

| 3  | sync    | To CU          | 4           | edge      | Synchronization of array                                                     |

| 4  | BDCHT   | From CU.       | 8           | byte/20ns | Broadcast data                                                               |

| 5  | HVST    | To CU          | 8           | byte/20ns | Data to CU (such as global MAX)                                              |

| б  | command | To proc. 8's   | 4(x 64)     | TBD       | Diagnostic                                                                   |

| 7  | sync    | To proc. 8's   | 4(x 64)     | edge      | Synchronization of array                                                     |

| 8  | sync    | From proc.     | 4(x 512)    | edge      | Synchronization of array                                                     |

| 9  | BDCST   | To proc. 8's   | 8(x 64)     | byte/20ns | Broadcast data                                                               |

| 10 | HVST    | From proc. 8's | 8(x 64)     | byte/20ns | 512-input OR of data from processor to CU. 1st 8-way OR done on proc. wiring |

## RELIABILITY/REPAIRABILITY/TRUSTWORTHINESS \_\_\_\_\_

Error Control Methods: SECDED on broadcast and harvest data.

Repair Method: Remove and replace of defective boards.

MIBF of Unit: See Chapter 5. Degraded Modes Available: None

#### PHYSICAL

Chip Count; 1980 Projection: 2,000 chips all small scale integration. Dominated by

(100K ECL, etc.)

If use 1977 parts: 2,000 chips

1,504 hex buffers.

Physical Size; 1980: 32 cards of 60-80 chips

1977: Same

Power Drain; 1980: 1.6 kw

1977: Same

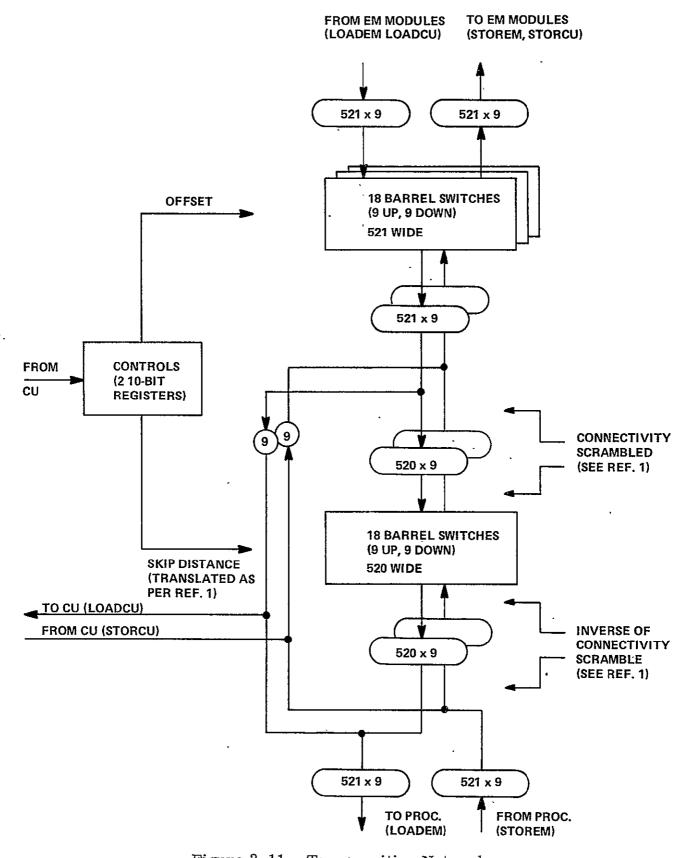

ORIGINAL PAGE IS OF POOR QUALITY The transposition network consists of 521 switchable data paths from EM to processor, and another 521 data paths from processor to There are two 10-bit control registers, one for offset of the starting element, and one for skip distance. Since there are two sets of data paths, the first from processor to EM module, and the second from EM module to processor, the settings of the two paths There is just one instruction could be separately controlled. that would go faster if both paths are used simultaneously with different settings, namely SHIFTN (see Table 2-10 and 2-11 for a SHIFTN is used in functions that operate description). "horizontally" across the parallelism of the array, such as global sum, global maximum, or global product. SHIFTN would also be used to implement a Fast Fourier transform on the FMP. In the aero codes used as benchmarks, there is very little use of SHIFTN, so there is no justification for having separate settings for the first and second data paths, and bidirectional data paths would serve as well.

A three-bit command register enables the following commands:

- 1. Enable transfers between processor and EM. The presence or absence of actual transfer is signified by the presence or absence of a signal on the strobe line that accompanies each byte-wide signal path.

- 2. Enable transfers between CU port and EM.

- 3. Enable transfers between the remaining eight paths and EM (built into the design to allow these eight ports to service the scalar processor).

- Broadcast from selected EM module to all processors.

Table 2-8 gives the characteristics of the transposition network. Figure 2-11 shows the barrel switches that implement it.

Figure 2-11. Transposition Network

## TABLE 2-8 TRANSPOSITION NETWORK CHARACTERISTICS

UNIT: Transposition Network (TN) No. In System: 1 FUNCTIONAL CHARACTERISTICS Function: Provides 521 data paths for fetching in parallel from all EM modules to all processors; provides 521 data paths for storing in parallel from all processors to 512 EM modules. Provides path from any one EM module to all processors. Provides data path to any EM module from CU, also path from any EM module to CU. Source of Control; During User Program: Commands from CU. During System Startup and Diagnostics: Same Storages; Capacity: None. Command register 10 bits offset, 10 bits skip distance, about 3 bits of command. Speed: Connectivity to Other Elements: No. Path To or From Sig. Timing Primary Use LOADEM 9(x 512) 20ns/byte Data to processor during LOADEM To Processor From Processor 9(x 512) byte/20ns EM addresses and STOREM data from proc. STOREM 3 To CU LOADCU byte/20ns Data to CU during LOADCU 4 STORCU From CU 9 byte/20ns Data and address from CU. 5 To EM modules 9(x 521) byte/20ns Data and address to EM modules 6 From PM modules 9(x 521) byte/20ns Data from EM modules 7 control From CU 13  $\mathbf{T}\mathbf{B}\mathbf{D}$ Reset controls To TBD byte/20ns 8 9(x 8)Reserved for scalar processor spare byte/20ns 9(x 8) Reserved for scalar processor From TBD spare RELIABILITY/REPAIRABILITY/TRUSTWORTHINESS Error Control Methods: SECDED applied to EM word passes through TN. Detects hard failures, corrects transients. Repair Method: TBD MTBF of Unit: See chapter 5 Degraded Modes Available: Some portion of the TN can be bypassed by programs that are compiled for a less-than full complement of processors. Most, however, cannot. PHYSICAL Chip Count; 1980 Projection: 10,980 If use 1977 parts: 17,270 (10,480 shifter chips + 500 control) (100K ECL, etc.) 16,770 F 100158 chips + 500 control) Physical Size; 1980: About 200 boards 1977: Same

1977:

2 - 37

if 200 signals allowed per board. Is

pin limited.

Power Drain: 1980:

#### 2.4.10 Data Base Memory (DBM)

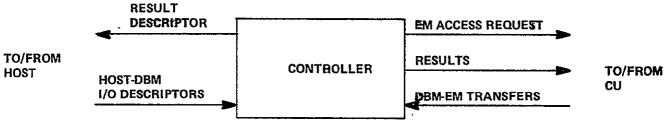

Data Base Memory (DBM) is the window in the computational envelope of the FMP. All jobs to be run on the FMP are staged into DBM before running both program and data, all output from the FMP is staged through the DBM. At some future time (but not with the initial operating system) DBM could be used to back up EM for those problems whose data base is larger than EM. Control of the data base memory is from a DBM controller, which accepts commands both from the CU for transfers between DBM and EM, and from the host for transfers between DBM and the file system.

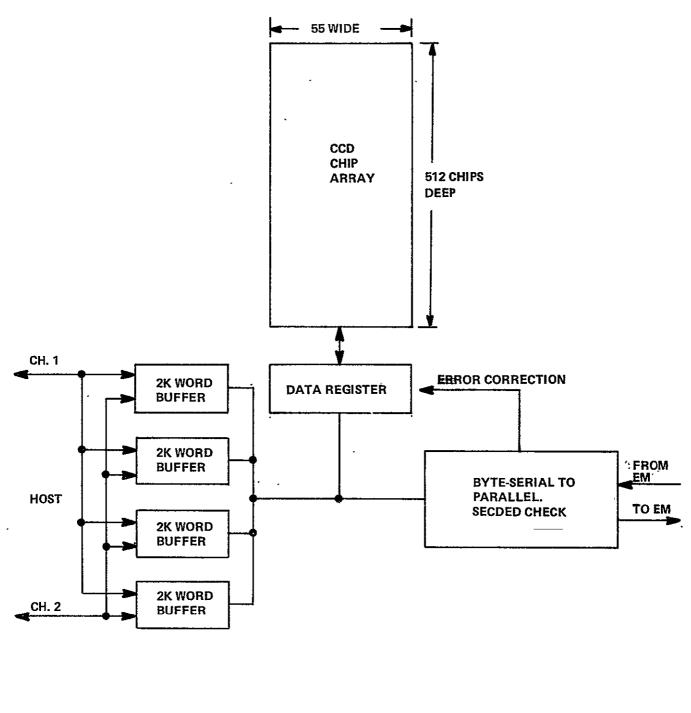

Many design options exist for the data base memory. Out of this set of options one particular design was chosen for the baseline system. This chosen design is a CCD memory built out of 256k-chips, which are projected to be available in the 1980 period. If data base memory were to be built before the appearance of sufficiently economical CCD chips, one would use some form of parallel-head rotating magnetic storage. The design described here is based on the existence of 256k-bit CCD chips each arranged in the form of 128 shift registers of 2,048 bits each.

With a projected shift rate of 2.5 MHz in the CCD chips, a desired transfer rate of 2.5 Mwd/s to and from EM, DBM is built 55 chips wide, for parallel emission of 55-bit words, by 512 chips deep. The natural block size with 2,048 bits in each shift register delivering a block of 2,048 words, is adopted. There are 64k blocks for a total of 134,217,728 words. Error correction is a SECDED, probably the modified Hamming-plus-parity implemented by Motorola's 10,163 chip.

Since the array of CCD chips is 512 x 55, the DBM is constructed in a number of physical modules, say each one 64 x 55 chips. The repair philosophy is to pull and replace individual modules, and the degraded mode of operation would be to run with one or more modules missing, and the operating system would have to know to avoid assigning any data to that space.

There are several (probably four) block-sized buffers, which stand between the CCD storage and the host interface, in order to reduce the interference with DBM-EM transfers produced by simultaneous DMB-host transfers. They can also serve as timing buffers to the host's disk packs. See Fig. 2-12.

After the transfer of a block to or from the CCD store, the shift registers rest at the starting position until shifting is required by the refresh requirements, or until the CCD store is again addressed, whichever occurs first. Therefore, whenever there are several requests for transfer pending at once, or when they occur with sufficient frequency, the access time is essentially zero to the first word of the block. For transfers arriving at random times, far enough apart in time so as not to interfere, the average access time is given by:

$$T_{av} = \frac{1}{2} (T_b 2/T_r)$$

where  $T_{\rm b}$  is the transfer time of a single block (0.82 ms) and  $T_{\rm r}$  is the time between refreshes.  $T_{\rm r}$  will be in the specification of the device, and is expected to lie between 1 ms and 10 ms. Therefore, the average access time for random data at low usage, to the first word of the block, has an upper bound which is expected to lie between 0.67 ms and 0.067 ms. As traffic increases, the access time is mostly due to interference between competing accesses, while the contribution due to delay in the memory goes to zero.

Figure 2-12. DBM Block Diagram

#### TABLE, 2-9 DATA BASE MEMORY CHARACTERISTICS

No. In System: 1 UNIT: Data Base Memory (DBM) and its controller

FUNCTIONAL CHARACTERISTICS

Function: In this memory, data is staged for FMP jobs not yet started, and results of FMP jobs are output from the FMP. Almost all communication between FMP and host goes through this memory, both data and program. CCD storage is postulated, although other options are available, including disk pack. Resolves host-CU conflicts.

Source of Control; During User Program: DBM-EM transfers controlled from CU, DBM-host transfers controlled from host.

During System Startup and Diagnostics: Same

Storages; Capacity: 134 x 10<sup>6</sup> words in blocks Speed: 140 Mb/s (an easily adjustable parameter)

### Connectivity to Other Elements:

|   | #   | Path    | To or From                                   | Sig.                          | Timing                                             | Primary Use                                                  |

|---|-----|---------|----------------------------------------------|-------------------------------|----------------------------------------------------|--------------------------------------------------------------|

|   |     |         | To/from EM<br>To/from host                   | 8+8<br>TBD, 2<br>paths<br>min | words/40 ns<br>rate matches<br>host file<br>system | ·                                                            |

|   | 3   | control | From CU                                      | TBD                           | TBD                                                | Receives control from CU for DBM-EM transfers                |

|   | 4   | result  | To CU                                        | TBD                           | TBD                                                | <u></u>                                                      |

| • | 5 į | control | From host                                    | TBD                           | TBD                                                | Receives control from host for DBM-<br>file-system transfers |

|   | 6 . | result  | To host                                      | TBD                           | TBD                                                | Monitoring and error cases                                   |

|   |     |         | /Denos ex s ex x x x x x x x x x x x x x x x | <i>(</i>                      |                                                    | !                                                            |

|   |     |         |                                              |                               |                                                    |                                                              |

RELIABILITY/REPARIABILITY/TRUSTWORTHINESS

Error Control Methods: TBD. SECDED may be adequate, and will be used if so. "Scrubbing" errors arising due to refresh will be needed in CCD memories. Repair Method: TBD.

MTBF of Unit: Domniated by controls since SECDED on memory.

Degraded Modes Available: Error correction codes allow valid data to be fetched in spite of errors in memory. Can operate with failed modules removed.

PHYSICAL

Chip Count; 1980 Projection: 29,160 (28,160 mem + 1,000 control)Physical Size: 1980: about 150 large boards 1977: eight disk pack drives Power Drain; 1980:

If use 1977 parts: (100K ECL, etc.) use disk pack 1977:

> ORIGINAL PAGE IS OF POOR QUALITY

As a background job, the DBM controller periodically initiates an access for the purpose of reading the contents of a block and rewriting that same block with all detectable errors corrected, since errors are spontaneously created in CCD memories at a low rate during the refresh operation. It has been conjectured that these errors are caused by cosmic ray bombardment of the CCD chips, discharging the little capacitors by temporarily ionizing The rate of periodically initiating access can rationally be determined only after getting the vendor's specification on the number of refreshes per error. Preliminary Fairchild data, if it continues to be true, indicates that one should scrub through the entire DBM every seven minutes, or that this background task should occur at one eighth the normal bandwidth of the DBM. Therefore, this background access is initiated every 6.55 ms. Only one error-scrubbing access will be pending at a time, even if the delay in starting exceeds 6.55 ms. They are not queued.

The DBM has a number of channels into the file system of the host. The number is to be determined by simulation. Initial estimates are that two channels provide more channel capacity than needed for the aerodynamic flow models. At least two are needed for reasons of reliability. Two are assumed for the baseline system design.

No buffering is needed on the EM side beyond the one-word buffers in each EM module. The CU will guarantee the acceptance by the EM of a word coming from DBM is less than 400 ns. Likewise, when transferring from EM to DBM, the EM module has its one-word buffer loaded nominally 800 ns or more ahead of the DBM requirement, and this time will not slip by more than 400 ns from interference with array transfers.

DBM-EM transfers have priority in the EM controls. However, there is little interference with CU-initiated EM transfers. For example, when transferring from EM to DBM, one EM cycle loads 521 of the per-EM-module one-word buffers, and then waits for 208 microseconds before another EM cycle is required for the DBM transfer path.

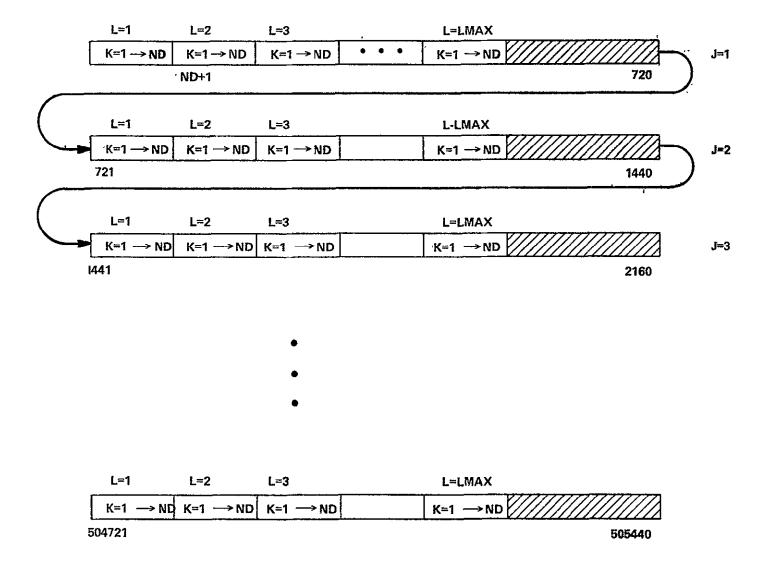

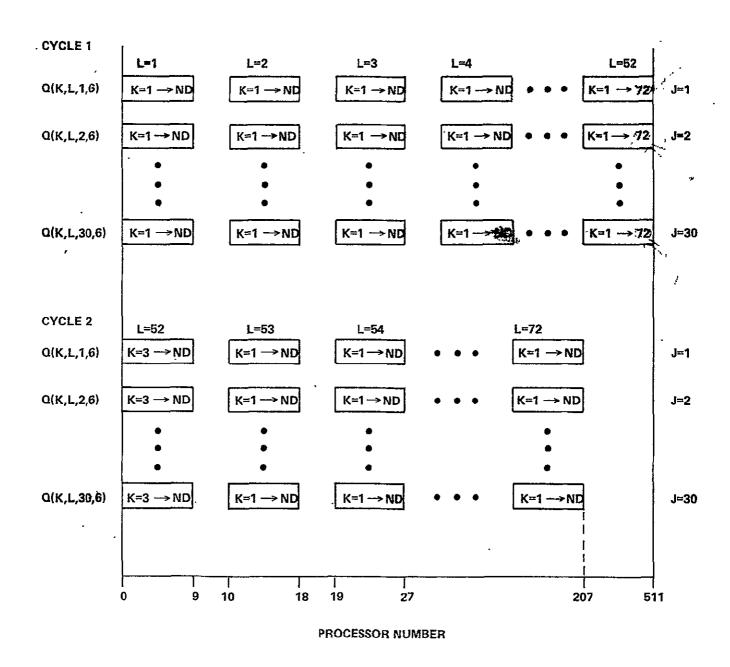

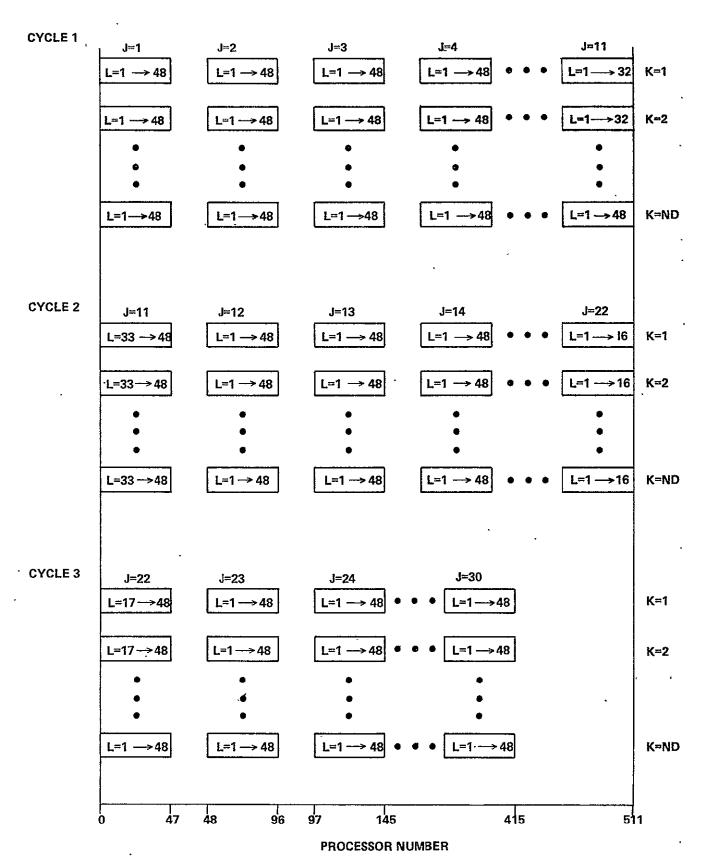

A design decision, to be made with the aid of simulation in phase II, is whether the LOADEM and STOREM instructions should be limited to 512 words per execution, or whether they should transfer 512 x N words at a time. The description given above is concordant with a design in which LOADEM and STOREM are 512-word instructions, which are the only use made of LOADEM and STOREM in the FORTRAN compiler described in Chapter Three. In Chapter Six the implications of this choice are discussed at further length.

Use of DBM is as a staging area for jobs going into the FMP or coming out of the FMP. The hardware design also permits its use as a source for overlaying data and program into the FMP. It is possible to transfer less than a full block, but not to start any place other than the beginning of the block. A decision to make heavy use of the overlay capability would result in reevaluating the transfer rate between EM and DBM.

#### 2.5 INSTRUCTION SET AND INSTRUCTION TIMING

This section lists the instruction set together with a list of numbers giving the execution times of each.

#### 2.5.1 Tables