### **General Disclaimer**

### One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some

of the material. However, it is the best reproduction available from the original

submission.

156748

N78-22272

(NASA-CR-156748) DESIGN AND DEMONSTRATION N78-223

OF AN ADVANCED DATA COLLECTION/POSITION

LOCATION SYSTEM Final Report, Aug. 1976 Jul. 1977 (Texas Instruments, Inc.) 175 p

Unclas

HC A08/MF A01

# TEXAS INSTRUMENTS

INCORPORATED

# FINAL REPORT FOR THE

### DESIGN AND DEMONSTRATION OF

# AN ADVANCED DATA COLLECTION/POSITION

### LOCATION SYSTEM

Prepared for

NASA-GODDARD

SPACE FLIGHT CENTER

Prepared by

Equipment Group

01-879210-F

Contract NAS 5-23599

# TEXAS INSTRUMENTS

### FOREWARD

The work described in this report was performed by the Space Systems Department, Equipment Group, Texas Instruments Incorporated, Dallas, Texas, under NASA Contract NAS 5-23599 for Goddard Space Flight Center. The reporting period is from August 1976 to July 1977. The technical director of this investigative program was James L. Coates. He was assisted by John F. DuBose Jr., James D. Quarfoot, and Joffrey K. Majors of the Space Systems Department and William L. Eversole of the Central Research Laboratory of Texas Instruments. Acknowledgement and appreciation are also due Earle Painter of GSFC for his constructive critiscism and suggestions throughout the course of the program.

# TABLE OF CONTENTS

| Section | Title                                     | Page No |

|---------|-------------------------------------------|---------|

| Ι.      | INTRODUCTION AND SUMMARY                  | 1-1     |

| ••      | A. Introduction                           | 1-1     |

|         | B. Breadboard Description                 | 1-1     |

|         | C. Description of Tests                   | 1-4     |

|         | D. Conclusion                             | 1-5     |

| II.     | HARDWARE DESCRIPTION                      | 2-1     |

|         | A. Introduction                           | 2-1     |

|         | B. Breadboard System Features             | 2-1     |

|         | 1. MSK Transmitter Simulator Features     | 2-3     |

|         | 2. Communications Link Simulator Features | 2-6     |

|         | 3. Search Subsystem Simulator Features    | 2-7     |

|         | 4. Receive Channel Simulator Features     | 2-9     |

|         | C. Breadboard Frequency Plan              | 2-11    |

|         | D. MSK Transmitter Simulator              | 2-16    |

|         | 1. Data Generator                         | 2-18    |

|         | 2. Data Checker                           | 2-24    |

|         | 3. MSK Modulator                          | 2-27    |

|         | E. Communications Link Simulator          | 2-34    |

|         | F. Search Subsystem Simulator             | 2-40    |

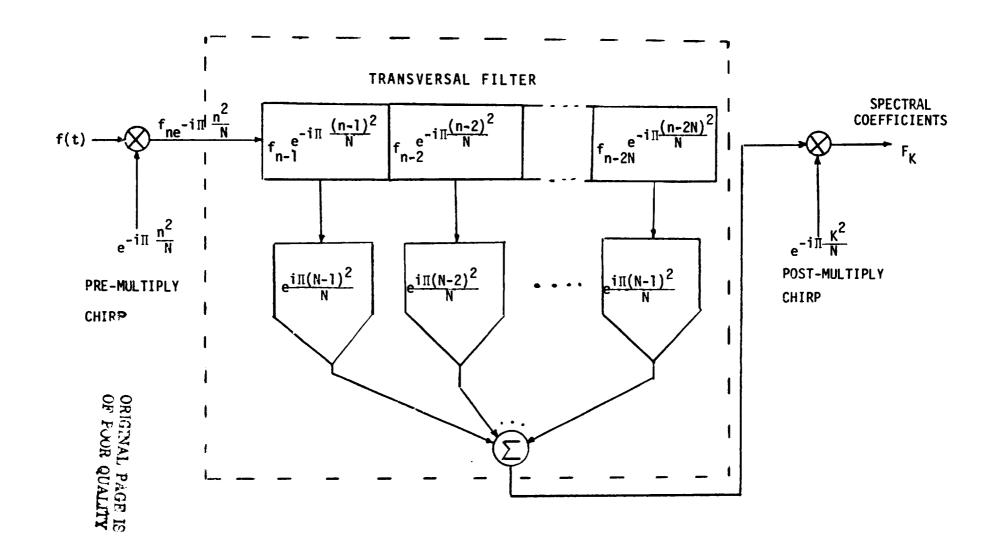

|         | 1. Chirp-Z Transformer                    | 2-40    |

|         | a. Theory of Operation                    | 2-40    |

|         | b. Hardware Implementation                | 2-50    |

|         | 2. Simulator Implementation               | 2-53    |

|         | G. Receive Channel Simulator              | 2-60    |

|         | 1. Non-Coherent MSK Demodulator           | 2-61    |

|         | 2. Frequency Measurement Circuit          | 2-67    |

|         | 3. Coherent MSK Demodulator               | 2-69    |

| III.    | BREADBOARD TEST RESULTS                   | 3-1     |

|         | A. Introduction                           | 3-1     |

|         | B. Chirp-Z Transformer Test Results       | 3-4     |

|         | 1. General                                | 3-4     |

#((\$ a))

Broders.

(41.) (B.R.)

Se of pear

Physical C

# TABLE OF CONTENTS (CON'T)

| Section |     | Title                                                        | Page       |

|---------|-----|--------------------------------------------------------------|------------|

|         |     | 2. Probability of Detection/False Alarm Rate Measurements    | 3-7        |

|         |     | 3. Dynamic Range Measurements                                | 3-25       |

|         |     | 4. Search Time and Channel Reassignment Time                 | 3-31       |

|         |     | 5. Temperature Considerations of CCD Devices                 | 3-32       |

|         | c.  | MSK Non-Coherent Demodulator Test Results                    | 3-33       |

|         | D.  | Alternative Non-Coherent Demodulation Schemes a Test Results | nd<br>3-56 |

|         | Ε.  | Frequency Measurement Test Results                           | 3-61       |

|         | F.  | Throughput Test Results                                      | 3-65       |

| īV.     | ANA | LYSIS OF RESULTS                                             | 4-1        |

|         | A.  | Introduction                                                 | 4-1        |

|         | В.  | Impact of the Chirp-Z Transformer on ADC/PL Systems          | 4-1        |

|         | C.  | Impact of MSK Modulation on ADC/PL Systems                   | 4-4        |

|         | D.  | Sample System                                                | 4-10       |

|         | E.  | RF Equipment for Landsat II Compatibility                    | 4-18       |

12.0 M

### LIST OF ILLUSTRATIONS

| Figure | Title                                                                                                      | Page |

|--------|------------------------------------------------------------------------------------------------------------|------|

| 2-1    | MSK/Chirp-Z Transformer Breadboard Configuration                                                           | 2-2  |

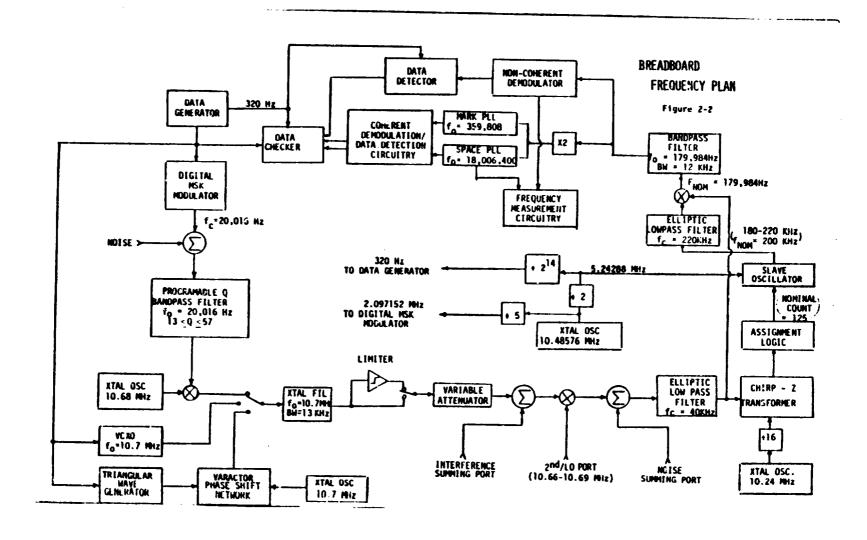

| 2-2    | Breadboard Frequency Plan                                                                                  | 2-12 |

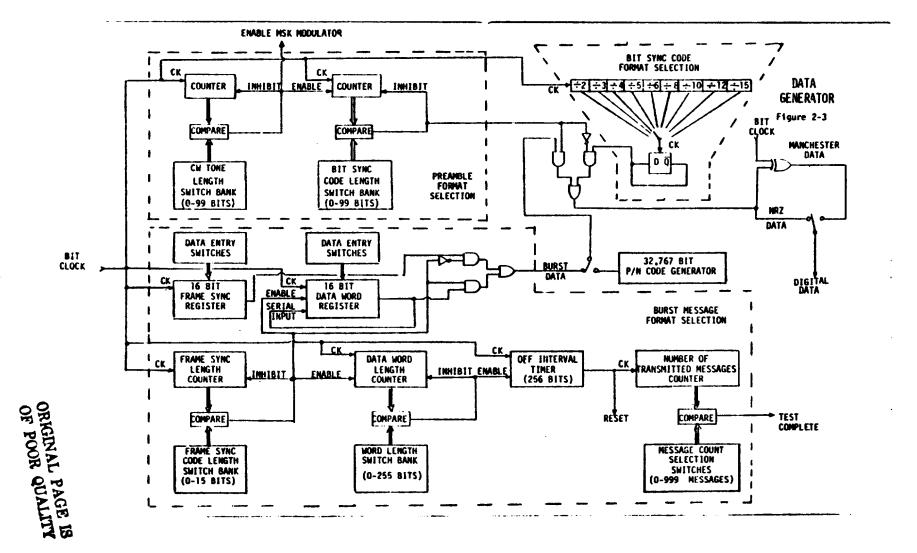

| 2-3    | Data Generator                                                                                             | 2-19 |

| 2-4    | Data Generator Message Formats                                                                             | 2-22 |

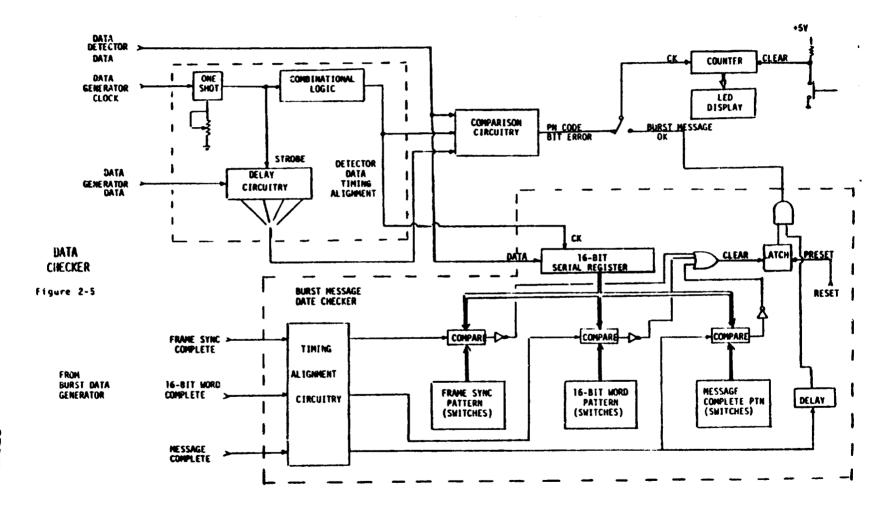

| 2-5    | Data Checker                                                                                               | 2-25 |

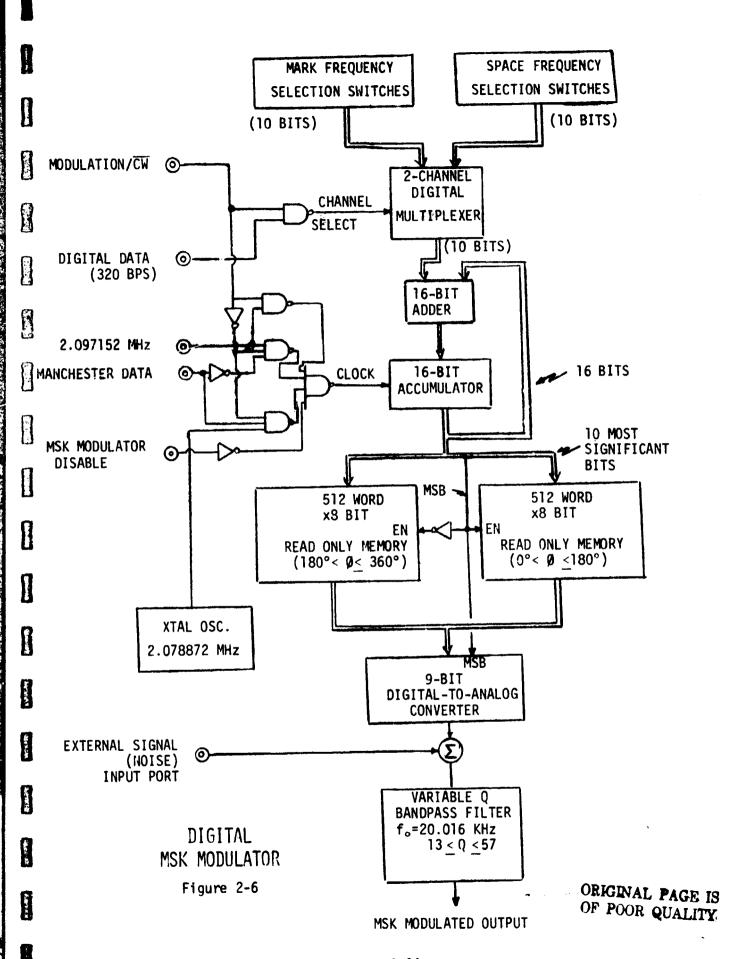

| 2-6    | Digital MSK Modulator                                                                                      | 2-29 |

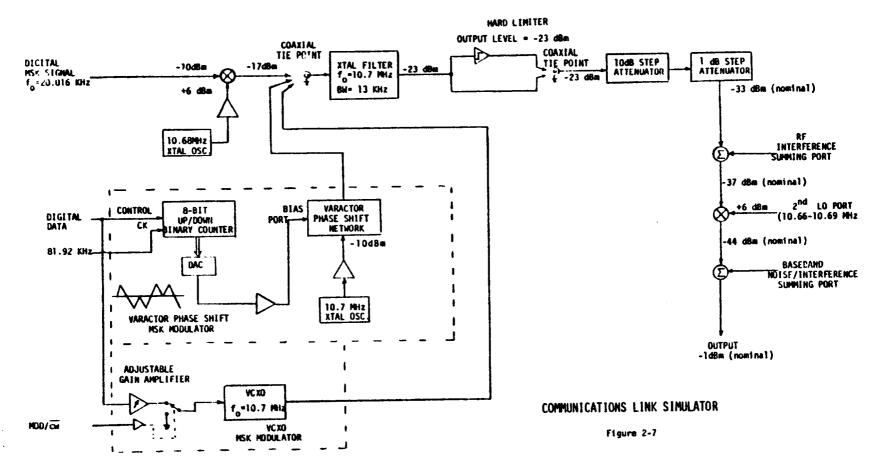

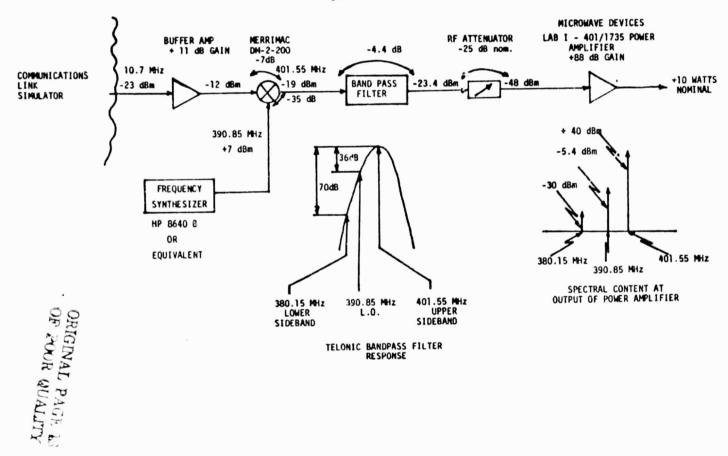

| 2-7    | Communications Link Simulator                                                                              | 2-35 |

| 2-8    | Chirp-Z Transformer Operation                                                                              | 2-42 |

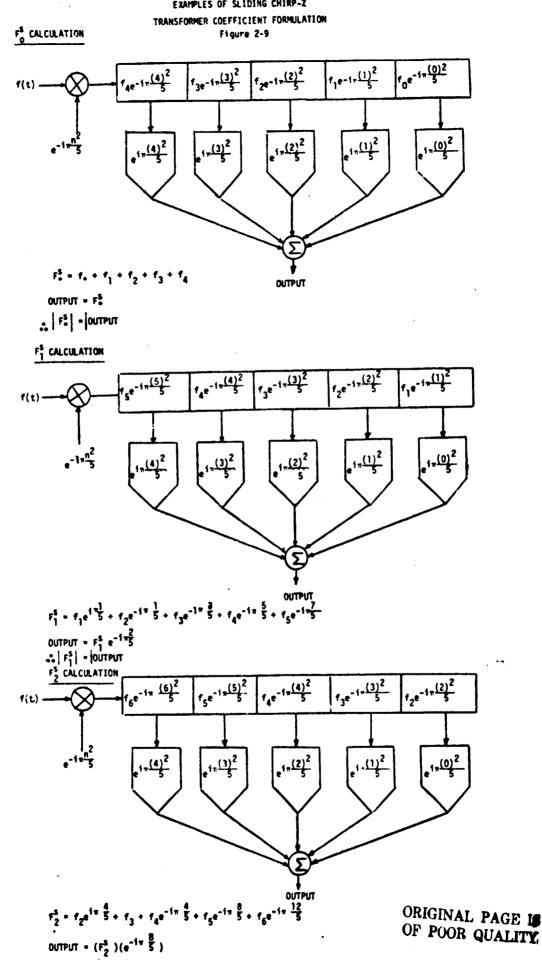

| 2-9    | Examples of Sliding Chirp-Z Transformer Coefficient Formulation                                            | 2-45 |

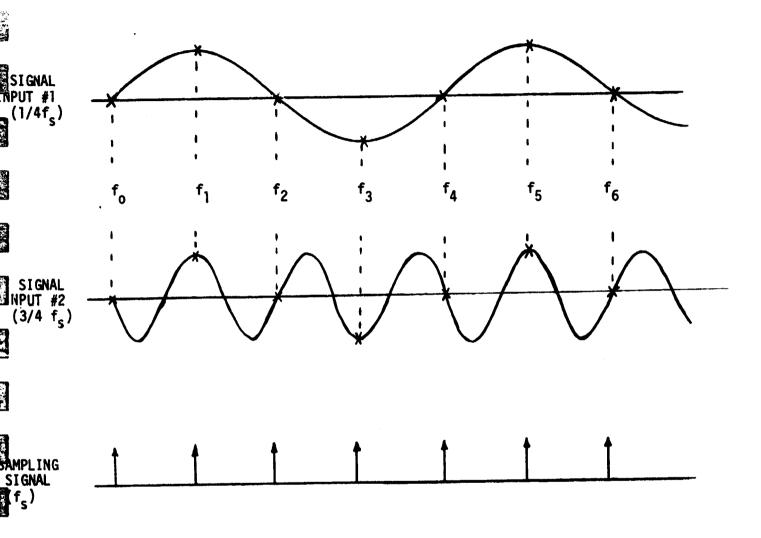

| 2-10   | Frequency Foldover Example                                                                                 | 2-48 |

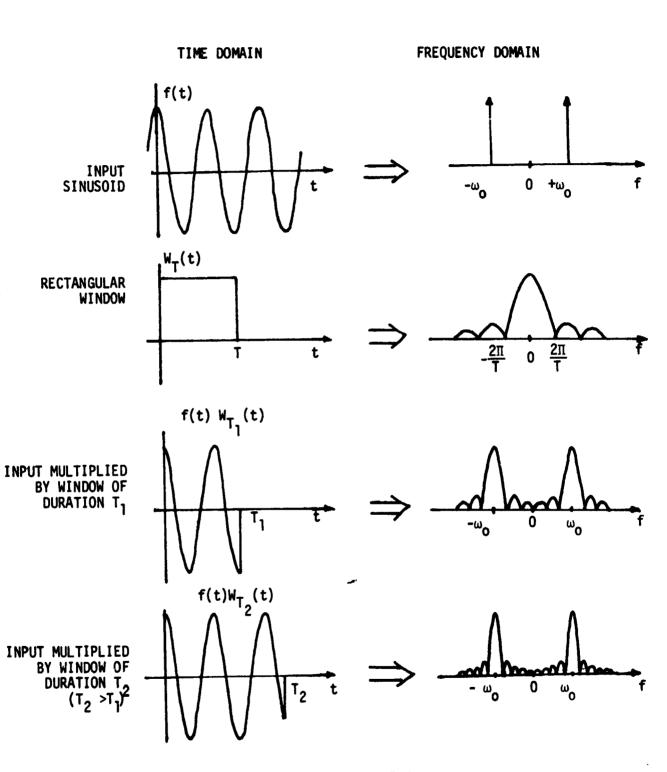

| 2-11   | The Need for Apodization                                                                                   | 2-49 |

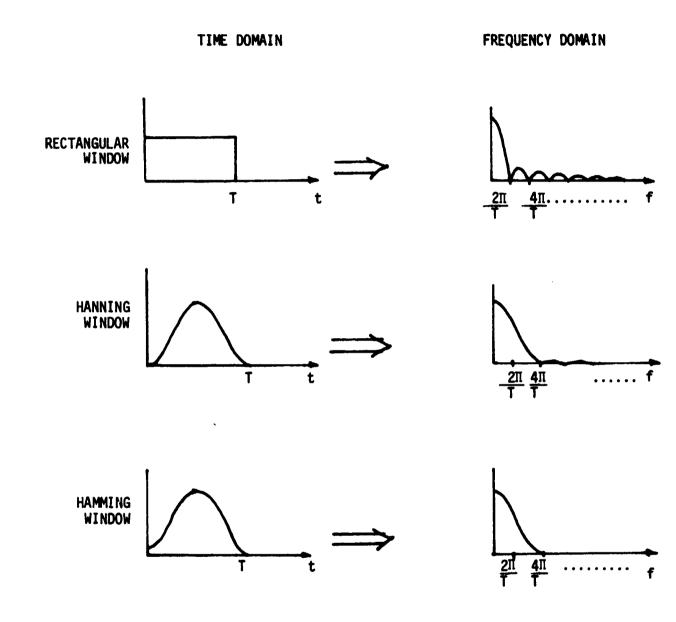

| 2-12   | Different Sampling Windows and Their Spectra                                                               | 2-51 |

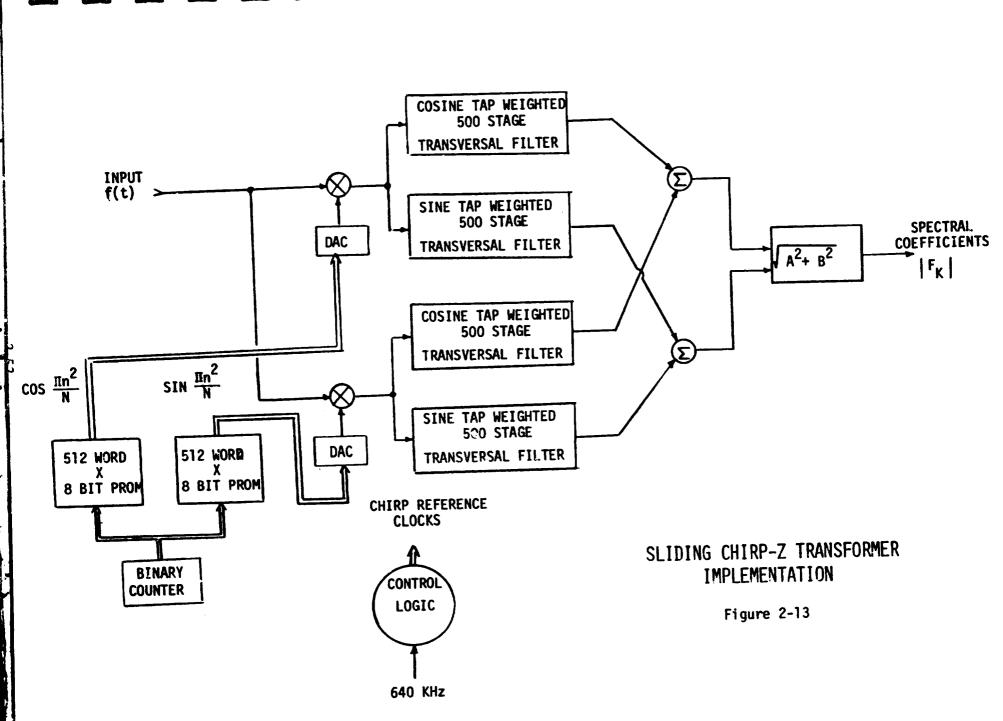

| 2-13   | Sliding Chirp-Z Transformer Implementation                                                                 | 2-52 |

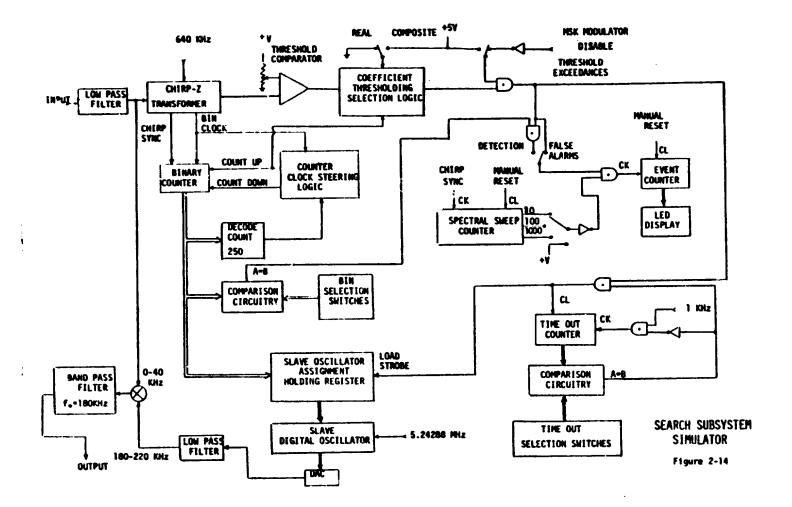

| 2-14   | Search Subsystem Simulator                                                                                 | 2-54 |

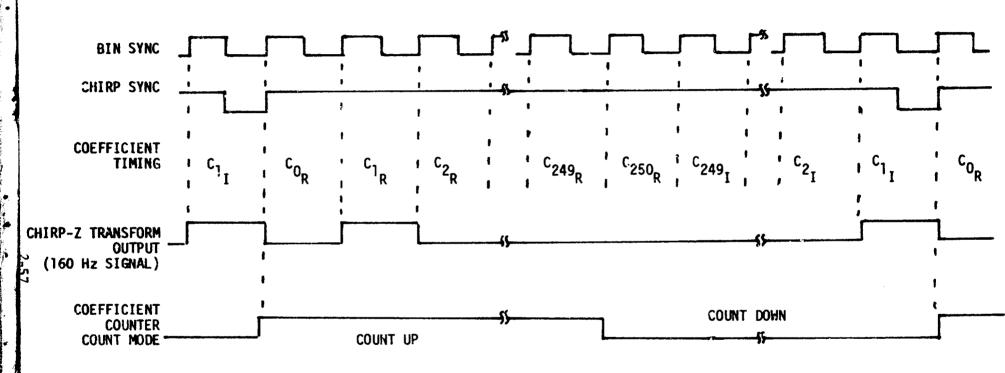

| 2-15   | Chirp-Z Transformer Spectral Coefficient Timing                                                            | 2-57 |

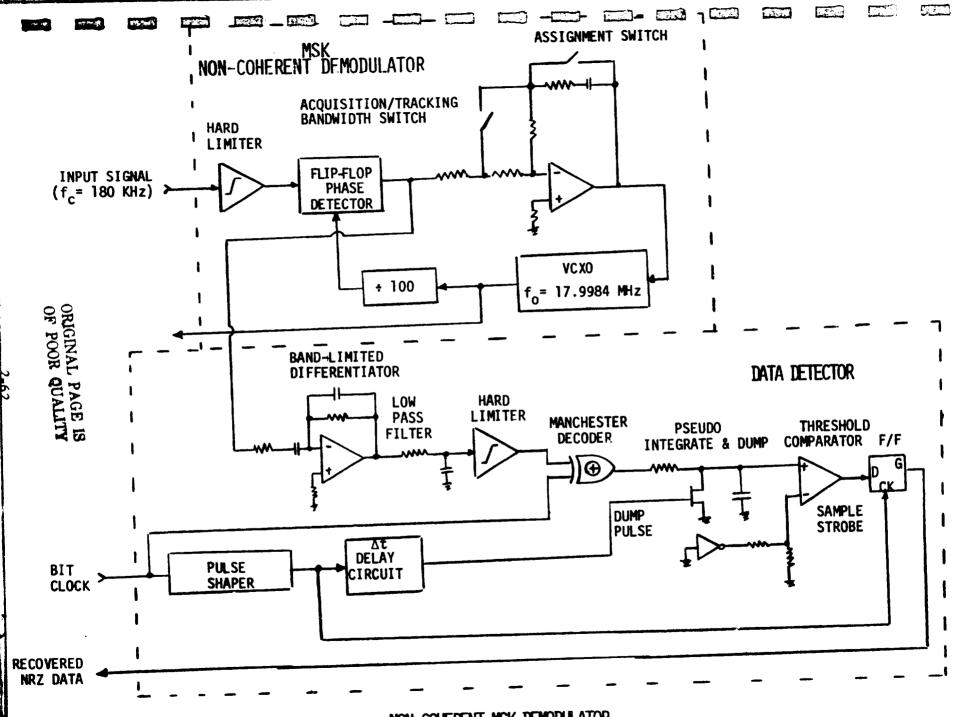

| 2-16   | Non-Coherent MSK Demodulator and Data Detector                                                             | 2-62 |

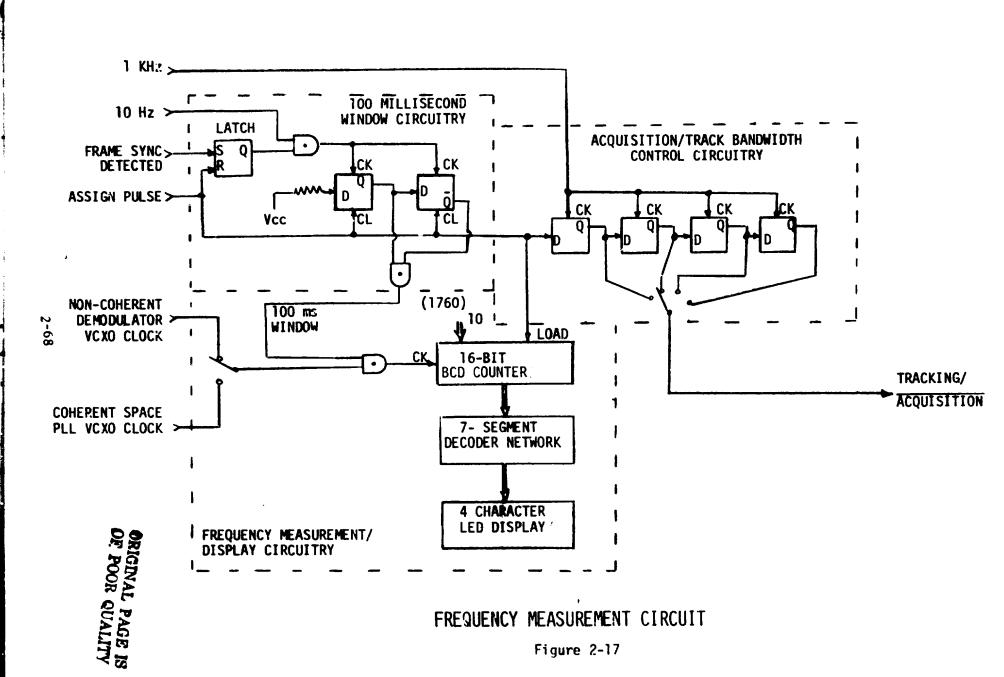

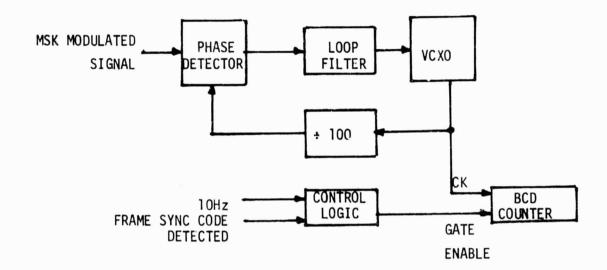

| 2-17   | Frequency Measurement Circuit                                                                              | 2-68 |

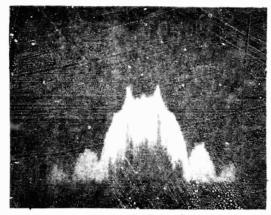

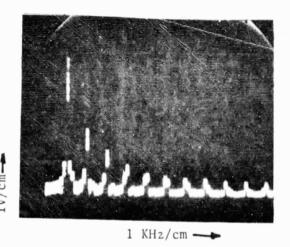

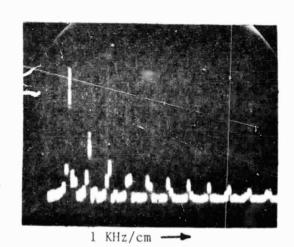

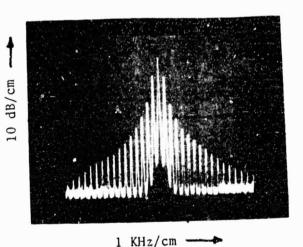

| 3-1    | Spectra of MSK Modulation As Processed by HF 14IT Spectrum Analyzer                                        | 3-2  |

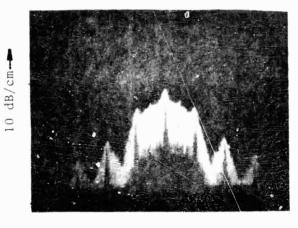

| 3-2    | Spectra of Different Signal Waveforms Processed by the Chirp-Z Transformer                                 | 3-5  |

| 3-3    | Spectra of MSK Modulation                                                                                  | 3-6  |

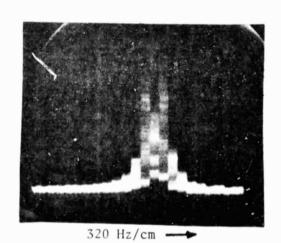

| 3-4    | Chirp-Z Transformer Frequency Cell Bandshape                                                               | 3-8  |

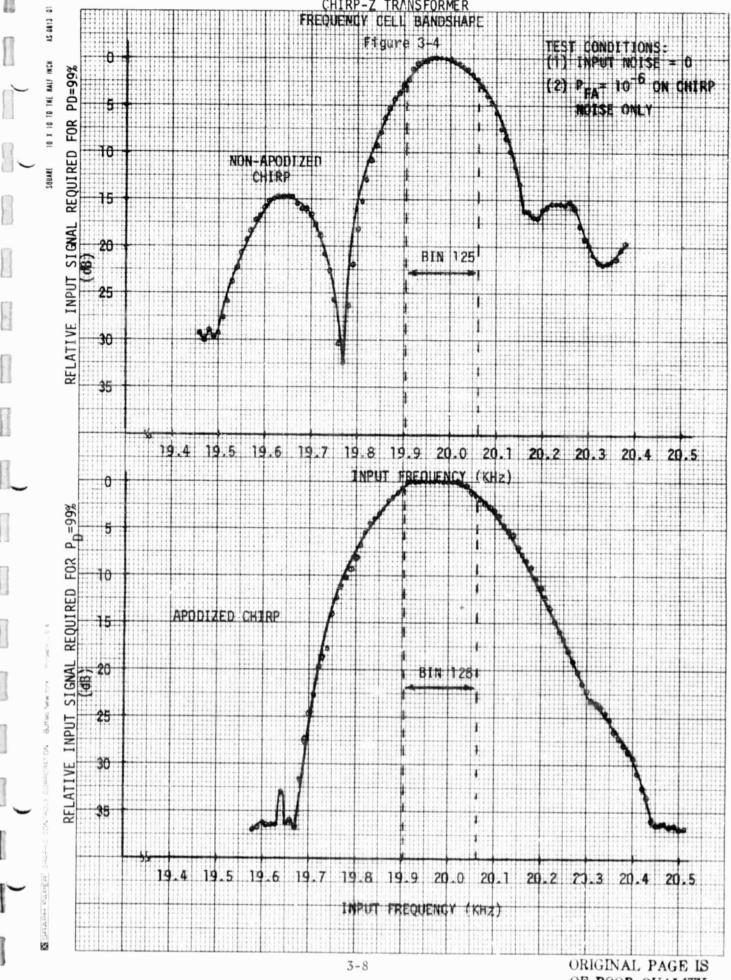

| 3-5    | Test Configuration for Chirp-Z Transformer & MSK Demodulator                                               | 3-10 |

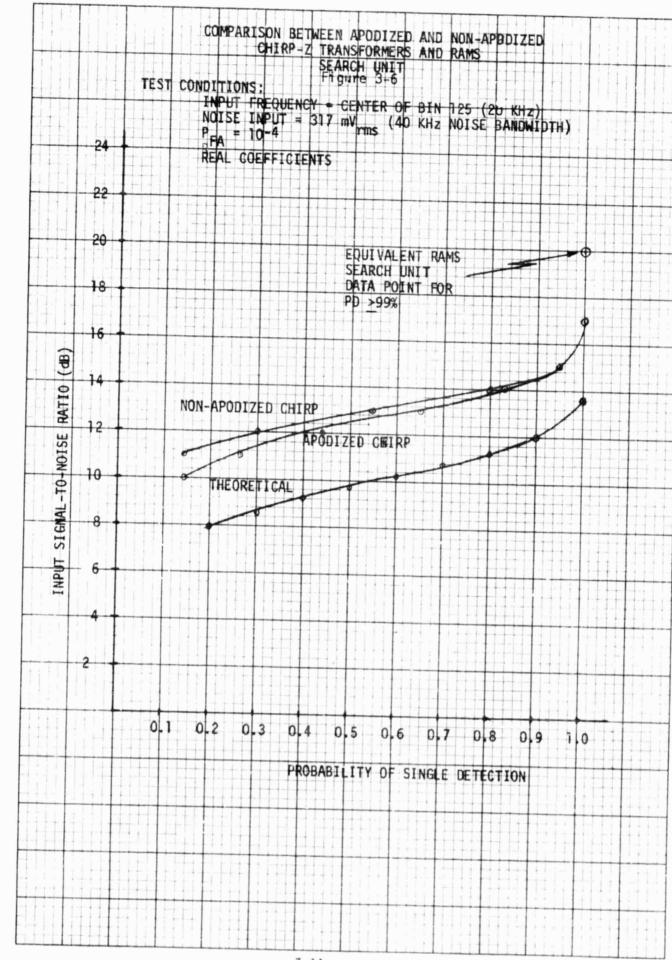

| 3-6    | Comparison Between Apodized and Non-Apodized Chirp-Z<br>Transformers and RAMS Search Unit                  | 3-11 |

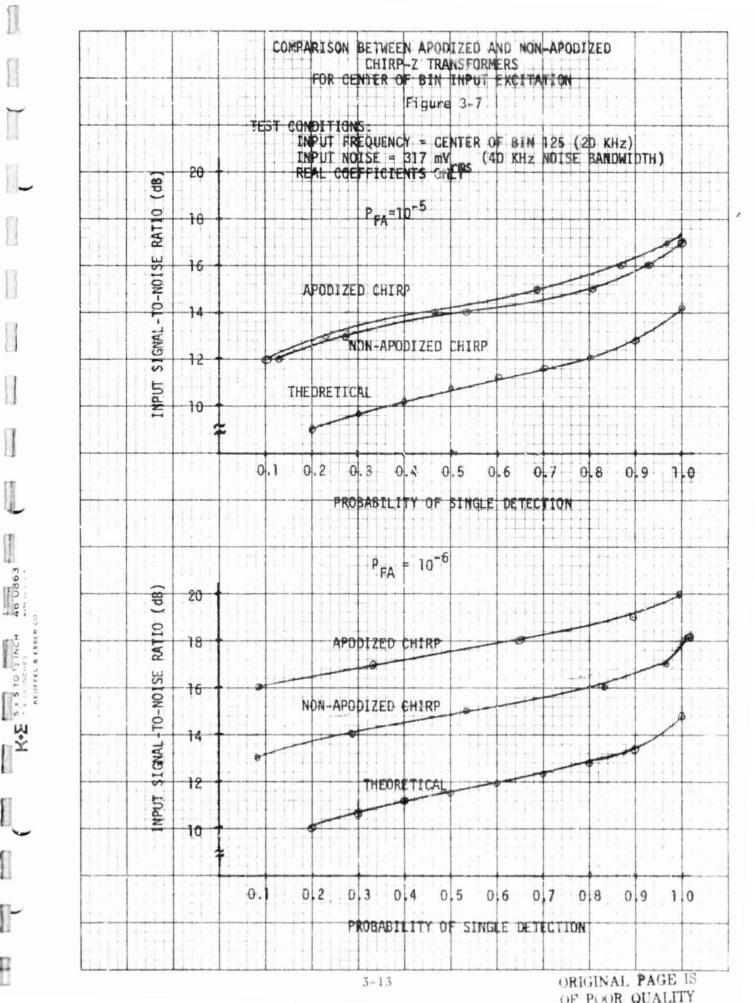

| 3-7    | Comparison Between Apodized and Non-Apodized Chirp-Z<br>Transformers for Center of Bin Input Excitation    | 3-13 |

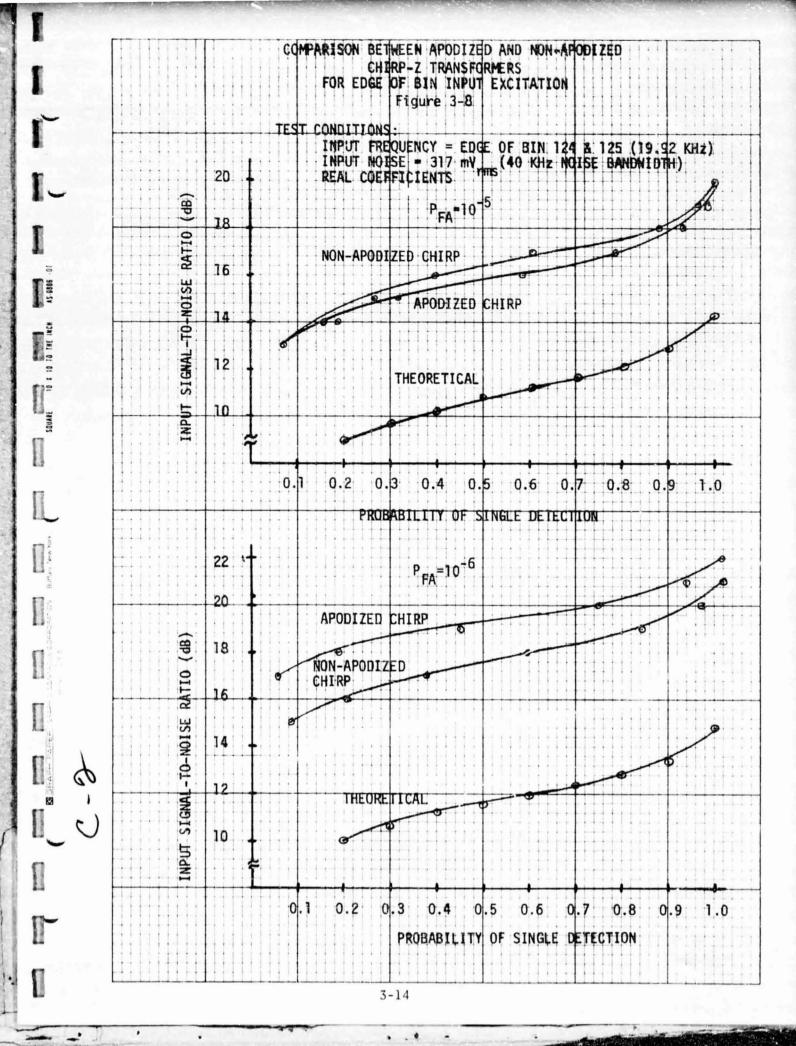

| 3-8    | Comparison Between Apodized and Non-Apodized Chirp-Z<br>Transformers for Edge of Bin Input Excitation.     | 3-14 |

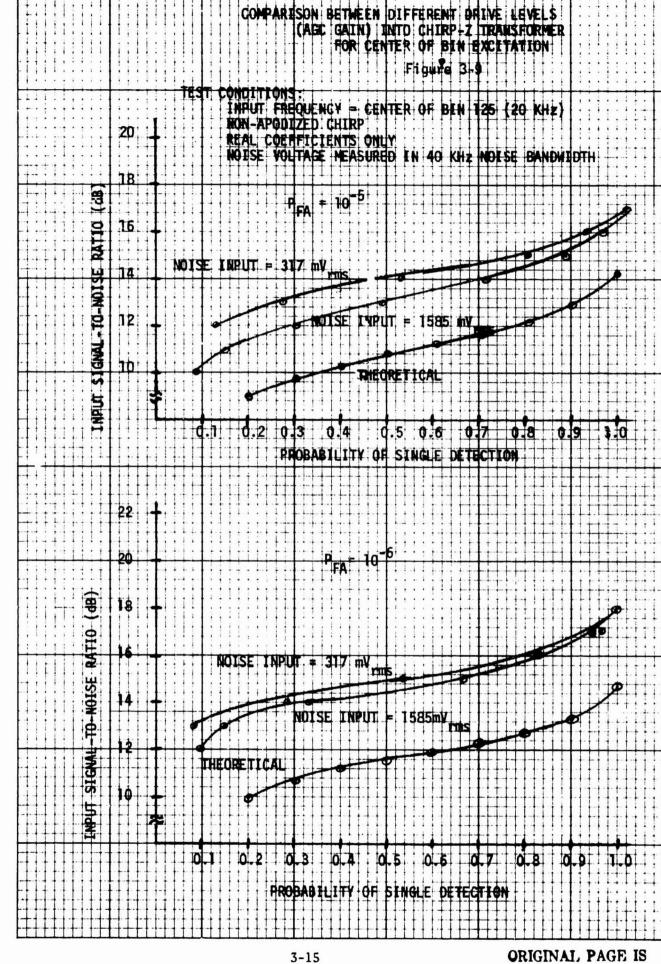

| 3-9    | Comparison Between Different Drive Levels (AGC Gaîn) Into Chirp-Z Transformer for Center of Bin Excitation | 3-15 |

# LIST OF ILLUSTRATIONS

|                                                                                                                |          |        | LIST OF ILLUSTRATIONS                                                                                                                                      |               |

|----------------------------------------------------------------------------------------------------------------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| A                                                                                                              |          |        | LIST OF TELOSTRATIONS                                                                                                                                      | _             |

|                                                                                                                | 13       | Figure | Title                                                                                                                                                      | Page          |

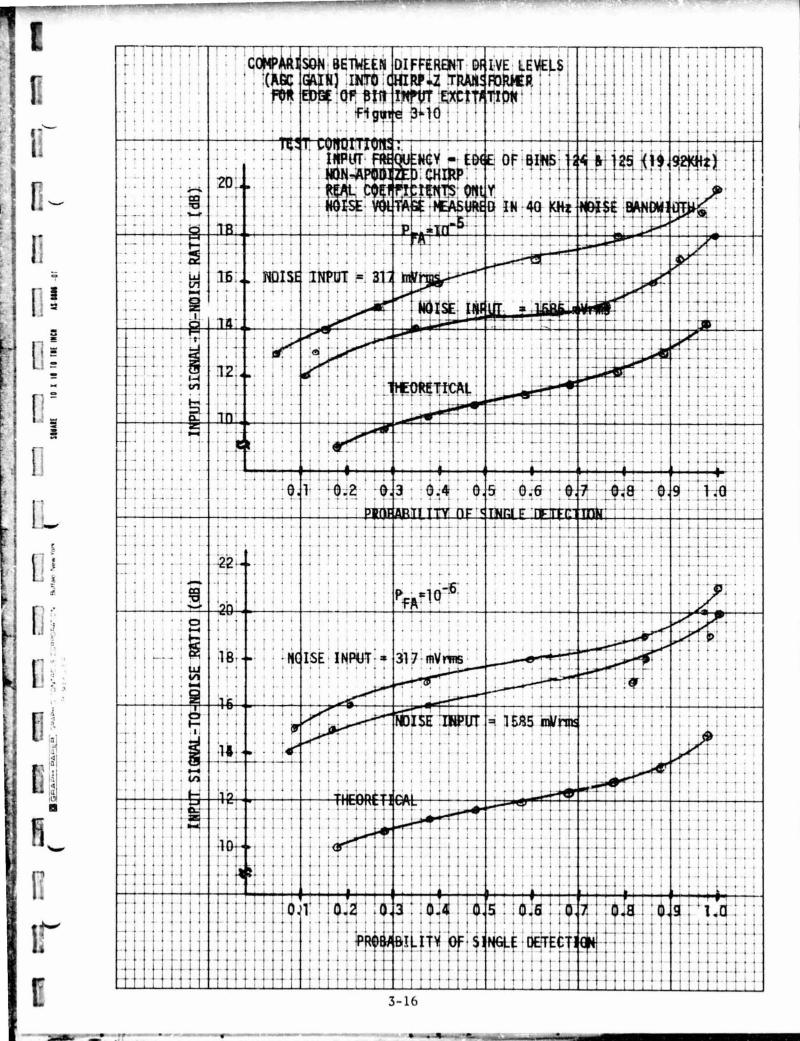

| X 4. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2. 2.                                                                    | []<br>[] | 3-10   | Comparison Between Different Drive Levels (AGC Gain) Into Chirp-Z Transformer for Edge of Bin Input Excitation                                             | 3-16          |

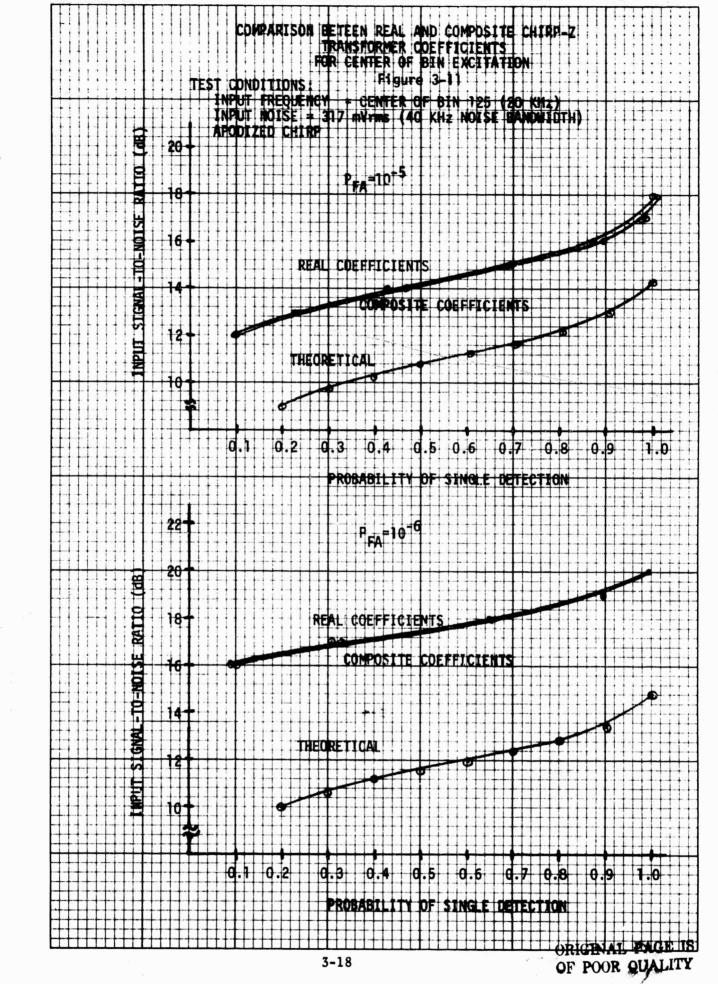

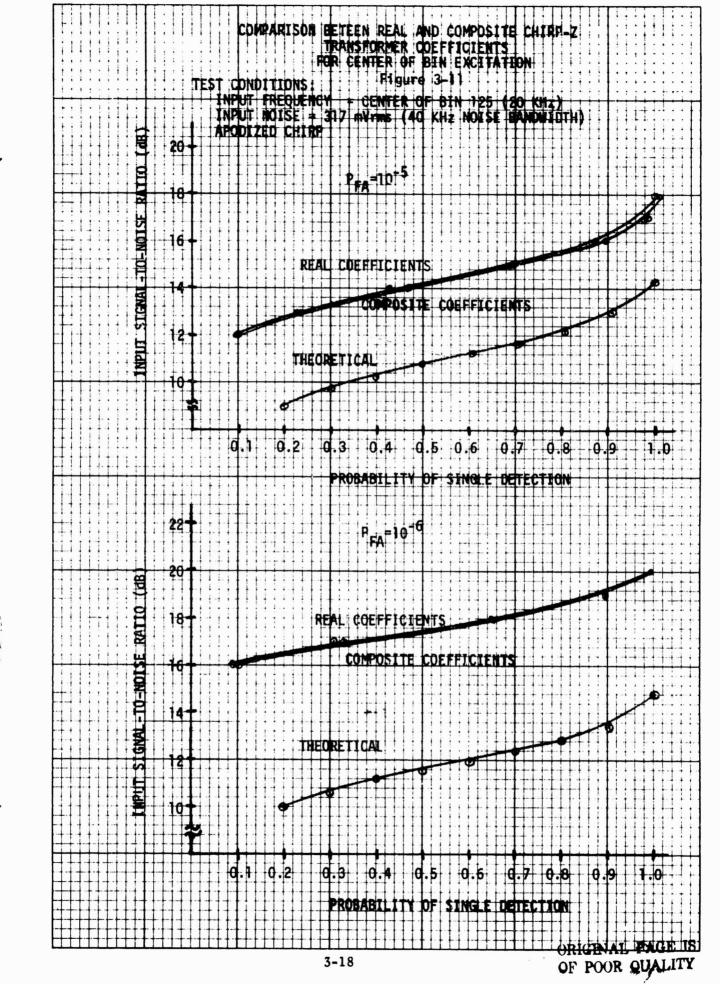

|                                                                                                                |          | 3-11   | Comparison Between Real and Composite Chirp-Z Transformer Coefficients for Center of Bin Excitation                                                        | 3-18          |

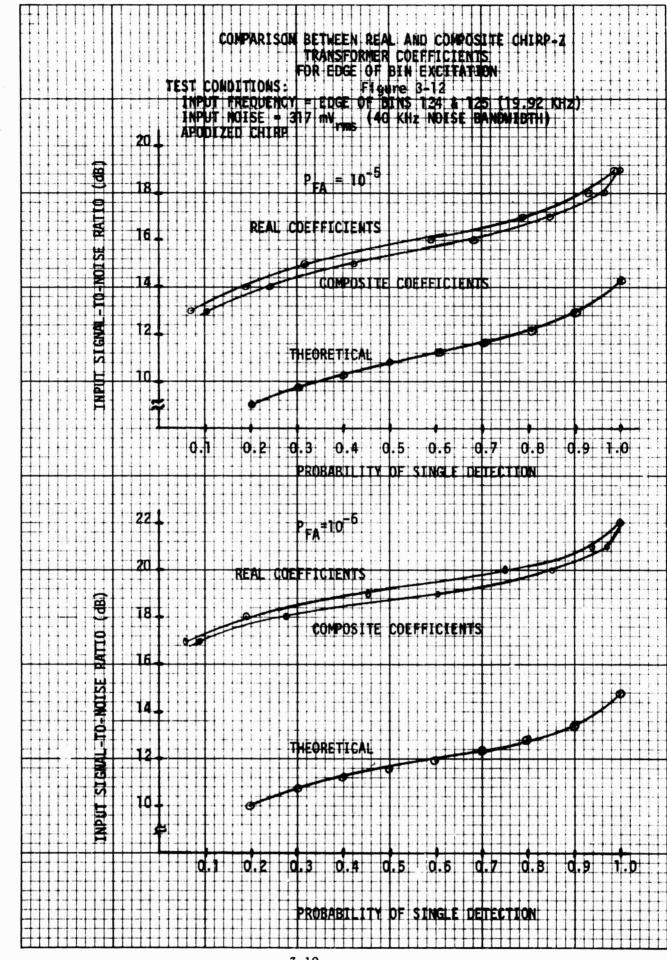

| 100 mars 1 m |          | 3-12   | Comparison Between Real and Composite Chirp-Z Transformer Coefficients for Edge of Bin Excitation                                                          | 3-19          |

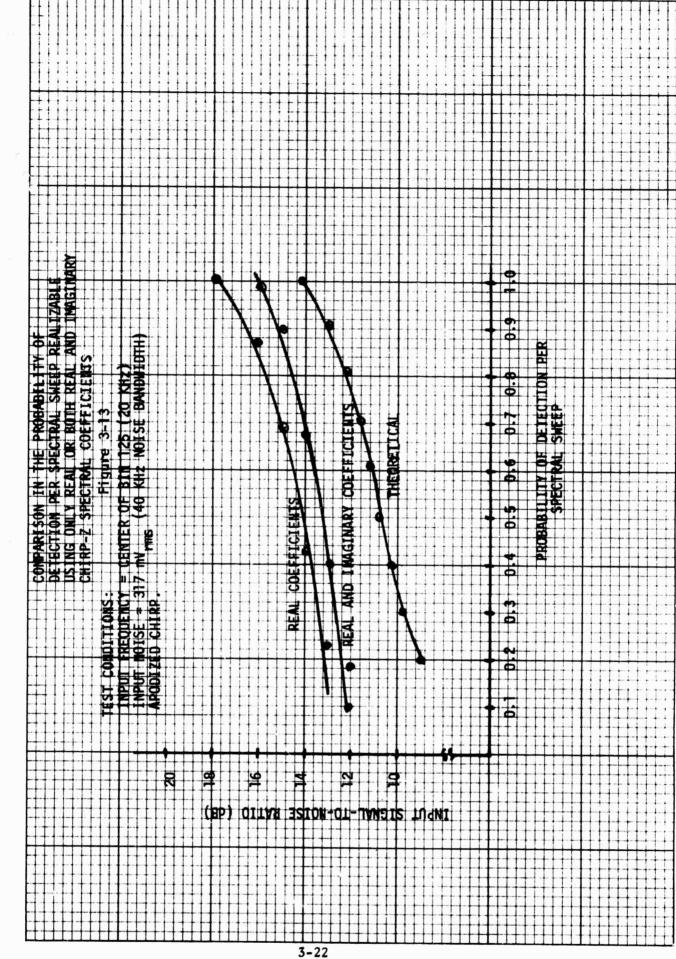

|                                                                                                                |          | 3-13   | Comparison in the Probability of Detection per<br>Spectral Sweep Realizable Using Only Real<br>or Both Real and Imaginary Chirp-Z Spectral<br>Coefficients | 3-22          |

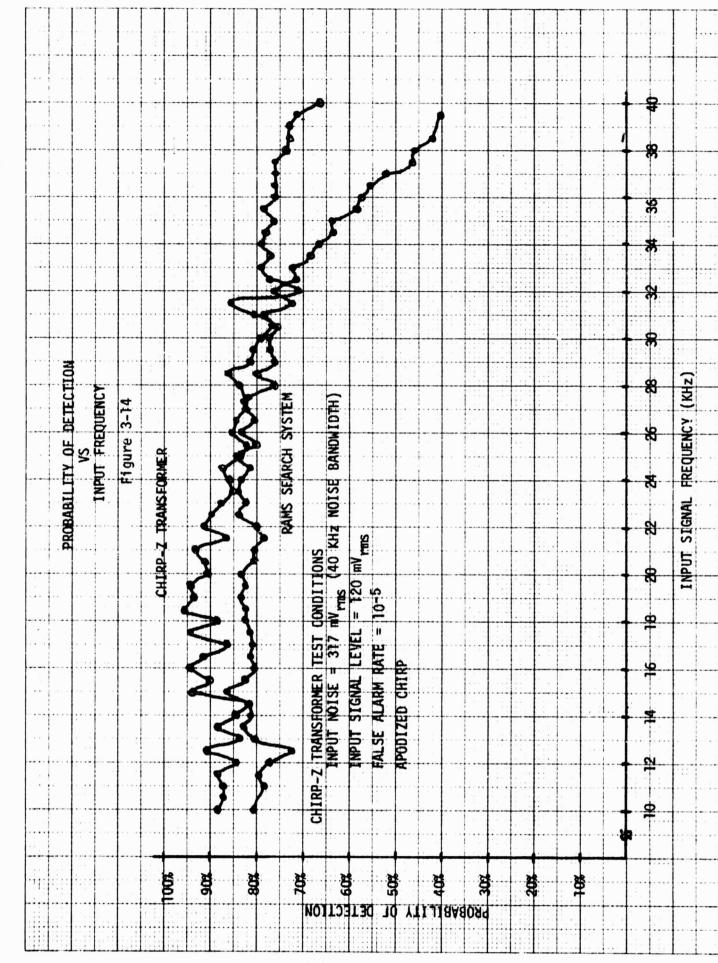

|                                                                                                                | п        | 3-14   | Probability of Detection vs. Input Frequency                                                                                                               | 3-23          |

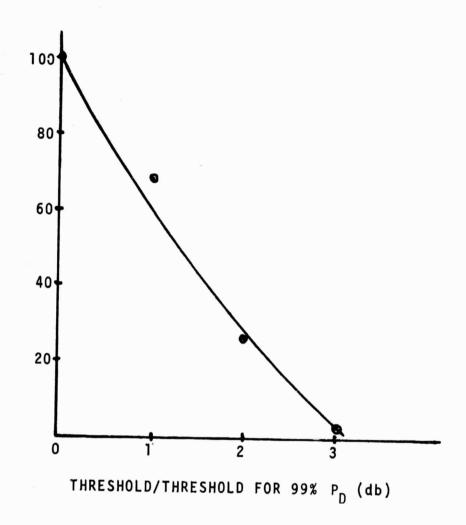

| 14                                                                                                             | IJ       | 3-15   | Soft Threshold Phenomenon (Warbling) in Chirp-Z Transformer                                                                                                | 3-24          |

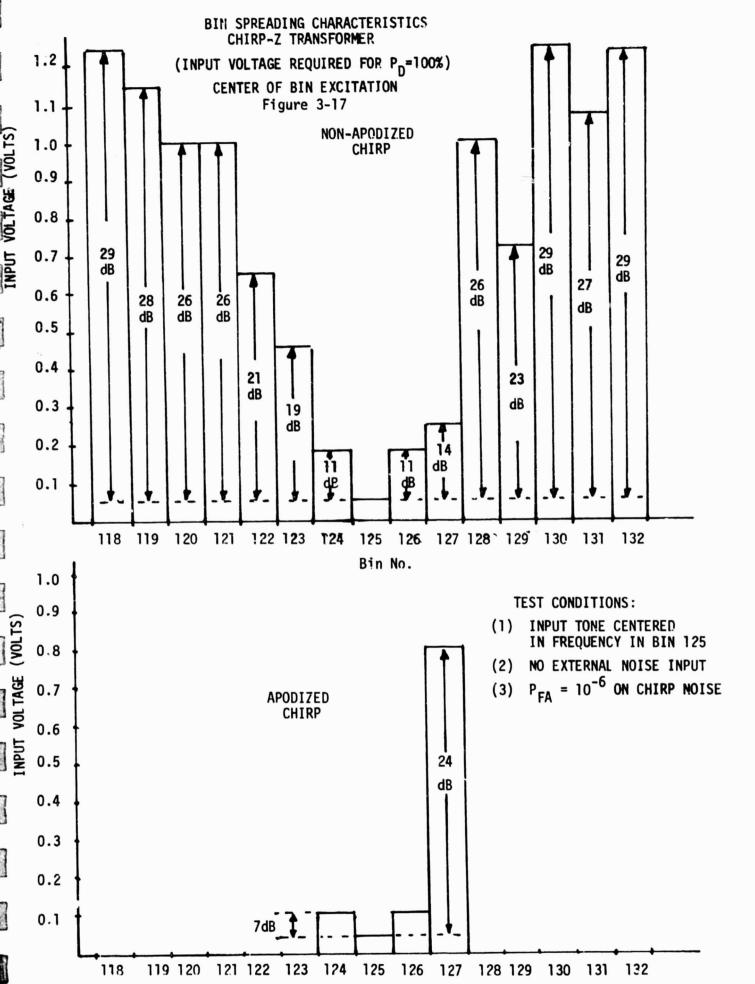

|                                                                                                                |          | 3-16   | Photographic Display of Bin Spreading vs. Signal Strength                                                                                                  | 3-27          |

|                                                                                                                |          | 3-17   | Bin Spreading Characteristics of Chirp-Z Transformer for Center of Bin Excitation                                                                          | 3-29          |

|                                                                                                                | П        | 3-18   | Bin Spreading Characteristics of Chirp-Z Transformer for Edge of Bin Excition                                                                              | 3-30          |

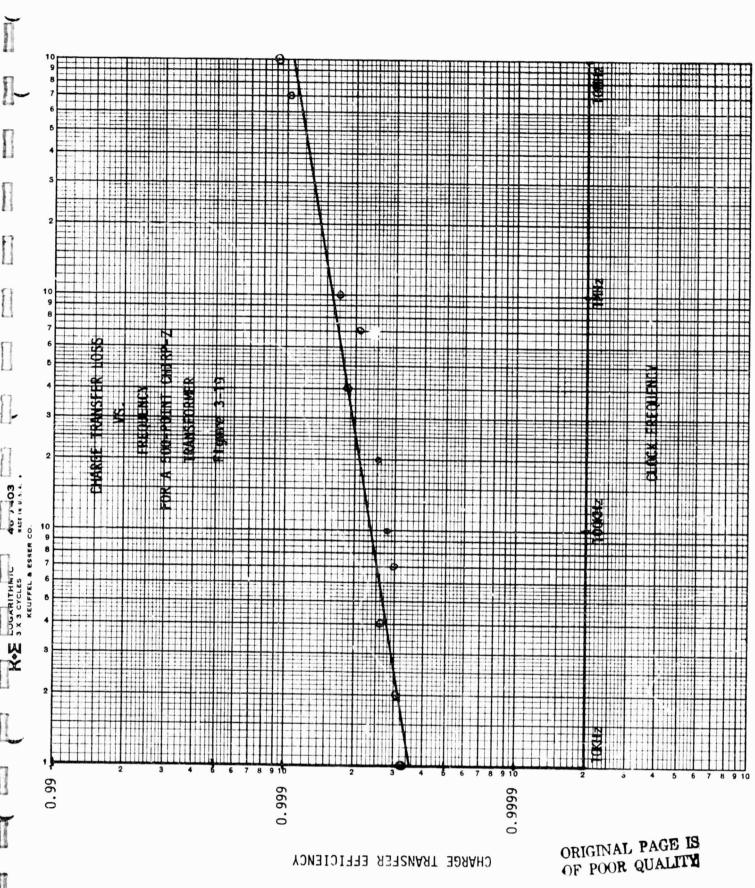

|                                                                                                                |          | 3-19   | Charge Transfer Loss vs. Frequency for a 500-Point Chirp-Z Transformer                                                                                     | 3-34          |

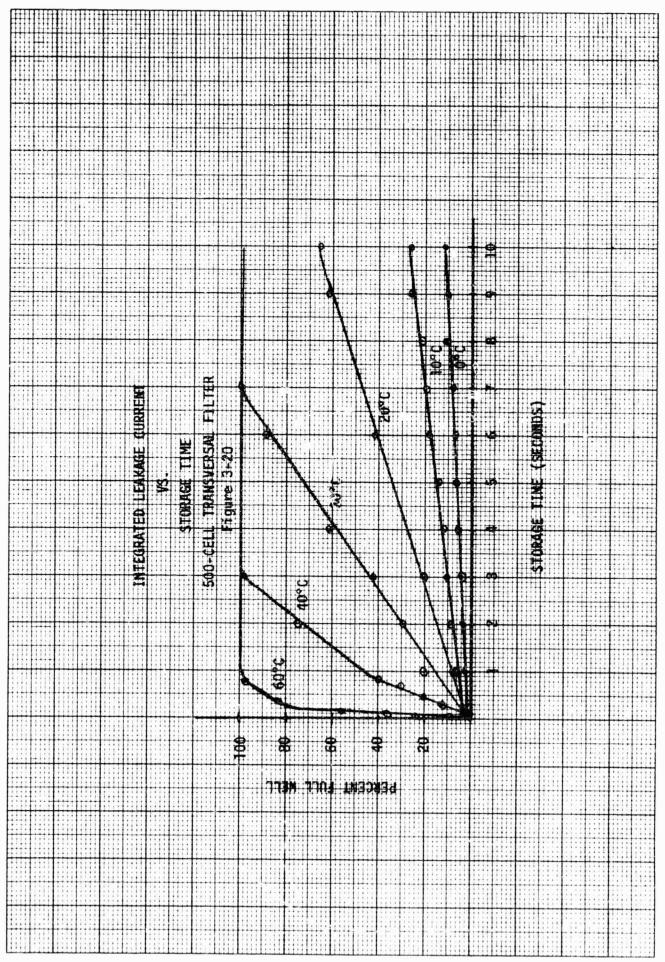

|                                                                                                                |          | 3-20   | Integrated Leakage Current vs. Storage Time for a 500-Point Transversal Filter                                                                             | 3-36          |

|                                                                                                                | N        | 3-21   | Non-Coherent MSK Demodulator Block Diagram and Key Waveforms                                                                                               | 3-40          |

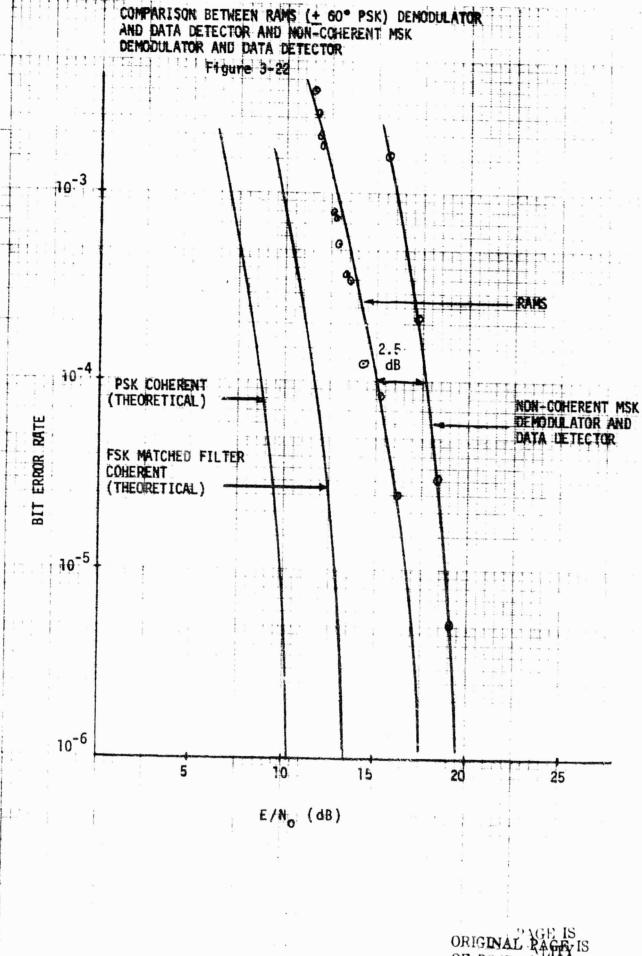

|                                                                                                                |          | 3-22   | Comparison Between RAMS (±60°PSK) Demodulator and Data Detector and Non-Coherent MSK Demodulator and Data Detector                                         | 3-42          |

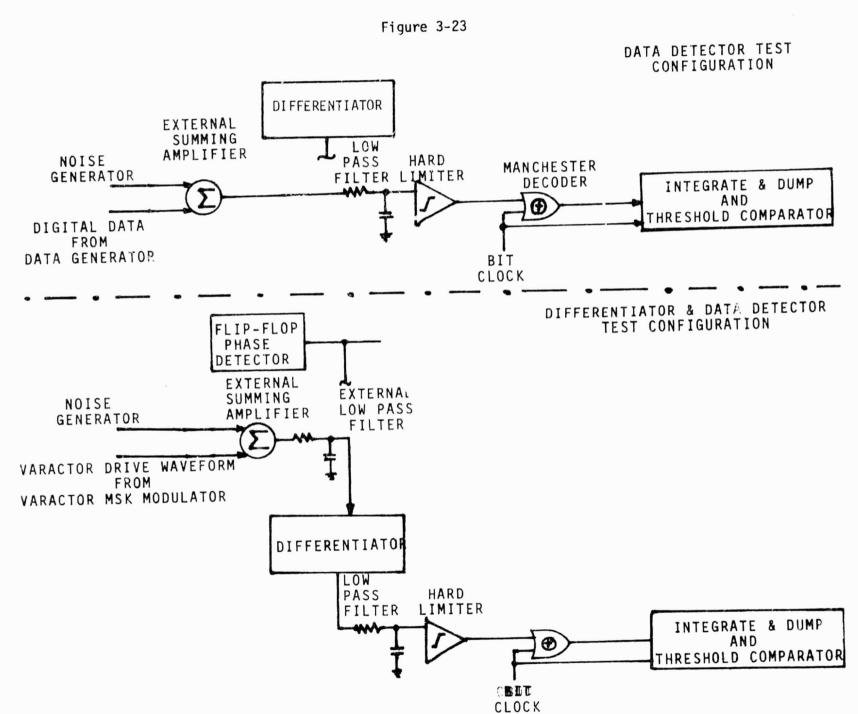

|                                                                                                                |          | 3-23   | Test Configurations for Analyzing Component Parts of Non-Coherent MSK Demodulator                                                                          | 3-43          |

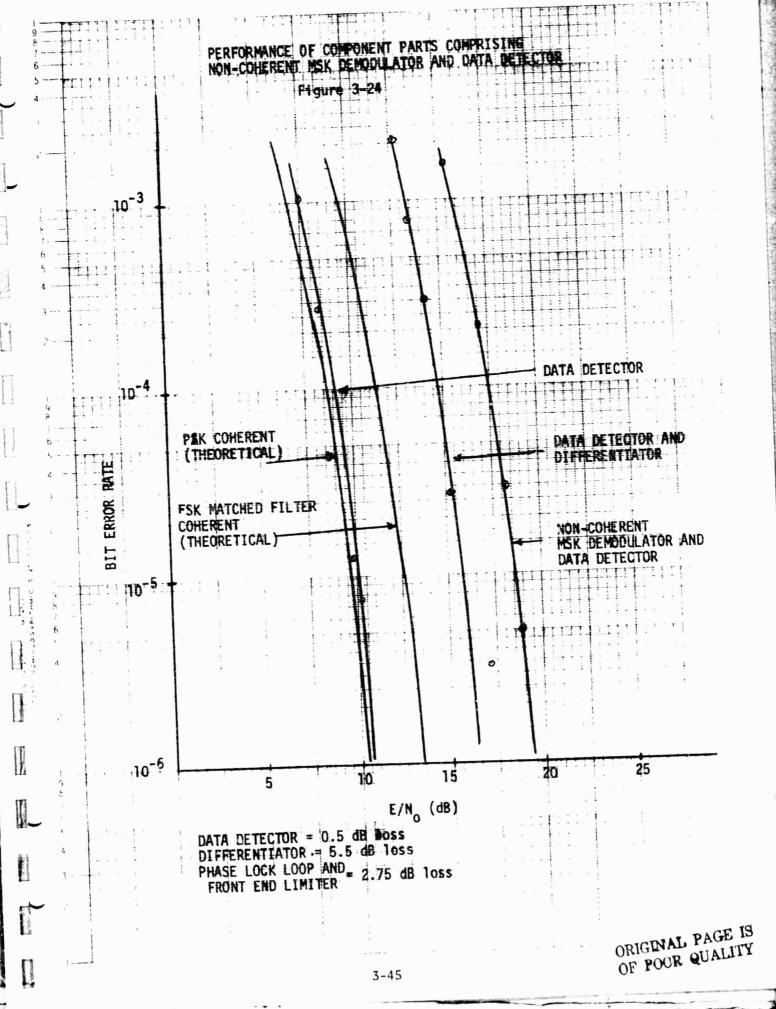

| 1                                                                                                              | Ž        | 3-24   | Performance of Component Parts Comprising Non-Cohere MSK Demodulator and Data Detector                                                                     | 3-45          |

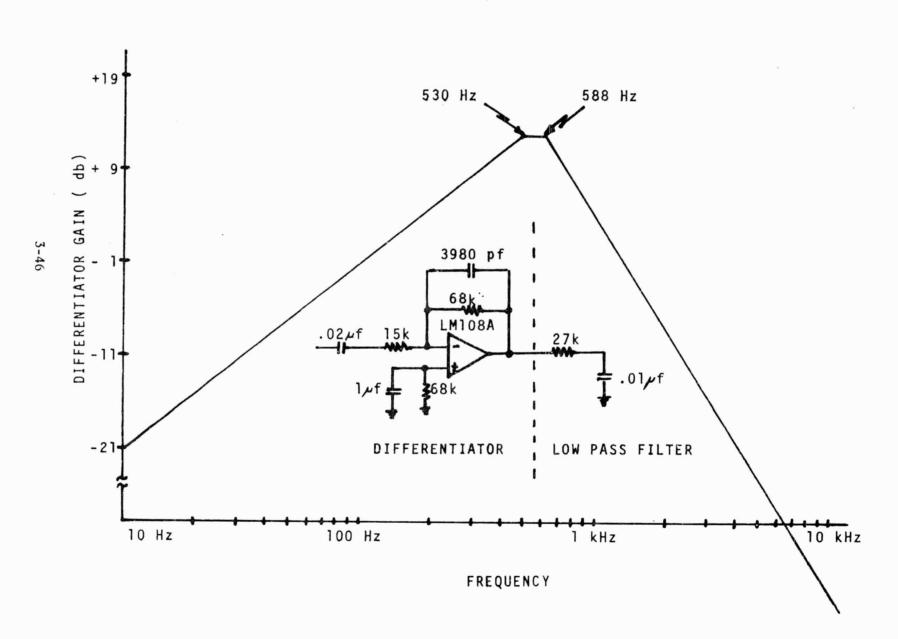

|                                                                                                                |          | 3-25   | Frequency Response of Differentiator and Low Pass Fi                                                                                                       | 1ter 3-46     |

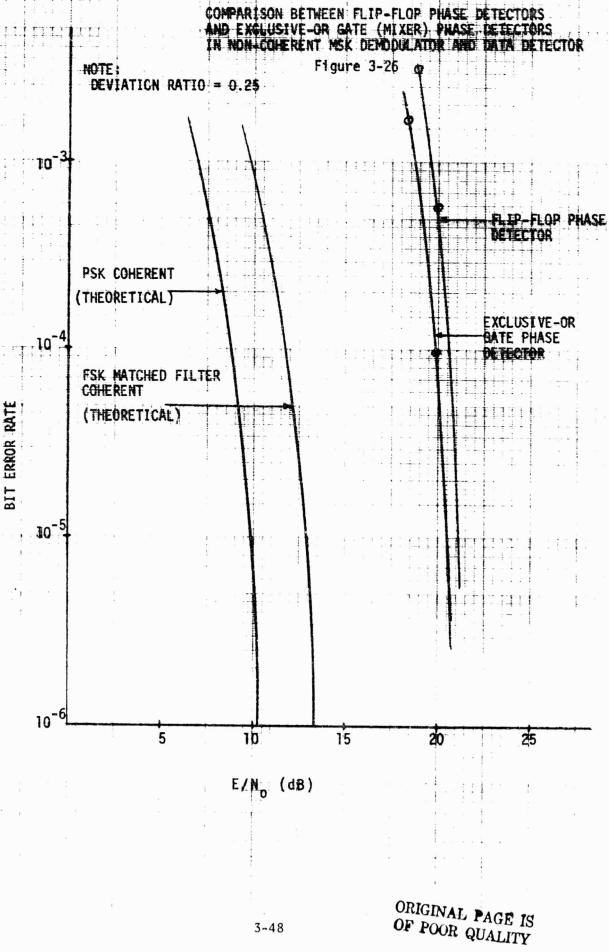

|                                                                                                                | 8        | 2-26   | Comparison Between Flip-Flop Phase Detectors and<br>Exclusive-or Gate (Mixer) Phase Detectors In<br>Non-Coherent MSK Demodulator and Data Detector         | 3-48          |

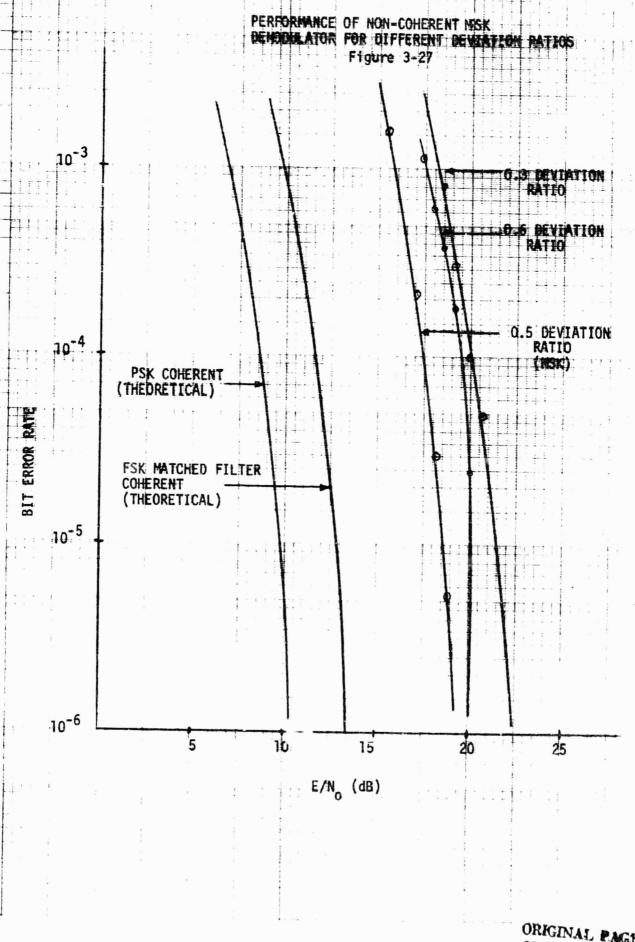

|                                                                                                                | E<br>T   | 3-27   | Performance of Non-Coherent MSK Demodulator for Diff Deviation Ratios                                                                                      | erent<br>3-51 |

| 1                                                                                                              |          |        |                                                                                                                                                            |               |

# LIST OF ILLUSTRATIONS (CON'T)

To the second

246.3

| Figure | Title                                                                                                                                             | Page          |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

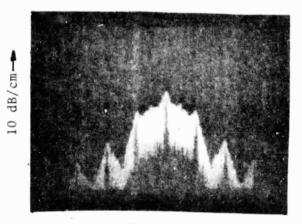

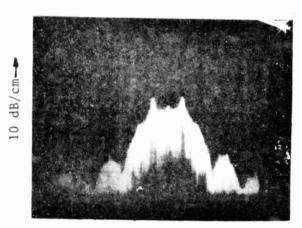

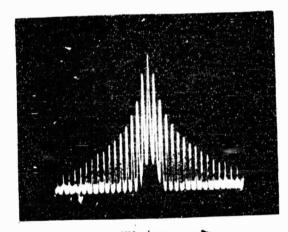

| 3-28   | Spectral Comparison Between Linear and Class C Transmission of MSK Modulation                                                                     | 3-53          |

| 3-29   | Comparison in MSK Demodulation Performance for Linear and Class C Transmission of MSK Modulated Signals                                           | 3-54          |

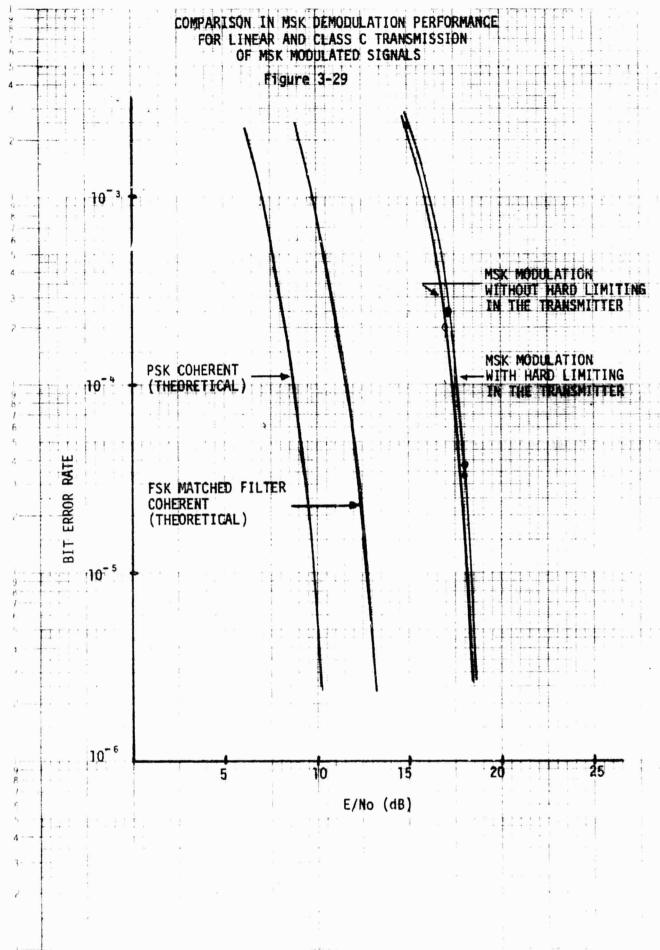

| 3-30   | Comparison of Different Types of MSK Modulators                                                                                                   | 3-55          |

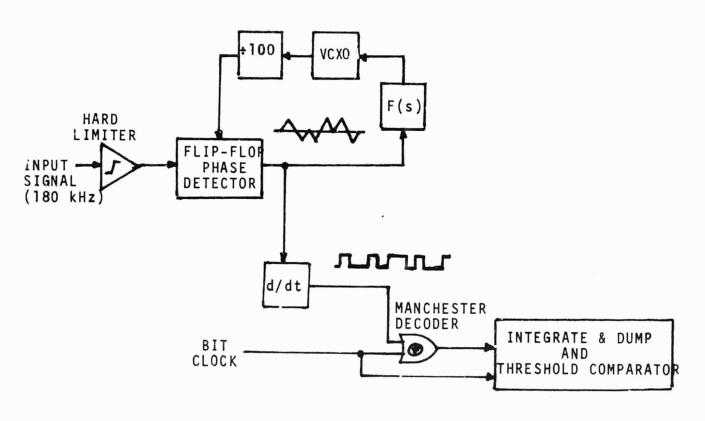

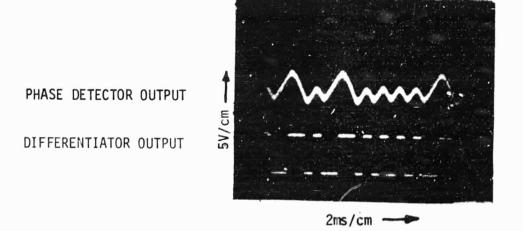

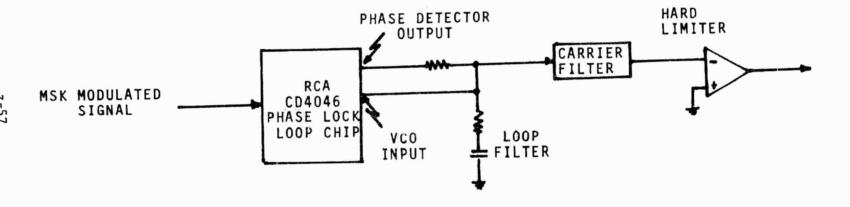

| 3-31   | Phase Lock Loop FM Discriminator Non-Coherent MSK Demodulator                                                                                     | 3-57          |

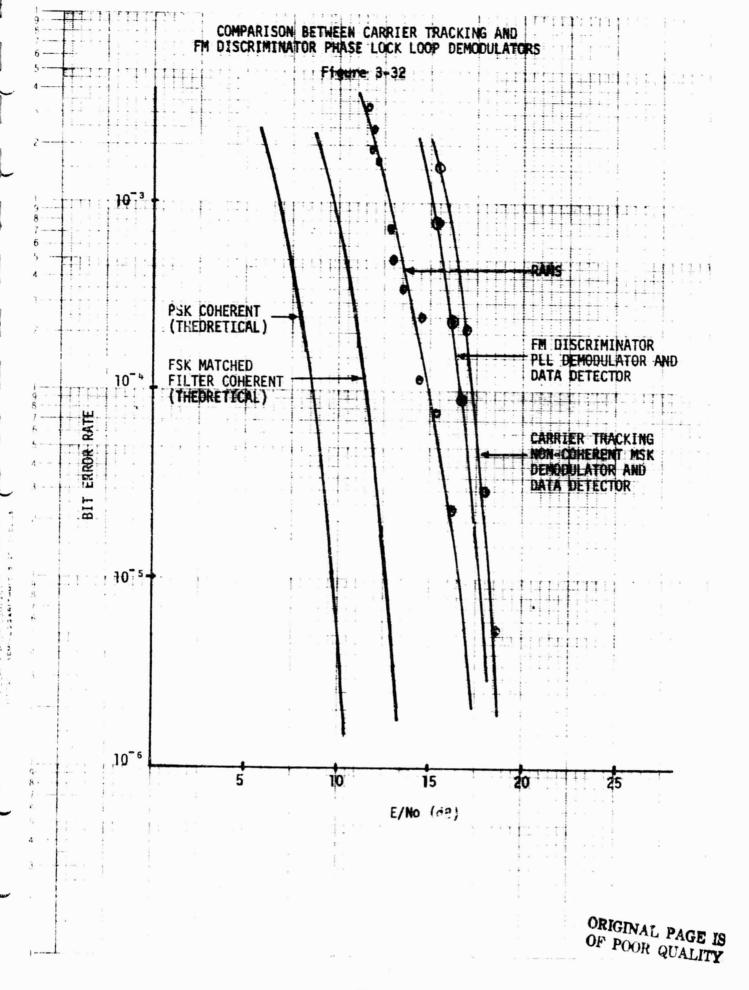

| 3-32   | Comparison Between Carrier Tracking and FM Discriminator Phase Lock Loop Demodulators                                                             | 3-59          |

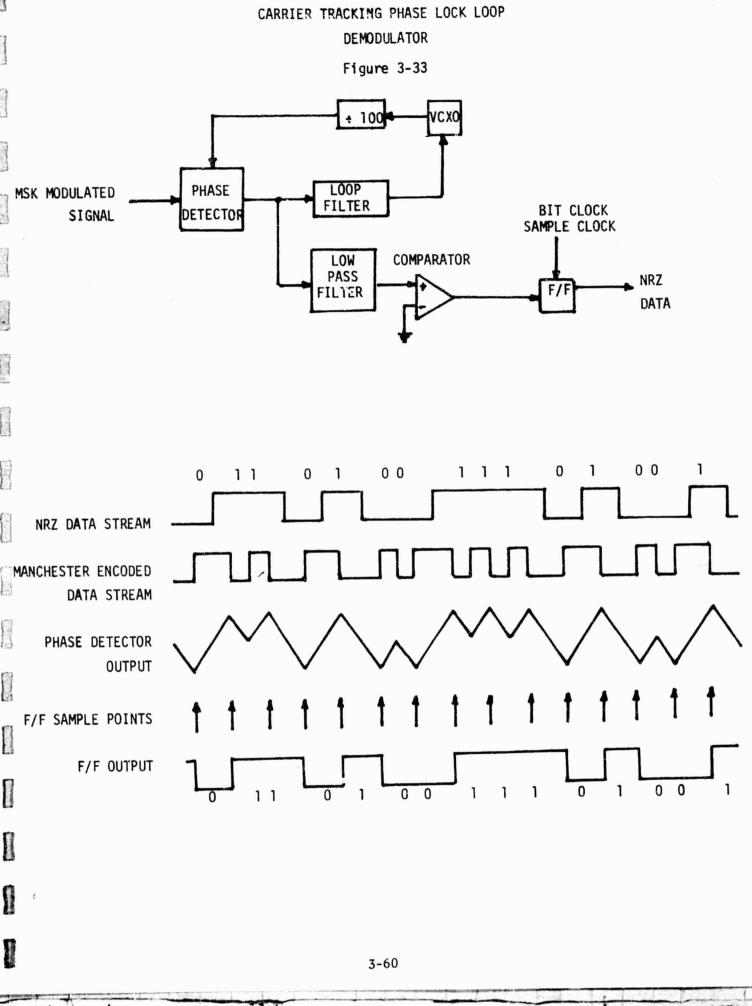

| 3-33   | Alternate Approach to Non-Coherent Carrier Tracking Phase Lock Loop Demodulator                                                                   | 3-60          |

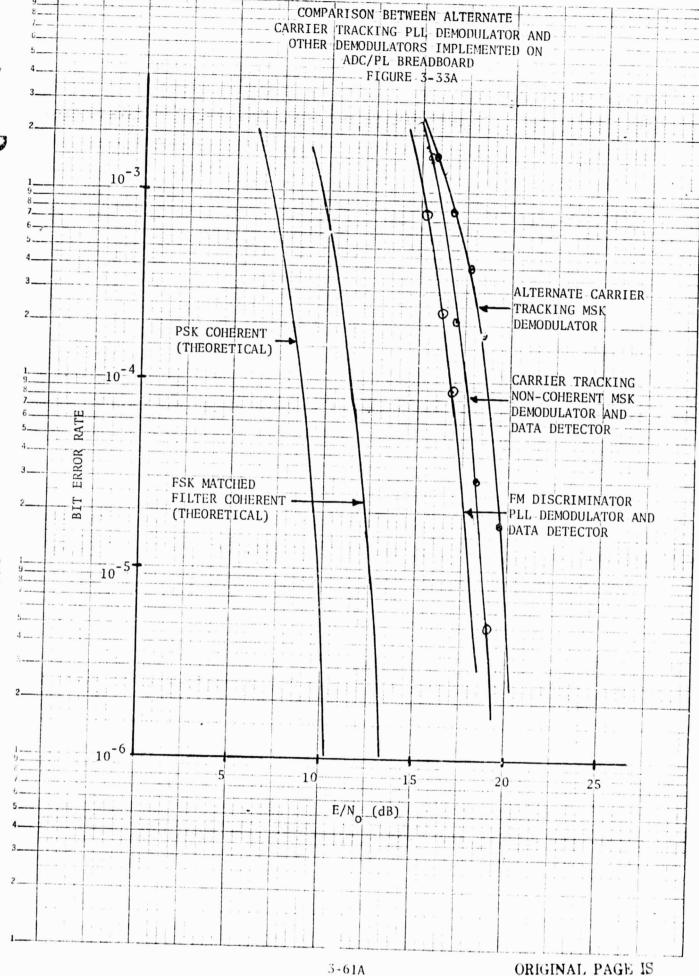

| 3-33 A | Comparison Between Alternate Carrier Tracking PLL Demodulator and Other Demodulators Implemented on ADC/PL Breadoard                              | 3-61 <i>A</i> |

| 3-34   | Block Diagram of Frequency Measurement Technique                                                                                                  | 3-62          |

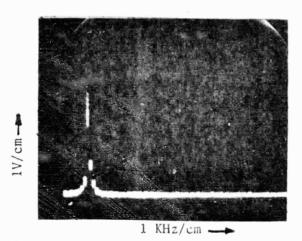

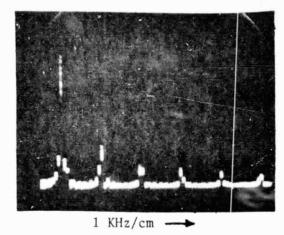

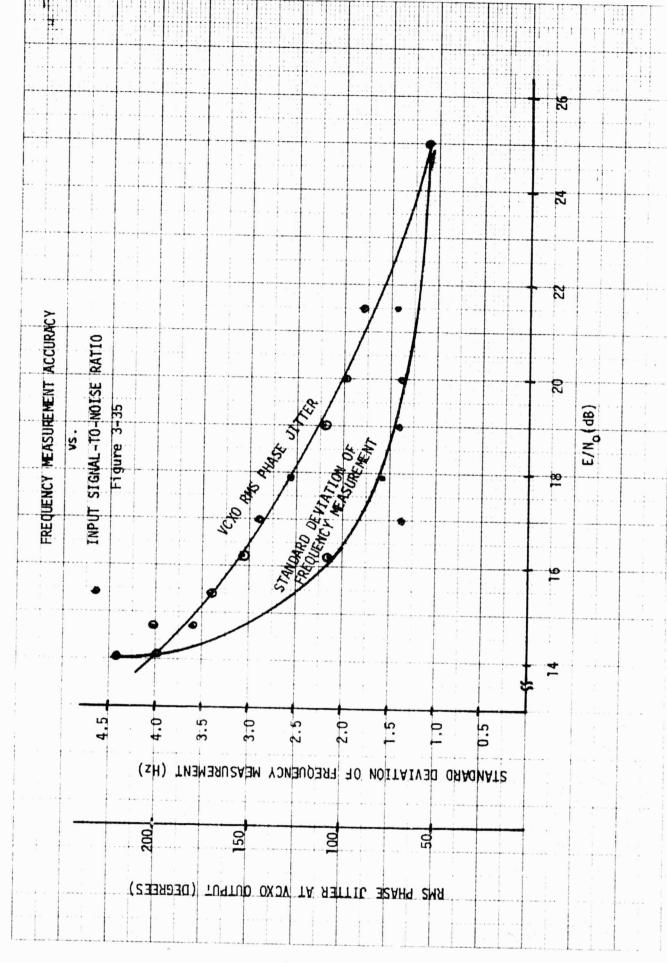

| 3-35   | Frequency Measurement Accuracy vs. Input Signal-<br>To-Noise Ratio                                                                                | 3-64          |

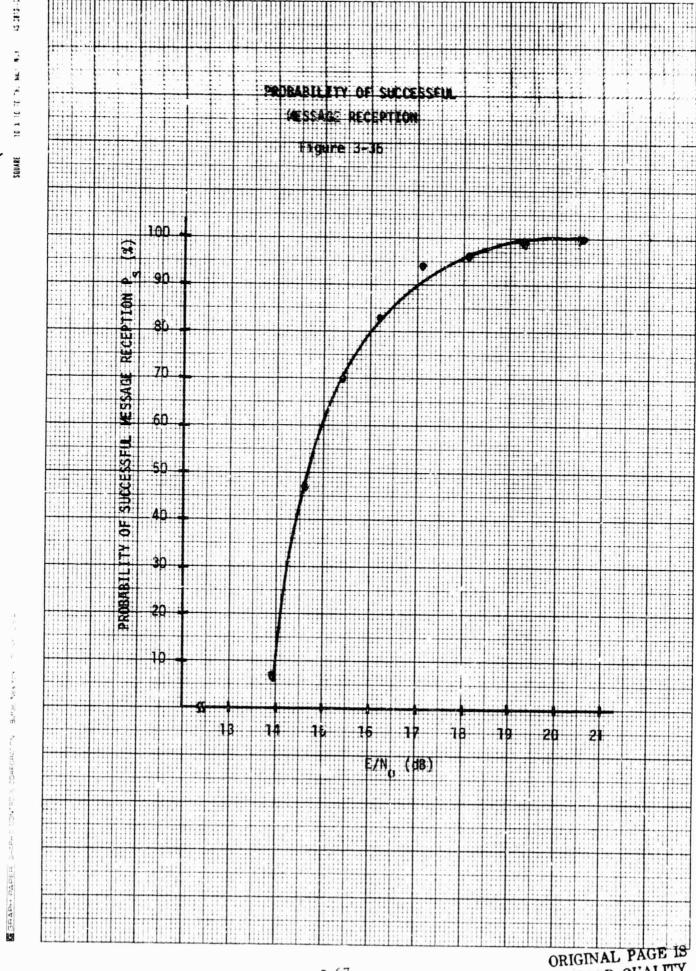

| 3-36   | Probability of Successful Message Reception                                                                                                       | 3-67          |

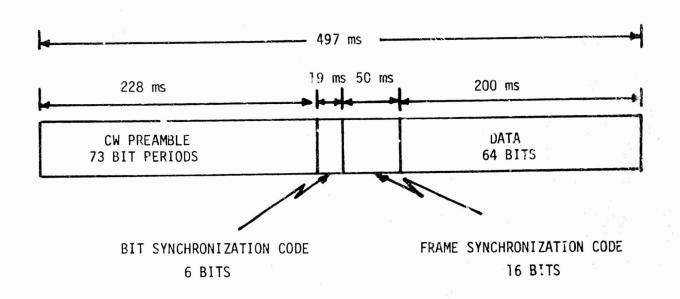

| 3-37   | Message Format for ADC/PL Breadboard Throughput Test                                                                                              | 3-68          |

| 3-38   | Comparison Between Measured and Calculated Curves of<br>the Probability of Successful Message Reception                                           | 3-70          |

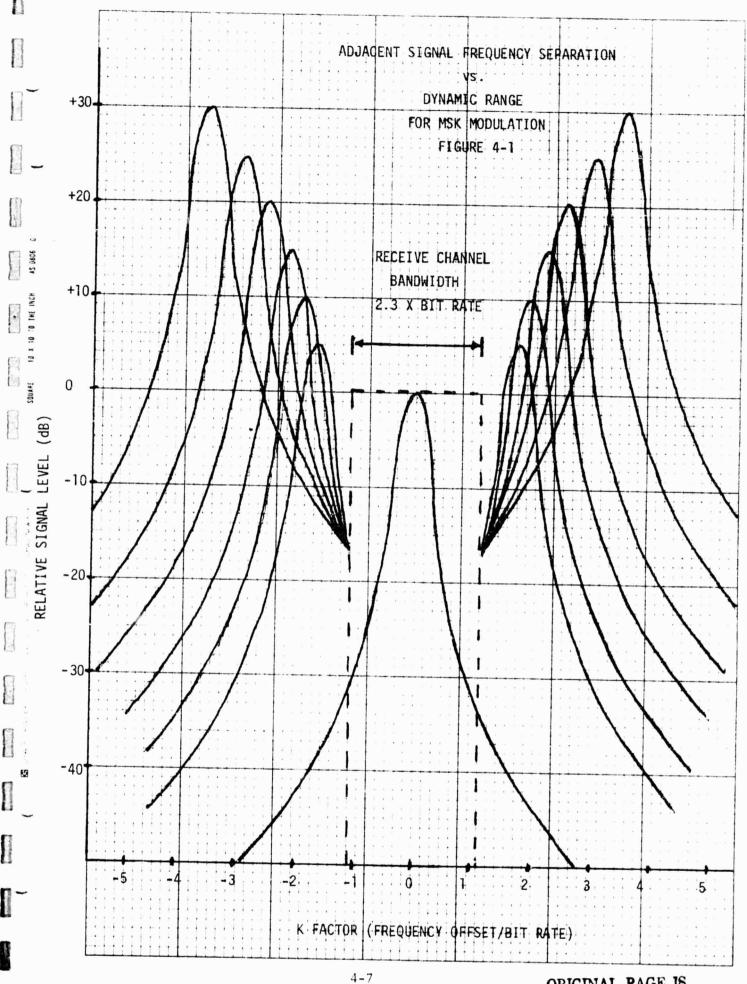

| 4-1    | Adjacent Signal Frequency Separation vs. Dynamic Range for MSK Modulation                                                                         | 4-7           |

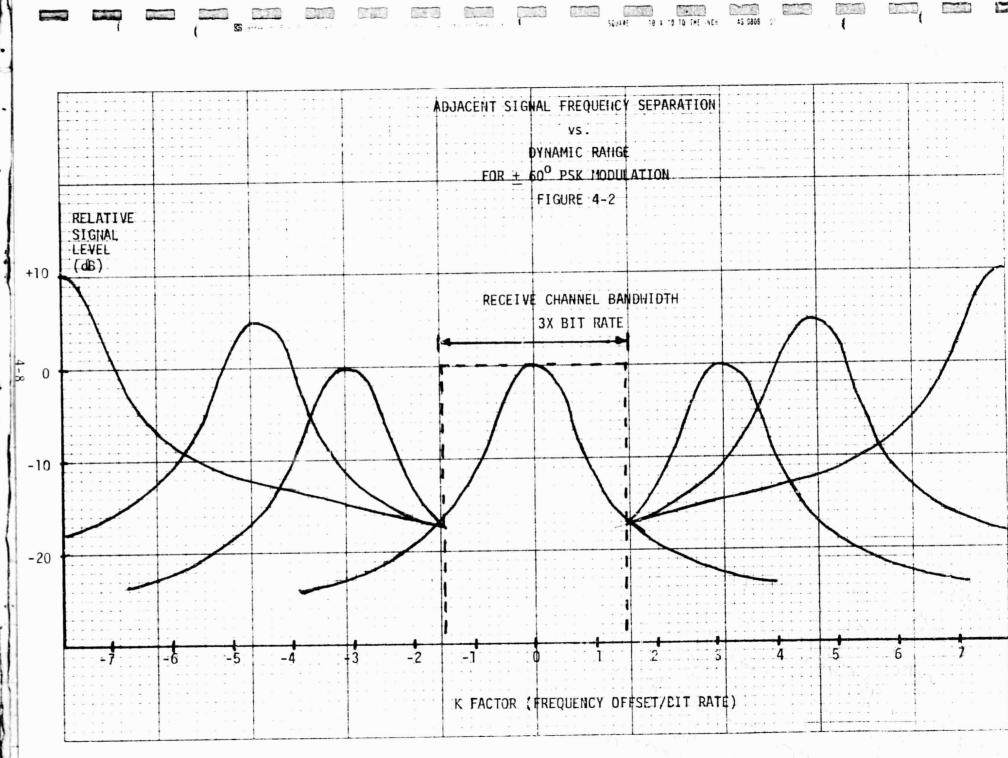

| 4-2    | Adjacent Signal Frequency Separation vs. Dynamic Range for <u>+</u> 60° PSK Modulation                                                            | 4-8           |

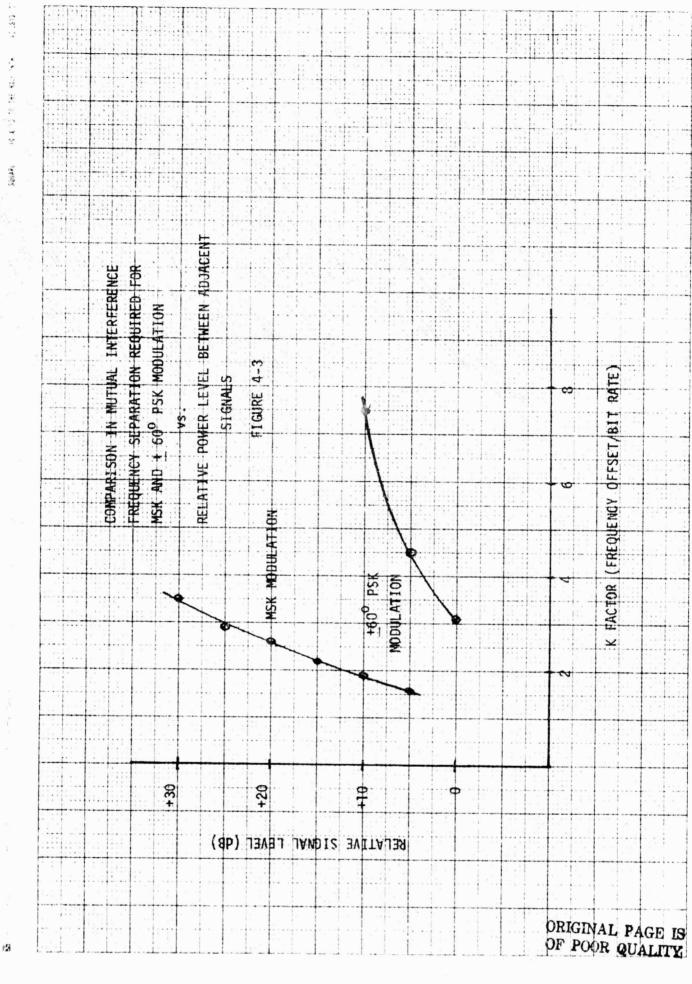

| 4-3    | Comparison In Mutual Interference Frequency Separation Required for MSK and +60° PSK Modulation vs. Relative Power Level Between Adjacent Signals | 4-9           |

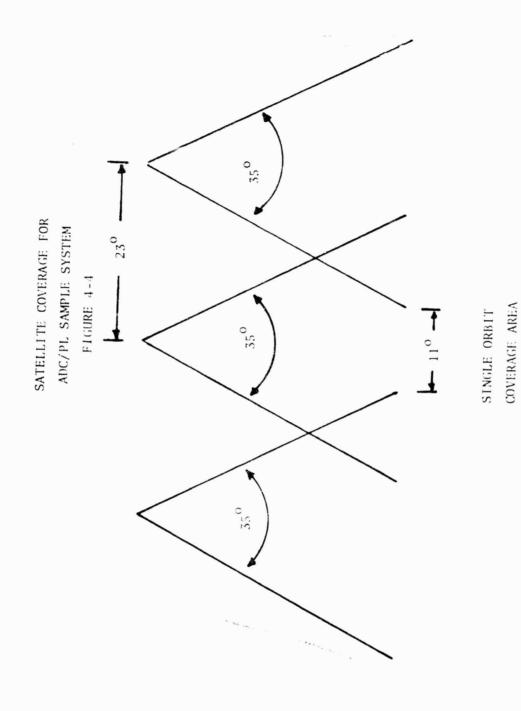

| 4-4    | Satellite Coverage for ADC/PL Sample System                                                                                                       | 4-16          |

| 4-5    | RF Up-Conversion/Transmit Hardware for Landsat                                                                                                    | . 10          |

|        | II Compatibility                                                                                                                                  | 4-20          |

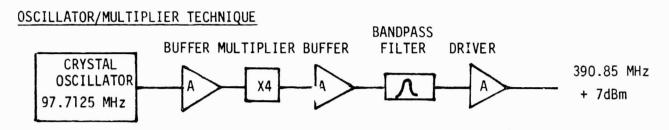

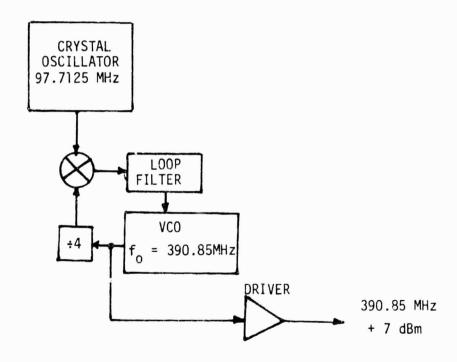

| 4-6    | Local Oscillator Generation Examples                                                                                                              | 4-22          |

|        |                                                                                                                                                   |               |

# LIST OF TABLES

3

\$

| Table | Title                                                                                    | Page |

|-------|------------------------------------------------------------------------------------------|------|

| 2-1   | Phase Lock Loop Parameters                                                               | 2-65 |

| 3-1   | Itemization of Losses in Non-Coherent  MSK Demodulator                                   | 3-49 |

| 4-1   | Summary of Tests Investigating the Use of Chirp-Z<br>Transformers In ADC/PL Applications | 4-3  |

| 4-2   | Comparison Between RAMS Search Unit and Equivalent Chirp-Z Transformer Search Unit       | 4-5  |

| 4-3   | Summary of Tests Investigating the Use of MSK Modulation in ADC/PL Applications          | 4-11 |

| 4-4   | ADC/PL Sample System                                                                     | 4-14 |

TEXAS INSTRUMENTS INCORPORATED

13500 North Central Expressway

P.O. Box 6015

Dallas, Texas 75222

July 1977

# DESIGN AND DEMONSTRATION OF AN ADVANCED DATA COLLECTION/POSITION LOCATION SYSTEM

Final Report 01-879210-F

# SECTION I INTRODUCTION AND SUMMARY

### A. INTRODUCTION

This report is the final report on a breadboard evaluation and demonstration program concerning the applicability of MSK modulation and chirp-z transformer technology in Advanced Data Collection/Position Location (ADC/PL) systems. The program effort consisted of three phases - design, testing, and evaluation. Section II describes the breadboard hardware built during the design phase of the program, Section III describes the tests conducted on the breadboard and the results of the tests, and Section IV presents a brief analysis and summary of the findings of the breadboard tests and developes a sample ADC/PL system which incorporates both MSK modulation and a chirp-z transformer.

### B. BREADBOARD DESCRIPTION

The ADC/PL breadboard consists of four major hardware units or simulators - an MSK Transmitter Simulator, a Communications Link Simulator, a Search Subsystem Simulator, and a Receive Channel Simulator. The purpose of the breadboard is to collect experimental data to characterize MSK modulation and chirp-z transformer techniques and to demonstrate the applicability of

these technologies to ADC/PL type systems. To accomplish these tasks the breadboard was designed to be quite versatile so that parameters such as data encoding techniques, message formats, frequency deviation ratio, signal-to-noise ratio. etc. could be easily manipulated by switches. No attempt was made in the breadboard effort to finalize a satellite receiver configuration or a platform transmitter design, although efforts were made in the design of the breadboard to determine suitable implementation techniques for a final hardware design. Most of the test equipment required to evaluate the MSK and chirp-z transformer technologies were built into the breadboard hardware to provide a complete and customized test bed for evaluating the two technologies.

The MSK Transmitter Simulator contains a data generator, a data checker, and a coherent MSK modulator. The data generator can output either a selectable number of burst messages or a continuous stream of pseudo random data, and the format of the data in either case can be either NRZ or Manchester encoded. The data checker provides a means of comparing the data recovered by the Receive Channel Simulator against that transmitted by the data generator. Either burst messages or the continuous data stream can be monitored by the data checker. In the case of continuous data, the data checker outputs the number of bit errors detected for bit error type measurements, and in the case of burst messages the data checker outputs the number of correct messages received for probability of success type measurements. The coherent MSK modulator were coherent implies the carrier is synchronous with the data clock - is a digital type MSK modulator based on the digital oscillator technique developed on the Random Access Measurement (RAMS) instrument. The carrier of the modulated output is at a baseband frequency of 20 kHz.

The Communications Link Simulator serves two functions - it simulates an r-f communications link and it houses two different hardware designs for implementing MSK modulation at an r-f frequency. The r-f communications link simulation is accomplished at an i-f of 10.7 MHz, which is a common i-f frequency that can be readily up-converted to an r-f frequency for transmission if so required at a later date. The input and output of the simulator are at baseband, and two separate oscillators are used for the up-conversion to 10.7 MHz and the subsequent down-converstion to baseband. This arrangement of separate translation oscillators allows the output of the simulator to be adjusted in baseband frequency from 10 to 40 kHz. Provisions are also included in the 10.7 MHz i-f of the simulator for summing wide-band, narrow-band, or CW interference in with

the signal to simulate unwanted signal and noise - like interference associated with r-f links. A hard limiter is also included in the  $10.7~\mathrm{MHz}$  i-f strip to simulate class C type processing of the MSK modulated signal.

The two MSK modulators housed in the Communications Link Simulator provide a means of evaluating the properties of MSK modulation when generated at an r-f frequency. The two types of modulators provided are a VCXO type modulator and a varactor phase shift modulator. The two modulators are non-coherent in that the 10.7 MHz carrier and the data clock a coot synchronously related. These two modulators then, along with the coherent digital MSK modulator in the MSK Transmitter Simulator, provide a means of evaluating the differences between coherent and non-coherent generation of MSK modulation.

The Search Subsystem Simulator consists of a chirp-z transformer search unit coupled with threshold detection logic and receive channel assignment logic. Circuitry is also provided to measure the probability of detection and false alarm rate parameters of the search unit. Two different types of charge-coupled devices are alternately used in the chirp-z transformer circuitry - an apodized chip specifically designed to minimize the sidelobes or spectral spreading resulting from strong signals and a standard non-apodized chip. The assignment circuitry, upon receiving a signal detected indication from the threshold detector, generates a local mixing frequency which is used to place the detected signal in the center of the i-f band of the receive channel. The output of the simulator is the incoming MSK modulated baseband signal translated to an i-f of 180 kHz, which is the center frequency of the receive channel.

The Receive Channel Simulator consists of a non-coherent MSK demodulator and data detector for demodulating and recovering the NRZ data stream and a frequency measurement circuit for performing the frequency measurements. Three different types of non-coherent demodulators were built and tested. The last two demodulators to be built and tested were built in an attempt to improve the E/N<sub>O</sub> performance measured on the first demodulator. The last two demodulators are not included in the hardware description of Section II, but are described in Section III under MSK non-coherent demodulator test results. The frequency measurement circuitry, in conjunction with the implementation of the phase lock loop in the non-coherent demodulator, is designed to provide an 0.1 Hz measurement resolution.

Although the ADC/PL breadboard was configured to interface with either a coherent or non-coherent demodulator, time did not allow construction of the coherent demodulator (which theoretically can demodulate MSK modulation and recover the NRZ data with an  $E/N_0$  performance equivalent to that obtainable with coherent PSK demodulation circuits).

### C. DESCRIPTION OF TESTS

The tests conducted on the ADC/PL breadboard are divided into four categories - chirp-z transformer tests, MSK demodulator/data detector tests, frequency measurement tests, and system throughput tests - with the majority of the testing devoted to characterizing the chirp-z transformer and the non-coherent MSK demodulator/data detector. The tests conducted on the chirp-z transformer include

- . Dynamic range tests

- . Bin spreading tests (mutual interference)

- Probability of detection tests for different false alarm rates

- Coefficient utilization tests (using only real vs. real and imaginary spectral coefficients in the signal detection process)

All of the tests listed above were conducted using both apodized and non-apodized charge-coupled device transversal filters in the chirp-z transformer. Although tests were not specifically conducted, discussions are also included in Section III concerning the temperature characteristics of charge-coupled devices and the search times and channel reassignment times achievable with a chirp-z transformer implemented search unit.

The tests conducted on the Receive Channel Simulator include

- Bit error rate vs. E/N tests for both types of non-coherent

MSK demodulators

- . Frequency measurement accuracy vs. signal-to-noise ratio tests

- Tests comparing linear and class-C transmission of MSK signals in terms of spectral spreading of the MSK signal and the E/N performance of the non-coherent demodulator/data detector.

- Tests comparing coherent and non-coherent generation of MSK modulation in terms of E/N<sub>o</sub> performance of the non-coherent demodulator/data detector.

- . Bit error rate vs.  $E/N_{_{\hbox{\scriptsize O}}}$  for different frequency deviation ratios. The primary non-coherent demodulator/data detector used in the Receive Channel

Simulator tests was a carrier tracking phase lock loop demodulator with the phase lock loop phase detector followed by a differentiator providing the demodulation of the MSK signal. Tests were conducted on the different components of this demodulator/data detector to itemize the contributions the different components made to the total loss in  $E/N_0$  performance as compared to that theoretically obtainable.

The final set of tests conducted on the ADC/PL breadboard are throughput tests utilizing all the equipment in the breadboard as an integrated system. The throughput test is conducted by having the MSK Transmitter Simulator generate an MSK signal which is routed through the Communications Link Simulator, detected and assigned to the receive channel in the Search Subsystem Simulator, demodulated and detected in the Receive Channel Simulator, and verified for proper reception in the error checker housed in the MSK Transmitter Simulator. The purpose of the test is to demonstrate the applicability of MSK modulation and chirp-z transformers to ADC/PL systems and to verify that the overall throughput test results agree with the test findings of the individual chirp-z transformer and MSK demodulator/data detector tests. To demonstrate compatibility between the MSK and chirp-z transformer technologies, the measured results of the throughput tests are compared against calculated results based on data taken from the individual chirp-z transformer and MSK demodulator/data detector tests.

### D. CONCLUSION

Data collection/position location systems implemented using low polar orbiting satellites are characterized as time-limited, band-limited systems. As a result, the key to improving the serviceability of such a system, or the number of users that can be accommodated by such a system, is to improve the efficiency in which the system uses the time and bandwidth available. The choice of MSK modulation and chirp-z transformers is directly aimed at improving these two key parameters. MSK modulation is shown to possess an extremely efficient utilization of bandwidth in that 99% of the spectral energy is contained within a double-sided bandwidth of 2.3 times the data rate. A chirp-z transformer implemented search unit is found to search the designated system bandwidth for the presence of signals in a time span equal to the analyzing bandwidth of the search unit - thus providing a very efficient utilization of time.

The chirp-z transformer implemented search unit was found to be superior to the RAMS search unit in every aspect. The probability of detection curves were superior to those obtained on RAMS, a dynamic range of 30 dB was found to be acceptable, bin spreading in the presence of signals separated in power by up to 30 dB was less than that experienced on RAMS for a 10 dB range of signals, and, most importantly, the search time for the same system bandwidth was reduced over an order of magnitude over the search time required in the RAMS instrument. The MSK modulation format did exhibit excellent spectral characteristics. The mutual interference band for signals as great as 30 dB apart in signal power was calculated to be approximately 3.5 times the data rate of the modulated signal, as compared to eight times the data rate for  $\pm 60^{\circ}$  PSK signals - as measured on the RAMS instrument. The non-coherent MSK demodulator/data detector did not perform as well in terms of  $\mathrm{E/N}_{\mathrm{O}}$  performance, being 2.5 dB worse in performance than the PSK demodulator used in the RAMS instrument. The coherent MSK demodulator should show a significant improvement in  $\mathrm{E/N}_{_{\mathrm{O}}}$  performance over that obtained with the non-coherent demodulator, since MSK modulation can theoretically be treated as a PSK modulation format with equivalent  $\text{E/N}_{_{\rm O}}$  performance if coherently demodulated. Unfortunately, time did not allow the implementation of the coherent demodulator.

Had MSK modulation and a chirp-z transformer been used on the RAMS instrument - with all parameters constant except the length of the CW preamble and the transmitted power - the number of serviceable platforms in the field of view could have been increased from the goal of 200 to over 800. For an ADC/PL system with a 100 kHz bandwidth and ten watt transmitters in the user platforms, a user community of approximately 2500 could be accommodated in the satellite field of view.

In conclusion, the findings of this breadboard program definitely show that MSK modulation and chirp-z transformers are vital technologies for maximizing the serviceability of future data collection/position location system.

### SECTION II

### HARDWARE DESCRIPTION

### A. INTRODUCTION

This section describes the special-purpose hardware specifically designed to demonstrate an Advanced Data Collection/Position Location (ADC/PL) system. Figure 2-1 shows the breadboard configuration for the ADC/PL system and, as shown, the system consists of four major hardware units or simulators - an MSK Transmitter Simulator, a Communications Link Simulator, a Search Subsystem Simulator, and two different implementations of a Receive Channel Simulator. The implementation of each of these four major units is presented to a detailed block diagram level following a brief discussion of the features incorporated into each of the four simulators and the frequency plan adopted for the breadboard system.

### B. BREADBOARD SYSTEM FEATURES

2

The utilization of the breadboard system is twofold. The first objective is to collect experimental data to characterize MSK modulation and chirp-z transform techniques and verify the applicability of these technologies to data collection and position location requirements. The second objective is to demonstrate the usage of the two technologies in data collection type systems by conducting simulated throughput tests. It is evident from these objectives that the hardware must be flexible in design to accommodate the various tests and parameter characterization studies required.

Before listing the features and programmable options incorporated into each simulator, the function of each simulator will be briefly described. The MSK Transmitter Simulator provides an MSK modulated data stream and also contains error detection facilities for verifying the

物准例

FILLAUD ALONGUAO

2-2

MS K/CHIRP-Z TRANSFORMER BREADBOARD CONFIGURATION

Figure 2-1

proper recovery of the modulated signal in the Receive Channel Simulator. The Communications Link Simulator serves not only to simulate a communications link by allowing interferring tones and front end receiver type noise to contaminate the received signal, but also contains MSK modulation circuitry to determine the feasibility of implementing the MSK modulation format at the final RF stage. The Search Subsystem Simulator contains a chirp-z transformer - implemented with charge coupled devices and associated logic - to implement a search and detect technique for locating incoming MSK modulated transmissions and assigning a receiver/demodulator channel to the detected signal. The two Receive Channel Simulators provide a means of characterizing both coherent and non-coherent demodulation techniques and weighing the E/No performance of each technique against hardware complexity and platform transmission time.

The following lists, which show the capabilities and options available within each major hardware unit, indicate substantial versatility and programmability is provided to accommodate the required characterization and throughput tests.

1. MSK Transmitter Simulator Features

N. Yang

- a. Modulation Format the modulation format is selectable between either MSK modulation or FSK modulation. In the case of FSK modulation, the deviation ratio can be varied from 0.1 to 10.0 in steps of 0.1.

- b. Encoding Format The format of the digital data stream prior to modulation can be selected to be either non-return-to-zero (NRZ) or Manchester (split-phase).

c. Message Format - A message can consist of either a 32,767 bit P/N code or a burst of selectable data of programmable length. For the case of burst data type messages, the following programmability features are provided:

- (1) CW Preamble The CW preamble is programmable in length from 0 to 99 bits in one bit increments.

- (2) Bit Synchronization Code The bit synchronization code can be varied in length from 0 to 99 bits in one bit increments. The bit pattern of the code is also programmable in that logic ones and zeroes can be chosen to be alternated in bit groups of one, two, three, four, five, six, eight, ten, twelve, or fifteen.

- (3) Frame Synchronization Code The frame synchronization code can be varied between 0 to 15 bits in length. In addition, the content or bit pattern of the code is programmable.

- (4) Sensor Data The data portion of the burst message can be varied in length from 0-255 bits. The bit pattern of the sensor data can be uniquely programmed for up to sixteen bits of sensor data. For sensor data formats longer than 16 bits in length, the unique 16-bit pattern selected will repeat.

- (5) Number of Messages Transmitted. The number of messages transmitted can be varied between 0 and 999. A 255 bit period is fixed between successive burst message transmissions, and during this fixed "dead" time the MSK modulator is disabled. Also, at the conclusion of the selected number of transmissions, the MSK modulator is disabled.

d. Output Signal-to-Noise Adjustments - A separate noise input port for the summation of modulated signal and noise, in conjunction with the presence of a bandpass filter of adjustable noise bandwidth located at the final output stage of the MSK Transmitter Simulator, allows precise and adjustable settings of output modulated signal-tonoise ratios to be derived.

8

- e. Modulation Center Frequency The center frequency of the output modulated signal is set to the center frequency of the bandpass filter-which is 20.016 KHz.

- f. Mark/Space Frequency Check A switch is provided to allow the operator to continuously output either the mark frequency or the space frequency for frequency verification purposes and checkout of the coherent demodulator in the Receive Channel Simulator.

- g. Data Checker Circuitry is provided in the MSK Transmitter Simulator to accept bit clock and data from either the coherent or non-coherent Receive Channel Simulator and compare the data pattern recovered against the data pattern transmitted. Features of the data checking circuitry are:

- (1) Either polarity of the recovered bit clock and digital data can be accommodated.

- (2) Adjustable delay lines in the data checker allow accommodation of data recovery circuitry delays up to a maximum of three bit periods.

- (3) For the continuous transmission of the 32,767

bit P/N code, a counter the contents of which

are displayed records the number of bit errors

- detected. This error count continues until the MSK Transmitter Simulator is reset.

- (4) For the burst message format the data checker is configured to display the number of correctly received messages.

### 2. COMMUNICATIONS LINK SIMULATOR FEATURES

- a. Input Requirements The filtering in the Communications Link Simulator restricts the centering of the modulated input signal to  $20 \text{KHz} \pm 6.5 \text{KHz}$ .

- b. Output Signal The output of the Communications Link Simulator consists of the modulated input plus an interference tone, if desired. The output carrier frequency may be adjusted over the range of 25KHz +15KHz.

- c. IF Throughput Frequency The input is up-converted to a working

IF frequency of 10.7MHz. The choice of 10.7MHz allows

the use of commercial off-the-shelf equipment to achieve a

final r-f output.

- d. Linearity All amplification and translation processes are linear class A type processes. Provision is made, however, to insert by switch selection a hard-limiter at the output of the final 10.7 MHz stage prior to down-conversion. This feature is included to examine what spectral spreading of the MSK signal, if any, will result from using non-linear class C type power amplifiers in an r-f transmitter. Another question that will be addressed by this feature is the amount of degradation, if any, that occurs in the MSK demodulation process as a result of non-linear processing of the transmitted signal.

- e. External Inputs In addition to the MSK modulated baseband signal input port, three other input ports are provided. One input is the down-conversion local oscillator port which can be driven from a commercial type frequency synthesizer. Another input provides a means of summing noise or interference with the modulated tone at the final IF frequency of 10.7 MHz. The third port is for inputting a serial digital data stream to be used in implementing the MSK modulation format at the 10.7 MHz IF frequency.

- f. IF Implementation of MSK Modulation Format Capability is provided to implement the MSK modulation format at the IF working frequency of 10.7 MHz. Two implementation techniques are provided a varactor type phase shift network driven by a ramp generator controlled by the digital data stream and a VCXO whose gain is adjusted to provide the mark and space frequencies when driven by the serial digital data stream. These modulation techniques are provided to evaluate the feasibility of accomplishing the MSK modulation format at the final RF stage thereby eliminating any up-conversion processes.

- 3. Search Subsystem Simulator Features

F.34.43

- a. Chirp-z Transformer Parameters the chirp-z transformer is a 500 point transform yielding 250 real frequency coefficients and 250 imaginary frequency coefficients. The critical parameters of the transformer are:

- (1) Analyzing Bandwidth 160 Hz

- (2) Search Band 0 to 40 KHz

- (3) Search Time 6.25 milliseconds

- b. Assignment Logic Parameters

- (1) Selection is provided to assign the Receive Channel

Simulator upon threshold detection either during the outputing of real frequency coefficients from the chirp-z transformer or during the outputting of both real and imaginary frequency coefficients. This feature allows data to be taken to determine if processing the imaginary spectral coefficients as well as the positive coefficients results in any improvement in the ratio of probability of detection to false alarm rate.

- (2) Time-out logic is provided to inhibit the assignment of the Receive Channel Simulator to any threshold occurrence once an assignment is made. The duration of the time-out window can be adjusted from 0 to 1.0 second in increments of 1.0 millisecond.

- restricted, by switch selection; to only that time period when an actual message is being transmitted by the MSK Simulator. The selection of this capability reduces the probability of burst type messages being missed because the Receive Channel Simulator has been assigned to a noise occurrence. The restriction effectively simulates a complex time-out assignment sequence whereby the Receive Channel Simulator is interrogated for an in-lock condition, the proper reception the frame synchronization code, etc.

- (4) The format of the channel assignment as output by the assignment logic is a sinusoidal signal of proper frequency such that the incoming signal, when up-converted by the sinusoid, will be centered at 180KHz.

- c. Assignment Logic Self Test Functions Several test features are incorporated into the assignment logic to provide a ready means of characterizing the chirp-z transformer. The two major test configurations implemented are:

- test mode the output of the threshold detector following the chirp-z transformer is interrogated for an event at a selectable frequency bin. If a detection is present, a counter is updated.

The counter will continue to be updated until a selectable number of spectral sweeps have been completed, at which time the test is terminated.

A seven segment LED display is included in the Simulator to display the counter's content.

- (2) False Alarm Test Mode This test mode is identical to the probability of assignment test mode except that the output of the threshold detector is interrogated at every frequency bin rather than just one particular frequency bin.

- 4. Receive Channel Simulator Features

(E.

1600

A. C. C.

A 23 W

- (a) Coherent Demodulator

- (1) A coherent demodulator utilizing two phase lock loops is provided to coherently recover the bit

- clock and the NRZ digital data stream from the incoming MSK modulated signal.

- (2) Another function of the coherent demodulator is to display by means of a seven segment LED display the frequency of the incoming modulated signal. A counter drives the LED display. The counter counts the zero crossings of an oscillator which is phase locked to the mark frequency of the incoming MSK modulated data, and thus records the mark (upper) frequency of the received signal.

The accuracy of the frequency measurement is + 0.1 Hz.

### (b) Non-Coherent Demodulator

- A non-coherent technique for demodulating the

MSK signal is accomplished using an FM discriminator

type demodulation technique. A phase lock loop

is utilized to track the modulation carrier, with

the data discrimination accomplished by differentiating

the output of the phase lock loop's phase detector.

- (2) Data recovery is accomplished by using a bit sync clock as supplied by the MSK Transmitter Simulator to drive a data detector located at the output of the demodulator.

- (3) The frequency measurement circuitry is that circuitry utilized in the coherent demodulator.

# C. Breadboard Frequency Plan

Se course

A

A diagram showing the allocation or assignment of frequencies is shown in Figure 2-2. The key frequency assignments are:

Digital Data Bit Rate - 320 Hz

Digital MSK Modulator Carrier - 20,016 Hz

Final I-F throughput Frequency - 10.7 MHz

Chirp-z Transformer Search Band - 0-40 KHz

Receive Channel Input Frequency - 180 KHz

The criteria used to select the above frequencies was not one of optimization in terms of minimizing the number of serviceable mobil and fixed platforms for a given frequency band allocation, but rather to simplify the breadboard hardware and use where possible existing designs or commercial equipment. While simplifying hardware and hardware design tasks, the frequencies selected also provide the opportunity to examine and demonstrate all pertinent properties of both MSK modulation/demodulation techniques and the chirp-z transformer as a search system.

The principle driving force in selecting the above frequencies was the existence of a proven design for a 500-point chirp-z transformer capable of running at a basic clock rate no greater than 750 KHz. The chirp-z transformer utilizes a four phase CCD chip, with the four phases being derived by dividing down the basic input clock by a divide-by-eight countdown circuit. The effective maximum rate in which the CCD cells can be clocked then is 93.75 KHz --which results in a total of 5.33 milliseconds being required to clock a given sample through all 500 cells. A maximum throughput rate of 5.33 milliseconds equates to a maximum analyzing bandwidth of 187.5Hz and a maximum search band of 46.875KHz. With these limitations, it was decided to implement a search system which covered the same frequency search band as did the Random Access Measurement instrument for ease in comparing the performance of the two systems.

A basic clock rate of 640KHz yields such a system by creating a frequency search range of 0-40 KHz. The analyzing bandwidth which results is 160Hz.

3

**高級**

ALC: NO

TANA .

The next assignment made was the carrier frequency of the baseband digital MSK modulator. Here the decision was made to place the carrier near the center of the chirp-z transformer search band to allow maximum flexibility of carrier adjustment via the frequency translation processes contained in the Communications Link Simulator. The exact carrier frequency chosen-20,016 Hz- was picked as it falls as near to the center of the frequency search band of the chirp-z transformer as is possible to achieve-considering the 32 Hz frequency resolution limitation of the digital MSK modulator.

The frequency resolution of the digital MSK modulator-32Hz-directly defines the digital data rate or bit clock frequency. The modulation format of the digital MSK modulator is one of continuous phase FSK modulation with the modulation index variable from 0.1 to 10.0 in steps of 0.1. A modulation index of 0.5 defines MSK modulation - which is but a special case of continuous phase FSK modulation. With a frequency resolution of 32 Hz in the digital MSK modulator and a modulation index resolution requirement of 0.1, the data rate is uniquely defined to be 320 Hz. The only question then is why a resolution limitation of 32 Hz in the digital MSK modulator. A finer frequency resolution would require a basic clock higher than the 2.097152 MHz clock used; and although a higher clock rate is feasible, the added expense and complications associated with a higher clock rate cannot be justified in terms of the objectives of the breadboard hardware. The choice of a basic clock frequency as high as 2.097152 MHz is necessary, however, to minimize the effects of the discrete nature of the digital MSK modulator by sampling the carrier frequency at a rate one hundred times faster than the carrier frequency itself. With a basic clock requirement as high as 2.097152 MHz, the 32 Hz resolution limitation is chosen as it divides into 2.097152 MHz by a power of two  $(2^{16})$  - which is a requirement

for the digital technique implemented - and it can be easily achieved by using only four 4-bit arithmetic stages in the digital oscillator portion of the digital modulator.

U

The Communications Link Simulator uses an i-f throughput frequency of 10.7 MHz - which is a standard i-f frequency frequently used as an intermediate frequency in r-f equipment. The choice of a standard i-f such as 10.7 MHz allows the use of standard off-the-shelf hardware, such as crystal filters, in implementing the Communications Link Simulator. Also, the 10.7 MHz i-f can be readily used to both drive a commercial off-the-shelf r-f translator/ transmitter and serve as the final i-f output frequency of a commercial receiver should it ever become necessary to expand the ADC/PL breadboard to have r-f transmission/reception capability.

The last key frequency assignment required is that of the center or receive frequency of the Receive Channel Simulator. The Search Subsystem Simulator, upon detecting the presence of a signal, assigns the detected signal to the Receive Channel Simulator by outputting a sinusoid of proper frequency such that the incomin signal, when mixed with the sinusoid will fall within the receive channel bandwidth of the Receive Channel Simulator. The selection of the receive frequency, or the frequency range of the sinusoid output by the Search Subsystem Simulator, is influenced by two conflicting requirements. The coherent demodulation technique requires quite stable crystal controlled VCXO's, which are readily available only at the higher frequencies, to provide acquisition discrimination in the two phase lock loops between the mark and space frequencies. On the other hand the implementation of the sinusoid output by the Search Subsystem Simulator and the bandwidth or Q limitations of the bandpass filter which follows the mixing of the incoming signal with the sinusoid place a limitation on how high the Receive Channel Simulator center frequency can be. The choice of the nominal center

frequency of 179,984 Hz is a compromise between the two conflicting requirements.

The VCXO center frequencies for the two phase lock loops in the coherent MSK demodulator are a direct fallout of the center frequency selection in the Receive Channel Simulator. For a nominal center frequency of 179,984Hz, the MSK modulation format yields a space or logic zero frequency of 180,064 Hz and a mark or logic one frequency of 179,904 Hz. Allowing for the frequency doubler, the phase lock loop assigned to the mark frequency will have a VCXO center frequency of 359.808 Hz. The center or rest frequency of the VCXO in the space frequency phase lock loop is complicated by the requirement that the VCXO also provide the clock input for implementing the frequency measurement. To transmit a nominal data message of 64 bits requires 200 milliseconds in time for a 320 bps data rate. To accomplish a 0.1 Hz measurement accuracy in 200 milliseconds requires the measured clock or VCXO output to be fifty times the actual frequency to be measured. The space VCXO must then be followed by a divide-by-fifty counter so that the VCXO itself can run at a frequency fifty times the incoming space frequency. This results in a VCXO rest frequency for the space phase lock loop of 18,006,400 Hz.

### D. MSK Transmitter Simulator

The MSK Transmitter Simulator consists of three major subunits - a digital data generator, a data checker, and an MSK modulator. The digital data generator can operate in one of two modes. It can output a 320 bps data stream of random data bits as generated by a 32,767 bit P/N code generator or it can output structured bursts of data with each data burst consisting of a CW preamble, a bit synchronization code, a frame synchronization code, and data. The structure of each transmission is fully programmable in that the CW preamble, bit synchronization code, frame synchronization code, and data may all be varied in length and all but the CW preamble may be programmed in terms of data or code content. In the case of the burst message mode, each message is separated in time from the previous message by 800 milliseconds and a provision is also incorporated in the hardware implementation to transmit a selectable number of transmissions and then halt all transmissions. feature allows message reception statistics to be easily measured. The digital data output by the data generator can be selected to be either Manchester (split-phase) or NRZ encoded data.

The data checker provides a means of comparing the data received by the Receive Channel Simulator with the data output by the data generator. Because of the two data modes available in the data generator, the data checker must contain two data checking facilities - one for handling the P/N code data and one for handling the burst messages. The P/N code data mode is used primarily to facilitate bit error measurements, and as such the output of the data checker in the P/N data mode will be a displayed count showing the time accumulated number of bit errors detected. By accumulating an error count for a pre-determined period of time, bit error rate measurements for various signal-to-noise ratios can be easily made. The burst data mode is

In this mode the interest is primarily concerned with questions such as can bit synchronization be established within the code length assigned to the bit synchronization code, can the search system detect the presence of signal and assign the Receive Channel Simulator within the time allocated to the CW code preamble, etc. The output of the data checker in the burst data mode then is a count display showing the number of correct messages received. If, for example, the data generator were programmed to transmit 500 burst messages, and at the conclusion of 500 transmissions the data checker displayed a count of 495, the probability of successfully receiving each transmission is 99.0 %. The count displayed then effectively represents the probability of success, and critical parameters governing the successful detection and reception of messages can be easily plotted as a function of the probability of success, with the signal-to-noise ratio serving as an independent parameter to create a family of curves.

The ADC/PL breadboard system contains three MSK modulators. The MSK modulator housed in the MSK Transmitter Simulator is an adaption of the digital oscillator technique developed for the Random Access Measurement System.

The effective carrier of the modulated output is at 20.016 KHz. Although a higher carrier could be implemented, the technique does impose frequency restrictions which inhibit implementing the modulation at the final r-f carrier. The use of the digital oscillator technique to achieve the MSK modulation format will thus require up-conversion circuitry to translate the modulation carrier to the final r-f frequency. For this reason two additiona MSK modulators are implemented in the Communications Link Simulator to test techniques for implementing MSK modulation at the final r-f carrier frequency.

The primary reason for having the digital oscillator type MSK modulator is that it is a very low risk technique of obtaining the proper MSK modulation format. In addition, the digital implementation provides a ready means of implementing coherent FSK modulation. The digital oscillator modulation technique is designed so that the deviation (ΔF/data rate) ratio can be varied from 0.1 to 10.0 in steps of 0.1 - where MSK modulation is but a special case of coherent FSK utilizing a deviation ratio of 0.5. The ability to vary the deviation ratio allows MSK modulation to be compared against other coherent FSK deviation ratios using the non-coherent demodulator in the Receive Channel Simulator. The digital MSK modulator also contains a programmable Q bandpass filter which is used to ascertain the effect of transmission bandwidth on the bit error performance of the coherent MSK demodulator, as well as the non-coherent MSK demodulator, in the Receive Channel Simulator.

# D.1 Data Generator

A detailed block diagram of the data generator is presented in Figure 2-3. Upon initiating a transmission, a CW tone length counter in the preamble format selection circuitry begins counting data clocks. When the count in the counter equals the count selected in the CW tone length switch bank, the counter is disabled and a bit sync code length counter is enabled to count data clocks. During the time the CW tone length counter is active an inhibit signal is output to instruct the MSK modulator to transmit carrier only - i.e., no modulation. Upon activating the bit sync code length counter, the data generator begins outputting the bit synchronization code. The format of the code is selectable and may consist of an alternating one-zero data pattern or alternating groupings of ones and zerors - with the groupings consisting of two, three, four, five, six, eight, ten, twelve, or fifteen bits of logic ones followed by the same number of logic zeroes. The provision

to select the format of the bit synchronization code was incorporated into the data generator to allow different bit synchronization codes to be evaluated in characterizing the acquisition properties of the coherent MSK demodulator. When the count in the bit synchronization code length counter equals the count selected in the bit sync code length switch bank, the counter is deactivated and the data generator begins outputting the 32,767 bit P/N code or the frame synchronization code portion of a burst message. Both the CW preamble and the bit synchronization code may be individually adjusted in length between 0 and 99 bit periods in increments of one bit period. It is also noted that regardless of whether the P/N code or burst message data mode is selected, the initial part of the message consists of a CW preamble followed by a bit synchronization code. This preamble occurs for every burst message transmitted, but only occurs once for the continuously transmitted P/N code - unless a reset button is pushed to re-initiate the data generator.

The burst message format selection circuitry structures the data portion of a burst message transmission. At the completion of the bit synchronization code, a frame sync code length counter is enabled and begins counting data clocks. At the same time, a frame sync register, which has been previously loaded with the frame synchronization code as selected by the frame sync data entry switches, begins serially shifting out the frame synchronization code. The length of the frame synchronization code is adjustable between 0 and 15 bits in one bit increments and is determined by the setting of the frame sync code length switch bank. When the count in the frame sync code length counter equals the count selected in the switch banks, both the frame sync counter and register are disabled and a data work length counter and a data word register are enabled. The data word content and length are selected in exactly the same manner as the frame synchronization code, except that the data content may be uniquely defined

for only sixteen bits while the word length may be varied from 0 to 255 bits in increments of one bit. As the data is serially shifted out of the data word register, it is routed at the same time back to the serial input of the register. For data word lengths greater than 16 bits, the 16-bit message selected by the data word data entry switches is repeatedly transmitted, as a whole or a portion thereof, until the count in the data word length counter equals the count selected in the word length switch bank. At this time both the counter and register are disabled and the time-out or interval timer is activated. At this same time an inhibit signal is activated to disable the MSK modulator.

H

The interval timer in the burst message format selection circuitry counts data clocks for a fixed interval of 256 bit periods - which is 800 milliseconds for a 320 Hz data clock. At the conclusion of the time-out interval the MSK modulator inhibit signal is deactivated, a reset pulse is generated to instruct the data generator to begin a new transmission by activating the CW tone length counter, and a transmitted message counter is updated by one count. The purpose of the transmitted message counter is to allow the number of burst messages transmitted to be selectable.

When the count in the transmitted message counter equals the count selected in the message count selection switches - which can range from 0 to 999 in increments of one, the automatic generation of the reset pulse at the conclusion of a time-out interval is disabled. The data generator is then deactivated and may be re-activated only by manually depressing the reset push button switch.

The formats of the messages as assembled by the data generator are shown in Figure 2-4. It is noted that for both the P/N code  $\dot{a}_c$  \*a selection and the burst message data selection, the beginning of the transmission consists of a CW preamble followed by a bit synchronization code. For the P/N code format, the pseudo-random data follows the bit

# P/N CODE DATA FORMAT

CH PREAMBLE BIT SYNCHRONIZATION CODE 32,767 BIT P/N CODE 0-99 BITS DATA

CODE SELECTABLE

f = f<sub>carrier</sub> FOR MANCHESTER ENCODING

f = f<sub>mark</sub> FOR NRZ ENCODING

## BURST MESSAGE DATA FORMAT

|                                                                                            | CW PREAMBLE<br>0-99 BITS | BIT SYNCHRONIZATION CODE<br>0-99 BITS<br>CODE SELECTABLE | I FIGURE 3111CHIOUTET TO THE                                      | DATA MESSAGE<br>0-255 BITS | T=255 BITS CW<br>PREAMBLE |

|--------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------|-------------------------------------------------------------------|----------------------------|---------------------------|

| f = f <sub>carrier</sub> FOR MANCHESTER ENCODING<br>f = f <sub>mark</sub> FOR NRZ ENCODING |                          | FOR MANCHESTER ENCODING R NRZ ENCODING                   | A 16-BIT DATA SELECTABLE<br>SEGMENT IS REPEATEDLY<br>TRANSMITTED. |                            |                           |

DATA GENERATOR MESSAGE FORMATS Figure 2-4

synchronization code, while for the burst message format the frame synchronization code and data follow the bit synchronization code. The frequency generated by the MSK modulator during the CW preamble depends on whether the serial data stream output by the data generator is NRZ or Manchester (split-phase) encoded. The use of two different frequency values during the CW preamble is due to the preference of different frequency preambles by the coherent and non-coherent demodulators in the Receive Channel Simulator. For the coherent demodulator, which is capable of recovering NRZ encoded data, the mark frequency is transmitted during the CW preamble as it falls in the center of a frequency bin in the Search System Simulator. In order that the two phase lock loops in the coherent demodulator uniquely lock to the mark and space frequencies, the pull-in range of the two loops must be less than the frequency separation of the mark and space frequencies. This requirement disallows any uncertainity in the assignment pattern of the Search System Simulator and for this reason the frequency transmitted during the CW preamble resides at the center of a frequency bin. It should be noted however that this is not a "real" problem since it can be readily resolved by simply making the analyzing bandwidth of the Search System Simulator less than half the bit rate clock of the transmitted message. For the breadboard system, however, this was not practical with the chirp-z transformer design utilized. For noncoherent demodulation, the demodulator implemented in the Receive Channel Simulator requires a component of carrier to always be present. For this reason then Manchester encoding is always used when non-coherent demodulation tests are being conducted. To allow the non-coherent demodulator to initially acquire the carrier, the CW preamble frequency for Manchester encoding is set at the carrier frequency.

## D. 2. Data Checker

A detailed block diagram of the data checker is shown in Figure The data checker consists of detector data timing alignment circuitry, burst message data checker circuitry, and comparison and event counter circuitry. The demodulation and data recovery circuitry in the Receive Channel Simulator recovers the transmitted data, but the recovered data will not be in phase with the data output by the data generator due to delays encountered in the circuitry. To compare the data received against the data transmitted, the phase error must be removed. The detector data timing alignment circuitry delays the bit clock and data generator data by an adjustable amount so that it will match the phase of the data output by the Receive Channel Simulator. The alignment is accomplished by adjusting the phase of the data generator data clock by an adjustable one-shot until the leading edge of the clock coincides with the leading edge of the recovered bit clock. The delayed clock is then used to load the data generator data serially into a four stage shift register. The data as it resides in the shift register is then in phase with the data recovered in the Receive Channel Simulator. To accommodate more than 360° or one bit interval of delay, a switch is provided to select the data from the shift register to be compared against the data output by the Receive Channel Simulator from any one of the four stages of the shift register. The data from the Receive Channel Simulator is also loaded into a single stage shift register, so that selecting data from the first stage of the four stage register accommodates phase shift discrepancies from  $0^{\circ}$  to  $360^{\circ}$ , the second stage shifts from 360° to 720°, etc. Additional circuitry is also provided to accomodate either phase of bit clock or data from the Receive Channel Simulator.

For the P/N code data mode, the delayed data generator data and the data from the Receive Channel Simulator are compared one data bit at a time. If an agreement is not found on any one data bit, an error pulse is output which updates the event counter by one count. Over an interval of time then, the count in the counter displays the number of data bit errors that have occurred in the time interval.

H

For the burst data transmission mode, the question is not how many data bit errors have occurred but rather how many recovered messages had one or more bit errors. The burst message data checker circuitry is implemented to inspect an entire message and output a count pulse if and only if the recovered message has no errors in it. This results in the event counter displaying the number of messages correctly received. The data from the Receive Channel Simulator is input into a 16-bit shift register whose contents are compared against three banks of switches-a frame sync. pattern switch bank, a data word pattern switch bank, and a message complete switch bank. However, the recovered data will be appropriately aligned in the shift register to allow comparing against one of the switch banks only at specific points in time. These points in time are provided by compare enable signals output by the burst data format selection circuitry in the data generator. A frame sync complete signal signifies that the frame synchronization code has just been transmitted, a 16-bit word complete signal becomes true each time the programmable 16-bit word in the data word portion of the message has been transmitted in its entirety, and a message complete signal signifies that the last bit of the burst message has just been transmitted. This last signal is necessary as the data word length may not consist of an integer number of 16-bit words. When one of the three signals occurs, it enables a comparison to be made between the contents of the 16-bit shift register and the appropriate switch bank.

At the beginning of a message transmission a latch is preset to a logic one. If a comparison is not found when one of the three compare enable signals occurs, the latch is cleared. If the latch remains set through the entire period of transmission then, no errors were found. The latch output is gated with a delayed version of the message complete signal to generate an event pulse to update the event counter counting the number of correct messages received, and thus the latch must remain set if a received message is to be counted as an error free message reception. It is also noted that the three compare enable signals output by the burst data format selection circuitry must be delayed in the same manner as the data generator data clock so that the comparisons will be made at the proper points in time.

#### D.3 MSK Modulator

The MSK modulator housed in the MSK Transmitter Simulator is a digitally implemented modulator based on the digital oscillator technique developed on the Random Access Measurement System (RAMS) program. Two analog MSK modulator techniques are housed in the Communications Link Simulator, but the digital implementation offers two advantages not found in the analy implementations. The digital technique provides a more precise formulation of MSK modulation in that the deviation ratio (which is 0.5 by definition for MSK modulation) is precisely 0.5 for the digital technique while only approximated in the analog technique. The availability of both modulation schemes allows data to be taken on the effect of the "purity" of the MSK modulation on the performance of both coherent and non-coherent demodulation techniques. Also, the digital implementation technique provides a low frequency modulation carrier- 20.016 KHz

that can be directly input into the Search Subsystem Simulator and the Receive Channel Simulator. This direct interface capability allows data to be taken to determine the effect, if any, on the demodulation processes from non-coherently up-converting and down-converting the MSK modulated signal via the Communications Link Simulator.

A detailed block diagram of the MSK modulator is shown in Figure 2-6. The digital oscillator used to implement the MSK modulation format is a non-recursive digital oscillator that uses a stored quantized phase plane as the quantizing element. The frequency output by the oscillator is determined by the rate in which a digital sampler cycles through the quantized phase plane. A binary number serves as a digital representation of the frequency to be generated and controls the cyclic rate of the sampler. The digital number is input into a full adder whose output is strobed into a holding register. The output of the holding register serves as the other input to the full adder. The holding register thus serves as an accumulator, and the accumulated count at any one time represents where in the discrete phase plane the output frequency resides. The accumulator is updated at the reference clock rate of 2.097152 MHz, and on each clock pulse the accumulated count is increased by an amount equal to the digital number input into the adder. Thus the digital number determines the rate in which the discrete phase points in the phase plane are addressed and cycled through and hence controls the frequency output.

If the digital number which controls the output frequency is one, the 16-bit accumulator register will take  $2^{16}$  or 65,536 clocks to cycle the accumulated count from 0 to 65,535 and then overflow back to 0. For the accumulator reference clock of 2.097152 MHz, the time required to complete one cycle through the phase plane is:

The presentation of  $2\pi$  radians in 31.25 milliseconds describes a frequency of 32 Hz. If the digital number is changed to two, the presentation of  $2\pi$  radians is accomplished in 15.625 milliseconds, describing a frequency 64 Hz. It is clear then that the digital number, when multiplied by 32, equals the frequency output by the digital oscillator.

The discrete phase plane is stored in a read-only memory (ROM) which is addressed by the contents of the accumulator. The accumulator content represents where in phase the output frequency is at some point in time, and as a function of time describes a sawtooth waveform with a repetition rate equal to the output frequency. The purpose of the ROM is to convert the sawtooth waveform into a sine wave function, with one period of the sine wave function described during a single cycle of the accumulator. The ROM physically consists of two separate ROMS, with one ROM containing the phase points for the first half of the accumulator count and the other the phase points for the second half of the accumulator The ten most significant bits of the accumulator address the ROM networks with the most significant bit of the accumulator used to steer the activation of the appropriate ROM. The ROM outputs are tristate so that corresponding outputs from each ROM can be tied together in a wired-or configuration. The wired-or output from the two ROM networks is a quantized or digital version of the desired sine wave and thus a digital to analog converter (DAC) is used to obtain the final output. The most significant bit of the accumulator is also applied to the DAC to obtain a bi-polar output which is the final MSK modulated output.