#### **General Disclaimer**

#### One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some

of the material. However, it is the best reproduction available from the original

submission.

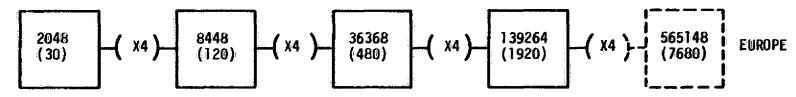

Produced by the NASA Center for Aerospace Information (CASI)

## **Technical Report**

# DATA SYSTEMS ELEMENTS TECHNOLOGY ASSESSMENT AND SYSTEM SPECIFICATIONS

(ISSUE NO. 2)

(NASA-CR-150677) DATA SYSTEMS ELEMENTS TECHNOLOGY ASSESSMENT AND SYSTEM SPECIFICATIONS, ISSUE NO. 2 (Teledyne Brown Engineering) 758 p HC A99/MF A01 CSCL 05E

N78-22972

Unclas 16644

G3/85

**April** 1978

### TECHNICAL REPORT SD78-MSFC-2204

#### DATA SYSTEMS ELEMENTS TECHNOLOGY ASSESSMENT AND SYSTEM SPECIFICATIONS (ISSUE NO. 2)

April 1978

#### Prepared For

DATA SYSTEMS LABORATORY

GEORGE C. MARSHALL SPACE FLIGHT CENTER

MARSHALL SPACE FLIGHT CENTER, ALABAMA

Contract No. NAS8-32539

Prepared By

SYSTEMS DIVISION

TELEDYNE BROWN ENGINEERING

HUNTSVILLE, ALABAMA

#### ABSTRACT

The ability to satisfy the objectives of future NASA Office of Applications programs is dependent on technology advances in a number of areas of data systems. This report examines the hardware and software technology of end-to-end data systems (data processing elements through ground processing, dissemination, and presentation) in terms of state of the art, trends, and projected developments in the 1980 to 1985 timeframe. Capability is considered in terms of elements that are either commercially available or that can be implemented from commercially available components with minimal development.

G. G. Hodges

Program Manager

APPROVED:

R. E. Alger

Manager

Data Processing Department

# PARTIES PACE BLANK NOT FILVED

#### TABLE OF CONTENTS

|       | Pag                                                    |

|-------|--------------------------------------------------------|

| EXECU | E SUMMARY                                              |

| INTRO | CTION                                                  |

| 1.    | TECHNOLOGY PERSPECTIVE                                 |

|       | 1.1 Microelectronic Technology 1-4                     |

|       | 1.2 Evolution of Solid-State Technologies 1-1          |

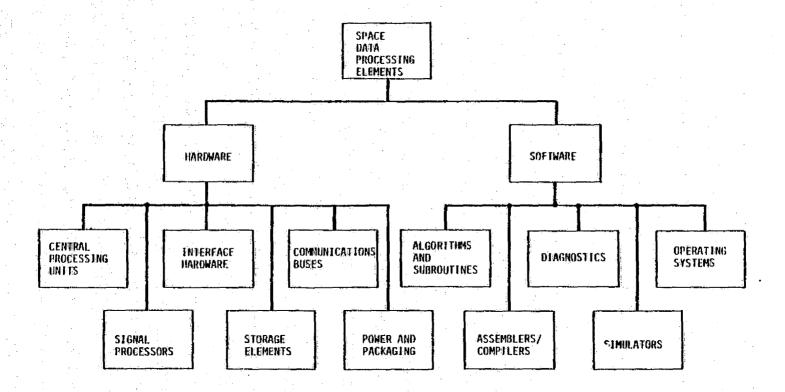

| 2.    | SPACE DATA PROCESSING ELEMENTS 2-1                     |

|       | 2.1 General-Purpose Spaceborne Computers 2-3           |

|       | 2.2 Signal Processors                                  |

| 3.    | SPACE DATA STORAGE ELEMENTS                            |

|       | 3.1 Aerospace Magnetic Tape Recorders 3-4              |

|       | 3.2 Magnetic Bubble Memories                           |

|       | 3.3 Electron-Beam Addressable Memories 3-2             |

| 4.    | SPACE DATA HANDLING ELEMENTS                           |

|       | 4.1 Digital Data Handling Systems 4-4                  |

|       | 4.2 Analog Data Systems                                |

| 5.    | SPACE-TO-GROUND COMMUNICATIONS ELEMENTS 5-1            |

|       | 5.1 Spaceborne Transmitters 5-3                        |

|       | 5.2 Spaceborne Antennas 5-3                            |

|       | 5.3 Relay Satellite Technology for Space Data Transfer |

|       | 5.4 Ground Station Antennas 5-5                        |

|       | 5.5 Microwave Receivers 5-6                            |

|       | 5.6 Modulation, Demodulation, and Coding 5-7           |

(1)

#### TABLE OF CONTENTS - Continued

|    | Page                                         |  |

|----|----------------------------------------------|--|

| 6. | PREPROCESSING ELEMENTS 6-1                   |  |

|    | 6.1 Bit Synchronizer Elements 6-4            |  |

|    | 6.2 Signal Decoder Elements 6-8              |  |

|    | 6.3 Demultiplexer/Decommutator Elements 6-18 |  |

|    | 6.4 Wideband Recording Elements 6-23         |  |

| 7. | GROUND PROCESSING ELEMENTS                   |  |

|    | 7.1 Processor/Computer Elements              |  |

|    | 7.1.1 Microcomputers                         |  |

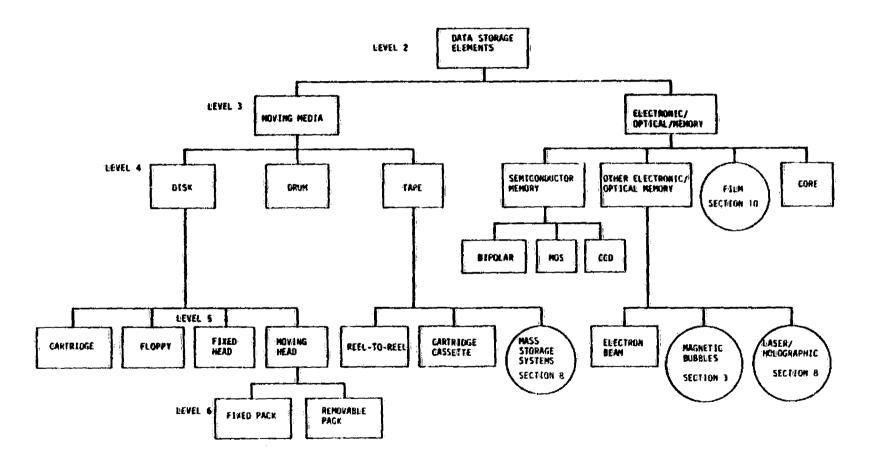

|    | 7.2 Data Storage Elements                    |  |

|    | 7.2.1 Semiconductor Memory                   |  |

|    | 7.2.1.1 Bipolar Memory                       |  |

|    | 7.2.2 Other Electronic/Optical Memory 7-103  |  |

|    | 7.2.2.1 Electron Beam Addressed Memory       |  |

|    | 7.2.3 Core Memories                          |  |

|    | 7.2.4 Disks                                  |  |

|    | 7.2.4.1 Fixed-Head Disks                     |  |

|    | 7.2.5 Magnetic Tape Systems 7-150            |  |

|    | 7.2.5.1 Half-Inch Reel-To-Reel Tape          |  |

#### TABLE OF CONTENTS - Continued

|    |                                                               | ٠.        | Page                |

|----|---------------------------------------------------------------|-----------|---------------------|

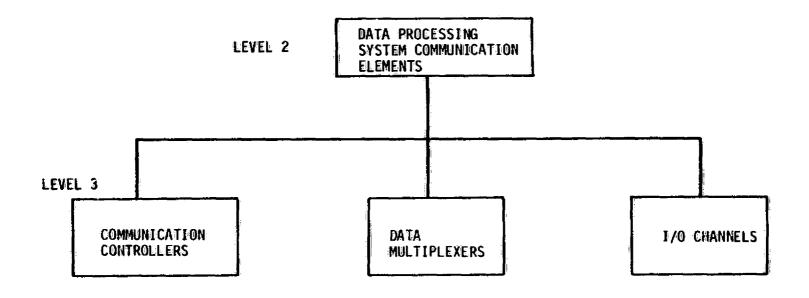

|    | 7.3 Data Processing System Communication Elements             |           | 7-165               |

|    | 7.4 Firmware                                                  |           | 7-172               |

| 8. | DATA BASE SYSTEMS ELEMENTS (GROUND)                           |           | 8-1                 |

|    | 8.1 Usability                                                 | , <b></b> | 8-5                 |

|    | 8.1.1 Data Base Tuning/Reorganization 8.1.2 Data Independence |           | 8-5<br>8-6          |

|    | 8.2 Accessibility                                             |           | 8-9                 |

|    | 8.2.1 Data Security                                           |           | 8-9<br>8-11<br>8-12 |

|    | 8.3 Data Model                                                |           | 8-13                |

|    | 8.4 Data Languages                                            |           | 8-16                |

|    | 8.5 Data Base Architecture (Hardware)                         | • .• •    | 8-20                |

|    | 8.6 Distributed Data Bases                                    | • • •     | 8-22                |

|    | 8.7 Standards                                                 |           | 8-24                |

|    | 8.8 Efficiency/Performance Evaluation                         |           | 8–25                |

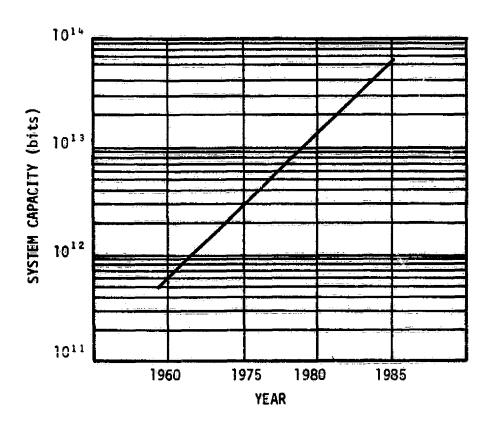

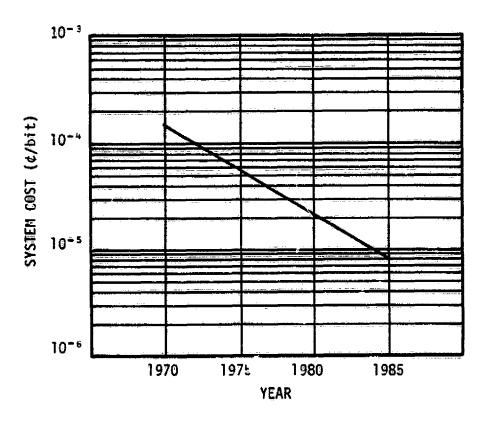

|    | 8.9 Large-Capacity Mass Storage Systems                       | ,         | 8-27                |

|    | 8.9.1 Large-Capacity Magnetic Mass Storage Systems (MSS)      |           | 8-27<br>8-35        |

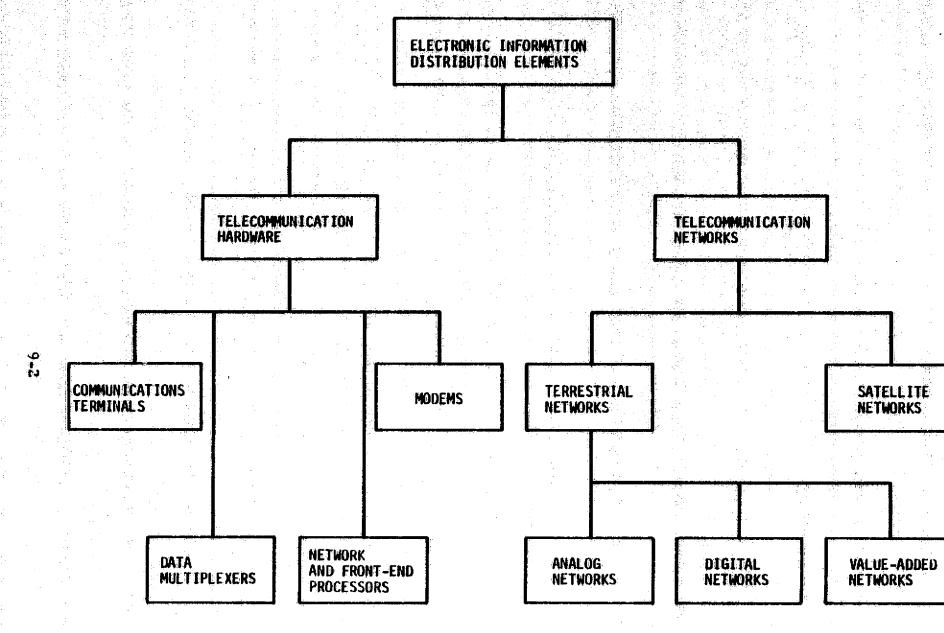

| 9. | INFORMATION DISTRIBUTION ELEMENTS                             | • • •     | 9-1                 |

|    | 9.1 Telecommunication Networks                                |           | 9-3                 |

|    | 9.1.1 Terrestrial Networks                                    |           | 9–4<br>9–25         |

|    | 9.2 Telecommunication Hardware                                | • • •     | 9-44                |

#### TABLE OF CONTENTS - Concluded

|         | e.     |                                            | ·         |         |         |      |   |   |    |   | Page                 |

|---------|--------|--------------------------------------------|-----------|---------|---------|------|---|---|----|---|----------------------|

|         | 9.2.2  | Modems Front-End Process Data Multiplexers | ors       |         |         |      | • | • | •  | • | 9-45<br>9-54<br>9-60 |

| 10.     | INFOR  | MATION PRESENTATION                        | ELEMENTS  | 3       | •, • •  |      | • |   |    | • | 10-1                 |

|         | 10.1   | Dynamic Informatio                         | n Present | tation  | Elemen  | its  | • |   |    | • | 10-4                 |

|         | 10.2   | Hardcopy Informati                         | on Prese  | ntation | n Eleme | nts  |   |   | •  | • | 10-43                |

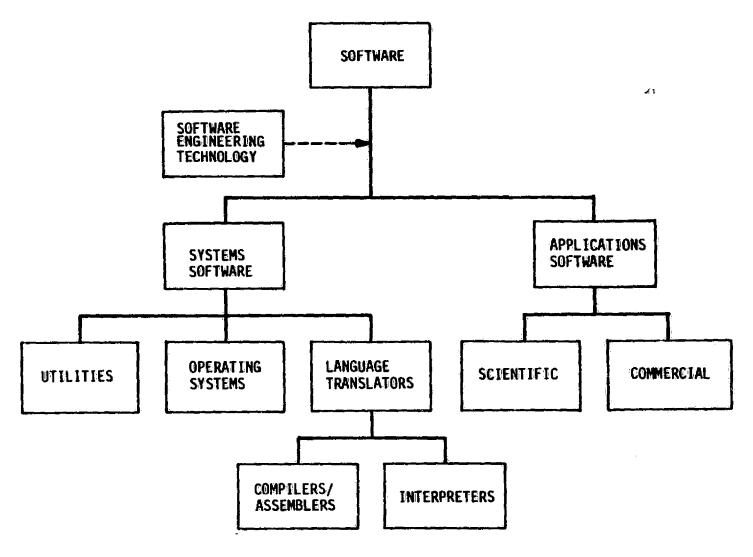

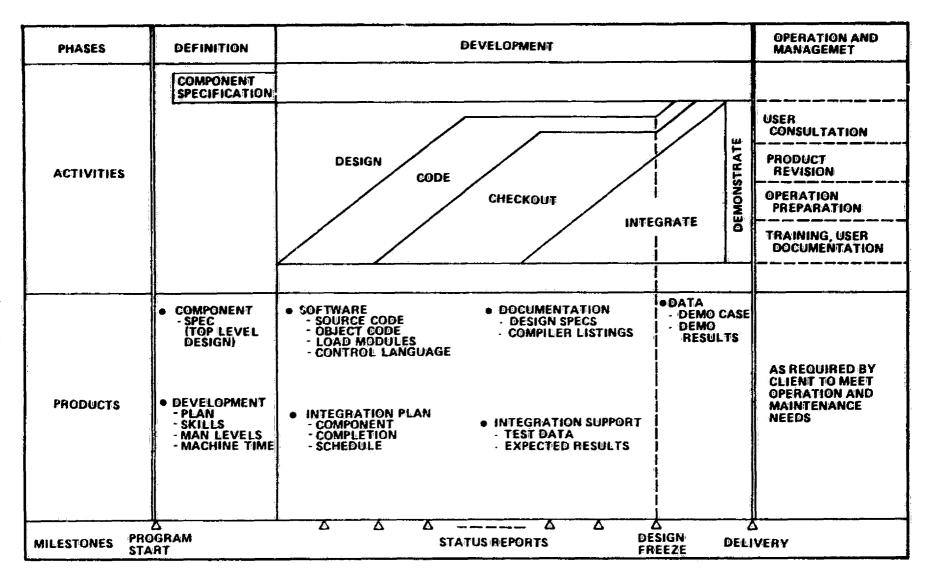

| 11.     | SOFTW  | ARE                                        |           |         |         | . •  | • |   |    | • | 11-1                 |

|         | 11.1   | Operating Systems                          | • • • •   |         |         |      |   | • |    | • | 11-7                 |

|         | 11.2   | Languages                                  | • • • •   |         |         |      |   | • | •. |   | 11-23                |

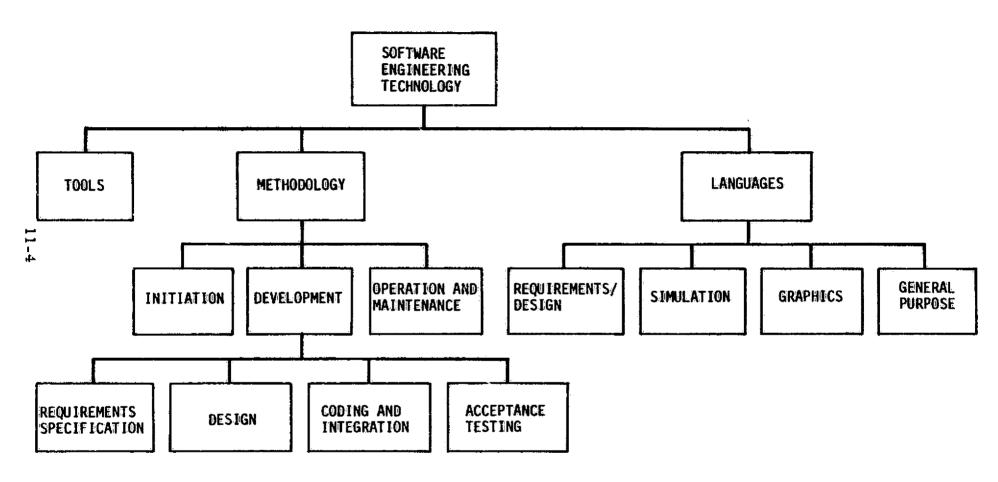

|         | 11.3   | Software Methodolo                         | gy        |         | • • •   | ٠, • |   |   |    | • | 11-43                |

| APPENDI | X A. : | SPACE-TO-GROUND COM                        | MUNICATIO | ONS ELI | MENTS   |      |   |   |    |   | A-1                  |

#### ACKNOWLEDGEMENTS

Many authorities in the field of data systems responded to requests for information in support of this report via the mails, telecom, and visits. Significant parts of the forecasts are the result of their contributions. Many of the respondents generously gave permission to use their names as sources of the information provided. However, the sponsoring agency (NASA) requested that specific references be made only to published literature to eliminate the possibility of embarassment to either individuals or organizations. Individuals and organizations that contributed are listed alphabetically at the end of the report. Their contributions are gratefully acknowledged.

A number of individuals within Teledyne Brown Engineering contributed to the various report sections and subsections. These authors are listed at the end of the report. The technical editors within the TBE publications department also deserve credit for their assistance in editing and coordinating the production of this document.

In addition to the contributors and authors, two individuals deserve special credit for their efforts in the guidance and preparation of this report. The first is Mr. Olen Ely, the program manager during the initial phases of the contract. Also, Mr. Ken Williamson, the NASA technical coordinator, contributed significantly in terms of guidance and helpful suggestions.

#### EXECUTIVE SUMMARY

#### INTRODUCTION

The ability to satisfy the objectives of future NASA Office of Applications (OA) programs depends on technology advances in all areas of data systems. This report examines the technology of end-to-end data systems (space processing elements through ground processing, dissemination, and presentation) in terms of state of the art, trends, and projected developments in the 1980 to 1985 timeframe. Capability is considered in terms of elements that are either commercially available or can be implemented from commercially available components with minimal development. The following paragraphs of this Executive Summary highlight the trends and projected developments in some of the more important areas of data systems as far as NASA's future programs are concerned. The summary and report itself begin with a technology perspective that focuses on the ongoing revolution in microelectronics. This first section of the report presents a background and a basis for many of the trends and projections that are given in the remaining sections of the report.

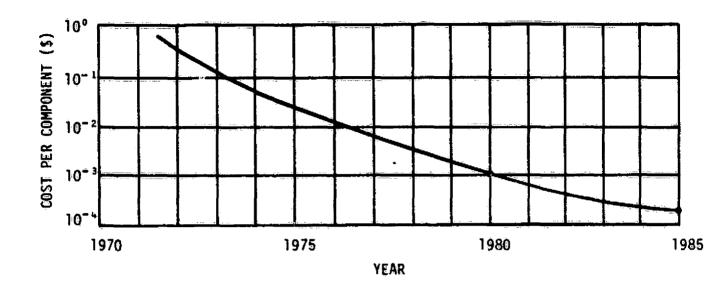

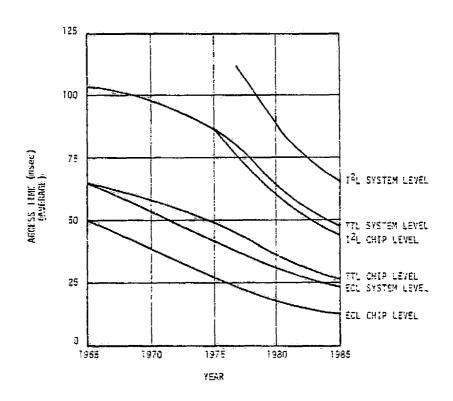

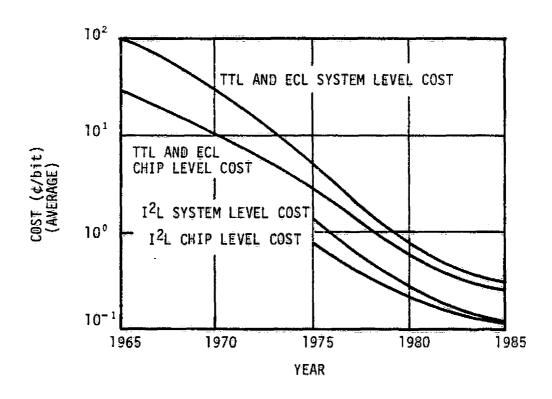

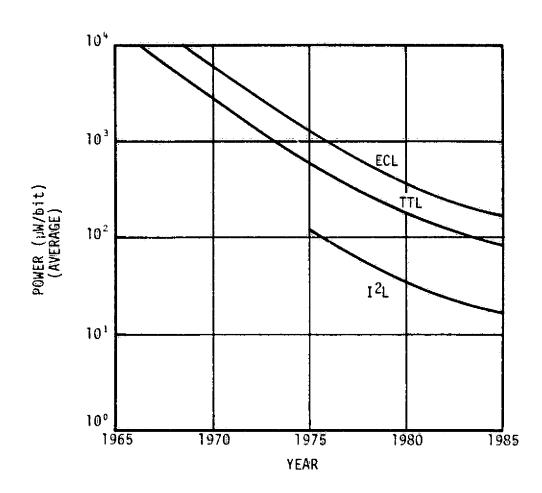

Data systems technology hardware is advancing at an unprecedented rate. Announcements of new products that outperform existing systems are made daily. The majority of advances are primarily the result of improvements in integrated circuit technology. Products are becoming faster, smaller, less expensive, more efficient, more flexible, and more reliable, to name a few areas of improvement. Although the major advances are occurring at the chip level, these advances are being implemented at the system level almost as rapidly as they occur. This report presents the technology status at both the chip level and the system level, with emphasis on the latter area since this is where the effects of NASA's programs will be most heavily felt.

Although the major emphasis throughout the report is on hardware technology, a section on software technology has been added to this report update. Software technology is addressed in Section 11. Software is

important not only because it is a potential bottleneck in data system development but also because it is expected to represent an increasingly larger percentage of the NASA budget for future data systems. Of course this is the case only because of the significant advances that are occurring in hardware technology.

The Executive Summary is presented in the same sequence as the report. The emphasis throughout this summary is on trends and projected developments.

#### TECHNOLOGY PERSPECTIVE

Microelectronic technology has advanced to the point where many established data system concepts are already being reevaluated in order to take advantage of these advances. Although past developments in microelectronic technology have already significantly reduced the cost per unit of performance of data system hardware, the impact of future developments should be even greater.

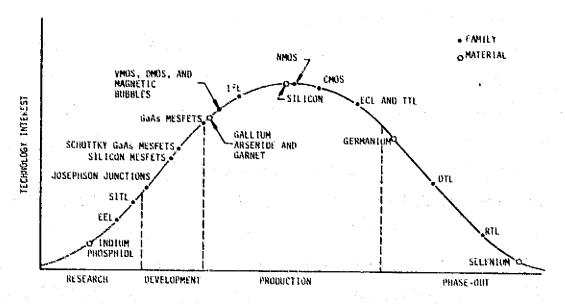

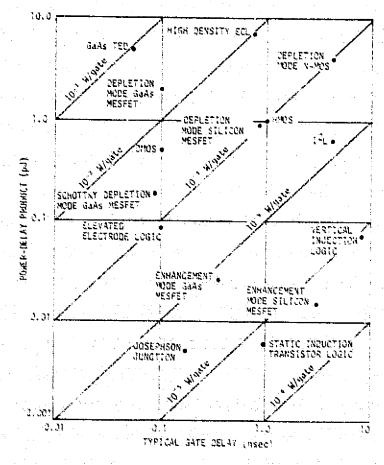

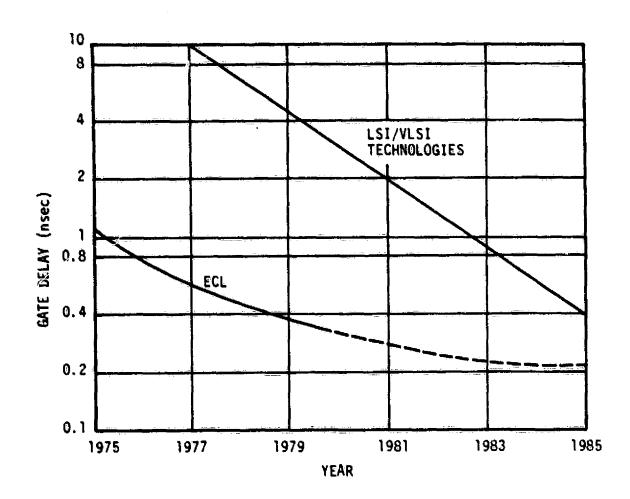

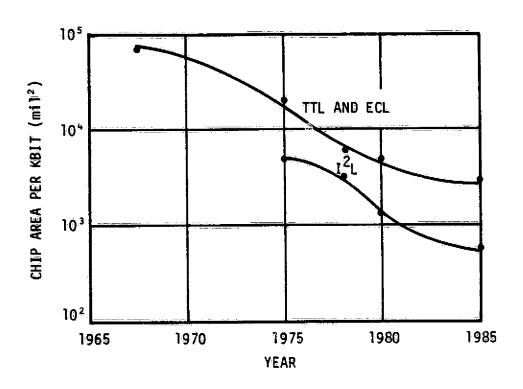

The state of the art in large-scale integrated (LSI) logic device technology includes logic devices with compexities in excess of  $2\times 10^4$  transistors per chip and memory devices with complexities in excess of  $1.3\times 10^5$  transistors per chip. As complex as these devices may seem, submicron technology promises to add approximately two orders of magnitude to the complexity of logic and memory devices by 1985. Currently, the two major candidates for the manufacture of suboptical microelectronic devices are X-ray lithography and electron-beam fabrication. However, photolithography continues to improve and push into the suboptical demain with the use of deep ultraviolet lithography. For example, one company recently reported a photolithographic system capable of fabricating 0.5-µm linewidths.

In addition to advancements in wafer processing, considerable work is being done toward developing new logic families that will provide improvements in both gate delay times and speed-power products. Additionally, new semiconducting materials, such as gallium ansenide, that

have higher carrier mobility (hence higher speed) than silicon are already in the advanced stages of development. During the next decade, impressive data system performance improvements will occur as the advances in submicron processing techniques are combined with new device technologies to produce very large integrated circuitry that offers significant increases in complexity and performance over today's technology.

#### SPACE PROCESSING ELEMENTS

Space processing elements have traditionally been characterized by extremely rugged construction, relatively small size, low-power operation, high reliability, and high cost. In order to achieve the required reliability and performance, a considerable effort was normally expended on packaging design, efficient electrical design, analytical models (worst-case electrical, thermal, etc) and extensive quality controls. The design of many early spaceborne computers (with a few exceptions) did not seriously consider either software development or architectural compatibility with already existing machines.

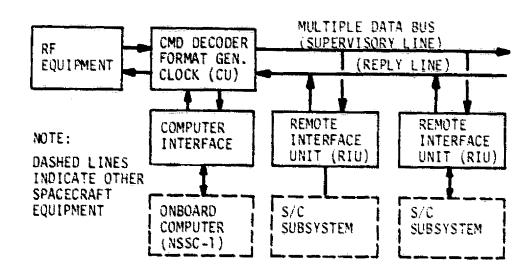

Developers of state-of-the-art spaceborne computers such as the NSSC II, which is currently being developed by IBM for MSFC, recognizes the importance of architectural compatibility and the rising cost of software; therefore, the NSSC II utilizes an IBM 360 architecture.

By 1985, commercial minicomputers with approximately the same complexity as the NSSC II will be available on one or two chips. The availability of such a great amount of computing power in such a small package will lead to greater application of imbedded processors and distributed processing within spacecraft subsystems. Because of the extremely small size of commercial minicomputers, there will be less difference between the physical configuration of a spaceborne computer and a commercial minicomputer and essentially the same machines may be used in both applications.

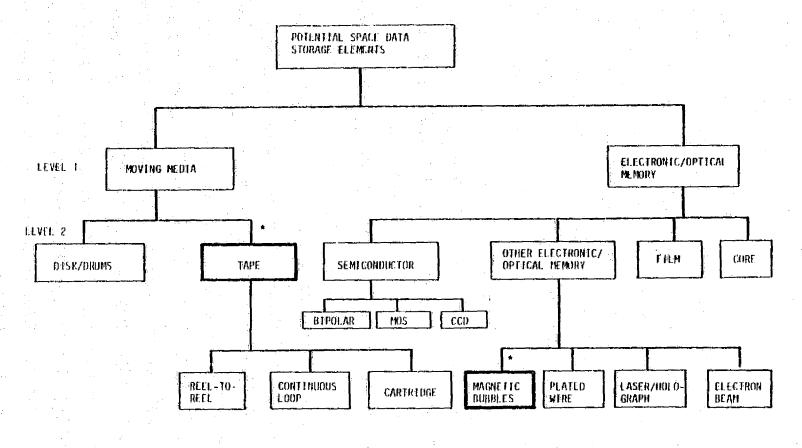

#### SPACE DATA STORAGE ELEMENTS

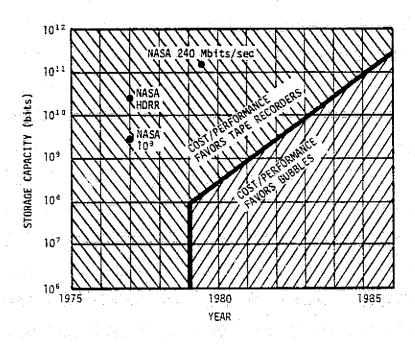

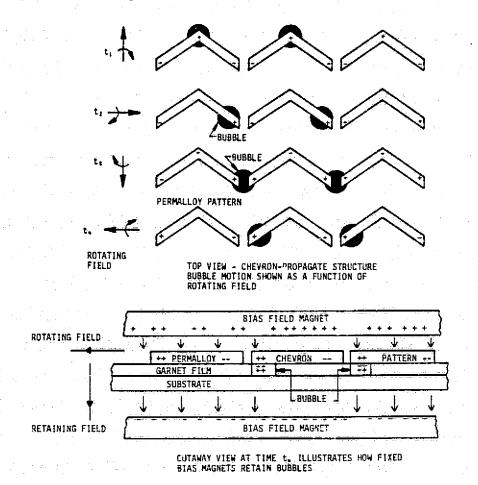

Space data storage has typically been performed with magnetic tape recorders that are limited in capacity, reliability, and lifetime. Although magnetic tape recorders will still be used extensively in space into the mid-1980's and possibly beyond, new technologies that are potentially more reliable are beginning to emerge. The most promising technology for replacing tape recorders across a broad front in space is magnetic bubbles.

NASA is currently developing a prototype 10°-bit bubble memory system. Although this system will not be competitive with existing magnetic tape recorders in terms of volume, weight, power, and storage capacity, it will provide for an early demonstration of flyable bubble memory recorder. Additionally, it will provide a mechanism for demonstrating the alleged higher reliability of bubble memory storage systems.

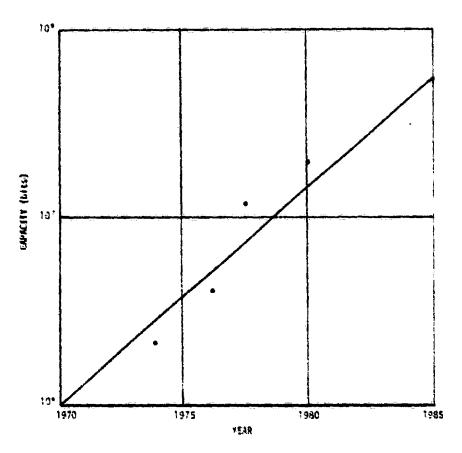

The potential for bubble memory spaceborne data recorders lies in the expected chip storage capacity increase from the currently available  $10^5$ -bit chips to  $10^8$ -bit chips by 1985. The larger-capacity bubble chips will make the performance of bubble memory systems competitive with tape data recorders for storage capacities of up to  $10^{10}$  bits by 1985.

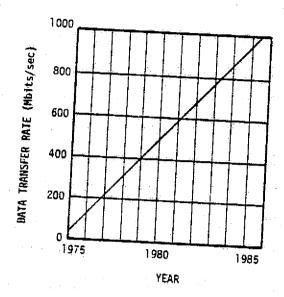

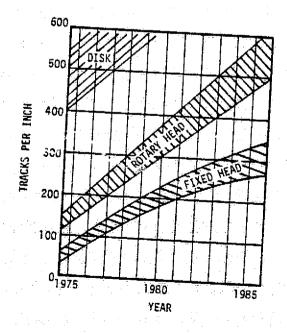

High density airborne digital tape recorders can be generally classified as rotary-head recorders and fixed-head recorders. The fixed-head recorders currently offer the highest data transfer rates. RCA is developing a 420-Mbit/sec fixed-head data recorder for GSFC that records 120 active data channels on a 2-in.-wide tape.

Authorities are predicting that the rotary-head tape recorders will be used extensively in future data systems that either require very high storage capacities or must interface with onboard digital computers that store and access data in blocks, rather than continuously as is currently done in most aerospace recorder systems.

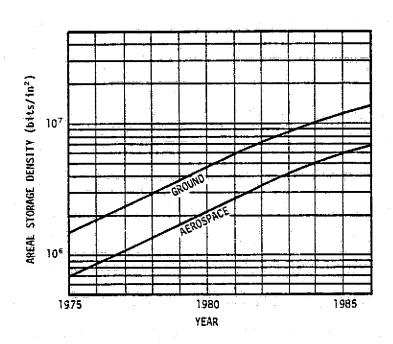

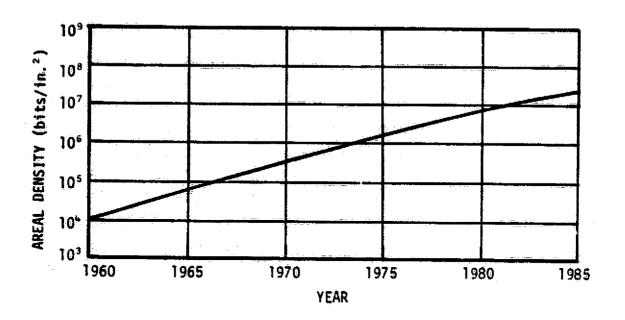

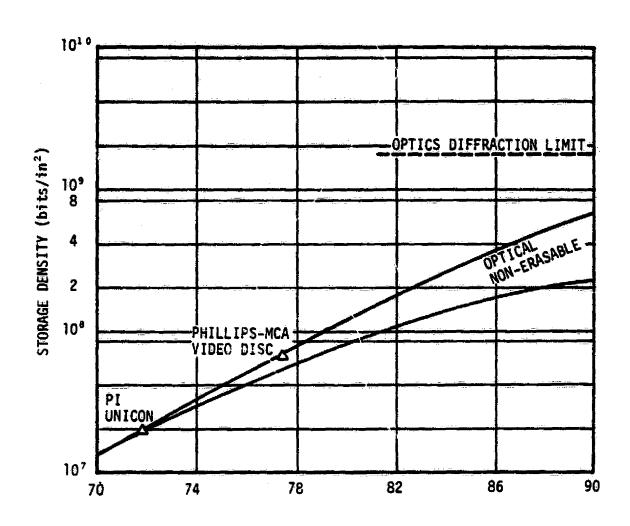

Tec! alongy projections for 1985 are for aerospace data recorders with storage densities of up to  $10^7$  bits/in<sup>2</sup> and data transfer rates of up to  $10^9$  bits/sec.

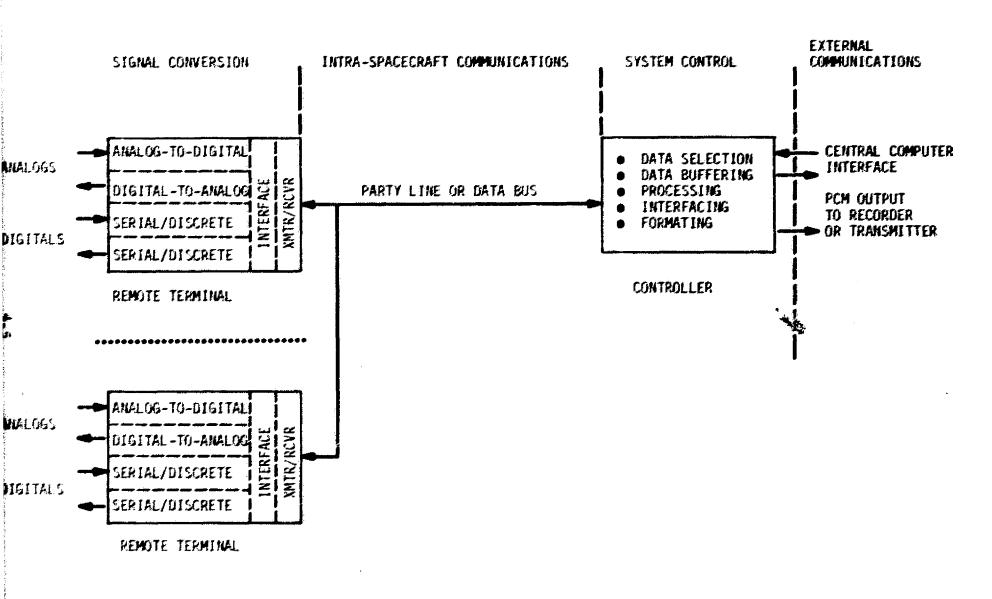

#### SPACE DATA HANDLING ELEMENTS

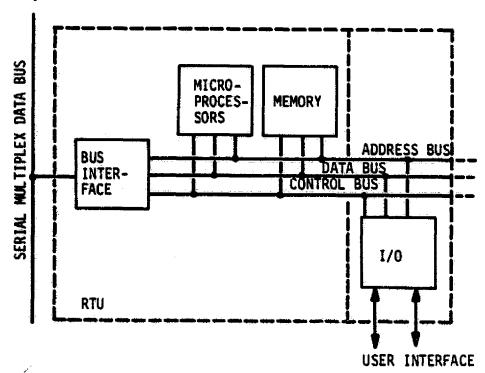

Future general-purpose data systems will provide increased flexibility, reliability, and data throughput capacity. Microcomputers will be incorporated into future remote terminal unit designs to provide remote programming and processing capabilities that will significantly increase the overall data system throughput capacity by eliminating much of the nonessential data bus traffic and reducing the central computer processing load. Space-qualified 64-Kbit RAM chips and 1-Mbit bubble memory chips should be available by 1980. These devices will make it feasible to package microcomputers with upwards of  $10^6$  bytes of memory by 1980 without increasing the current size of the remote unit. Improvements in analog and digital circuit integration levels will more than offset the additional size and power required for the remote unit processor and memory functions.

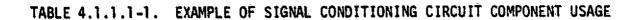

By 1980, low-cost, low-power, monolithic analog-to-digital converters and digital-to-analog converters should be available from a number of different sources.

Technology projections for 1985 that will impact the ultra-high data rate and high-speed digital data handling systems of the future include the following:

- Space-qualified GaAs MESFET logic with propagation delays of less than 100 psec and clock rates in excess of 5 GHz will be available.

- All monolithic analog-to-digital series-parallel converters will be available with a conversion speed of 10 nsec for 8 bits.

- Hybrid analog-to-digital parallel converters will be available with a conversion speed of 2 nsec for 8 bits.

- Short-channel MOS analog switches will be available with switching speeds less than 500 psec.

These developments will provide the technology neccessary to build data systems having analog sample rates of up to  $400~\mathrm{MHz}$  for 8-bit resolution and output PCM data rates of up to 5 GHz for a single output serial data stream. This technology will support the development of real-time imaging systems similar to the Thematic Mapper with resolutions of less than  $5~\mathrm{m}$ .

Projected power consumption per gate for the high-power 5-GHz GaAs MESFET logic is 10 mW per gate. At this power level, only medium-scale integration can be used. For applications that require logic speeds less than 1 GHz, low-power GaAs MESFET logic with power dissipations of only 0.3 mW per gate can be used to provide highly reliable LSI designs with integration levels in excess of 1,000 gates per chip.

These developments in high-speed, relatively low-power logic, coupled with the developments in bubble memories discussed in Section 3.2 and semiconductor memories discussed in Subsection 7.2.1, will make high-rate data handling much easier by 1985.

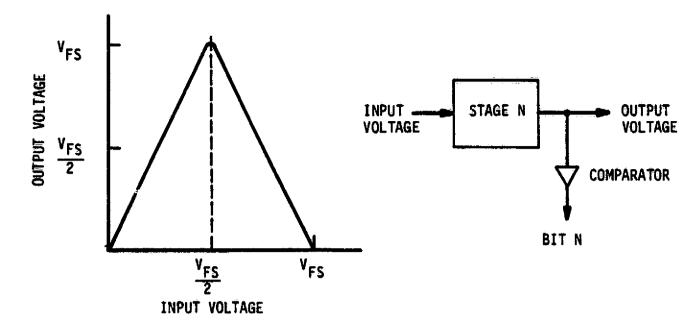

Another development that is likely to have a significant impact on data handling system designs by 1980 is the optical data bus. Both the Air Force and the Navy are actively pursuing the development of optical transmission lines in an operational airborne environment. Advantages claimed include transmitting higher serial data rates (up to 100 Mbits/sec), reduced weight, and less susceptibility to RFI/EMI/EMP.

#### SPACE-TO-GROUND COMMUNICATIONS ELEMENTS

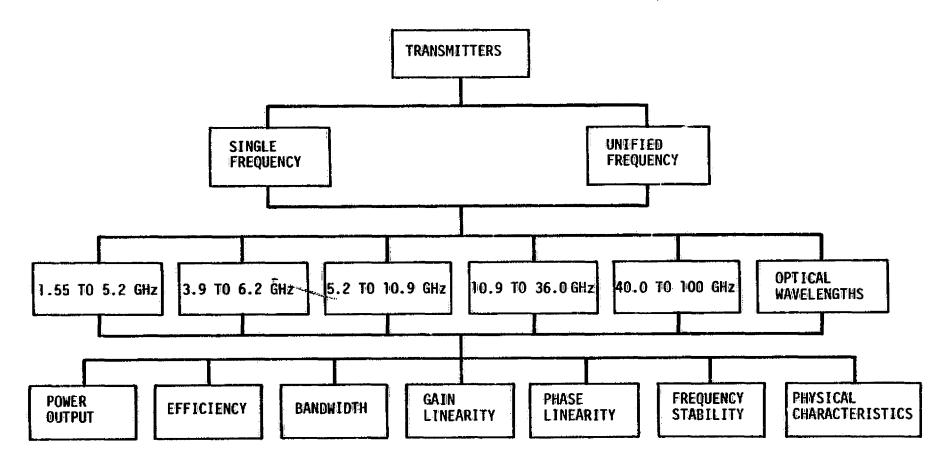

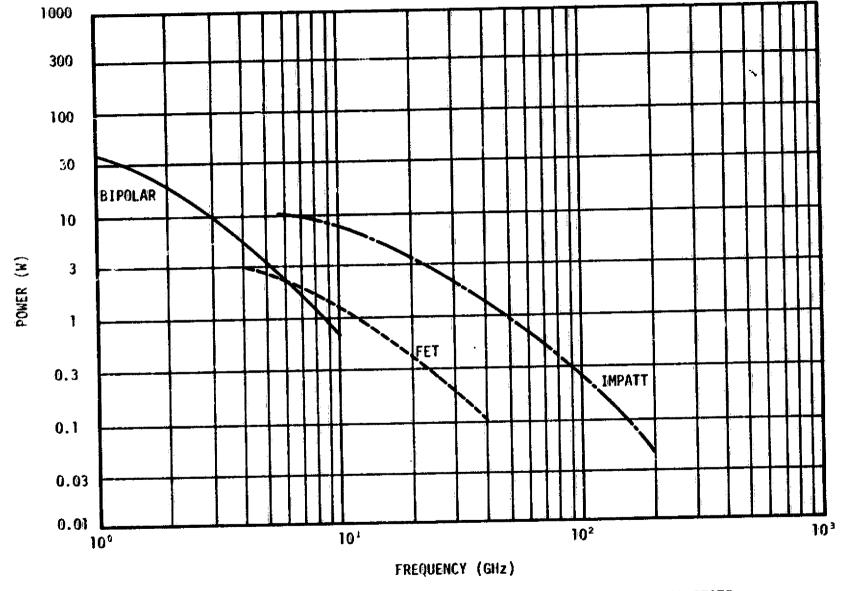

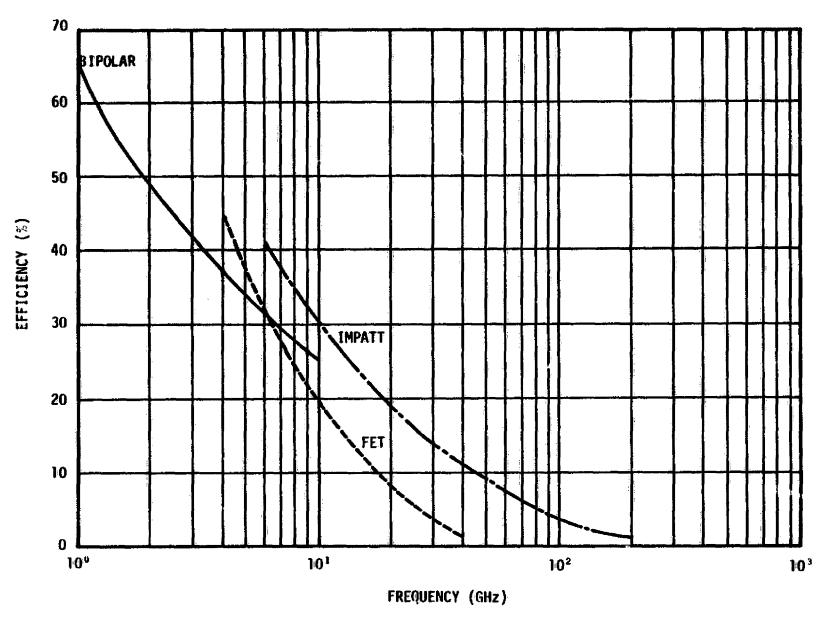

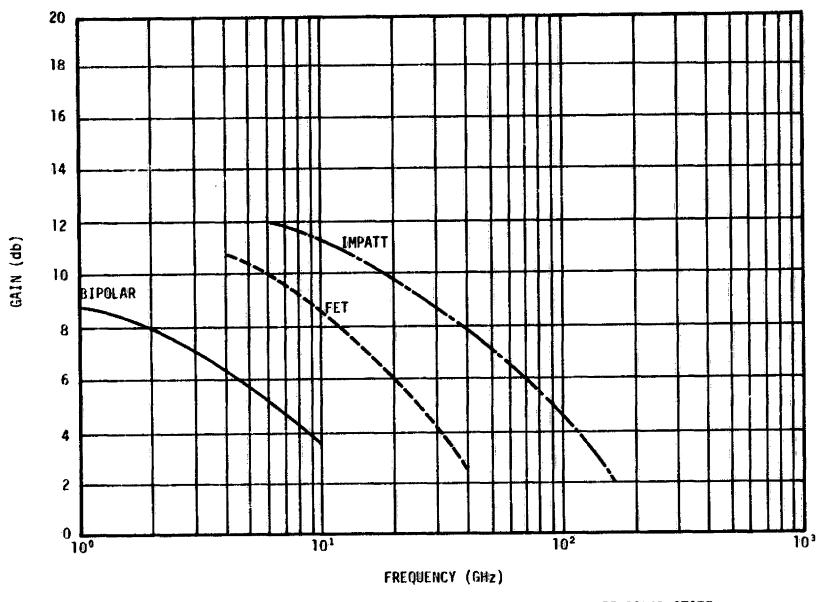

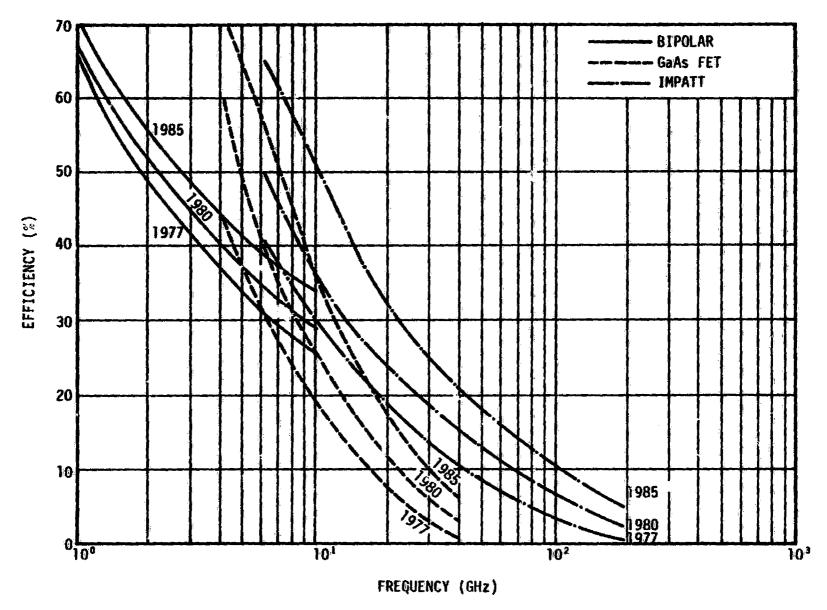

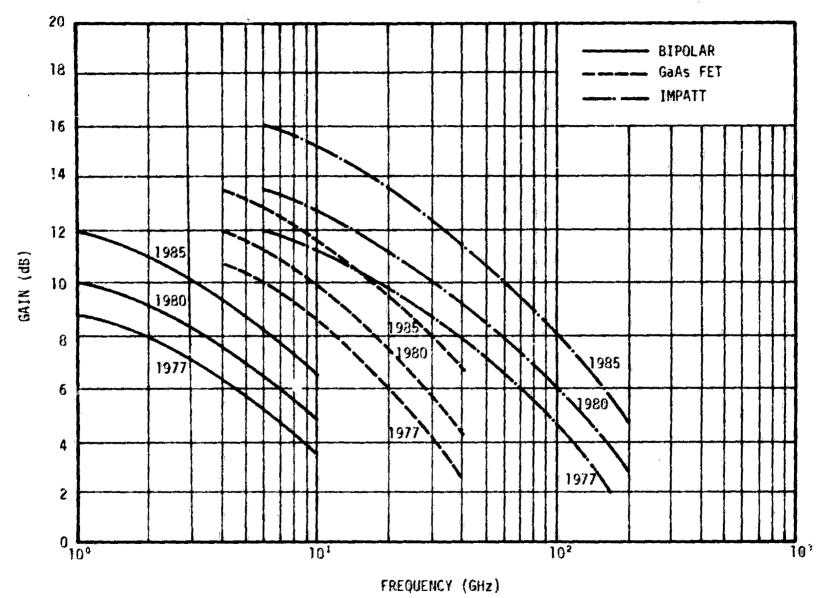

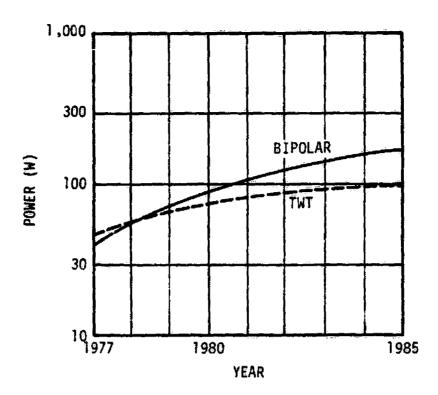

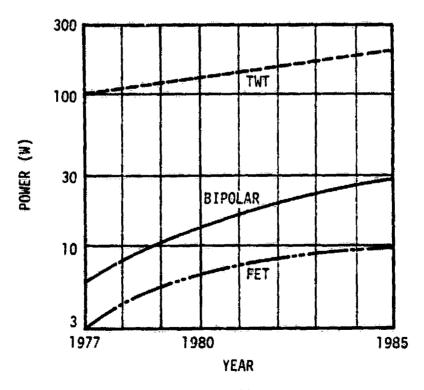

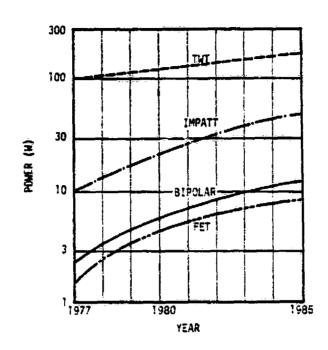

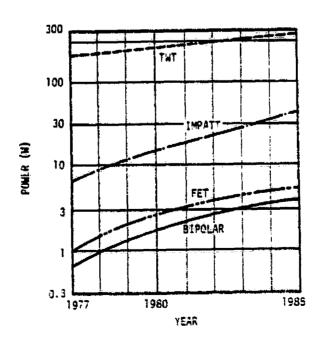

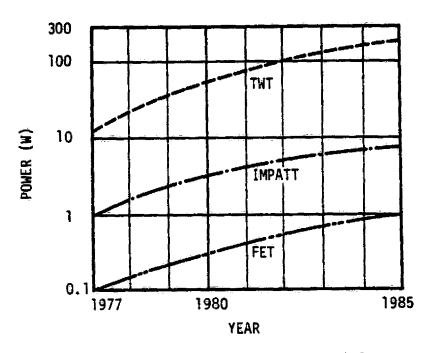

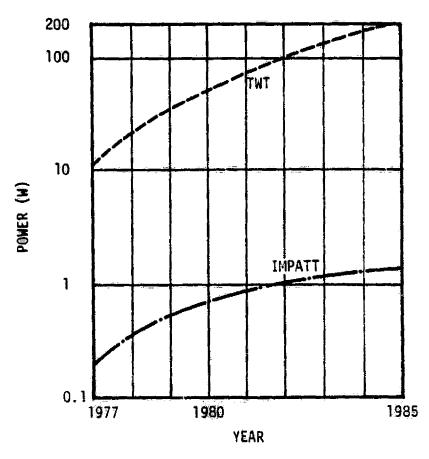

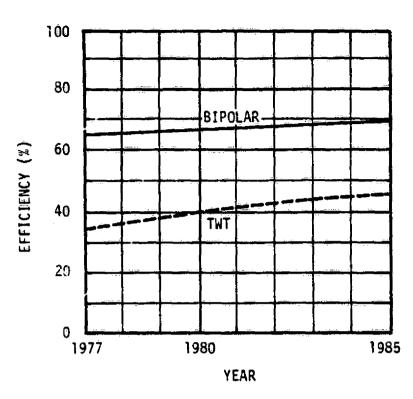

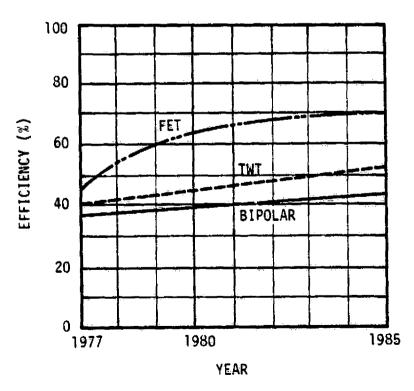

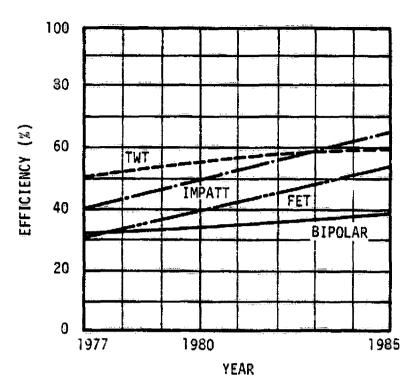

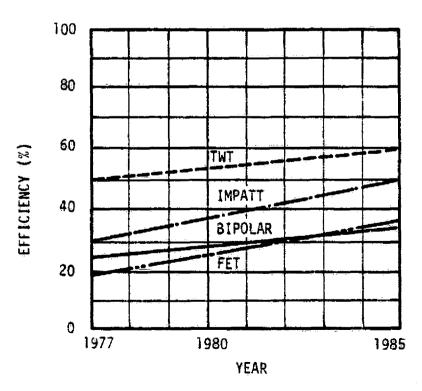

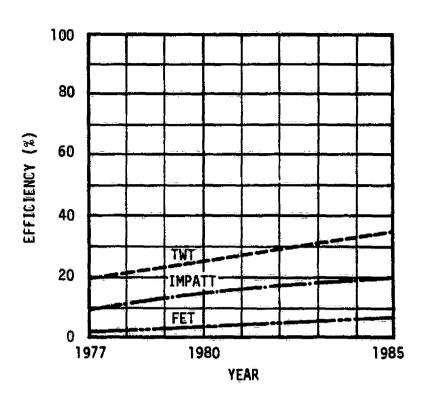

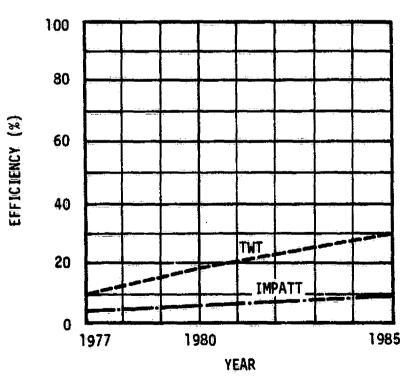

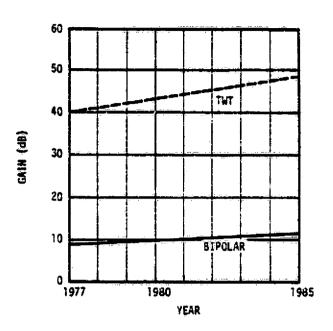

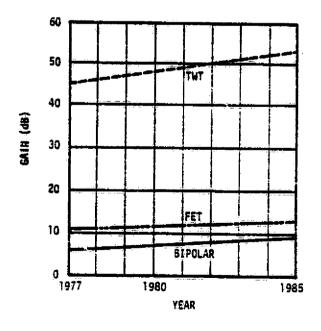

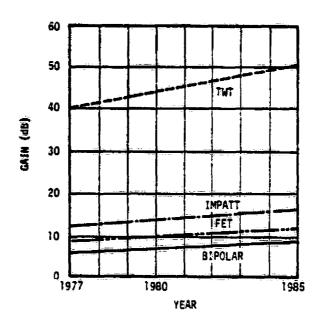

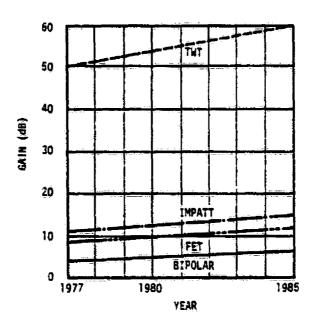

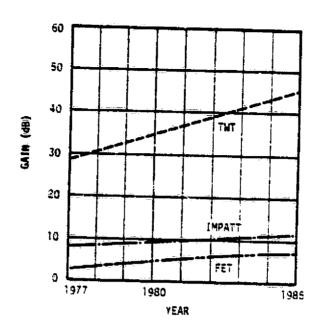

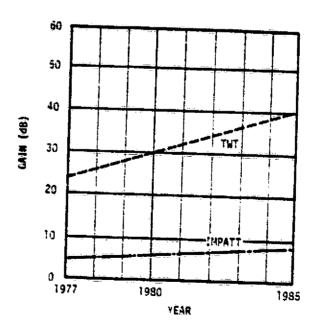

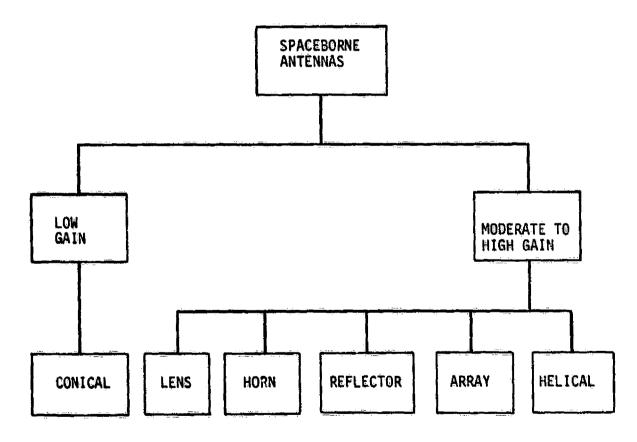

Both solid-state and tube-type power sources for space-to-ground communication systems are currently experiencing improvements in power output, efficiency, and size over a wide range of frequency bands, and the current trends are expected to continue through the 1980 to 1985 time period. Transmitters will be using a variety of devices for different frequency bands between now and 1985. Below 6 GHz, bipolar devices will be competing with TWTs for size, power, and efficiency. FETs should be equivalent to the IMPATTs of today in the 6- to 50-GHz band by the mid-1980's, whereas IMPATTs should improve in power and efficiency to provide approximately 1 to 2 W at 100 GHz. Efficiency in FETs should increase significantly by 1985, approaching 70% of the theoretical maximum. In spite of these advances, TWTs will continue to either equal or outperform solid-state devices in terms of efficiency, gain, and power output in most frequency bands.

The major areas of research in communications are going on at frequencies above 30 GHz, including the optical band. Improvements in these frequency bands are likely to be reflected in the lower frequency bands also.

Reflector-type antennas will be prevalent in all bands through 1985. These will be folding types below 10 GHz, and will be deployable at all frequencies. Prime focus and offset reflectors with cluster array feeds will be common. Phased-array antenna systems will be capable of competing with reflector types in performance, weight, and volume. However, they will be more expensive by a factor of 1.5 to 2. Phase arrays will handle much higher power without experiencing multipactor. Array feeds of low-loss air-stripline or microstrip networks using high-permittivity substrates will allow designs with sidelobes that are down more than 30 dB.

The use of the TDRSS for a civilian space data relay satellite will continue through 1990. An upgrading of the system would be technically feasible during the mid-1980's, but current NASA planning does not incorporate any design changes. The use of relay satellites employing laser technology will be feasible by 1985, with such systems capable of data rates in excess of 1 Gbit/sec.

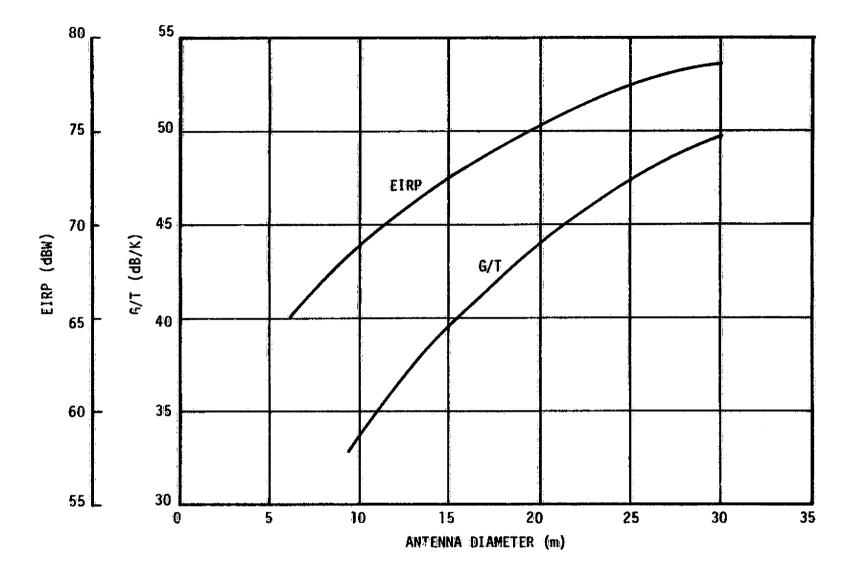

Future developments in ground station antennas will be related to the continued increase in frequency of the satellite communication systems. Ground station antennas at these higher frequencies will use the same design techniques that have been developed for the lower bands. The ground antennas at the 4- to 6-GHz and 11- to 14-GHz bands will employ frequency reuse techniques that will require stricter pointing tolerances and lower sidelobe levels.

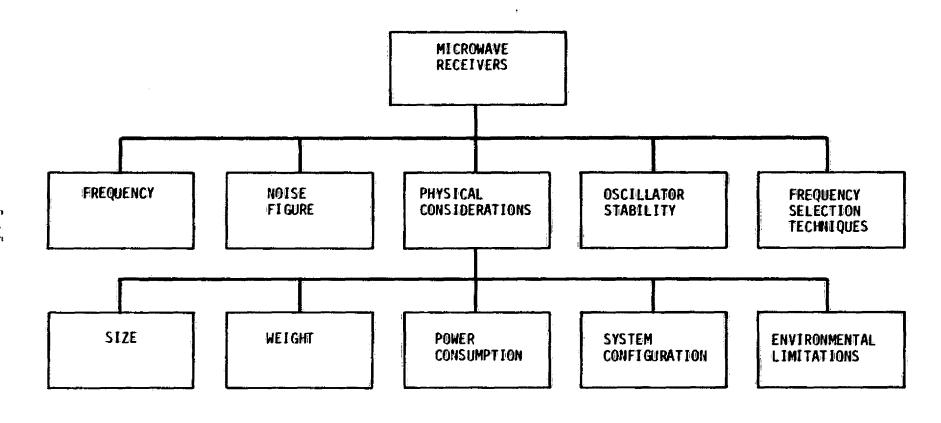

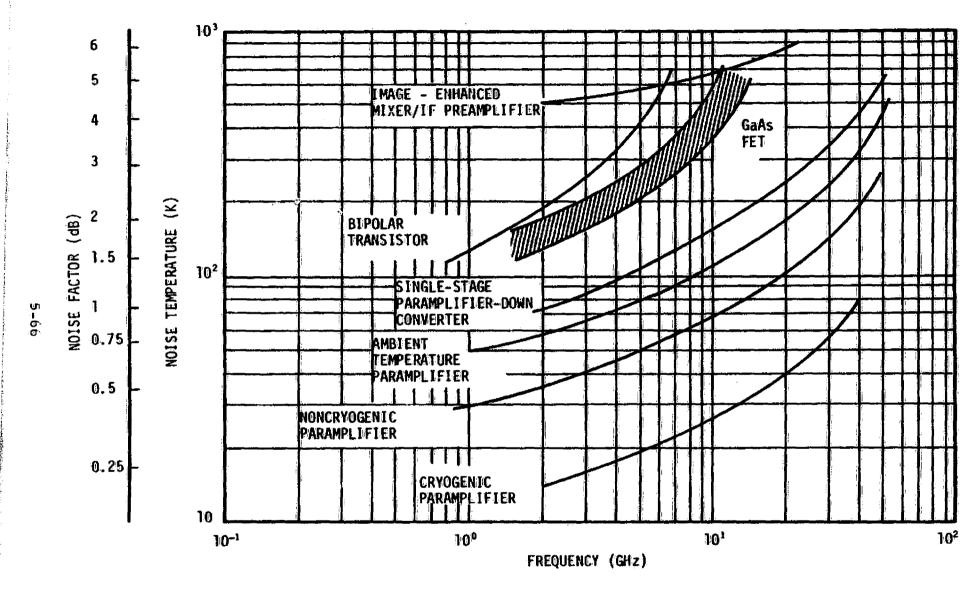

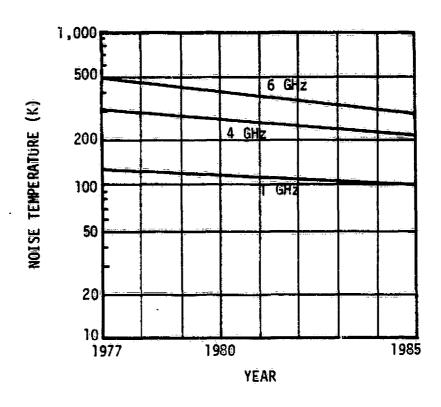

As a result of developments in super components, receiver sizes in all frequency bands will decrease to somewhere in the range of 25 to 50% of their present size by 1985, while performance will improve. Power consumption will continue to decrease to approximately 50% of the present consumption by 1985, especially for the higher-frequency receivers.

Solid-state devices will be capable of operating at higher frequencies with sufficiently low noise figures and high enough gains to replace TWTs in most systems.

The analog portion of the receiver of the future will shrink as more and more digital circuitry is used. The trend is to have digital circuitry from the conversion to baseband to the output of the receiver. When short (<512-bit) PN Codes are used, it is likely that CCD transversal filters will be employed.

Modulation schemes for data transmission through 1985 will be for either low-data-rate narrowband systems or high-data-rate wideband systems. The high-rate systems will use M-ary PN schemes for frequencies below the optical band. Data rates for both the optical and RF bands will range up to 1-Gbit/sec for terrestrial systems and up to 300-Mbits/sec for spaceborne systems.

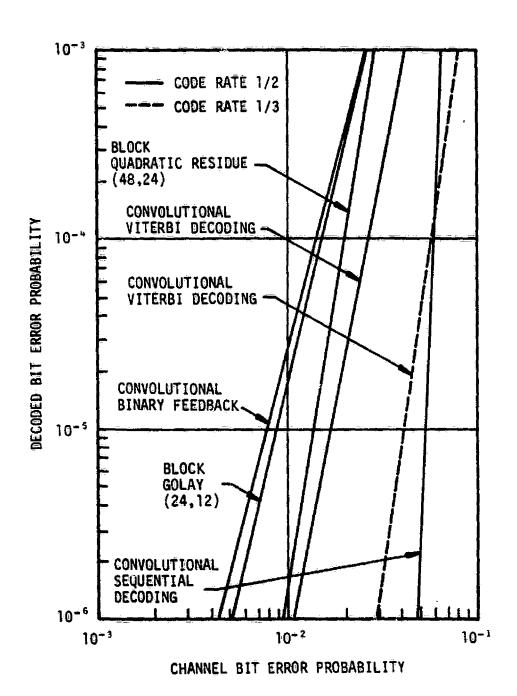

Error correction coding will exhibit a trend toward convolutional codes for error correction and concatenated codes for multipurpose applications and extremely high-quality data. Future systems that use higher frequencies will be more susceptible to fading and atmospheric disturbances and will not necessarily employ the same error correction techniques used at the lower frequencies.

#### PREPROCESSING ELEMENTS

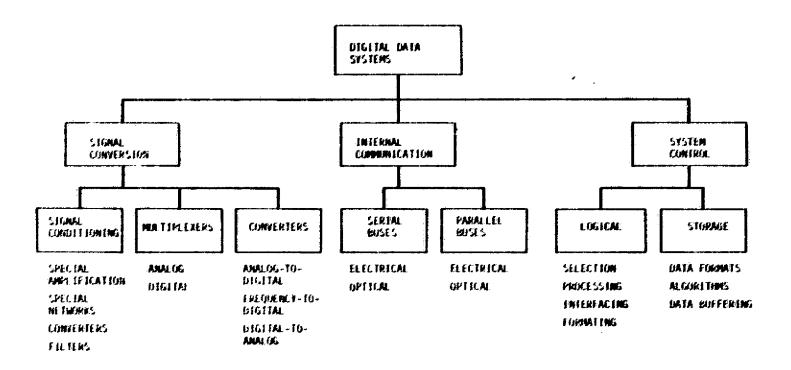

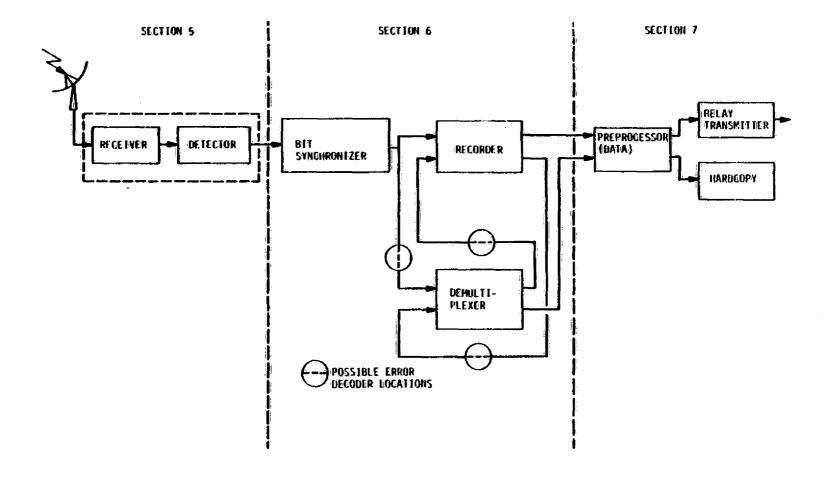

Preprocessing elements include those hardware and software elements that take the outputs from the ground communications system (ground station receivers) and perform the functions necessary to input the data into the ground processing system. Functions performed by the preprocessing elements include data detection and synchronization, demultiplexing, reformatting, data buffering, decoding, error correction, and calibration.

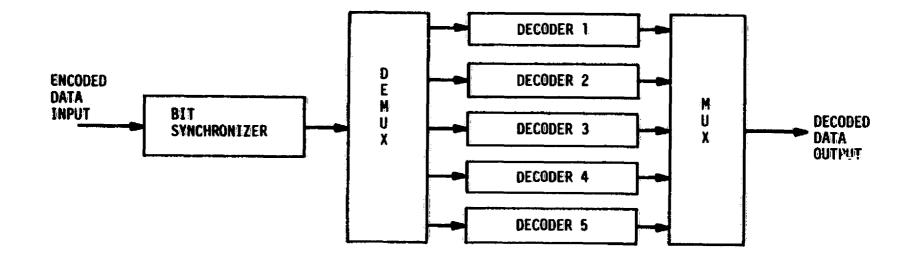

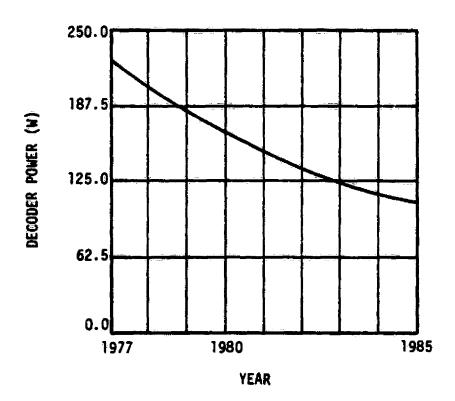

The TDRSS ground station, currently under development, represents the state of the art in operational ground stations. When operational in 1980, the TDRSS ground station will handle data rates to 300 Mbits/sec and will employ a Viterbi decoder system that is capable of data rates to 50 Mbits/sec. Development hardware for future system applications is currently being tested in the laboratory with bit synchronizers that operate at 500 Mbits/sec and demultiplexers capable of handling rates to 1 Gbits/sec.

In general, the trends in preprocessing elements are toward higher data rates and more real-time processing and data handling, including real-time data reformatting, retransmission, and distribution.

Tape recorders currently used for ground data storage are mostly the fixed-head, high-density digital instrumentation type. Trends in high-density digital instrumentation recorders are toward wider tapes, more heads per inch of tape, and higher data rates. Several companies are currently developing fixed-head instrumentation recorders with data recording rates in excess of 200 Mbits/sec.

The use of rotary-head type data recorders will increase because of the higher data packing densities and faster start-stop times that can be achieved with the rotary-head systems.

Flexible high-rate instrumentation recorders should be available by 1985 that record and play back at data rates up to 1 Gbits/sec with data storage densities of  $10^7$  bits/in<sup>2</sup>.

#### GROUND PROCESSING ELEMENTS

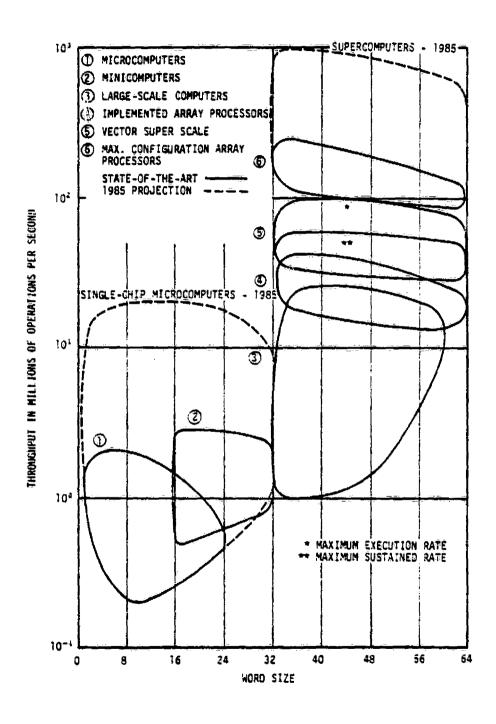

Data processing elements covered in this report include micro-computers, minicomputers, large-scale computers, super-scale computers, bipolar memory systems, MOS memory systems, CCD memory systems, electron-beam memory systems, core memory, disks, tapes, and firmware. Software is discussed in Sections 8 and 11.

The market size and capabilities of microcomputers will continue to increase during the 1980 to 1985 timeframe. By providing very inexpensive low-end processing, microcomputers will find their way into many new designs, performing functions that could not be done economically with

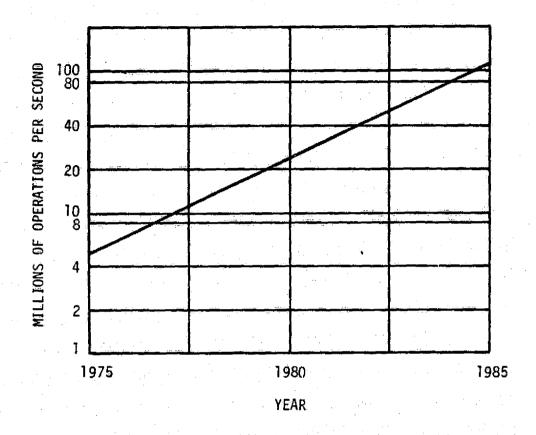

programming (or done at all) before. The most powerful microcomputers of 1980 and 1985, capable of achieving instruction rates of 5 and 20 million instructions per second (MIPS), respectively, will expand the market for these computers on the high end. Software for this class of computers will become somewhat more sophisticated, but, with rare exception, will not rival that of larger machines.

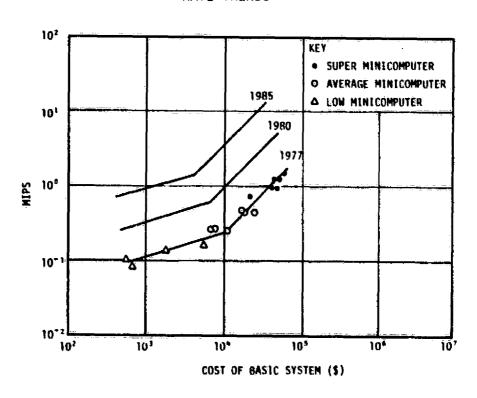

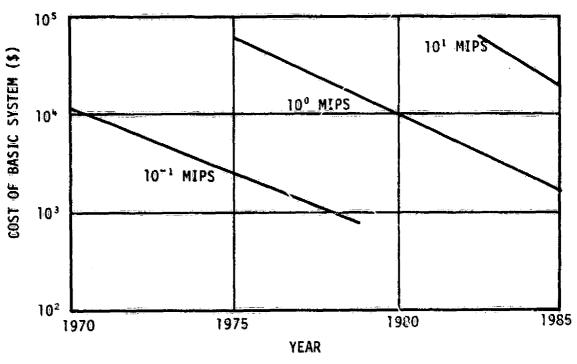

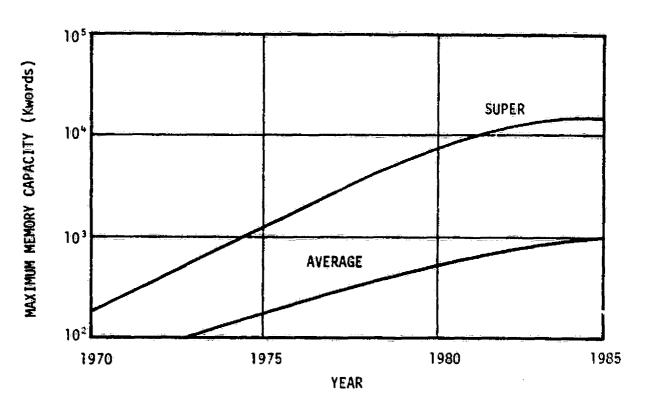

The rapid growth in the capabilities of minicomputers experienced during the past decade will continue during the 1980 to 1985 timeframe. By taking advantage of the predicted improvements in LSI logic circuits and semiconductor memories, the most powerful minicomputers of 1980 and 1985 should be capable of 12 and 60 MIPS, respectively, at costs in the vicinity of \$40,000. Mean time between failure for these systems is expected to approach 10,000 hr, and software offered with the machines is going to become much more sophisticated, rivaling that of medium-scale computers of today.

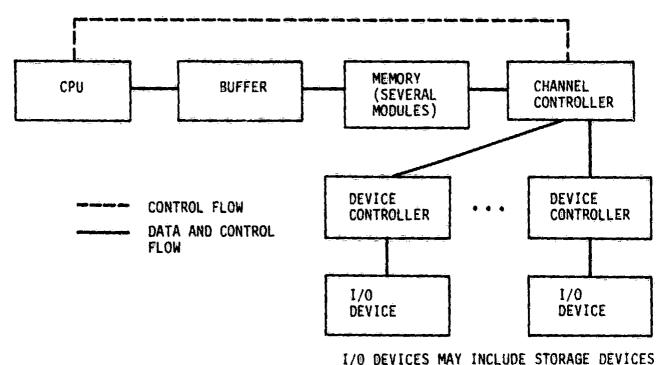

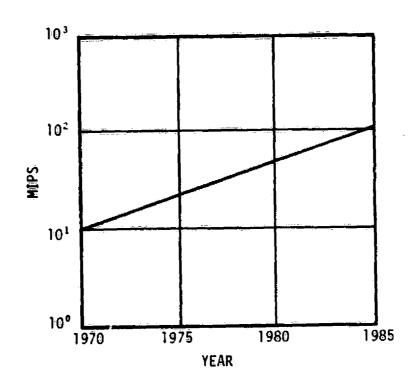

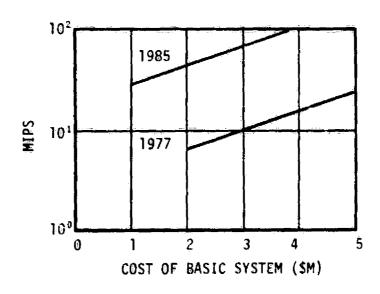

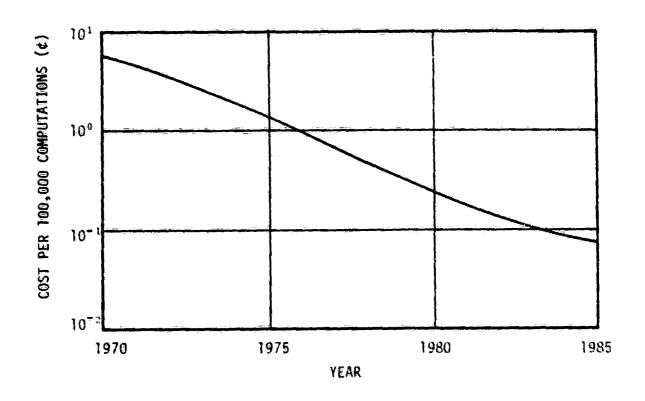

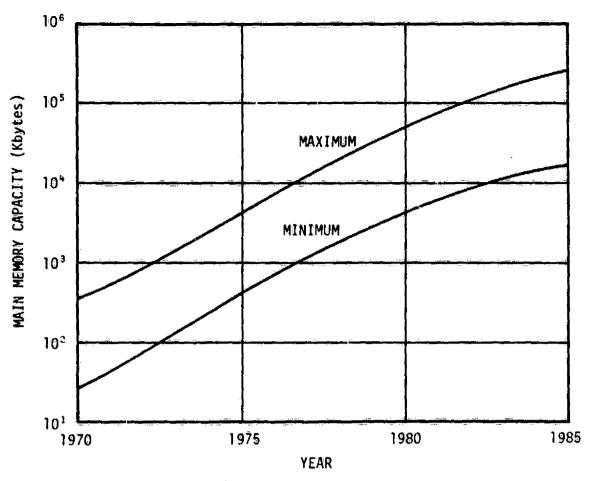

The historic 12 to 15% annual price/performance improvement in large-scale computers will continue during the 1980 to 1985 timeframe as a result of achievements in logic circuits, main memories, and mass storage. The desire for ever greater speed will force the continued growth of multilevel hierarchical storage systems. In particular, the use of buffer memories will expand. More emphasis will be placed on system reliability, with improvements achieved through the use of error-correcting codes in memory systems, fault-tolerant design, and hardware redundancy. The most powerful large-scale computers of 1980 will be capable of 45 MIPS, with increases to 100 MIPS by 1985. Expanded use of distributed data processing systems will occur in conjunction with, rather than instead of, the growth of large-scale computers. Many of the large-scale computers of the next decade will be geared to large data base management operations.

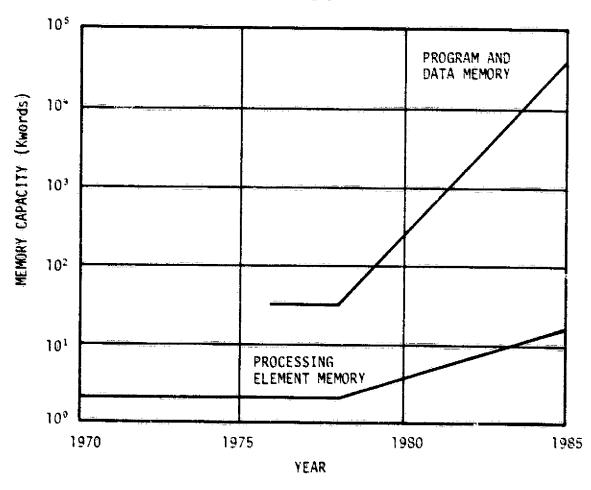

Super-scale computers of the next decade will continue to have a very limited market, addressing problems that throughput large amounts of data and in which computations are highly parallel in nature. Their characteristics will continue to improve, with emphasis placed on larger memories and faster execution times since the quality of the solution to the problems addressed depends on the number of data points considered and on the number of computations performed. Both vector and parallel designs will be used to build systems.

Vector super-scale computers are expected to achieve 100 to 150 MTPS by the early 1980's, with increases to 200 to 300 MTPS by the mid-1980's. Parallel super-scale computers will be capable of achieving instruction rates as high as 1,000 MTPS by 1985. One limiting factor in achieving these rates is the extent to which the parallel or vector capabilities are utilized, which depends primarily on software advances. Since software development is slower than hard to development, it will be the limiting factors, preventing the more optimistic projections made by some experts from being achieved. Only very limited software support is available on most state-of-the-art super-scale computers. Major advances in software support are needed so that systems can be more fully utilized. For this reason, emphasis will be placed on software development during the next decade.

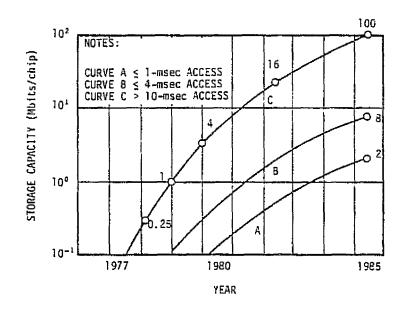

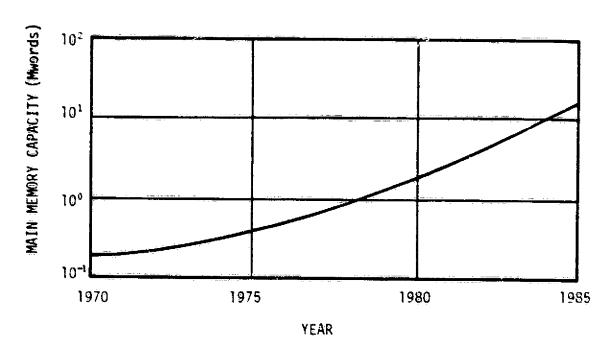

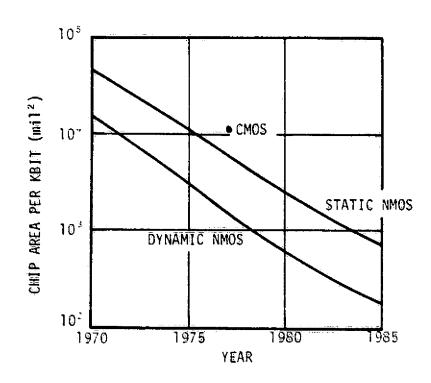

MOS technology, particularly NMOS, will continue to be the dominant processor memory technology during the 1980 to 1985 timeframe. Major improvements will occur in all performance categories of NMOS and CMOS memory systems during this time period. By 1980, chip densities will quadruple, and access and cycle times will improve by 40%. By 1985, chip densities will increase by an additional factor of 16, and access and cycle times will improve by 60%.

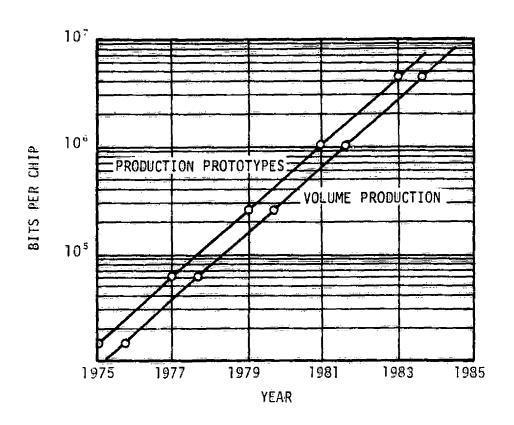

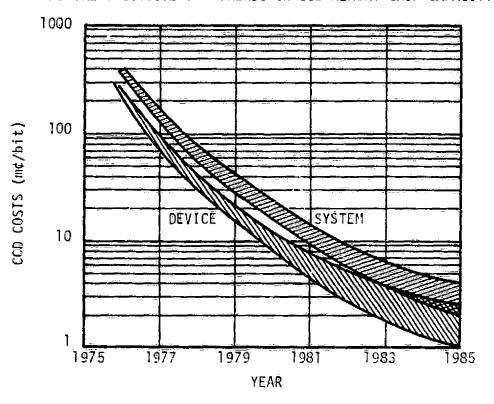

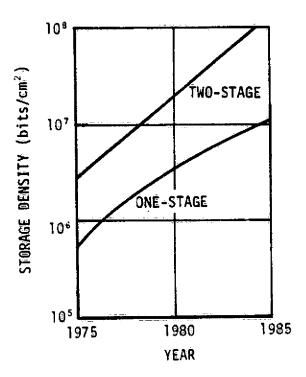

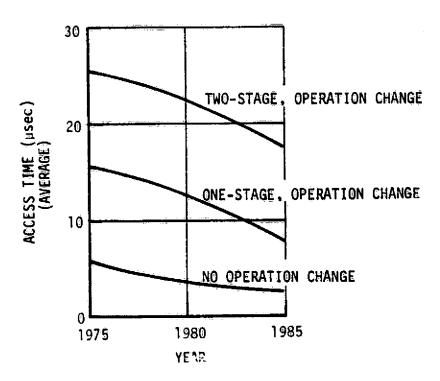

Charge Coupled Device (CCD) memories offer the greatest densities available in semiconductor read-write memories; however, CCD memories are generally organized as serial rather than random-access devices and thus have relatively long access times. This position should be maintained or improved on in the 1980 to 1985 timeframe, with devices storing 256 Kbits and 4 Mbits being available in 1980 and 1985, respectively.

Electron beam memories offer great potential in terms of performance, cost per bit, and total system capacity. However, for major advances to occur, the following problem areas must be overcome:

- Electron optics must be upgraded to accomplish submicron beam diameters in production.

- Cathode development must occur to accomplish increased beam brightness with decreased beam size.

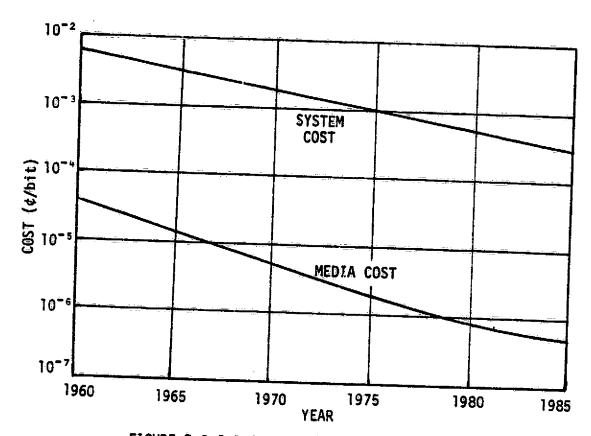

If sufficient progress is made in these areas, electron beam memories should be commercially available in 1980 with capacities to  $2\times10^9$  bits for two-stage deflection units with access times of 3.3 µsec (no operation changes involved) and costs on the order of 0.01 to 0.02 c/bit. By 1985, similar units should have capacities to  $8\times10^9$  bits, with access times of 2.5 µsec and costs of 0.001 to 0.005 c/bit.

Because of the rapid advances being made in semiconductor memory technology and because of the limited research currently going into electron-beam memory technology, electron-beam technology may never reach its projected potential as a viable candidate to fill the memory access time gap between semiconductor and moving magnetic media.

Fixed-head disk storage technology is still evolving and viable although moving-head disks (see below) are evolving faster. By 1985, areal density, spindle capacity, and system capacity will improve 150%, and cost per bit will improve by 30% (drive) to 60% (system).

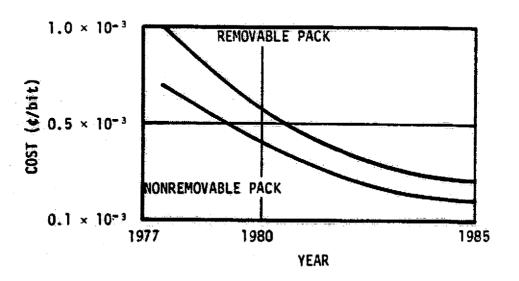

Moving-head disk storage technology is also still evolving and viable. By 1980, spindle capacities, maximum system capacities, and cost per bit will improve by 50%, and transfer rates will improve by 25% over current values. By 1985, spindle capacities and maximum system capacities will improve by 150%, cost per bit will improve by 80%, and transfer rates will improve by 275% over current values. However, access time will not experience major advances. Fixed-disk packs will become common once again to achieve the tighter mechanical tolerances needed to accomplish higher densities at the least cost.

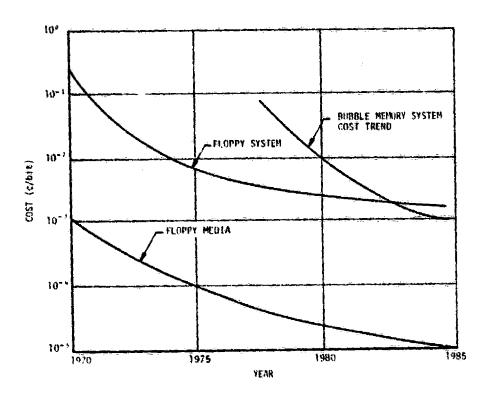

Floppy disks are currently used in low-cost key entry and low storage capacity applications. Trends in floppy disk technology are toward increasing the storage capacity and transfer rates by increasing the track and in-track densities, improving reliability by using better media and encoding, and lower power consumption. By 1985, capacity should improve by 300%, transfer rates by 75%, and power consumption and reliability (MTBF) by about 20%.

Cartridge disks are gap fillers between floppy disks and full-sized disks. Some trends in cartridge disk technology are toward more cartridges per drive, more disks per cartridge, and higher areal density. These will cause the storage capacity per drive (and cartridge) as well as the transfer rate to increase and cost per bit to decrease. By 1985, drive capacity should increase by 100%, system cost should improve by 50%, and transfer rates should improve by 35%.

Half-inch reel-to-reel tape, in 7- and 9-track formats, is the major medium used for storage and interchange of digital data throughout the world. Major trends in half-inch tape are toward higher in-track density, higher transfer rates and capacities, and lower cost per bit. By 1985, these measures will have improved 100% for both low-cost and high-performance tape drives, with two exceptions. Cost per bit for low-cost half-inch tape drives will have improved only 50%, while transfer rates for the same class will improve 400%.

Cassette/cartridge tapes are used in data entry terminal and small business systems. Trends include increasing tape speed and more tracks to reduce access time. By 1985, these characteristics will have improved around 100%.

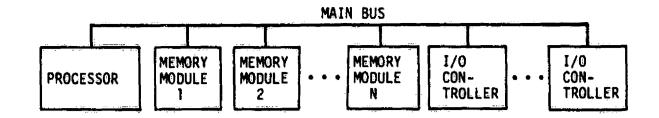

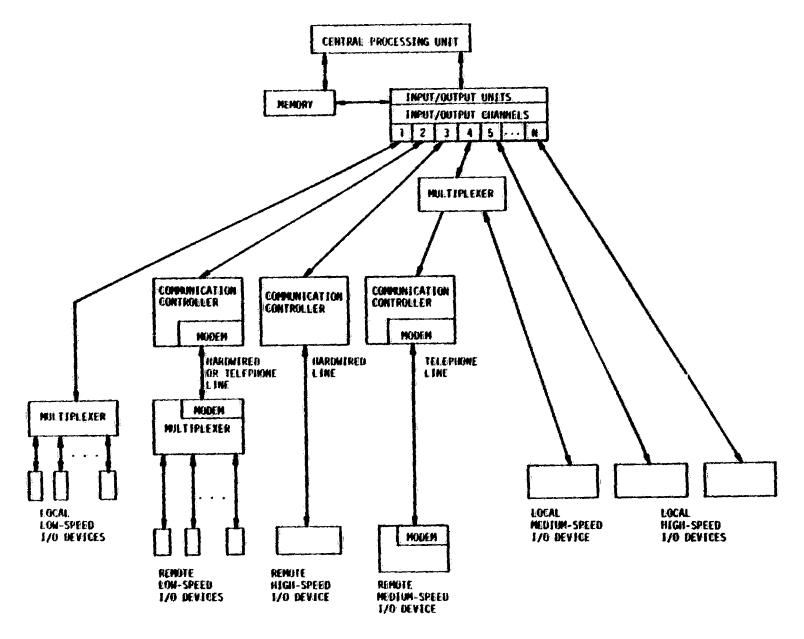

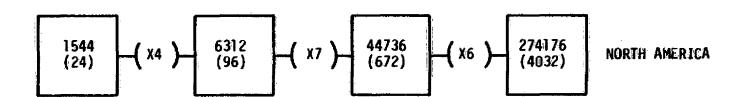

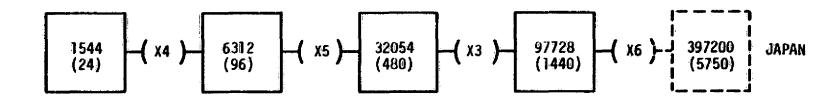

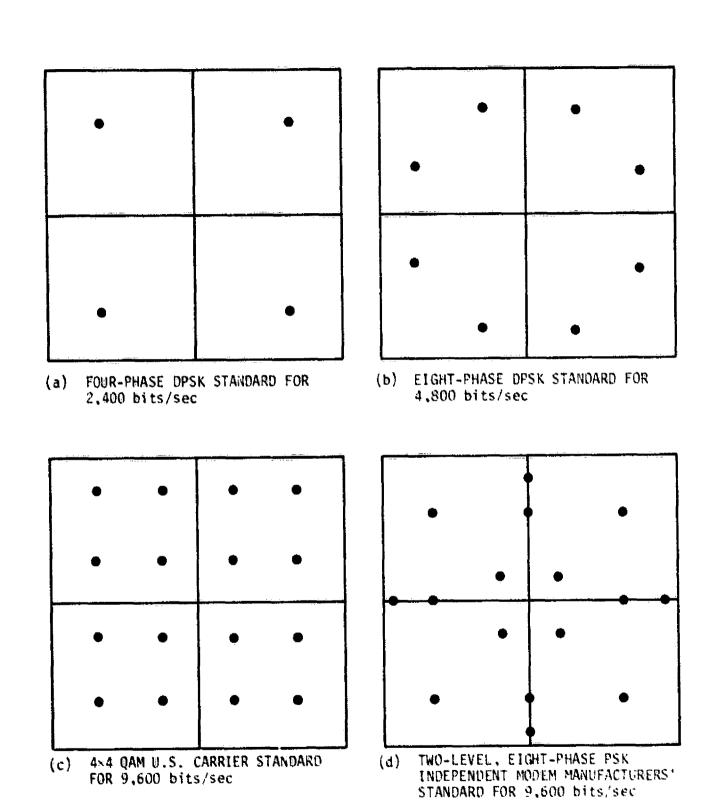

Trends in data processing communications elements are toward use of single microelectronic devices to do all, or important portions of, various communications tasks. This reduces the power consumption (where lower levels of integration were used before) and/or frees the main processor element for other work (where the processor did the communications task before). By 1985, fairly complex byte-oriented I/O channels will be implemented on one small printed circuit board with the main tasks being done by less than 10 integrated circuits. Modems capable of 9,600-baud transmission/reception will be built in the same way, as will other important communications controllers. Multiplexers/demu?tiplexers with Gbit/sec data rates will also be available.

Read-only memories, particularly MOS and bipolar ROMs and MOS PROMs, are following the same trends as read-write memories. Major improvements will occur in all performance and capacity categories, though ROMs will probably be speed-optimized rather than power- or capacity-optimized. By 1985, chip densities will improve by a factor of 16, access and cycle times will improve by 75%.

#### DATA BASE SYSTEMS ELEMENTS

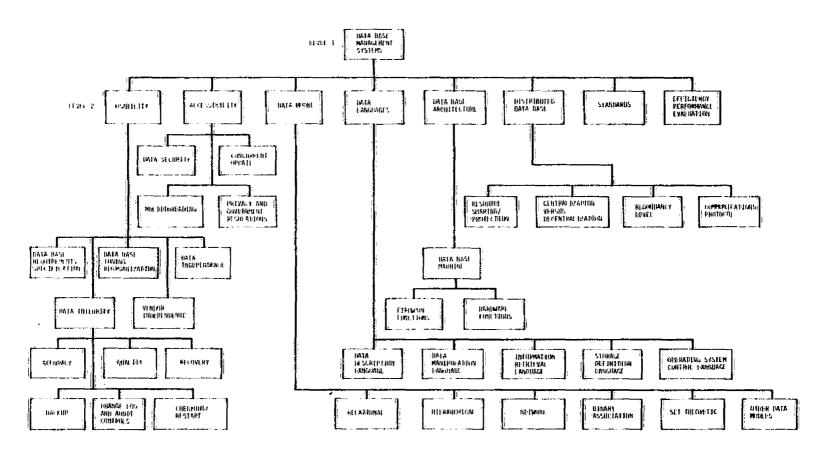

Data Base Management System (DBMS) software and/or techniques are receiving wide attention for managing the large data bases of the future. Some of the key issues associated with DBMSs are data independence (loosely defined as the immunity of applications programs to the data base structure), data base security, data models, and data base machines.

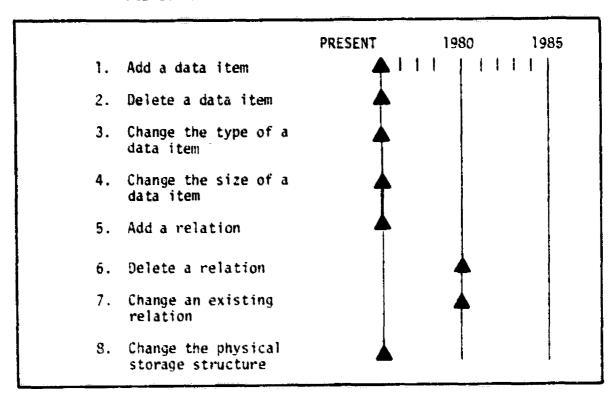

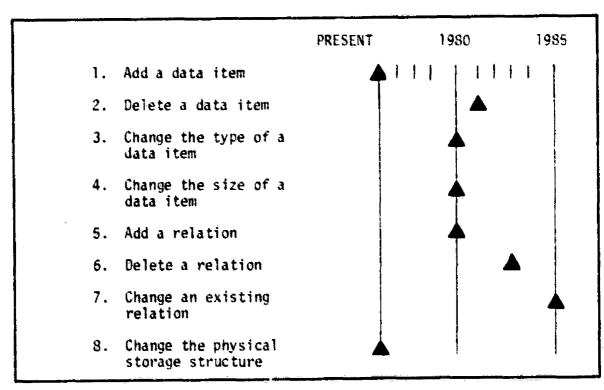

Data independence is gradually becoming a reality with certain limitations. It is expected that existing applications programs will essentially be immune to data item changes, as well as to changes that add a relationship, by no later than 1982. At the same time, changing relationships will still be a problem under many circumstances for the foreseeable future.

Present DBMSs provide security at the data base and file level. Projections call for security at the record level to be widely available by 1980, security at the data aggregate level to be standard by 1983, and the individual data item to be protected by 1984. These features will be implemented primarily in software prior to the mid-1980's, when such features will be available in hardware, probably as an option.

Data models are receiving the attention of a number of software and hardware vendors. Current DBMS software is primarily oriented toward hierarchical models. The current trend is away from hierarchical data models toward relational and network models. Although there is very high interest in relational models, the network model is expected to be the primary data model available and in use through 1985. In this respect, a high-level language capable of translating a data base from a hierarchical model to a network model is expected to be available by 1983.

Many authorities are of the opinion that the major mainframe manufacturers will orient their next generation of computers toward data base management, and thus create the so-called data base machine. Such a machine will exhibit a hierarchical memory structure, sophisticated data clustering capabilities, and a full complement of subsidiary DMBS processors capable of performing functions such as searching, sorting, security checking, etc. Projections are that a machine with capabilities such as these is expected to be available by 1982.

#### INFORMATION DISTRIBUTION ELEMENTS

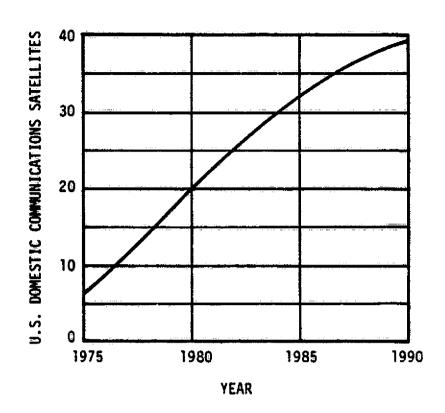

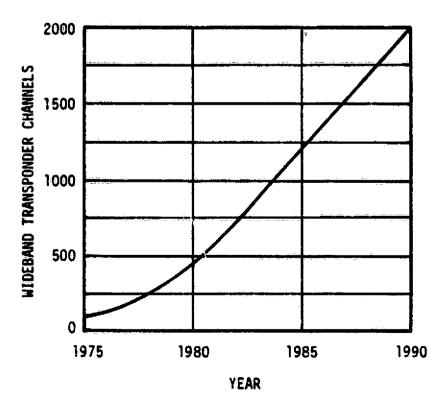

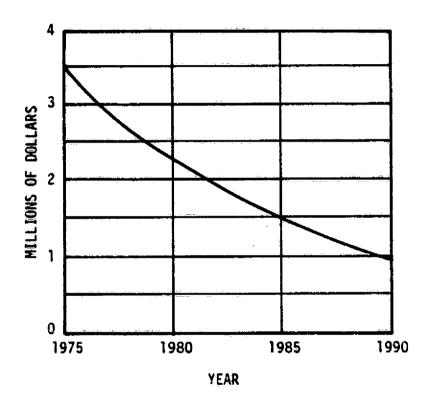

Terrestrial networks will continue to provide the dominant method of interconnection for data communications in the early to mid-1980's, although long-haul links will tend to use more and more satellite channels. The average user, however, will interface to the satellite via a telephone line in lieu of having a satellite terminal. At the same time, the use of small satellite terminals, particularly for reception of wideband data, will grow at a rapid rate.

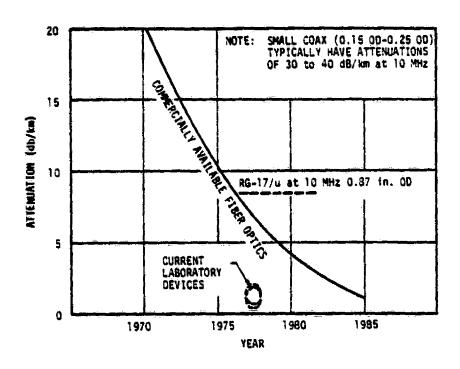

Terrestrial networks will still be predominantly analog, and thus require modems, into the mid-1980's, with a continued strong trend toward an all-digital network. By 1985, the major long-haul networks will probably be digital, with a continued dominance of analog circuits to subscribers. Optical fibers will be used extensively in future networks.

Data rates over voice-grade lines are expected to increase to 9,600 bits/sec on multi-point lines, including switched voice-grade lines, and to approach 14 to 15 Kbits/sec on point-to-point lines. The improvements will be primarily the result of improvements in software techniques and modem hardware. However, the use of digital links between switches will also play an important role in increasing the data rates.

Packet-switched networks will continue to increase and will play a major role in computer communications of the future. Small satellite terminals will see increased use (particularly receiving terminals) and will likely prove to be feasible for distribution of wideband NASA data that require fast turnaround.

#### INFORMATION PRESENTATION ELEMENTS

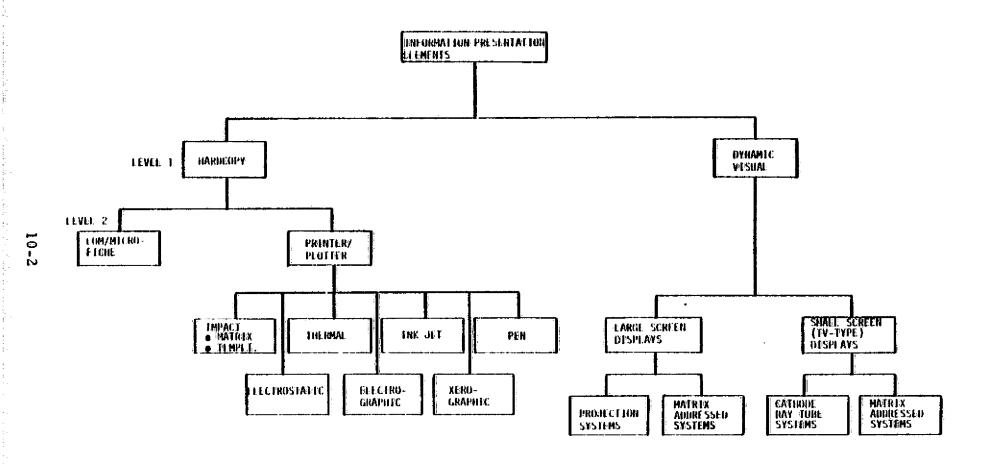

Information presentation elements include both the dynamic or real-time systems (terminals, graphic display systems, and image presentation systems) and hardcopy systems (CON, printer/plotters, etc.) for presenting data in a viewable form. Advances in capability in all areas of information presentation will result from research in the specific technology areas as well as research in related areas of data processing and memory systems.

The capability, flexibility, and throughput of all types of information presentation systems will increase as the individual devices become more intelligent and thus more independent of the host processor. Flexibility of both dynamic and hardcopy systems will increase as a result of internal processing and memory capacity. In general, prices are likely either to remain constant or to increase as a result of the added capability.

The cathode ray tube will remain the dominant display medium for most applications where size is not a limiting factor. (The size of CRTs is not expected to exceed 25 in.). Plasma panels will become more economical and will be used for applications requiring a display with mechanical ruggedness and a thin profile. Electroluminescent displays will become available on a limited basis by 1980 and will be capable of good-quality video by 1985. The liquid crystal panel displays will become a major competitor of the CRT for devices not displaying motion.

In the hardcopy area, there will be a continued improvement in the area of COM technology, primarily as a result of the use of front-end processors. COM prices will not decline in the foreseeable future, since any reduction in component prices will be reflected in greater sophistication and flexibility.

With few exceptions, printers will employ well-developed and time-proven technology. The low-speed printers will exhibit little to no improvement in speed and will decline only slightly in cost. The higher-speed impact printers will remain constant in capability and will be

replaced by the nonimpact technologies. The very-high-rate (above 20K lpm) nonimpact printers will remain constant in speed but will increase in reliability and decrease in cost.

#### SOFTWARE

Systems software, particularly operating systems, are an important extension of the hardware, serving to interface applications programs with the hardware while making the hardware configuration invisible to the applications software. Operating systems will continue to keep pace with the hardware in the 1980's. They are expected to be more usable, flexible, and dependable. Hardware technology will aid this development during the 1980's as larger and larger portions of the operating systems will be implemented in firmware.

Software includes both systems software and applications software. Due to the rapid advances of data processing hardware technology in the 1980's, both systems and applications software will become larger (in terms of number of instructions) and more complex.

The three major concerns about software are cost, programmer productivity, and quality. These concerns point to a general concern as to whether the technology that produces the software can continue to meet the demands for the larger and ever more complex programs in the 1980's. Analysis of two aspects of software engineering technology — language and methodology — indicates that by 1985 software technology may well become the limiting factor in data systems development. Programming has traditionally been practiced as a craft, and although there is a movement by the industry toward more scientific and disciplined approaches, software engineering is still in its infancy. In fact, it is at least 10 years behind the related discipline of digital engineering (which produces the hardware). It is possible for software engineering to catch up with the demands placed on it by the development of a universal engineering language and increased use of software libraries. However, the industry remains content to invent general-purpose coding

languages and tighter programming controls with the hope that these actions will provide a major "breakthrough". At present, there are no trends to indicate that either the existing solution attempts can provide the breakthrough or that before 1985 the industry will give up trying to make them work. Similarly, there is no trend to indicate that programmer productivity will increase beyond its present 3% growth rate.

#### CONCLUDING REMARKS

In summary, all areas of data systems technology are advancing at unprecedented rates. Although technology is advancing rapidly and there is a high probability of satisfying NASA's future requirements, technological capability does not imply availability, and developments at the system level may be required in a number of areas. In view of this, a continuing assessment of technology at the component and the system level is required to establish where such developments are needed and how to best accomplish the desired result.

#### INTRODUCTION

#### OVERVIEW

Future NASA Office of Applications (OA) programs require the collection and subsequent dissemination of unprecedented volumes of data on a timely basis over widespread geographic areas. Users of the data range from large Government departments (Interior, Agriculture, etc.) to the individual (college professor, researcher, etc.) with a common limitation: budget.

The OA foresaw the technical, logistical, and integration problems associated with such a complex undertaking and implemented the Data Management Program to review and input to those functions that affect NASA's participation in the objectives, including requirements, capabilities, integration, and budget assessment. This report covers one aspect of the capabilities function: i.e., technology assessment. Also, because technology assessment covers cost as well as performance, inputs to budget will result.

The scope of a technology assessment for end-to-end data systems is so massive that it was impossible to provide the breadth and depth of coverage that is desirable within a limited resources program. Selected areas of technology that were considered as critical to NASA's future programs have been given the broadest and most in-depth coverage.

Technology assessment as defined herein is directed toward establishing the state of the art, trends, and future capabilities (1980-1985) for end-to-end data systems. Data systems elements making up end-to-end data systems were defined by the NASA Data Systems Laboratory and are as follows:

Data Generation - Sensing of physical parameters that characterize the phenomena to be investigated and translation of these parameters into electrical signals acceptable to a data system.  Data Processing (Space) - Processing of data, usually but not exclusively in the digital mode, to change them to a form more acceptable for data transmission, storage, or use onboard

等。 第二章 等级的,2000年(1900年) 2000年 6000年 6000年

- Data Storage (Space) Storage of data for delayed transmission; for delayed processing, display, or other use onboard; or for physical return of the storage media

- Data Handling (Space) The acquisition and/or distribution of data for data processing, display, storage, or other use onboard. The combining of data streams from several sources or the modification of single data streams to a format suitable for storage and/or transmission.

- Communication (Space to Ground) All functional elements necessary to transfer data to or from a spacecraft to the ground. Includes the functions performed by modulator, transmitter, airborne antennas, relay systems, ground antennas, receivers, and demodulators

- Preprocessing Elements (Ground) The data processing elements (hardware and software) that take either predetection or postdetection data and detect (as necessary), demultiplex, and reformat the data into a parallel, digital format with calibration

- Processing Elements (Ground) The hardware and software components that take parallel formatted digital data (either raw or semiprocessed) and produce end products suitable for either further processing, display, or storage within a data base

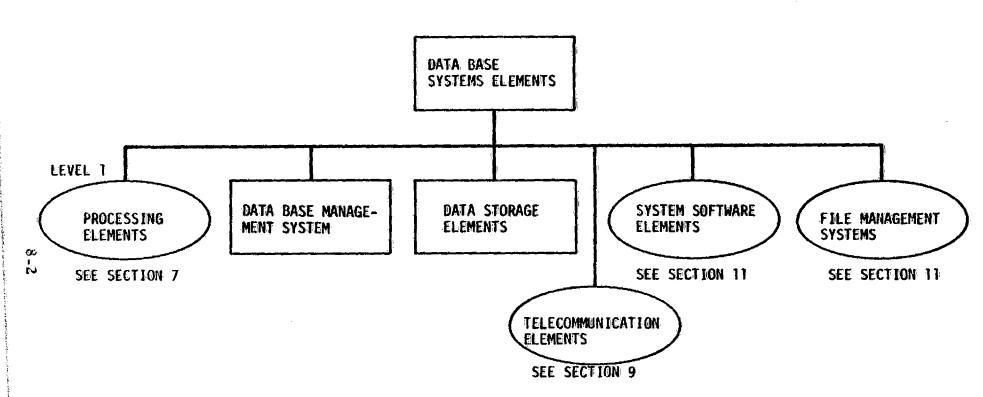

- Data Base System Elements (Ground) The hardware and software components that enable the creation of an integrated data base from logical files and the subsequent retrieval of information from the data base using either specified keys and/or relationships

- Information Distribution Elements (Ground) The manual and electronic means (hardware, software, and protocol) for requesting and distributing processed and preprocessed data in response to a user request

Information Presentation Elements (Ground) - The hardware and software elements necessary to provide hardcopy and dynamic visual presentations of image, alphanumeric, and graphic data.

In the following sections, current and future data system technologies are discussed within the context of the above definitions with the following exceptions. Data generator elements, which are covered by a separate contractor study, are not covered in this report. This section, which would have been Section 1, was replaced by a new section entitled "Technology Perspective" that discusses the microelectronic revolution as it relates to the various technologies discussed throughout the remaining sections of the report. Another modification to the report format was the inclusion of the software technology discussion as a separate section (Section 11) rather than as part of ground-based processor technology as organized outlined. Thus the report is organized into 11 sections with Sections 2 through 10 consistent with the corresponding data system elements as defined above. The elements are discussed in terms of the subelements or levels that make up the parent element. For example, data processing elements make up hardware (processors, data storage, etc.) and firmware (memory and microcode). elements are discussed in terms of state of the art (performance capabilities of typically top-of-the-line or high-performance devices), trends (uses, effects on cost and performance, historical extrapolations, etc.), and projected developments (forecasted capabilities for some future time period -- 1980 to 1985 for this report).

#### PUSPOSE AND USE OF REPORT

The report is intended as the beginning of a data bank that can be used by designers, analysts, and planners of NASA data systems. The trends and projections should enable designers for future NASA data systems to assess particular aspects of the technology such as the various system component technologies to determine reasonable data system design configurations. An individual data component or subcomponent

will frequently have application in several data systems element areas. For example, semiconductor memories could conceivably be used in any of the 10 data systems areas. To minimize repetition of data within the report, discussions relating to a specific data system element or component are presented within the parent element section where its application is expected to most heavily affect NASA data systems. In the above example of semiconductor memories, the subject is covered under Data Processing Systems Elements (Section 7) and is referenced in other sections where applicable.

Finally, an important consideration concerning the technology forecasts is that a forecast does not necessarily imply availability. Further, a list of specifications does not imply that all specifications within a given list will be feasible within the same system. For example, speed and power consumption are usually opposing considerations (i.e., as the propagation delay within a circuit decreases, the power increases) and the specification for low power consumption per bit may not correspond to the best projections for access and cycle times. To clarify limiting factors such as these, verbal discussions that attempt to identify pertinent considerations are presented within the report. Thus the user must interpret data herein within the intended context for it to be meaningful.

#### APPROACH

The approach to developing the assessment was based on a combination of analysis of literature in the different technology areas and a sampling of opinions of experts and authorities currently working the areas.

Many authorities in the data systems field responded to requests for information via the mail, telecons, and visits, and significant parts of the forecasts are the result of their contributions. Many of the respondents generously gave permission to use their names as the source of the information. However, the sponsoring agency (NASA) requested that specific references be made only to published literature

to eliminate the possibility of embarrassment to either the individual or the organization. Individuals and organizations that contributed are listed alphabetically at the end of the report. Many of these individuals are outstanding in their fields. Their contributions are gratefully acknowledged.

As with literature, the responses of individuals regarding future capabilities varied rather widely. These responses had to be weighted based on some criteria. Frequently, the criteria used were in favor of the majority of responses. Another criterion was the availability of prototype hardware that appears to have potential as production equipment in the timeframe of interest. Finally, the past experience of the individual within a given area was weighted heavily. For example, if an individual or his organization has been dominant in a given field for a reasonable length of time, then the opinions of that individual were weighted heavily.

#### SPECIAL CONSIDERATIONS

A number of traps exist in any report of this type, even when reporting state of the art. One of the first traps is to distinguish in the literature and in replies to questions between what is feasible on a production basis versus what is available on a custom-design (higher-cost) basis. Beyond this, one must distinguish between what is available on a custom-design basis and what is available only in the laboratory; and finally, for space applications, there must be a distinction between what is available for terrestrial applications versus space applications. The literature is usually vague on these distinctions.

Another very important consideration is that just because technology will support a capability, this does not mean that the capability will be available. The availability in many instances is a function of market demand or emphasis in the area of concern. Microprocessors, semiconductor memories, and other integrated circuit devices, for example, provide the capability for building tremendous flexibilities

into data system elements, but the capability does not imply availability. Similarly, various elements of data systems comprise several underlying technologies: i.e., RF technology and integrated circuits. Thus developments in one technology -- e.g., IC speed -- that would permit an advance in a data system element capability is not necessarily reflected on a one-for-one basis because of either the limitations or lack of emphasis in another area. Attempts are made to account for this in the discussions where possible.

In summary, an attempt was made to distinguish between what is likely to be available commercially and what is feasible in terms of technology. Projections are based on the use of commercially available components; thus developments at the component level will not be required. Developments at the system level (above the IC level) may be required.

#### REPORT FORMAT

The report is formatted to comply with NASA's data bank organization and to facilitate update. As a result, a large number of pages are only partially filled.

#### 1. TECHNOLOGY PERSPECTIVE

During the last decade, the evolution of electronic technology has been so dramatic that it has often been referred to as a revolution. The common denominator in this revolution, whether it be space data systems or digital watches, is the "miracle" of the chip. Although there have been significant advances in a number of other technology areas that relate to NASA end-to-end data systems requirements, none can compare with the advances in microcircuit technology. The complexity of microelectronic devices has increased exponentially during the last 15 years, and all indications are that the microelectronics revolution is far from having run its course. In fact, it is currently projected that the revolution should continue at its present pace for at least another 10 years or more. It is for these reasons that the technology perspective presented in this section focuses on the microelectronics revolution and attempts to project where it is headed within the 1980-1985 timeframe. The information presented in this section thus provides a common thread for many of the projections found throughout the remaining sections of this report.

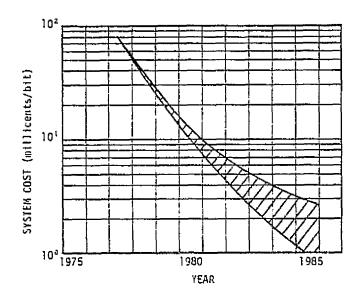

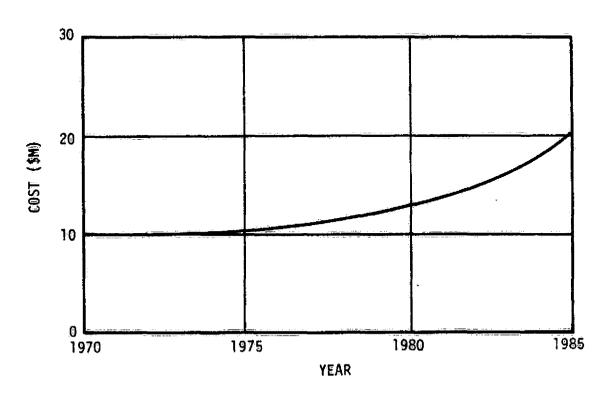

Another important aspect of the technology perspective presented in this section is that it emphasizes the need for accurate technological forecasting. Now, more than ever before, timing is most critical in the development and/or procurement of large data systems or data system elements. One example that underscores the tremendous current economic pressures resulting from advancing technology is the recent price reduction of large-scale computers by most of the industry, including the largest price reductions ever made by IBM. These price reductions are representative of the trend in improving cost/performance that is expected to continue for the next decade, as explained in Section 7. This example also illustrates the importance of using technological forecasting as a tool to reduce the cost of data systems development and/or procurement.

As a result of the microelectronics revolution, data system technology has advanced to the point at which requirements are beginning to assume their rightful role as driver of the data system design. This will increase at an accelerated rate in the 1980-1985 timeframe. Future space data systems will have access to new technologies that are capable of enhancing every aspect of space data management from the space sensor through the final processed and displayed data on the ground. The designers of these data systems will have considerable flexibility in where the data are processed, where and in what form they are stored, when and how the data are transmitted to the ground, and how they are handled on the ground. Capabilities available for future data systems include:

- Data management systems with adaptive features and interactive capabilities (including limited voice interaction) onboard and via space-to-ground communication links

- Space processing options that range from sophisticated dedicated processing to shared resource processing, with on-line, fast-access storage for data and complex software algorithms. Processing capabilities may be distributed at any point from the sensor to the final display.

- High-capacity data base storage (10<sup>11</sup> to 10<sup>12</sup> bits) onboard the spacecraft with update capabilities either onboard or via the ground-to-space communications link

- Programmable/adaptive data handling systems with asynchronous, variable-bandwidth, priority-controlled message handling, using store and forward techniques

- Communications power and bandwidth capabilities to satisfy the most complex orbital requirements

- More powerful ground data processing and data management capabilities through faster processors and memories, more sophisticated system architectures, and more sophisticated vendor software

- Capabilities for distribution of wideband data via small satellite terminals, and increased terrestrial capabilities employing packet-switching techniques and advanced hardware technologies.

The ability to implement the preceding capabilities will be based to a large extent on the availability of microelectronic (integrated circuit) devices, including extremely low-cost computers and high-capacity memory devices on a chip. The need to share computer and memory resources onboard the spacecraft will be nil. Each subsystem will have its own processor and storage devices, except in instances where the same data are shared by many users. Even in the case of shared data, there will be instances where it is cost/performance-effective to duplicate data in different memories onboard a spacecraft. Thus distributed processing and distributed data bases onboard the spacecraft will be the norm.

This section addresses the technologies that will be available to support future end-to-end system designs from the standpoint of current trends and projected developments in basic microelectronic technology. The capabilities of specific data system elements at the subsystem level are discussed in the remaining sections of the report.

#### 1.1 MICROELECTRONIC TECHNOLOGY

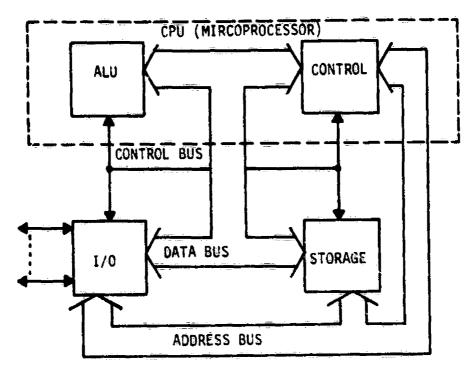

Microelectronic devices, also designated Integrated Circuits (ICs), play an extremely important role in present-day data systems, and this role is projected to increase significantly in future data system designs. This section discusses the technology of microelectronic devices in general. Other sections of the report discuss specifics of microelectronics as they relate to microprocessors, memory devices, peripheral devices, communications, display systems, and related subjects. Discussion in this section centers on factors that are common to all microelectronic devices, such as state of the art in microelectronic technology, how microelectronic devices are used in current data systems, what factors are affecting future development of microelectronic devices, and future projections for microelectronics. The bibliography lists a number of excellent articles that provide a more detailed discussion for those readers who wish to pursue the subject in greater depth.

# 1.1.1 Background

The history of microelectronics began with the development of the transistor by W. Shockley of Bell Laboratories in 1947. During the 1950's the digital computer provided a large market for the transistor and stimulated research into methods of further microminiaturization. Most of the initial research was aimed at miniaturization of conventional computers and/or hybrid packaging techniques. These techniques were in general expensive but in many cases were adapted for aerospace applications where the additional cost could be offset by significant reductions in weight.

The origin of modern integrated circuit technology can be traced to the development of the planar process at Fairchild Semiconductor in 1959. The planar process was based on two important process patents. The first, by K. Lehovec of Sprague Electric, provided a means for electrically isolating the individual transistors from the integrated circuit substrate, thus allowing a circuit to be fabricated on a single substrate with multiple active devices. The second invention, by

J. Hoerni of Fairchild, provided a method for using silicon dioxide as an insulator between the interconnecting metalization patterns and the underlying semiconductors.

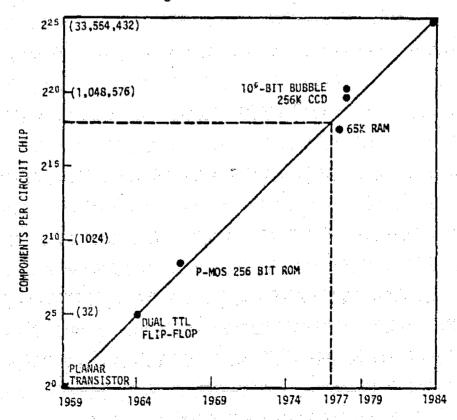

In 1964, five years after the production of the first planar transistor, Gordon E. Moore observed that the number of components in advanced integrated circuits had been doubling every year...Mr. Moore, who was then the director of research at Fairchild, predicted that the doubling process would continue into the foreseeable future. Today, after 19 years, there has been no significant deviation from Moore's original projection (also called Moore's Law). Moore's Law, illustrated in Figure 1.1.1-1, extrapolates the forecast to 1984 and overlays some of the circuit devices that have kept pace with the law. If this trend continues, the number of components per chip for production integrated circuits will exceed 30 million by 1984. The probability of this trend continuing is discussed in the following subsections.

FIGURE 1.1.1-1. MOORE'S LAW ILLUSTRATED FOR 1959-1984

# 1.1.2 State of the Art in Microelectronics

Electronic technology has progressed through several levels of integration [small-scale integration (SSI), medium-scale integration (MSI), and large-scale integration (LSI)] to the point where very-large-scale integration (VLSI) is beginning to emerge, with initial production devices providing complexities in excess of 100,000 circuit elements (resistors, capacitors, transistors) per chip. Laboratory devices that contain more than one million circuit elements have been developed, and techniques capable of dwarfing these figures are being researched.

The state of the art in terms of production devices that are currently being built on a single chip includes a variety of digital and analog devices, as well as mixed devices capable of handling both analog and digital signals. Some examples of state-of-the-art single-chip microelectronic devices are: 16-bit microcomputers with 2,048 bytes of ROM and 144 bytes of RAM on the chip, 65-Kbit random access memories, 262-Kbit sequential storage chips, and complete multi-channel data acquisition systems that include a 16-channel analog multiplexer and a 10-bit A/D converter.

Advances in microelectronic devices are normally discussed in terms of digital devices. The major emphasis in this report is also on digital devices since the trends for future data systems are so heavily oriented in that direction. Actually, however, significant advances are occurring in both analog and digital devices. Analog devices that are available as monolithic (one-chip) devices include operational amplifiers, power amplifiers, isolation amplifiers, filters, regulators, oscillators, mixers, analog switches, multiplexers, and other related components. Beyond the fact that these components can be fabricated as monolithic units, mixed processing techniques enable the development of linear devices with very unique characteristics. As an example, amplifiers can be fabricated with FET inputs and bipolar outputs. The FET input operates with low input bias current as a result of the high input impedence, but the bipolar output provides good linearity on the output side. Both of these advantages are not achievable with either an all-FET device or an all-bipolar device.

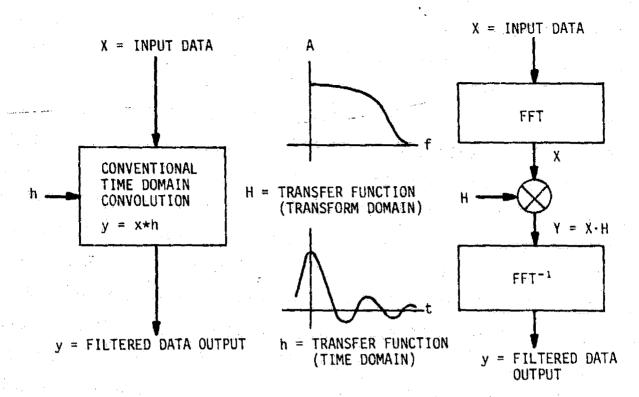

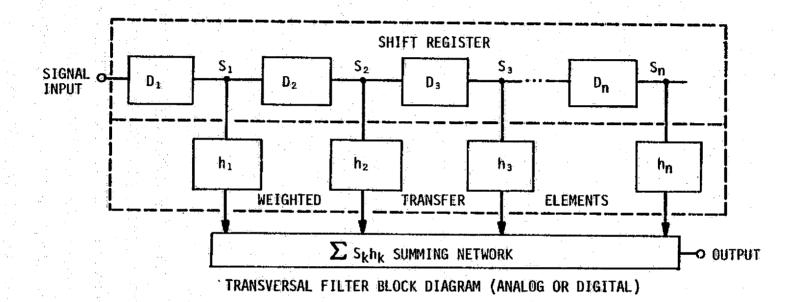

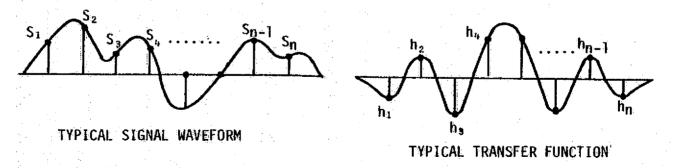

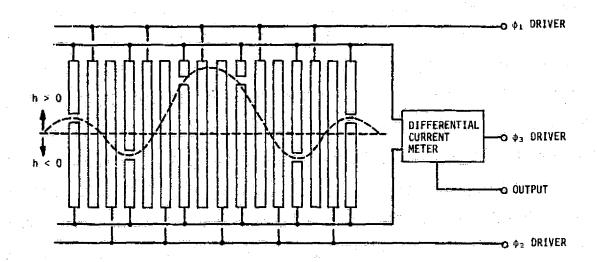

Simultaneously, the technology permits mixing of analog and digital circuitry on the same chip, including but not limited to analog-to-digital and digital-to-analog converters. One unique device in this category that is nearing market availability is a programmable CCD filter. The device operates as a transversal filter under the control of a separate microprocessor and read-only memory. The device can be factory programmed to operate as one of four types of filters, low-pass or bandpass, each in narrowband or broadband versions. This device is discussed further in Section 2.2.

Because of the complex nature of current microelectronic devices, the large number of integrated circuit device processes currently in use, and the large number of microelectronic manufacturers, the exact state of the art of microelectronic technology is difficult to assess except in terms of the general complexity and performance characteristics of available devices and the fundamental limitations of current device fabrication techniques. Since performance characteristics for several state-of-the-art devices are discussed in subsequent sections, only the latter topic is discussed here.

For those readers who are interested in greater detail on how state-of-the-art large-scale integrated circuit devices are manufactured, an article from the September 1977 issue of <u>Scientific American</u> is suggested for further reading. The article, "The Fabrication of Microelectronic Circuits" by William G. Oldham of the University of California at Berkeley, is very readable and contains a number of useful illustrations that demonstrate fabrication and packaging processes. The article discusses the factors that currently limit the economical production of high-complexity microelectronic devices such as the effects of circuit size on process yield. The article also discusses several advanced wafer processing techniques, including X-ray lithography and electron-beam lithography. Additional information and future predictions for semi-conductor fabrication techniques are discussed in Subsection 1.1.3.

# 1.1.3 Trends and Projected Development in Microcircuit Complexity

This subsection discusses the outlook for the continued evolution of microcircuit device complexity. At the present time, semiconductor\* microelectronic devices are beginning to emerge with complexities in excess of 20,000 circuit elements for logic devices (Ref. 1-1) and in excess of 130,000 circuit elements for memory devices (Ref. 1-2). Measured in terms of logical functions and/or bits of storage, these chips represent complexities of approximately 2,000 gates with 11,000 bits of read-only storage and 65,000 bits of random-access storage, respectively. As complex as these devices are, they are not nearly as complex as the devices projected for 1990 by Dr. Carl Hammer, Director of Computer Sciences, Sperry Univac (see Table 1.1.3-1). In a recent paper (Ref. 1-3) Dr. Hammer predicted that by 1990 memory devices would contain up to 800,000,000 bits per chip and logic arrays (processors) would contain up to 6,000,000 logical functions per chip. Measured in terms of today's technology, these projections represent an increase in chip complexity of at least a factor of 2,000 (or 211) over today's technology. As pointed out by Dr. Hammer, even these 1990 projections are still well within the macroscopic domain; i.e., still not approaching atomic dimensions.

TABLE 1.1.3-1. COMPARISON OF STATE-OF-THE-ART LSI DEVICE COMPLEXITY WITH DR. CARL HAMMER'S 1990 PROJECTIONS

|                                    | MEMORY CHIP COMPLEXITY                                               | LOGIC CHIP COMPLEXITY                                                |

|------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|

| 1978<br>1990                       | 1.3 × 10 <sup>5</sup> transistors<br>8 × 10 <sup>8</sup> transistors | 2.2 × 10 <sup>4</sup> transistors<br>6 × 10 <sup>6</sup> transistors |

| Projected<br>Improvement<br>Factor | 6.1 × 10 <sup>3</sup>                                                | 2.7 × 10 <sup>2</sup>                                                |

<sup>\*</sup>Nonsemiconductor microelectronic devices, such as bubble memories, of even greater complexity are scheduled for commercial production by mid-1978.

In order to understand how the complexity of future microelectronic devices may evolve, it is appropriate to first discuss the relationships between minimum device fabrication geometries and logical/ storage cell dimensions. These dimensions can then be related to the practical and ultimate limits of the various process technologies to provide future device complexity projections.

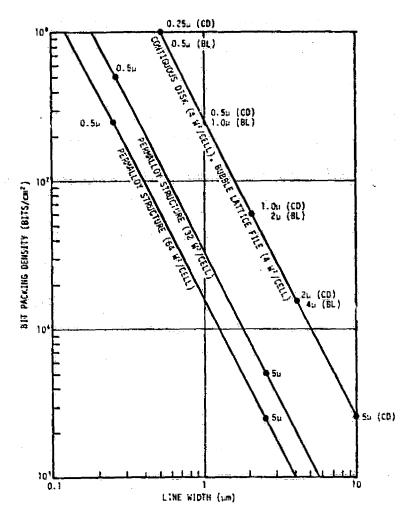

If we call the minimum circuit feature W, then the area of a memory storage cell or circuit device (transistor, diode, etc.) can be expressed as  $NW^2$ . Two other measurement units commonly used to express device size or memory cell size are square mils and square micrometers. The area of the device can be expressed either as the number of circuit functions per square unit of measure or as the number of square units of measure per circuit function. Since one mil is equal to 25.38  $\mu$ m. one square mil is equal to 644  $\mu$ m<sup>2</sup>.

The area of state-of-the-art memory storage cells varies from  $4\ \text{W}^2$  for contiguous disk bubble memories (see Section 3.2) up to  $52.2\ \text{W}^2$  for dynamic MOS random-access memories (Ref. 1-2). Static and other less efficient memory configurations have storage cells that are larger than  $100\ \text{W}^2$ . Since complex logic devices often contain a mixture of random logic and structured storage arrays, a similar measure of average device size is less meaningful. However, state-of-the-art microprocessors have device densities as low as  $60\ \text{W}^2$  (Ref. 1-1).

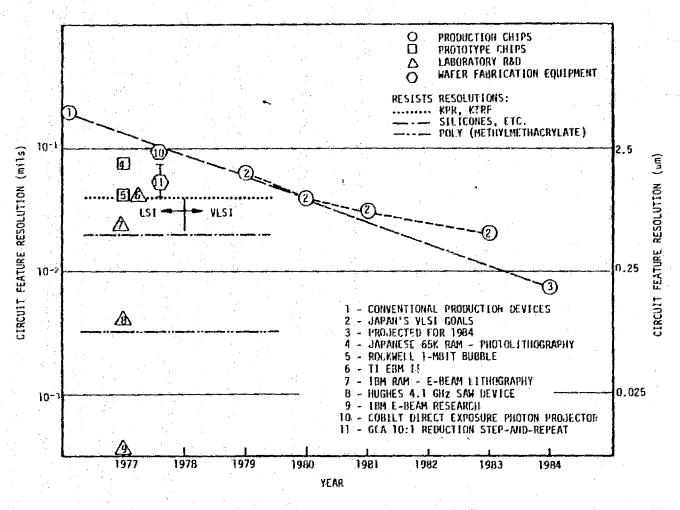

Currently, most state-of-the-art production LSI circuit devices have minimum circuit features of from 4 to 6 µm. The optical lithography systems used by most manufacturers employ high-pressure mercury arc lamps with ultraviolet output in the 200- to 600-µm range. Depending on the lithography system used, the minimum circuit features that can be printed routinely vary from about 4 µm using proximity printing with a 10-µm gap down to 1.6 µm for f-2.55 projection printers. Some of the 65K memory circuit devices scheduled for production in late 1978 or early 1979 are expected to employ 2-µm circuit features. Although 1 µm was previously considered an ultimate limit for optical lithography.

several companies are currently researching device features down to  $0.5~\mu m$  using deep ultraviolet lithography.

X-ray lithography and electron-beam lithography are currently the two most viable techniques to eventually replace optical lithography and thus overcome the limitations of resolution and depth of focus imposed by the wavelength of light. Electron-beam systems have been touted as the next logical step in the fabrication of microcircuits. These systems are currently employed on a limited basis to produce masks that are then used in the standard lithographic processes. Further, some E-beam systems are used as direct-wafer-exposure devices for laboratory-and/or custom-developed chips. The general feeling among American authorities is that the initial cost, the low throughput, and the yield forbid the use of these systems for direct wafer production for at least 3 to 4 years. On the other hand, the Japanese have based their entire VLSI program on the use of E-beam fabrication devices. Some of the advantages of scanning electron-beam lithography systems are:

- Computer control rather than masks is used to form the pattern and provide a high degree of pattern flexibility.

- Microscopic pattern distortions can be compensated for in real time.

- They provide excellent pattern registration and overlay.

The major disadvantage of scanning electron-beam systems has been the difficulty in achieving the necessary throughput for cost-effective use.

IBM has been researching electron-beam fabrication systems for the past 15 years and currently has a system (designated EL-1) which has a throughput rate of 22 wafer exposures per hour based on 2.25-in. wafers with 2.5-µm minimum features. The system design is such that it may be adjusted to make exposures in the 1-µm range.

Table 1.1.3-2, extracted from an article in the June 7, 1977, issue of <u>Electronics</u> by L. Altman and C. Cohen, entitled "The Gathering Wave of Japanese Technology", shows the goals of the Japanese VLSI

program using direct-wafer-exposure E-beam processes. The program calls for production devices with minimum line widths of 0.02 mils (0.5  $\mu m)$  by 1983. In order to achieve 30 million components per chip, as discussed in Subsection 1.1.1, the circuit dimensions must be no larger than 0.2  $\mu m$ . Although the Japanese VLSI program will most likely not reach 0.2  $\mu m$  by 1984, it is probable that the competition for business in this highly profitable area will push American firms to achieve this level of complexity by that time.

TABLE 1.1.3-2. GOALS OF JAPANESE VLSI PROGRAM

|       | RANDOM-ACCESS MEMORY                     |                        | MICROPROCESSOR                           |                          |                                 |

|-------|------------------------------------------|------------------------|------------------------------------------|--------------------------|---------------------------------|

|       | CHIP SIZE<br>(× 1,000 mil <sup>2</sup> ) | BIT DENSITY<br>(Kbits) | CHIP SIZE<br>(× 1,000 mil <sup>2</sup> ) | WORD<br>LENGTH<br>(bits) | MINIMUM<br>LINE WIDTH<br>(mils) |

| 1976  | 32                                       | 16                     | 52                                       | 8 and 16                 | 0.2                             |

| 1979- | 32                                       | 64                     | 50                                       | 16                       | 0.07                            |

| 1980  | 50                                       | 256                    | 60                                       | 32                       | 0.04                            |

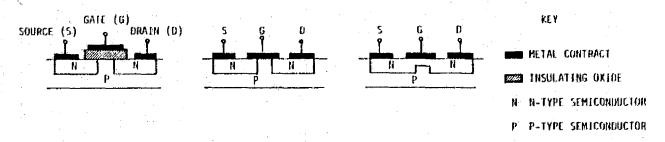

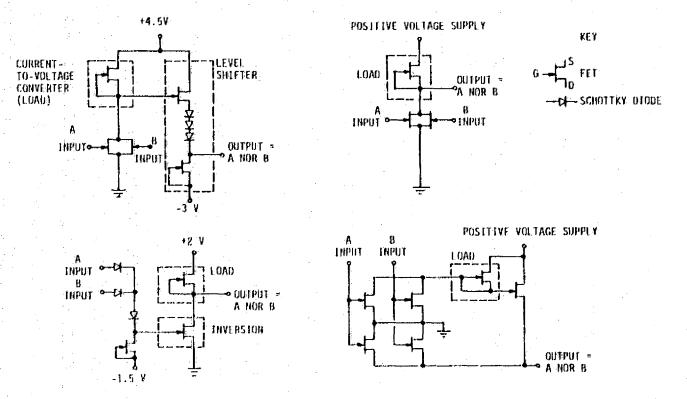

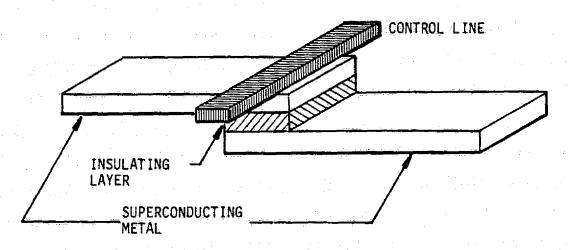

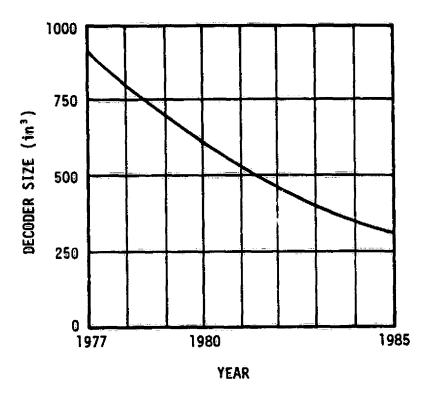

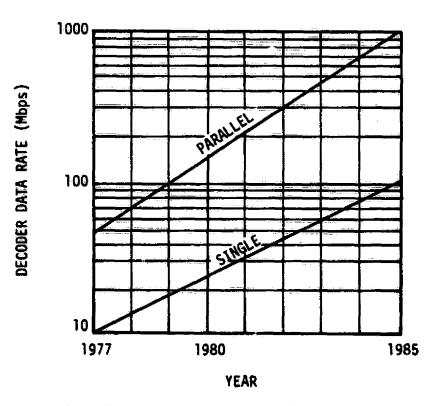

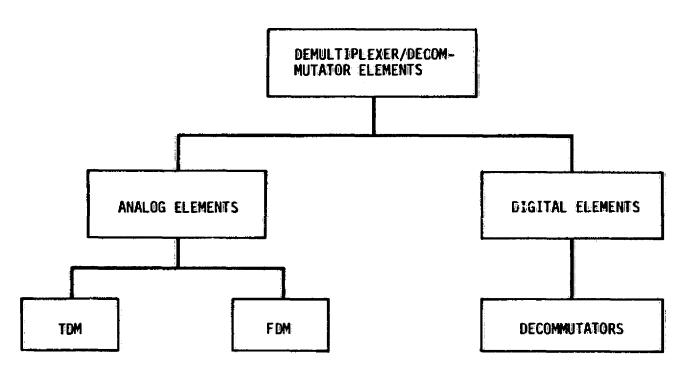

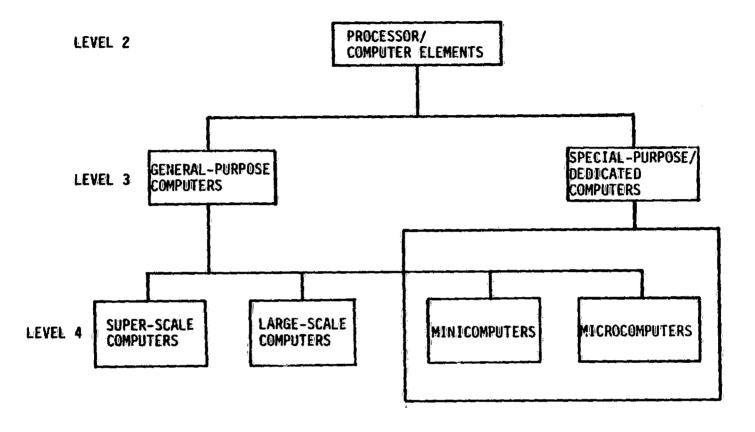

| 1981- | 45                                       | 256                    | 55                                       | 32                       | 0.03                            |