#### **General Disclaimer**

#### One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some

of the material. However, it is the best reproduction available from the original

submission.

Produced by the NASA Center for Aerospace Information (CASI)

(NASA-CR-150832) DESIGN, PROCESSING AND TESTING OF LSI ARRAYS HYBRID MICROELECTRONICS TASK Final Report, 3 Aug. 1977 - 2 Aug. 1978 (Hughes Aircraft Co.) 91 p HC A05/MF A01 CSCL 09C G3/33

N79-10341

Unclas 33926

FINAL REPORT Contract No. NAS8-32607

### DESIGN, PROCESSING AND TESTING OF LSI ARRAYS HYBRID MICROELECTRONICS TASK 3 AUGUST 1977 - 2 AUGUST 1978

**15 SEPTEMBER 1978**

Prepared for George C. Marshall Space Flight Center Marshall Space Flight Center Alabama 35812

MICROELECTRONIC PRODUCTS DIVISION NEWPORT BEACH, CALIFORNIA 92663

# DESIGN, PROCESSING AND TESTING OF LSI ARRAYS HYBRID MICROELECTRONICS TASK

#### FINAL REPORT

3 August 1977 to 2 August 1978

Contract No. NAS 8-32607

#### Prepared for

GEORGE C. MARSHALL SPACE FLIGHT CENTER MARSHALL SPACE FLIGHT CENTER, ALABAMA 35812

15 September 1978

R. P. Himmel S. M. Stuhlbarg S. Salmassy

INDUSTRIAL ELECTRONICS GROUP

Microelectronic Products Division

Hughes Aircraft Company • Newport Beach, California 92663

#### CONT ENTS

| 1.0 | INTR       | ODUCTIO                                             | ON AND SUMMARY                                                   | 1-1                                          |

|-----|------------|-----------------------------------------------------|------------------------------------------------------------------|----------------------------------------------|

| 2.0 | TEC        | HNICAL I                                            | DISCUSSION                                                       | 2-1                                          |

|     | 2.1        | Tasks I                                             | and II - Cost Factors Study                                      | 2-1                                          |

|     |            | 2.1.1<br>2.1.2<br>2.1.3                             | Cost Factors                                                     | 2-5<br>2-1<br>2-1                            |

|     | 2.2        | Task III                                            | Packaging Implementation                                         | 2-3                                          |

|     |            | 2.2.1                                               | Tape Process/Materials Evaluation Wafer Bump Processor/Materials | 2-3                                          |

|     |            | 2. 2. 3<br>2. 2. 4<br>2. 2. 5<br>2. 2. 6<br>2. 2. 7 | Evaluation                                                       | 2-4.<br>2-50<br>2-54<br>2-54<br>2-51<br>2-58 |

| 3.0 | PRO        | GRAM RE                                             | COMMENDATIONS                                                    | 3 - 1                                        |

|     | 3.1<br>3.2 |                                                     | Approach                                                         | 3-2<br>3-2                                   |

| 4.0 | ACK        | NOW LED                                             | GEMENTS                                                          | 4-1                                          |

| ΔDD | EN DES     | ' Δ. 17°1.0                                         | OW CHART LISTING                                                 | A 1                                          |

### LIST OF ILLUSTRATIONS

| Figure |                                                                                                          | Page   |

|--------|----------------------------------------------------------------------------------------------------------|--------|

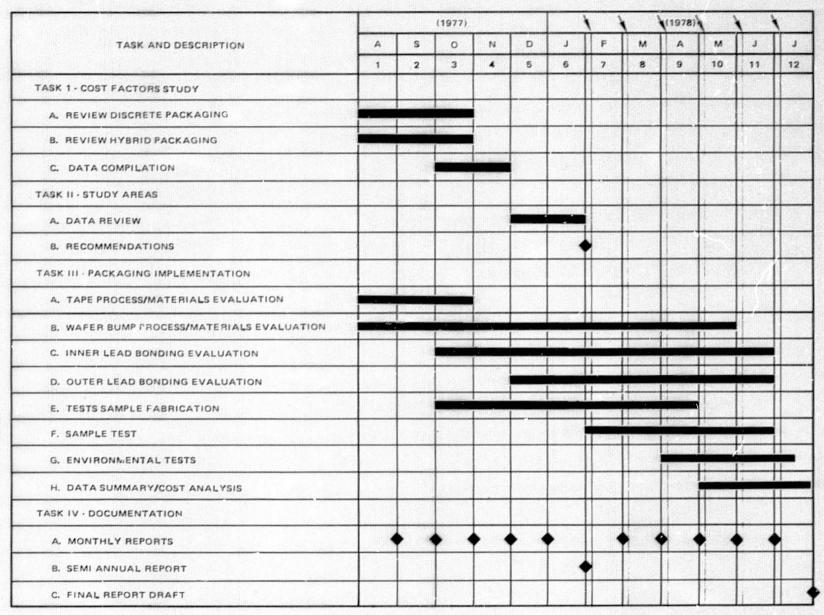

| 2-1    | Program Schedule - NASA Contract No. NAS8-32607                                                          | 2-2    |

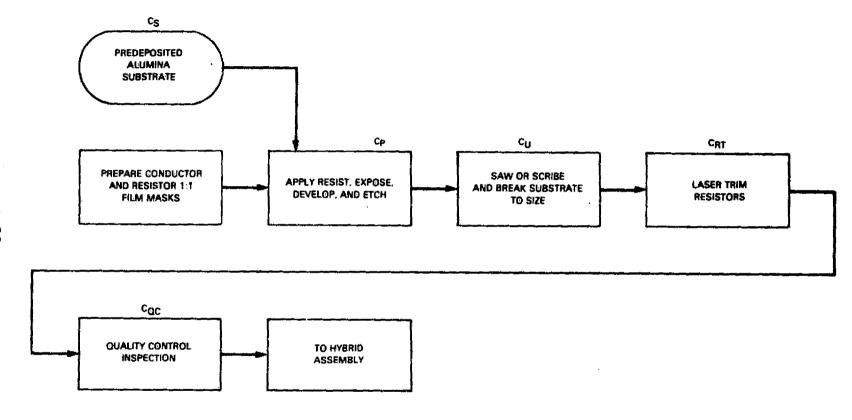

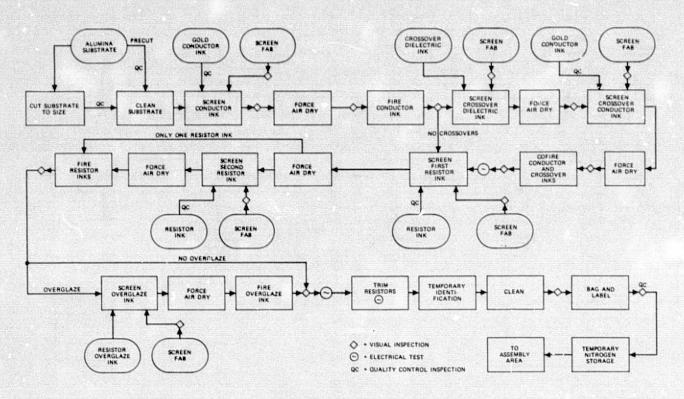

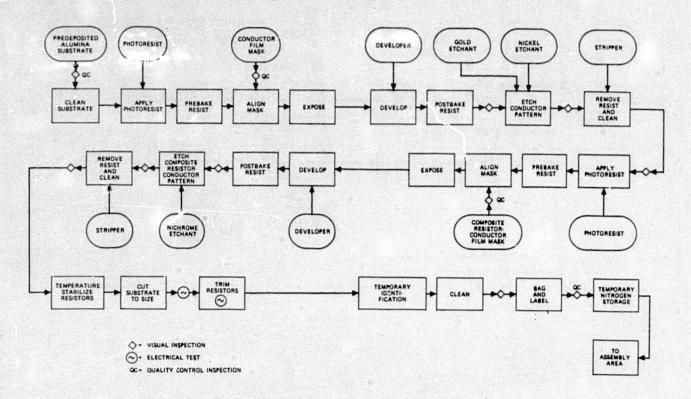

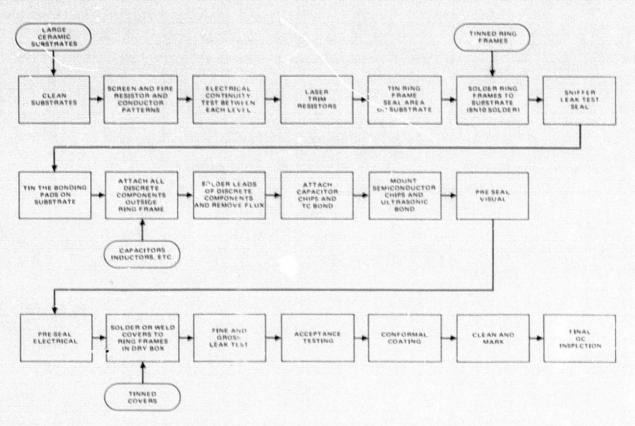

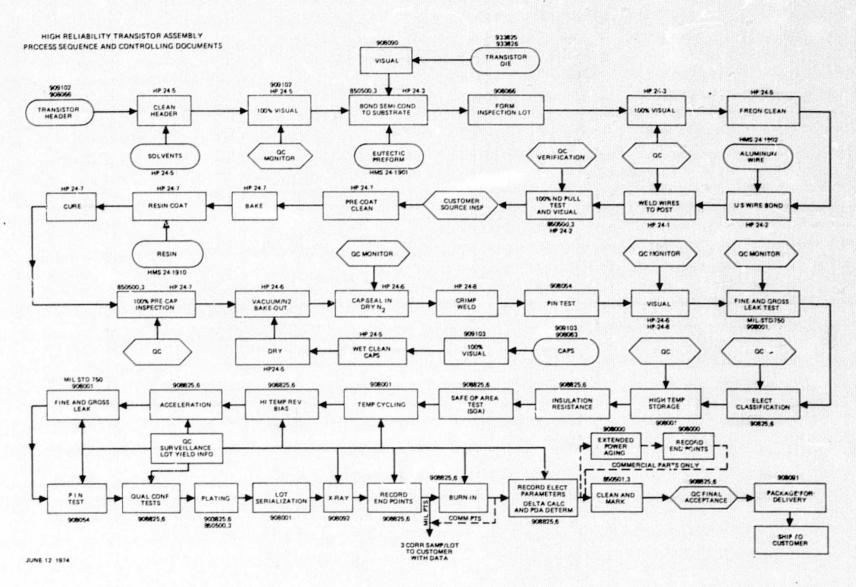

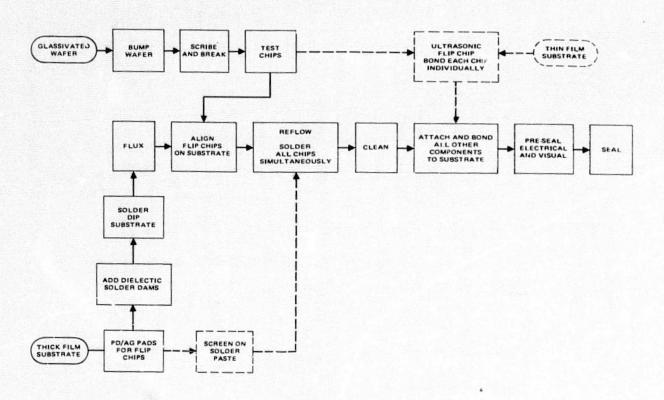

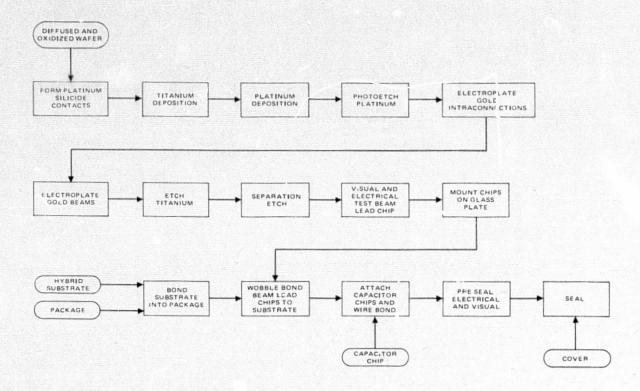

| 2-2    | Thin Film Substrate Fabrication                                                                          | 2 - 20 |

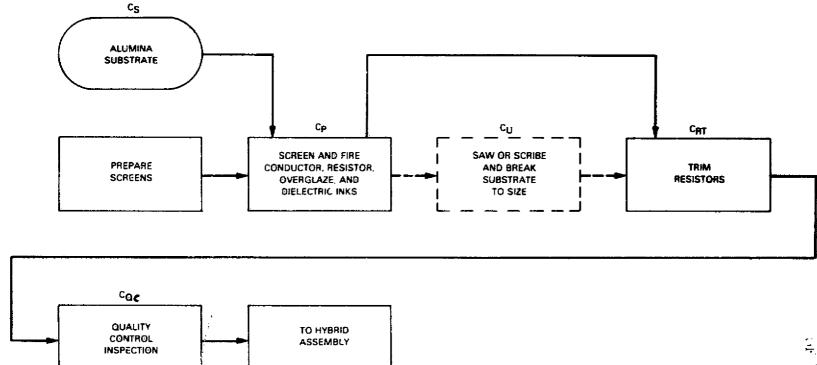

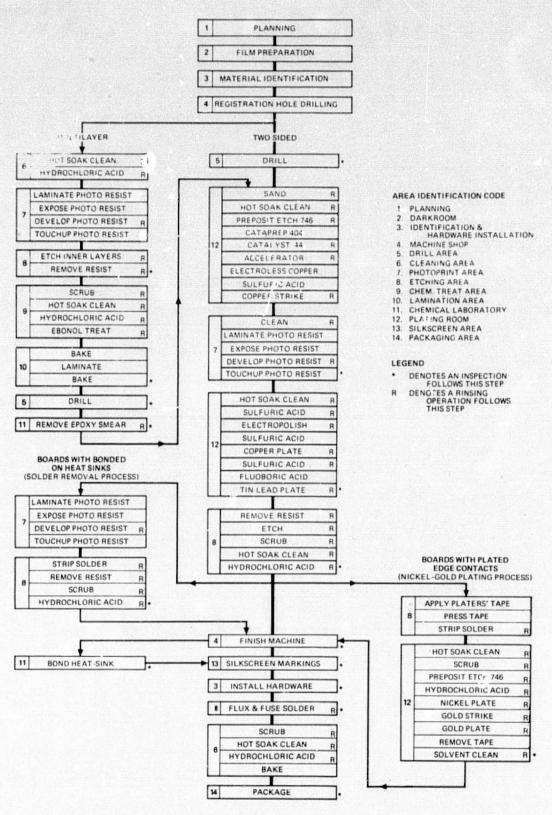

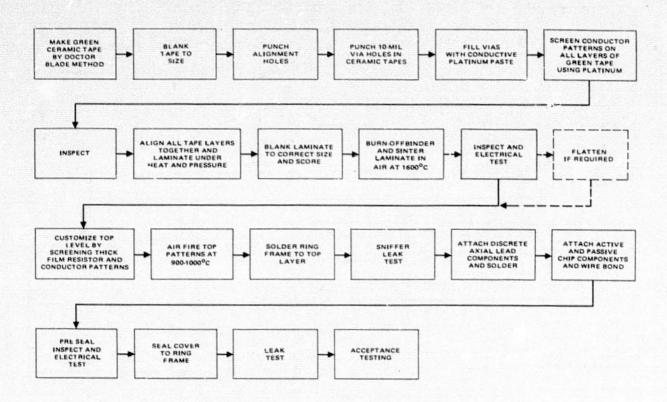

| 2-3    | Thick Film Substrate Fabrication                                                                         | 2-21   |

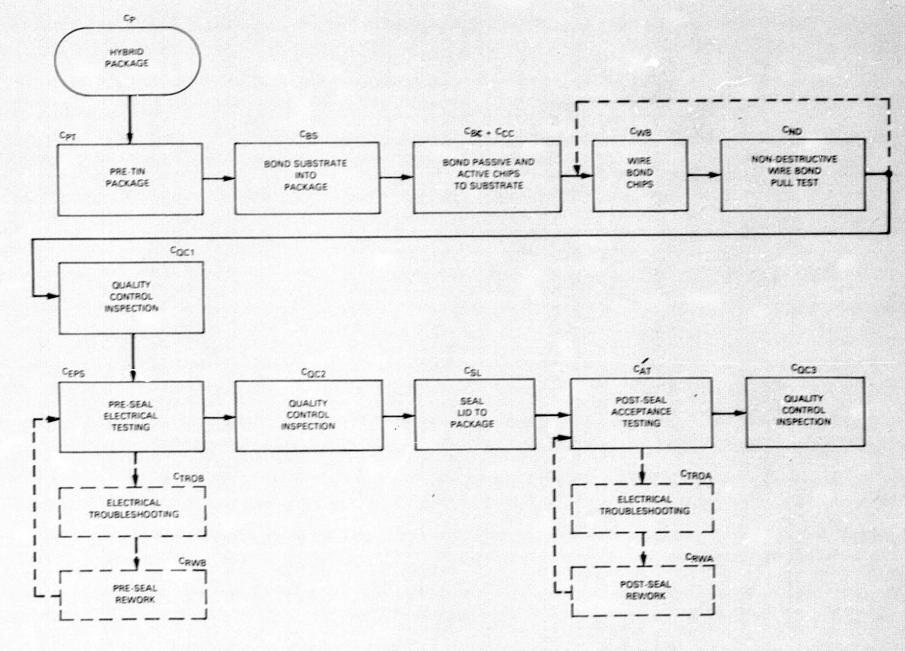

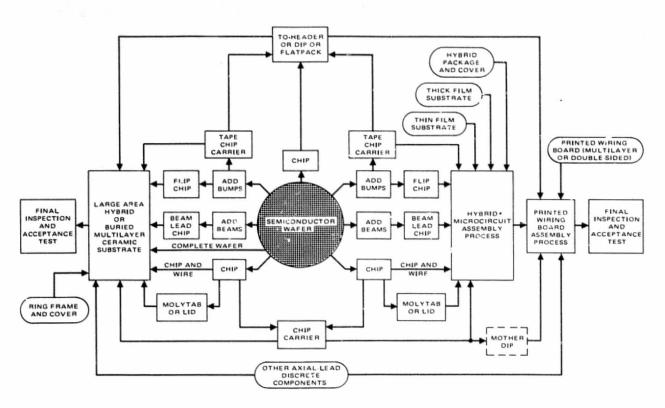

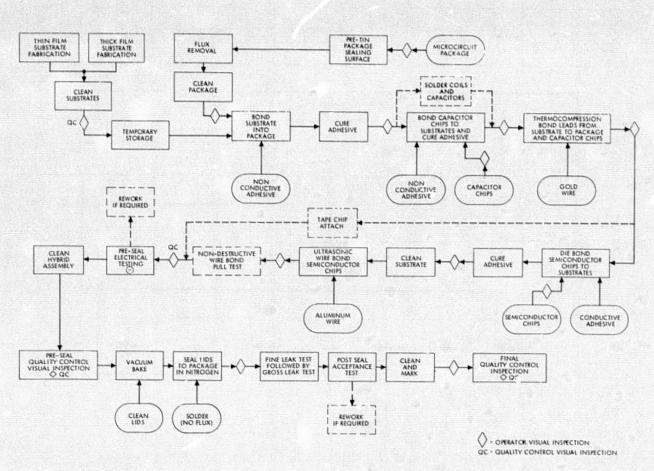

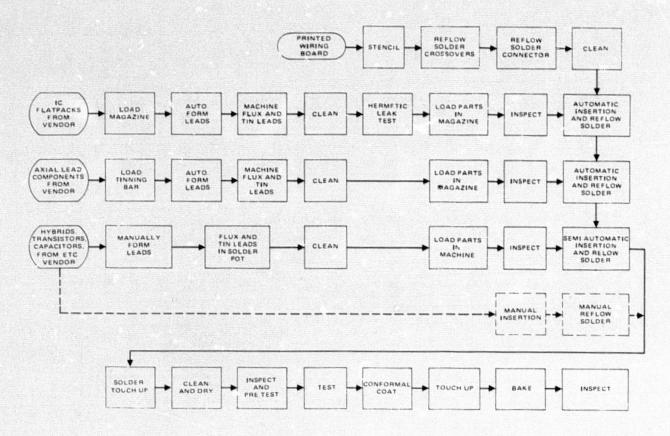

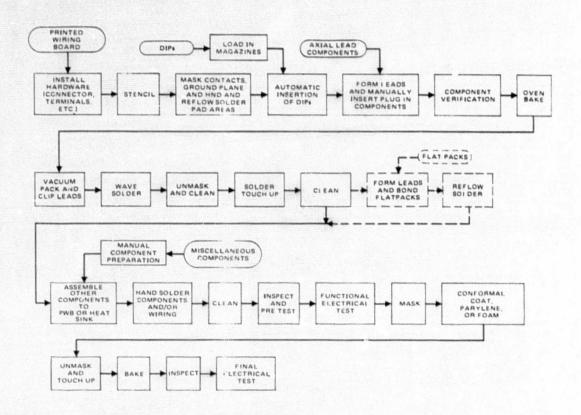

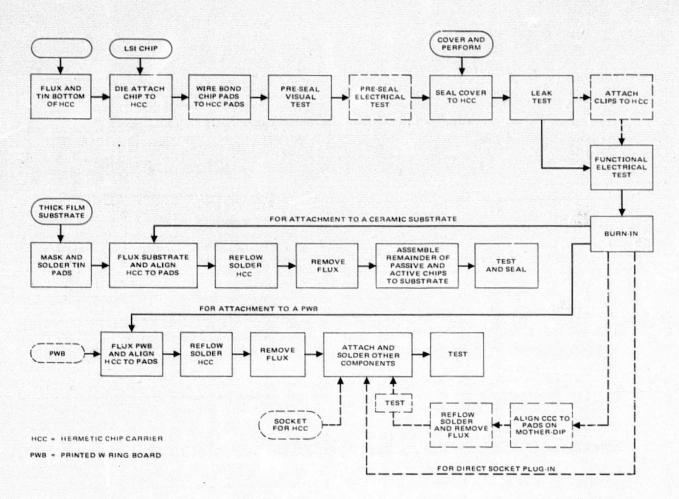

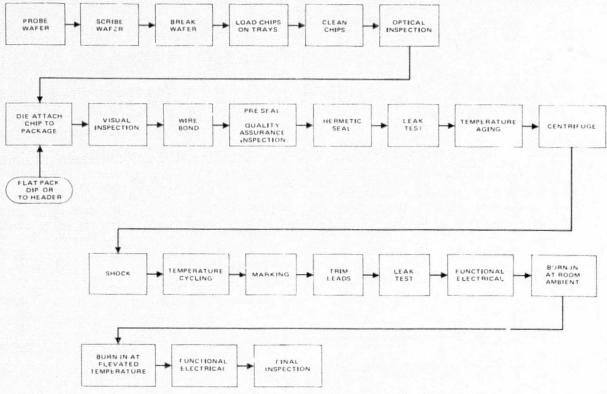

| 2-4    | Hybrid Microcircuit Assembly and Test                                                                    | 2-24   |

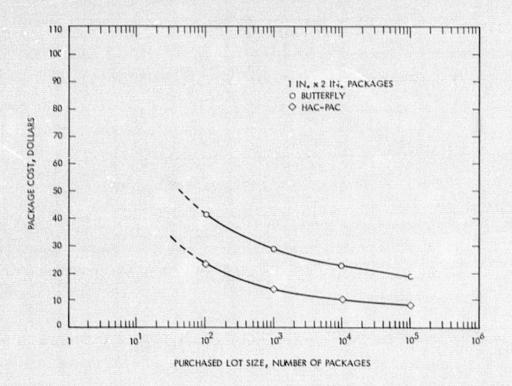

| 2-5    | Package Cost Versus Purchased Lot Size                                                                   | 2-25   |

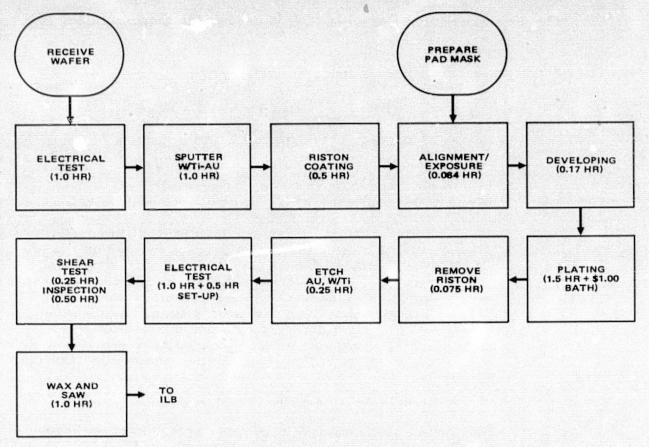

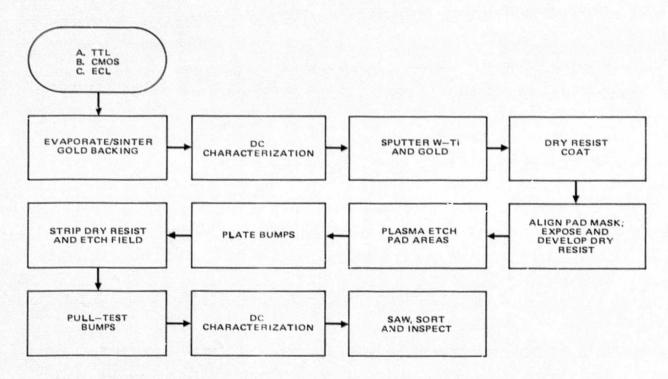

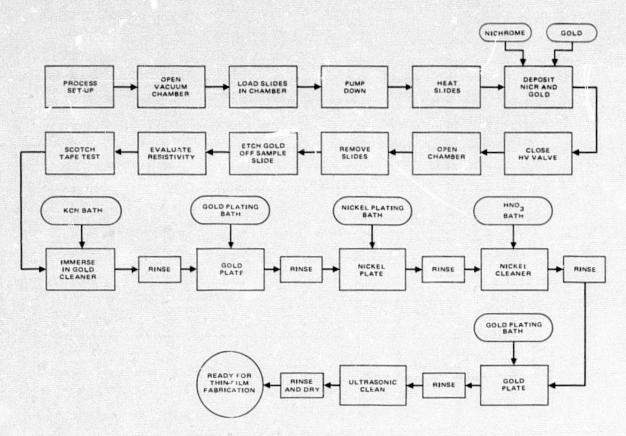

| 2-6    | Wafer Bumping Process                                                                                    | 2-34   |

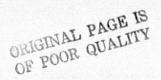

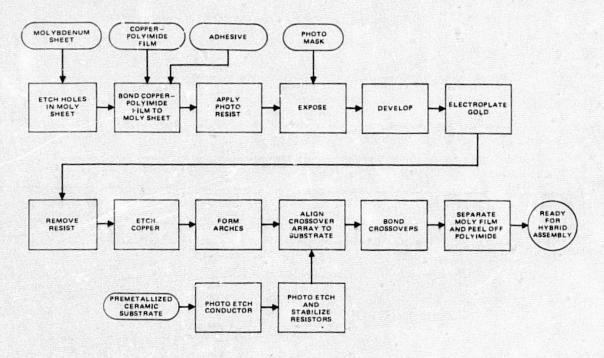

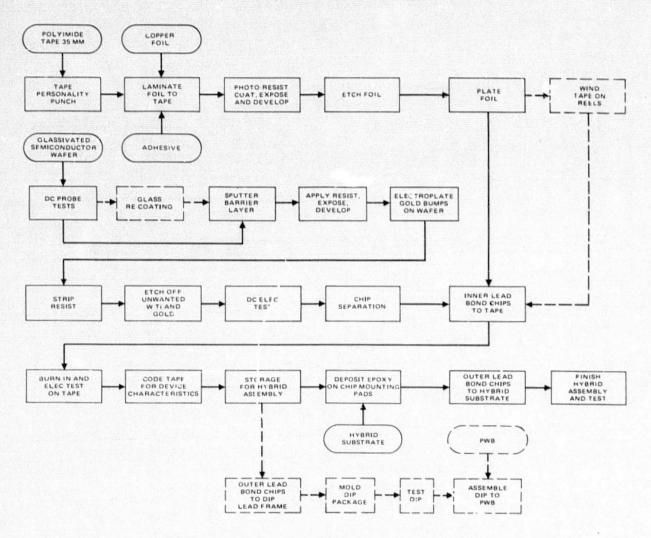

| 2-7    | Flow Diagram - Modified Tape Processing                                                                  | 2-37   |

| 2-8    | Typical Tape Photo-Mask                                                                                  | 2-38   |

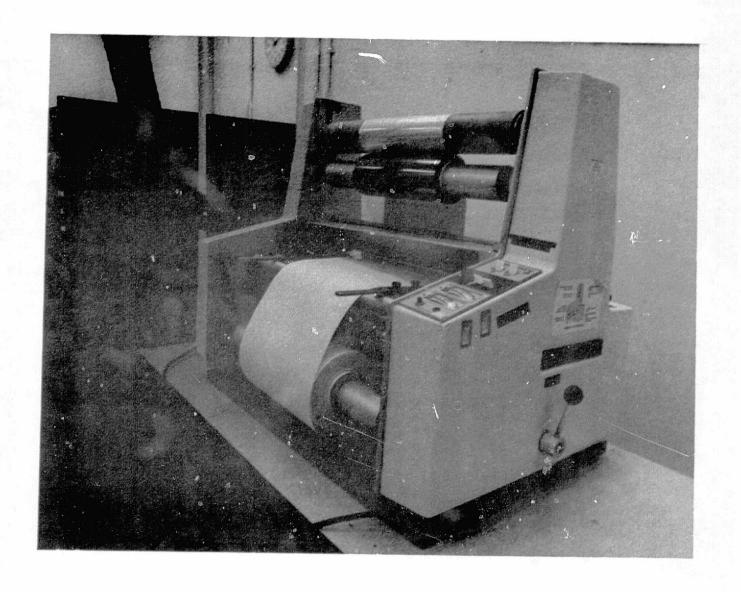

| 2-9    | Dry Film Laminator                                                                                       | 2-39   |

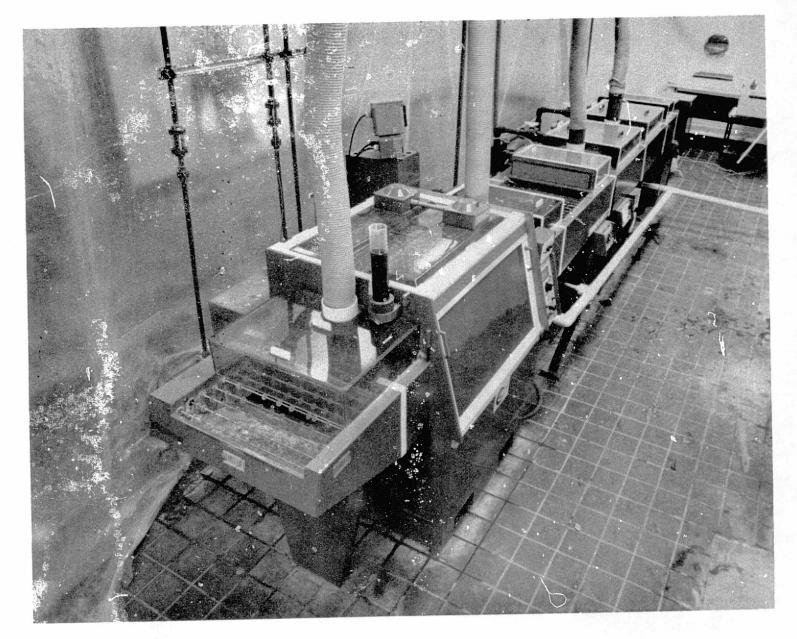

| 2-10   | Chem Cut Model 547 Spray Etcher                                                                          | 2-40   |

| 2-11   | Tape Carrier for 82-Pad ECC Devices Aligned over Hermetic Chip Carrier                                   | 2-41   |

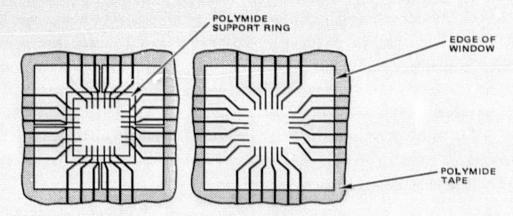

| 2-12   | Tape Chip Carrier Positions with and Without Polyimide Support Ring                                      | 2-43   |

| 2-13   | Bump Process Flow Diagram                                                                                | 2-43   |

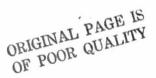

| 2-14   | Smooth, Dense, Fine-Grained Gold Bump Plated at a Current Density of Five Amperes per Square Foot        | 2-45   |

| 2-15   | Coarse-Grained, Porous Bump Plated at a Current Density of 20 Amperes per Square Foot                    | 2-46   |

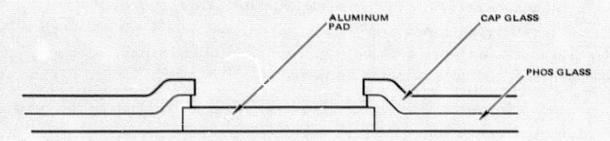

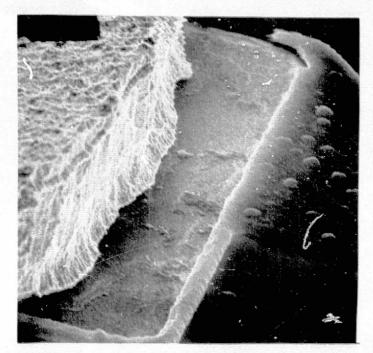

| 2-16   | Fissures in the Sputtered Gold and Tungsten-Titanium<br>Layers at the Edges of Windows in Glass over the | 2 42   |

| ~      | Pads                                                                                                     | 2-48   |

| 2-17   | Tungsten-Titanium Barrier Layer Lifting Free of Chip after Aluminum Pad Underneath is Etched Away        | 2-48   |

### LIST OF ILLUSTRATIONS (Continued)

| Figure |                                                                                                                                                          | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2-18   | Undercut of the Phosphorous Glass Due to Differential Etch Rates. Undercut will Cause Poor Step Coverage of Subsequent Layers                            | 2-49 |

| 2-19   | Pad Area Exposed Due to Misaligned Bump. Aluminum Pad is Etched Away                                                                                     | 2-49 |

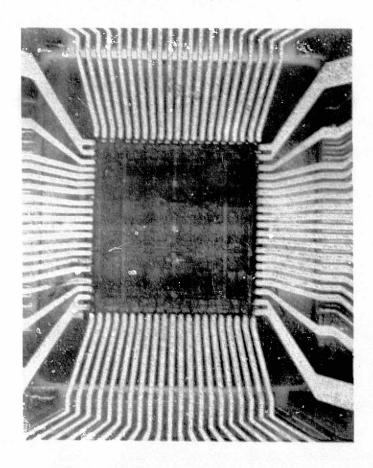

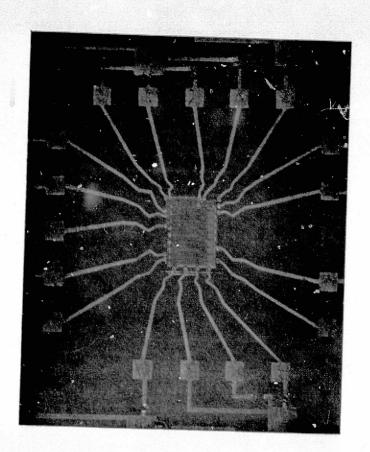

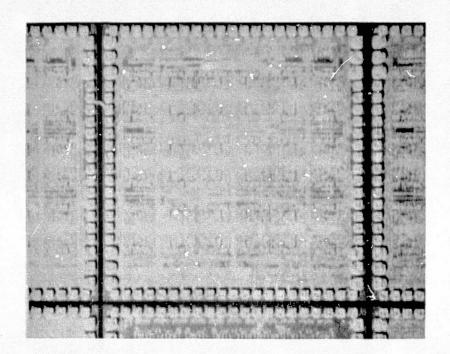

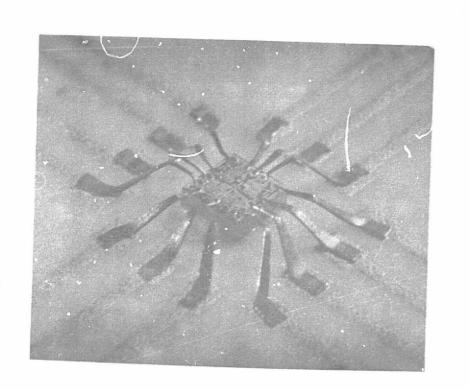

| 2~20   | Hughes Type 1824D Microprocessor RAM Chips Inner-Leaded-Bonded to 35-mm Tape Carriers                                                                    | 2-51 |

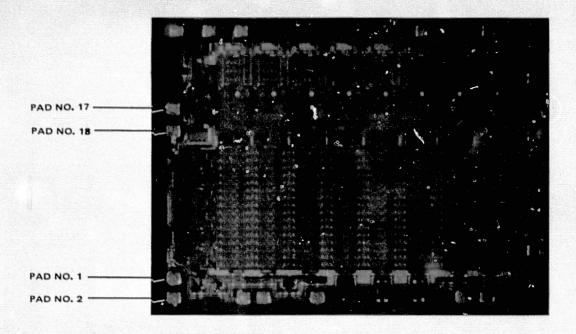

| 2-21   | Bumped 18-Pad MOS Device and 82-Pad ECL Devices Showing Close Pad Spacings                                                                               | 2-52 |

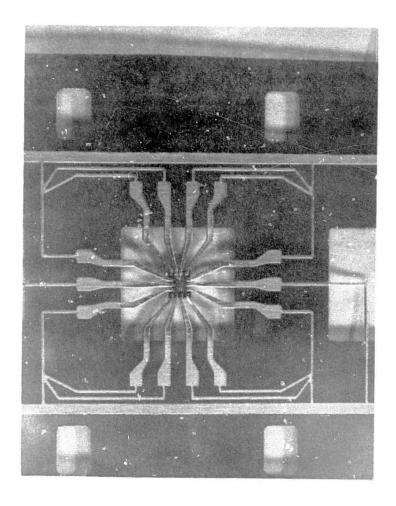

| 2-22   | TTL Device Inner-Lead-Bonded to 16 mm Tape                                                                                                               | 2-53 |

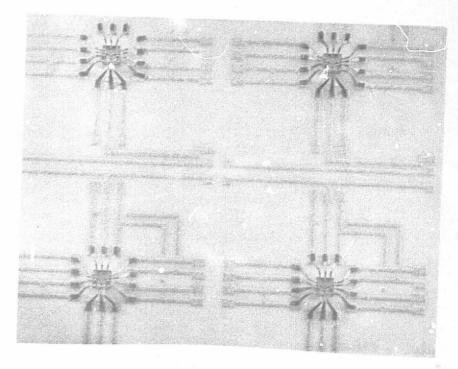

| 2-23   | Inner-Lead-Bonded 82-Pad ECL Devices                                                                                                                     | 2-55 |

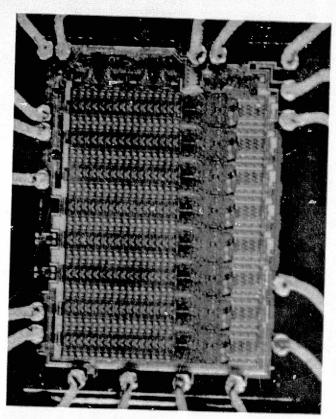

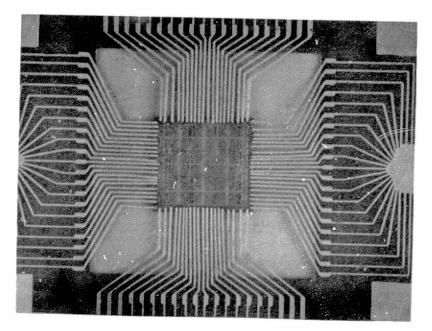

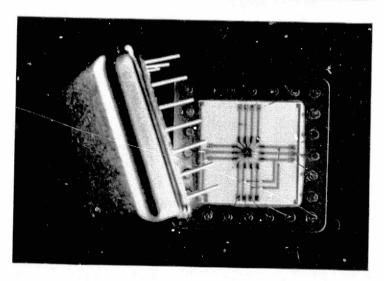

| 2-24   | Array of TTL Devices on Ceramic-Based Thick Film Network                                                                                                 | 2-56 |

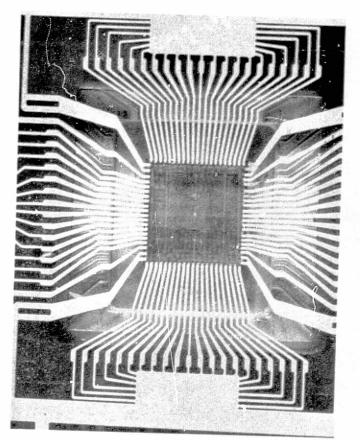

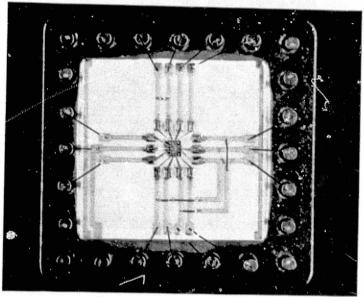

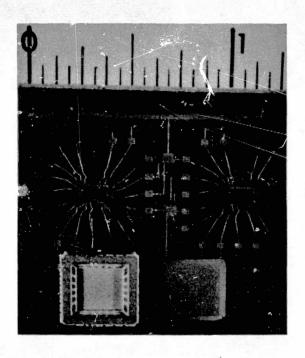

| 2-25   | Environmental Test Packages for TTL Devices                                                                                                              | 2-59 |

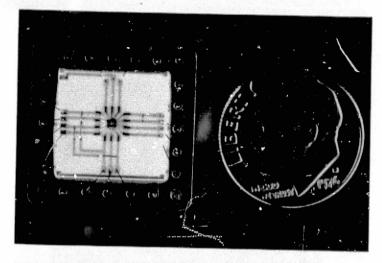

| 2-26   | Hermit Chip Carrier (24 pads) Shown with Metal Lid/<br>Sealing Pre-forms, Adjacent to Tape-Mounted 18-Pad<br>Hughes Type 1824D Micro-Processor RAM Semi- |      |

|        | conductor Device                                                                                                                                         | 2-60 |

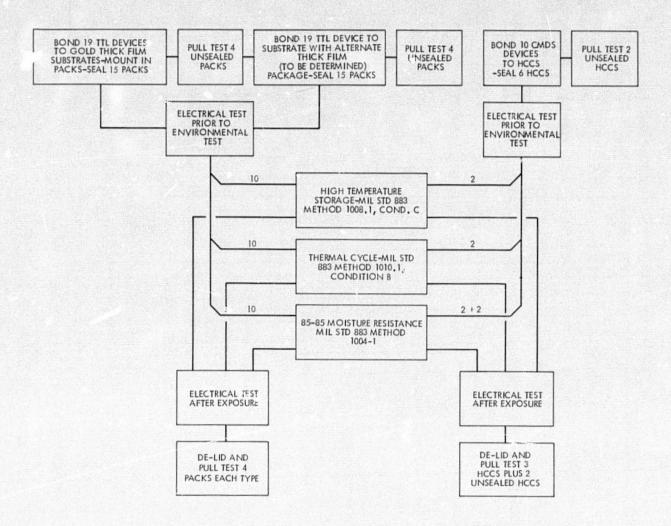

| 2-27   | Environmental Test Matrix                                                                                                                                | 2-62 |

#### LIST OF TABLES

| rable |                                                                            | Page  |

|-------|----------------------------------------------------------------------------|-------|

| 2-1   | Packaging Implementation Sub-Task Breakdown                                | 2-3   |

| 2-2   | Computerized Cost Factors Data Classification                              | 2-4   |

| 2-3   | Task I/II Distribution Between Cost Factors Data and Mathematical Modeling | 2-5   |

| 2-4   | Primary Nonrecurring Cost Factors Associated with PWBs                     | 2-7   |

| 2-5   | Major Manufacturing Cost Factors Involved in Fabrication of PWBs           | 2-8   |

| 2-6   | Primary Nonrecurring Cost Factors Associated with PWB Assembly             | 3-9   |

| 2-7   | Major Manufacturing Cost Factors Involved in PWB Assembly                  | 2-10  |

| 2-8   | PWB Assembly - Production Cost Factors                                     | 2-11  |

| 2-9   | Flow Chart Listing                                                         | 2-13  |

| 2-10  | Substrate Processing — Values of Constants and Parameters                  | 2-15  |

| 2-11  | Assembly and Testing — Values of Constants and Parameters                  | 2-16  |

| 2-12  | Reference Hybrid                                                           | 2-18  |

| 2-13  | Knopp Hardness of Plated Bumps                                             | 2-47  |

| 2-14  | Outer Lead Pull Strengths                                                  | 2-57  |

| 2-15  | Environmental Test Results - TTL Type 5400 Devices                         | 2-61  |

| 3-1   | Recommended Tape Chip Carrier Work Approach — Task B                       | 3 - 3 |

#### 1.0 INTRODUCTION AND SUMMARY

This report summarizes the effort on Contract NAS 8-32607, which involved determination of those factors affecting the cost of electronic subsystems utilizing LSI microcircuits, and development of the most efficient methods for low-cost packaging of LSI devices as a function of density and reliability.

This one-year program has been divided into three Tasks as follows:

#### TASK 1. Cost Factors Study

Perform a cost study to identify all the factors involved in packaged electronic subsystems as a function of density and reliability. The study should encompass LSI devices packaged both by hybrid technology and standard discrete packaging.

#### TASK 2. Study Areas

Based on an analysis of the cost factors determined in Task 1, provide recommendations for study in the area(s) that show the most promise for cost reductions in high density packaging.

#### TASK 3. Packaging Implementation

One specific high cost impact area in hybrid packaging has been LSI chip testing and bonding. Beam-tape technology has been established as a viable and cost saving technique for producing high-volume discrete device packages. Many types of semi-conductors are currently available on beam-tape and, with few exceptions, most semiconductors can be adapted to beam-tape. It is required during this study that a demonstration program be performed to adapt LSI chips on beam-tape for hybrid packaging.

Tasks I and II essentially have been combined to constitute the COST FACTORS STUDY, which has been expanded at NASA request and by mutual consent to include limited mathematical modeling. Both the cost factors

and the mathematical modeling are intended for usage as guidelines for the preparation of mathematical pricing models suitable for computer programming. The combined Tasks I and II previously have been published in the Semi-Annual Report on this contract (Report No. P78-162, dated 10 March 1978). This information is repeated herein, after addition of minor corrections, and expansion in several areas related to process yield.

Task III, a Packaging Implementation program comprising demonstration and testing of tape chip carrier (TGC) processes, was initiated on contract award, in parallel with Tasks I and II. This effort (reported herein) has been completed essentially as proposed and reported during the program, with demonstratable results in all areas except gang burn-in on tape.

Recommendations are included; both for future cost factors study efforts, and for further process refinement related to TCC technology.

#### 2.0 TECHNICAL DISCUSSION

This combination study/development program comprises both the identification of cost factors related to LSI/hybrid technology, and the demonstration of a particular packaging approach: tape chip carrier technology, as applied to the adaptation of LSI chips for hybrid packaging.

The Program Schedule of Figure 2-1 includes the Sub-Tasks involved in both the cost factors and the TCC packaging implementation portions of the program. As indicated in the Introduction and Summary Section, the combined Tasks I/II have been modified somewhat by NASA/Hughes mutual consent, and this report includes results of the modified task.

With respect to Task III, the effort has included TCC tape/wafer process/materials evaluation, inner-lead bonding (ILB) evaluation, outer-lead bonding (OLB) evaluation, test sample fabrication, and environmental testing/data analysis. Table 2-1 is a summary/breakdown of Task III subtasks, indicating qualitatively the degree of progress achieved on each of them.

#### 2. 1 TASKS I AND II - COST FACTORS STUDY

To initiate the required cost factors study involving LSI devices packaged both by hybrid technology and standard discrete parts assembly methods, a survey questionnaire was formulated, and a proposed mailing list was prepared comprising approximately 100 selected LSI packaging experts and hybrid microelectronics managers. When this was reviewed by MSFC personnel, it was determined that interviews with cognizant Hughes personnel, coupled with a literature survey, would be preferable, and that the resulting cost factors data would be more useful than an industry-wide survey in making an initial cost model which could be programmed for computer input.

Figure 2-1. Program schedule - NASA Contract No. NAS8-32607.

# TABLE 2-1. PACKAGING IMPLEMENTATION SUB-TASK BREAKDOWN

CONTRACT NO. NAS8-32607, TASK III

12 AUGUST 1978

|           |                                                                                                                                                                                                            |              | UGUST 1978                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A.        | TAPE PROCESS/MATERIALS EVALUATION PERCENTAGE COMPLETION                                                                                                                                                    | PLAN         | EXECUTI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A.1       | SELECT T <sup>2</sup> L (A), MOS (B), AND ECL (C) VEHICLES                                                                                                                                                 | 20 00 75 100 | 20 00 75 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | PREPARE TAPE WORKSHEETS (A), (B), (C)                                                                                                                                                                      |              | THE RESERVE TO SERVE THE PERSON NAMED IN COLUMN TWO IN COL |

|           | PROCURE MASKS (A), (B), (C)                                                                                                                                                                                | 12500        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | ALIGN/EXPOSE/DEVFLOP/ETCH TAPES (A), (B), (C)                                                                                                                                                              |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | ALIGN/EAFOSE/DEV( COP/ETCH TAPES (A), (B), (C)                                                                                                                                                             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A.5       | FABRICATE UP TO 100 EACH TAPE POSITIONS (A), (B), (C)                                                                                                                                                      |              | a property and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A.6       | PLATE/PUNCH-OUT PLATING LINKS<br>(FOR GOLD PLATING, PLATE PRIOR TO PUNCH-OUT)                                                                                                                              |              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| В.        | WAFER BUMP PROCESS/MATERIALS EVALUATION                                                                                                                                                                    |              | To a control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B.1       | DEMONSTRATE WAFER DC CHARACTERIZATION (B) ONLY                                                                                                                                                             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8.2       | DEMONSTRATE WAFER BUMPING (A), (B), (C) (W-Ti/Au)                                                                                                                                                          |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8.3       | DEMONSTRATE WAFER RE-CHARACTERIZATION (B) ONLY                                                                                                                                                             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8.4       | DEMONSTRATE SHEAR TEST (A), (B), (C) (SAMPLE BASIS)                                                                                                                                                        | 1000         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| C.<br>C.1 | INNER-LEAD BONDING EVALUATION PROCURE ILB COLLETS (THERMODES AS REQUIRED)                                                                                                                                  |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C.2       | MOUNT AND SAW WAFERS (A), (B), (C)                                                                                                                                                                         |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C.3       | DEMONSTRATE ILB (A), (B), (C)) (APPROXIMATELY 40 TAPE POSITIONS EACH)                                                                                                                                      |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C.4       | CHECK-OUT PULL-STRENGTH                                                                                                                                                                                    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | (EXCISE SAMPLES AND DESTRUCTIVE-TEST)                                                                                                                                                                      |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| F         | SAMPLE TEST/BURN-IN STUDY                                                                                                                                                                                  |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| F.1       | DEMONSTRATE GANG BURN-IN (A) ONLY                                                                                                                                                                          | - 8          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | (CONTROL SAMPLE NOT BURNED-IN)                                                                                                                                                                             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| F.3       | PROCURE CUSTOM TAPE PROBER ( (B) AND (CI )  DEMONSTRATE FUNCTIONAL TESTING ON TAPE (A) AND (B) (CONTROL SAMPLE NOT FUNCTIONALLY TESTED)                                                                    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| E.        | TEST NETWORK FABRICATION                                                                                                                                                                                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| E.1       | FABRICATE TEST NETWORKS FROM EXISTING SCREENS (A) ONLY (10 FRITTED PD-Ag, 10 MIXED-PHASE GOLD; 16 CHIP POSITIONS PER NETWORK)                                                                              |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| E.2       | PROCURE 10 CUSTOM HERMETIC CHIP CARRIERS (HCC's FROM EXISTING HUGHES STOCK (B) ONLY (W-Ni-Au)                                                                                                              | TOWN.        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

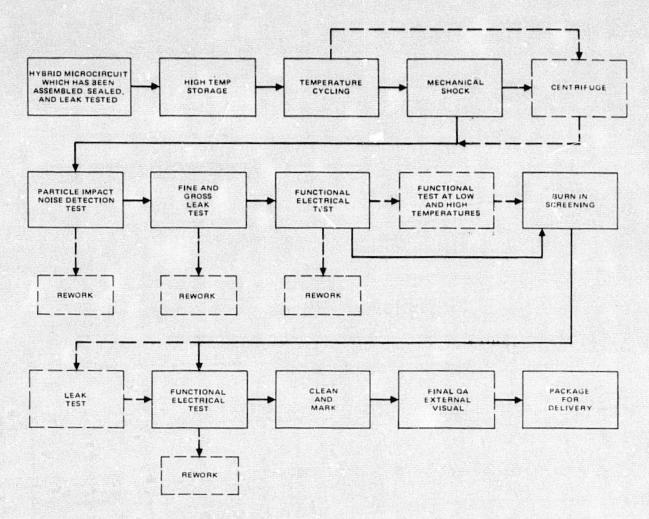

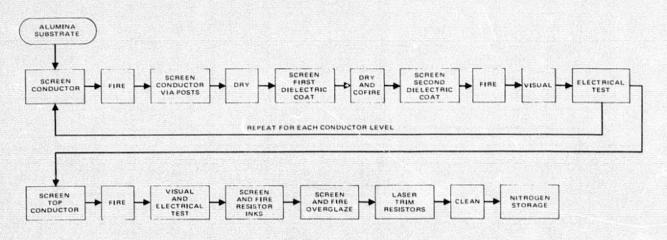

| D.        | OUTER-LEAD BONDING EVALUATION                                                                                                                                                                              |              | lar man                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |