NGR-14-005-181

(NASA-CR-158647) A ROCKET-BORNE N79-24571

DATA-MANIPULATION EXPERIMENT. USING A

MICROPROCESSOR: (Illinois Univ.), 112 p

HC A06/MF A01 CSCL 04A Unclas

G3/46 22317

# AERONOMY REPORT NO. 84

# A ROCKET-BORNE DATA-MANIPULATION EXPERIMENT, USING A MICROPROCESSOR

by L. L. Davis L. G. Smith H. D. Voss

April 1, 1979

Library of Congress ISSN 0568-0581

Aèronomy Laboratory

Department of Electrical Engineering

University of Illinois Urbana, Illinois

#### CITATION POLICY

\_

The material contained in this report is preliminary information circulated rapidly in the interest of prompt interchange of scientific information and may be later revised on publication in accepted aeronomic journals. It would therefore be appreciated if persons wishing to cite work contained herein would first contact the authors to ascertain if the relevant material is part of a paper published or in process.

# AERONOMY REPORT NO. 84

# A ROCKET-BORNE DATA-MANIPULATION EXPERIMENT USING A MICROPROCESSOR

bу

L. L. Davis L. G. Smith

H. D. Voss

April 1, 1979

Supported by-National Aeronautics and Space Administration Grant NGR-14-005-181 Aeronomy Laboratory

Department of Electrical Engineering

University of Illinois

Urbana, Illinois

#### ABSTRACT

This report describes the development of a data-manipulation experiment using a Z-80 microprocessor. The instrumentation is included in the payloads of two Nike Apache sounding rockets used in an investigation of energetic particle fluxes. The data from an array of solid-state detectors and an electrostatic analyzer is processed to give the energy spectrum as a function of pitch angle.

The experiment performed well in its first flight test: Nike Apache 14.543 was launched from Wallops Island at 2315 EST on 19 June 1978. The system has been designed to be easily adaptable to other data-manipulation requirements and some suggestions for further development are included.

# TABLE OF CONTENTS

|                   |                       |       |     |   |   |   |  |    |    |    |  | P | age |

|-------------------|-----------------------|-------|-----|---|---|---|--|----|----|----|--|---|-----|

| ABSTRACT          |                       |       |     |   | • |   |  |    |    | •  |  |   | 11i |

| TABLE OF CONTENTS |                       |       |     |   |   |   |  |    |    | ıν |  |   |     |

| LIST OF TABLES    |                       |       |     |   |   |   |  |    |    |    |  |   | vi  |

| LIST OF FIGURES . |                       |       |     |   |   |   |  |    |    | •  |  |   | vıi |

| 1. INTRODUCTION.  |                       |       |     |   |   |   |  |    |    |    |  |   | 1   |

| 2. ENERGETIC PAR  | TICLE EXPERIMENTS     |       |     |   |   |   |  |    |    |    |  |   | 3   |

| 2.1 Introduc      | tion                  |       |     |   |   |   |  |    |    |    |  |   | 3   |

| 2.2 Energeti      | c Particle Spectromet | ter.  |     |   |   |   |  |    |    | •  |  |   | 3   |

| 2 3 Electros      | tatic Analyzer        |       |     |   |   |   |  |    |    |    |  |   | 8   |

| 3. GENERAL DESCR  | IPTION OF THE EXPERIM | MENT  |     |   |   |   |  |    |    |    |  |   | 10  |

| 3.1 Z-80 Mic      | rocomputer            |       |     |   |   |   |  |    |    |    |  |   | 10  |

| 3.2 Peripher      | al Devices            |       |     |   |   |   |  | ٠. | .* |    |  |   | 12  |

| 3.3 Data Man      | ipulation             |       | •   |   |   |   |  |    |    |    |  |   | 14  |

| 4. HARDWARE       |                       |       |     |   |   |   |  |    |    |    |  |   | 20  |

| 4.1 CPU-Memo      | ry Board              |       |     |   |   |   |  |    |    |    |  |   | 20  |

| 4.1.1 M           | emory address decodin | ıg .  |     |   |   |   |  |    |    |    |  |   | 20  |

| 4 1.2 R           | eset circuit          |       |     |   |   |   |  |    |    |    |  |   | 27  |

| 4.1.3 C           | lock                  |       |     |   |   |   |  |    |    |    |  |   | 27  |

| 4.1.4 R           | ead-write control     |       |     |   |   |   |  |    |    |    |  |   | 27  |

| 4.2 PIO #1 α      | nd CTC Board          |       |     |   |   |   |  |    |    |    |  |   | 27  |

| 4.3 A/D and       | FIFO Board            |       |     | • |   |   |  |    |    |    |  |   | 31  |

| 4.4 PIO #2 .      |                       |       |     |   |   | ٠ |  |    |    |    |  |   | 37  |

| 5. SOFTWARE       |                       |       |     |   |   |   |  |    |    |    |  |   | 41  |

| 5.1 Z-80 Arc      | hitecture             |       |     | • |   |   |  |    |    |    |  |   | 41  |

| 5.2 Data-Man      | ipulation Software    |       |     |   |   |   |  |    |    |    |  |   | 44  |

| 5.2.1 I           | nitialization         |       |     |   |   |   |  |    |    |    |  |   | 44  |

| 5.2.2 I           | nput routine          |       |     |   |   |   |  |    |    |    |  |   | 47  |

| 5.2.3 <i>O</i>    | utput routine         |       |     |   |   |   |  |    |    |    |  |   | 49  |

| 6. THE SDB-80 BO  | ARD AND THE EPROM PRO | OGRAM | MER |   |   |   |  |    |    |    |  |   | 59  |

| 6.1 The SDB-      | 80 Board              |       |     |   |   |   |  |    |    |    |  |   | 59  |

| 6.2 EPROM Pr      | ogrammer              |       |     |   |   |   |  |    |    |    |  |   | 62  |

| 6.2.1 P           | rogramming waveforms  |       |     | • |   |   |  |    |    |    |  |   | 62  |

| 6.2.2 P           | rogrammer hardware .  | •     |     |   |   |   |  |    |    |    |  |   | 62  |

|       |       |         |                                                   |     |     |    | Page |

|-------|-------|---------|---------------------------------------------------|-----|-----|----|------|

|       |       | 6.2.3   | SDB-80 modifications                              |     | •   |    | 65   |

|       |       | 6.2.4   | EPROM-programmer software                         |     | •   | •  | 67   |

|       |       | 6.2.5   | Operation of the programmer                       |     |     | •  | 73   |

| 7. I  | FLIGH | IT PERF | FORMANCE                                          |     |     | •  | 75   |

| 8. (  | CONCI | LUSION  | AND RECOMMENDATIONS FOR FUTURE WORK               |     | •   | •  | 80   |

| 8     | 3.1   | Concli  | usion                                             |     |     | •  | 80   |

| 8     | 3.2   | Sugges  | stions for Future Work                            |     |     | •  | 80   |

|       |       | 8.2.1   | The data-manipulation program                     |     |     | •  | 80   |

|       |       | 8.2.2   | The MSD circuit                                   |     |     | ٠  | 80   |

|       |       | 8.2.3   | Automatic reset circuit                           |     | •   | •  | 83   |

|       |       | 8.2.4   | Circuit layout                                    |     | •   | •  | 83   |

|       |       | 8.2.5   | The development system                            |     | •   | •  | 83   |

|       |       | 8.2.6   | Other applications of the rocket-borne data-manip | ıla | tio | on |      |

|       |       |         | experiment                                        |     | •   | •  | 86   |

|       |       | 8.2.7   | Data-transmission systems                         |     |     | •  | 86   |

|       |       | 8.2.8   | Applications in ground-based data processing      |     |     | •  | 86   |

| REFEI | RENCI | ES      |                                                   |     |     |    | 89   |

| APPE  | NDIX  | I. Cá   | ircuit Schematics                                 |     |     |    | 90   |

| APPE  | NDIX  | II.1    | Data-Manipulation Program                         |     | -   |    | 94   |

| APPE  | NDIX  | II.2    | EPROM Programmer                                  |     |     |    | 97   |

# LIST OF TABLES

| Table |                                                               | Page |

|-------|---------------------------------------------------------------|------|

| 1.1   | Abbreviations                                                 | 2    |

| 2.1   | Important characteristics of the six solid-state detectors in |      |

|       | the payloads of Nike Apaches 14.542 and 14.543                | 7    |

| 4.1   | Z-80 Control signals                                          | 24   |

# LIST OF FIGURES

| Figure |                                                                        | Page |

|--------|------------------------------------------------------------------------|------|

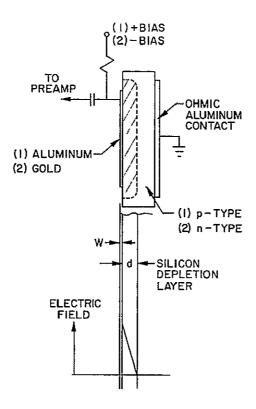

| 2.1    | Surface barrier detector. Note the differences between the             |      |

|        | detectors with surface layers of (1) aluminum and (2) gold             | 5    |

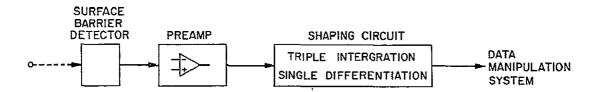

| 2.2    | Major components of the solid-state detector instrumentation .         | 6    |

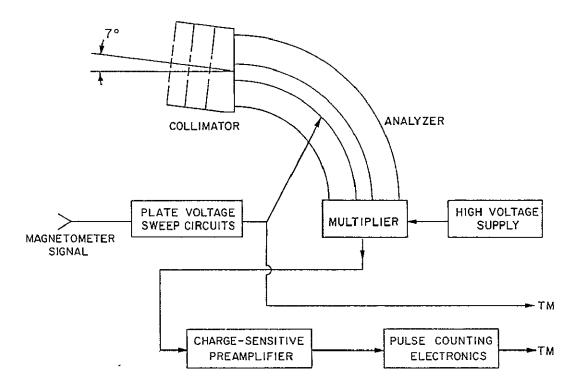

| 2.3    | Block diagram of the electrostatic analyzer. The acceptance            |      |

|        | angle of the collimator is exaggerated                                 | 9    |

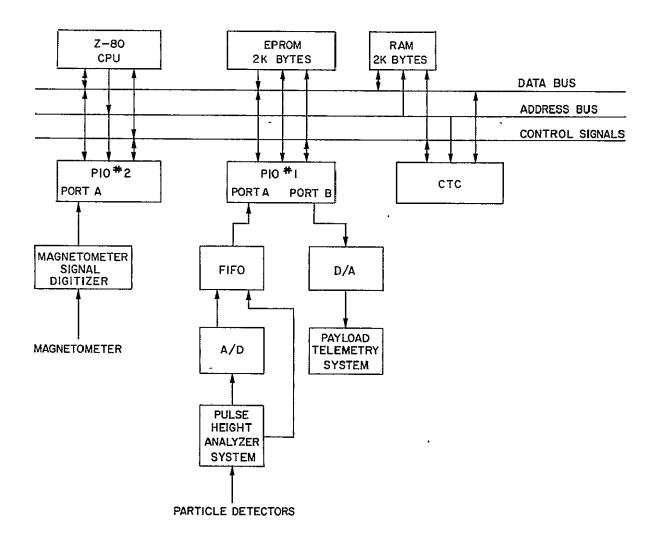

| 3.1    | The data-manipulation system                                           | 11   |

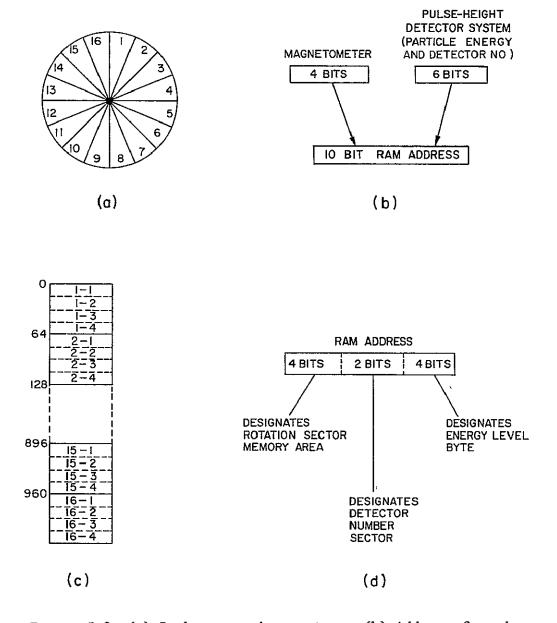

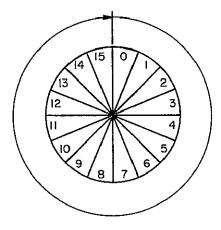

| 3.2    | (a) Rocket rotation sectors; (b) Address formed from the two           |      |

|        | data words; (c) Memory (d) RAM address                                 | 15   |

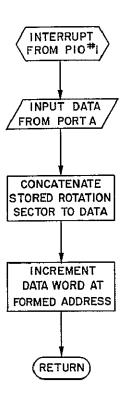

| 3.3    | Input routine algorithm                                                | 16   |

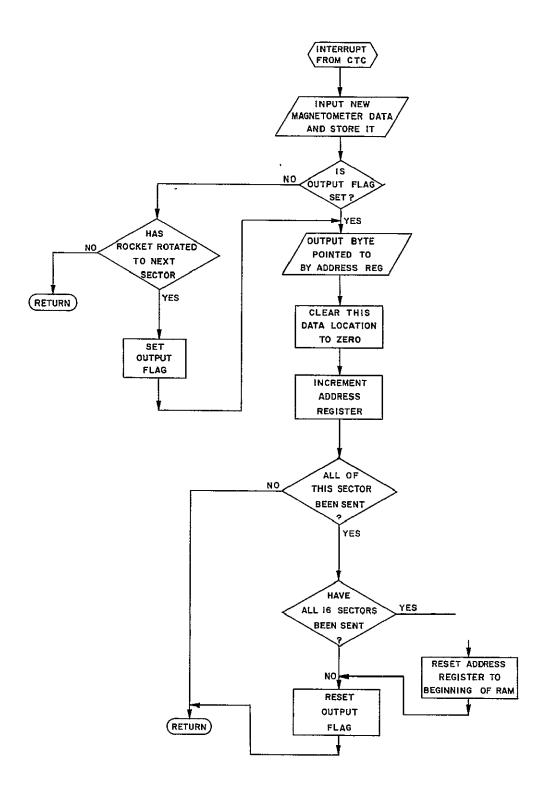

| 3.4    | Output routine algorithm                                               | 17   |

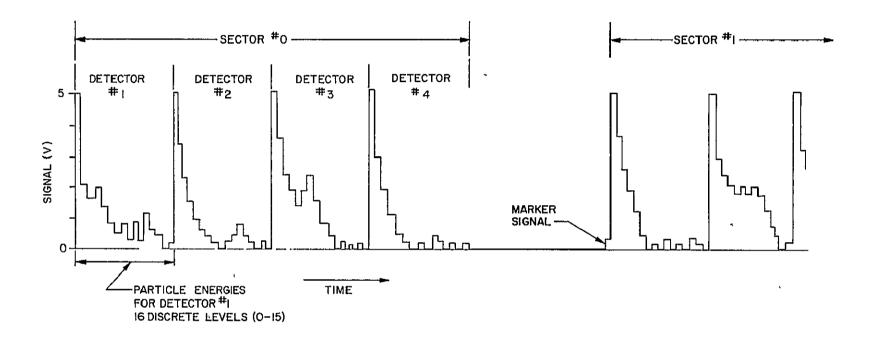

| 3.5    | Example of output from D/A. The ordinate is the telemetered            |      |

|        | signal (in volts) and is proportional to number of units               |      |

|        | (5V $\equiv$ 32 particles) in the accumulation period                  | 19   |

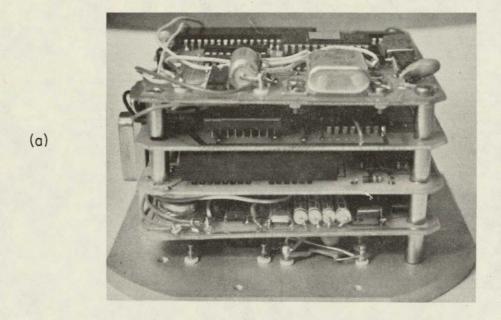

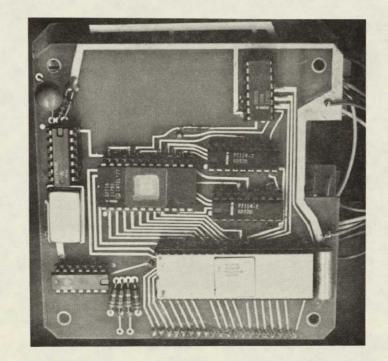

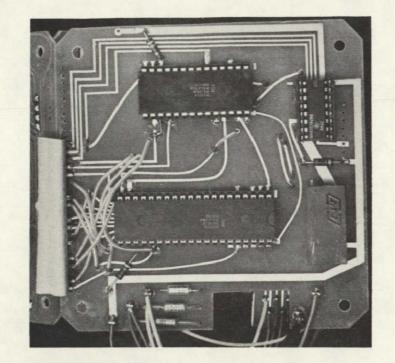

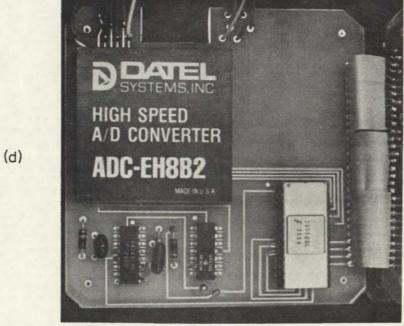

| 4.1    | Data-manipulation system circuit boards. (a) boards connected          |      |

|        | for installing in payload, (b) CPU-memory board, (c) PIO #1-CTC        |      |

|        | board, and (d) A/D FIFO board                                          | 21   |

| 4.2    | Location of the data-manipulation system in the payload of             |      |

|        | Nike Apache 14.542                                                     | 23   |

| 4.3    | The CPU-Memory board. An arrow on one end of a line indicates          |      |

|        | a single direction signal; arrows on both ends indicate a              |      |

|        | bidirectional signal; dotted arrows indicate some lines go in          |      |

|        | one direction and some the other direction                             | 25   |

| 4.4    | Address decoding: (a) Connection of the 8205 one-of-eight              |      |

|        | <pre>decoder; (b) Truth table (X = don't care state); (c) Memory</pre> |      |

|        | addresses                                                              | 26   |

| 4.5    | Reset circuit                                                          | 28   |

| 4.6    | System clock                                                           | 29   |

| 4.7    | The PIO#1-CTC board. The arrows have the same meaning as in            |      |

|        | Figure 4.3                                                             | 30   |

| 4.8    | PIO block diagram (MOSTEK Z80 Manual)                                  | 32   |

| 4.9    | Timing diagrams: (a) PIO#1 Port A handshake line timing;               |      |

|        | (b) A/D control signal timing; (c) FIFO handshake line timing.         | 33   |

| Figure |                                                                 | Page |

|--------|-----------------------------------------------------------------|------|

| 4.10   | The A/D-FIFO board. The arrows have the same meaning as in      |      |

|        | Figure 4.3                                                      | 34   |

| 4.11   | The circuit and timing diagram for the input to the FIFO and    |      |

|        | the ready-for-input status signal                               | 36   |

| 4.12   | The circuit and timing diagram for input to PIO#1 from the      |      |

|        | FIFO                                                            | 38   |

| 4.13   | The PIO#2 board. The arrows have the same meaning as in         |      |

|        | Figure 4.3                                                      | 39   |

| 5.1    | Z80-CPU register configuration (MOSTEK Z80 Micro-Reference      |      |

|        | Manual)                                                         | 42   |

| 5.2    | Block diagrams of (a) one port of a PIO and (b) one channel of  |      |

|        | the CTC (MOSTEK Z80 Manual)                                     | 43   |

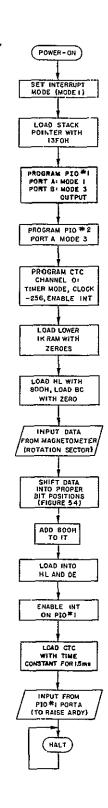

| 5.3    | Flow chart of the initialization section                        | 45   |

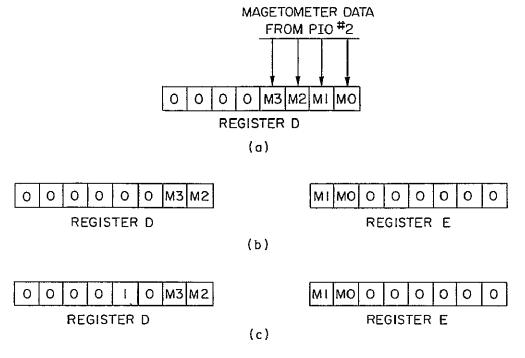

| 5.4    | Magnetometer data bit positioning: (a) Data bits are put into   |      |

|        | register D; (b) shifted right two places into top two bits of   |      |

|        | E; (c) 800H is then added                                       | 46   |

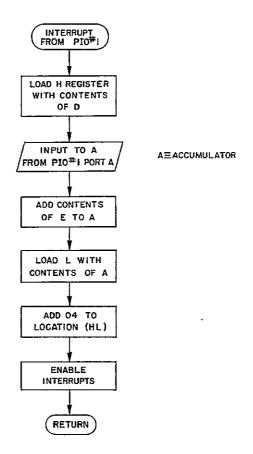

| 5.5    | Flow chart of the input routine                                 | 48   |

| 5.6    | Output section of the software                                  | 50   |

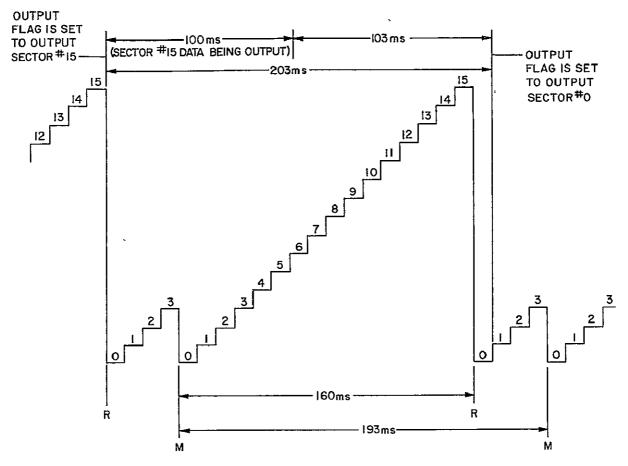

| 5.7    | Here and in the following figure the output of the MSD is       | •    |

|        | represented as an analog signal to show the relationship        |      |

|        | between the rocket spin period and the counter cycle time.      |      |

|        | The case shown here is for a 5.18 Hz spin rate (i.e., 193 ms    |      |

|        | period). 10 ms must be added to the spin cycle time to get      |      |

|        | the interval between the times when the output flag is set      |      |

|        | between succeeding sections. Since the counter is incremented   |      |

|        | at 100 Hz, there are 20 increments between the times the        |      |

|        | counter is reset (the last count has a shorter interval, 3 ms). |      |

|        | This diagram also represents the situation for a spin period    |      |

|        | greater than 193 ms and for no magnetometer signal. R indicate  | S    |

|        | indicates the internal reset of the 4-bit counter and M the     |      |

|        | reset of the counter by the magnetometer                        | . 52 |

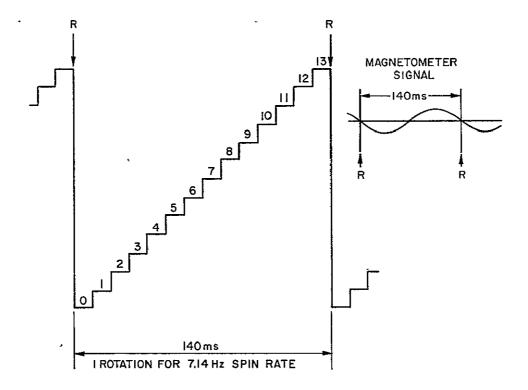

| 5.8    | 7.14 Hz spin rate causes the magnetometer signal digital        |      |

|        | representation to have 14 levels (refer to Figure 5.7).         |      |

|        | indicates reset of 4-bit counter by the magnetometer            | 53   |

| Figure |                                                                | Page       |

|--------|----------------------------------------------------------------|------------|

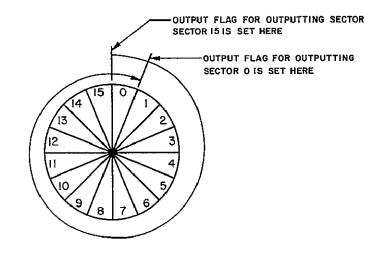

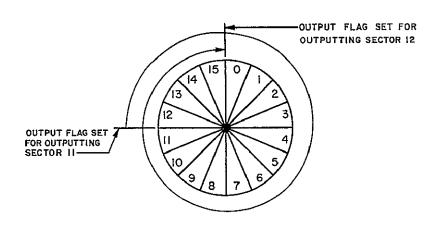

| 5.9    | The interval between the output flag being set to output       |            |

|        | consecutive sectors depends on which sector it is being set    |            |

|        | for. (a) $1 + 1/16$ revolutions occur between when the output  |            |

|        | flag is set to output consecutive sectors except for 12, 13,   |            |

|        | and 14. (b) The interval between the output flag being set     |            |

|        | for sectors 11 and 12 is 1 + 4/16 revolutions. (c) The         |            |

|        | interval between the output flag being set for sectors 12 and  |            |

|        | 13, sectors 13 and 14, and sectors 14 and 15 is exactly one    |            |

|        | revolution                                                     | 55         |

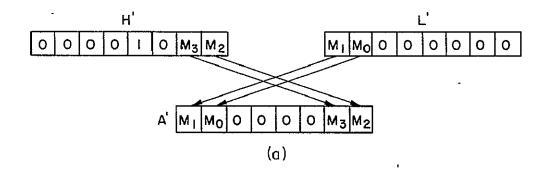

| 5.10   | The marker signal is obtained from HL' and is put in A' for    |            |

|        | output to D/A. (a) Sector number in HL' is put in A'.          |            |

|        | (b) Three shifts are then done to put data in proper bit       |            |

|        | positions for output to the D/A (i.e., two right circular      |            |

|        | shifts and one right shift with a zero put into the 7th bit) . | 57         |

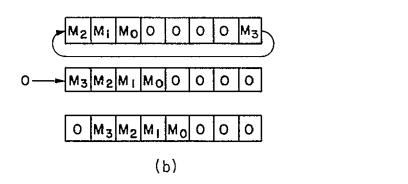

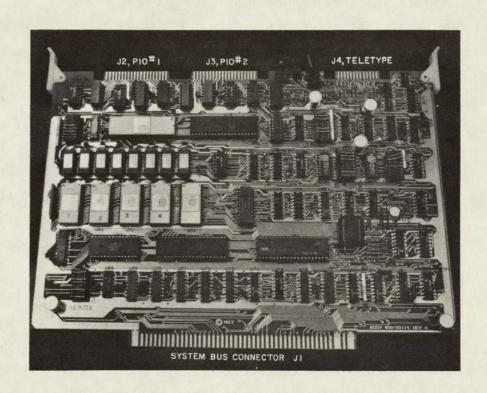

| 6.1    | The EPROM programmer and the teletype connected to the MOSTEK  |            |

|        | SDB-80 board. This system was used to develop the data-        |            |

|        | manipulation system software                                   | 60         |

| 6.2    | MOSTEK SDB-80 Board                                            | 61         |

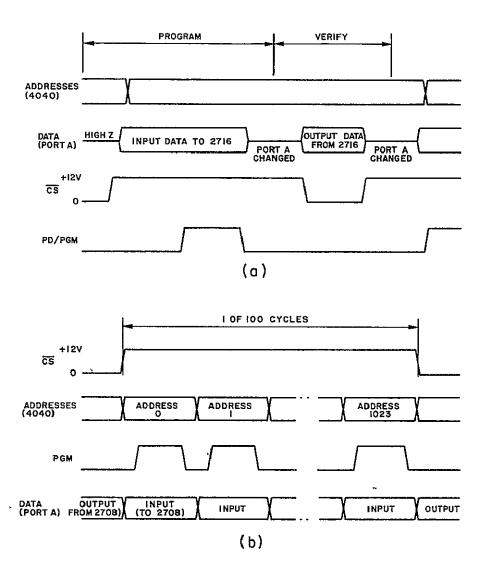

| 6.3    | Programming waveforms. (a) 2716 program and verify waveforms.  |            |

|        | (b) 2708 program waveforms                                     | 63         |

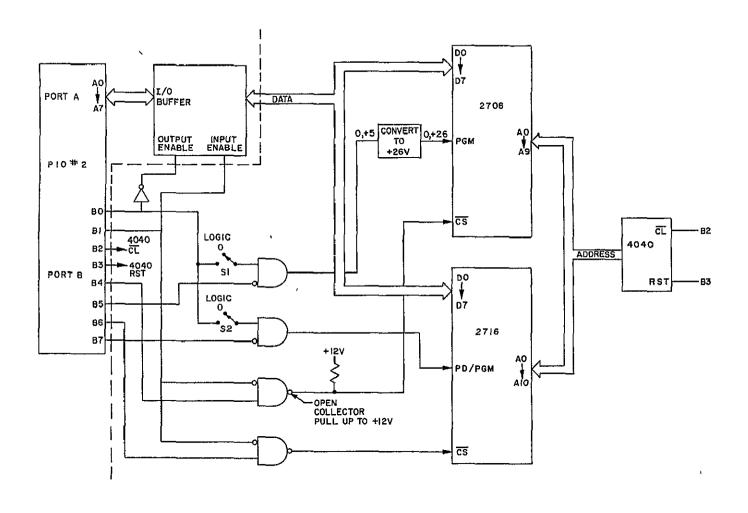

| 6.4    | 2708 and 2716 EPROM programmer. Everything to the left side    |            |

|        | of the dotted line is on the SDB-80 board                      | 64         |

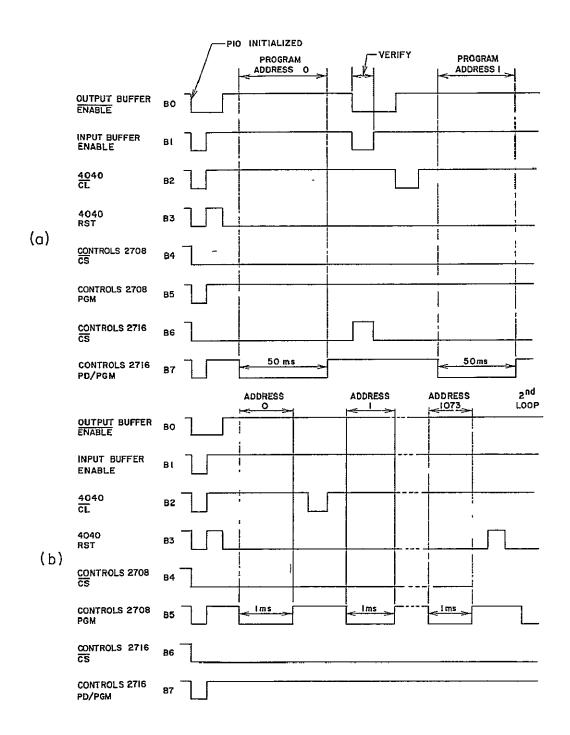

| 6.5    | Port B timing diagram. (a) 2716 program and verify. (b) 2708   |            |

|        | program                                                        | 66         |

| 6.6    | Connection of the 2716 EPROM that contains the programmer      |            |

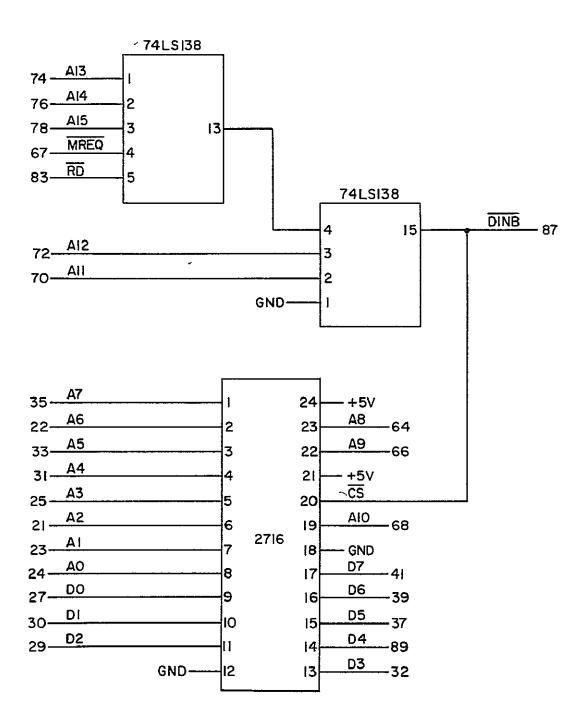

|        | software                                                       | 68         |

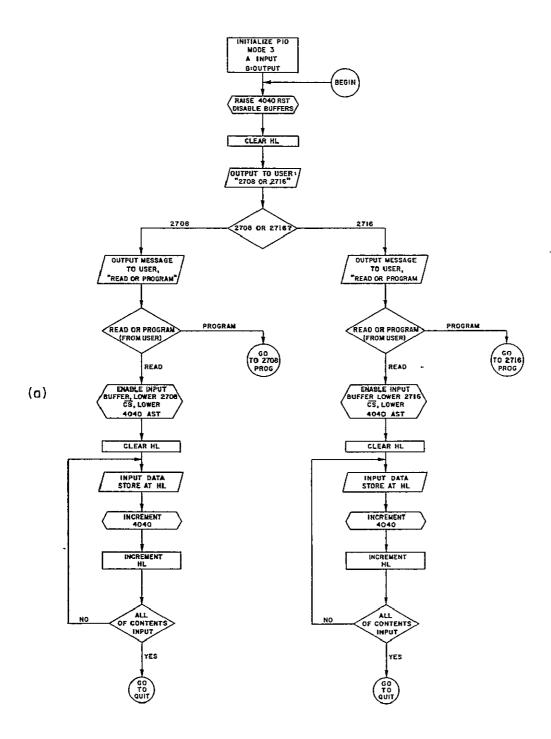

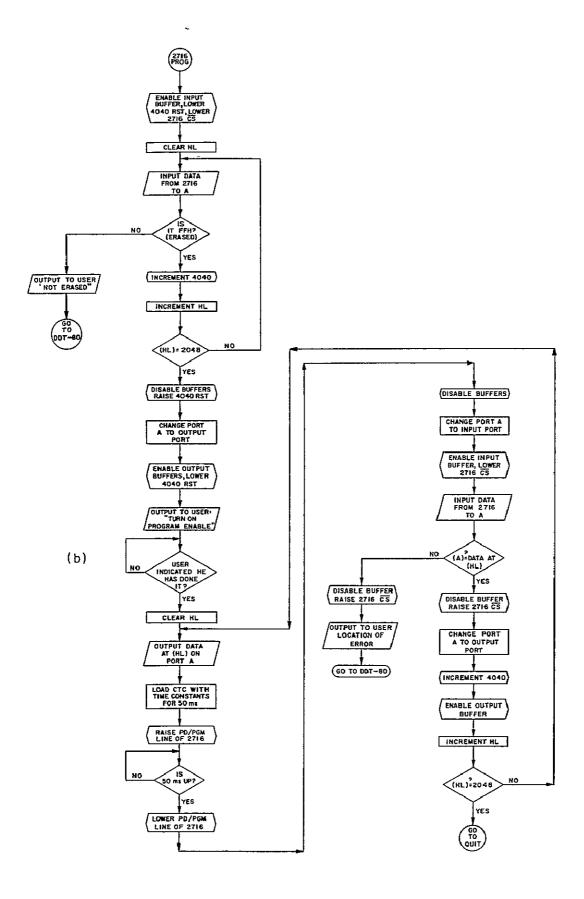

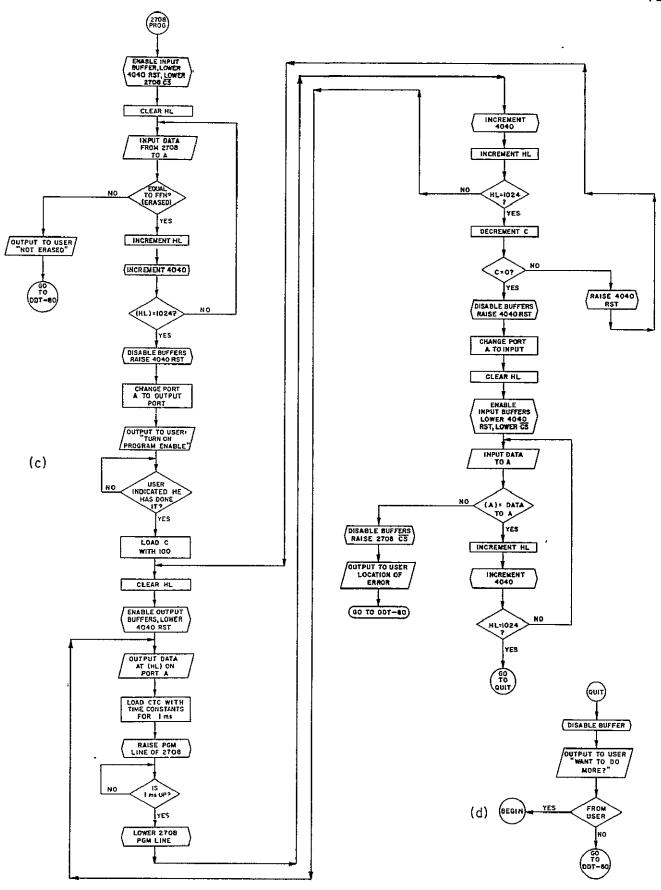

| 6.7    | Flow chart of the EPROM programmer software. (a) The           |            |

|        | initializaton and read routines. (b) 2716 program routine.     |            |

|        | (c) 2708 program routine. (d) QUIT routine                     | 69         |

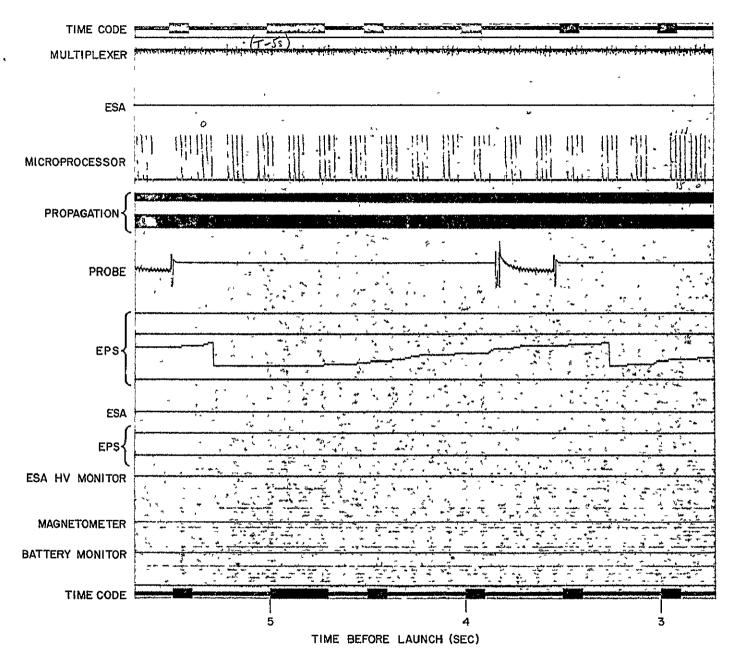

| 7.1    | Section of chart record from Nike Apache 14.543: 5 seconds     |            |

|        | before launch                                                  | <b>7</b> 6 |

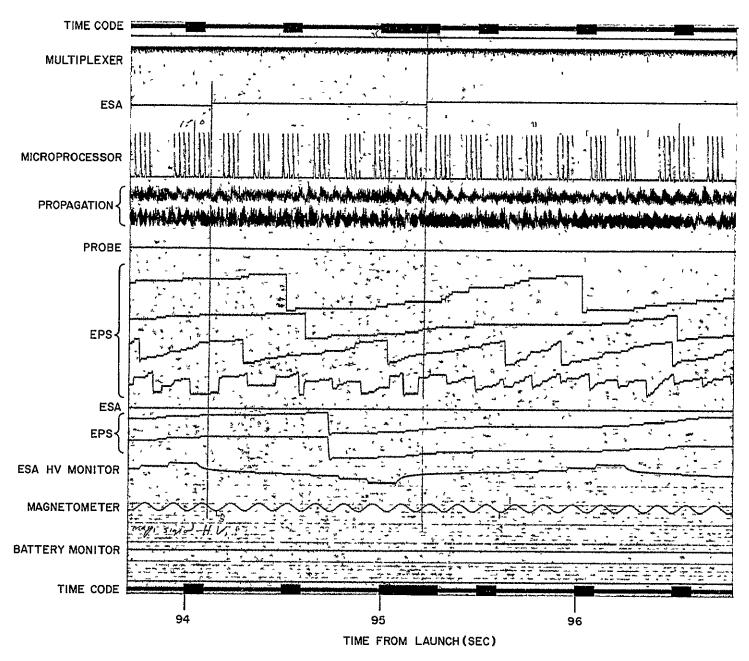

| 7.2    | Section of chart record from Nike Apache 14.543: 95 seconds    |            |

|        | after launch                                                   | 77         |

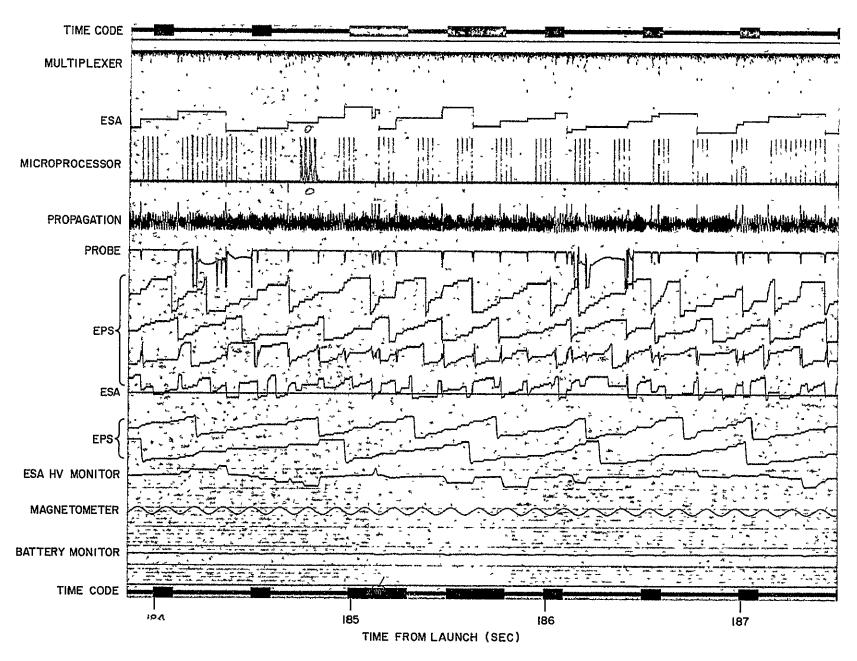

| 7.3    | Section of chart record from Nike Apache 14.543: 185 seconds   |            |

|        | after launch                                                   | 79         |

| Figure |                                                                | Page |  |  |  |  |  |  |  |

|--------|----------------------------------------------------------------|------|--|--|--|--|--|--|--|

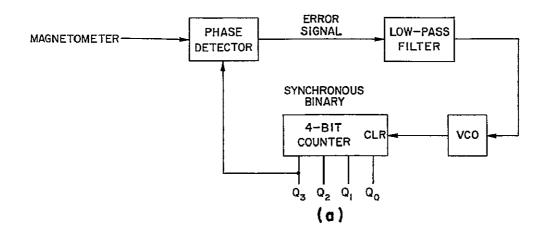

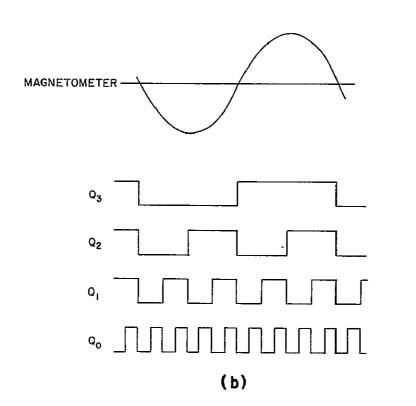

| 8.1    | Suggestion for improvement in the MSD system. (a) Block        |      |  |  |  |  |  |  |  |

|        | diagram showing how the system can be phase locked to the      |      |  |  |  |  |  |  |  |

|        | magnetometer. (b) Timing diagram of the counter compared to    |      |  |  |  |  |  |  |  |

|        | the magnetometer signal                                        | 82   |  |  |  |  |  |  |  |

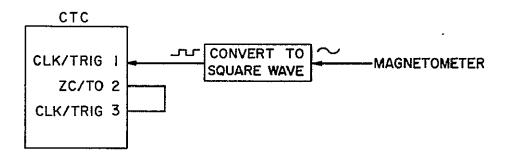

| 8.2    | Using the CTC to generate the MSD signal                       | 84   |  |  |  |  |  |  |  |

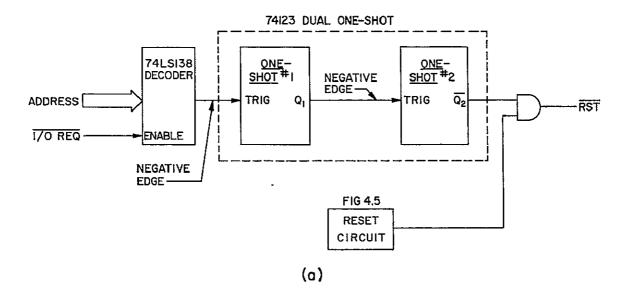

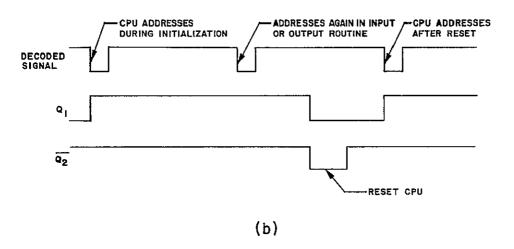

| 8.3    | (a) Block diagram of the automatic reset circuit. (b) Timing   |      |  |  |  |  |  |  |  |

|        | diagram showing when the CPU would be reset                    | 85   |  |  |  |  |  |  |  |

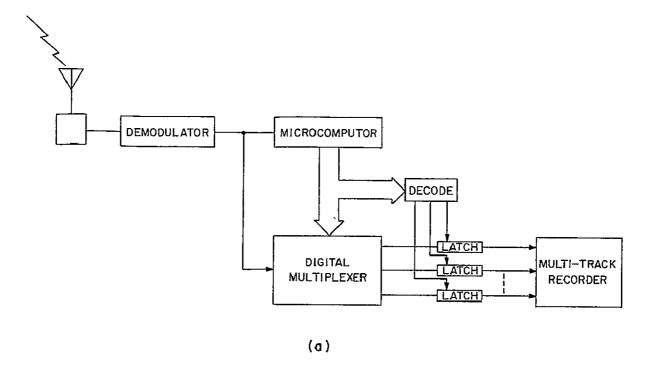

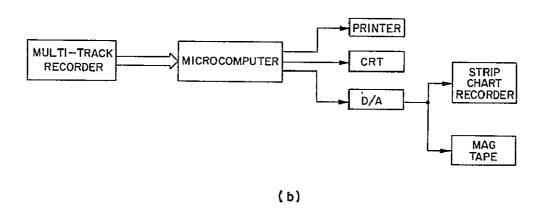

| 8.4    | Ground-based data-reduction system. (a) Real-time data-logging |      |  |  |  |  |  |  |  |

|        | system. (b) Off-line data-reduction system                     | 88   |  |  |  |  |  |  |  |

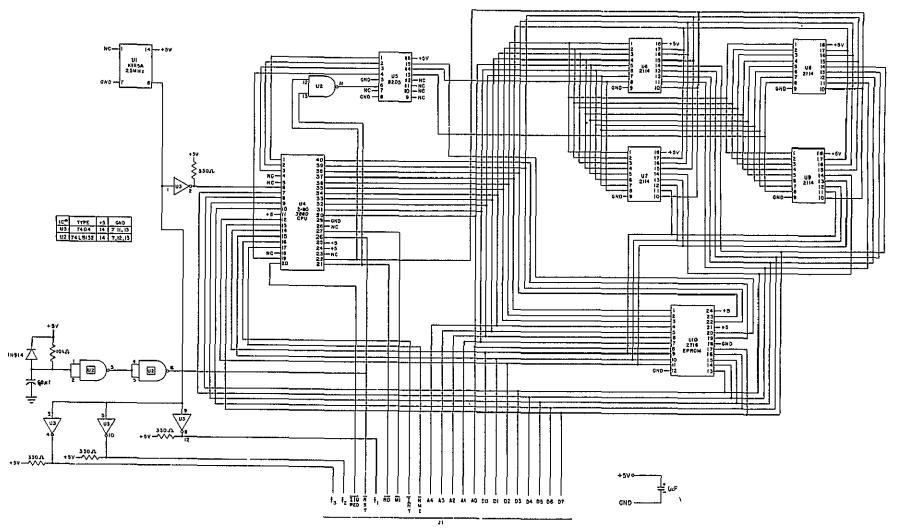

| 1.1    | CPU-memory board                                               | 90   |  |  |  |  |  |  |  |

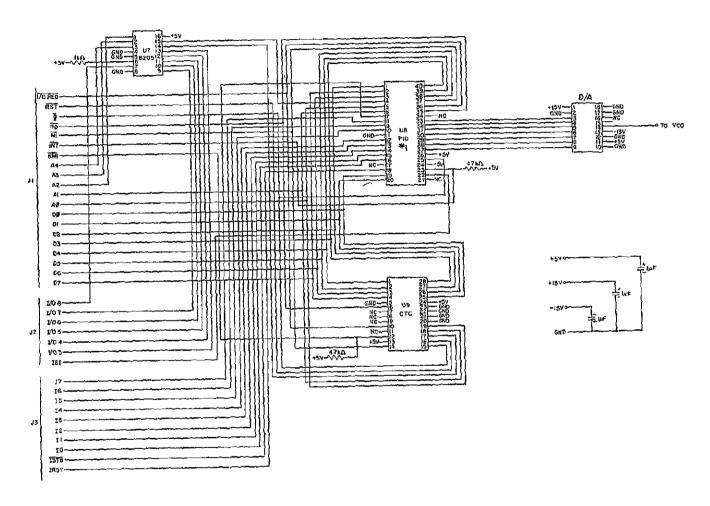

| I.2    | PIO#1 and CTC board                                            | 91   |  |  |  |  |  |  |  |

| 1.3    | A/D and FIFO board                                             | 92   |  |  |  |  |  |  |  |

| I.4    | EPROM programmer                                               | 93   |  |  |  |  |  |  |  |

|        |                                                                |      |  |  |  |  |  |  |  |

#### 1. INTRODUCTION

This report describes in detail the development of a rocket-borne datamanipulation experiment designed to process data from an array of solid-state

detectors and an electrostatic analyzer into a form giving the energy spectrum

as a function of pitch angle. The information provided by the system will aid

in further study of energetic particles in the E region of the ionosphere.

Previous phases of the investigation have been described in reports by Voss

and Smith [1974, 1977] and in papers by Smith et al. [1974], Geller et al.

[1975] and Smith and Voss [1976].

The energetic particle experiments in the rocket payloads are described in Chapter 2. These provide the input to the data-manipulation experiment.

A general description of the data-manipulation experiment is given in Chapter 3. The Z-80 microcomputer, the nucleus of the system, is described together with the devices used to interface the detectors to it. The hardware configuration is shown in block diagram form. The input and output algorithms used in the software are shown and a description is given of the format in which data are output from the system.

The hardware and software are described in detail in Chapters 4 and 5, respectively. The four printed circuit boards that contain the data-manipulation experiment are described. Timing diagrams of the interface circuits are presented and an explanation is given of the timing logic. The software is shown in an instruction-level flow chart, and the effects of various parameters in the software are described. A feature of the design is the ability of the experiment to accept a range of rocket spin rates.

Chapter 6 contains a description of the equipment for developing the software; the MOSTEK software development board (SDB-80) was used. The chapter also includes details on the design and operation of the EPROM programmer.

In Chapter 7 the performance of the data-manipulation experiment during the flight of Nike Apache 14.543 is discussed. Some actual data from the flights are presented to show that the system fulfilled its design goal.

In Chapter 8 suggestions for future work are given. Some improvements to the present system in terms of both hardware and software are included. Possible uses of microprocessors in other experiments and in the telemetry system are suggested in a block diagram form.

Table 1.1 contains a glossary of abbreviations used in the text and figures of this report.

### Table 1.1

#### Abbreviations

A/D analog-to-digital

CPU central processing unit

CTC counter-timer circuit\*

DIP dual in-line package

EPROM erasable programmable read-only memory

EPS energetic particle spectrometer

ESA electrostatic analyzer

FIFO first-in first-out memory

IEI interrupt enable input

I/O input-output

LSI large-scale integration

MOS metal-oxide semiconductor

MSD magnetometer-signal digitizer

PHA pulse-height analyzer

PIO parallel input-output circuit\*

RAM random access memory

<sup>\*</sup>Circuits used in the Z-80 microcomputer

#### 2. ENERGETIC PARTICLE EXPERIMENTS

#### 2.1 Introduction

The data-manipulation experiment in the rocket payload receives data from an energetic particle spectrometer (EPS) and an electrostatic analyzer (ESA). The function of these two types of particle detectors is to provide a broadband spectral analysis of energetic particles (including electrons and protons) which are believed to be important as an ionization source in the nighttime E region. The energetic particle spectrometer is used for the higher energies and the electrostatic analyzer for the lower energies.

The energetic particle spectrometer and electrostatic analyzer experiments prepared for Nike Apache payloads 14.542 and 14.543 are described in this chapter. The objective here is to explain the origin and nature of the signals which are the input to the data-manipulation experiment.

It should be noted that the payloads each include, in addition to the data-manipulation experiment described in this report, two other systems for processing data from the particle detectors. One is a relatively simple system which generates a staircase waveform; this is particularly valuable for rapid evaluation of the performance of the detectors. The system has been used in previous payloads and is described in *Voss and Smith* [1974].

The other system uses a multiplexer followed by a sample-and-hold circuit. This was developed for the payloads of Nike Apaches 14.542 and 14.543. It is described in detail in *Leung et al.* [1979].

The three systems involve some redundancy both for protection against instrumentation malfunction and to allow intercomparison of their performance. Only those circuits which are relevant to the microcomputer data-manipulation experiment will be described in the following sections.

# 2.2 Energetic Particle Spectrometer

The energetic particle spectrometer (EPS) comprises a group of six solidstate detectors in each of the payloads with each detector selected for a particular objective. The detectors are oriented in several directions relative to the payload spin axis and as a group will resolve the energy spectrum between 12 and 400 keV. The data obtained from the detectors can be used to identify the particles as electrons, protons or heavier nuclei.

The solid-state detectors are so-called surface barrier devices with a depletion depth of 300  $\mu m$  and a sensitive area of 50  $mm^2$ . They are manufactured by Ortec Inc. A surface-barrier detector is a reverse-blased diode fabricated

by depositing a thin layer of gold or aluminum on n- or p-type silicon, respectively, as shown in Figure 2.1. The metal also serves to attenuate light.

When an energetic particle enters into the detector, it loses its kinetic energy through lattice interactions. These particles supply energy to the lattice electrons and lift them from the valence band into the nearly empty conduction band. The high electric field across the depletion region causes the electron-hole pairs created by the ionization event to be quickly swept out of the depletion region yielding a current pulse proportional to the energy of the incident particle. The particle loses some energy in the thin metal surface layer (dead zone) so that the thickness of the layer determines the low energy limit of the detector. The resolution (full-width at half-maximum) is typically 7 keV at room temperature.

Current pulses produced by the detectors are at low levels and must be amplified. The pulse is also shaped to minimize the noise content. A block diagram of the amplifying and shaping circuits is shown in Figure 2.2. The shaping circuits employ a triple-integration and single-differentiation scheme to improve the noise characteristics of the pulse. The output of the pulse shaper then goes to the data-manipulation experiment.

Table 2.1 shows the specifications of the six detectors in each of the payloads. The detectors have different energy ranges to aid in the identification of the energetic particles: detector 3 has a broom magnet to screen out low energy electrons while detector 2, because of its thicker surface, screens out low energy protons; detector 6 detects both protons and electrons. If the output pulses from detectors 2 and 6 are similar while that from detector 3 is different, then the detected particles are electrons; if the output pulses from detectors 3 and 6 are similar while that from detector 2 is different, the detected particles are protons or heavier nuclei. Note that detectors 4 and 5 on the payload of Nike Apache 14.542 have aluminum surface layers while detectors 4 and 5 on the payload of Nike Apache 14.543 have gold surface layers. This is done because the payloads were designed to be launched at different times of the day into correspondingly different atmospheric brightness conditions (i.e., dusk and midnight).

More information on the solid-state detectors is given in *Voss and Smith* [1974, 1977]. The EPS experiment for Nike Apache payloads 14.542 and 14.543 is described in more detail in a report being prepared by K. L. Fries, L. G. Smith, and H. D. Voss.

Figure 2.1 Surface barrier detector.

Note the differences

between the detectors

with surface layers of

(1) aluminum and (2) gold.

Figure 2.2 Major components of the solid-state detector instrumentation.

Table 2.1

Important characteristics of the six solid-state detectors

in the payloads of Nike Apaches 14.542 and 14.543.

| Designation | Geometrical<br>luctor<br>(cm² ster) | Front Surface Maternal (pg cm <sup>-2</sup> )** | Look Angle<br>from<br>Spin Axis<br>(deg) |       |          | lnergy<br>Channels | Pitch<br>Angle<br>Sectors | Comments                                                          |

|-------------|-------------------------------------|-------------------------------------------------|------------------------------------------|-------|----------|--------------------|---------------------------|-------------------------------------------------------------------|

| 1P5 i U     | 0 05                                | 40-Au                                           | 90                                       | `10   | >15      | 12                 | 15                        | High Resolution Detectors<br>Inergetic Particle<br>Identification |

| PPS 4 D     | 0 05                                | 40-Au                                           | 90                                       | >150  | >15      | 12                 | 15                        | Electron Broom Magnet CWEF*                                       |

| LPS 2 U     | 0 05                                | 100-A1                                          | 90                                       | . >12 | >55      | 11                 | 15                        | For Fnergetic Particle Identification, CWEF                       |

| 1 PS 3 U    | 0 05                                | 40-A1 (Au)                                      | 45                                       | -10   | >25 (15) | 12                 | 15                        | Precipitated   lux                                                |

| 1 PS 3 D    | 0 05                                | 40-A1(Au)                                       | 1 35                                     | >10   | >25 (15) | 12                 | 15                        | Backscattered Flux                                                |

| 1PS 1 00    | 0 05                                | 40-A1                                           | 90                                       | >10   | >25      | 12                 | 15                        | CWLF and Ion Mass<br>Determination                                |

<sup>\*</sup> Comparison with earlier flights

<sup>\*\*</sup> farentheses for Nike Apache 14.515 only

i U indicates ascent and D indicates descent

# 2.3 Electrostatic Analyzer

An ESA is included in the payloads to measure particle flux in the 0.5 to 10 keV range with a resolution of less than 1 keV. An ESA essentially consists of two cylindrical parallel plates followed by a detector. A voltage is applied to the plates to deflect particles into the detector. The plate voltage determines the energy of the particle which can successfully traverse the analyzer section.

A block diagram of the ESA is shown in Figure 2.3. The plate voltage is stepped logarithmically through six levels and then is allowed to decay exponentially to zero. The voltage sequence alternates between positive polarity and then negative polarity and is symmetrical about zero. This allows the ESA to scan for electrons and protons as well as positive ions. A fraction of the output of the sweep circuit is also telemetered to ground so that the actual plate voltage can be continuously monitored. The voltage sequence is synchronized to the rocket spin such that one step corresponds to one rocket rotation and the decay to two rocket rotations. The total sequence thus repeats after 16 rotations (i.e., six positive-going steps and decay plus six negative-going steps and decay).

The detector is an electron multiplier, Johnston Model MM1-5NG. An incoming particle strikes the first of the copper-beryllium dynodes and in so doing generates secondary electrons. An applied potential causes these electrons to strike succeeding dynodes thereby generating more electrons. After 20 stages the electrons strike an anode and the charge pulse is collected at the anode.

The signal from the detector is processed in the payload in two independent ways. In the first a charge preamplifier in the ESA is used to drive a staircase generator which gives a direct method of measuring the count rate. This does not involve the data-manipulation experiment.

The second method of processing the ESA data extracts considerably more information: it gives pulse-height analysis of the detector output (which allows energetic positive ions to be identified) and it provides pitch-angle information. For this method the detector is used with the preamplifier and charge shaping circuits of the type developed for the solid-state detectors (see Figure 2.2). The signal is then processed in the data-manipulation experiment in exactly the same way as the signals from the solid-state detectors. The ESA is described in detail in *Pozzi et al.* [1979].

Figure 2.3 Block diagram of the electrostatic analyzer. The acceptance angle of the collimator is exaggerated.

## 3. GENERAL DESCRIPTION OF THE EXPERIMENT

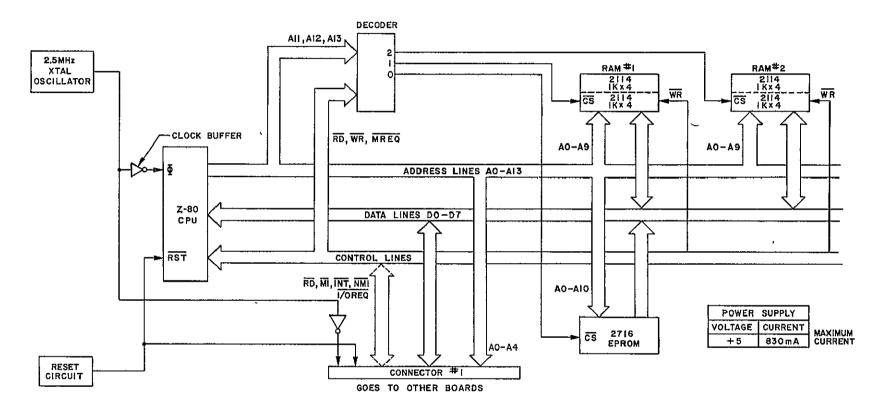

This chapter presents a general description of the data-manipulation experiment in terms of the hardware and software involved. The information content of the output is also explained. A block diagram of the complete system is shown in Figure 3.1.

#### 3.1 Z-80 Microcomputer

The Z-80 microcomputer family of components (available from Zilog and Mostek) has been used to implement the experiment. A microcomputer consists of three main parts: a CPU (the microprocessor), memory, and interface circuits to peripheral devices. All of these main parts are MOS LSI devices and their small size allows a powerful system to be constructed in a small physical space.

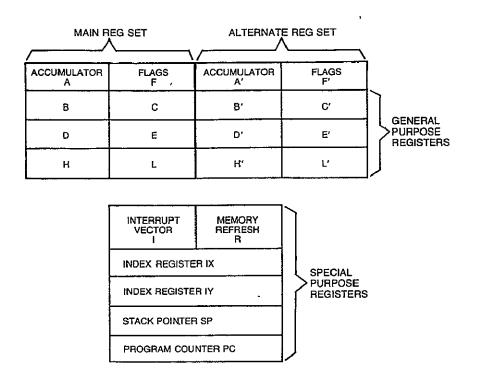

The Z-80 CPU uses 8-bit data words and 16-bit addresses (i.e., a 2<sup>16</sup> or 65,536 byte address space). It contains eighteen 8-bit registers and four 16-bit registers. The registers include two sets of six general purpose registers that may be used individually as 8-bit registers or in pairs as 16-bit registers. There are also two sets of accumulator and flag registers. There are six special purpose registers such as a program counter and a stack pointer. The Z-80 CPU can execute 158 instructions; these include special I/O instructions which allow the CPU to address 256 I/O devices in addition to the memory addresses. The CPU is contained in a 40-pin dual-in-line package (DIP).

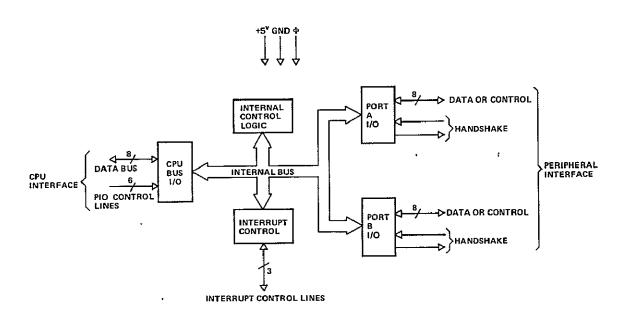

The Z-80 Parallel I/O Circuit (PIO) is a programmable device that provides two 8-bit parallel interfaces between peripheral devices and the CPU. Each of the two interfaces also has two 'handshake' lines so that the peripheral devices can control when data is input or output. The PIO can be programmed to operate in different modes depending on the application. For instance it can be programmed to be used as an input port that generates an interrupt to the CPU when one of the handshake lines is toggled; or interrupt capability and the handshake lines can be disabled so that data is input or output under software control. The PIO is contained in a 40-pin DIP.

The Z-80 counter-timer circuit (CTC) is a programmable four-channel device that provides counting timing functions for the CPU. It can also be programmed to act as an interval timer. In this mode a time constant is loaded into a down counter in the CTC by the CPU and the system clock is then used to decrement the counter; when it reaches zero, an interrupt is generated. Other modes allow external circuits to decrement the down counter or to be driven by

Figure 3.1 The data-manipulation system.

a divided system clock. The CTC is packaged in a 28-pin DIP.

In the system described here the PIO's and the CTC are programmed as follows. One port of PIO #1 (Port A) is programmed as an interrupting input port with the handshake lines enabled. Port B is programmed as a non-interrupting output port and the handshake lines are not used. Port A of PIO #2 is programmed as a non-interrupting input port and the handshake lines are again not used. The CTC is programmed to interrupt the CPU approximately every 1.5 ms.

An Intel 2716 EPROM is used to contain the non-volatile program for the rocket. It must be programmed by a special programmer (described in Chapter 6) before it is placed in the circuit. Its contents cannot be changed by the CPU after it is in the circuit although an ultra-violet light can be used to erase it if the program is to be changed. It can contain a 2 K byte program and is packaged in a 24-pin DIP.

The RAM portion of the memory consists of four Intel 2114 memory chips (also available from EMM SEMI). The 2114 has 1 K  $\times$  4 bits and is packaged in an 18-pin DIP.

## 3.2 Peripheral Devices

When a particle is sensed by one of the detectors, the pulse that is generated (as described in the previous chapter) goes to a pulse-height analyzer (PHA). It latches onto the peak of the pulse and holds it until a reset signal is received. The peak of the highest level pulse is held if more than one is received before it is reset.

Four detectors are used in the PHA system although six particle detectors and the electrostatic analyzers are accommodated during a flight. An apogee switch is used to switch two of the particle detectors out and the electrostatic analyzer and another particle detector in at apogee. Thus the upleg and downleg records of a rocket flight produced by two of the PHA's are for different devices.

The four PHA outputs are sequentially multiplexed to the analog input of the A/D. Every 50  $\mu s$  (actually 51.2  $\mu s$ ) the multiplexer switches to the next PHA, thus each PHA is reset every 200  $\mu s$ . Two bits from the PHA system are included with each PHA output going to the A/D to identify which PHA produced it.

The A/D converts the 0 to 10 V analog signal from the PHA system to an 8-bit digital signal although only the upper 4 bits are used. An 8-bit converter was used due to the unavailability of a suitable 4-bit converter. The A/D used

in the system is a Datel ADC-EH8B which converts the signal by the successive approximation method. The conversion time is approximately  $2.4~\mu s$ .

The first-in first-out memory (FIFO) is used to store data in a queue while the CPU is servicing an interrupt from the CTC (the CTC has a higher priority than PIO #1). Nine-bit words are accepted at the input and automatically shifted toward the output and are removed at any rate in the same sequence in which they were entered. Up to 40 9-bit words can be contained in the FIFO, but only 6 of the 9 bits are used in this system (4 bits from the A/D, 2 identifying bits from the PHA system). The three unused inputs are tied to ground. The FIFO allows data to be taken at a faster rate from the PHA system without losing data when the CPU cannot be interrupted by the PIO.

The D/A converts the system output from PIO #2 to an analog signal varying between 0 and 5 V. The D/A used in the system, a Micro-Networks MN3020, converts an 8-bit word to an analog signal between 0 and 10 V. Since the telemetry circuitry requires a signal between 0 and 5 V, the most significant bit of the D/A is not used and is tied to ground.

The magnetometer signal digitizer (MSD) converts the magnetometer signal to a 4-bit digital signal that represents the rocket's spin position. The magnetometer signal is a sine wave whose frequency equals the spin rate of the rocket. The conversion is done by incrementing a 4-bit counter at a constant rate (100 Hz) and resetting it when the magnetometer signal crosses a zero reference point in the downward direction. Therefore, the counter is reset once per revolution of the rocket.

The circuit of the MSD is described in Lewng et  $\alpha l$ . [1979]. It can be noted here that when the rocket is not spinning as during testing and before launch, the 4-bit counter resets itself, allowing the operation of the experiments to be observed.

The rotation is divided into equal sectors only for certain values of rocket spin rate: e.g., 6.67 Hz will give exactly 15 sectors (i.e., 100/6.67); 6.25 Hz will give exactly 16 sectors; and 5.88 Hz will give exactly 17 sectors. In general, because the rocket spin rate is pre-set only within a limited range, there will not be an integer number of sectors.

In the following section, for simplicity, the data manipulation will be described for the special case of a spin rate of 6.25 Hz. Later, in Section 5.2.3, the effect of other values of spin rate will be considered in detail.

## 3.3 Data Manipulation

As indicated above, the rocket rotation is divided into 16 discrete sectors (for a spin rate of 6.25 Hz). This is shown in Figure 3.2(a). The 4-bit number provided by the MSD is used to generate an address for a memory sector that corresponds to a rotation sector. The offset within each memory sector is provided by the data from the FIFO. The entire memory address is formed by concatenating the 4-bits from the MSD with the data from the FIFO, as shown in Figure 3.2(b).

The lower 1 K bytes of the RAM are divided into 16 sectors corresponding to the rocket rotation sectors as shown in Figure 3.2(c). Each of these 16 sectors is further divided into four areas corresponding to the PHA's. Each of these areas contains 16 bytes that correspond to 16 energy levels of the particles. Figure 3.2(d) shows which parts of the 10-bit address correspond to the rotation sectors, PHA's and energy levels.

When data is input to Port A of PIO #1, an interrupt is generated by the PIO. The CPU services the interrupt by inputting the data. An address is then generated as stated above and the location pointed to is incremented. A flowchart of the input routine alogrithm is shown in Figure 3.3.

The CTC generates an interrupt every 1.536 ms which causes the CPU to go to an output routine. Data outputs are done in synchronism with rocket rotation. One memory sector (corresponding to a rotation sector) is output during 1 + 1/16 revolution of the rocket. Data starts being output when the rocket has rotated to the rotation sector directly after the one corresponding to the memory sector to be output. For example, data from sector #1 starts being output when the rocket has rotated to sector #2 (referring to Figures 3.2(a) and 3.2(c)). Note that this results in the data in each sector being accumulated over 17 revolutions (i.e.,  $16 + 16 \times 1/16$ ). Since the duration of each sector is 10 ms (the period of the 100 Hz oscillator), it follows that the output sequence represents the particle data (in each sector) accumulated for a period of 170 ms (i.e.,  $17 \times 10 \text{ ms}$ ) less the reset time of the PHA (42.5 ms). The output sequence repeats at intervals of 2.72 s (i.e.,  $17 \times 160 \text{ ms}$ ) for this spin rate (6.25 Hz).

The output routine algorithm as shown in Figure 3.4 outputs a byte of data when the output flag has been set. If the flag has not been set, the routine checks to see if the rocket has rotated to within the next sector. If it has, the output flag is set and the routine outputs the first byte in the sector.

Figure 3.2 (a) Rocket rotation sectors; (b) Address formed from the two data words; (c) Memory (d) RAM address.

Figure 3.3 Input routine algorithm.

Figure 3.4 Output routine algorithm.

Otherwise the routine just updates the stored magnetometer data and the routine is exited.

An address register (two of the 8-bit general purpose registers) is used to point to the byte to be output. After the data at a RAM location has been output to the D/A, the location is cleared. The address register is then incremented and checked to see if all of the sector has been sent. If it has, the output flag is reset. If all of the 16 memory sectors have been sent (1 K bytes), the address register is reset to the beginning address of the RAM.

An example of the output from the system is shown in Figure 3.5. Note that the data from each detector has a 5 V peak at the beginning. Although this peak should by definition correspond to the number of zeroes (no particles or particles below the sensitivity of the detectors) from each detector, it is automatically set to the maximum voltage by the CPU since the number of zeroes would be large anyway. The peaks are also useful in that they separate the detectors allowing the data to be read easily.

Note also the signal labeled "marker" at the beginning of the data for sector #1. This signal is included to identify which sector is being output. It varies between 0 and approximately 5 V in 16 discrete steps. For instance the marker for sector #0 is 0 V, the marker for sector #7 is approximately 2.5 V and the marker for sector #15 is approximately 5 V.

Figure 3.5 Example of output from D/A. The ordinate is the telemetered signal (in volts) and is proportional to number of units ( $5V \equiv 32$  particles) in the accumulation period.

#### 4. HARDWARE

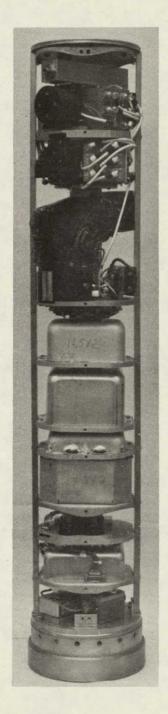

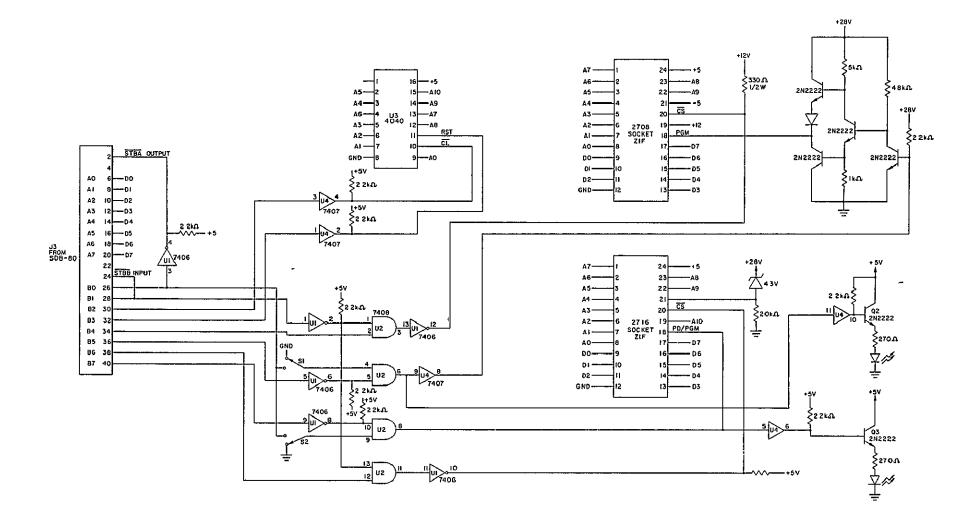

The designs of the microcomputer, the A/D-FIFO interface, and the D/A interface are discussed in this chapter. The microcomputer and the A/D and D/A converters are contained on four printed circuit boards as shown in Figure 4.1. The circuit board for PIO #2 also contains the MSD and the PHA. A photograph of this board is shown in *Leung et al.* [1979]. Figure 4.2 shows the location of the system on the payload.

Some control signals used in the system are defined in Table 4.1. The detailed timing diagrams of these signals are not presented here as they are not necessary for an understanding of the system operation, but they are available in the MOSTEK data books in the reference list.

#### 4.1 CPU-Memory Board

The CPU-memory board contains the Z-80 CPU, EPROM and RAM memory, reset circuitry and the system clock oscillator as shown in Figure 4.3. A flexible ribbon cable (Ansley #FSN-21A-20) from connector #1 provides the necessary address, data, and control lines for the operation of the other three boards in the system.

A detailed schematic of the CPU-memory board is shown in Appendix I.1.

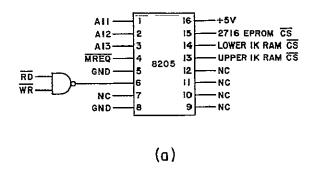

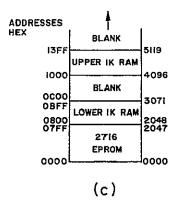

4.1.1 Memory address decoding. A one-of-eight decoder (Intel 8205 or T.I. 74LS138) is used to enable the RAM and EPROM memories. A diagram of the decoder circuit pin connections is shown in Figure 4.4(a). Address bits All, Al2, and Al3 from the Z-80 CPU define which output of the decoder will go low. The  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ , and  $\overline{\text{MREQ}}$  control lines are used as enabling inputs to the decoder. If  $\overline{\text{RD}}$  or  $\overline{\text{WR}}$  goes low and, in addition,  $\overline{\text{MREQ}}$  goes low, the decoder is enabled and one of the eight outputs specified by the address lines will go low. Only three of the eight outputs are used because only 4 K bytes of memory are in this system.

This particular decoder circuit was used because only one external gate was needed to generate the three select signals (the abbreviation for a select signal is  $\overline{\text{CS}}$  where the line indicates active low) and because it will allow easy system expansion in the future with a minimum of changes on the board (i.e., only additional address lines and the other  $\overline{\text{CS}}$  lines need be brought out to add another memory board). The resulting memory address map is shown in Figure 4.4(c). The 1 K gap between the RAM segments exists because the decoder generates  $\overline{\text{CS}}$ 's for 2 K memory segments and the RAM chips are 1 K segments.

(b)

Figure 4.1 Data-manipulation system circuit boards: (a) boards connected for installing in payload, (b) CPU-memory board.

Figure 4.1 Data-manipulation system circuit boards (continued). (c) PIO #1-CTC board, and (d) A/D FIFO board.

(c)

Solid-state detectors, Preamplifiers, Shapers

Electrostatic analyzer experiment

Counting circuits

Microcomputer, Magnetometer digitizer, Pulse-height analyzer

Figure 4.2 Location of the data-manipulation system in the payload of Nike Apache 14.542.

#### Table 4.1

# Z-80 Control signals.

- MI: An output signal from the CPU that indicates the current machine cycle is the instruction fetch cycle. MI also occurs with I/OREQ to indicate an interrupt acknowledge cycle, and it indicates to I/O devices when to place data on the data bus.

- MREQ: The memory request signal is an output signal from the CPU that indicates the address bus holds a valid address for a memory read or memory write operation.

- I/OREQ: The I/O request signal is an output signal from the CPU that indicates the lower half of the address bus holds a valid I/O address for an I/O read or write operation.

- RD: The read signal is an output signal from the CPU that indicates data should be placed on the data bus by memory or an I/O device.

- WR: The write signal is an output signal from the CPU that indicates that the CPU data bus holds valid data to be stored in the addressed memory or an I/O device.

- INT: The interrupt request signal is generated by I/O devices. The request will be honored at the end of the current instruction by the CPU if software has enabled an internal interrupt enable flip-flop.

- NMI: The non-maskable interrupt request signal is also generated by I/O devices. The request will always be honored at the end of the current instruction.

RST: Reset signal

Φ: System clock

NOTE: The lines above the signals mean they are active low.

Figure 4.3 The CPU-Memory board. An arrow on one end of a line indicates a single direction signal; arrows on both ends indicate a bidirectional signal; dotted arrows indicate some lines go in one direction and some the other direction.

8205 PIN NUMBERS AI3 MREQ ROWR A1I AI2 13 н н Н Н н Н L Н x X Н н Н X X н. X н H X X X Н X (b)

Figure 4.4 Address decoding: (a) Connection of the 8205 one-of-eight decoder; (b) Truth table (X = don't-care state); (c) Memory addresses.

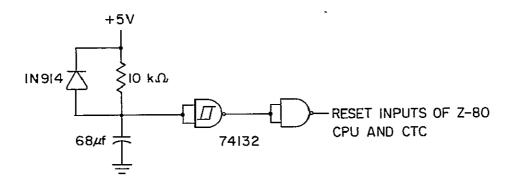

4.1.2 Reset circuit. The Z-80 CPU and CTC have a reset input that cannot be brought high until the data, address and control lines have stabilized after power-on. The reset input can also be used to restart the CPU and CTC in their initial states after power-on by bringing it low for a short period, but this feature was not needed in the data manipulation experiment since it is a dedicated system (i.e., the software is not changed). When the reset line goes high, the CPU starts at address zero and the CTC is in its initial state (i.e., it is not yet programmed for operation). The PIO does not have a reset input but it is in its initial state automatically after a power-on.

The reset circuit itself is simple as shown in Figure 4.5. When power is applied, the 68  $\mu$ f capacitor starts charging through the 10  $k\Omega$  resistor. When the Schmitt trigger input of the first NAND gate reaches approximately 1.6 V, it switches and an instant later the reset line goes high. If for some reason power is interrupted to the system, the capacitor discharges rapidly through the diode. The reset line goes high approximately 77 ms after power is applied [i.e., -(10<sup>4</sup>)(68  $\times$  10<sup>-6</sup>)ln(1.6/5)].

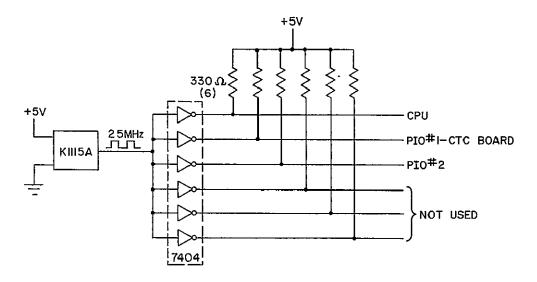

- 4.1.3 Clock. A Motorola K1115A 2.5 MHz crystal oscillator provides the system clock signal. It was used because of its small size, slightly larger than a 14-pin DIP, and because it provides a TTL compatible output. As shown in Figure 4.6 a 7404 with 330  $\Omega$  pull-up resistors on the outputs is used to buffer the clock signal. The 330  $\Omega$  pull-up resistors are required in the Z-80 components' specifications. The K1115A oscillator is specified to tolerate a minimum shock of 100 G's for 0.1 milliseconds with three shocks in each plane. This specification is adequate for a rocket flight: the oscillator performed well both in pre-flight tests and in actual flight of Nike Apache 14.543.

- 4.1.4 Read-write control. As shown in Figure 4.3 the 2114 RAM circuits receive the  $\overline{\text{WR}}$  control signal. It controls whether data is input or output: a high level causes data to be output by the RAM's; a low level causes data to be input (the  $\overline{\text{CS}}$  lines must be low also).

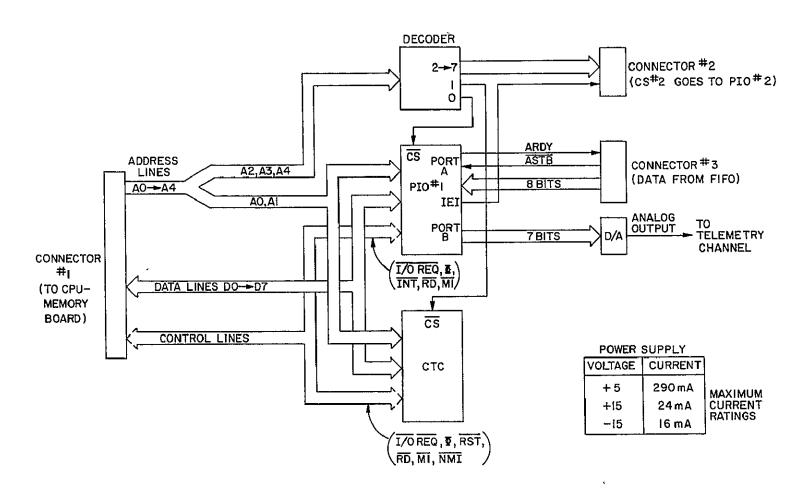

# 4.2 PIO #1 and CTC Board

This printed circuit board contains PIO #1, the CTC and the D/A as shown in Figure 4.7. A detailed schematic of the board is shown in Appendix I.2.

The 8205 (or 74LS138) decoder on this board is used to select which I/O port is enabled. PIO #1 has I/O addresses 1 through 3, the CTC has 4 through 7, and PIO #2 has 8 through 11. The other outputs of the decoder are brought out on connector #2 for future expansion of the I/O capability.

Figure 4.5 Reset circuit.

Figure 4.6 System clock.

Figure 4.7 The PIO#1-CTC board. The arrows have the same meaning as in Figure 4.3.

The interrupt enable input (IEI) signal from PIO #1 is brought out on connector #2 so that other I/O ports added in the future can generate maskable interrupts. This signal would be used in the daisy-chain interrupt mode (i.e., Mode 2) described in the MOSTEK Z-80 literature in the reference list. This signal is not used in this system, however, since the Mode l interrupt option is used, as described in the following chapter.

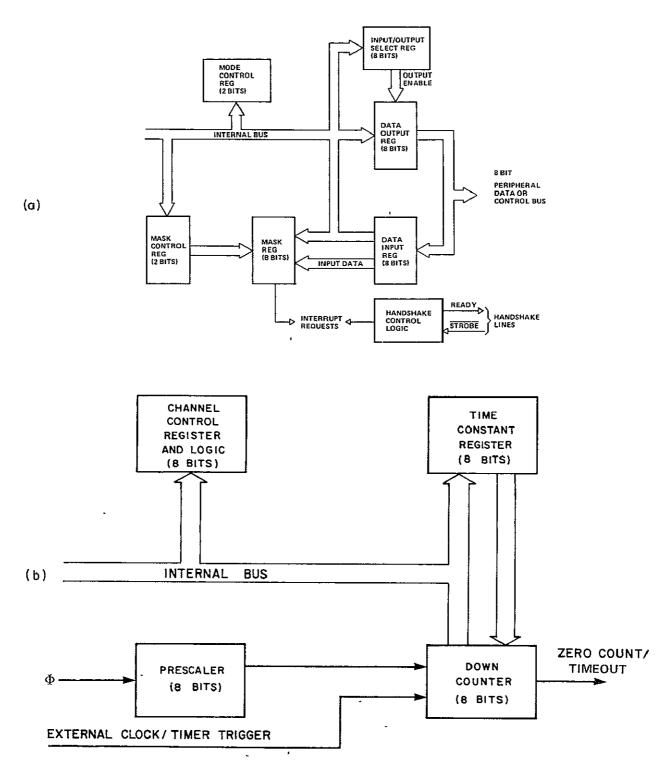

Even though there are only two ports, the PIO's require four addresses because each port has control logic that must be addressed individually, as shown in Figure 4.8. This logic is programmed to control whether a port is an input or an output port, the handshake lines, and the generation of interrupts.

The two handshake lines, RDY and STB, control the data input to a port and the generation of an interrupt to the CPU when the port is programmed to operate in the appropriate mode (i.e., Mode 1, consult the PIO data book). In the data manipulation system the handshake lines are used only for Port A of PIO #1.

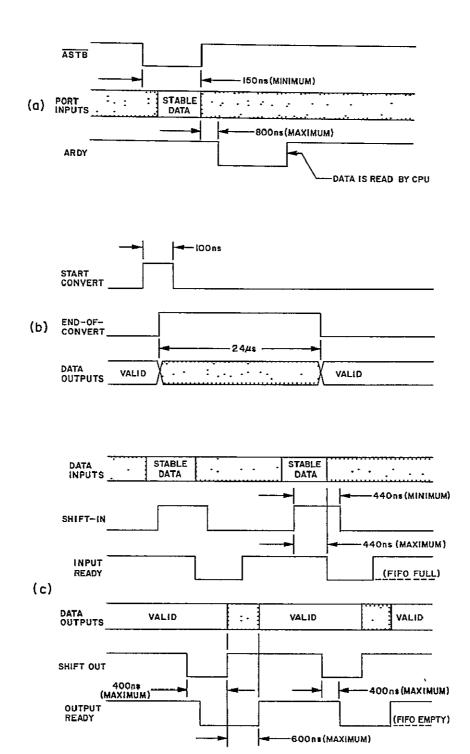

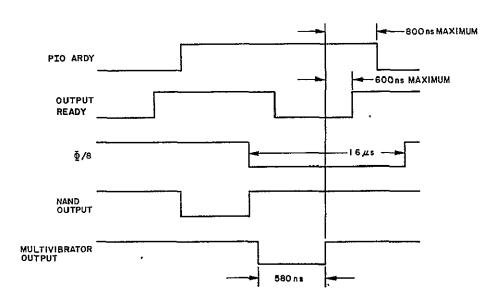

The timing diagrams for ARDY and ASTB are shown in Figure 4.9(a) where the "A" indicates they are for Port A. Data is loaded into the Port A input register by applying a pulse of 150 ns (or greater) to the ASTB pin (normally high, pulsed low). ARDY indicates when the input register is empty and is ready to accept an input (normally low, active high). When data is loaded into the input register, an interrupt is generated by the PIO by bringing the INT line low. When the CPU has read the input register contents, ARDY returns high. When the PIO is initialized after power-on, Port A must be read once to bring ARDY high even though there is no data in the input register.

As stated in the previous chapter the CTC generates an interrupt when an internal down-counter reaches zero. The CTC in this system is connected to the  $\overline{\text{NMI}}$  line of the CPU which is used to generate non-maskable interrupts. Thus it has a higher priority than PIO #1 or any I/O port that would be added in the future.

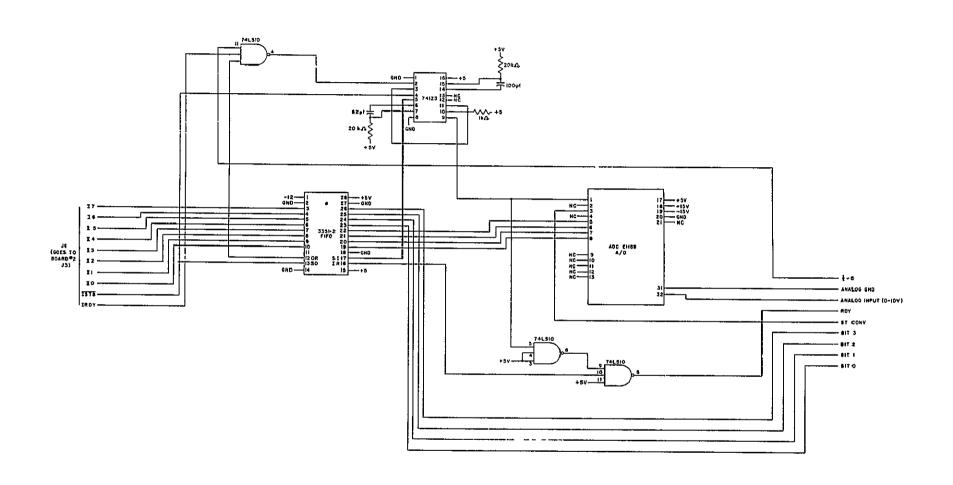

### 4.3 A/D and FIFO Board

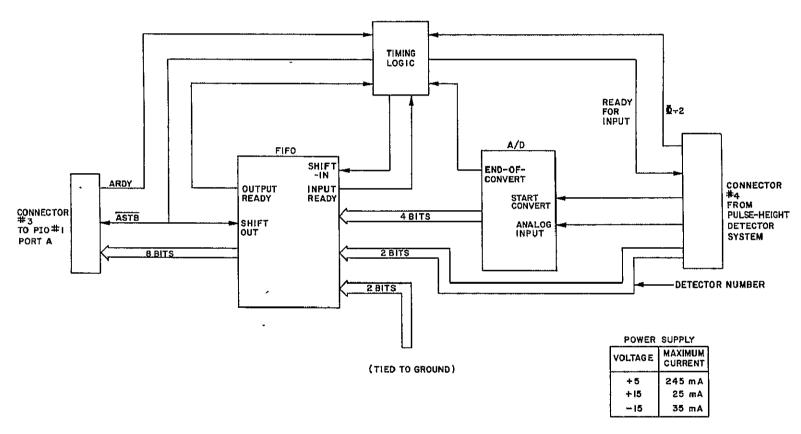

This board contains the A/D, the FIFO, and associated timing logic as shown in Figure 4.10. A detailed schematic of the board is shown in Appendix I.3. Data is input to this board from the PHA system and is output to Port A of PIO #1.

The A/D starts converting an analog signal to its digital representation when a pulse of  $100~\mathrm{ns}$  minimum width is applied to its start-convert pin as

Figure 4.8 PIO block diagram (MOSTEK Z80 Manual).

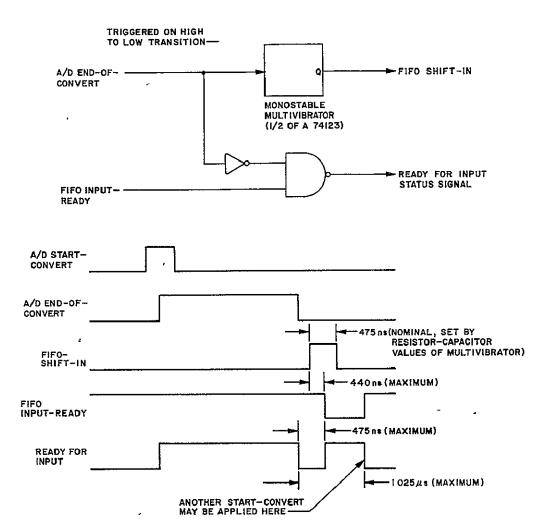

Figure 4.9 Timing diagrams: (a) PIO#1 Port A handshake line timing; (b) A/D control signal timing; (c) FIFO handshake line timing.

Figure 4.10 The A/D-FIFO board. The arrows have the same meaning as in Figure 4.3.

shown in Figure 4.9(b). When the conversion is finished, the end-of-convert line goes low until another conversion is started.

The FIFO can be regarded as nine 40-bit serial shift registers. Data is input to the first register and trickles through until a location containing data or the 40th location is encountered. The FIFO has handshake signals similar to the PIO signals which control data input and output.

The timing diagram of the FIFO handshake signals is shown in Figure 4.9(c). The input-ready signal indicates when data may be entered into the first register. Data is entered by bringing the shift-in line high. This causes the input-ready line to go low but data will stay in the first register until the shift-in input goes low. The data then propagates to the second location providing it is empty, and the input-ready line goes high again. The input-ready line will stay low if the FIFO is full. Once data has been shifted to the second location, it automatically continues until other data or the last register is encountered as stated above. The output-ready line goes high when the data reaches the last location. Data is shifted-out when the shift-out line is brought low and returns high. Data is not shifted from the 39th to the 40th location until the shift-out line goes back high, therefore, the output data is stable until then. The output ready line goes back high when the data has been shifted unless the FIFO is empty.

The end-of-convert signal from the A/D is used to enter data into the FIFO. When the end-of-convert signal makes a high-to-low transition, it triggers a 74123 monostable multivibrator as shown in Figure 4.11. The multivibrator then generates a 475 ns pulse on the shift-in line of the FIFO.

The A/D end-of-convert signal and the FIFO input-ready line are combined to generate a status signal to indicate when the board is ready for an input, but it is not used by the PHA system. Since data is input at relatively long intervals of 50  $\mu$ s the status signal is not needed. It may be noted that the ready-for-input signal, if used, would have to be used judiciously since it will momentarily go low up to 1.025  $\mu$ s before another start-convert can be applied, as noted on the diagram. It momentarily goes low because the FIFO input-ready signal does not go low for up to 440 ns after the shift-in input is brought high.

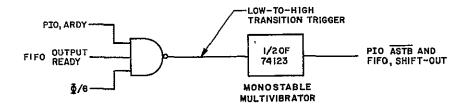

Data is strobed into PIO #1 using: the output-ready signal from the FIFO; ARDY of the PIO; and the system clock divided by eight (i.e., 0.3125 MHz). These three signals are input to a NAND gate whose output goes to another

Figure 4.11 The circuit and timing diagram for the input to the FIFO and the ready-for-input status signal.

monostable multivibrator as shown in Figure 4.2 (the multivibrator is the other half of the 74123 used above). When the divided clock signal makes a high-to-low transition while the other two NAND gate inputs are high, the monostable will be triggered and the  $\overline{\text{ASTB}}$  line of the PIO will receive a 580 ns pulse. This signal is also used to drive the shift-out line of the FIFO. The divided clock signal is provided by the PHA system.

The divided clock signal is included because ARDY could possibly stay high longer than the time it takes the output-ready signal to go low and return high as shown in Figure 4.12. Because of this a method was needed to trigger the multivibrator after both signals have been high for a period of time. If only ARDY and output-ready were used, an extra pulse from the multivibrator could possibly occur causing a data sample to be lost. By using the high-to-low transition of the clock to trigger the multivibrator only one pulse will be generated by multivibrator.

On the systems constructed for Nike Apaches 14.542 and 14.543  $\Phi/2$  was used instead of  $\Phi/8$  (i.e.,  $\Phi$  is the symbol for the clock signal). This could cause a problem if  $\Phi/2$  goes low, high, then back low again after output ready has returned high and before ARDY goes low; or if ARDY goes low while both  $\Phi/2$  and output-ready are high. The system using  $\Phi/2$  appeared to work well during tests and the rocket flight but on future flights  $\Phi/8$  should be used.

The same signal for the PIO ASTB line and the FIFO shift-out line can be used because the data hold time beyond the ASTB low-to-high transition required by the PIO is zero and a finite amount of time is required to shift data from the 39th to the 40th position in the FIFO after the shift-out transition. Since the data on the output pins of the FIFO will not change instantaneously when the transition occurs, the hold time of the FIFO is greater than zero.

In Figure 4.12 note that an extra trigger to the multivibrator could possibly occur during a pulse. This is permissible since it will only cause the pulse to be longer than 580 ns.

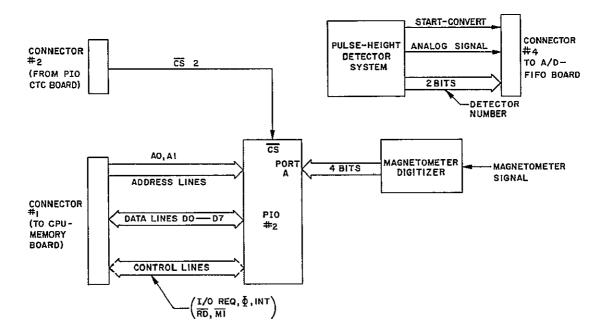

### 4.4 PIO #2

As shown in Figure 4.13 PIO #2 is on the board that contains the PHA system and the magnetometer signal digitizer. Four bits of Port A are used to input the magnetometer data, but Port B is not used.

Although only four of the sixteen PIO I/O bits are used, the PIO circuit provided the easiest and most efficient interface to the MSD since all the Z-80 control signals are handled by the PIO's internal logic. In addition the extra

Figure 4.12 The circuit and timing diagram for input to PIO#1 from the FIFO.

Figure 4.13 The PIO#2 board. The arrows have the same meaning as in Figure 4.3.

I/O bits could be used for a future experiment.

As stated before PIO #2 has addresses 8 through 11 with the  $\overline{\text{CS}}$  provided by the decoder on the P-IO-CTC board, but only the addresses for Port A are needed (i.e., 8 and 9).

A detailed schematic of this board is given in Leung et al. [1979].

### 5. SOFTWARE

The software written for the data-manipulation experiment is discussed in this chapter. Since some understanding of the Z-80 architecture is needed, a brief description of it is included.

#### 5.1 Z-80 Architecture

The Z-80 CPU register configuration is shown in Figure 5.1; the CPU contains two sets of independent accumulator, flag, and general purpose registers. A single exchange instruction enables the CPU to switch between the accumulator and flag pairs while another single instruction is used to switch between the general purpose register sets. This exchange capability is useful (it saves time) when an interrupt is serviced because the contents of the registers do not have to be saved in RAM.

The 8-bit accumulator register is used to hold the results of 8-bit arithmetic and logical operations while the flag register indicates the status of 8 or 16-bit operations, such as indicating whether or not the result of an operation is negative or positive. The 8-bit general purpose registers can be used in pairs for 16-bit operations, specifically the BC, DE and HL pairs in both sets. The HL pairs are used by several instructions for memory addresses.

The program counter holds the 16-bit address of the current top of the stack located in external RAM. The stack is a last-in-first-out memory file that is used to temporarily store data from the registers. The other special purpose registers are not used by the data manipulation experiment software.

The Z-80 CPU has both maskable and non-maskable interrupts. The CPU can be programmed to respond to a maskable interrupt in any one of three possible modes. Mode 1 is used in the present application since there are only two interrupting devices. In this mode a maskable interrupt from PIO #1 causes the CPU to jump to location 0038 H (where H means hexadecimal or base 16). A non-maskable interrupt from the CTC causes the CPU to jump to location 0066 H.

The Port I/O logic of one port of a PIO is composed of six registers with "handshake" control logic as shown in Figure 5.2(a). The 2-bit mode control register is loaded by the CPU to select the desired operating mode. The input register holds data input to the port and the output register holds data that is to be output. The handshake logic controls the transfer of data between the peripheral and the PIO.

Figure 5.1 Z80-CPU register configuration (MOSTEK Z80 Micro-Reference Manual).

Figure 5.2 Block diagrams of (a) one port of a PIO and (b) one channel of the CTC (MOSTEK Z80 Manual).

The 8-bit I/O select register and the 8-bit mask register are used when the port is programmed to operate in Mode 3. In this mode any of the data lines can be programmed to be an input or output as specified by the select register. The 2-bit mask control register and the mask register are used to control the generation of interrupts in Mode 3, but they are not used in the data manipulation software.

The logic for one channel of a CTC is composed of two registers, two counters and control logic as shown in Figure 5.2(b). The time constant register is loaded by the CPU to initialize and re-load the down counter at a count of zero. The channel control register is loaded by the CPU to select the mode and conditions of channel operation. The prescaler divides the system clock by 16 or 256 for decrementing the down counter. The external clock/timer trigger and the zero count/timeout signals are not used in the data manipulation experiment.

## 5.2 Data-Manipulation Software

The software for the system comprises three main parts: initialization, the input routine, and the output routine. During initialization the CTC and PIO's are programmed for operation, the RAM is cleared and other pre-operation details are taken care of. The input and output routines function as explained previously. These three sections of the software are discussed further below. A listing of the program is given in Appendix II.1.

5.2.1 Initialization. The flowchart of this section of the software is shown in Figure 5.3. After power-on the PIO's and the CTC are programmed as shown although the interrupt capability of PIO #1 is not enabled and the CTC time constant is not loaded until just before the "Halt" instruction. This is done to prevent an interrupt from occurring before the initialization is finished. HL' and DC' are loaded with 800 H and zero respectively for use in the output routine. Data from the magnetometer must be shifted right two positions and 800 H must be added as shown in Figure 5.4 before it can be used to designate the rotation sector memory area shown in Figure 3.2(d). The ARDY line of PIO #1 must be raised the first time by reading Port A although the data is not used. After the ARDY line is raised, the CPU executes a "Halt" instruction. When this is done, the CPU enters an inactive state that can only be exited when an interrupt is received. After the interrupt is serviced, the CPU executes the instruction directly following the Halt instruction which is a jump back to it.

Figure 5.3 Flow chart of the initialization section.

Figure 5.4 Magnetometer data bit positioning: (a) Data bits are put into register D; (b) shifted right two places into top two bits of E, (c) 800H is then added.

5.2.2 Input routine. A more detailed flowchart of the input routine than in Figure 3.3 is shown in Figure 5.5. Register pair DE is used to hold the current magnetometer data and is updated by the output routine. The data from the PHA system in A is concatenated with the magnetometer data in DE by simply adding register E to A. Register pair HL is then used to hold the concatenated data which point to the RAM location to be incremented.

The two lowest order bits of each RAM location are not used since they could be lost when the location is output due to noise (i.e., low order accumulations would be difficult to discriminate from zero). Therefore, four must be added to each location so that it is incremented beginning in the third bit position (i.e.,  $4_{10} = 100_2$ ).

When a maskable interrupt is serviced by the CPU, an internal flip-flop is automatically reset such that subsequent maskable interrupts will be ignored. This flip-flop must be set when the input routine is exited so that maskable interrupts are again enabled.

The input routine requires between 30 and 31.6  $\mu$ s for execution (for a 2.50 MHz system clock) providing the CPU does not service a CTC interrupt. 24.8  $\mu$ s are required for executing the instructions in the routine and from 5.2 to 6.8  $\mu$ s are required by the CPU to exit the "Halt" state and prepare for servicing the interrupt (i.e., the contents of the program counter are stored in the stack file).

Since the input routine requires 31.6  $\mu s$  and data is input to the FIFO every 51.2  $\mu s$ , the FIFO is never allowed to store data past its maximum limit. In fact, no more than four inputs are input to the FIFO during the output routine since the maximum time required for the output routine is about 170  $\mu s$ .

The time it takes for the system to catch up with the inputs waiting in the FIFO can be calculated as follows. Let  $T_1$  equal the maximum time of the output routine,  $T_2$  equal the time it takes the system to catch up,  $r_1$  equal the input rate to the FIFO, and  $r_2$  the output rate from the FIFO to the data manipulation system.

$$r_1(T_1) + r_1(T_2) \le r_2(T_2)$$

(5.1)

Now although it would appear that  $T_1$  = 170 µs, the possibility of the CTC interrupt occurring during the input routine must be taken into account. If the CTC interrupt is received directly after the PIO interrupt, the input routine for that interrupt would have to be finished after the output routine

Figure 5.5 Flow chart of the input routine.

since the CTC has a higher priority. In this case the time to complete the input routine should be added on to the maximum time of the output routine. The input routine would, in the worst case, start at the "Load H register with contents of D" instruction as shown in Figure 5.5. In this case  $T_1$  would be approximately equal to 195  $\mu$ s (i.e., 170  $\mu$ s + 24.8  $\mu$ s).

Using equation (5.1) a value for  $T_2$  can now be obtained as follows

$$\frac{1 \text{ input}}{51.2 \text{ } \mu\text{s}} (195 \text{ } \mu\text{s}) + \frac{1 \text{ input}}{51.2 \text{ } \mu\text{s}} (T_2) \le \frac{1 \text{ output}}{31.6 \text{ } \mu\text{s}} (T_2)$$

(5.2)

Since it is impossible to get a partial input, we round the first term up to 4. Thus equation (5.2) becomes

$$4 + \frac{T_2}{51.2 \text{ us}} \le \frac{T_2}{31.6 \text{ us}} \tag{5.3}$$

This gives a value of 330  $\mu$ s for  $T_2$ , but since this is not an integer multiple of 31.6  $\mu$ s, 347.6  $\mu$ s should be used.

Since this is the worst case value for the catch-up time, there is no danger of the system getting behind (i.e., 0.3476 ms << 1.536 ms, the CTC interrupt interval). The output routine normally takes much less time than 170  $\mu$ s, as will be shown in the next section. In most cases no more than two or three inputs would be waiting in the FIFO at the end of the output routine.

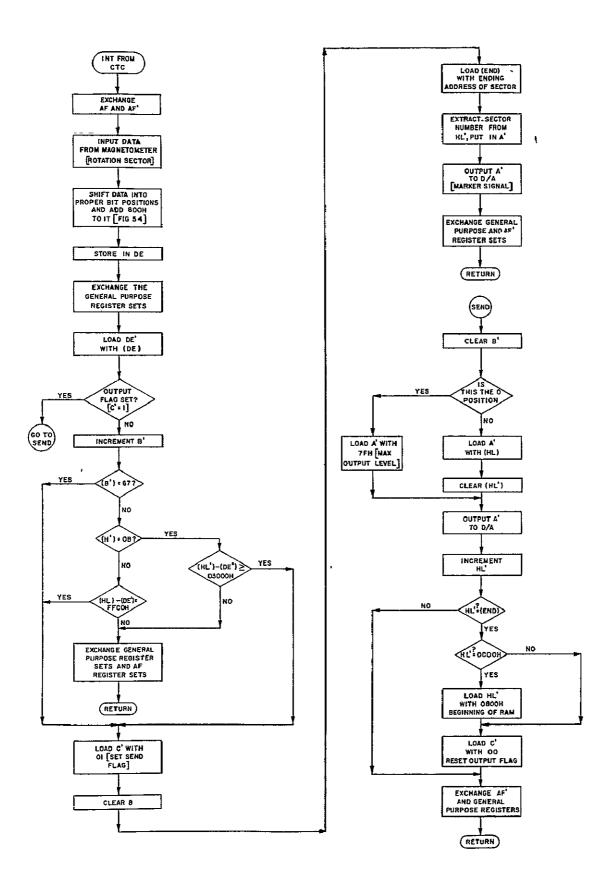

5.2.3 Output routine. The output routine is the most complex of the three software sections. As will be explained below, this results from a desire to provide a method for outputting data in the event of failure of the MSD and the need to accommodate a range of values of rocket spin rate.

A more detailed flowchart than the one in Figure 3.4 is shown in Figure 5.6. The register sets are exchanged after the magnetometer data in DE is updated. Data for the input routine is contained in one register set while data for the output routine is contained in the alternate set. Note that DE' also contains the updated magnetometer data for use later in the routine. Register C' is used as the output flag, as described in Chapter 3. A 01 H contained in C' corresponds to the flag being set while 00 corresponds to its being reset.

(a) MSD failure mode. The software includes a method to output data even if there is a failure of the MSD. In this mode the energy spectrums are obtained but there is no pitch-angle distribution.

Figure 5.6 Output section of the software.

Register B' is incremented every time there is a CTC interrupt (i.e., every 1.536 ms) and is reset to zero when data is output. If the output flag is not set by the MSD before B' is incremented to 67, it is set automatically.

The number of times B' is incremented before the output flag is set imposes a lower limit on the spin rate that can be accommodated. The last data output and the first time B' is incremented overlap such that B' would be incremented 67 times between outputs. Since there are 65 outputs (i.e., the 64 data bytes and the marker signal) and B' is incremented 67 times, the largest spin period that can be accommodated is 193 ms (i.e.,  $(65+67) \times 1.536$  ms - 10 ms). Figure 5.7 illustrates the situation for a spin period of 193 ms (or longer). A spin period of 193 ms corresponds to a spin rate of 5.18 Hz which is considerably slower than the spin rates of past flights (which have been in the range of 6.4 to 7.5 Hz).

The choice of 67 in the above discussion is determined as a compromise between complicating requirements. The output rate in the event of an MSD failure is desired to be as fast as possible, which sets an upper limit on the number of times B' is incremented. It was arbitrarily decided that the interval between outputs should be no more than 10% longer than the time it takes to output a sector. This corresponds to 110 ms and an upper limit of 72 times (i.e., 110/1.536) to increment B'. A 5.5 Hz spin rate (182 ms period) was arbitrarily decided upon as the slowest spin rate anticipated. This gives a lower limit of 60 times (i.e., 182/1.536) to increment B'. Thus the interval created should be greater than 60 but less than 72; 67 was adopted.

(b) Outputting sectors #12 to #15. The last four sectors are output when the magnetometer signal digitizer indicates the rocket has rotated to sector #0 (1.e., the 4-bit counter output is zero). Figure 5.8 illustrates the reasons for doing this. When the spin rate is faster than 6.67 Hz (i.e., 150 ms period), data will not be input to one or more of the higher order sectors by the input routine. However, because the software is written assuming there would be sixteen sectors, all sixteen are always output even though the data in the highest order sectors may be zero. Therefore a method to set the output flag for the high order sectors was needed, other than the method used for the low order sectors explained in Chapter 3 (i.e., for the lower order sectors the output flag to output a particular sector is set when the rocket has rotated to the sector directly following it). By setting the output flag for the last four sectors when the 4-bit counter is reset to zero, a spin rate of up to

Figure 5.7 Here and in the following figure the output of the MSD is represented as an analog signal to show the relationship between the rocket spin period and the counter cycle time. The case shown here is for a 5.18 Hz spin rate (i.e., 193 ms period). 10 ms must be added to the spin cycle time to get the interval between the times when the output flag is set between succeeding sections. Since the counter is incremented at 100 Hz, there are 20 increments between the times the counter is reset (the last count has a shorter interval, 3 ms). This diagram also represents the situation for a spin period greater than 193 ms and for no magnetometer signal. R indicates the internal reset of the 4-bit counter and M the reset of the counter by the magnetometer.

Figure 5.8 7.14 Hz spin rate causes the magnetometer signal digital representation to have 14 levels (refer to Figure 5.7). R indicates reset of 4-bit counter by the magnetometer.

8.33 Hz (i.e., 120 ms period: 12 sectors of input data) can be accommodated without causing the output to get out of synchronism with the rocket rotation.

Register pair HL' is used to contain the address of the next byte to be output, and the difference between the contents of HL' and DE' is used to set the output flag since DE' contains the updated magnetometer data. If the output flag is not set, but the difference between the contents of HL' and DE' is FFCO H (i.e., the 2's complement of 0040 H), it will be set. For instance if the contents of DE' were 840 H and the contents of HL' were 800 H, the output flag would be set. Since H' contains 0B H when HL' points to a location in the last four sectors, the output flag can be set when the most significant byte of the difference between HL' and DE' equals 03. For example when HL' contains B40 H (i.e., corresponds to sector #13) and DE' contains 800 H (i.e., corresponds to sector #0) the difference is 340 H. By only considering the upper byte the software is simplified and takes less time.

(c) Sampling time. In the simplified description in Chapter 3 it was shown that the accumulation interval for each sector is the time it takes for 17 revolutions of the rocket. This will now be shown to be true for the actual output routine just described.

As shown in Figure 5.9 the interval between when the output flag is set for one sector and when it is set for the succeeding sector is 1 + 1/16 revolution for the first twelve sectors. The interval between when it is set for sector #11 and when it is set for sector #12 is 1 + 4/16 revolution since the flag is not set to output sector #12 until the rocket has rotated to sector #0. The following three sectors also start being output at sector #0 on succeeding revolutions so that the interval between setting the flag is 1 revolution for these sectors. Thus the sum of the sixteen intervals is seventeen revolutions (i.e.,  $12(1 + 1/16) + (1 + 4/16) + 4 \times 1 = 17$ ).