# NOTICE

THIS DOCUMENT HAS BEEN REPRODUCED FROM MICROFICHE. ALTHOUGH IT IS RECOGNIZED THAT CERTAIN PORTIONS ARE ILLEGIBLE, IT IS BEING RELEASED IN THE INTEREST OF MAKING AVAILABLE AS MUCH INFORMATION AS POSSIBLE

(NASA-CR-163237) PATTERN CLASSIFICATION USING CHARGE TRANSFER DEVICES Final Report (North Carolina State Univ. at Raleigh.)

138 p HC A07/MF A01 CSCL 14E

N80-25760

Unclas G3/43 22432

DEPARTMENT OF ELECTRICAL ENGINEERING

NORTH CAROLINA STATE UNIVERSITY

RALEIGH, NORTH CAROLINA

# PATTERN CLASSIFICATION USING CHARGE TRANSFER DEVICES

Final Report

on Grant NSG 1535

to the

National Aeronautics and Space Administration

Langley Research Center

Hampton, Virginia

June 16, 1980

#### 1 INTRODUCTION

### 1.1 Project Goals

For the past two and a half years, we have performed a study of the feasibility of the use of Charge Transfer Devices (CTDs) in the classification of multi-spectral image data. This work consisted of two primary stages: 1) An evaluation of particular devices to determine their suitability in a matrix multiplication subsystem of a pattern classifier and 2) The design of a prototype of such a system if a suitable device was found. The work centered around "analog-analog correlator" devices which consist of two tapped delay lines, on chip multipliers, and a summed output; these devices will be discussed in more detail in Section 2 of this report.

### 1.2 Summary of Results

In general, our results have been encouraging; one of the tested devices showed performance characteristics which warranted further development, the design of the system was accomplished, and construction was begun. Reference is made to two previous progress reports dated December 20, 1977 and August 28, 1979. These papers contain detailed reports on the results to the time of their issue, and the material contained in them will only be summarized in this report.

The previous reports indicated the following findings:

- (1) The first device evaluated, the Reticon AAC-32 was found to be not suitable because of serious linearity problems.

- (2) A second series of devices, the Reticon R5402/5403, was tested and was found to have acceptable accuracy and reasonable linearity indicating a need to explore its use in a pattern classifier.

- (3) An architectural design and part of the detailed design for a multispectral classifier using the Reticon devices and controlled by an LSI-11 microcomputer was completed.

- (4) Software was developed to support communication between the LSI-11 and a VAX medium scale computer. This software allowed the reading of LANDSAT tapes and the subsequent transfer of the multispectral images to the LSI-11 floppy disk for use by the classifier.

- (5) Software was also developed to support the display of false colored images on a Chromatics graphics terminal.

Additional accomplishments since the August report are:

- (1) The design for the classifier was completed.

- (2) A printed circuit layout for the analog boards was completed, and the boards were fabricated. The other boards will be wire-wrapped.

- (3) A test jig for the analog board was built and checkout begun.

- (4) System software development was begun.

### 2 CTD THEORY

This section contains a brief overview of Charge Transfer

Device characteristics. For a detailed explanation of CTD

construction and operation see the 1977 report and its references.

A CTD is simply a monolithic integrated circuit which moves packets of charge linearly in synchronism with a clock. Depending upon the application, these charge packets may be used to represent either digital or analog information. CTDs have been used for a wide variety of purposes, particularly analog signal processing, digital memories, and imaging arrays.

Two very common types of CTDs are the "Bucket Brigade Device" (BBD) and the "Charge Coupled Device" (CCD). The major difference between these two devices is the manner in which the charge packets are stored and transferred from cell to cell. This difference results in slightly differing performance characteristics between the two types.

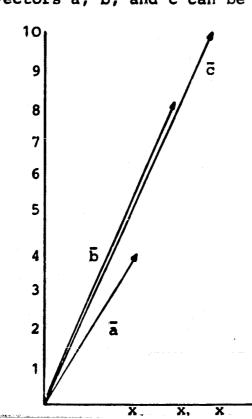

A common use of CTDs is signal processing has been as simple analog delay lines or shift registers. By modifying the clocking electrodes complex functions of the input rather than simple delays have been realized. These functions are of the form:

\[ \textbf{a}\_i \textbf{b}\_i \text{ where the } \textbf{b}\_i \text{ are samples of the input signal and the } \textbf{a}\_i \text{s} \text{ are weighting coefficients. Such devices are known as "fixed tap weight devices" (from their filtering applications) because the weights are determined at manufacture and cannot be changed afterward. Fixed tap weight devices have been used to produce a variety of functions such as matched filtering, correlation, or the magnitude of the discrete Fourier transform.

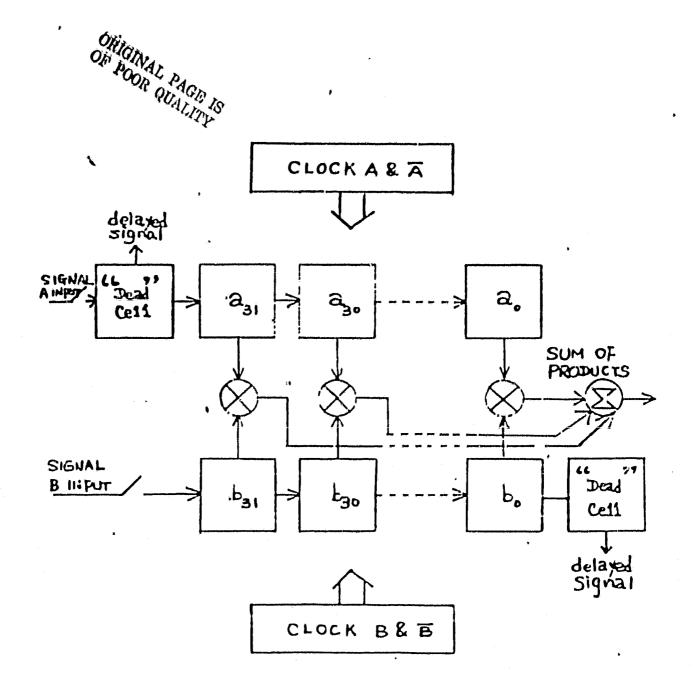

The versatility of the CTD may be extended by using two delay lines, adding analog multipliers at each point, and providing a mechanism for summing the outputs of the multipliers. Such a device may be used to perform sum-of-product operations in which both of the operands are arbitrary. Experimental samples of these "variable tap weight devices" are now available, and these devices are the subject of this study.

### 3 PATTERN CLASSIFICATION USING CTDS

A major bottleneck in pattern classification operations has been the matrix multiplication required in the calculation of the discriminate function:

$$(\overline{x} - \overline{\mu}_1)^T$$

$C_1^{-\frac{1}{2}}$   $(\overline{x} - \overline{\mu}_1)$

where  $\bar{x}$  is the data point vector,  $\bar{u}$  is the mean vector of the ith class, and  $C_i$  (also commonly signified by  $\Sigma_i$ ) is the covariance matrix of the ith class.

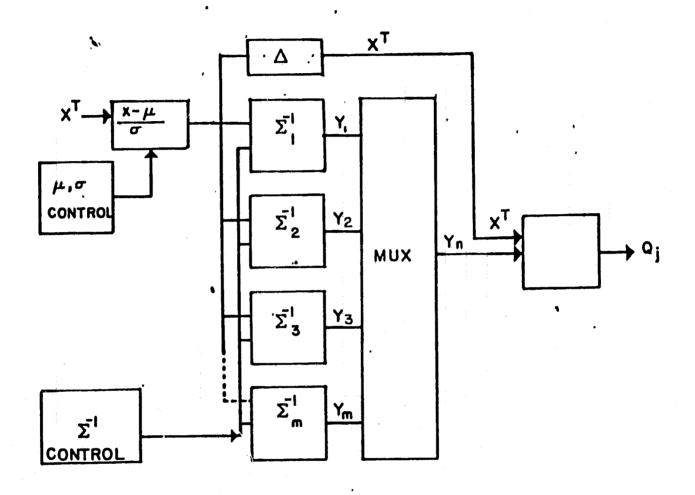

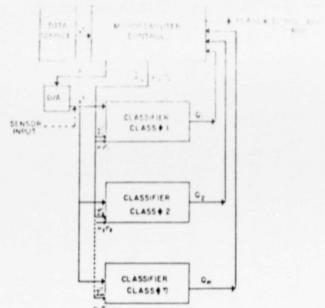

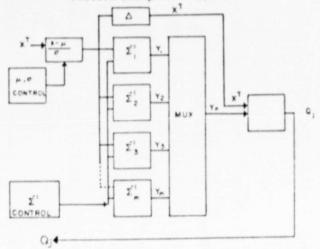

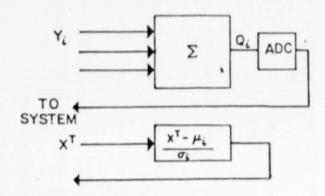

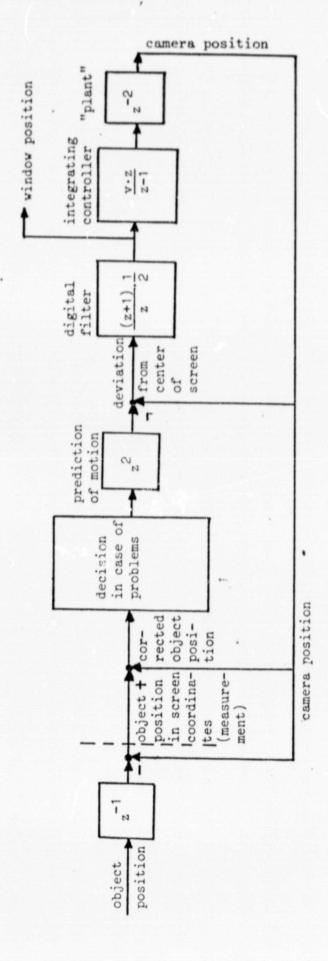

Figure 3.1 illustrates a proposed layout of sum of product CTDs (SOPs) which may be used to calculate the discriminant function. In this arrangement each of the first group of SOP devices ( $\Sigma_i$  -- $\Sigma_m$ ) perform one of the row-column multiplications of the  $\overline{\mathbf{x}}$ - $\overline{\mathbf{u}}_i$   $^{\mathrm{T}}C_i^{-1}$  term of the discriminant function calculation. The results from these operations are then multiplexed into the final SOP device along with the  $\overline{\mathbf{x}}$ - $\overline{\mathbf{u}}_i$  term producing the desired final result. It is seen that this configuration requires at least two CTD loading times to perform the calculation.

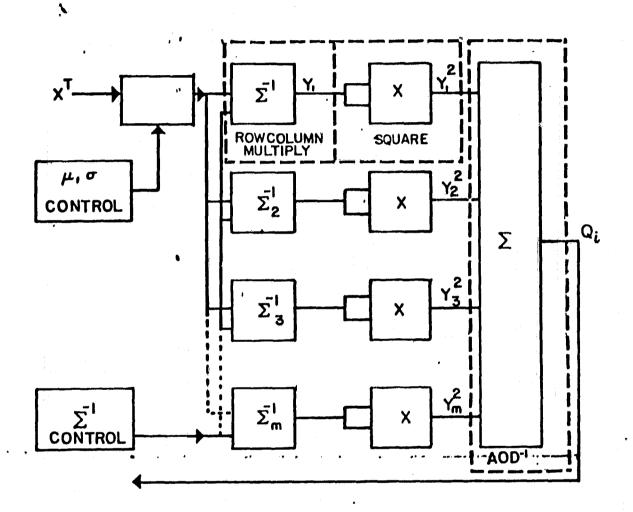

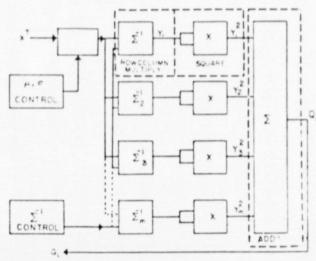

A reduction of the calculation time to one SOP device loading time would be highly desirable. Figure 3.2 shows an arrangement which accomplishes this reduction by eliminating the multiplexer and the final CTD. The diagonal symmetry of the covariance matrix allows this simplification because the matrix may be transformed into upper triangular form. In this case the SOP devices perform the  $C_i^{-1}$   $\overline{x}$ - $\overline{\mu}_i$  calculation as before. These results are then each squared and the results summed to produce the answer.

Figure 3.1 Functional Layout of Classifier

Figure 3.2 Layout of Classifier with Higher Speed Capability

#### 4 DEVICE EVALUATIONS

### 4.1 AAC-32

Once the matrix multiplier configuration was derived an evaluation of the available devices was needed. A detailed account of the evaluation techniques and testing set-up hardware is given in the 1977 report.

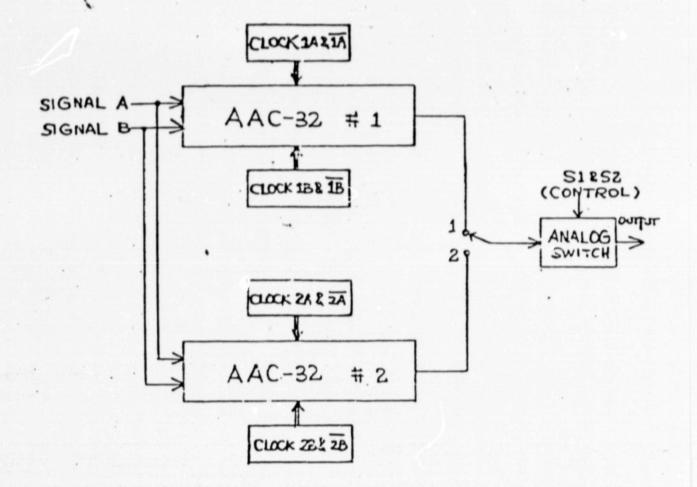

The first device evaluated was the Reticon AAC-32, a bucket brigade device. This chip contains two tapped 32 cell delay lines with an untapped or "dead" cell at the start of one delay line and the end of the other. Thirty-two on-board multipliers and a summer compute the sum-of-products function.

After determining values for the various bias voltages and currents required by the chip, tests were made to determine proper signal levels and to evaluate the performance of the device.

Zeroing and signal level adjustments were satisfactorily executed, then linearity, accuracy, and repeatability were examined.

The results showed an accuracy of about 5 bits and a repeatability of about 8-9 bits with the variance appearing to be the result of random noise. Also noted were short-term and long-term drifts when the device was left unclocked and a start-up inaccuracy. These results all appeared to indicate that the device was acceptable for a matrix multiplication application.

The AAC-32 however, showed a exhibited a serious linearity problem: in one quadrant, the output was severely clipped.

Adjustments and reductions of the input could not remove the clipping. The failure appeared to be caused by the multipliers; observations of the delayed signal after it passed through the

bucket brigade showed no distortion problems. This non-linearity caused the AAC-32 to be ruled unsuitable.

# 4.2 <u>R5402/5403</u> <u>Series</u>

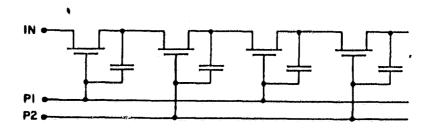

The Reticon R5402/5403 chips are revised versions of the AAC-32 which do not exhibit many of the earlier chip's problems. The difference between the 5402/5403 chips is in the number of taps: the R5402 has 16 taps; the R5403 has 32. A major change in both chips from the AAC-32 is the presence of a string of storage capacitors on one side of the device. The input signal on that side passes down the string of capacitors and is passed in parallel to the bucket brigade upon a sample and hold strobe signal.

The tests performed on the AAC-32 were repeated on the R5402/5403, and the results were encouraging. The chips exhibited acceptable accuracy (~7-8 bits) and repeatability and did not have the linearity problems of the AAC-32. The conclusion of the evaluation of the R5402/5403 was that the chips' performance was marginally satisfactory and that the design of a classifier around these devices should proceed.

### 5 CLASSIFIER SYSTEM DEVELOPMENT

### 5.1 Organization

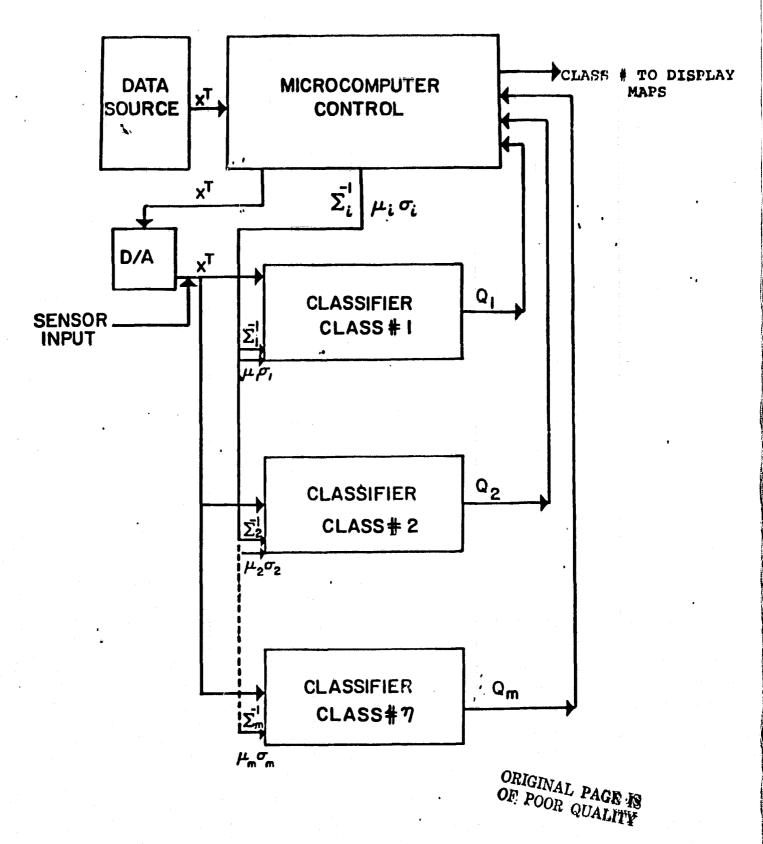

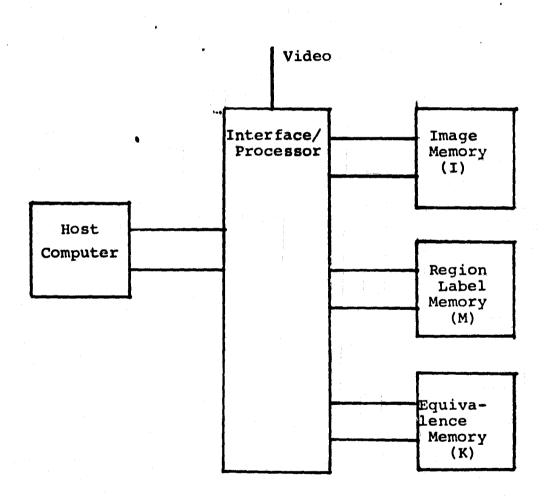

Figures 5.1 and 5.2 illustrate the functional blocks and data flow of the classifier system. Figure 5.1 shows the set-up of a general classifier system while Figure 5.2 shows the set-up of the prototype system designed around the Reticon devices.

Figure 5.1 Block Diagram of General Classification System

Figure 5.2 Block Diagram of Prototype System

In Figure 5.1 the sensor input could be directly from a LANDSAT sensor after optical and geometric corrections have been made, and the data source could be RAM built into the system for storing the necessary mean and covariance information. In the prototype system, however, the LSI-11 is the controlling microcomputer while the floppy disk serves as the sensor input by storing a LANDSAT image. All of the classifier hardware: CTD's, signal conditioning and conversion circuitry, RAM, and controlling circuitry is contained in one block, and communication with the LSI-11 is over two parallel data buses (16 bits in each direction per interface). The terminal is a 512x256 point color graphics display and serves as an output for the classified images. A more detailed description of the system is given in the 1979 report.

### 5.2 Hardware

### 5.2.1 Classifier Module Organization

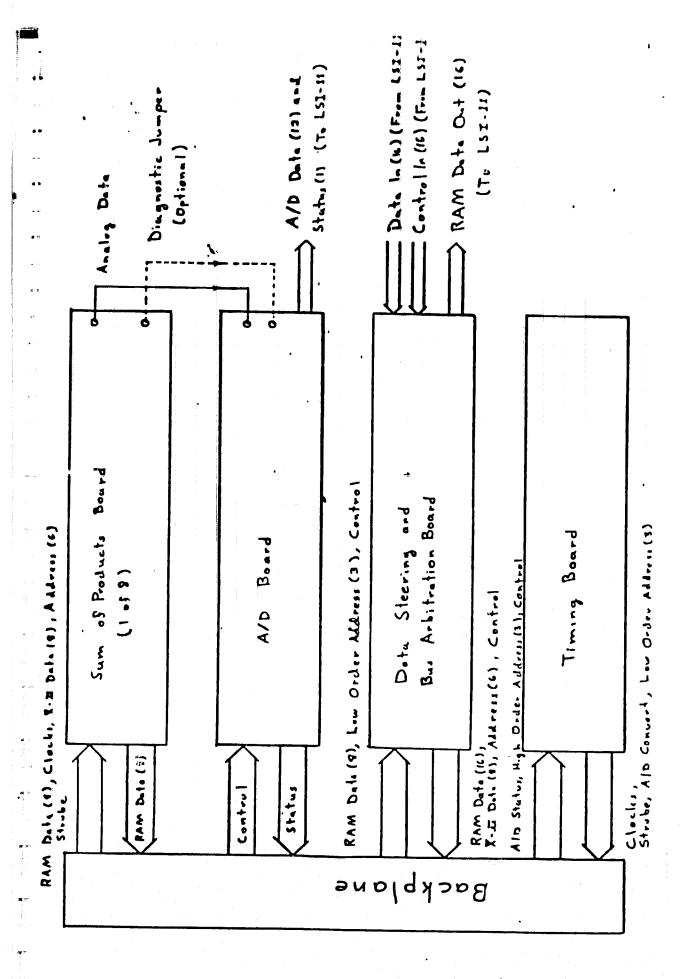

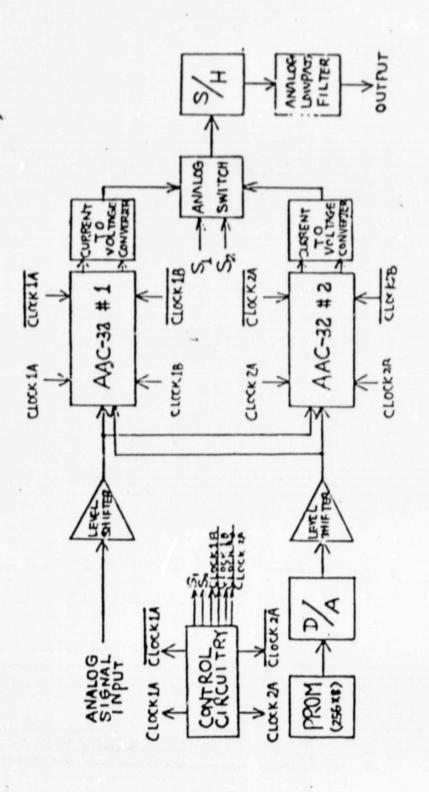

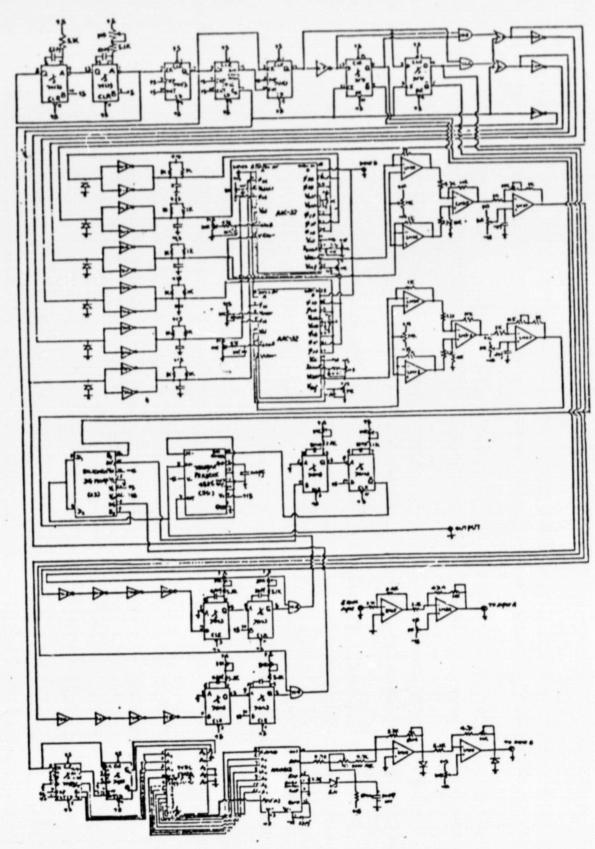

This section contains a description of the classifier modules and their operation. These modules are: analog boards, timing and control/interface, and analog-to-digital conversion. Figure 5.3 indicates how these modules are integrated to form the classifier system. The modules all plug into a backplane over which the digital TTL level signals and power pass. The analog signals are not sent over the backplane over which the digital TTL level signals and power pass. The analog signals are not sent over the backplane to reduce potential noise problems; instead, they are passed from board to board by shielded cables. Except fo the A/D converter data output, a single board provides the required interface with the LSI-11.

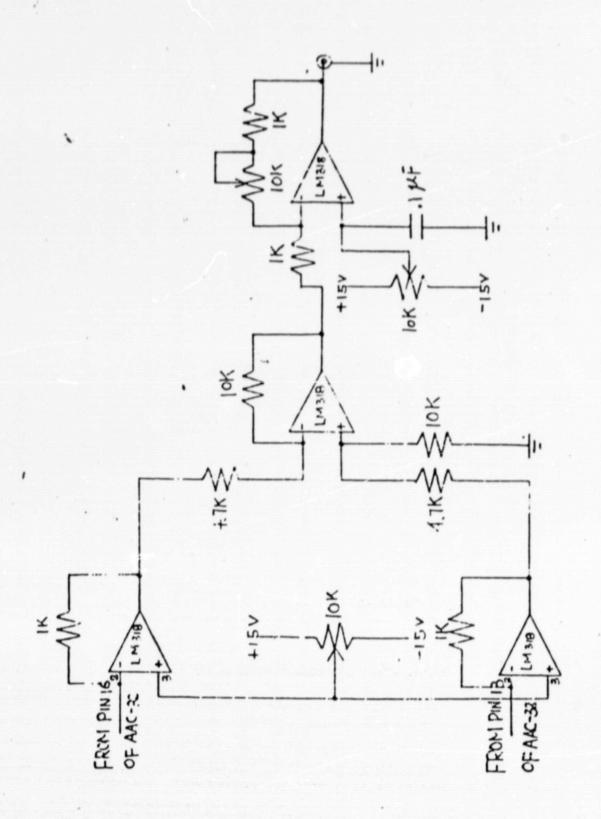

# 5.2.2 Analog Board

The major functional component of the classifier is the analog or sum-of-products board. Eight of these boards form the core of the classifier; each contains a CTD and squaring circuit; the necessary D/A conversion, signal conditioning, and bias circuitry, and the RAM which is loaded with the appropriate column of the covariance matrix inverse. Upon receipt of the proper data and control signals each of these boards will cycle the CTD producing the row-column vector dot product and squaring the result. An analog multiplexer is included for diagnostic monitoring of critical on-board signal points.

Figure 5.3 Classifier Module Organization and Data Flow

ORIGINAL PAGE IS

Appendix A contains the schematic of the analog board along with a diagram of the printed circuit card layout for the board and a parts list.

### 5.2.3 Timing and Interface Modules

The functions of the timing and control module and the interface module are closely intertwined; for that reason, they will be discussed together in this section. Clocking, control, data steering, and interfacing with the LSI-ll are accomplished by these modules. Ten circuit groups make up the two modules:

- (1) Transition Detector (TD)

- (2) Counter Clock Reset/Enabler (CDREC)

- (3) Counter and Decoder Circuit (CDC)

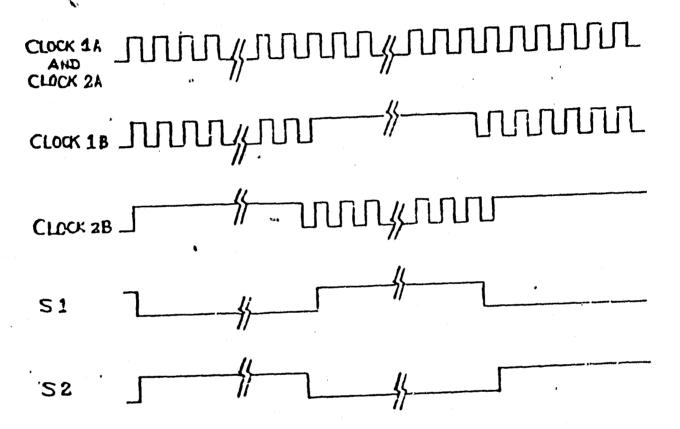

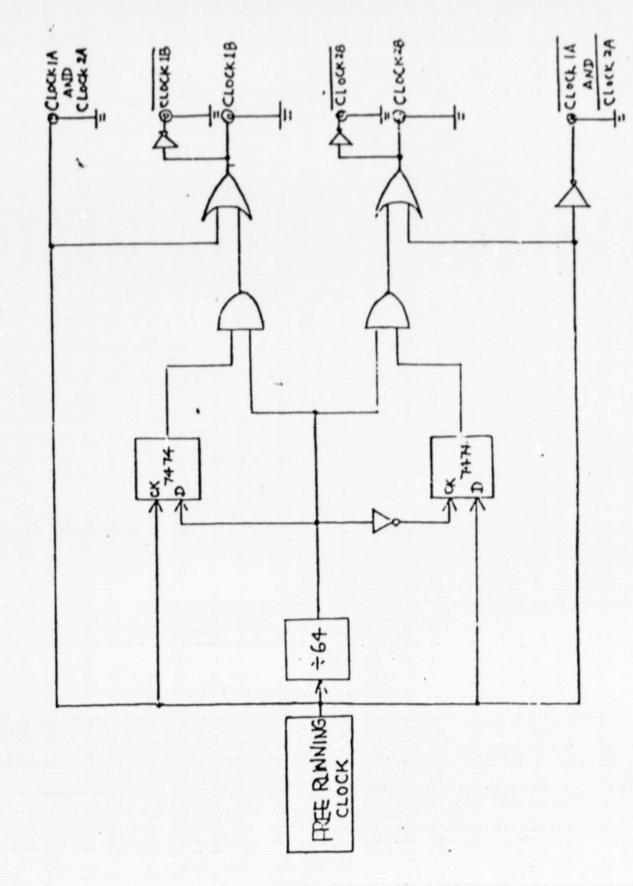

- (4) Clock Generator Circuit (CGC)

- (5) Address Bus Arbitrator (ABA)

- (6) Mode Decode (MD)

- (7) Subtractor (SUB)

- (8) A/D Conversion Decoder (ADCD)

- (9) Master Clock Generator (MCG)

- (10) Chip Enable Decoder (CED)

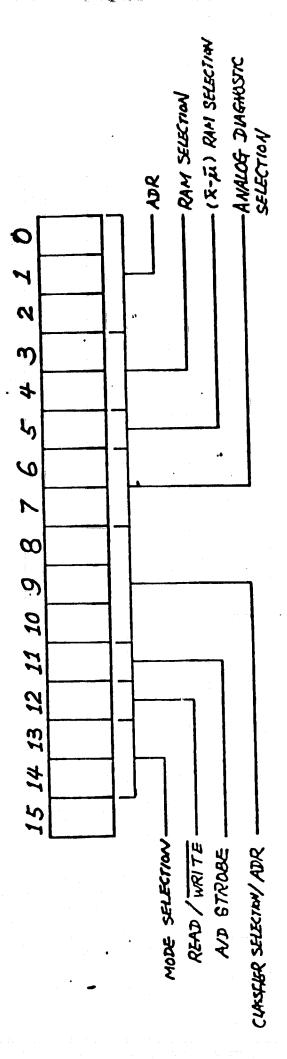

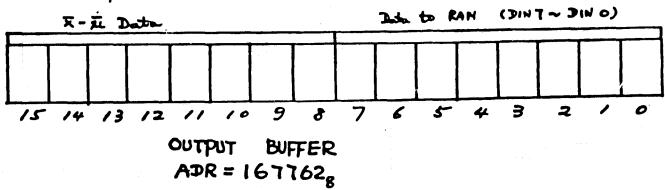

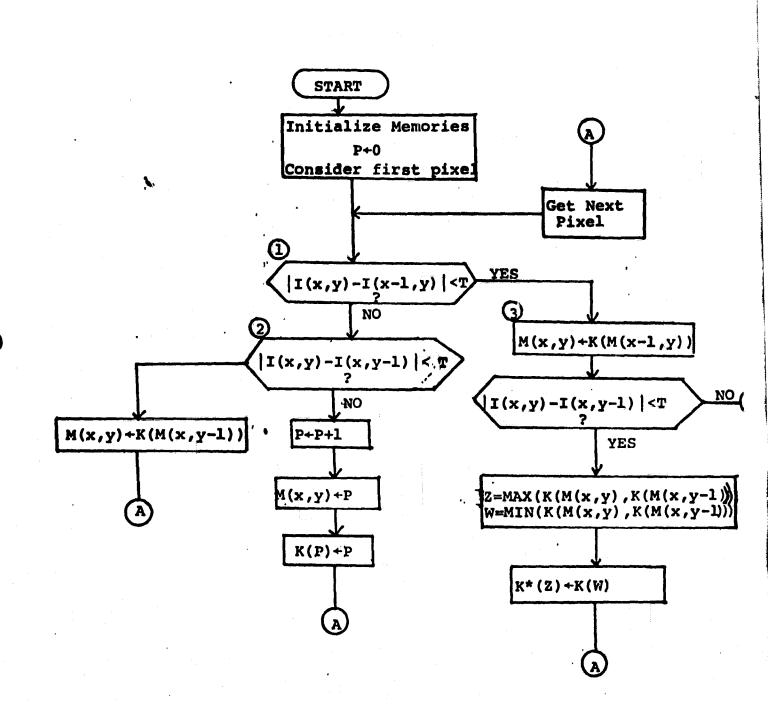

The instructions arrive from the LSI-ll in the form of a 16-bit control word (see Figure 5.4). There are three basic operating modes for the classifier: LOAD, DIAGNOSE, and RUN. In LOAD mode the LSI-ll has control of the address bus and is loading new information for the classifier to process. In the DIAGNOSE mode the LSI-ll is driving different parts of the classifier to test their performance. In both of these modes the LSI-ll controls the backplane bus, and the CTD output data is invalid.

Figure 5.4 Control Word Format

In the RUN mode classifier operations proceed normally with the backplane bus controlled by the timing circuitry. These modes are selected by the mode selection bits (13-14) of the control word which are decoded by the Mode Decoder.

The Address Bus Arbitrator is a three-line multiplexer that has, as inputs, the three low order address bits of the control work and the three low order bits from the CDC, and has the three low order bits of the backplane address bus as outputs. When the classifier is in LOAD or DIAGNOSE mode the Arbitrator allows the LSI-11 to control these three bits, otherwise the timing circuitry exercises control.

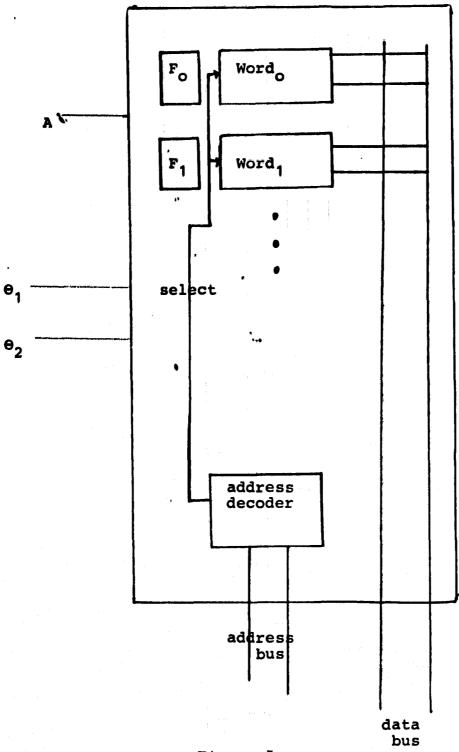

The RAM selection bits (3,4,5) of the control word) go to the Chip Enable Decoder. This circuit has 6 output lines; the RAMs on the analog boards are enabled, two at a time, by four of these, the x-RAM is enabled by the fifth, and the  $\mu$ -RAM is enabled by the last. During RUN mode this circuit is bypassed and all RAMs are enabled.

The Data Output Bus Enable selects the pair of RAM output bus drivers to be enabled. This selection is necessary to avoid having two RAMs attempting to control the backplane bus. This circuit is located on each of the analog boards.

The Subtractor is simply an ALU set to continually perform the necessary subtraction to obtain the  $\overline{x}$ - $\overline{\mu}$  term. The inputs come from the x-RAM which is loaded once per pixel and the  $\mu$ -RAM which is loaded once per image.

The Transition Detector generates a single pulse to initiate a new cycle of the CTDs to produce the discriminate function results. This pulse is generated when the classifier is in the RUN mode and a change is detected on the three high order address bits.

The Counter Clock Reset/Enabler generates the signals to clock the CTD. When the CDC receives a Counter Enable signal from the CDREC it will begin the loading of the CTD. The Clock Enable signal is sent to the CGC to enable the CTD clocks.

In addition to the Counter Enable signal, the CDC receives the Master Clock from the MCG. The data is loaded into the CTD twice (assuming an eight-feature vector); this method should yield better accuracy than loading once and padding with zeros. During loading four outputs are produced. Three of these are low-order addresses and go to the address arbitrator. The other output is the Count Finished signal issued when the loading cycle is complete.

In addition to the Clock Enable and Count Finished signals the CGC receives the Master Clock signal and the three decoded mode signals. The clocks are always enabled during the LOAD and DIAGNOSE modes, and during RUN mode the clocks are started when the Count Enable signal is true. When the Count Finished signal is received one more clock cycle is applied to the A side of the CTD to correctly align the data because of the "dead" cell. The clocks are now halted, and the CTD is strobed to pass the data from the capacitors to the bucket brigades. The Load Ready strobe is now sent to the A/D Conversion Decoder.

The A/D Conversion Decoder generates the convert command that activates the A/D converter. In Run mode this command is controlled by the Load Ready Strobe, and in the other modes it is under the control of the LSI-11. The signal "A/D status" is generated by the A/D converter upon completion of its operation. This signal is used to restart the CTD clocks to avoid drifts and to signal the LSI-11 to read the A/D.

### 5.2.4 A/D Board

The A/D converter is the same 12 bit,  $30\mu sec$  Analog Devices module used in the chip evaluations and operates in the same fashion.

In addition to the A/D converter the board contains the summers for the eight signals from the analog boards. Switching is also provided between the summer output and a diagnostic signal jack used for monitoring various points on the analog boards during testing.

### 5.3 Testing Software

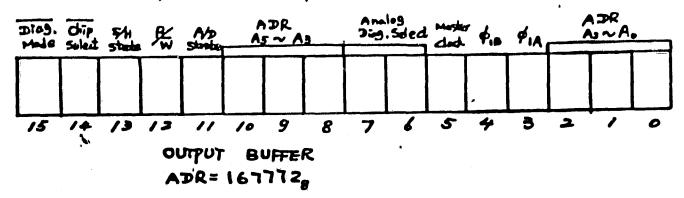

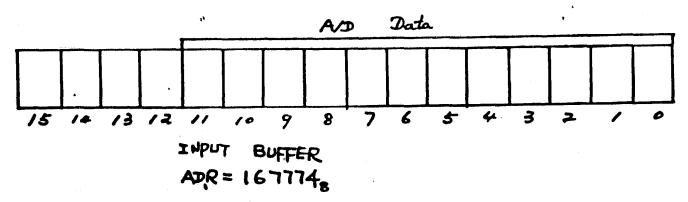

Special arrangements were necessary for testing of the analog boards. A testing stand was constructed to allow the board to be exercised without the full classifier. A subset of the control word signals which was necessary for the operation of the analog board was used. Clocks, control, and data which are normally provided internally were added. The revised communication word formats are shown in Figure 5.5. The purposes of the system were to check out the RAM on the board and to adjust the signal levels and offsets of the CTD inputs.

The adjustment algorithms are similar to those used for the device evaluation. These algorithms are discussed in the previous reports. We are including two new RAM testing programs here; Appendix D contains program listings.

# SECOND DRV-11

Figure 5.5 Revised Communication Word Formats fdr Testing

ADR = 1677648

### 1. Program RAMTSB

RAMTSB checks the RAM in a bit-by-bit fashion. It loads the RAM with 1 at the first bit of the first location then checks the output. It then loads the RAM with 0 and checks the output. If the outputs are not consistent with the input data an error is logged. The testing sequence is from the first bit of the first location to the first bit of the last location (63). The program then checks the second and remaining bits in the same manner.

### 2. Program RAMTST

This program is an abbreviated version of RAMTSB which tests the RAM in a byte-by-byte fashion. It will not find all possible errors, but it may serve as a quick first test of the RAM operation. The program operates by loading each location with all 1's and all 0's and examining the result.

#### 6 CONCLUDING REMARKS

The principal goal of this project has been the evaluation of Charge Transfer Devices and their potential use in pattern classifiers. As such, much of the work has been centered around testing the devices rather than construction of a final system. Since the devices were experimental and the application was new the work often involved a "ground-up" approach. In the case of the AAC-32, for example, very little information was available regarding optimum operating points, etc. In addition, some traditional types of tests were found to produce misleading results, for

example, the correlation of two sampled analog sine waves appeared to produce very good performance i.e., a high signal-to-noise ratio. It was not until the testing methodo-logy was rethought and a different form of test was applied that the problems with the device became evident.

Three general conclusions may be drawn from the work:

- (1) With the advent of "variable tap weight" devices there is a strong potential for the use of CTDs in pattern classifiers. They can be used to provide matrix multiplication subsystems. Suitable architectures were developed in this project, and their potential performance is good. The time required to produce an answer has been reduced to one CTD loading time. Further, such a classifier architecture allows the parallel computation of all of the discriminate functions (i.e. up to eight in this case) at once. Such a system of very fast, low power classifiers could be of tremendous benefit in processing data from sources such as LANDSAT satellites, particularly by making on-board classification feasible. This could make the use of pattern classification techniques and satellite data much more widespread, and could open the door to new uses of the techniques which are not possible now because of prohibitive computational requirements and their resulting delays or high cost.

- (2) The evaluation of the Reticon AAC-32 clearly showed that it is not suitable for use in a classifier application. The failure did not, however, rule out the use of CTDs in classifiers because it appeared to result from a design problem in the analog multipliers rather than the CTD technology. It is interesting to note that if the failing quadrant was avoided, the AAC-32 did show usefulness in other applications such as programmable transversal filters. (See Appendix C).

The Reticon R5402/5403 indicated the validity of the conclusions since it did not have the problems of the AAC-32. The performance of these new devices indicated that they were candidates for matrix multiplication applications.

(3) A design for a micro-computer controlled classifier using the R5402/5403 chips was accomplished, and the paper system has a reasonable size, complexity, and power consumption. The further devleopment of the system for testing and evaluation purposes is recommended.

This project has by no means concluded that a CTD based classifier will operate well, only that such a system appears to be possible. The only was to accurately guage the performance of a CTD based classifier is to build and test it as is recommended. Several questions remain which cannot be answered simply by testing devices. These questions include: the stability of the system, particularly the analog interface and signal conditioning circuitry; the effects of long term drifts and aging on the accuracy of the total system when added together; the speed at which the total system may be operated, and the reliability of the devices when operated in such a system. The CTD technology is developing rapidly, and performance characteristics can certainly be expected to improve in the future. This project and other novel applications of the devices will certainly aid in indicating areas of technology development which need improvement and would increase the chances of the production of future devices which could operate even better.

# APPENDIX A

ANALOG BOARD SCHEMATIC AND PARTS LIST

The schematic is oversized and has been sent to NASA under separate cover.

# Edge View from Pins

|                                       | •             |

|---------------------------------------|---------------|

| · · · · · · · · · · · · · · · · · · · | 2 RMINXTI     |

| . 3                                   | 4 RMTN's 6 I  |

| 5                                     | 6 RMINISI     |

| 7                                     | 1             |

| •                                     | 9 RMINY 41    |

| · · · · · · · · · · · · · · · · · · · | · PWINX3I     |

|                                       | 12 RMTNx 27   |

| 1-3                                   | · 4 PMINY 1 I |

| 16                                    | 16 RMTNXOI    |

| 17 ADDRST                             | 1 8 RWNOTI    |

| 19 ADDR41                             | 20            |

| 2   ADDR3I                            | 2 2 YMUDAT 7I |

| 23 ADDRZI                             | 24 XMUDATET   |

| . 25 ADDRII                           | 26 XMUDAT53   |

| 27 ADDROI                             | 2 % XMUDATHI  |

| 29 +15 V DL 0                         | 30 XMUDATET   |

| 31 GND<br>33 -15 V DC                 | 3 2 XMUDATOT  |

| 33 -15 V DC                           | 3 4 XMUDATII  |

|                                       | 36 XMUDATUI   |

| 37                                    | 3 9           |

| 33 45 V. DC Wiring                    | 40            |

| 41                                    | 43            |

| 43 Sta                                | 44            |

| 15 Rmour, go                          | 46            |

| 4'7 RMOUT, 10                         | 48 DIAMODET   |

| 4'9 RMOUTY 20'                        | 50 CHSELII    |

| 51 RMOUT.30                           | 5 2 AICLKI    |

| 53 RMOUTX 40                          | 54 MASCLKT    |

| ES RMOUTY 50                          | 56 Biclki     |

| 57 RMOUTER                            | 58 DIASELIT   |

| 59 RMOUTY TO                          | GO DIASELOT   |

| 41                                    | 62 CIDSTRBI * |

| 6 3                                   | . 64          |

| 65                                    | 66            |

| 6:7                                   | 68            |

| 6 9 ÖRIGINAL PAGI                     |               |

| 7 / OF POOR QUAL                      |               |

| 73 +15 V DC                           | 7 4           |

| 7 5 GND                               | 7 (           |

| 77-15 V DC                            | 78            |

| 79 + 5 V DC                           | 80            |

|                                       |               |

All signals TTL compatible unless otherwise specified.

All unnamed pins reserved for future expansion.

- x Depends upon slot

- \* This signal is 0-+15V

# Timing Board Pin Definitions

# Edge View from Parts

|          | •                  | 700 and 45 2 .g                          | •                  |            |

|----------|--------------------|------------------------------------------|--------------------|------------|

|          |                    |                                          | .2                 |            |

|          | 3                  | 300° 00° 00° 00° 00° 00° 00° 00° 00° 00° | 4                  |            |

| * / * .  | <u>.</u>           |                                          | · .c               |            |

|          | .7                 |                                          | 9                  |            |

| 7        | 1                  | •                                        |                    |            |

|          | . 11               | And the second second second             | 12                 |            |

| •        | 1.3                | <b>*</b>                                 | 1 4                | ·          |

|          | 15                 | •                                        | 1.6                |            |

|          | · ·                |                                          |                    |            |

|          |                    |                                          | <u>.1.8</u> .      |            |

| 1        | 19 ADDR4I          |                                          | 20 ADSTRBI         |            |

|          | 21 ADDR31          |                                          | <u>a a</u> '       |            |

|          | 33                 |                                          | 24                 |            |

|          | 25                 | ,                                        | 26                 |            |

|          | <b>4</b> 7         |                                          | 2 (<br>2 <b>8</b>  |            |

|          | 29 +15 V DC        |                                          | 3 0                |            |

|          | 31 GND             |                                          | 3 2                |            |

| i        | 33 - 15 V DC       | SO                                       | 3 4                |            |

| ·        | 35 + 5 V 1 Dc      | 1d                                       | 3 4                | . <b>C</b> |

| +        | 37                 | Solder,                                  | 38                 | da da      |

| 1        | 3 9                |                                          | . 40               | Computer   |

| 1        | 41                 | Wir                                      | 43                 | er         |

| 1.       | +3.                | بسر                                      |                    | •          |

|          |                    | i i i                                    |                    | Side       |

|          | ·4·7               | ະ , ຄ                                    | <u> 4 C</u>        | <u>.</u>   |

|          | 4 9                |                                          | 48                 |            |

|          |                    | (0                                       | <u>5. 0</u>        |            |

|          | 5.1                |                                          | <u>5.2</u>         |            |

|          | 53                 |                                          | 54                 |            |

|          |                    | aganda garage                            | <u>5 (</u>         |            |

|          | 57                 | and the state of the state of the        | ***** <u>**5\$</u> |            |

|          | 159                | •                                        | 60                 |            |

|          | & 1 RUNMODET       | ••                                       | - 42               |            |

|          | 63 DIAMODET        |                                          | 64                 |            |

|          | 65 LODMODEI        |                                          | 66                 |            |

|          | 67 CTRADR20        |                                          | · 6 8 CTDSTRBO *   |            |

|          | 69 CTRADRIO        | * *                                      | 70 ADENVO          |            |

|          | 71 CTRADERO        |                                          | 72 ADSTATI         |            |

|          | 7 5 415 V DC       | •                                        | 74 MASCLKO         |            |

|          | 75 GND             |                                          | 76 A1CLKO          |            |

|          | 77-15 V DC         |                                          | 78 B1CLKO          |            |

| 1        | 79 + 5 V DC        |                                          | 80                 |            |

|          |                    |                                          |                    |            |

| IAll eid | anals TTL compatib | פו                                       |                    |            |

All signals TTL compatible unless otherwise specified.

\*This signal is 0-+15V

All unnamed pins reserved for future expansion.

# Interface and Data Steering Board Pin Definitions

### Edge View From Pins

| •            | •            | •              |

|--------------|--------------|----------------|

| 1 RMINL 70   |              | 2 RMINRTO      |

| 3 RMINLGO    |              | 4 RMINIRGO     |

| 5 RMINLEO    |              | 6 RMINRSO      |

| 7 RMINL40    | •            | 3 RMINRHU      |

| 9 RMINL30    |              | 10 RMJNRSD     |

| II RMINLOD   |              | 12 RMINROD     |

| 13 RMTNLID   |              | 14 RMTNR10     |

| 15 RMINLOO   | •            | 16 RMINRUO     |

| 17 ADDR50    | •            | 18 RWNOTO      |

| 19 ADDRYO    |              | 20 ADSTRBO     |

| 2   ADDR30   |              | 22 XMUDATTO    |

| - 23 ADDRZU  |              | 24 XMUDATED    |

| 25 ADDRIO    |              | 26 . XMU DATS: |

| 27 ADDRUO    | •            | 2 & XMUDATEC   |

| 29 415 V DC  | "<br>1       | 30 XMUDATO     |

| 31 GND       | 70           | 3 2 XMUDATAD   |

| 33 -15 VDC'  |              | 3 4 X MUDATE   |

| 35 +5 V DC   | lder/        | . 36 XMUDATOO  |

| 37           | /13          | 3 9            |

| 3 9          | ¥.           | 40             |

| 41           | Wiring       | 43             |

| 4.3          | .ng          | 44             |

| 45 RMOUTRET  | ro           | 46 RMOUTLAT    |

| 47 RMOUTRIT  | 3 <u>1</u> d | 48 RM OUT L 1T |

| 44 RMOUTROI  | r ·          | 50 RMOUTLOI    |

| 51 RMOUTRST  |              | 52 RMOUTL3I    |

| 53 RMOUTRYI  |              | 54 RMOUTL4I    |

| 55 RMOUTRSI  |              | 56 RMOUTLSI    |

| 57 RMOUTRGI  |              | 58 RMOUTLGI    |

| 59 RMOUTRTI  |              | GO RMOUTL7I    |

| & 1 RUNMUDEO |              | 62 CHSEL30     |

| 63 DIAMOREO  |              | 64 CHSELRO     |

| 65 LODMODED  |              | 66 CHSELLO.    |

| 67 CTRADEST  | •            | 69 CHSELDO     |

| 69 CTRADRII  |              | 70 DIASCLIO    |

| 71 CTRADRET  |              | 72 DIASELOC    |

| 75 +15 V DC  |              | 74 MASCLKI     |

| 7 5 GND      |              | 76             |

| 77 -15 V DC  |              | 78             |

| 79 +5 V DC   |              | 80             |

All signals TTL compatible unless otherwise specified.

All unnamed pins reserved for future expansion.

| 13                                                       |             |

|----------------------------------------------------------|-------------|

| 1 5                                                      |             |

| 17                                                       |             |

|                                                          |             |

| _2 1                                                     |             |

| 23                                                       |             |

| 32                                                       |             |

| <b>2</b> 7                                               | õ           |

| 29 +15 V DC                                              | ld€         |

| 31 GND<br>33-15 V DC                                     | , it        |

| 33-15 V DC                                               | Solder/Wiri |

| 35+5 NDC'                                                | Ħ.          |

| 3.7                                                      | ing         |

| 39                                                       | เก          |

| 41                                                       | Side        |

| 43                                                       | O           |

| 46                                                       |             |

|                                                          |             |

|                                                          |             |

| 4 9                                                      |             |

| 4 9 5 1                                                  |             |

| 4 9<br>5 1<br>5 3                                        |             |

| 4 9<br>5 1<br>5 3<br>5 5                                 |             |

| 4 9<br>5 1<br>5 3<br>5 6<br>5 7                          |             |

| 49<br>51<br>53<br>55<br>57                               |             |

| 49<br>51<br>53<br>56<br>57<br>59                         |             |

| 49<br>51<br>53<br>56<br>57<br>59<br>61<br>63 DIAMUDE I   | e e         |

| 49<br>51<br>53<br>56<br>57<br>59<br>61<br>63 DIAMUDE I   |             |

| 49<br>51<br>53<br>56<br>57<br>59<br>61<br>63 DIAMUDE I   | · •         |

| 49<br>51<br>53<br>56<br>57<br>59<br>61<br>63 DIAMUDE I   |             |

| 49<br>51<br>53<br>56<br>57<br>59<br>61<br>65<br>67<br>61 |             |

| 49<br>51<br>53<br>56<br>57<br>59<br>61<br>63 DIAMUDE I   |             |

| <u>2</u>                                                                                                   | <del></del>      |

|------------------------------------------------------------------------------------------------------------|------------------|

| 4                                                                                                          |                  |

| <u>L</u>                                                                                                   |                  |

| 9                                                                                                          |                  |

| 10                                                                                                         |                  |

| 13                                                                                                         |                  |

| _14                                                                                                        |                  |

| 16                                                                                                         |                  |

| 18                                                                                                         |                  |

|                                                                                                            | <del></del>      |

| 32                                                                                                         |                  |

| 24                                                                                                         | ·                |

| 26                                                                                                         |                  |

| 2 8                                                                                                        |                  |

| 30                                                                                                         | ·                |

| 3 2                                                                                                        |                  |

| 3 4                                                                                                        |                  |

| 36                                                                                                         |                  |

| 38                                                                                                         |                  |

|                                                                                                            |                  |

| 40                                                                                                         |                  |

| 40                                                                                                         | $\times$         |

|                                                                                                            | $\times$         |

| 4 2                                                                                                        |                  |

| 4 6                                                                                                        |                  |

| 46 46                                                                                                      |                  |

| 4 2<br>4 4<br>4 6<br>4 8<br>5 0                                                                            |                  |

| 4 5<br>4 4<br>4 6<br>5 0<br>5 2                                                                            |                  |

| 4 2<br>4 4<br>4 6<br>4 8<br>5 0<br>5 2<br>5 4                                                              |                  |

| 4 5<br>4 4<br>4 6<br>5 0<br>5 2<br>5 4<br>5 6                                                              |                  |

| 4 2<br>4 4<br>4 6<br>4 8<br>5 0<br>5 2<br>5 4<br>5 6<br>5 8                                                |                  |

| 4 2<br>4 4<br>4 6<br>4 8<br>5 0<br>5 2<br>5 4<br>5 6<br>5 8<br>6 0                                         |                  |

| 4 2<br>4 4<br>4 6<br>4 8<br>5 0<br>5 2<br>5 4<br>5 6<br>5 8<br>6 0                                         |                  |

| 4 2<br>4 4<br>4 6<br>4 8<br>5 0<br>5 2<br>5 4<br>5 6<br>5 8<br>6 0                                         |                  |

| 4 2<br>4 4<br>4 6<br>4 8<br>5 0<br>5 2<br>5 4<br>5 6<br>5 8<br>6 0                                         |                  |

| 4 2<br>4 4<br>4 6<br>5 0<br>5 2<br>5 4<br>5 6<br>5 8<br>6 0<br>6 4<br>6 6                                  | OC NVI           |

| 4 2<br>4 4<br>4 6<br>4 8<br>5 0<br>5 2<br>5 4<br>5 6<br>5 8<br>6 0<br>6 4<br>6 6<br>6 6<br>6 8             | TVNDC            |

| 4 2<br>4 4<br>4 6<br>5 0<br>5 2<br>5 4<br>5 6<br>5 8<br>6 0<br>6 2<br>6 4<br>6 6<br>6 6<br>7 0 A1<br>7 2 A | DC NVI<br>DSTATO |

| 4 2<br>4 4<br>4 6<br>4 8<br>5 0<br>5 2<br>5 4<br>5 6<br>5 8<br>6 0<br>6 2<br>6 4<br>6 6<br>6 6<br>7 2 A    | DENVI            |

| 4 2<br>4 4<br>4 6<br>5 0<br>5 2<br>5 4<br>5 6<br>5 8<br>6 0<br>6 2<br>6 4<br>6 6<br>6 6<br>7 0 A1<br>7 2 A | DC NVI<br>DSTATO |

80

All signals TTL compatible unless otherwise specified.

All unnamed pins reserved for future expansion.

Computer Side

Right

The board used is a double sided PCB, with 72 possible gold finger contact evenly distributed in both sides, the space between contacts is .125 in., the base material used is FR4, the overall size of the board is  $\frac{1}{2}$ , 7.1 x 5.2 in.

#### PARTS LIST

#### RESISTANCES

The following values are given in Kohms and are assumed to be of 5% tolerance and 1/4 W maximum dissipation, unless otherwise especified.

| location | value(Kohms) | location | value(Kohms)  |

|----------|--------------|----------|---------------|

| R1       | . 1.         | R41      | 150           |

| R2       | 10.          | R42      | 62.           |

| R3       | 20. "        | R43      | 42.           |

| R4       | 1.           | R44      | 100.          |

| R5       | 10.          | R45      | 15,           |

| R6       | 20.          | R46      | 2.            |

| R7 .     | 10.          | R47      | <b>68</b> .   |

| RB       | 1.           | R48      | 300.          |

| R9       | 1. 0         | R49      | <b>33</b> . • |

| R10      | 10.          | R50      | 100.          |

| R11      | 20.          | R51      | 100.          |

| R12      | <b>1</b> ,   | R52      | 1.            |

| R13      | 20.          | R53      | 100.          |

| R14      | 20.          | R54      | 1.            |

| R15      | 2.           | R55      | 10.           |

| RIS      | 10.          | R55      | 5. 1          |

| R17      | 20.          | R57      | 1.            |

| R18      | 2.           | R58      | 10.           |

| R19      | 10.          | R59      | <b>5.</b> 1   |

| R20      | 20. ·        | R60      | 1.            |

| R21      | 10.          | R61      | . 62          |

| R22      | 4. 7         | R62      | , 62          |

| R23      | 20.          | R43      | , 62          |

| R24      | 10.          | R64      | , 62          |

| R25      | 4. 7         | R65      | . 62          |

| R26      | 10.          | R66      | . 62          |

|          |              | R67      | . 62          |

| R28      | 20.          | R68      | . 62          |

| R29      | <b>1</b> ,   | R69      | . 62          |

| R30      | 56.          | R70      | 2.            |

| R31      | 15.          | R71      | ₽.            |

| R32      | 100, ohms    | 72       | 2.            |

| R33      | 20.          | R73      | 2.            |

| R34      | 270.         | R74      | 5. 1 ohms     |

| R35      | 100.         | R75      | 5. 1ohms      |

| R36      | 62.          | Ŕ76      | . 47          |

| R37      | 160.         | R77      | . 47          |

| R38      | 120.         | R78      | . 47          |

| R39      | 150.         | R79      | . 47          |

| R40      | 100.         | RBO      | 20.           |

#### CAPACITORS

The following capacitors are given in uF with 15 Vdc ratings and tolerances better to 10% unless otherwise specified.

| location | value |    | location    | vulue |

|----------|-------|----|-------------|-------|

| C1       | 15p f |    | C28         | 9. 1  |

| CZ       | 0. 1  |    | C29         | 0. 1  |

| c3 ·     | 0. 1  |    | C30         | 0. 1  |

| C4       | 15pf  |    | C31         | 0. 1  |

| C5       | 0. 1  |    | CBS         | 0, 1  |

| C6       | 0. 1  |    | C33         | 0. 1  |

| C7       | 0. 1  |    | C34         | 0. 1  |

| C8       | 15pf  |    | C35         | 0, 1  |

| C9       | 0. 1  |    | C36         | 0, 1  |

| C10 .    | 0. 1  |    | C37         | 0, 1  |

| C11      | 15pf  |    | C3B         | 0. 1  |

| C12      | 0. 1  |    | <b>C3</b> 9 | 100pf |

| C13      | 0. 1  |    | C40         | 0, 1  |

| C14      | 15pf  |    | C41         | 0. 1  |

| C15      | 0. 1  |    | C42         | 0, 1  |

| C16      | 0. 1  | 11 | C43         | 100pf |

| C17      | 15pf  |    | C44         | 0, 01 |

| C18      | 0. 1  |    | C45         | 0.01  |

| C19      | 0, 1  |    | C46         | 0.01  |

| C20 .    | 15pf  |    | C47 .       | 0, 01 |

| C21      | 0. 1  | •  | C48         | 0.1   |

| C55      | 0. 1  |    | C49         | 0.1   |

| C53      | 15pf  |    | C50         | 0, 1  |

| C24      | 0. 1  |    | C51         | 0, 1  |

| C25      | 0. 1  | •• | C52         | 0.1   |

| C26      | 15pf  | •  | C53         | 0.1   |

| C27      | 0, 1  | •  |             |       |

### DIODES

The selected diodes must supply 0.7 forward biased voltage.

| location | model  |  |

|----------|--------|--|

| Di       | GE 914 |  |

| D2       | GE 914 |  |

| D3       | GE 914 |  |

| 0.4      | CF 914 |  |

### INTEGRATED CIRCUITS

| location | model       |

|----------|-------------|

| ICi      | AD509JH     |

| IC2      | AD509JH     |

| IC3      | AD509JH     |

| IC4      | AD509JH     |

| IC5      | AD509JH     |

| IC6 '    | AD509JH     |

| IC7      | AD509JH     |

| ICB      | AD509JH     |

| IC9      | AD509JH     |

| IC10     | RC4200NB    |

| IC11     | DG509CJ     |

| IC12     | R5402 E 146 |

| IC13     | MC1408L8    |

| IC14     | MC1408L8    |

| IC15     | N82S09N     |

| 1616                  | 74L5240HD |  |

|-----------------------|-----------|--|

| IC17                  | 5N7432J   |  |

| IC18                  | SN7474N   |  |

| IC19                  | DS0026CN  |  |

| 1020                  | D50026CN  |  |

| 43 44 444 444 444 674 |           |  |

| JUMPERS               |           |  |

73 71 takes the multiplexer output to the BNC connector takes the output of the squaring circuit to the BNC connector joins both paths of ground

ORIGINAL PAGE IS OF POOR QUALITY

.

APPENDIX B

**PUBLICATIONS**

# BOOKS

Snyder, Benz, and Reece, "Pattern Classification Using Charge Transfer Devices", in Remote Sensing of Earth from Space: Role of "Smart Sensors", AIAA Progress in Aeronautics and Astronautics Series, vol. 67.

# CONFERENCES

Snyder, Reece, and Benz, "Multispectral Classification Using Charge Transfer Devices", AIAA Smart Sensors Conference, Langley Research Center, 1978.

Snyder, Husson, and Benz, "Satellite Pattern Classification Using Charge Transfer Devices", IEEE Conference on Pattern Recognition and Image Processing, Chicago, 1979.

Snyder, Reece, and Benz, "Pattern Classification Using CTDs", Government Microcircuits Applications Conference, Monterrey, 1978.

Snyder, Rajala, and Hirzinger, "Image Modeling" The Continuity Assumption and Tracking", Submitted to the 5th International Conference on Pattern Recognition, Miami Beach, December 1980.

Snyder and Tang, "Optimal Computation of Image Gradients Using Eigenvector Techniques and 3x3 Neighborhoods, Submitted to the 5th International Conference on Pattern Recognition, Miar,i Beach, December 1980.

# CONFERENCES (con t.)

Snyder and Cowart, "An Interative Approach to Region Growing,"

Submitted to the 5th International Conference on Pattern Recognition, Miami Beach, December 1980.

Snyder and Hirzinger, "Techniques for Processing Time-Varying Images", to be presented at the International Computer Technology Conference, San Francisco, August 1980.

# PATTERN CLASSIFICATION USING CHARGE TRANSFER DEVICES

W. E. Snyder<sup>\*</sup> and J. H. Reece<sup>/</sup>

North Carolina State University, Raleigh, N. C.

and

H. F. Benz<sup>F</sup>

NASA Langley Research Center, Hampton Va.

### Abstract

The potential uses of charge transfer devices (CTD's) in pattern classification operations are explored. The needs for a hardware-based pattern classifier are established, and a matrix multiplication subsystem based upon a sum of products CTD is presented. An evaluation process for sum-of-products devices (particularly analog-analog correlators) is developed, and the feasibility of employing, a particular device in a pattern classifier is determined. Finally, the possible impact of future trends in technology is considered.

# I. Introduction

Recent technological innovations are making general purpose computers cheaper and more accessible. Witness, for example, the dramatic increase in computational complexity available per dollar in just the last five years. These same technological innovations are making instrumentation packages simpler to use, more computationally dense, and much less expensive. It thus is becoming more and more reasonable to talk about special purpose, dedicated pattern recognition equipment.

We can discuss only a small subset of the "pattern recognition problem" in this context, since that larger problem is far from well defined, much less solved, and "special purpose equipment" implies that we are trading away flexibility in exchange for speed and/or simplicity of use. We have chosen to deal with the problem of multispectral satellite image classification. Under certain assumptions, this problem can be considered well defined, and a pressing need exists for special equipment which can deal rapidly with the vast amounts of data coming from satellites every minute.

NASA has been and continues to be concerned about the fact that present (general purpose computer-based) techniques are too slow and too expensive to begin to deal with more than a tiny fraction of the LANDSAT data which are currently available. This paper is one of the results of an ongoing

study conducted by NASA to investigate technologies which might contribute to the solution of this data processing bottleneck. This paper discusses the use of metal-oxide-semiconductor (MOS) technology in the construction of special purpose equipment for pattern classification.

# \* II. Device Background

Charge transfer devices may be divided into two classes: the "bucket brigade device" (BBD) and the "charge coupled device" (CCD) with various subclasses within the major groupings. The two types of CTD's differ in the manner in which charge is stored and transferred from cell to cell and have slightly differing performance characteristics. Most CCD's have lower noise figures and higher transfer efficiencies (the percentage of charge in the original cell which is transferred to the new cell) than BBD's.

When used as analog signal processors, charge transfer devices may be employed to obtain complex functions of the input

waveform. One such function is  $\sum_{i} a_{i}b_{i}$ , where the b's are

samples of the input waveform and the a's are weighting coefficients. This function is found in recursive filtering, correlation, convolution, and a number of other operations.

As shown in Fig. 1 and photographed in Fig. 2, the corresponding cells of two CTD delay lines can be connected to multipliers and the multiplier outputs then summed. In this

case the result is again  $\sum_i a_i b_i$ , but the weighting coefficients

are determined by the data stored in the second CTD and may be changed simply by clocking in new data.

Such variable too weight devices may be used as sampled correlators of continuous analog signals. More important to this project, however, is the fact that, since they operate on discrete data samples, variable tap weight devices may be used to generate the vector dot product,

$$\bar{X} \cdot \bar{Y} = \sum_{i=1}^{n} x_i y_i$$

where n is the dimension of the vector and may be as large as the number of cells in the CTD. This product is obtained simply by loading one vector into one side of the CTD and the second vector into the other. The answer thus obtained is the result of one row by column operation of a matrix multiplication.

Unlike conventional filtering application, in which a useful new result is available each clock cycle, dot product operations with two arbitrary vectors require that the entire CTD be loaded before a useful answer is produced. Thus, for a typical 16 component vector, 16 clock cycles are required to load the device. However, 5-Mhz clock rates are quite reasonable, making it possible to perform 16 multiply and add operations in 3.2 usec.

# III. Pattern Classification Hardware

In the case of multispectral image classification, the input X is a vector resulting from measurements of light intensity in several different spectral ranges. Each vector X corresponds to a single point (pixel) in a scene. A typical LANDSAT scene consists of an array of over one million ordered pixels.

It has been shown that, for a given class, all pixels belonging to that class may be reasonably described by a multivariate normal distribution. With this assumption, the probability that a vector X belongs to a class i is

$$P(i|X) = \frac{1}{(2\pi^{N/2})(|\sum_{i}|^{1/2})} \exp[-\frac{1}{2}(X-\mu_{i})^{T} \sum_{i}^{-1}(X-\mu_{i})]$$

where  $\sum_{i}$  and  $\mu_{i}$  are the covariance matrix and mean vectors, respectively, which describe the statistics of class i.

Taking the logarithm of the probability gives a discriminant function

$$g_{i}(X) \triangleq en[P(i|X)] = -1/2(X-\mu_{i})^{T} \sum_{i}^{-1}(X-\mu_{i}) + en[\sum_{i}^{-1/2} + en(2\pi^{-N/2})]$$

Since the logarithm function is monotonic, the class having the largest discriminant function for a given measurement X will also be the class having the largest

probability P(i|X) that X belongs to that class.  $\ln(2\pi^{-N/2})$  is a constant for all classes and therefore does not contribute to discriminating one class from another. Furthermore, the

term  $\ln |\Sigma|^{-1/2}$  needs to be computed only once for each class.  $(X-\mu_1)^T \sum_{i=1}^{-1} (X-\mu_1)$ , however, must be computed for each of the

millions of measurements made in an image. Consequently, this matrix computation with a general purpose computer is very time consuming.

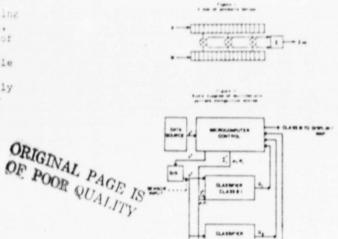

Figure 3 shows a block diagram for a hardware configuration of a system for classifying multispectral data. Data may come directly from a sensor array in analog form, or for purposes of testing, from a digital data source. The microcomputer is the control element for the system. In a training mode, it derives the statistics which describe the various classes. In classification mode, the microcomputer loads those statistics into an array of parallel CTD classifiers, controls steering of data input to those classifiers, and examines their outputs.

The individual classifiers are shown in Figs. 4 and 5. In Fig. 4, each of the row-column dot product operations is performed in a charge transfer device. The outputs are multiplexed together and fed to one more CTD for the post-multiplication dot product.

In contrast, Fig. 5 depicts a hardware simplification which also results in increased speed, since it eliminates the multiplexer and a delay. This simplification is made feasible by the diagonal symmetry of the covariance matrix, which may be transformed into upper triangular form.

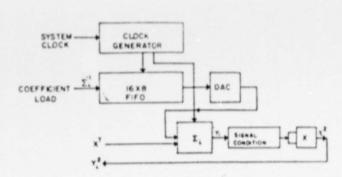

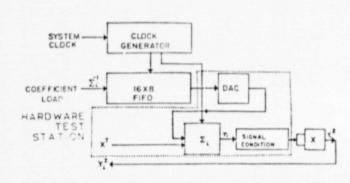

The matrix operation shown in Fig. 5 can be decomposed into cellular substructures as shown in Figs. 6 and 7. At the conclusion of the training mode, the processor loads one row of the covariance matrix into the first-in-first-out memory associated with each cell. The hardware then takes over and under control of the clock generator, performs the entire discriminant function computation.

On a pixel-by-pixel basis, the output of the individual hardware classifiers is digitized and read by the processor, which then classifies the pixel as belonging to the class whose discriminant function was maximized. Using 128 CTD's, a pixel described by 16 multispectral measurements may be classified into one of nine categories in 3.2 usec.

# IV. In Situ Cell Qualification

The critical element in the pattern classifier system is the charge transfer device that performs the row-column multiply. Extensive testing has been performed on prototype units which have recently become available from semiconductor manufacturers.

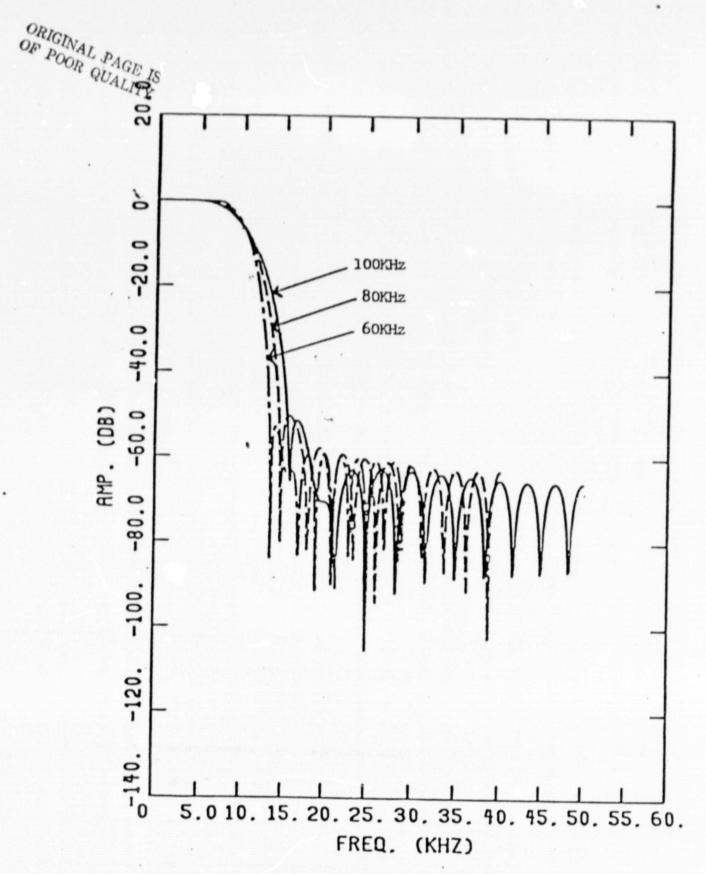

The hardware test station shown in Fig. 8 has been implemented. It tests individual devices in a cellular

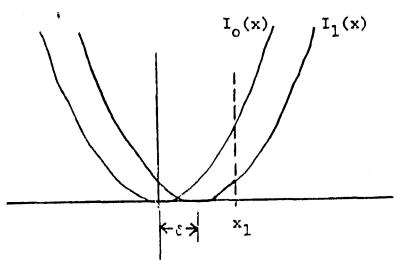

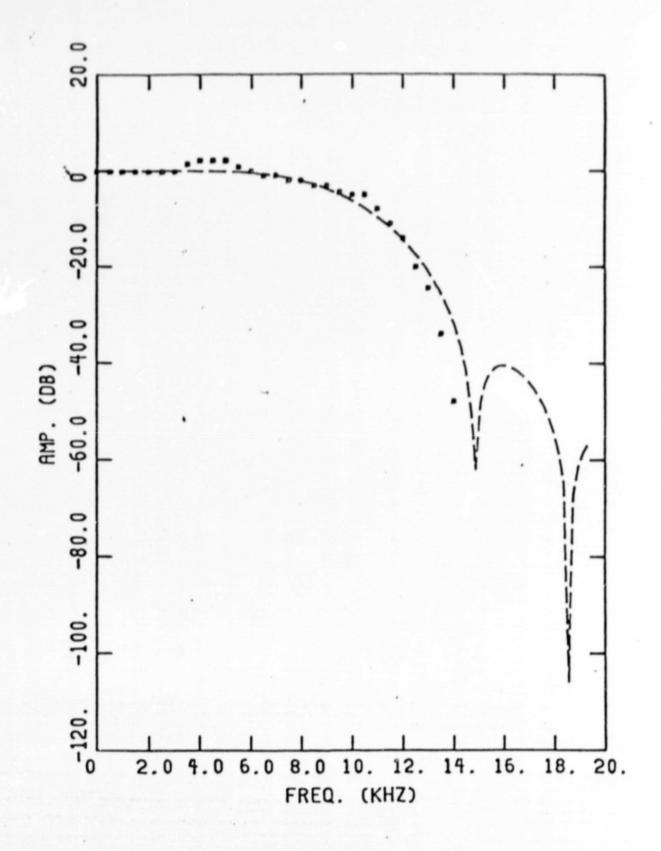

structure similar to the structures used in the classifier. Typical results of one of the tests on one of the devices are shown in Fig. 9. The figure shows the aggregate linearity and offset for a Reticon 5402, a 16-element analog-analog sum of products device. Plotted is the computed output in expanded scale and inverted decimal form) versus the B input values, where all of the B cells are filled with the fractional numbers indicated. Similarly, the A cells are filled with the numbers indicated, and these point values are connected to form families. It is apparent from this figure that there is a small offset, the point where the curves all intersect. There is also a small nonlinearity, where the points fall off the curve. The rotated appearance of the curve is caused by the small offset in the B side being multiplied and summed by the data in the A side. These test results demonstrate adequate linearity and offset at the 8 equivalent bit input and 8 equivalent bit output to continue further development. Figure 10 is a photograph of the test system showing the chip under test, the microcomputer and the associated data conversion circuitry.

# V. Conclusion

This paper has shown one method of implementing dedicated hardware for pattern classification. Recent technological developments have made such classifiers feasible using sampled analog processing. Test results have indicated that prototype development should continue. It is expected that continued technological improvement will lead to more compact, lower power, and even faster system configurations.

# Acknowledgements

This work was supported by NASA Research Grant NSG 1353.

1

References

<sup>1</sup>Kriegler, F. T., et al., "Midas, Prototype Multivariate Interactive Digital Analysis System - Phase I," Vol. 1, HASA CR-132463, ERIM 195800-25-F, Aug. 1974, p. 72.

Presented as Paper 78-1723 at the AIAA/NASA Conference on "Smart" Sensors, Hampton, VA., Nov. 14-16, 1978. This paper is declared a work of the U.S. Government and therefore is in the public domain.

\*Assistant Professor of Electrical Engineering, North Carolina State University.

+Graduate Student, North Carolina State University. #Aerospace Technologist, NASA Langley Research Center. SATELLITE PATTERN CLASSIFICATION USING CHARGE TRANSFER DEVICES

W.E. Snyder

C. Husson and H.F. Benz

North Carolina State University Raleigh, North Carolina

#### Abstract

The potential uses of Charge Transfer Devices (CTDs) in pattern classification operations are explored. The needs for a hardware-based pattern classifier are established, and a matrix multiplication subsystem based upon a sum-of-products CTD is presented. Applications of the subsystem to the classification of multi-modal Gaussian distributions in general and to LANDSAT data processing in particular are discussed. Finally, the potential impact of this technology on satellite data processing methodologies is discussed.

Key words: Gaussian Classifier, Charge coupled device

#### 1. Introduction

Recent technological innovations are making general purpose computers cheaper and more accessible. Witness, for example, the dramatic technological increase that has been made in just the last five years. These same technological innovations are making instrumentation packages simpler to use, more computationally dense, and much less expensive. It is thus becoming more and more reasonable to talk about special purpose, dedicated pattern recognition equipment.

We can discuss only a small subset of the "pattern recognition problem" in this context since that larger problem is far from well defined, much less solved, and "special purpose equipment" implies that we are trading away flexibility in exchange for speed and/or simplicity of use. We have chosen to deal with the problem of multispectral satellite image classification. Under limiting assumptions, this problem can be considered well defined and a pressing need exists for special equipment which can deal rapidly with the vast amounts of data coming from satellites every minute.

NASA has been and continues to be concerned about the fact that present (general purpose computer-based) techniques are too slow and too expensive to reduce to classified images more than a tiny fraction of the LANDSAT data which is currently available. This paper is one of the results of an on-going study conducted by NASA to

NASA Langley Research Center Hampton, Virginia

investigate technologies which might contribute to the solution of this data processing bottleneck.

Of particular interest to NASA are technologies which may lead to flyable "on-board" processors, units on the satellite which can classify a multi-spectral image in real-time and transmit to the ground only the classified image. A unit must meet several requirements before it can be placed in such an application. First, it must be capable of dealing with the analog data directly as it comes from the sensors. Second, since the unit is to be placed on a satellite, it must consume little power, be light in weight, and be highly reliable. Finally, the unit must be programmable from the ground and capable of deriving its own classification parameters.

This paper discusses the use of Metal-Oxide-Semiconductor (MOS) technology in the construction of special purpose equipment for pattern classification. The computational function of individual sum-of-products chips is first described, then, a scheme for the organization of the chips into a pattern classifier is shown.

The potential of on-board classification has both possible gains and hazards associated with it. With the obvious benefits of timely data availability comes the potential of the unavailability of the raw data for further processing. This difficulty is discussed in Section 4.

#### 2. Device Background

Charge Transfer Devices may be defined for. the purposes of this paper as devices which move charge linearly in synchronism with a clock. If the charge is quantized in a binary manner, CTDs may be used as digital delay lines or as shift register memories. It is, however, the ability of CTDs to move analog data that has resulted in their widest application. They have been used to acquire analog video data and to process analog data from other sources. Special classifier hardware fits into this last category.

Charge transfer devices may be divided into two classes: the "bucket brigade device" (BBD) and the 'bharge coupled device" (CCD) with various subclasses within the major groupings. The two types of CTDs differ in the manner in which charge is stored and transferred from cell to cell and have slightly differing performance characterismics.

Most CCDs have lower noise figures and higher transfer efficiencies (the percentage of charge in the original cell which is transferred to the new cell) than BBDs.

When used as analog signal processors, charge transfer devices may be employed to obtain complex functions of the input waveform. One such function is  $\text{Ea}_i b_i$  where the 'b's are samples of the input waveform and the 'a's are weighting coefficients. This function is found in recursive filtering, correlation, convolution, and a number of other operations.

Buss shows a simple means for implementing "fixed tap weight" devices where the tap weights are the weighting coefficients of the  $\rm Ea_ib_i$  function and are fixed at the time of manufacture. The tap weights are realized by splitting the transfer electrodes of one clock phase of the CTD in the ratio  $(1+a_i)$ :  $(1-a_i)$  where  $a_i$  is the ith desired coefficient.

In an alternate and potentially somewhat more useful approach, as shown in Figure 1 and photographed in Figure 2, the corresponding cells of two CTD delay lines can be connected to multipliers and the multiplier outputs then summed. In this case the result is again  $\Sigma_{a_1b_1}$ , but the weighting coefficients are determined by the data stored in the second CTD and may be changed simply by clocking in new data.

Such variable tap weight devices may be used as sampled correlators of continuous analog signals. More important to this application, however, is the fact that since they operate on discrete data samples, variable tap weight devices may be used to generate the vector dot product,

$X \cdot Y = \sum_{i=1}^{n} X_i Y_i$  where n is the dimension of the vector and may be as large as the number of cells in the CTD. This product is obtained simply by loading one vector into one side of the CTD and

the second vector into the other. The answer thus obtained is the result of one row by column opera-

tion of a matrix multiplication.

Unlike conventional filtering applications, in which a useful new result is available each clock cycle, dot product operations with two arbitrary vectors require that the entire CTD be loaded before a useful answer is produced. Thus for a typical 16 component vector, 16 clock cycles are required to load the device. However, 5 Mhz clock rates are quite reasonable, making it possible to perform 16 multiply and add operations in 3.2 µs.

#### 3. Pattern Classification Hardware

It has been shown that for the purpose of LANDSAT data classification, all pixels belonging to a given class may be described (typically), by a multimodel multivariate distribution. The multimodel distribution may be adequately decomposed into an aggregate of Normal distributions. Classification then consists of determining which of several Normal distributions a particular pixel is most likely to belong to and assign the pixel to the class having that distribution. With this assumption, the probability that a vector X belongs to a class i is

$$P(w, |X) =$$

$$\frac{1}{(2\pi)^{N/2}(|c_{i}|^{1/2})} \exp(-1/2(x-\mu_{i})^{T}c_{i}^{-1}(x-\mu_{i}))$$

Where  $C_i$  and  $u_i$  are the covariance matrix and mean vectors respectively which describe the statistics of class i.

The usual definition of the Normal distribution includes a term representing the a-priori probability  $P(w_i)$  that a sample X belongs to a particular class  $w_i$ . Experience has shown that very satisfactory results can be had by treating all a-priori probabilities as equal. If this is the case, then for the purposes of classification, the a-priori probabilities may be neglected.

Taking the logarithm of the probability gives a discriminant function

$$g_i(X) = InP(w_i|X) =$$

$$-1/2(x-\mu_i)^Tc_i^{-1}(x-\mu_i) + 2n|c_i|^{-1/2} + 2n(2\pi^{-N/2})$$

Since the logarithm function is monotonic, the class having the largest discriminant function for a given measurement X will also be the class having the largest probability  $P(w_i \mid X)$  that X belongs to that class.

$\ln(2\pi^{-N/2})$  is a constant for all classes and therefore does not contribute to discriminating one class from another. Furthermore the term  $\ln|C|^{-1/2}$  needs to be computed only once for each class.

$(X-\mu_1)T$   $C_1^{-1}(X-\mu_1)$  however must be computed for each of the millions of measurements made in an image. Consequently, this matrix computation with a general purpose computer is very time consuming.

Figure 3 shows a block diagram for a hardware configuration of a system for classifying multi-spectral data.

Data may come directly from a sensor array in analog form or, for purposes of testing, from a

digital data source. The microcomputer is the control element for the system. In a training mode, it derives the statistics which describe the various classes. In classification mode, the microcomputer loads those statistics into an array of parallel CTD classifiers, controls steering of the data input to those classifiers, and examines their outputs.

The individual classifiers are shown in figures 4 and 5. In figure 4, each of the row-column dot product operations is performed in a charge transfer device. The outputs are multiplexed together and fed to one more CTD for the postmultiplication dot product.

In contrast, figure 5 depicts a hardware simplification which also results in increased speed since it eliminates the multiplexer and a delay. This simplification is made possible by the following argument:

By the constructed diagonal symmetry of the C matrix, the product  $z = [x^T] [c^{-1}][x]$  may be rewritten as

$z = [x^T][A]^T[A][X]$  where A is upper triangular

$z = [x^T A^T][AX]$

$= [Y^T][Y]$

- v2

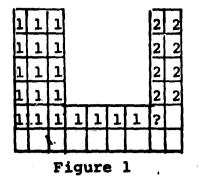

The matrix operation shown in figure 5 can be decomposed into cellular substructures as shown in figure 6. If 8 features are assumed, then 8 of the sum-of-products structures in figure 6 are needed -- one for each row column operation.

At the conclusion of the training mode, the processor loads of the covariance matrix associated with each class into the covariance memory associated with each cell. If 8 possible classes are assumed, this memory is 64 x 8 bits as shown. During this time, the X-µ vector for each class is loaded into the X-µ RAM also.

At this point, the hardware controller takes over and performs the discriminant function computation. The outputs of all sum-of-products cells are summed and passed through the analog to digital converter whose output is read by the processor as shown in figure 7. This operation is repeated for each class simply by stepping to the next group of covariance matrix rows and X-µ vectors in RAM. The processor then classifies the pixel as belonging to the class where discriminant function was maximized.

Operating the classifier in this fashion with longer memories holding all of the statistical information allows the use of only a single classifier without the need to reload the covariance information for each discriminant function calculation. In this manner a significant reduction in hardware over the use of a separate classifier for each class is realized with only a slight reduction in operating speed.

#### n. The Potential of On-Board Classification

We have shown in this paper an architecture which makes feasible the possibility of on-board classification. An on board classifier offers significant potential gains in performance of the satellite system; data would be available to the user in minutes rather than months.

There are significant logistical and technical problems which must be overcome before these benefits could become reality. In this section, we demonstrate only a few and their potential solutions.

#### A Scenerio

We will make this demonstration through a scenerio of how a typical classification might be performed:

- (1) A county agricultural agent reserves the satellite for its next pass over. In so doing, he specifies the coordinates of some areas known to be corn, soybeans, and cotton.

- (2) The coordinates of these training sets are transmitted to the satellite. As the satellite passes over, image data is acquired and stored. The on-board classifier performs a cluster analysis on the training sets and derives a Gaussian fit for each cluster.

In an alternative proposed system<sup>3</sup> the satellite clusters the entire scene, transmits the cluster statistics, and for each pixel, transmits the number of the cluster to which that pixel is assigned.

- (3) Once appropriate statistics have been derived to describe training sets, the classifier described in section 3 is initialized by loading the statistics into the RAMS, and the data is then classified as belonging to one of the classes identified as corn, soybeans, or cotton. The results of the classification are then encoded and transmitted to the ground.

- (4) The agriculture agent then can receive a false colored map of the area or a digital tape with the classification results.

It should be noted that this scenerio has passed over a significant amount of pre-processing which must be done to the sensor output prior to classification, including correcting for geometric distortion.

On board classification provides a tremendous potential benefit since it makes reasonable direct user interaction with the satellite; and provides data for the user in expeditious time. The one factor which some users may consider detremental in such a system is the fact that no longer does the ground user have the raw data to mull over at his leisure.

This factor does open up a new area of study, for in those instances when the user has both a computer and the time to study the image, he may

with to attempt to improve the classifier performance by doing post-classification processing to reduce errors. Since the raw data is missing, this might seem impossible, however, two pieces of lata are available, the training sets, and the catput of the on-board classifier. It is possible in this circumstance to improve classifier performance by using these data. We are currently attractions to problem and will be publishing our results in the near future.

# s. Conclusion

This paper has shown one method of implementing dedicated hardware for pattern classification. Recent technological developments have made such classifiers feasible using sampled analog processing.

Test results have indicated that prototype development should continue. It is expected that continued technological improvement will lead to more compact, lower power, and even faster system configurations.

# Bibliography

\*Buss, D. IEEE Journal of Solid State Circuits, SC-8, p. 138 (1973).

Environmental Research Institute of Michigan, ERIM 10880-49-F NASA CR-2730, MIDAS, Prototype Multivariate Interactive Digital Analysis System for Large Area Earth Resources Surveys Vol. 1. Systems Description, Sept. 1976.

Hilbert, Ed, "Cluster Compression Algorithm," JFL PR 77-43 Jet Propulsion Lab.

Pattern Classification Using Charge Transfer Devices\*

W.E. Snyder and J.H. Reece North Carolina State University, Raleigh, NC 27650 Harry F. Benz NASA-Langley Research Center, Hampton, VA 23665

#### Abstract

The potential uses of Charge Transfer Devices (CTDs) in pattern classification operations are explored. The needs for a hardware-based pattern classifier are established, and a matrix multiplication subsystem based upon a sum of products CTD is presented. An evaluation process for sum of products devices (particularly analog-analog correlators) is developed, and the feasibility of employing a particular device in a pattern classifier is determined. Finally, the possible impact of future trends in technology is considered.

#### 1. Introduction

Recent technological innovations are making general purpose computers cheaper and more accessible. Witness, for example, the dramatic increase in computational complexity available per dollar in just the last five years. These same technological innovations are making instrumentation packages simpler to use, more computationally dense, and much less expensive. It is thus becoming more and more reasonable to talk about special purpose, dedicated pattern recognition equipment.

We can discuss only a small subset of the "pattern recognition problem" in this context since that larger problem is far from well defined, much less solved, and "special purpose equipment" implies that we are trading away flexibility in exchange for speed and/or simplicity of use. We have chosen to deal with the problem of multispectral satellite image classification. Under certain assumptions, this problem can be considered well defined and a pressing need exists for special equipment which can deal rapidly with the vast amounts of data coming from satellites every minute.