# Aerospace Applications of Microprocessors

Preprint for a workshop held in Greenbelt, Maryland November 3-4, 1980

# NASA Conference Publication 2158

# Aerospace Applications of Microprocessors

Preprint for a workshop sponsored by NASA Goddard Space Flight Center, Greenbelt, Maryland, and the American Institute of Aeronautics and Astronautics, New York, and held in Greenbelt, Maryland, November 3-4, 1980

National Aeronautics and Space Administration

Scientific and Technical Information Office

#### FOREWORD

NASA/Goddard Space Flight Center (GSFC), in cooperation with the AIAA Technical Committee on Computer Systems, sponsored this workshop on Aerospace Applications of Microprocessors. The rapidly increasing capabilities and decreasing costs of digital computing systems in general, and microprocessors in particular, have meant orders of magnitude increases in their use in aerospace systems, particularly onboard satellites and aircraft.

The objectives of the workshop were to assess the state of microprocessor applications and to identify current and future requirements and associated technological advances which allow effective exploitation of this rapidly advancing technology. There were four sessions in the workshop:

- I. Air/Space Applications of Microprocessors;

- II. Ground Based Aerospace Microprocessor Applications;

- III. Microprocessor Software Technology; and

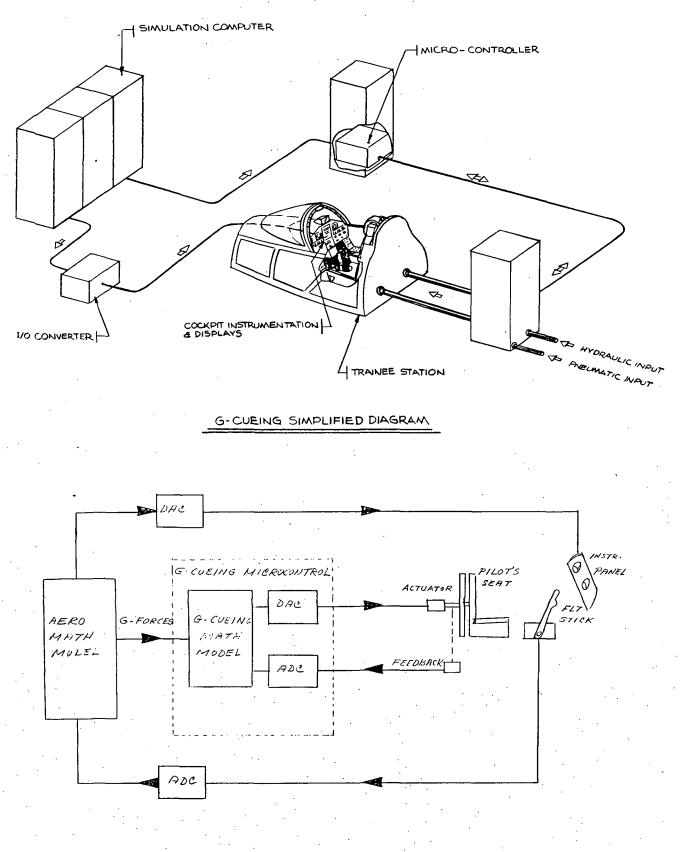

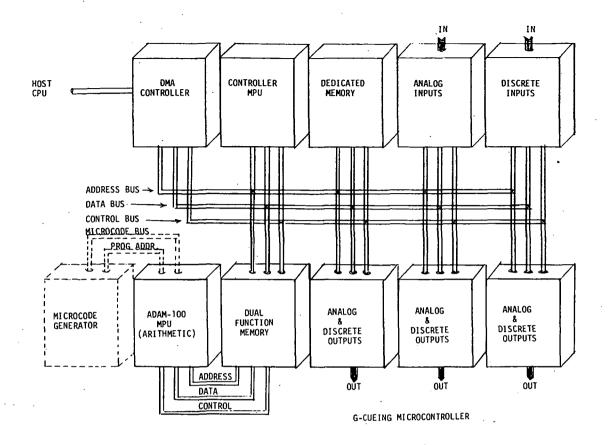

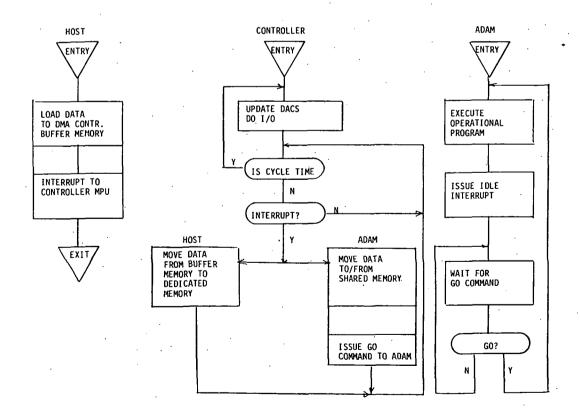

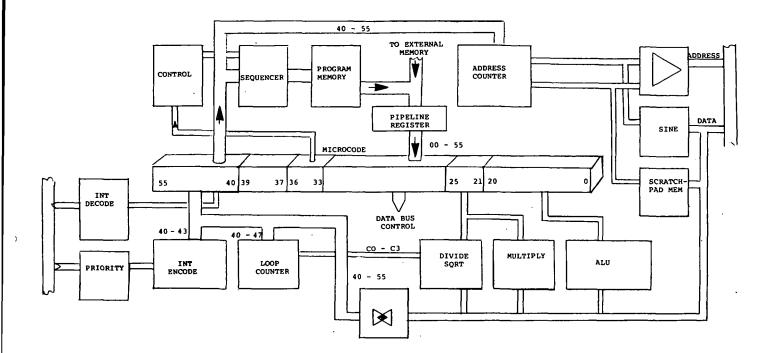

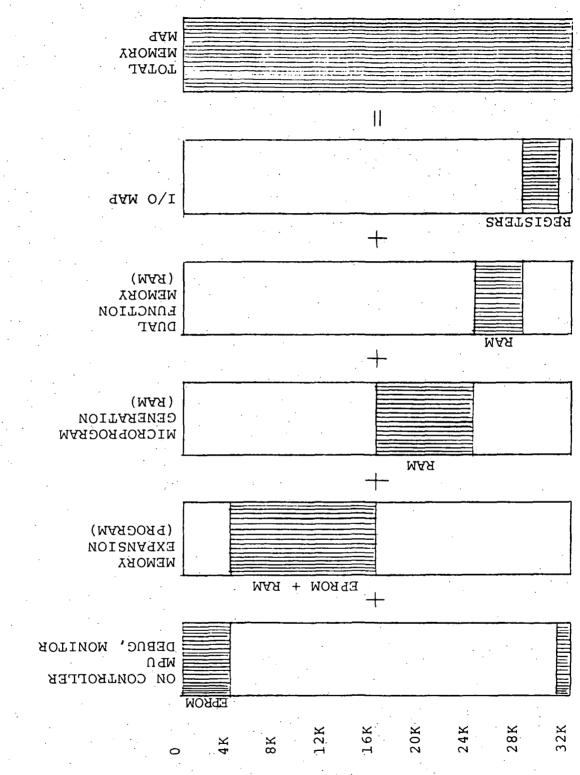

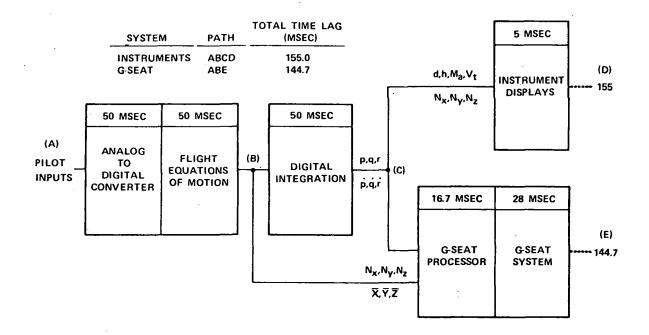

- IV. Microprocessor Hardware Technology.

This document contains only a synopsis and key figures of each presentation. The synopses and figures were submitted as camera-ready copies prior to the workshop. Only minor editorial changes have been made.

In addition to the formal presentations, the workshop was structured to provide time for audience interaction. On the evening of November 3, a panel discussion on "Are Microprocessor Trends and Aerospace Requirements Heading in the Same Direction?" was held. The panelists were:

Terry Straeter, General Dynamics Data Systems Service, (Moderator); Rocky A. Evans, Military Products Manager, Intel Corporation; Adrian Hooke, Jet Propulsion Laboratory; Charles Husson, Langley Research Center; and John Shea, Vice-President Integrated Circuit Electronics.

The workshop was organized by a subcommittee of the AIAA technical committee on computer systems. Co-chairmen were:

John Sos, Goddard Space Flight Center Terry Straeter, General Dynamics Data Systems Services.

Other committee members were:

M. Kelly, Sperry Flight Systems;

T. McTigue, McDonnell Douglas Aircraft;

R. Schwartz, McDonnell Douglas Astronautics; and

T. Smith, NAVAIR Systems Command; and

NASA/GSFC members were:

E. Connell

R. Nelson.

Use or identification of commercial products in this document does not constitute an official endorsement of such products or their manufacturers, either expressed or implied, by NASA.

John Y. Sos Program Co-chairman

iii

# Page Intentionally Left Blank

### CONTENTS

| FOF | REWORDiii                                                                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------------|

|     | SESSION I — AIR/SPACE APPLICATIONS OF MICROPROCESSORS<br>Chairman: Adrian Hooke, Jet Propulsion Laboratory                      |

| 1.  | AN IMAGING INFRARED (IIR) SEEKER USING A<br>MICROPROGRAMMED PROCESSOR                                                           |

| 2.  | EIGHT MICROPROCESSOR-BASED INSTRUMENT DATA SYSTEMS<br>IN THE GALILEO ORBITER SPACECRAFT*                                        |

| 3.  | A COMMAND & DATA SUBSYSTEM FOR DEEP SPACE EXPLORATION<br>BASED ON THE RCA 1802 MICROPROCESSOR IN A DISTRIBUTED<br>CONFIGURATION |

|     | Jack S. Thomas, California Institute of Technology                                                                              |

| 4.  | SYNERGISTIC INSTRUMENT DESIGN       21         Dale E. Winter, Jet Propulsion Laboratory                                        |

| 5.  | APPLICATION OF MICROPROCESSORS TO INTERPLANETARY<br>SPACECRAFT DATA SYSTEMS                                                     |

| 6.  | THE ROLE OF THE MICROPROCESSOR IN ONBOARD IMAGE<br>PROCESSING FOR THE INFORMATION ADAPTIVE SYSTEM                               |

| 7.  | APPLICATION OF A MICROPROCESSOR TO A SPACECRAFT<br>ATTITUDE CONTROL SYSTEM                                                      |

| 8.  | A PLASMA WAVE FOURIER TRANSFORM PROCESSOR EMPLOYING 1802<br>MICROCOMPUTERS FOR SPACECRAFT INSTRUMENTATION                       |

| 9.  | PROTOTYPE DEVELOPMENT OF A MICROPROCESSOR-BASED ONBOARD<br>ORBIT DETERMINATION SYSTEM                                           |

| S   | ESSION II — GROUND BASED AEROSPACE MICROPROCESSOR APPLICATIONS<br>Chairman: Louis Fulmer, Goodyear                              |

| 10. | THE REMOTE COMPUTER CONTROL (RCC) SYSTEM                                                                                        |

| •   |                                                                                                                                 |

v

| 11. | A MICROPROCESSOR APPLICATION TO A STRAPDOWN LASER<br>GYRO NAVIGATOR                                                      |

|-----|--------------------------------------------------------------------------------------------------------------------------|

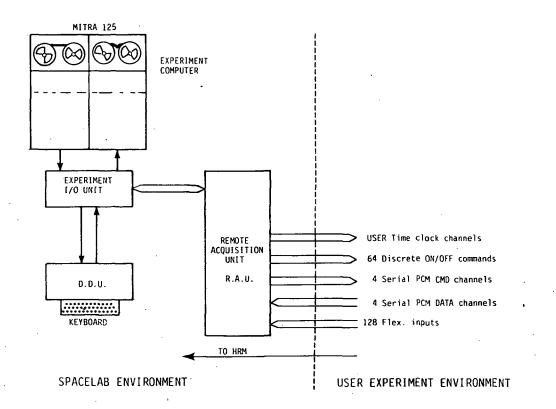

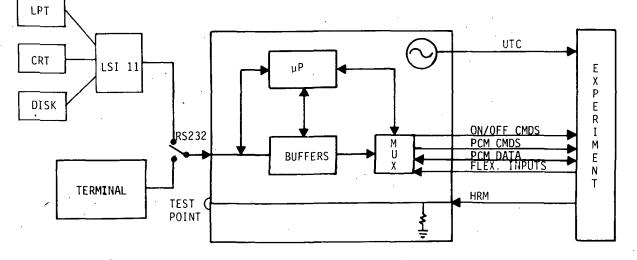

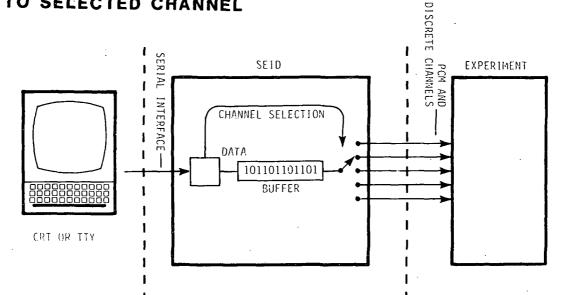

| 12. | THE SPACELAB EXPERIMENT INTERFACE DEVICE (SEID)                                                                          |

| 13. | G-CUEING MICROCONTROLLER (A Microprocessor<br>Application in Simulators)                                                 |

| 14. | MICROPROCESSOR SOFTWARE APPLICATIONS FOR FLIGHT<br>TRAINING SIMULATORS                                                   |

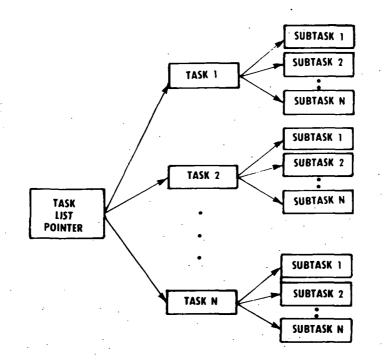

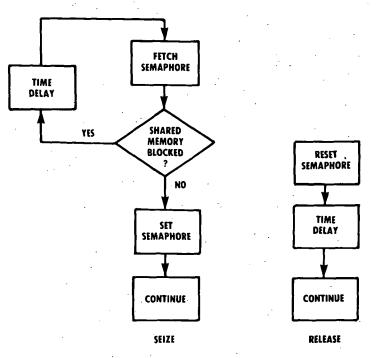

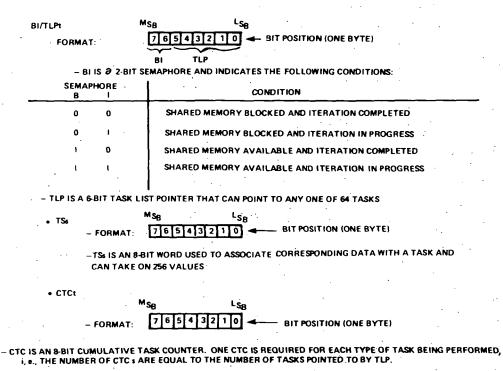

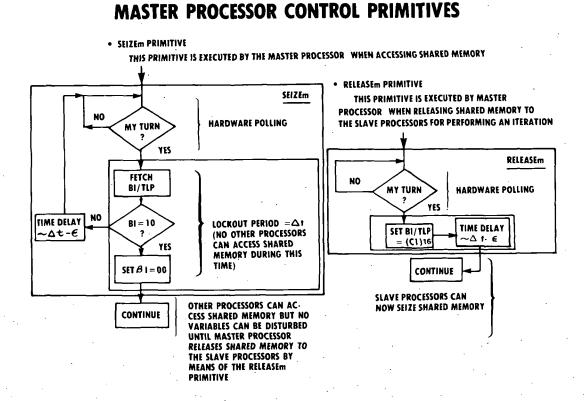

| 15. | AN EXPERIMENTAL DISTRIBUTED MICROPROCESSOR IMPLE-<br>MENTATION WITH A SHARED MEMORY COMMUNICATIONS AND<br>CONTROL MEDIUM |

| 16. | DISTRIBUTED MICROPROCESSORS IN A TACTICAL<br>UNIVERSAL MODEM                                                             |

|     | SESSION III — MICROPROCESSOR SOFTWARE TECHNOLOGY                                                                         |

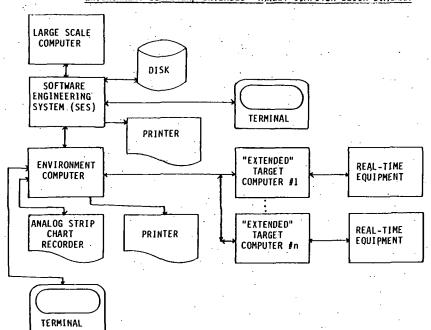

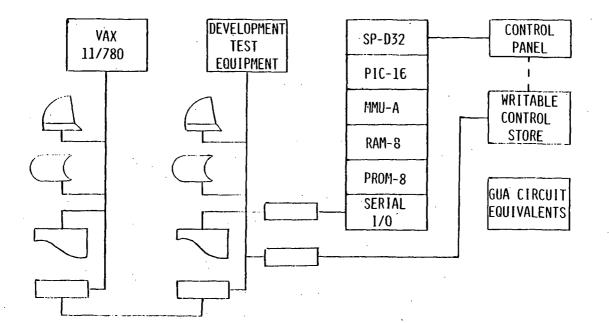

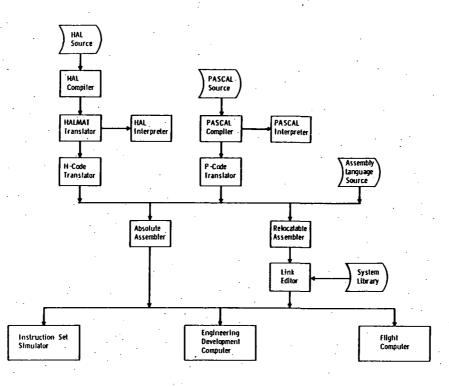

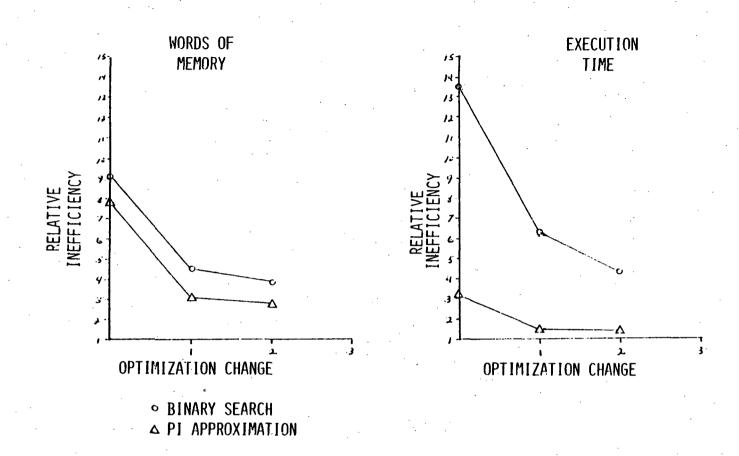

| 17. | MICROCOMPUTER SOFTWARE DEVELOPMENT FACILITIES                                                                            |

| 18. | MICROPROCESSOR USER SUPPORT AT LANGLEY RESEARCH CENTER139<br>Jerry H. Tucker, Langley Research Center                    |

| 19. | DEBUGGING EMBEDDED COMPUTER PROGRAMS                                                                                     |

| 20. | REAL-TIME OPERATING SYSTEM FOR SELECTED INTEL PROCESSORS151<br>W. R. Pool, Ford Aerospace                                |

| 21. | A FOURIER TRANSFORM WITH SPEED IMPROVEMENTS FOR<br>MICROPROCESSOR APPLICATIONS                                           |

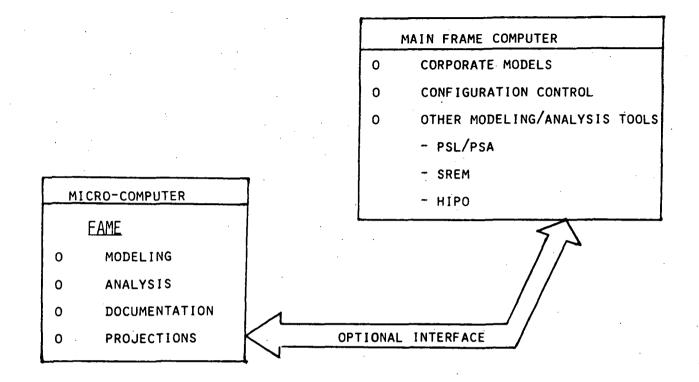

| 22. | FAME—A MICROPROCESSOR BASED FRONT-END ANALYSIS<br>AND MODELING ENVIRONMENT                                               |

| 23. | APPLICATION OF SOFTWARE TECHNOLOGY TO A FUTURE<br>SPACECRAFT COMPUTER DESIGN                                             |

|     |                                                                                                                          |

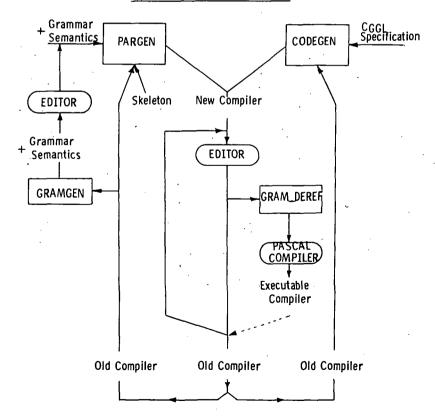

| 24. | A TRANSLATOR WRITING SYSTEM FOR MICROCOMPUTER HIGH-<br>LEVEL LANGUAGES AND ASSEMBLERS                                                           |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

|     | W. Robert Collins, Computer Sciences Corporation, John C. Knight,<br>Langley Research Center, and Robert E. Noonan, College of William and Mary |

|     |                                                                                                                                                 |

|     | SESSION IV — MICROPROCESSOR HARDWARE TECHNOLOGY<br>Chairman: Richard Balestra, NAVAIR Systems Command Headquarters                              |

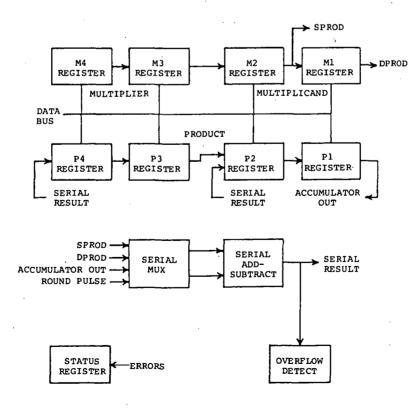

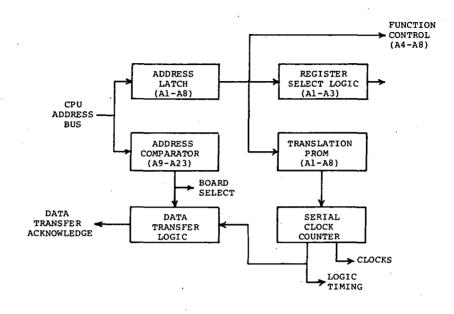

| 25. | A HIGH PERFORMANCE MULTIPLIER PROCESSOR FOR USE WITH<br>AEROSPACE MICROCOMPUTERS                                                                |

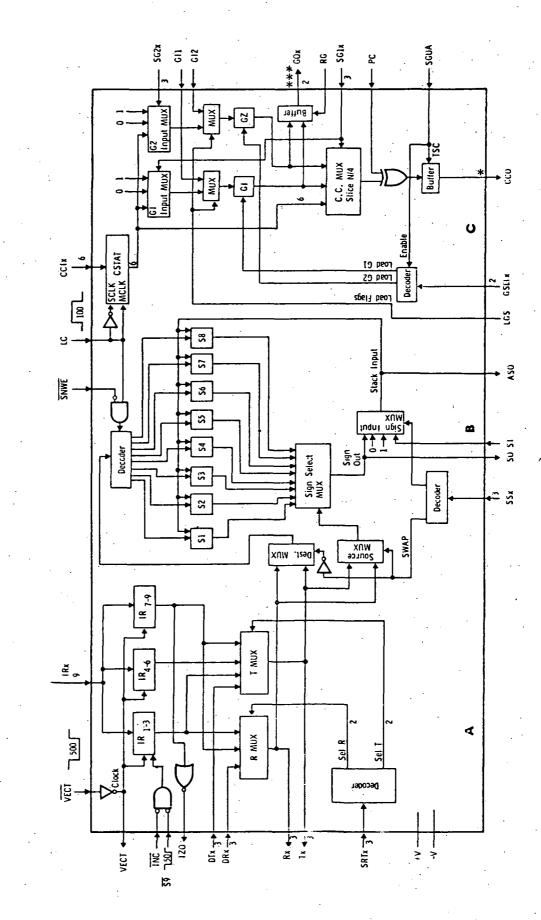

| 26. | APPLICATION OF ADVANCED ELECTRONICS TO A FUTURE<br>SPACECRAFT COMPUTER DESIGN                                                                   |

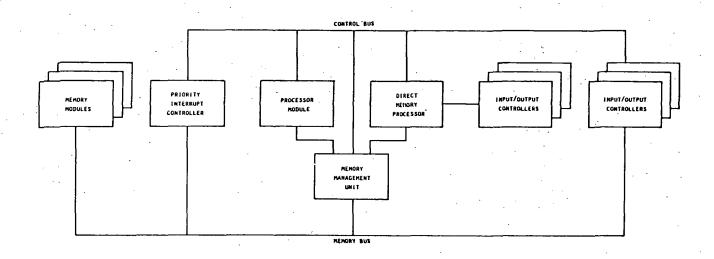

| 27. | EVOLUTION OF A STANDARD MICROPROCESSOR-BASED<br>SPACE COMPUTER                                                                                  |

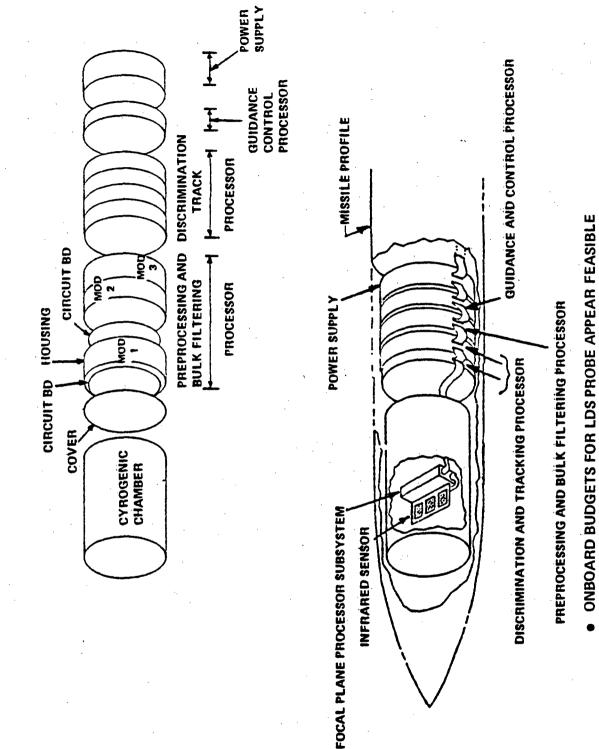

| 28. | MICROPROCESSORS FOR IMAGING SEEKERS                                                                                                             |

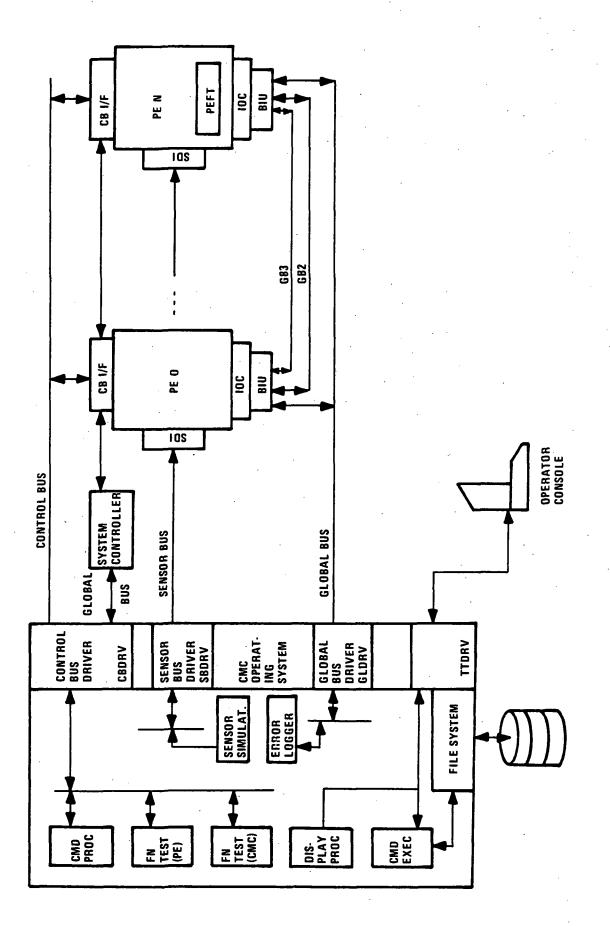

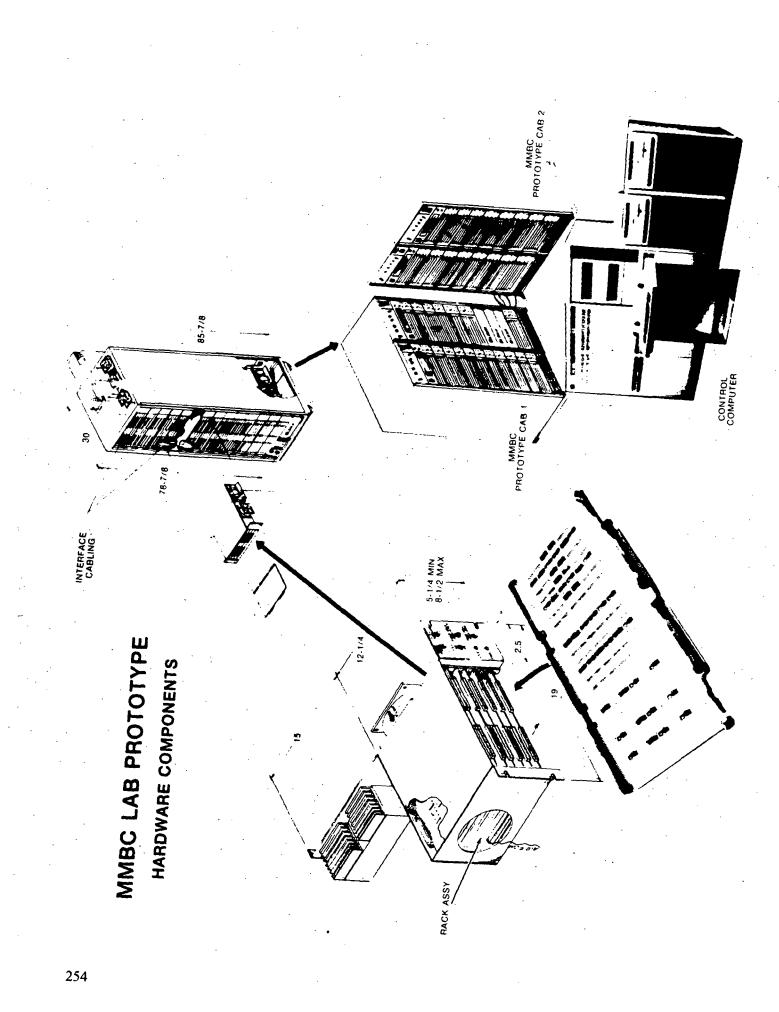

| 29. | MODULAR MISSILE BORNE COMPUTERS                                                                                                                 |

| 30. | MICROPROCESSOR-CONTROLLED TELEMETRY SYSTEM                                                                                                      |

| 31. | MICROCOMPUTER ARRAY PROCESSOR SYSTEM                                                                                                            |

vii

### SESSION I

#### AIR/SPACE APPLICATIONS OF MICROPROCESSORS

Preceding Page Blank

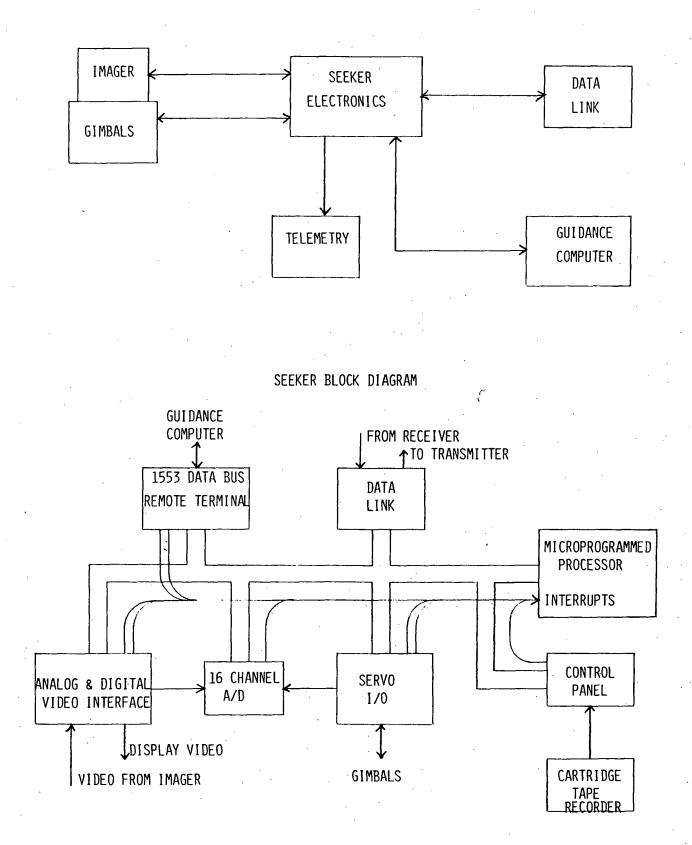

#### AN IMAGING INFRARED (IIR) SEEKER USING A MICROPROGRAMMED PROCESSOR

#### Kerry V. Richmond McDonnell Douglas Astronautics Co. St. Louis, Missouri

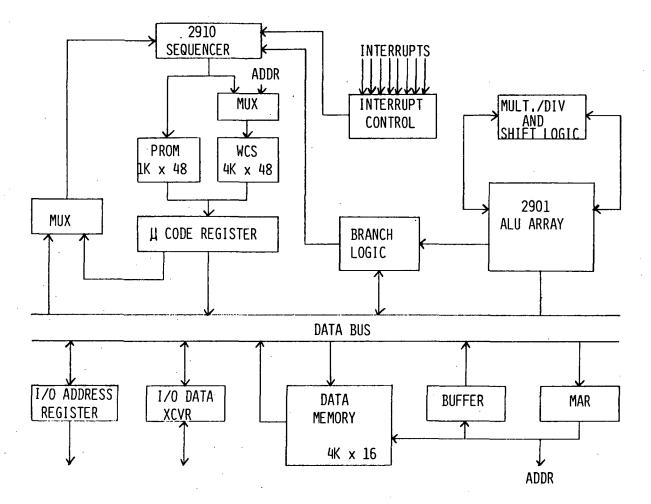

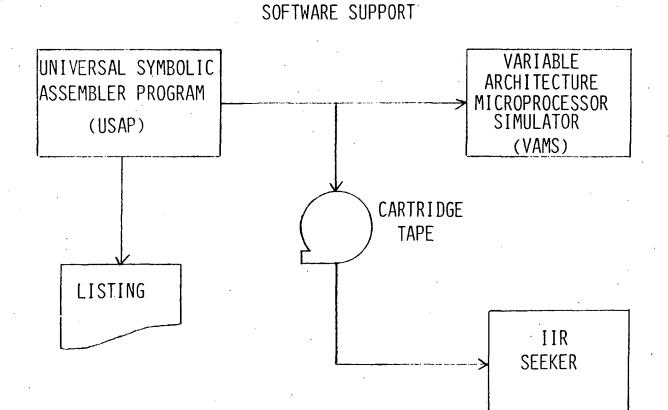

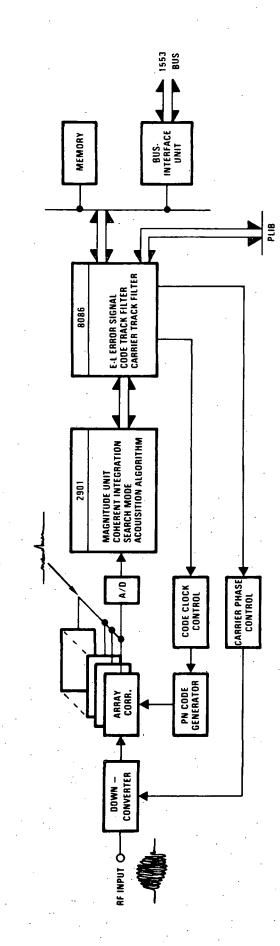

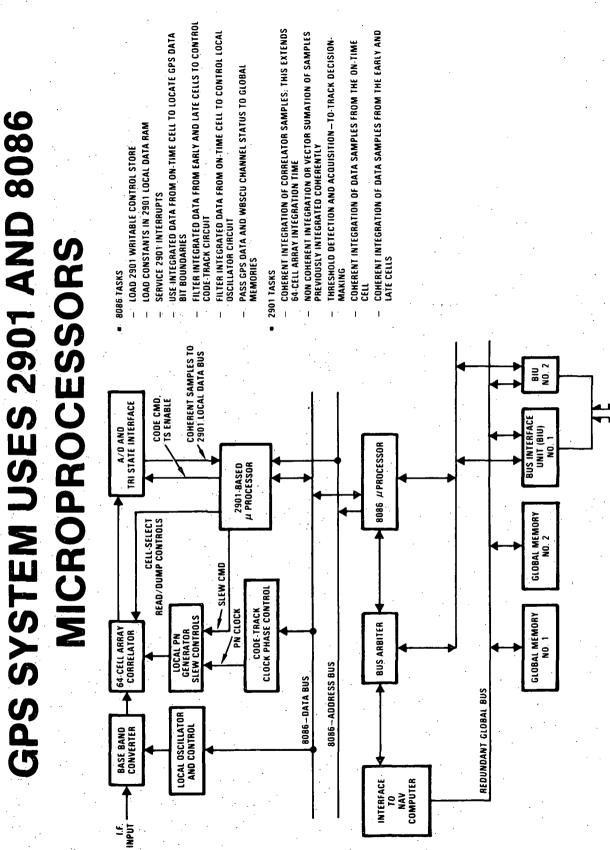

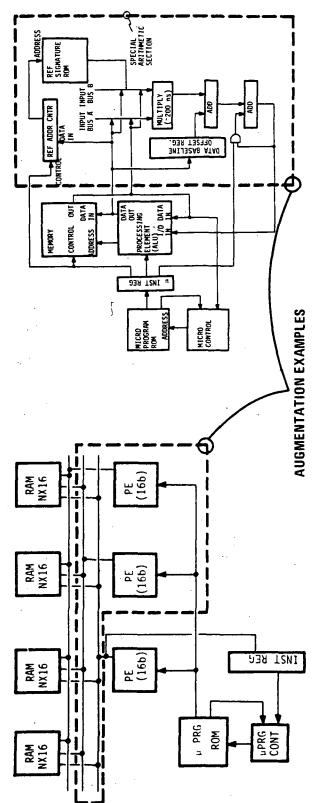

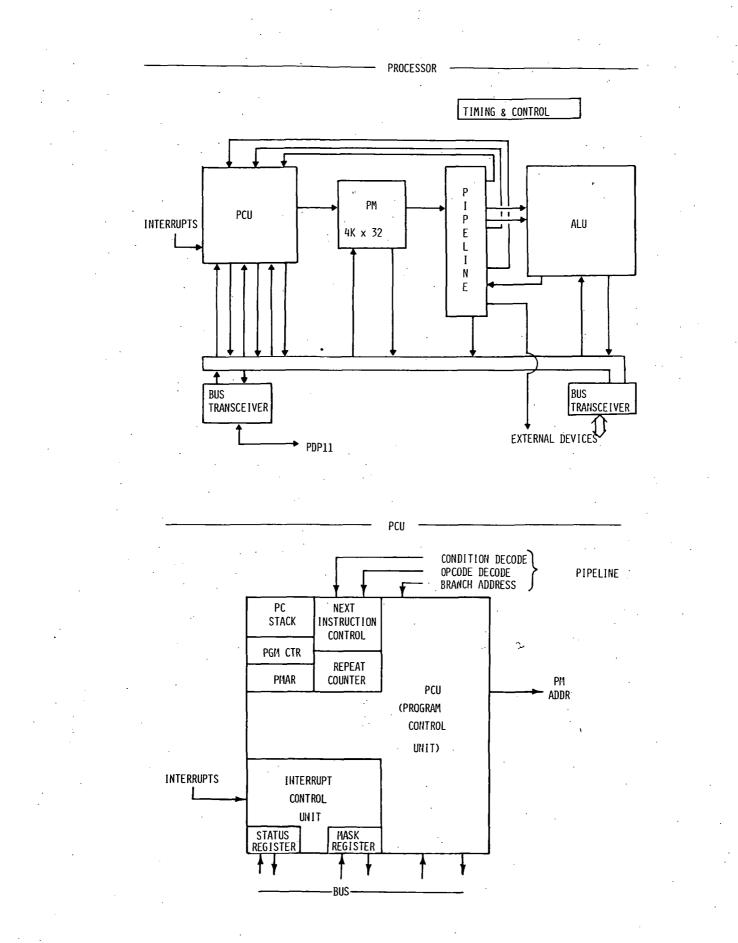

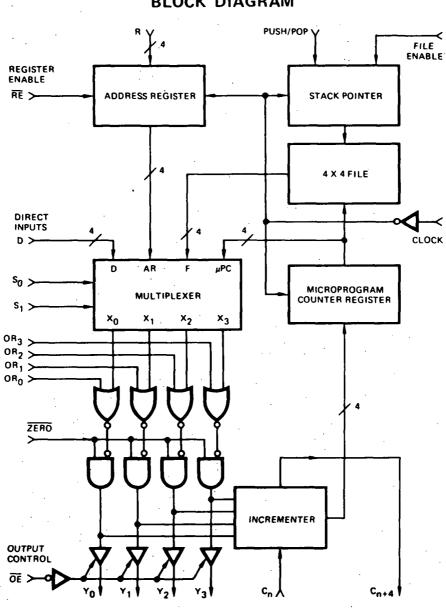

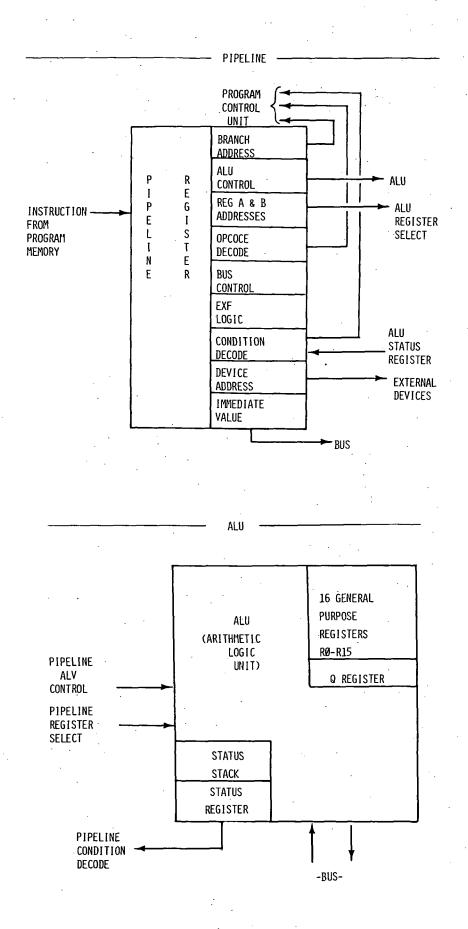

A recently developed IIR seeker uses a microprogrammed processor to perform gimbal servo control and system interface via a MIL-STD 1553 port while performing the seeker functions of automatic target detection, acquisition and tracking. Although the acquisition and centroid tracking are relatively low computation load seeker modes, the automatic detection mode requires up to 80% of the available capability of a high performance 2900 based microprogrammed processor. With the high speed processing capability available it is possible to implement a digital servo in the same processor using only 5% of the computation capacity. This digital servo includes six modes of gimbal control at the basic processor 60 Hz computation loop plus a 200 Hz rate loop, the latter being transparent to the main seeker functions. These two asynchronous timing loops plus a 50 Hz system interface loop driven from the 1553 port are implemented in the one processor. The fast response required by the rate loop for the rate sensor demodulator inputs also requires an interrupt driven analog data acquisition system. A 4K microcode program driven by eight interrupts implements these functions as well as the other operator and system interfaces.

The eighth interrupt is used to force the processor into special "front panel" code which suspends all other interrupt processing and saves the state of the processor to allow the programmer to view the contents of all registers and memory as well as enter new values and resume normal processor execution at the interrupted location or any other selected location. This programmer debug aid in the hardware coupled with a set of support software including a symbolic cross assembler and a software simulation of the 2900 based processor allow efficient program development and checkout.

This system developed around the microcoded processor required by one of the system tasks has been designed, checked out and flown successfully. Although system complexity was increased significantly by adding the additional functions this approach can be cost effective when the basic computation capacity is already available.

#### IIR SEEKER MISSILE INTERFACES

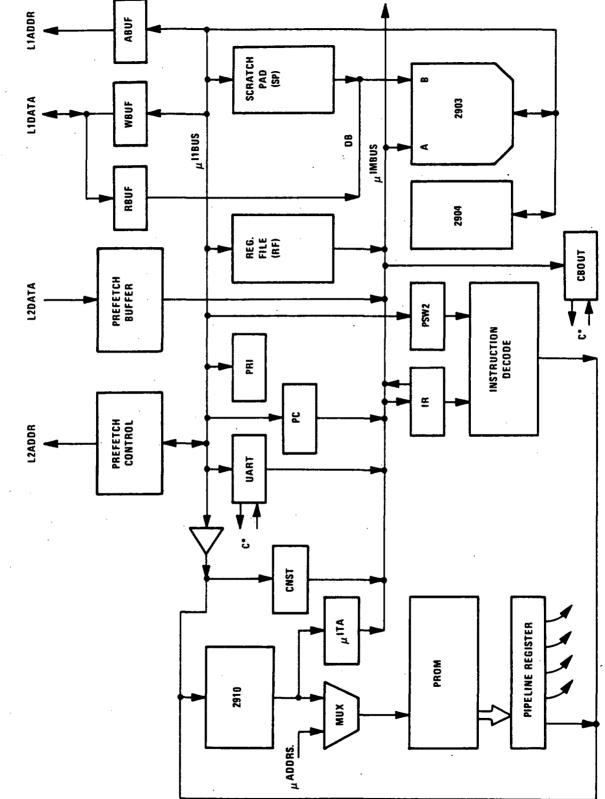

#### CPU BLOCK DIAGRAM

MICROCODE WORD

| 24 | 23  |    | 22 | 21 | 20 |     | 19        | 18 | 17 | 16 | 15  | 14        | 13 | 12    | 11 | 10          | 9 | 8 | 7           | 6  | 5 | 4   | 3 | Γ | 2  | ١ |

|----|-----|----|----|----|----|-----|-----------|----|----|----|-----|-----------|----|-------|----|-------------|---|---|-------------|----|---|-----|---|---|----|---|

|    | Str | ob | es |    |    | Ado | B<br>dre: | s  | -  |    | Add | A<br>Ires | S  | Shift |    | ALU<br>Dest |   |   | ALU<br>Fund | :. |   | ALU |   |   | Ci | n |

| 48    | 47 46        | 45 | 44 | 43   | 42   | 41 | 40 | 39   | 38   | 37   | 36 | 35 | 34 | 33   | 32 | 31 | 30 | 29 | 28 | 27 | 26 | 25 |

|-------|--------------|----|----|------|------|----|----|------|------|------|----|----|----|------|----|----|----|----|----|----|----|----|

| Spare | Bus<br>Contr | 0] |    | Sequ | lenc | er | B  | ranc | h Co | ond. | In |    |    | FIEL | D  |    |    |    |    |    |    |    |

# CPU PERFORMANCE/REQUIREMENTS

- o 2900 BIT SLICE MICROPROGRAMMED PROCESSOR

- o 48 BIT WIDE MICROCODE WORD

- o 267 NANOSECOND CYCLE TIME

- o 4K PROGRAM MEMORY

- o 2K SCRATCH PAD MEMORY

- o 8 INTERRUPTS

# SEEKER INTERRUPTS

SYSTEM INTERRUPTS

- o CONTROL PANEL

- o A/D COMPLETION

- 60 Hz MAIN LOOP

- o END OF GATE

- o END OF FIELD

- 200 Hz SERVO RATE LOOP

- o SAMPLE AZIMUTH DEMODULATOR

- o SAMPLE ELEVATION DEMODULATOR

- 50 Hz GUIDANCE COMPUTER TIMING LOOP

- o 1553 INPUT DATA READY

- o 1553 OUTPUT DATA READY

### ANALOG DATA ACQUISITION DEMODULATOR DATA REQ. TOP CIRCULAR WAIT LIST BOTTOM DATA REQUIREMENTS APPLICATION A/D SOFTWARE INTERRUPT INTERRUPT HANDLER DATA AND DATA SERVO FUNCTIONS CPU I/0 GIMBALS SCAN | RATES 200 Hz D/A AND TORQUE RATE LOOP CURRENT AMPLIFIERS MOTORS SOFTWARE DEMODULATOR, A/D 2 AXIS 1 AND INTERRUPT DRIVER RATE SENSOR GIMBAL POSITION 60 Hz A/D POSITION LOOP PICK-OFF POTS SOFTWARE TRACK TRACKER RATES IMAGER INTERFACE SOFTWARE.

# FRONT PANEL FUNCTIONS

o READ/LOAD DATA MEMORY

- o READ/LOAD REGISTERS CPU

- I/O ADDRESS

- MEMORY ADDRESS

- CONDITION CODE

- o READ/LOAD INTERRUPT STATUS

- o EXIT/RETURN TO PROGRAM

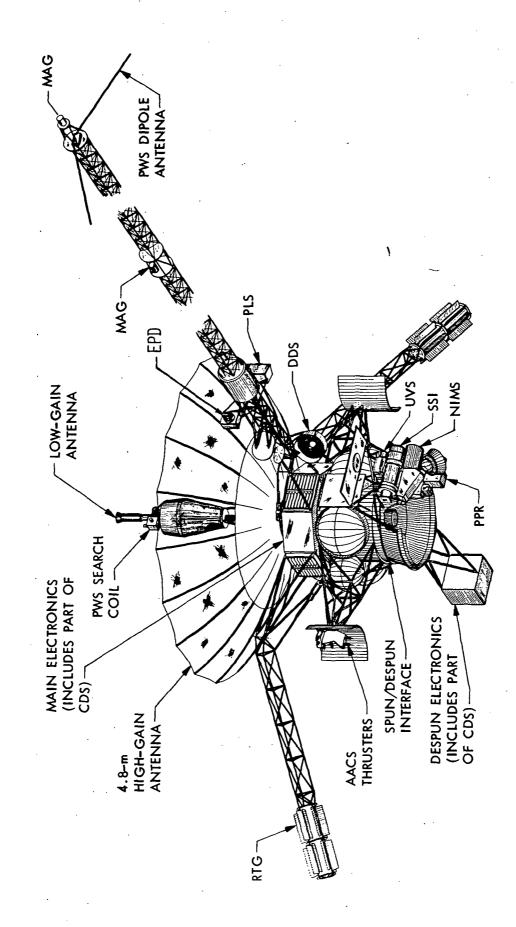

#### EIGHT MICROPROCESSOR-BASED INSTRUMENT DATA SYSTEMS IN THE GALILEO ORBITER SPACECRAFT\*

#### Robert C. Barry Jet Propulsion Laboratory Pasadena, California

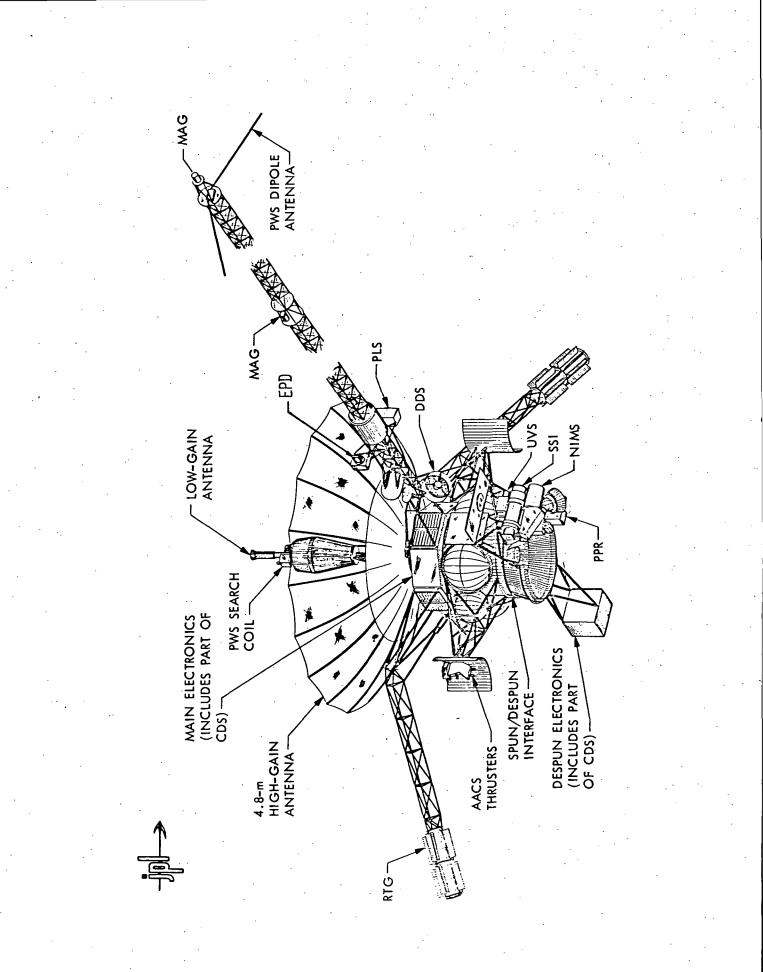

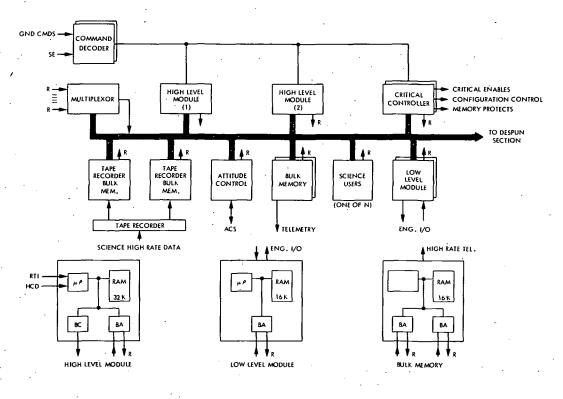

The Galileo Orbiter spacecraft carries nine scientific instruments, all but one of which are controlled by individual microprocessors. Scientific investigations include interplanetary measurements of charged atomic particles, magnetic and electric fields, and dust. In orbit, Galileo will investigate Jupiter's magnetosphere and atmosphere, and surface properties of the four largest satellites. Launch is scheduled for early in 1984.

While the complexity of the instruments and their data systems varies widely, all utilize components from the RCA 1800 microprocessor family, and all perform the same basic functions. The decisions to utilize microprocessors in the instruments were heavily influenced by the spacecraft distributed Command and Data System (CDS) design which uses this same LSI family.

A typical instrument data system consists of a microprocessor, 3K Bytes of Read Only Memory (ROM) and 3K Bytes of Random Access Memory (RAM). It interfaces with the spacecraft data bus through an isolated user interface with a direct memory access bus adapter. Microprocessor control and data lines provide interrupts, serial, and/or parallel data from instrument devices such as registers, buffers, analog to digital converters, multiplexers, and solid state sensors. These data systems support the spacecraft hardware and software communication protocol, decode and process instrument commands, generate continuous instrument operating modes, control the instrument mechanisms, acquire, process, format, and output instrument science data.

The approach has resulted in many specific improvements over past missions. Some of the most important include: increased instrument autonomy, functional commanding, and macro mode generation; enhanced telemetry output from both operational and scientific points-of-view; and additional flexibility for inflight optimization, problem work-arounds, and instrument generalization for support of multiple missions.

There was a significant but manageable underscoping of the microprocessor development tasks and costs. This was related to difficulty in establishing firm requirements at an early date, interfacing complexity, parts acquisition problems, and a general lack of extensive experience in microprocessor hardware and software design.

While the Galileo entry-level introduction into instrument microprocessor appears to be proceeding well, additional effort is needed for standard use of microprocessors in science instruments to achieve a significant part of its high potential benefit. This includes generation and clarification of spacecraft system level requirements in concert with the objectives of the end-to-end information system design, improved use of microprocessor development tools and practices, and justification for increased instrument funding compatible with the increase in capability and cost.

\*This work was performed for the Jet Propulsion Laboratory, California Institute of Technology, sponsored by the National Aeronautics and Space Administration under Contract No. NAS7-100.

#### INTRODUCTION

- HISTORICAL ASPECTS OF INSTRUMENTS ON JPL SPACECRAFT

- INCREASING COMPLEXITY

- HIGHLY INTEGRATED SPACECRAFT

- HIGHLY INTEGRATED MISSION OPERATIONS & FLIGHT TEAM

- EXTENSIVE DATA PROCESSING & CORRELATION THE NORM

- WHAT ROLE DO INSTRUMENT MICROPROCESSORS PLAY IN THIS?

- NOT A DRAMATIC CHANGE, A NATURAL EVOLUTION

- VERY FLEXIBLE, EXPANDABLE CONCEPT

- GALILEO IS THE STARTING POINT

- LIMITATIONS OF THIS PRESENTATION

- RESTRICTED TO A HIGH-LEVEL, BRIEF REVIEW

- TIME RESTRICTIONS FORCE GENERALIZATION

- ACCENTUATE COMMON ELEMENTS

- LITTLE DISCUSSION OF UNIQUE IMPLEMENTATIONS

#### MATERIAL TO BE COVERED

- REASONS FOR USE OF MICROPROCESSOR-BASED DATA SYSTEMS IN THE INSTRUMENTS

- FUNCTIONS PERFORMED BY THE PS

- SUMMARY OF THE INSTRUMENTS

- SELECTED HIGHLIGHTS FROM THE GALILEO APPLICATIONS

- PROBLEM AREAS ENCOUNTERED

- EVALUATION OF THE GALILEO APPROACH

WHY USE MICROPROCESSORS IN THE GALILEO INSTRUMENTS?

- SUPPORT THE GENERALIZED SPACECRAFT SYSTEM INTERFACE (BUS)

- PROVIDE INCREASED INSTRUMENT AUTONOMY

- REDUCE REQUIREMENT FOR SPACECRAFT SERVICES

- INCREASE INSTRUMENT DESIGN CONTROL

- UTILIZE SEMICONDUCTOR INDUSTRY ADVANCES

- AVAILABLE, PROVEN LSI PRODUCTS (RCA CDP1800 SERIES)

- DECREASE POWER AND MASS REQUIREMENTS (CMOS LSI)

- INCREASE RELIABILITY (REDUCE PARTS COUNT)

- SIMPLIFY DESIGN (REPLACE DISCRETE, MSI LOGIC)

- EXTEND INSTRUMENT CAPABILITY (FALLOUT, NOT A REQUIREMENT)

- ADD FLEXIBILITY TO ACCOMODATE CHANGING REQUIREMENTS (SOFTWARE)

- PROVIDE ENHANCED MODE GENERATION AND CONTROL (MINIMAL H/W)

- GENERALIZE INSTRUMENT

- MODIFY OR UPGRADE FOR FUTURE USE ON OTHER SPACECRAFT

### INSTRUMENT DATA SYSTEM FUNCTIONS

- SUPPORT SPACECRAFT INTERCOMMUNICATION BUS AND PROTOCOL

- DECODE AND PROCESS INSTRUMENT COMMANDS

- GENERATE INSTRUMENT OPERATING MODES

- CONTROL MECHANISMS

- PROCESS SCIENCE DATA FOR OUTPUT

#### DATA SYSTEM FUNCTIONS

- SUPPORT OF SPACECRAFT BUS AND PROTOCOL

- SERIAL, SYNCHRONOUS DATA AT 403.2 KBPS

- ISOLATED USER INTERFACES (TRANSFORMERS)

- MEMORY TO MEMORY TRANSFER USING DIRECT MEMORY ACCESS

- S/C COMMAND DATA SYSTEM (CDS) INITIATES AND CONTROLS ALL ACTIVITY ON A TIME MULTIPLEXED BASIS

- DECODING AND PROCESSING OF INSTRUMENT COMMANDS

- ACCOMODATE VARIOUS INPUT DATA

- COMMANDS

- MEMORY LOAD

- S/C TIME AND SPIN DATA

- PROCESS COMMANDS

- ERROR CHECKING & VALIDATION

- UPDATE OF INSTRUMENT STATE DATA

#### DATA SYSTEM FUNCTIONS (CONT'D)

- GENERATION OF INSTRUMENT OPERATIONAL MODES

- ALLOW FUNCTIONAL LEVEL COMMANDING (TYPICALLY 3 TO 8 MAJOR MODES)

- REDUCE INTER-SUBSYSTEM COMMUNICATION

- SYNCHRONIZE WITH SPACECRAFT TIMING

- PROVIDE MORE MODE GENERATION FLEXIBILITY TO THE INSTRUMENT

- MECHANISMS CONTROL FUNCTIONS (SENSORS, FILTER WHEELS, MULTIPLEXERS, ETC.)

- SENSE MECHANISM STATUS

- GENERATE CONTROL SIGNALS

- ACQUIRE AND BUFFER DATA

- SCIENCE DATA PROCESSING

- APPLY ALGORITHMS TO PROCESS DATA (COMPRESSION, STATISTICS, DE-SPIN, ETC.)

- FORMAT DATA (CONTROL SUBCOMMUTATION, ADD ENGR & STATUS, ETC.)

- OUTPUT TO BUS UPON REQUEST

## INSTRUMENT SUMMARY

| <u>ABBR.</u><br>SS1 | NAME<br>SOLID STATE IMAGING           | PRINCIPAL INVESTIGATOR<br>DR. J.S. BELTON,<br>(TEAM LEADER) | INSTITUTION<br>KIT PEAK NATIONAL OBSERVATORY,<br>TUSCON, AZ     |

|---------------------|---------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|

| NIMS                | NEAR INFRARED MAPPING<br>SPECTROMETER | DR. R. CARLTON,<br>(TEAM LEADER)                            | JET PROPULSION LABORATORY, ,<br>PASADENA, CA                    |

| PPR                 | PHOTOPOLARIMETER<br>RADIOMETER        | DR. J.E. HANSEN                                             | GODDARD INSTITUTE FOR SPACE STUDIES,<br>NEW YORK, NY            |

| UVS                 | ULTRAVIOLET SPECTROMETER              | DR. C.W. HORD                                               | LABORATORY FOR ATMOSPHERIC AND SPACE<br>PHYSICS, BOULDER, CO    |

| EPD                 | ENERGETIC PARTICLE DETECTOR           | DR. D.J. WILLIAMS                                           | NOAA SPACE ENVIRONMENT LABORATORY,<br>BOULDER, CO               |

| PLS .               | PLASMA SUBSYSTEM                      | DR. L.A. FRANK                                              | UNIVERSITY OF IOWA,<br>IOWA CITY, IOWA                          |

| MAG                 | MAGNETOMETER                          | DR. M. KIVELSON                                             | UCLA<br>LOS ANGELES, CA                                         |

| DDS                 | DUST DETECTOR SUBSYSTEM               | DR. EBERHARD GRÙN                                           | MAX PLANCK INSTITUT FÜR KERNPHYSIC,<br>HEIDELBURG, WEST GERMANY |

| PWS                 | PLASMA WAVE SUBSYSTEM<br>(NO ⊔P)      | DR. D.A. GURNETT                                            | UNIVERSITY OF IOWA,<br>IOWA CITY, IOWA                          |

|                | • •                         |              | INSTRU              | IMENT CO      | MPLEXITY CO            | MPARISON         |               |               |               |

|----------------|-----------------------------|--------------|---------------------|---------------|------------------------|------------------|---------------|---------------|---------------|

| INST           | RO <b>M</b><br><u>KBYTE</u> | RAM<br>KBYTE | TELM DATA<br>(KBPS) | DATA<br>Modes | NO<br>Command<br>Parms | NO<br>MECHANISMS | NO<br>SENSORS | MASS<br>_(KG) | PWR<br>(WATT) |

| SSI            | 3                           | 3.5          | 768. то 0.02        | 3             | 24                     | 9                | 800 x 800 CCD | 28.0          | 25.           |

| NIMS           | 3                           | 1.75         | 11.52               | 6             | 31                     | 9                | . 17          | 18,1          | 16.           |

| PPR            | - 4                         | 0.25         | 0.18                | 5             | 12                     | 10               | 3             | 4.3           | 12.           |

| ·UVS           |                             | 0,75         | 1.0                 | 3             | 20                     | 6                | · 3           | 4.2           | 4.5           |

| EPD-1          | .4                          | 2.66         | 0.92                | 15            | 150                    | 50               | 17            | 8.5           | 8.6           |

| EPD-2          | 2.                          | 0,25         |                     | '             | 50                     | · <u> </u>       | - <b>-</b> -  | (INCL         | ABOVE)        |

| PLS-1          | 4                           | 4            | 0.6                 | 7             | 140                    | 31               | 20            | 10.7.         | 9.5           |

| PLS-2          | (SAME                       | AS PLS-1     | ) • • •             | •             |                        | -                |               |               |               |

| DDS            | 3                           | 2            | .024                | 3 .           | 33                     | 9                | 4             | 4.0           | 1.8           |

| PWS<br>(NO ⊬P) |                             | 0.25         | 645. то 0.2         | 2             | 7                      | 11               | 3             | 5.3           | 5.6           |

#### INSTRUMENT DATA SYSTEM HIGHLIGHTS (SELECTED FROM AMONG THE EIGHT INSTRUMENTS)

#### 1) FUNCTIONAL COMMANDING AND MACRO MODE GENERATION

- 2) TASK ALLOCATION BETWEEN MICROPROCESSOR AND OTHER INSTRUMENT HARDWARE

- HIGH RATE DATA TRANSMISSION

- SPECIALIZED PROCESSORS (FORMATTERS, MULTIPLIER, ENCODER/COMPRESSOR, ETC.)

- SOFTWARE OVERALL CONTROL

- HYBRID INSTRUMENT OPERATION (WITH OR WITHOUT µP)

- 3) ENHANCED DATA ACQUISITION & TELEMETRY OUTPUT

- SUBSYSTEM UNIFORMITY

- ADDED ENGINEERING VISIBILITY (SPECIAL HIGH-RATE MODES, SUBCOMS, ETC.)

- SOME ADDITIONAL ON-BOARD PROCESSING & BUFFERING (DATA DISCRIMINATION, DATA SEARCH, OPTIMUM AVERAGING, COMPRESSION, ETC.)

- 4) MEMORY RE-ALLOCATION AND REPROGRAMMABILITY FOR SCIENCE MODE OPTIMIZATION AND RESPONSE TO SUBSYSTEM OR SPACECRAFT FAILURES

- RAM MARGIN

- RAM REPLACEMENT OF ROM VIA BUS COMMAND

- ROM LINKAGES TO RAM FOR SUBROUTINE REPLACEMENT

#### INSTRUMENT DATA SYSTEM HIGHLIGHTS (CONT'D)

- 5) HIGHLY FLEXIBLE APPROACH

- ALLOWS SUBSYSTEM OPTIMIZATION

- WIDE RANGE OF DATA RATES

- 8 UNIQUE DESIGNS

- 6) CLEAR BENEFIT IN LOGIC REPLACEMENT OBSERVED

- (7) ADVANCED DATA SYSTEM TECHNIQUES

- MULTIPLE MICROPROCESSORS

- POWER HSARING, FAILURE ISOLATION

- AUTO-CALIBRATION

- BACKGROUND PROCESSING, HIGH LEVEL LANGUAGE (FORTH)

- 8) COMPATABLE WITH LONG-RANGE DEEP SPACE EXPLORATION DESIGNS AND GOALS

- PACKET TELEMETRY

- ADDED AUTONOMY

- EEIS

#### PROBLEM AREAS ENCOUNTERED

- 1) HARDWARE DESIGN LIMITATIONS AND CONSTRAINTS

- SPACECRAFT MASS, POWER, AND RELIABILITY REQUIREMENTS

- LIMITED OPTIONS IN µP AND CHIP FAMILY SELECTION (1802, 1852, 1856, 1834, TC244)

- LIMITED MEMORY SIZE (RAM IS 256 x 4 BITS)

- JUPITER MISSION REQUIRED HIGH RADIATION TOLERANCE

- PARTS DEVELOPMENT AND ACQUISITION PROBLEMS

- CAUSED INCREASED COST, SCHEDULE PROBLEMS

- 2) USE OF READ ONLY MEMORY (ROM) AS PRIMARY PROGRAM MEMORY

- INCREASED COSTS AND SCHEDULING PROBLEMS

- DECREASED FLEXIBILITY

- INCREASED NEED FOR EARLY SYSTEM-LEVEL VALIDATION

- 3) UNDERSCOPING OF MICROPROCESSOR DEVELOPMENT TASKS AND COSTS

- SOFTWARE, SOFTWARE MANAGEMENT AND DOCUMENTATION

- DEVELOPMENT SYSTEMS AND SUPPORT EQUIPMENT

- INTERFACE REQUIREMENTS STABILITY

- ADDED TESTING COMPLEXITY

#### PROBLEM AREAS ENCOUNTERED (CONT'D)

4) BUS DESIGN

- BUS ADAPTER COMPLEXITY

- LOW ERROR REQUIREMENT

- OPEN-LOOP PROTOCOL (NO HANDSHAKE)

- 5) SYSTEM LEVEL REQUIREMENT IMMATURITY

- END-TO-END INFORMATION SYSTEM (EEIS) GOALS REDUCED

- EARLY INTERFACE REQUIREMENT STABILITY AND DETAILED DESCRIPTION

- 6) PERSONNEL EXPERIENCE AND TRAINING

- µP

- SOFTWARE

#### EVALUATION OF THE GALILEO APPROACH

- CURRENT STATUS

- MOST INSTRUMENTS HAVE AN OPERATIONAL BREADBOARD DATA SYSTEM NOW

- EXPECT ON-TIME DELIVERY OF ADVERTISED CAPABILITY

- EXPECT TO SIGNIFICANTLY ENHANCE THE SCIENCE VALUE OF THE MISSION

- EACH INSTRUMENT PROVIDES SCIENCE OPTIMIZATION FOR ITS INVESTIGATORS

- EACH HAS PROVIDED FOR INCREASED IN-FLIGHT FLEXIBILITY

- ADDITIONAL EFFORT MUST BE EXPENDED TO SOLVE PROBLEMS ASSOCIATED WITH:

- SYSTEM REQUIREMENTS DEFINITION

- IMPROVED USE OF MICROPROCESSOR DEVELOPMENT TOOLS

- FUNDING CONSISTENT WITH THE ENHANCED CAPABILITY AND COST

#### FUTURE PROJECTIONS

- TECHNOLOGY IMPROVEMENT

- SEMICONDUCTOR TECHNOLOGY (ADVANCED µP, DENSE MEMORY, HIGHER SPPED, ETC.)

- ADVANCED ARCHITECTURE AND SOFTWARE DESIGN (MULTIPLE MICROPROCESSORS, HIGH LEVEL LANGUAGES, ETC.)

#### APPLICATION ADVANCES

- INSTRUMENT AUTONOMY

- HIGHLY FUNCTIONAL COMMANDING

- EXTENSIVE ON-BOARD PROCESSING (ESPECIALLY FRONT-END APPLICATIONS)

# Page Intentionally Left Blank

#### A COMMAND & DATA SUBSYSTEM FOR DEEP SPACE EXPLORATION BASED ON THE RCA 1802 MICROPROCESSOR IN A DISTRIBUTED CONFIGURATION

Jack S. Thomas California Institute of Technology Jet Propulsion Laboratory Pasadena, California

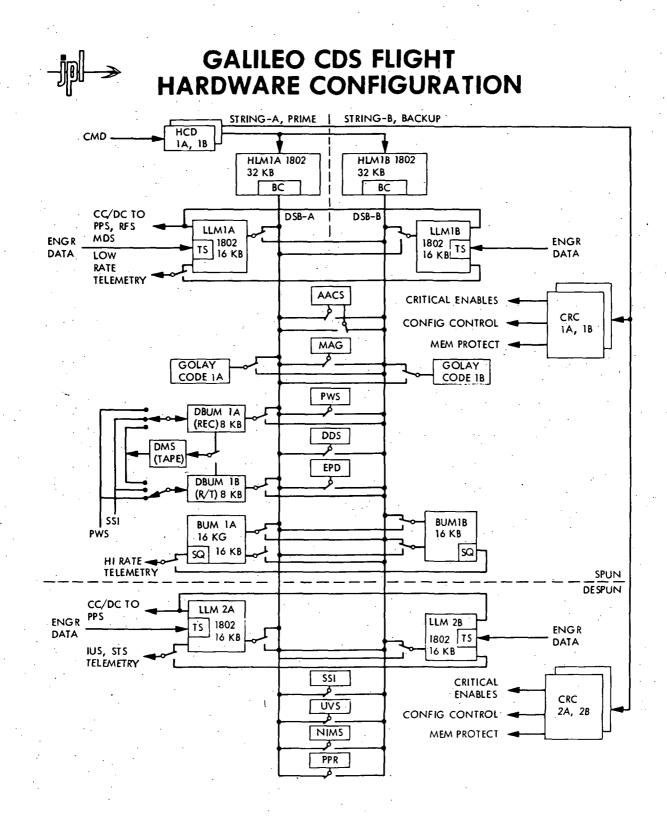

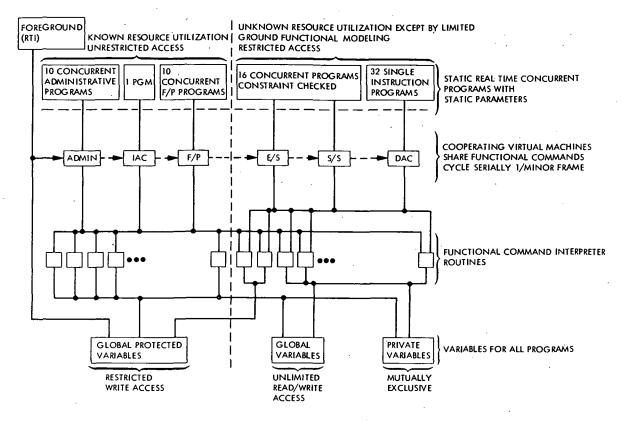

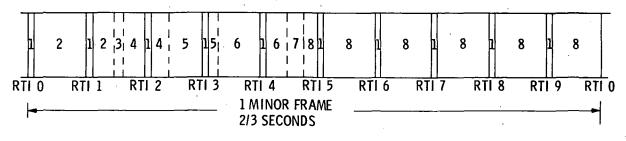

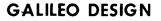

The Command and Data Subsystem (CDS) is an RCA 1802 CMOS microprocessor-based subsystem that acts as the central nervous system for the Galileo Orbiter Spacecraft. All Communication between the ground and spacecraft flows through the CDS. The CDS also distributes commands in real time, algorithmetically expanded from a data base loaded from the ground and in response to spacecraft alarms.

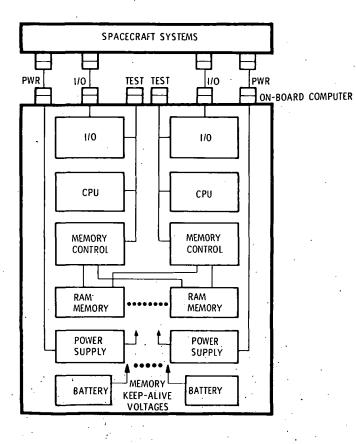

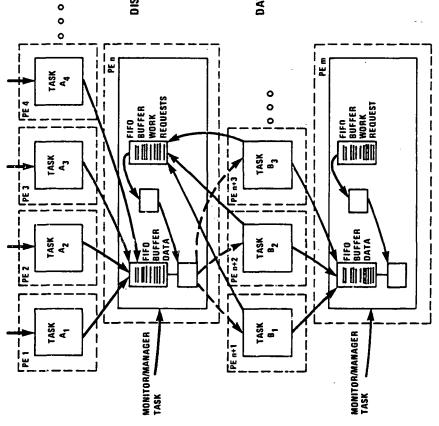

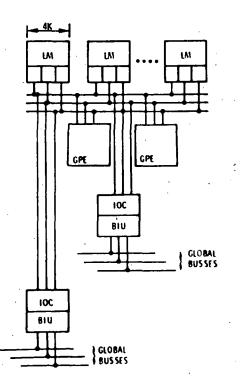

The distributed microprocessor system is configured as a redundant set of hardware with three microprocessors on each half. The microprocessors are surrounded by a group of special purpose hardware components which greatly enhance the ability of the software to perform its task.

The presenter shows how the software architecture makes a distributed system of six microprocessors appear to each user as a single virtual machine, and collectively as a set of cooperating virtual machines that prevent the simultaneous presence of the several users from interfering destructively with each other.

18

ð

# → GALILEO CDS FLIGHT SOFTWARE ARCHITECTURE

### HLM PROCESSOR TIME ALLOCATION

- 1. FOREGROUND EXECUTIVE

- 2. ADMINISTRATIVE PROGRAMS

- 3. IMMEDIATE ACTION COMMAND PROGRAM

- 4. FAULT PROTECTION PROGRAMS

- 5. ENGINEERING SEQUENCE PROGRAMS

- 6. SCIENCE SEQUENCE PROGRAMS

- 7. DELAYED ACTION COMMAND PROGRAMS

- 8. PROCESSOR TIME MARGIN

#### SYNERGISTIC INSTRUMENT DESIGN

#### Dale E. Winter Jet Propulsion Laboratory Pasadena, California

- I. The Synergistic Approach

- A. Do a functional design

- 1. Block-out all system functions.

- 2. Identify all areas that are exclusively analog.

- 3. Identify all areas that are exclusively digital.

- 4. Identify any analog/digital hybrid areas.

- B. Design hardware to promote efficient software.

- 1. Supply task-efficient timing.

- 2. Supply task efficient I/O structures.

- 3. Design a task/code efficient system architecture.

- C. Design software to promote efficient hardware.

- 1. Structure software to minimize hardware.

- 2. Customize coding to be task efficient.

- 3. Directly replace hardware functions wherever possible.

- 4. Use time and memory space wisely.

- D. Completed design yields bonuses.

- 1. Additional features can be included with nominal hardware increases.

- 2. Design changes can be made easily.

- 3. Less hardware means less power, less mass and fewer failures.

- II. The Galileo Television Camera

- A. Taking pictures.

- 1. Filter selection and shuttering with software timed pulses directly to mechanism drive amplifiers.

- 2. CCD readout H1 rate timing executed in hardware.

- 3. CCD readout LO rate timing and video/data system time syncronization executed in software.

- 4. Software timing is precision synchronized with system clock to assure exposure accuracy.

- B. Telemetry acquisition.

- 1. Software controlled ADC and Mux.

- 2. Precision sample times.

- 3. Software can position sample times anywhere within the camera cycle to monitor specific activities.

#### C. Communications

- 1. Non-immediate bus adapter does most work in software.

- 2. Software sequencing sync's up with time broadcast.

- 3. Software rate buffers telemetry for transmission.

#### D. In-flight problem solving.

- 1. Programmable telemetry can profile electrical activity.

- 2. Multi-mode memory switching and mixing.

- 3. In-flight re-programming capability.

- 4. Diagnostic software reports and time tags errors.

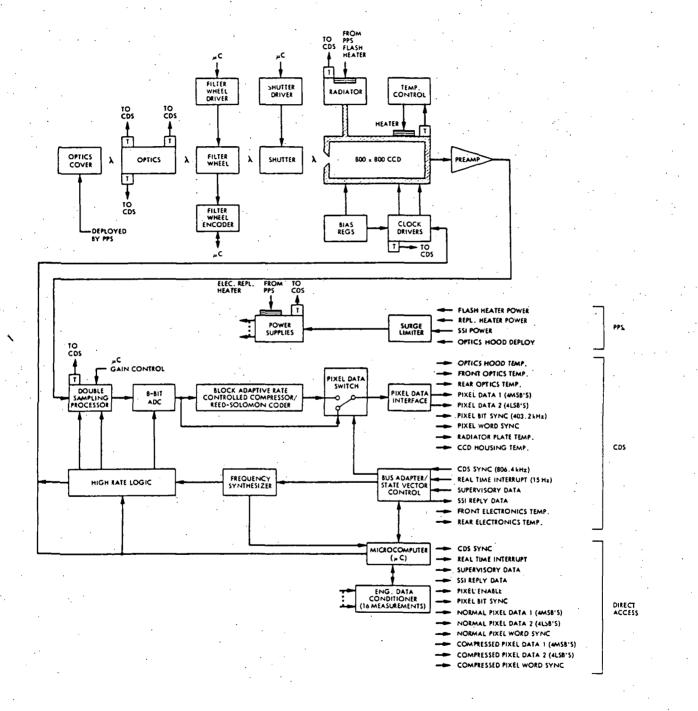

#### SSI Timing

SSI image parameter control and timing signal generation is based on applicat on of microcomputer technology. In addition to controlling serial pixel shifting and pixel analog-to-digital conversion, all timing, sequencing, mechanism control, engineering and status data acquisition, and buffering shall be performed under programmed microcomputer control. SSI data rates and formats shall be as specified in GLL-3-280, Telemetry Measurements and Data Formats. Additional SSI rates and timing intervals are presented in Table 1. Figures 2A, 2B and 2C present the relationship between the various SSI timing parameters for SSI imaging modes of 8 2/3, 30 1/3 and 60 2/3 seconds respectively.

|    |                              |                      |                       | · · · · · · · · · · · · · · · · · · · |

|----|------------------------------|----------------------|-----------------------|---------------------------------------|

|    |                              | 8 2/3 Second<br>Hode | 30 1/3 Second<br>Mode | 60 2/3 Second<br>Node                 |

| a. | Pixel bit rate               | 806.4 KBPS           | 806.4 KBPS            | 806.4 KBPS                            |

| Ь. | Pixel rate                   | 100.8K Pixels/s      | 100.8K Pixels/s       | 100.8K Pixels/s                       |

| c. | Line time                    | 8 1/3 m sec          | 33 1/3 m sec          | 66 2/3 m sec                          |

| d. | Read frame time              | 6 2/3 sec            | 26 2/3 sec            | 53 1/3 sec                            |

| e. | Frame repetition<br>time     | 8 2/3 sec            | 30 1/3 sec            | 60 2/3 sec                            |

| f. | Prepare time                 | 2.0 sec              | 3 2/3 sec             | 7 1/3 sec                             |

| g. | Filter steps<br>allowed      | 2                    | 3                     | 7                                     |

| h. | Maximum normal<br>exposure   | 800 m sec            | 800 m sec             | 800 m sec                             |

| i. | Maximum extended<br>exposure | 6400 m sec           | 25600 m sec           | 51200 m sec                           |

| j. | SSI reply data rate          | 403.2 KBPS           | 403.2 KBPS            | 403.2 KBPS                            |

| k. | CDS sync                     | 806.4 KBPS           | 806.4 KBPS            | 806.4 KBPS                            |

| 1. | Real-time interrupt          | 15 Hz                | 15 Hz                 | 15 Hz                                 |

TABLE 1. SSI TIMING PARAMETERS

#### FIGURE 1. SSI FUNCTIONAL BLOCK DIAGRAM

# Galileo REQUIREMENTS

- COMMUNICATE VIA CDS BUS PROTOCOL

- MEET CAMERA FUNCTIONAL OBJECTIVES

- PREVENT HAZARDOUS CONDITIONS

- PROVIDE CAMERA HEALTH DATA

- PROVIDE FOR BACK-UP MODES

- PROVIDE FOR POST LAUNCH REPROGRAMMING

- PROVIDE DIAGNOSTIC TOOLS

# Galileo DESIGN CRITERIA

- FUNCTIONAL REQUIREMENTS

- CIRCUIT STIMULATION REQUIREMENTS

- COMMUNICATIONS REQUIREMENTS

- •TIMING CONSIDERATIONS

- HARDWARE/SOFTWARE TRADEOFFS

- DIAGNOSTICS

- FAULT DETERMINATION

- REPROGRAMMING TECHNIQUES

## Galileo DESIGN APPROACH

- EFFICIENT PROGRAM ARCHITECTURE

- OPTIMAL MEMORY USAGE AND EXECUTION TIMES

- ERRONEOUS COMMAND PROTECTION

- PARITY ERRORS/ILLEGAL COMMANDS

- CONTINUOUS DIAGNOSTICS

- CHECKSUMS/SCRATCH-PAD WRITE-READ

- FAULT DATA IN TELEMETRY

- PARITY ERROR, COMMAND TRAFFIC, ILLEGAL COMMAND COUNTS

- DIAGNOSTIC RESULTS/FAULT TIME TAG

- SPECIAL FAULT ANALYSIS TOOLS

- PROGRAMMABLE ENGINEERING READOUTS

- PROGRAMMABLE MEMORY MONITOR

- BACK-UP MEMORY CONFIGURATIONS

- EXECUTE CODE FROM RAM, ROM + RAM, ROM/RAM + SCRATCH-PAD

- USE SPARE SCRATCH-PAD FOR CODE OR DATA

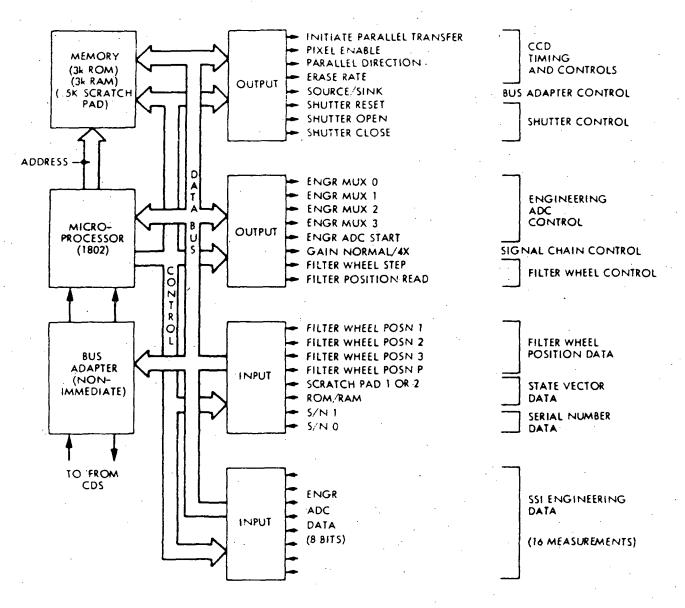

### فواناده DATA SYSTEM ARCHITECTURE

- OUTPUT PORTS SUPPLY LOW AND MEDIUM RATE PULSES AND SIGNALS TO CAMERA ELECTRONICS

- SOFTWARE DISPATCHES AND TIMES OUTPUTS IN ACCORDANCE WITH COMMAND, FUNCTIONAL AND ELECTRICAL REQUIREMENTS

- INPUT PORTS SUPPLY ENGINEERING, FILTER POSITION AND STATUS DATA TO THE SOFTWARE

- FLAGS SUPPLY RTI, PROGRAM LINK MODE, SRTI PHASE AND CDS BUS PARITY ERROR DATA TO THE SOFTWARE

- SOME OUTPUTS ARE RE-CLOCKED WITH SRTI OR SRTI PHASE TO ASSURE SYSTEM SYNCHRONISM

# Salileo SSI MICROCOMPUTER

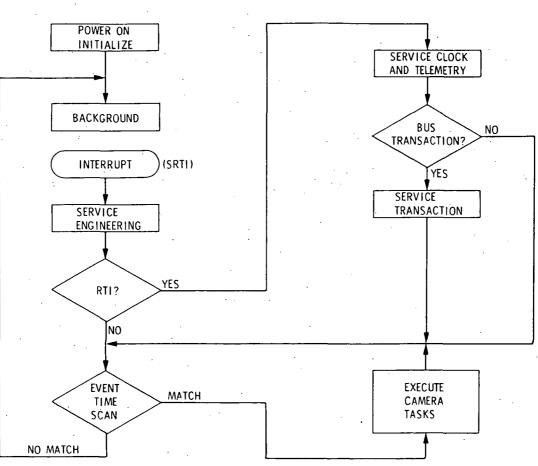

# Galileo SOFTWARE STRUCTURE

- REAL TIME INTERRUPT DRIVEN

- FOREGROUND/BACKGROUND OPERATION

- INTERNAL SPACECRAFT TIME CLOCK

- TIME DISPATCHED EVENTS

- SYNCHRONOUS OUTPUTS

BASIC PROGRAM FLOW

Galileo

# Page Intentionally Left Blank

#### APPLICATION OF MICROPROCESSORS TO INTERPLANETARY SPACECRAFT DATA SYSTEMS

#### Samuel G. Deese Jet Propulsion Laboratory Pasadena, California

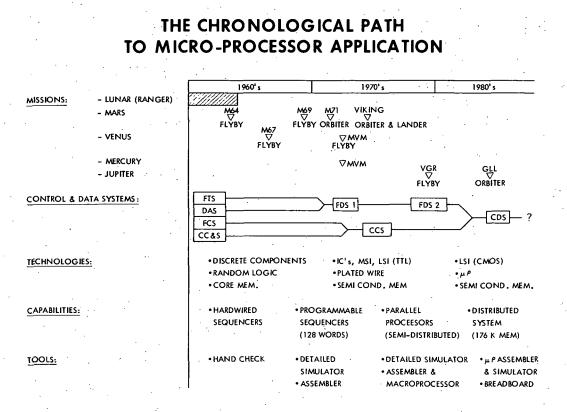

The Jet Propulsion Laboratory has committed to the use of a microprocessor based distributed data system in the 1984 Galileo mission to Jupiter. There has been an evolution of this commitment following the advances in component and device technology. Early spacecraft were very simple with subsystems very much single function oriented. Our understanding was very high and the need for design and analysis tools very low.

As technology grew, so did the complexities of the systems. Step by step, subsystems and functions were combined thus increasing their capability as well as complexity. Missions became more ambitious and the returns were high. Costly design and analysis tools were developed to support system test and operations. With these tools we were able to some small degree analyze and/or predict the performance of the spacecraft.

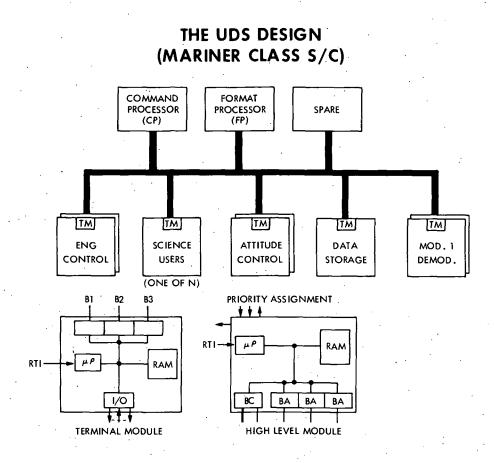

The Galileo Command and Data Subsystem (CDS) evolved from the combination of two special purpose computers from previous spacecraft: the Flight Data Subsystem and the Computer Command Subsystem. The CDS architecture utilizing concepts investigated in the development of the Unified Data Subsystem (UDS) takes advantage of the microprocessor technology and serves as the core of the distributed microprocessors interconnected by a high speed data bus.

The CDS design is complete and breadboard integration and test are in process. The flight software is in the requirements and "prototype" design phase. Many obstacles have been encountered and overcome. Some worthy of mention are:

- 1) Choice of a microprocessor architecture based primarily on its power and radiation hardness qualifications.

- 2) High speed operation of CMOS logic.

- 3) Adaptation of a Higher order Language to a microprocessor and in particular to a processor with an architecture not well suited for the CDS application.

- 4) The difficulties in obtaining quantities of <u>qualified</u> parts that are very complex and have difficult requirements, i.e. radiation hardening.

- 5) Availability of design and analysis tools for understanding and validating distributed systems with concurrent processing.

Ongoing advanced development and preproject studies are primarily based on data system designs having the same requirements as the CDS. We are committed in the future to the continued application of microprocessors to distributed data systems; solutions to the above problems; and to continue to follow advances in technology with the incorporation of VLSI into modular fault tolerant building blocks.

In summary, technology and complexity have very rapidly advanced since the first Ranger spacecraft in the 1960s. The design and analysis tools have sadly lagged this progress leaving our ability to "best" design and understand what we have designed less than optimum. Along with our use of the new technologies of the future, we must also attack this deficiency.

#### THE BASELINE - UDS

THE UDS, A DEVELOPMENT SPONSORED BY THE NASA UNDER CONTRACT NAS7-100 WITH THE CALIFORNIA INSTITUTE OF TECHNOLOGY AT JPL. SALIENT FEATURES:

- REAL TIME CONTROL - PRECISE TIMING

- DISTRIBUTED ARCHITECTURE

+ DISTRIBUTED FUNCTIONS (HI-LEVEL CONTROL, LOW-LEVEL EXECUTION)

+ INTERACTION MINIMIZED

+ HIERARCHICAL CONTROL

+ COMPUTER INDEPENDENCE

- STANDARDIZED SOFTWARE AND SUPPORT EQUIPMENT

- STANDARD INTERFACES

FEASIBILITY DEMONSTRATED VIA:

- BREADBOARD OF BASIC SYSTEM UTILIZING NAKED MINI'S

- ONE REMOTE TERMINAL UNIT (RTU) INCLUDING 8080 MICROPROCESSOR

- DEVELOPED CONCEPT OF UDS DESIGN LANGUAGE (UDL)

- DESIGNED AND IMPLEMENTED "TYPICAL" APPLICATION SOFTWARE

- EXPLORED CONCEPTS OF DEBUGGING A DISTRIBUTED SYSTEM

THE RTU

INITIALLY DEVELOPED AS A PART OF THE UDS.

- UDS I/O TYPE INTERFACES

- UDS BUS INTERFACE

- MICROPROCESSOR DRIVEN

PROPOSED FOR DEVELOPMENT AS A NASA STANDARD FOR POSSIBLE USE WITH:

- MMS (DHCS NSSC-1)

- GALILEO

- VARIOUS PREPROJECT STUDIES

#### CONCEPT DIED

- BURDENED WITH UNIVERSAL I/O

- SALE OF THE CONCEPT NO VOLUNTARY FIRST USER

- FEW SUPPORT FACILITIES

MAIN INHERITANCE FROM THIS EFFORT - RCA 1802 MICROPROCESSOR, IMPLEMENTATION CONCEPTS OF BA AND BC. A COMMITMENT TO A DISTRIBUTED DATA SYSTEM UTILIZING THE MICROPROCESSOR TECHNOLOGY IN A FLIGHT DEVELOPMENT ENVIRONMENT

DRIVERS ON DEVELOPMENT

- UDS AS A BASELINE

- LOW POWER AND RADIATION DICTATE ACCEPTANCE OF THE RCA 1802

- COMBINING FDS AND CCS INTO SINGLE SUBSYSTEM

- CHEAPER OPERATIONS

- VOYAGER AS A BASELINE

- CMOS (4000 SERIES) SUPPORT LOGIC

- MUST USE HOL (SPECIFICALLY, HAL-S)

- NOTION THAT THE MORE YOU DO ON BOARD - THE CHEAPER ON GROUND

STATUS

- DESIGN COMPLETE (HARDWARE)

- ARCHITECTURAL DESIGN OF FLIGHT SOFTWARE IN PROGRESS. SOME PROTOTYPE/ BREADBOARD DESIGNS. (J. THOMAS PRESENTATION)

- BREADBOARD AND SUPPORT EQUIPMENT INTEGRATED DESIGN VERIFICATION IN PROCESS

- HAL-S HAS BEEN REMOVED AS A REQUIREMENT.

- DESIGNS FOR SOFTWARE AND OPERATIONS SUPPORT TOOLS IN PROGRESS.

#### OTHER PROPOSED APPLICATIONS

COMET RENDEZVOUS

- MANY IMPLEMENTATIONS PROPOSED DEPENDING ON CHARACTER OF MISSION AT ANY GIVEN TIME AND ECONOMIC ENVIRONMENT.

- + BASED ON "CORE" DISTRIBUTED DATA SYSTEM

- + USERS NEED COMPUTING POWER

- + COMPUTING POWER DERIVED AS A STANDARD FOR THE S/C AND

- WOULD SIMPLY BE INCORPORATED INTO THE USER DESIGN (RTU SANS THE I/O).

OTHER PROPOSALS HAVE BEEN MADE, PRIMARILY BASED ON THE DISTRIBUTED SCHEME.

## COMET RENDEZVOUS PROPOSED DESIGN

#### THE CHRONOLOGICAL PATH OF PROBLEMS

EARLY DESIGNS (M69, M71, M73)

- SIMPLE DESIGNS EASILY UNDERSTOOD

- COMPONENT COMPLEXITY LESS; EASILY TESTED AND SCREENED

+ PROCESS PROBLEMS (PURPLE PLAGUE, CORROSION, ETC.)

- HARDWARE AND SOFTWARE DESIGN AIDS AVAILABLE EARLY

+ DETAILED SIMULATOR

• MEMORY SIZING

• TIMING

TEST SOFTWARE DEVELOPMENT AND VALIDATION

+ ASSEMBLER/LOADER

- SIMPLER SOFTWARE (128/500 words)

RECENT DESIGNS (VIKING, VOYAGER)

- DESIGNS MORE COMPLEX

- INCREASED COMPONENT COMPLEXITY

- HARDWARE AND SOFTWARE DESIGN AIDS AVAILABLE EARLY

+ DETAILED SIMULATOR

+ ASSEMBLER/MACRO PROCESSOR

THE CHRONOLOGICAL PATH OF PROBLEMS (CONT.)

RECENT DESIGNS (VIKING, VOYAGER) CONT.

- INCREASED COMPLEXITY IN SEQUENCING

- ON-BOARD FAULT MANAGEMENT (LIMITED)

- MORE COMPLEX SOFTWARE

- DECREASING R&AD FUNDS

GALILEO AND FORWARD

- LACK OF EARLY DEVELOPMENT TOOLS

- VERY COMPLEX COMPONENTS

- INCREASED COMPLEXITY IN SEQUENCING, ON-BOARD FAULT MANAGEMENT

- MORE SEVERE ENVIRONMENTS

- LACK OF CONTINUITY OF MISSIONS

- FURTHER DECREASE IN R&AD FUNDS

- MUST BE CHEAP

SPECIFIC PROBLEMS

- DIFFICULTY IN APPLYING HOL (HAL-S) TO RCA 1802

- RCA 1802 ARCHITECTURE PROBABLY NOT BEST SUITED FOR CDS TASK.

#### THE CHRONOLOGICAL PATH OF PROBLEMS (CONT.)

SPECIFIC PROBLEMS (CONT.)

- RADIATION HARDENING PROBLEMS

- ARCHITECTURAL EVALUATION

- MEMORY SIZING

- BUS TRAFFIC

- TIMING MARGINS

- DEVELOPMENT AND TEST OF TEST SOFTWARE

- COMPETITION IN LABOR MARKET

# Page Intentionally Left Blank

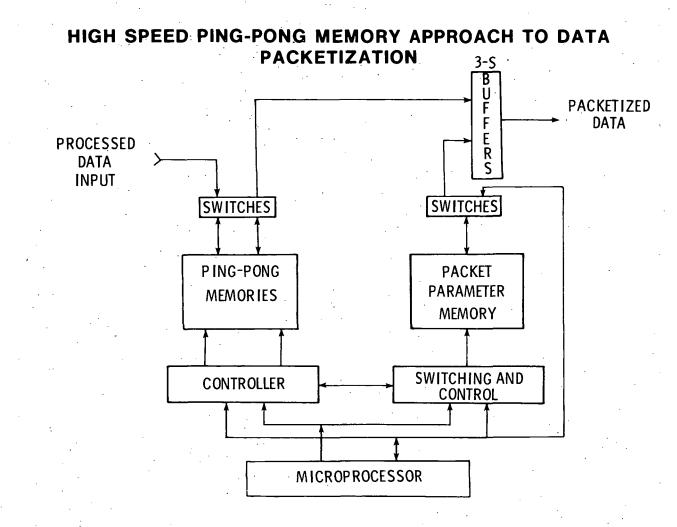

#### THE ROLE OF THE MICROPROCESSOR IN ONBOARD IMAGE PROCESSING FOR THE INFORMATION ADAPTIVE SYSTEM

#### W. Lane Kelly, IV, and Barry D. Meredith Langley Research Center Hampton, Virginia

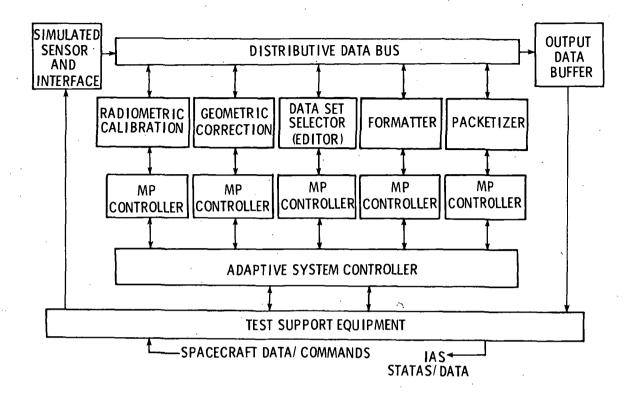

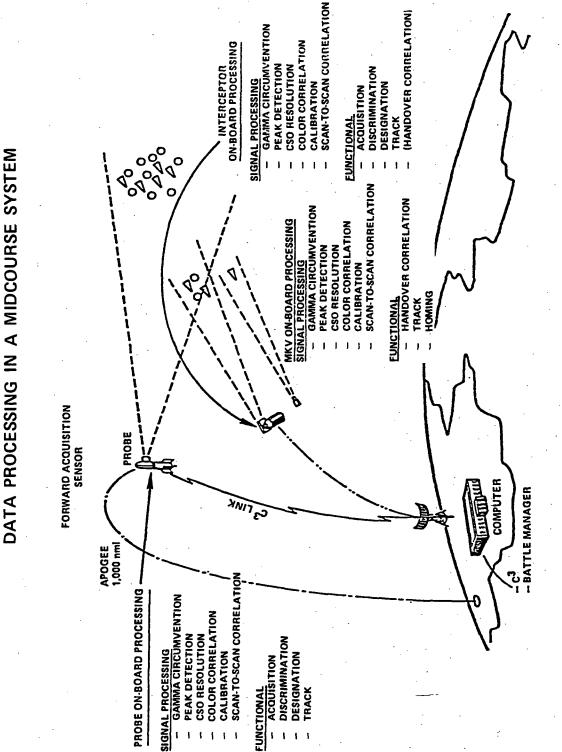

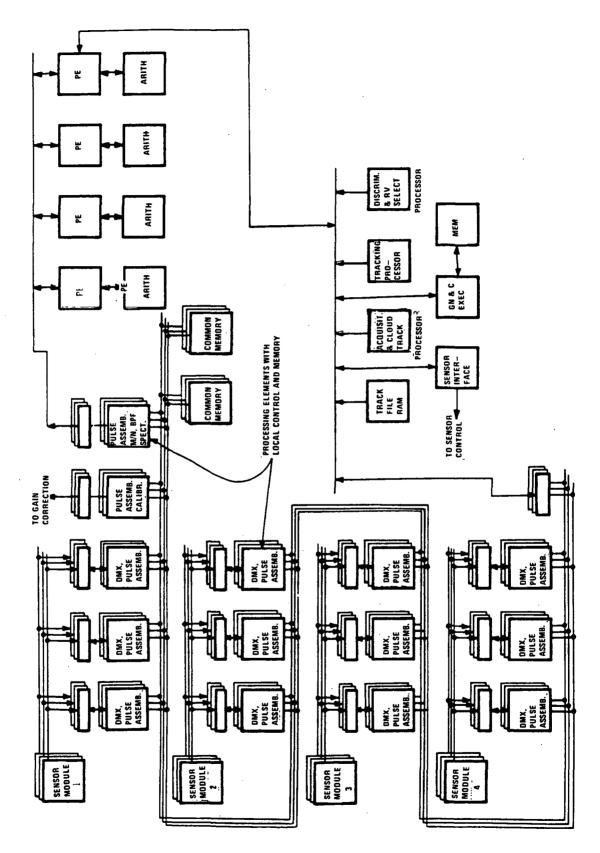

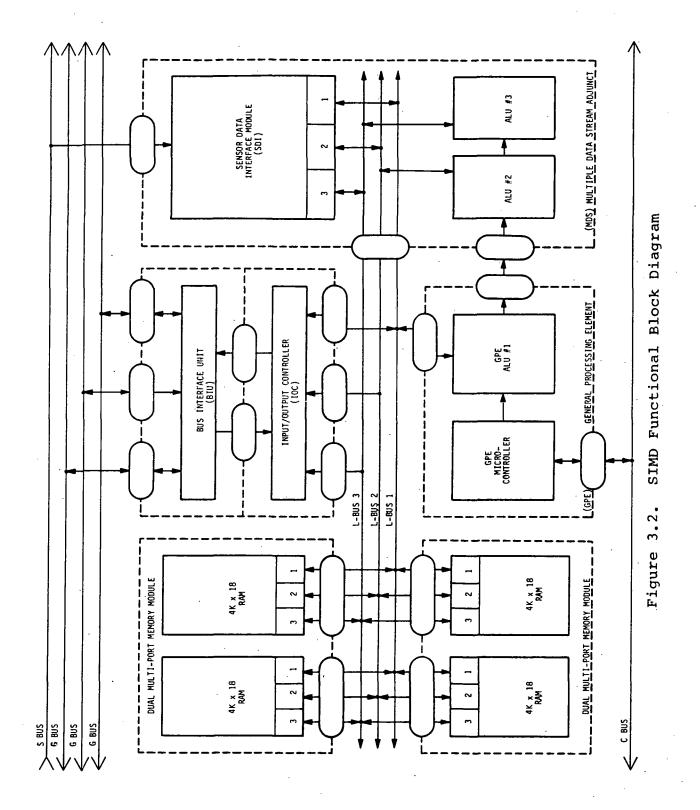

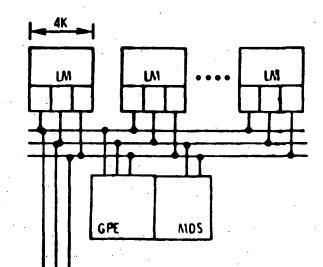

The Information Adaptive System (IAS) is an element of the NASA End-to-End Data System program and is focused toward high speed onboard data processing for NASA missions in the 1980's. Particular emphasis is placed on multispectral-image data processing since the speed and quantity of that variety of data places the greatest burden on the current NASA data system. Some of the image processing functions planned for the IAS include sensor nonuniformity correction, geometric correction, data editing, formatting, packetization and adaptive system control.

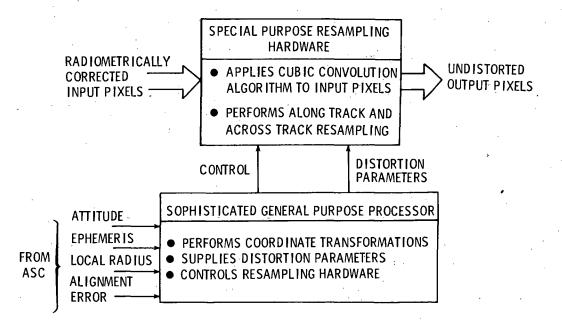

The design of the IAS is intended to apply to a variety of future missions; therefore, architectural flexibility is a key design feature. The programmability of the microprocessor lends this required flexibility to the system, allowing it to accommdate new processing functions and interface with a variety of sensor configurations. The high throughput rate required for multispectral image data processing prohibits the use of conventional computer software approaches without significant increases in the speed of the central processing unit. Hence, a combination of high speed special purpose hardware and microprocessors for control and computational support, appears to offer the best technical approach for the near term. In addition, a sophisticated microprocessor will serve as the overall system supervisor interfacing with commands from the spacecraft and the ground.

This paper presents the preliminary design of the Information Adaptive System and discusses the role of the microprocessor in the implementation of the individual processing elements.

# THE CURRENT NASA DATA SYSTEM PROBLEM

- EVER INCREASING DEMAND MET WITH PROBLEM BY PROBLEM SOLUTIONS.

- CURRENT DATA LOAD 10" bits/day.

- DATA PROCESSING DELAYS ARE EXCESSIVE.

- DATA PROCESSING COSTS ARE TOO HIGH.

- FORTHCOMING PROJECTS WILL INCREASE DATA LOAD BY AN ORDER OF MAGNITUDE.

- SHUTTLE CAPABILITY WILL BOOST LAUNCH RATE BY FACTOR OF 6.

# **NEEDS # II - INFORMATION ADAPTIVE SYSTEM**

GOAL: DESIGN, DEVELOP AND DEMONSTRATE IN EARLY 1983 A SYSTEM ARCHITECTURE THAT UTILIZES ADVANCED TECHNOLOGY FOR HIGH-SPEED MULTISPECTRAL IMAGE DATA PROCESSING.

DESIGN FEATURES:

- HIGH DATA THROUGHPUT RATE

- PROGRAMMABILITY

- FLEXIBLE ARCHITECTURE

- ADAPTABILITY

#### IAS DEMONSTRATION SYSTEM BLOCK DIAGRAM

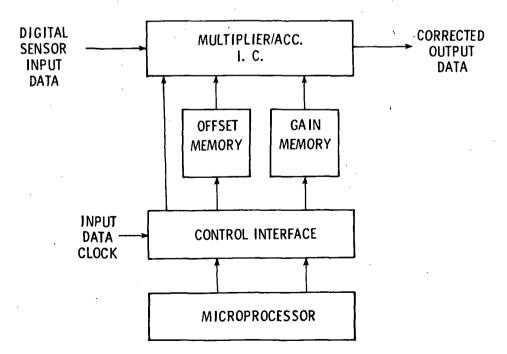

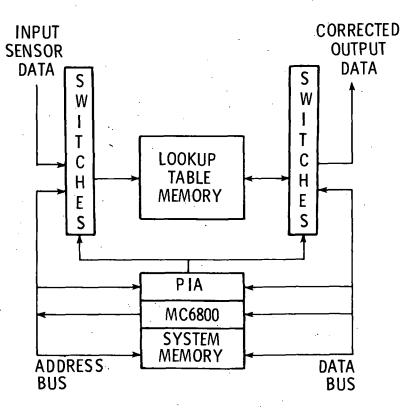

## RADIOMETRIC CORRECTION - LINEAR CURVE FIT APPROACH

LOOKUP TABLE DESIGN FOR RADIOMETRIC CALIBRATION

# SOURCES OF DISTORTION IN IMAGE DATA AND THEIR CORRESPONDING ERROR MEASUREMENT TECHNIQUES

EPHEMERIS VARIATIONS ------- GLOBAL POSITIONING SYSTEM (GPS)

SPACECRAFT ATTITUDE ------ ADVANCED STAR TRACKER VARIATIONS

SENSOR MISALIGNMENT ------ PERIODIC GROUND CALIBRATION

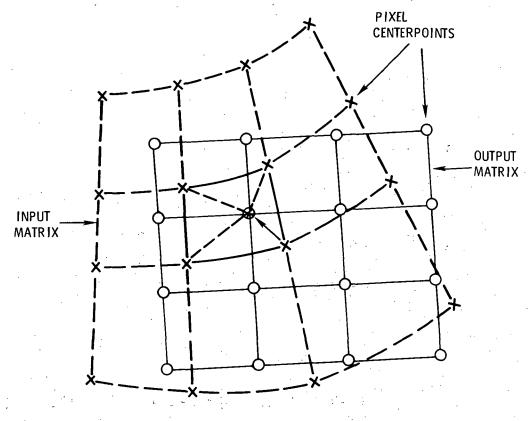

#### **GEOMETRIC CORRECTION**

#### **GEOMETRIC CORRECTION PROCESSING**

# EDITING CRITERIA UNDER INVESTIGATION

# FOR THE IAS

TIME

SPACECRAFT POSITION

INFORMATION FROM OTHER EXPERIMENTS

• CLOUD COVER

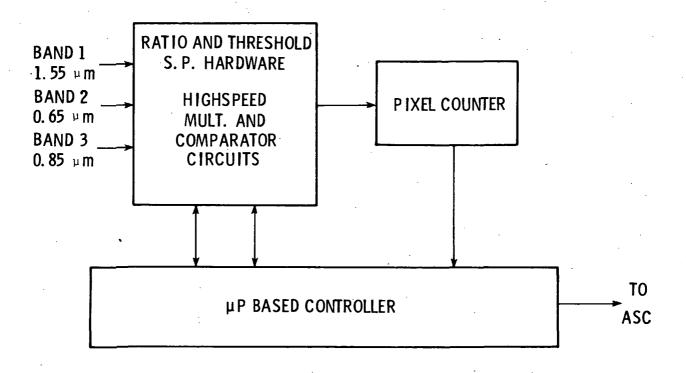

# IMPLEMENTATION OF CLOUD DETECTION ALGORITHM

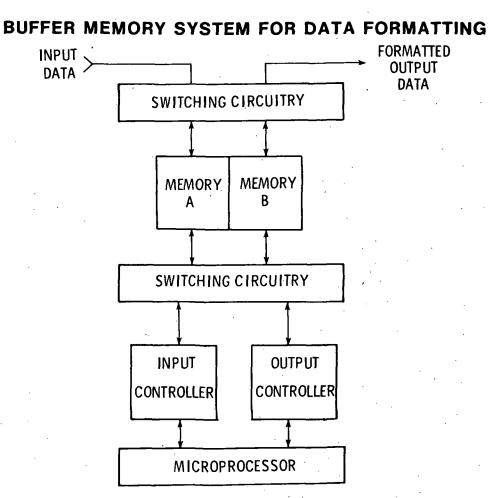

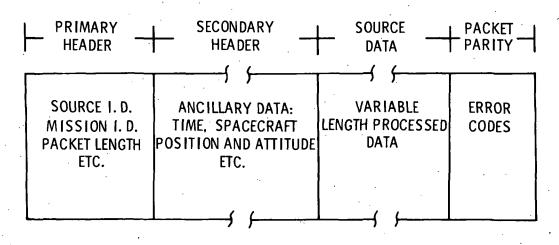

## NASA DATA PACKET FORMAT

## ADAPTIVE SYSTEM CONTROLLER TASKS

- INITIALIZE INDIVIDUAL CONTROLLERS

- ASSIST CONTROLLERS IN INITIALIZATION OF IAS COMPONENTS

- ESTABLISH AND MAINTAIN OPERATING MODE

- MONITOR STATUS OF ALL IAS COMPONENTS

- FORMULATE ERROR MESSAGES

- MAINTAIN COMMUNICATION WITH SPACECRAFT AND GROUND

- PROVIDE COMPUTATIONAL SUPPORT TO IAS MODULES

# ADAPTIVE SYSTEM CONTROLLER DESIGN FEATURES

- SOPHISTICATED MICROPROCESSOR ARCHITECTURE

- ADAPTABLÉ

- EXPANDABLE

- COMPATABLE WITH HIGH ORDER LANGUAGE

# Page Intentionally Left Blank

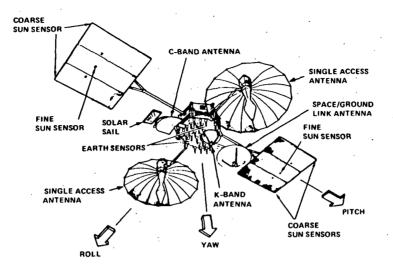

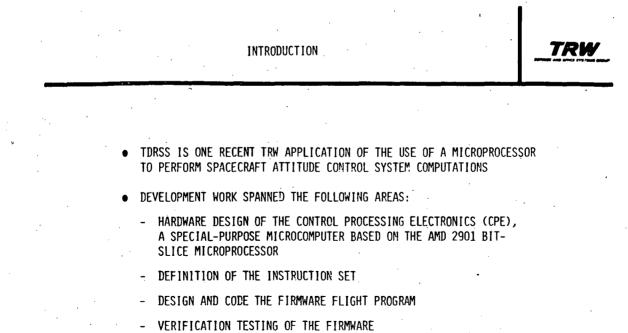

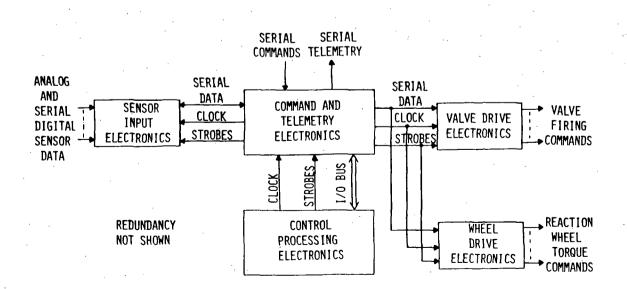

#### APPLICATION OF A MICROPROCESSOR TO A SPACECRAFT ATTITUDE CONTROL

#### D. H. Brady and F. W. Hermann TRW Defense and Space Systems Group Redondo Beach, California

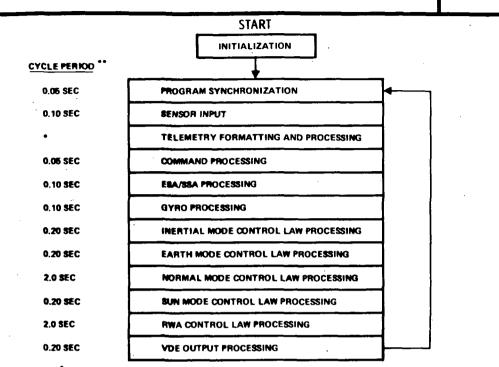

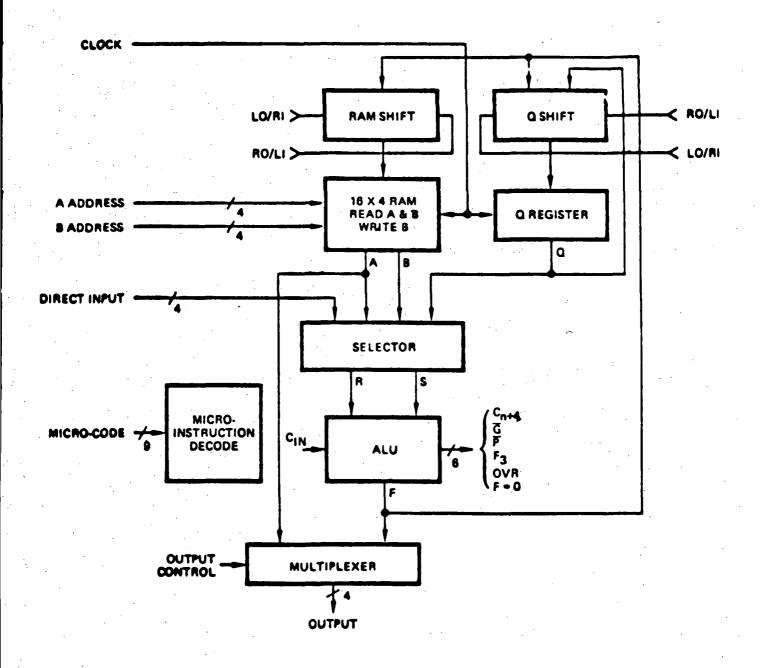

The space-qualified TDRSS attitude control system (ACS) microprocessor development work spanned three main design areas: hardware and instruction set, ACS firmware, and hardware/firmware verification testing.

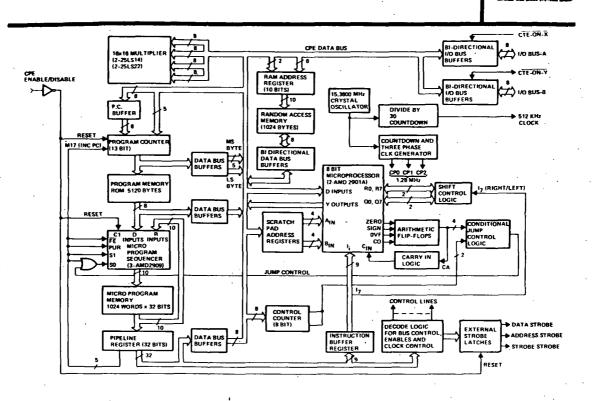

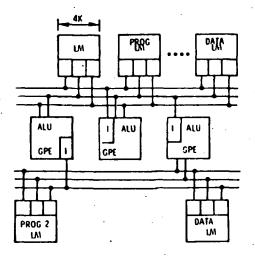

The Control Processor Electronics (CPE) hardware utilizes two parallel AM2901 4-bit microprocessors, with a microprogrammed instruction set tailored to the TDRSS controls application. Fourteen special purpose I/O instructions interface with the ACS hardware, each transferring data for one sensor while meeting timing and data-handling requirements. The ACS firmware resides in 5120 bytes of ROM with 1024 bytes of RAM for scratch data storage. The 16-bit add, subtract, and divide operations are overflow-protected and multiplies are done in hardware.

The firmware includes data processing for five sensors, four attitude control laws, and telemetry and commands. The main design limitations were: 16-bit word length, 1024 8-bit byte RAM, and computation speed/task sharing tradeoffs. It performed ACS computations quickly and without significant data degradation. The word length limitation motivated the careful selection of control filter topology and sacrifice of dynamic range in favor of null performance.

The flight program design was tested with three tools: Varian V-73 minicomputer, CDC Cyber computer, and the CPE development station. The V-73 simulation tested source (assembly) programs prior to development station availability. The CDC Cyber simulation was used primarily for accuracy analysis. The development station included commercial versions of the flight hardware which were run at full speed. All formal verification tests were run on the development station to verify timing, accuracy, and interface requirements.

From this development experience, additional hardware and software requirements were identified:

- Rapid Memory Examine/Change

- Floating point hardware

- High level language

47

7.

TDRSS SPACECRAFT CONFIGURATION

TRACKING AND DATA RELAY SATELLITE (TDRSS) MISSION:

COMMERCIAL COMMUNICATION FOR WESTERN UNION

• SATELLITE TRACKING AND DATA RELAY FOR NASA

#### TDRSS ATTITUDE CONTROL HARDWARE

CONTROL ELECTRONICS ASSEMBLY

- SENSORS

- EARTH SENSOR

- COARSE SUN SENSORS

- FINE SUN SENSORS

- GYROS

- REACTION WHEEL TACHOMETERS

- SOLAR ARRAY DRIVE RESOLVERS

- ACTUATORS

- THRUSTERS

- REACTION WHEELS

#### TDRSS CONTROL ELECTRONICS ASSEMBLY

TRW

CPE BLOCK DIAGRAM

TRW

TRW

CPE INSTRUCTION SET

- SPECIFIED BY CPE CONTROL FIRMWARE DESIGNERS TO BE OPTIMUM FOR TDRSS APPLICATION

- INSTRUCTION SET MICROPROGRAMMED BY HARDWARE DESIGNERS

- 108 TOTAL INSTRUCTIONS INCLUDING:

- SINGLE- OR MULTIPLE-BIT SET, RESET AND TEST

- 16-BIT FRACTIONAL FIXED-POINT ARITHMETIC

- 16-BIT ADD, SUBTRACT AND DIVIDE CLAMPED AT ±1.0 WHEN OVERFLOW OCCURS

- MULTI-BIT LOGICAL AND ARITHMETIC SHIFTS (SINGLE AND DOUBLE-PRECISION)

- FOURTEEN INPUT/OUTPUT INSTRUCTIONS DEDICATED TO PARTICULAR SENSORS OR ACTUATORS WITH ALL HARDWARE TIMING BEING TAKEN CARE OF IN THE MICROCODE. FOR EXAMPLE, INSS INSTRUCTION INPUTS ALL DATA ASSOCIATED WITH THE COARSE AND FINE SUN SENSORS TO PAGE O OF RAM; OUWTQ OUTPUTS TORQUE COMMANDS TO THE REACTION WHEELS FROM PAGE O OF RAM.

PROGRAM STRUCTURE

\*TELEMETRY BIT RATES OF 200, 1000, AND 4000 BITS/SECOND ARE SELECTABLE FOR THE 512 BIT MAIN FRAME. THESE PRODUCE TELEMETRY CYCLE TIMES OF 2.048, 0.512, AND 0.128 SECONDS RESPECTIVELY.

\*\* EXECUTION FREQUENCY (NOT EXECUTION TIME) FOR EACH PROGRAM MODULE.

FIRMWARE DEVELOPMENT/VERIFICATION PHILOSOPHIES

TRW

DESIGN SCOPE -

- MICROPROCESSOR DEDICATED TO ATTITUDE CONTROL FUNCTION

- INSTRUCTION SET TAILORED TO CONTROL NEEDS (ARITHMETIC LIMITING, CONTROL HARDWARE I/O)

DESIGN PERSONNEL

- FIRMWARE DESIGNED CODED, AND TESTED BY CONTROL SYSTEMS ENGINEERS

- IMPROVED COMMUNICATION FOR MECHANIZATION OF CONTROLS REQUIREMENTS IN FIRMWARE

- INTERACTION IMPROVED FOR ACHIEVING ADEQUATE PERFORMANCE IN THE FIRMWARE

INDEPENDENT VERIFICATION

- ACHIEVED BY SWAPPING MODULE RESPONSIBILITY AT VERIFICATION TIME

- VERIFICATION TEST PLAN INDEPENDENT OF MODULE DESIGNERS

- REVIEW OF TEST RESULTS BY CONTROL LOOP ANALYSTS

#### CONSTRAINTS AND THEIR EFFECTS ON FIRMWARE DESIGN

16 BIT WORD LENGTH MAXIMUM, 8-BIT BYTES

- CAREFUL MAGNITUDE SCALING FOR COMPUTATIONS

- QUANTIZATION EFFECTS ON CONTROL FILTER TOPOLOGIES

- LOW LEVEL PERFORMANCE/DYNAMIC RANGE TRADEOFFS

1024 8-BIT BYTES ADDRESSABLE IN RAM

- ATTITUDE CONTROL FILTER COMPLEXITY

- FILTER STATE ACCURACY/MULTIPLE PRECISION ARITHMETIC

DATA PROCESSING

- COMPUTATION COMPLEXITY/TIME DELAYS

- COMPUTATION COMPLEXITY/TASK SHARING

#### FILTER IMPLEMENTATION TOPOLOGIES

WORD LENGTH EFFECTS -

• ACCURACY, QUANTIZATION

FILTER TOPOLOGIES -

- POLYNOMIAL FORM (REJECTED)

- CASCADED FORM (ACCEPTED)

OTHER ALTERNATIVE FORMS

- PARALLEL FORM

- MATRIX FORM

- DFT, FFT

SCALING CONSIDERATIONS

- TOPOLOGY AND GAIN DISTRIBUTION FOR INTERMEDIATE STATES

- DYNAMIC RANGE, ETC.

#### FIRMWARE DEVELOPMENT & VERIFICATION TOOLS

- VARIAN V-73 MINICOMPUTER

- 8 AND 16 BIT ARITHMETIC

- FORTRAN FUNCTIONS SIMULATING INDIVIDUAL CPE INSTRUCTIONS

- PROVIDES INTERFACE IN ENGINEERING UNITS FOR MAXIMUM VISIBILITY

- INPUT SAME AS ASSEMBLER INPUT

- CYBER 74 TIMESHARE

- SCIENTIFIC SIMULATION OF ARITHMETIC INSTRUCTIONS

- PROVIDES TOOL FOR CONTROL LOOP DESIGNERS

- ASSESS LIMITED WORD LENGTH EFFECTS

- FILTER DESIGN

- RESIDENCE FOR CONTROLLED CPE SOURCE PROGRAM

- RESIDENCE FOR CPE ASSEMBLER PROGRAM

#### FIRMWARE DEVELOPMENT & VERIFICATION TOOLS (CONTINUED)

- TI 990/10 MINICOMPUTER

- VERIFICATION TOOL

- USED AS DRIVER FOR VERIFICATION TESTS

- DATA COLLECTION AND PRINTOUT

- PROVIDES DYNAMICS SIMULATION FOR DYNAMIC ENVIRONMENT

- CPE DEVELOPMENT STATION

- BREADBOARD CPE

- FRONT PANEL FOR PROGRAM ENTRY, EDIT, AND EXECUTION

- INTERFACE BOX

· . .

- HARDWARE LINK OF TI 990/10 AND BREADBOARD CPE

- GROUND STATION COMMAND SIMULATOR

**DEVELOPMENT STATION EQUI PMENT**

TRW DOFFINGE AND SPACE SYSTEM CADUP

TF 990/10 AND PROM PROGRAMMER

1 ...... 1208

IIII

#### REVIEWING THE FIRMWARE DESIGN

- INITIAL DESIGN

- COARSE PROGRAM FLOWS

- DETAILED PROGRAM FLOWS

- CODE CHECKOUT, MODULE LEVEL

#### DESIGN REVIEW AREAS -

- HARDWARE DESIGN

- MICROCODE DESIGN

- INSTRUCTION SET DESIGN

- GROUND STATION COMMANDS SET

- TOTAL INTEGRATED PROGRAM VERIFICATION

- SUBSYSTEM TESTING

- SPACECRAFT OPERATIONS DESIGN

- FLIGHT EXPERIENCE

- TELEMETRY DATA AVAILABLE

- PROGRAM STRUCTURE

- DESIGN PHILOSOPHIES

REVIEWING THE FIRMWARE DESIGN

SOME DESIGN IMPROVEMENTS UNCOVERED -

- RAM MEMORY LOAD AND MOVE DATA INSTRUCTION

- EXECUTIVE PROGRAM AND SUBROUTINES STRUCTURE

- GROUND COMMANDS TAILORED TO SPACECRAFT OPERATIONS

- MICROPROCESSOR DEVELOPMENT STATION SOFTWARE CHECKOUT FEATURES

- RAM

- SCRATCHPAD VISIBILITY

- RAPID MEMORY EXAMINE/CHANGE

- CONTROL FILTER STATES WORD LENGTH ≥ 24 BITS

- FLOATING POINT HARDWARE

- HIGH LEVEL LANGUAGE

# Page Intentionally Left Blank

#### A PLASMA WAVE FOURIER TRANSFORM PROCESSOR EMPLOYING 1802 MICROCOMPUTERS FOR SPACECRAFT INSTRUMENTATION

Donald C. Lokerson and James N. Caldwell Goddard Space Flight Center Greenbelt, Maryland

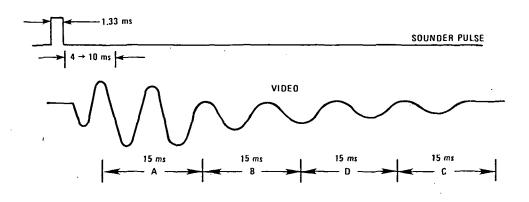

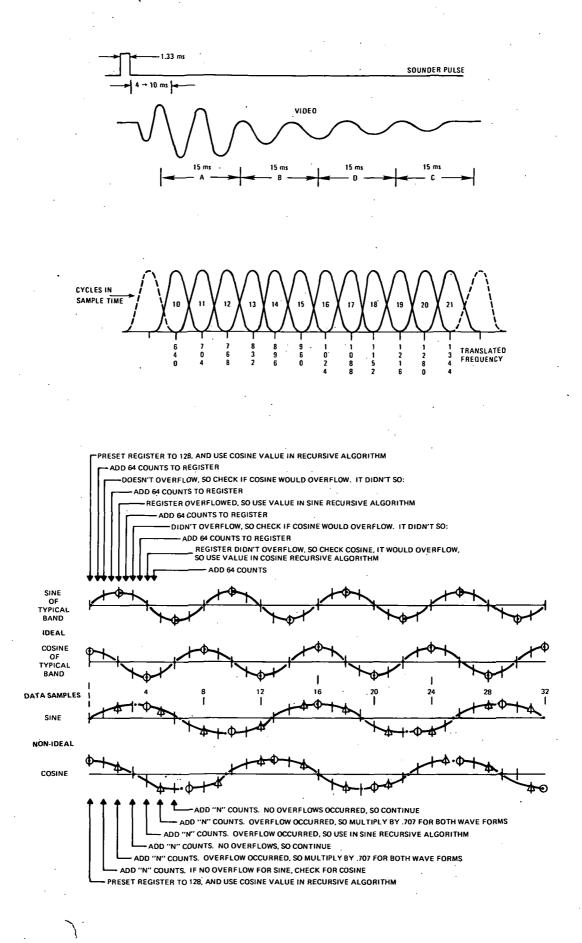

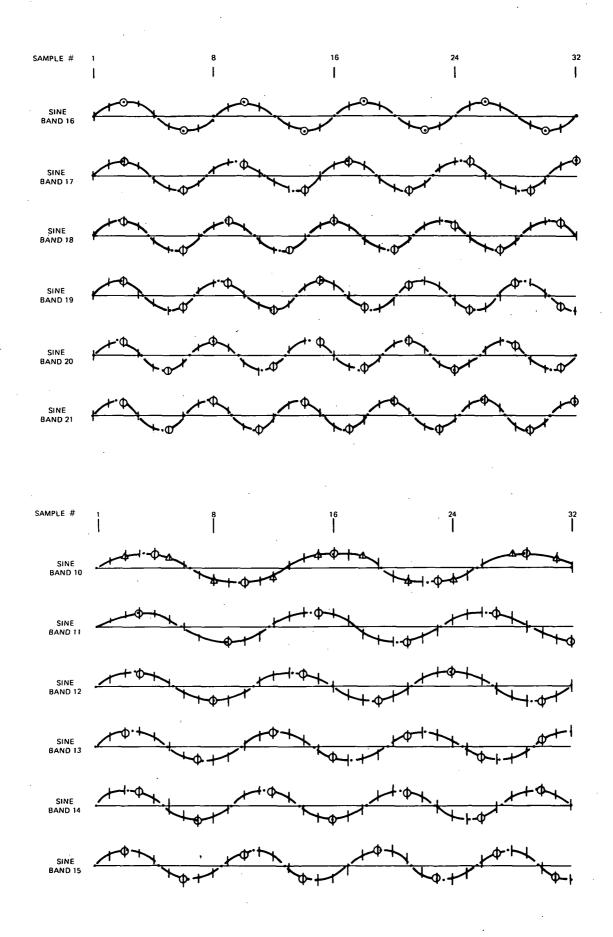

The requirements of low power, small space, low weight, and high data compression limit the capabilities of interplanetary plasma wave processing. The processing of plasma wave signals in spinning spacecraft in the range from D.C. to 500Hz are described. Another signal source from the intermediate frequency of a sounder transponder is processed by the same hardware, but with linear Fourier transform software.

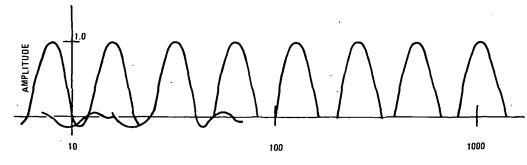

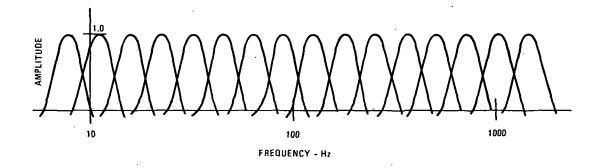

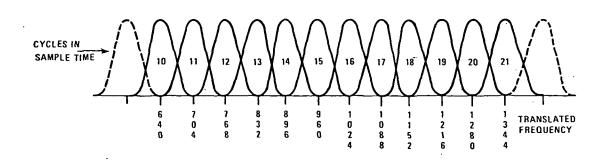

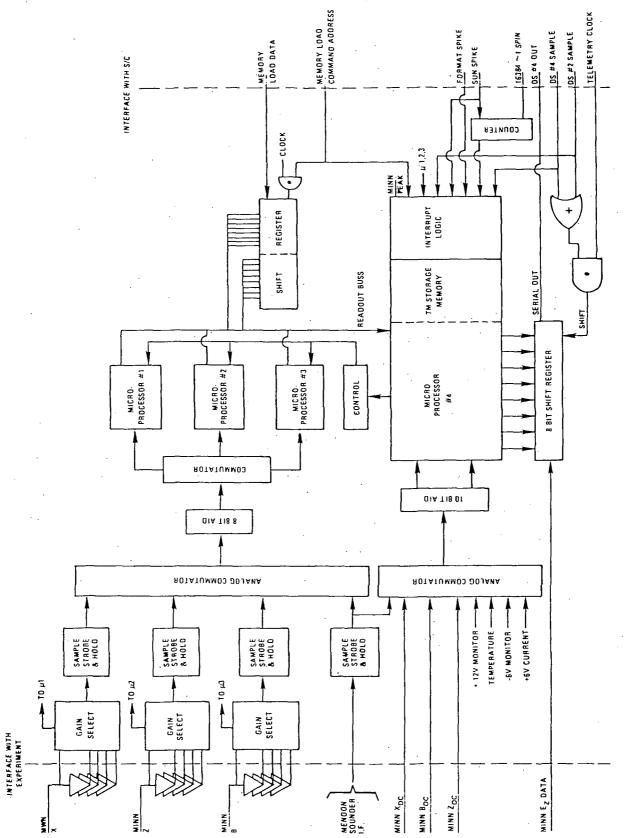

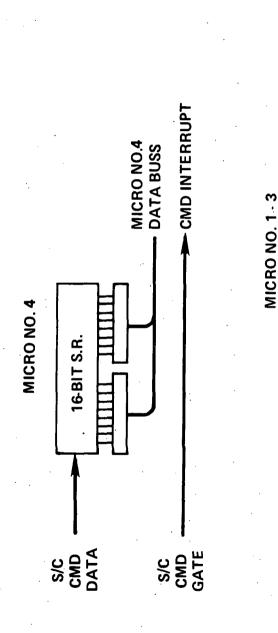

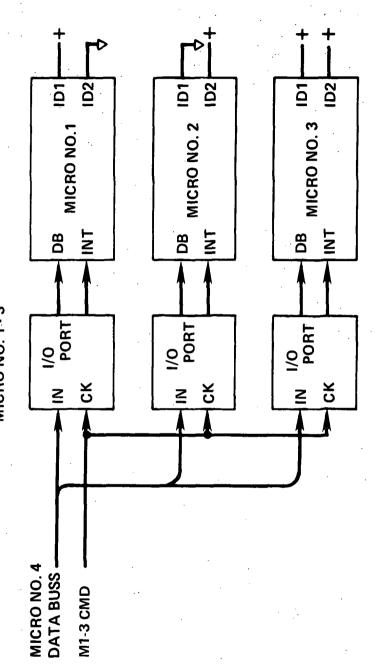

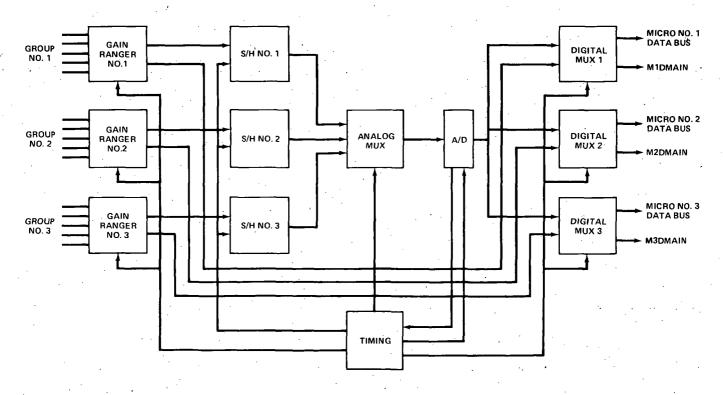

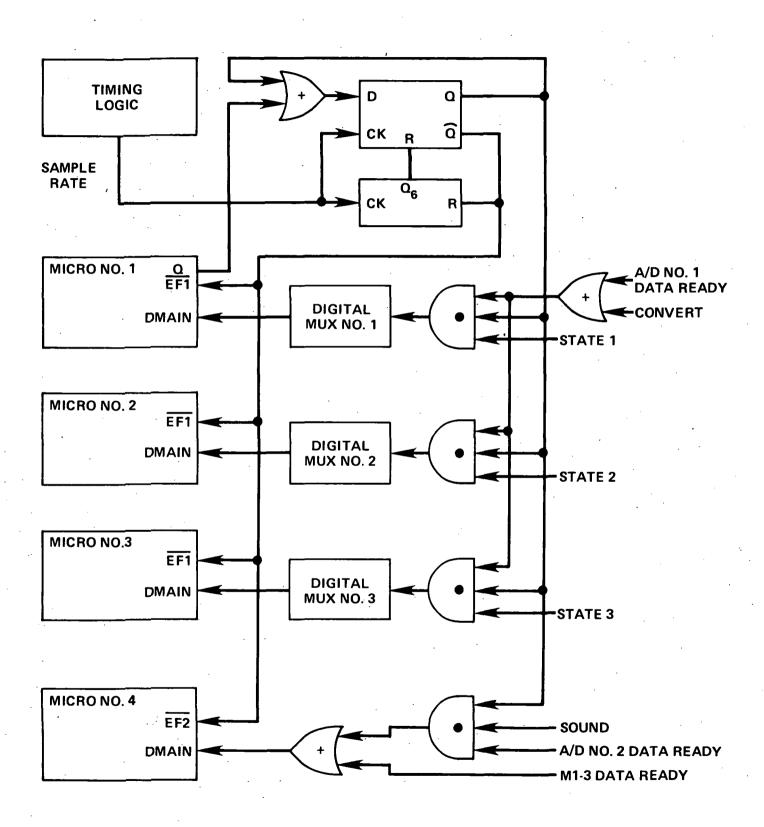

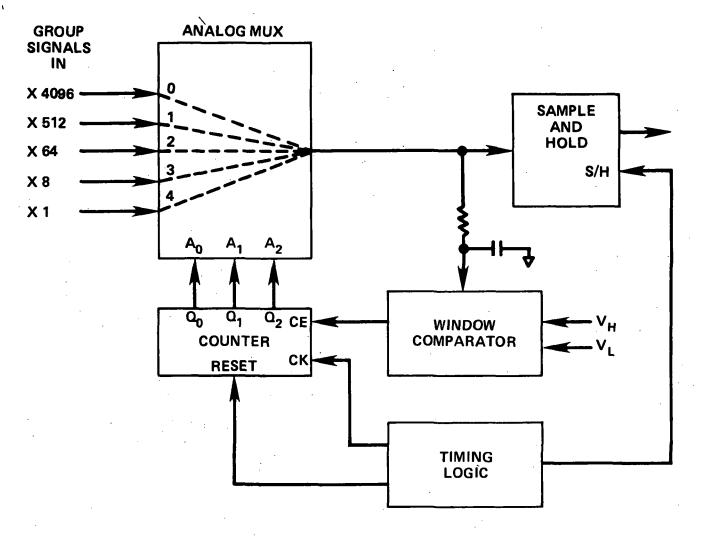

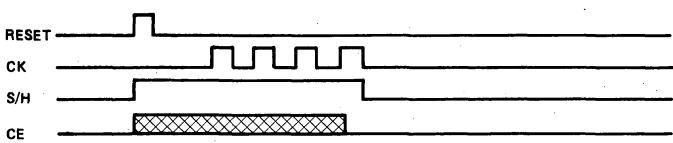

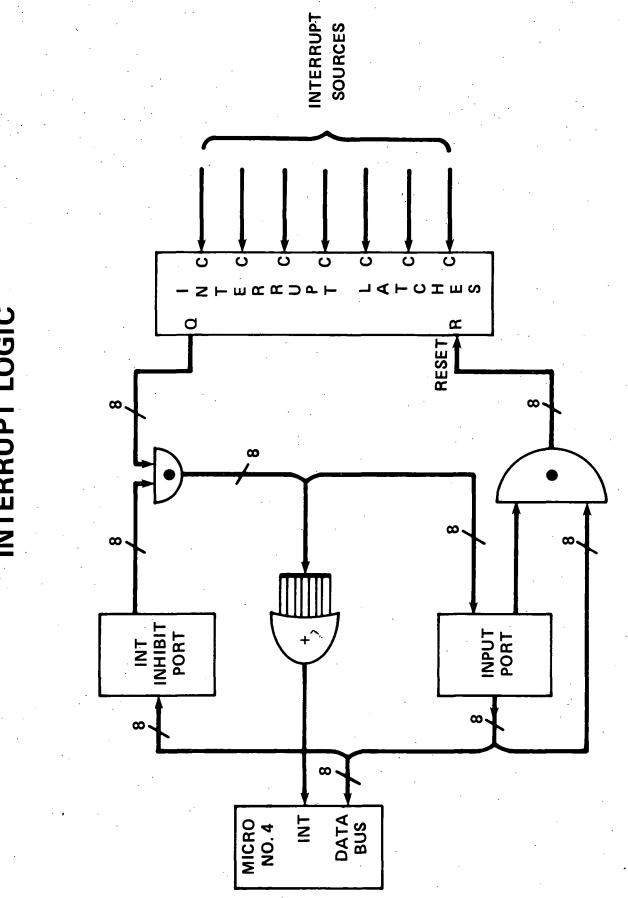

Three antenna inputs are filtered to prevent aliasing above 500Hz. A 92db range of data is multiplexed to an analog-to-digital converter, and then to three RCA 1802 microcomputers. Groups of this data are collected under DMA control by each microcomputer. A logarithmically-spaced Fourier transform is computed. Each computer requires 2 kilowords of read-only-memory and a half kiloword of random access memory.

Data at lower frequencies is spin modulated by the spacecraft. For these signals, data is sampled 512 times in one spin and also processed by logarithmically-spaced Fourier transform techniques. A fourth microcomputer performs this task and coordinates all operations. This microcomputer requires 5 kilowords of read-only-memory and 3.5 kilowords of random address memory. The computer also performs data averaging, peak detection, data formatting, output compression, and ground commanded tasks.

Functional block diagram of SPM-FFT Processor

# COMMANDS

M1-3 CMD

#### INPUT

#### STATE 0

- GAIN RANGE ALL INPUT GROUPS

- STROBE ALL SAMPLE AND HOLD AMPLIFIERS

# STATE 1

#### • A/D CONVERT S/H NO. 1

5

• DMA GAIN RANGE AND A/D DATA FOR GROUP NO. 1 TO MICRO NO. 1

#### STATE 2

- A/D CONVERT S/H NO. 2

- DMA GAIN RANGE AND A/D DATA FOR GROUP NO. 2 TO MICRO NO. 2

#### STATE 3

• A/D CONVERT S/H NO. 3

• DMA GAIN RANGE AND A/D DATA FOR GROUP NO. 3 TO MICRO NO. 3

# **DMA CONTROL**

# **GAIN RANGING**

INTERRUPT LOGIC

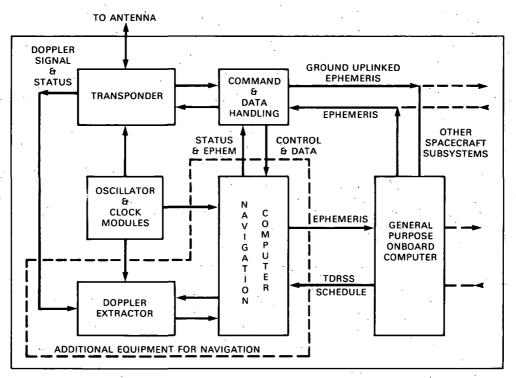

### PROTOTYPE DEVELOPMENT OF A MICROPROCESSOR-BASED ONBOARD ORBIT DETERMINATION SYSTEM

### Keiji K. Tasaki and Rose S. Pajerski Goddard Space Flight Center Greenbelt, Maryland

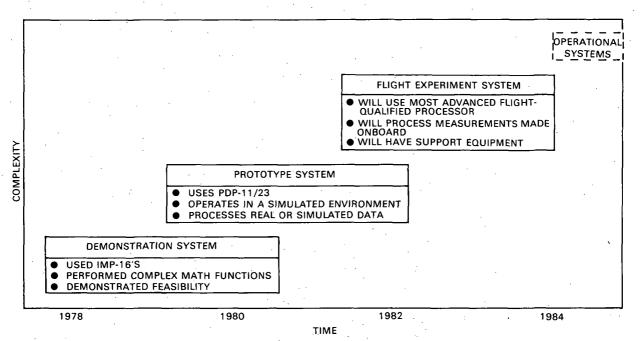

# DEVELOPMENT STAGES OF ONBOARD ORBIT DETERMINATION SYSTEMS

# **OBJECTIVES**

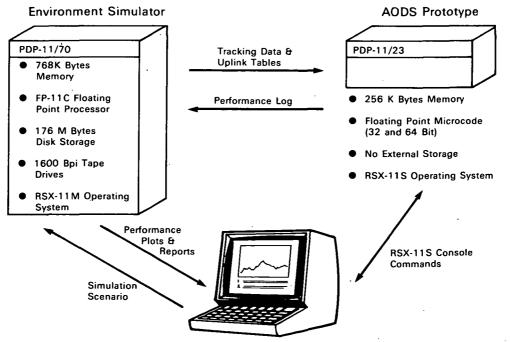

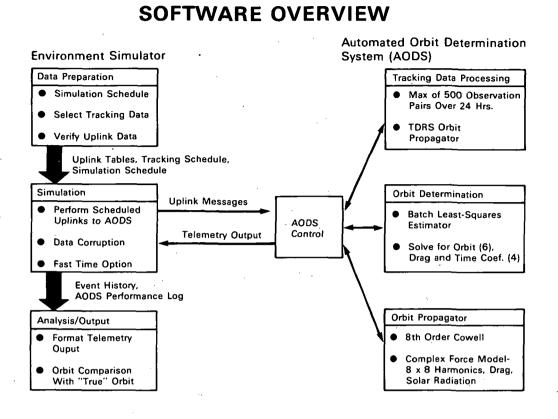

1. DEVELOP A MICROPROCESSOR-BASED AUTOMATED ORBIT DETERMINATION SYSTEM (AODS) USING:

- PDP-11/70 AS THE DEVELOPMENT MACHINE

- PDP-11/23 AS THE TARGET MACHINE

- HIGH-LEVEL LANGUAGE FORTRAN

- 2. EXERCISE THE SYSTEM IN CONJUNCTION WITH A SIMULATOR.

- 3. REFINE SOFTWARE TO ACHIEVE HIGHER EFFICIENCY.

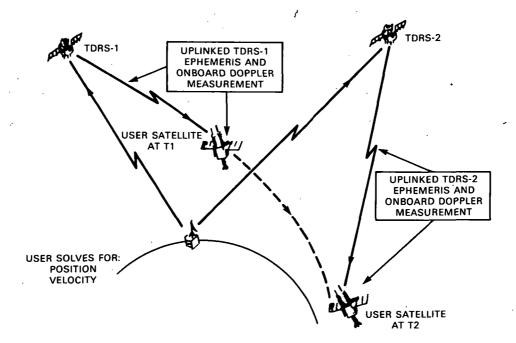

# **ONBOARD NAVIGATION WITH TDRSS**

### HARDWARE OVERVIEW

Programmer/Analyst

# **TYPICAL AODS SIMULATION SCENARIO**

| Propagate<br>Orbit                       |   |   |   |      | -    | - | 4 - |   | - | - | -  | .= | -      | _  |    | _  |

|------------------------------------------|---|---|---|------|------|---|-----|---|---|---|----|----|--------|----|----|----|

| Compute<br>Predicted<br>Doppler          |   |   |   |      | •    | • | •   | • | • | • |    |    | •      | •  | •  | •  |

| Output AODS<br>Status<br>Log             |   |   |   |      |      |   |     |   |   |   |    |    |        |    |    |    |

| Output<br>Performance<br>Reports         |   |   |   |      |      |   |     |   | • |   |    |    |        | •  | •  | •  |

| Determine<br>Orbit                       |   |   |   |      |      |   |     |   |   |   | _  | _  | -      | -  |    |    |

| Process<br>Tracking<br>Data              |   |   | • | <br> | <br> |   | •   | • | • | • | •  | •  | •<br>• | •  | •  | •  |

| Process AODS<br>Initialization<br>Parms. |   | - |   | -    |      |   |     |   |   |   |    |    |        | •  |    |    |

| Load code<br>into11/23                   | - | - |   |      |      |   |     | _ |   |   |    |    |        |    |    | ·  |

| ime from Start<br>1 rev=90 minut         |   | 1 | 2 | 3    | 4    | 5 | 6   | 7 | 8 | 9 | 10 | 11 | 12     | 13 | 14 | 15 |

# **FLIGHT EXPERIMENT CONFIGURATION**

# FLIGHT EXPERIMENT CONSIDERATIONS

1. SELECTION OF A FLIGHT-QUALIFIED PROCESSOR

- 64-BIT FLOATING POINT ARITHMETIC

- LARGE ADDRESSABLE MEMORY (BEYOND 64K)

- MULTITASKING OPERATING SYSTEM

- 2. HARDWARE INTERFACE

- RECEIVER AODS COMMAND AND DATA MODULE

- AODS OTHER ONBOARD PROCESSORS

### SESSION II

### GROUND BASED AEROSPACE MICROPROCESSOR APPLICATIONS

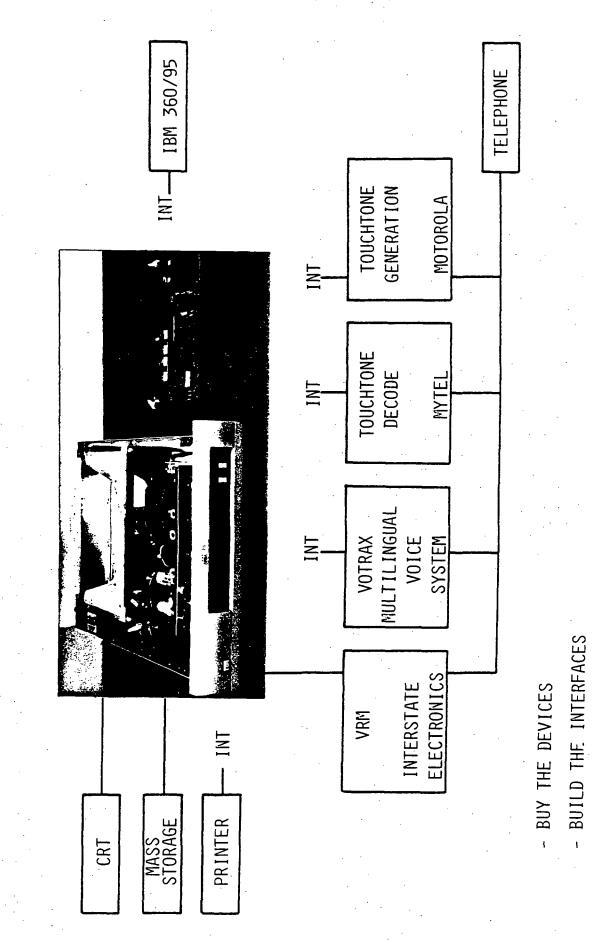

### THE REMOTE COMPUTER CONTROL (RCC) SYSTEM

### William Holmes Goddard Space Flight Center Greenbelt, Maryland

system to remotely control job flow on a host Α computer from any touchtone telephone is currently being developed at Goddard Space Flight Center (GSFC). Using this system a computer programmer can submit jobs to a host computer from any touchtone telephone. In addition the system can be instructed by the user to call back when a job finished. Because of this system every touchtone is telephone becomes a conversant computer peripheral. This system known as the Remote Computer Control (RCC) system utilizes touchtone input, touchtone output, voice input, and The RCC system is microprocessor based and is voice output. currently using the INTEL 80/30 microcomputer. Using the RCC system a user can submit, cancel, and check the status of jobs on a host computer. A user can also have the RCC system call when a specified condition is fulfilled. For example, a user could have the RCC call when a specific job has been successfully completed on a host computer.

The peripherals used for communication with the user over the telephone are the MH88205 DTMF Receiver/Decoder by Mitel for touchtone input, the MC14410P integrated circuit Motorola for touchtone output, the Voice Recognition by Module (VRM) by Interstate Electronics for voice input and the ML-I Multi-Lingual Voice System by Federal Screw Works for voice output. The RCC system peripherals consist of a operator control, a printer CRT for for logging all activity, mass storage for the storage of user parameters, and a PROM card for program storage.

This RCC system enables a user to communicate with a host computer and control job flow on a host computer from any touchtone telephone at any time. The use of this system can decrease turnaround time on a host computer by time between job minimizing the termination and user notification of job termination. This system can help distribute the work load of a host computer to off hours by enabling a user to control the host computer job flow from any remote touchtone telephone.

**Remote Computer Control**

- CONTROL JOB FLOW

- HAVE HOST COMPUTER GENERATE TELEPHONE CALLS UPON REQUEST

**Pilot System**

71

PROGRAM THE MICROPROCESSOR

SYSTEM COMMANDS / DEMONSTRATION

- ID'S ID'S CORRELATED WITH VALID HOST COMPUTER NUMERIC LOGON 1

- PRE-STORED ON DISK IN HOST MACHINE J03S SUBMIT I

- STATUS BY NUMERIC JOB ID

- CANCEL BY NUMERIC JOB ID

- NOTIFY TO ANY TELEPHONE NUMBER

- NOISSES ELVNIMENT. -

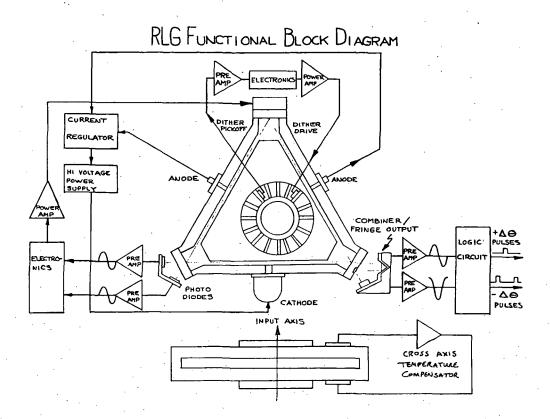

#### A MICROPROCESSOR APPLICATION TO A STRAPDOWN LASER GYRO NAVIGATOR

C. Giardina and E. Luxford The Singer Company-Kearfott Division Little Falls, New Jersey

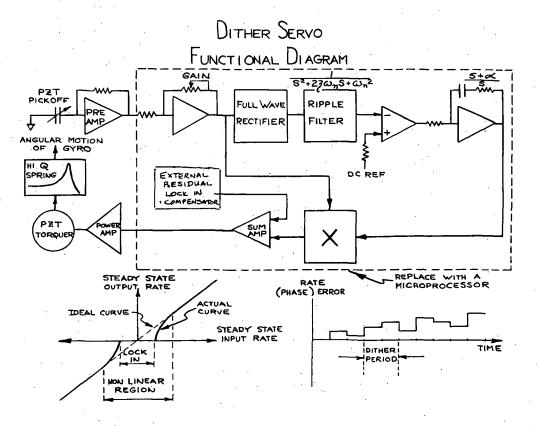

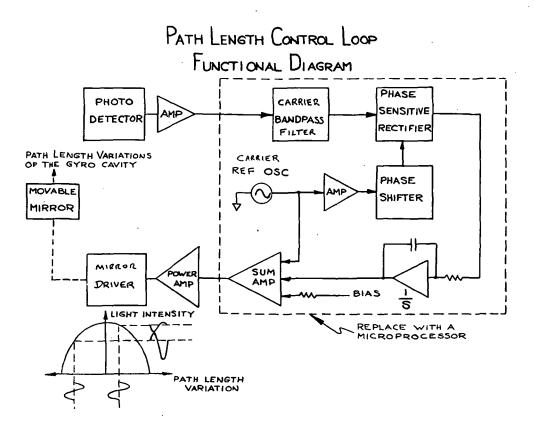

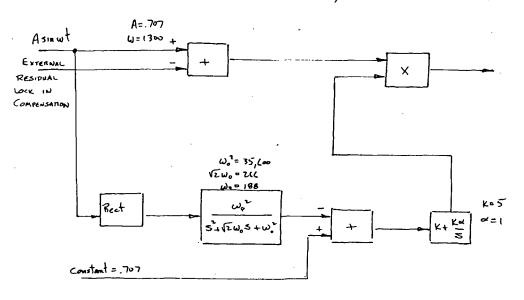

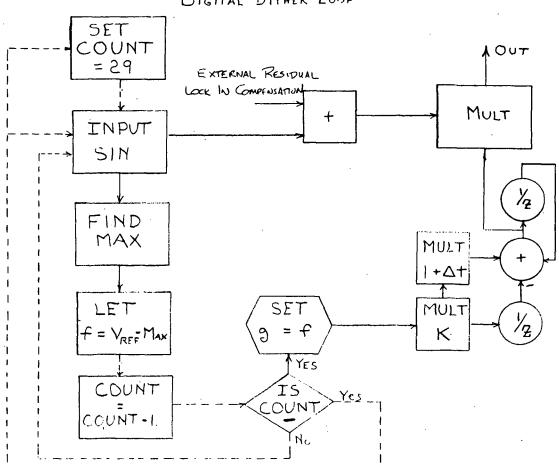

This paper is concerned with replacing analog circuit control loops for laser gyros (path length control, cross axis temperature compensation loops, dither servo and current regulators), with digital filters residing in microcomputers. The object of using this type of design is to improve on system reliability (through part count reduction), reduce size and power requirements, and therefore, improve on system performance. Consistent replication in the design is a further benefit derived by replacing analog components with digital software.

In addition to the control loops, a discussion will be given on applying the microprocessor hardware to compensation for coning and skulling motion where simple algorithms are processed at high speeds to compensate component output data (digital pulses) for linear and angular vibration motions.

Highlights are given on the methodology and system approaches used in replacing differential equations describing the analog system in terms of the mechanized difference equations of the microprocessor. Here standard one for one frequency domain techniques are employed in replacing analog transfer functions by their transform counterparts. Direct digital design techniques are also discussed along with their associated benefits. Time and memory loading analyses are also summarized, as well as signal and microprocessor architecture utilized to do the "best job".

Trade offs in algorithm, mechanization, time/memory loading, accuracy and microprocessor architecture are also given.

| RLG | CONTROL | LOOPS | - | PERFORMANCE | INFORMATION |

|-----|---------|-------|---|-------------|-------------|

|     |         |       |   |             |             |

| Loop                                      | Purpose of Loop                                                                                                                             | Method of Improving Performance                                                                                                | Required Control<br>Loop Bandwidth                |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Dither                                    | Eliminate damping in<br>dither spring mecha-<br>nism                                                                                        | Overcome backscattered light between<br>two beams due to mirror (reflector)<br>imperfections and thereby circumvent<br>lock-in | Moderate when compared<br>to microcomputer speeds |

| Current<br>Regulator                      | Balance anode currents                                                                                                                      | Minimize drift due to gas flow in laser cavity                                                                                 | Long when compared to microcomputer speeds        |

| Path Length<br>Control                    | Maintain path length<br>in cavity at an in-<br>tegral number of<br>wave lengths                                                             | Minimize drift due to temperature<br>variation of block                                                                        | Long when compared to<br>microcomputer speeds     |

| Cross Axis<br>Temperature<br>Compensator  | Center beam in cavity                                                                                                                       | Minimize drift due to temperature variation of block                                                                           | Long when compared to microcomputer speeds        |

| Variable<br>Beam Inten-<br>sity Corrector | Locate mirrors to<br>minimize total back-<br>scatter "vector" from<br>the three mirrors<br>(thereby reducing<br>effective lock-in<br>level) | Minimize output random noise<br>resulting from dither                                                                          | Long when compared to<br>microcomputer speeds     |

RLG CONTROL LOOPS - OBSERVABLES AND METHOD OF CONTROL COMPARISON

|                                           |                                                                                                                                                                                   |                                                                                                   | Method of Obser                                                                        | ving Signal                                                                                                                                                                                  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Loop                                      | Observed Signal                                                                                                                                                                   | Control Signal                                                                                    | Analog                                                                                 | Digital                                                                                                                                                                                      |

| Dither                                    | Dither Amplitude                                                                                                                                                                  | Force applied to gyro<br>dither spring through<br>voltage applied to PZT<br>device                | Full wave recti-<br>fied dither ampli-<br>tude                                         | Measurement of<br>peak dither ampli-<br>tude through succes-<br>sive measurement of<br>amplitude                                                                                             |

| Current<br>Regulator                      | Difference in anode<br>currents                                                                                                                                                   | Base voltage applied<br>to control transistor                                                     | Output voltage<br>from difference<br>amplifier repre-<br>senting difference<br>current | Same as analog                                                                                                                                                                               |

| Path Length<br>Control                    | Beam Intensity                                                                                                                                                                    | Force applied to<br>movable mirror<br>through voltage<br>applied to P2T device                    | Rectification of a<br>carrier signal mod-<br>ulating beam inten-<br>sity               | Measurement of beam<br>intensity variation<br>with path length<br>variation through<br>successive iterations<br>of path length                                                               |

| Cross Axis<br>Temperature<br>Compensator  | Beam Intensity                                                                                                                                                                    | Force applied to gyro<br>block through voltage<br>applied to P2T device                           | Rectification of a<br>carrier signal mod-<br>ulating beam inten-<br>sity               | Measurement of beam<br>intensity variation<br>with force applied to<br>the block through suc-<br>cessive iterations of<br>that applied force                                                 |

| Variable<br>Beam<br>Itensity<br>Corrector | Variation in beam<br>intensity (distor-<br>tion) as gyro period-<br>ically locks in during<br>dither reversals.<br>Variation usually<br>occurs only with a<br>given gyro turn-on. | Force applied to a<br>set of two movable<br>mirrors through<br>voltages applied to<br>PZT devices | Rectification of a<br>carrier signal mod-<br>ulating "winking"<br>amplitude            | Measurement of "wink-<br>ing" signal through<br>successive iterations<br>of position of two<br>movable mirrors. The<br>signal amplitude will<br>be determined through<br>direct integration. |

Dither Cortrol Losp ( 4 processor section )

### DIGITAL DITHER LOOP

#### REDUCTION IN SYSTEM COMPLEXITY AND COST SAVINGS

|                                                                                    | Analog                | Microprocessor (Digital) |

|------------------------------------------------------------------------------------|-----------------------|--------------------------|

| Electronics Circuit Board Area<br>Required for this Function                       | * 250 in <sup>2</sup> | 50 in <sup>2</sup>       |

| Number of parts                                                                    | 1400 discrete parts   | 10 chips                 |

| Cost                                                                               | \$4000                | \$1000                   |

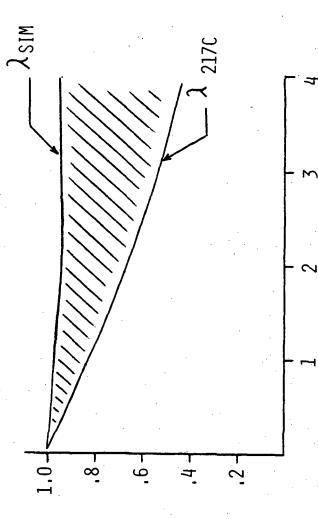

| Reliability<br>(Predicted)<br>failure rate λ ≈<br>failures per 10 <sup>6</sup> hrs | 200                   | 30                       |

With hybridization approximately same board area could be achieved but cost factor then becomes about 8:1.

|                                                  | COMMENTS                             | 28 PIN DIP<br>NO INTERRUPTS<br>NO JUMPS<br>192 INSTRUCTIONS/<br>PROGRAM MAX | 40 PIN DJP<br>2 INTERRUPTS<br>JUMPS ETC                  | 40 PIN DIP<br>2 LEVEL INTERRUPTS<br>JUMPS ETC   | 40 PIN DIP<br>2 LEVEL INTERNUPTS<br>JUMPS ETC                          |                   | 9-65 INTERRUPT<br>Levels               |

|--------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------|-------------------|----------------------------------------|

|                                                  | 1/0<br>INTERFACE                     | 4 INPUT<br>CHANNELS<br>8 OUTIUT<br>CHANNELS<br>CHANNELS                     | 2 INPUT<br>CHANNELS                                      | 4 I/O<br>PORTS                                  | TIU 8                                                                  |                   | 24 LINES                               |

|                                                  | MULTIPLY<br>TIME                     | MUST BE<br>DONE IN<br>SOFTWARE<br>344SEC                                    | MUST BE<br>Done IN<br>Software<br>90 USEC                | 4 USEC<br>MULT 6<br>DIV                         | NO<br>MUST BE<br>DOUBLE<br>PRECISION<br>AT LEAST                       | 12 USEC           | 12 USEC                                |

|                                                  | LOAD<br>STORE<br>ADDITION<br>TIME    | ALL<br>INSTRUC-<br>TIONS<br>4007SEC                                         | ALL IN-<br>STRUC-<br>TIONS<br>8.5 USEC<br>OR<br>17 USEC  | ALL<br>INSTRUC-<br>TIONS<br>1 USEC OF<br>2 USEC | ALMOST<br>ALL 53<br>ALL 53<br>INSTRUC-<br>TIONS<br>4.5 USEC<br>(4 BIT) | 1-2 USEC          | 16-32K OF 1-2 USEC<br>16 BIT<br>WORDS  |

| MENTATION                                        | PERHANENT<br>MEMORY                  | EPROM<br>24 BIT<br>INSTRUC-<br>TION WORD<br>BY 192<br>WOLDO                 | ROM<br>H bit<br>ADDRESS<br>WORD<br>2K WORDS              | EPROM<br>8 BIT<br>WORD<br>4K WORDS              | ROM<br>8 BIT<br>ADDRESS<br>WORD<br>4 K                                 | 16 BIT<br>WORDS   | 16-32K OF<br>16 BIT<br>WORDS           |

| FOR LOOP IMPLE                                   | PAD MEMORY                           | RAM<br>25 BIT DATA<br>VORD BY 40<br>WORDS                                   | RAM<br>8 NLT UATA<br>WORD<br>64 WORDS                    | RAM<br>B BIT DATA<br>WORD<br>128 WORDS          | RAM<br>4 BIT DATA<br>WORD<br>128 WORDS<br>16 BIT WORDS                 | 16 BIT WORDS      | 32-64 K OF<br>B BIT WORDS              |

| DEVICES BEING CONSIDERED FOR LOOP IMPLEMENTATION | OTHER EQUIPMENT<br>REQUIRED          | -sv power supply                                                            | +5V POWER SUPPLY<br>•D/A - SAMPLE &<br>HOLD<br>ETC.      | +5V POWER SUPPLY<br>A/D & D/A<br>ETC            | +5V POWER SUPPLY                                                       | A/D-D/A<br>BOARD  | +5V POWER SUPPLY<br>A,G-D/A<br>BCARD   |

| DEVICES                                          | D/A ON CHIP<br>SAMPLE & HOLD<br>ETC. | YES 9 BIT D/A<br>Analog 6<br>Digital output                                 | 02                                                       | Q                                               | YES 8 BIT D/A<br>ANALOG 6<br>DIGITAL OUTPUT                            | ·                 | 01                                     |

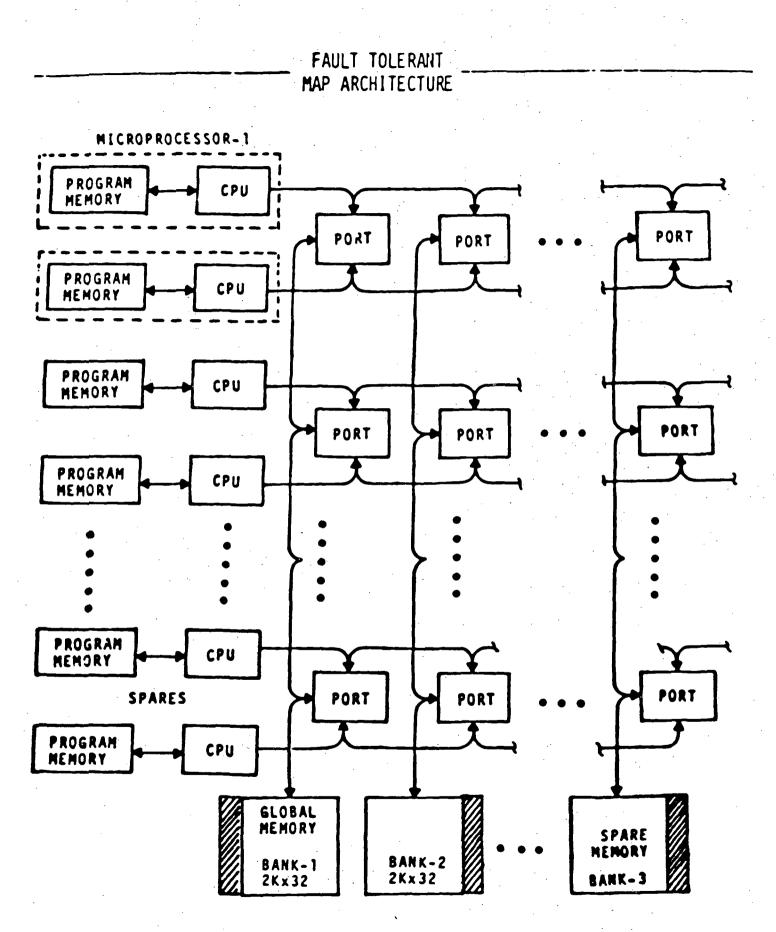

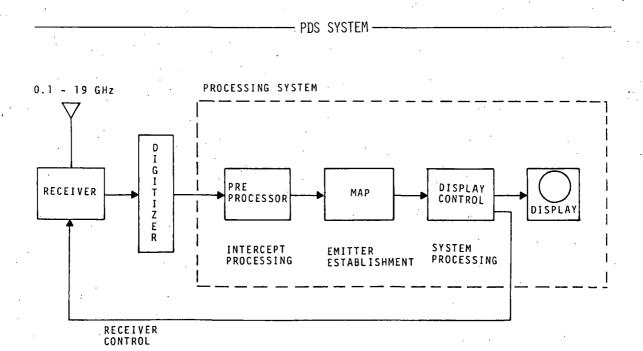

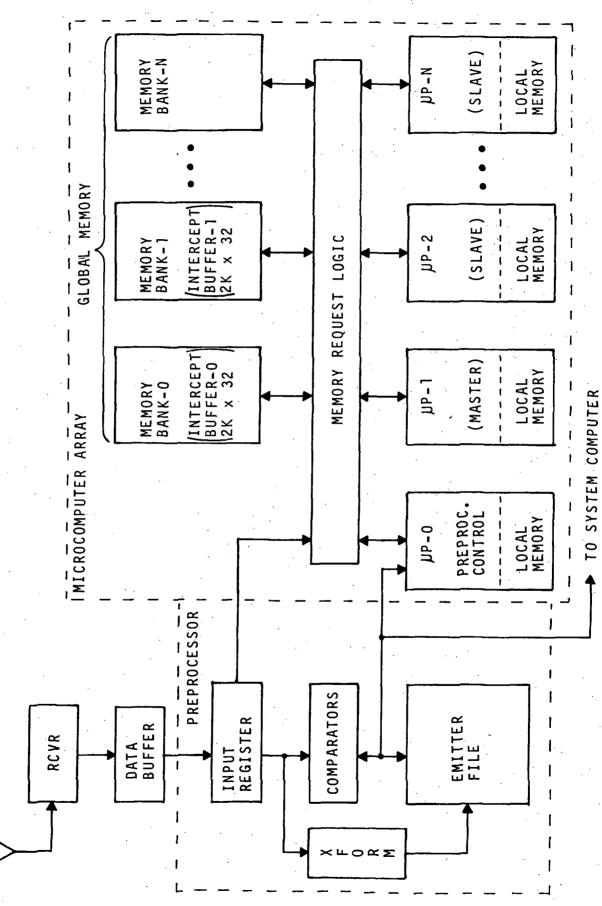

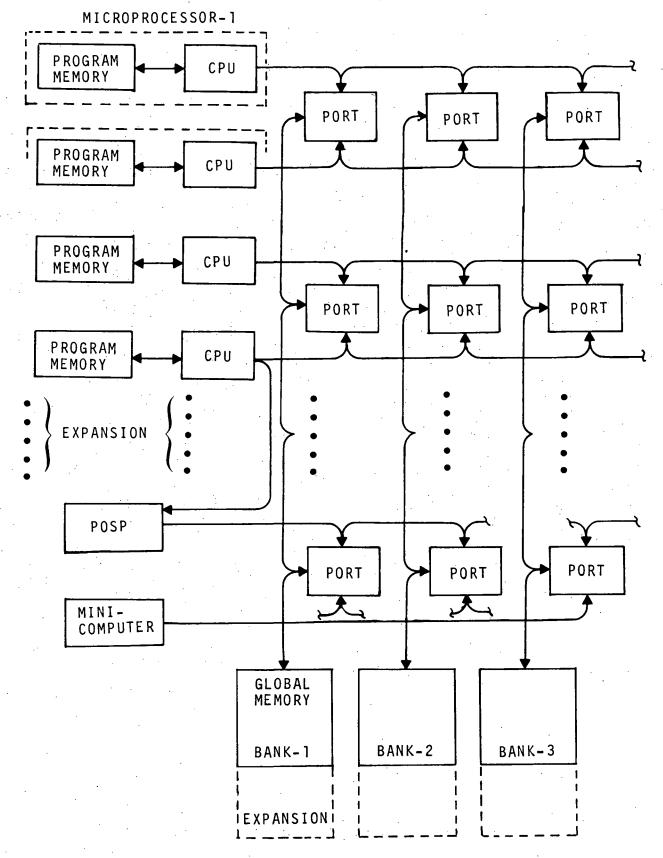

|                                                  | A/D ON CHIP                          | YES 9 BITS A/D<br>ANALOG INPUT<br>ONLY                                      | YES 8 BIT A/D<br>ANALOG OH<br>DIGITALI INPUTS<br>ALLOWED | 01.                                             | YES 8 BIT A/D<br>ANALOC &<br>DIGITAL INPUT                             | Q                 | Ov                                     |