# AN IMAGING INFRARED (IIR) SEEKER USING A MICROPROGRAMMED PROCESSOR

Kerry V. Richmond

McDonnell Douglas Astronautics Co.

St. Louis, Missouri

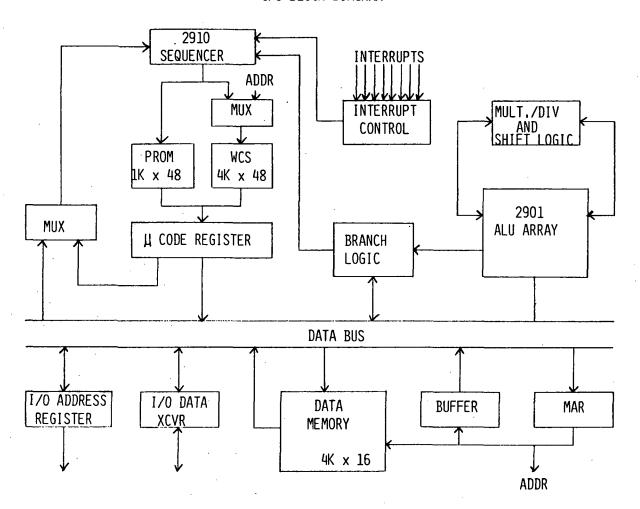

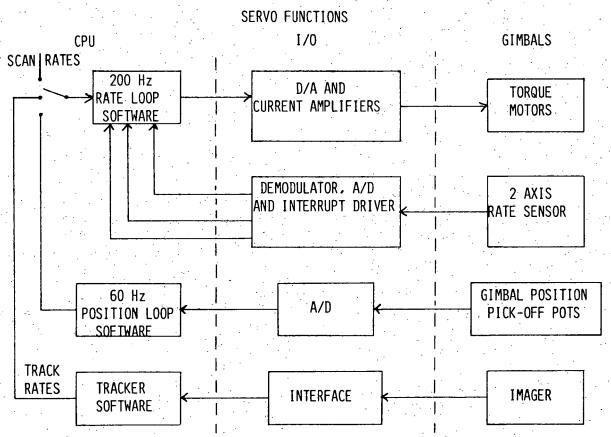

A recently developed IIR seeker uses a microprogrammed processor to perform gimbal servo control and system interface via a MIL-STD 1553 port while performing the seeker functions of automatic target detection, acquisition and tracking. Although the acquisition and centroid tracking are relatively low computation load seeker modes, the automatic detection mode requires up to 80% of the available capability of a high performance 2900 based microprogrammed processor. With the high speed processing capability available it is possible to implement a digital servo in the same processor using only 5% of the computation capacity. This digital servo includes six modes of gimbal control at the basic processor 60 Hz computation loop plus a 200 Hz rate loop, the latter being transparent to the main seeker functions. These two asynchronous timing loops plus a 50 Hz system interface loop driven from the 1553 port are implemented in the one processor. The fast response required by the rate loop for the rate sensor demodulator inputs also requires an interrupt driven analog data acquisition system. A 4K microcode program driven by eight interrupts implements these functions as well as the other operator and system interfaces.

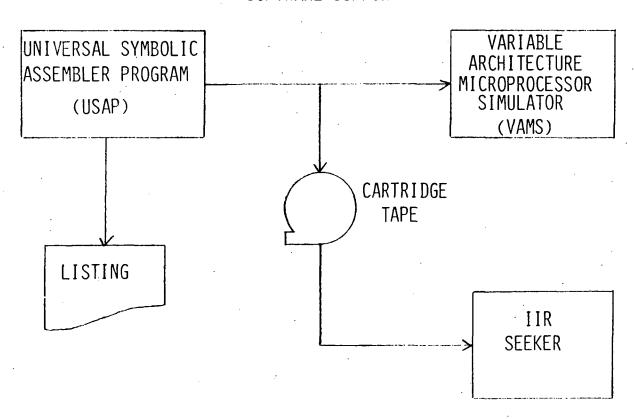

The eighth interrupt is used to force the processor into special "front panel" code which suspends all other interrupt processing and saves the state of the processor to allow the programmer to view the contents of all registers and memory as well as enter new values and resume normal processor execution at the interrupted location or any other selected location. This programmer debug aid in the hardware coupled with a set of support software including a symbolic cross assembler and a software simulation of the 2900 based processor allow efficient program development and checkout.

This system developed around the microcoded processor required by one of the system tasks has been designed, checked out and flown successfully. Although system complexity was increased significantly by adding the additional functions this approach can be cost effective when the basic computation capacity is already available.

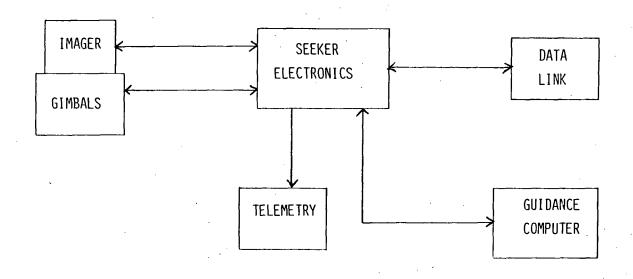

#### IIR SEEKER MISSILE INTERFACES

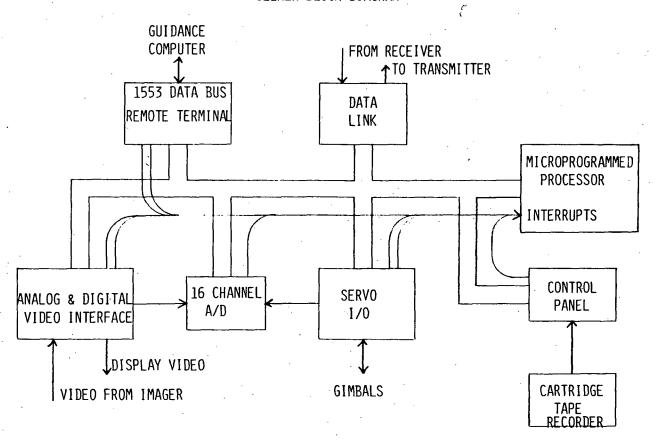

#### SEEKER BLOCK DIAGRAM

#### CPU BLOCK DIAGRAM

MICROCODE WORD

| 24      | 23 | 22_ | 21 | 20        | 19 | 18 | 17 | 16  | 15         | 14 | 13    | 12 | 11                  | 10 | 9 | 8           | 7  | 6 | 5          | - 4 | 3  | 2 | ı |

|---------|----|-----|----|-----------|----|----|----|-----|------------|----|-------|----|---------------------|----|---|-------------|----|---|------------|-----|----|---|---|

| Strobes |    |     | A  | B<br>ddre | SS |    |    | Add | A<br>ires: | 5  | Shift |    | ALU<br>Des <b>t</b> | •  |   | ALU<br>Fund | :. |   | ALU<br>our | ce  | C1 | n |   |

| 48    | 47 | 46 | 45 | 44 | 43        | 42 | 41 | 40 | 39   | 38   | 37   | 36 | 35 | 34          | 33     | 32 | 31 | 30 | 29 | 28 | 27 | 26 | 25 |

|-------|----|----|----|----|-----------|----|----|----|------|------|------|----|----|-------------|--------|----|----|----|----|----|----|----|----|

| Spare |    |    | ol |    | Sequencer |    |    | Bi | ranc | h Co | ond. | In |    | inst<br>ATA | . FIEL | .D |    |    |    |    |    |    |    |

### CPU PERFORMANCE/REQUIREMENTS

- o 2900 BIT SLICE MICROPROGRAMMED PROCESSOR

- o 48 BIT WIDE MICROCODE WORD

- o 267 NANOSECOND CYCLE TIME

- o 4K PROGRAM MEMORY

- o 2K SCRATCH PAD MEMORY

- o 8 INTERRUPTS

### SEEKER INTERRUPTS

## SYSTEM INTERRUPTS

- o CONTROL PANEL

- o A/D COMPLETION

## 60 Hz MAIN LOOP

- o END OF GATE

- o END OF FIELD

# 200 Hz SERVO RATE LOOP

- o SAMPLE AZIMUTH DEMODULATOR

- o SAMPLE ELEVATION DEMODULATOR

## 50 Hz GUIDANCE COMPUTER TIMING LOOP

- o 1553 INPUT DATA READY

- o 1553 OUTPUT DATA READY

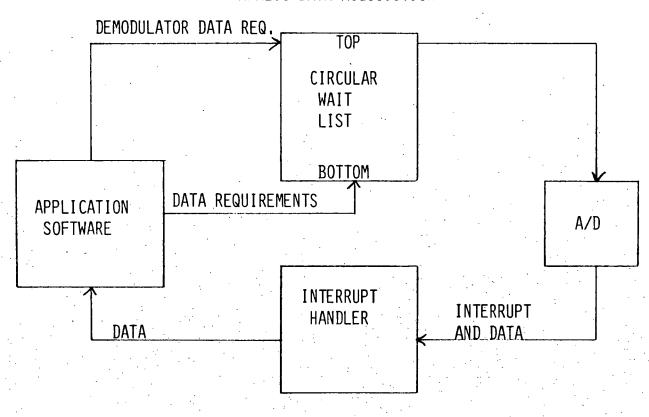

#### ANALOG DATA ACQUISITION

#### FRONT PANEL FUNCTIONS

- o READ/LOAD DATA MEMORY

- o READ/LOAD REGISTERS

CPU

I/O ADDRESS

MEMORY ADDRESS

CONDITION CODE

- o READ/LOAD INTERRUPT STATUS

- o EXIT/RETURN TO PROGRAM

# SOFTWARE SUPPORT