#### AN EXPERIMENTAL DISTRIBUTED MICROPROCESSOR IMPLEMENTATION WITH A SHARED MEMORY COMMUNICATIONS AND CONTROL MEDIUM

#### Richard S. Mejzak Naval Air Development Center Warminster, Pennsylvania

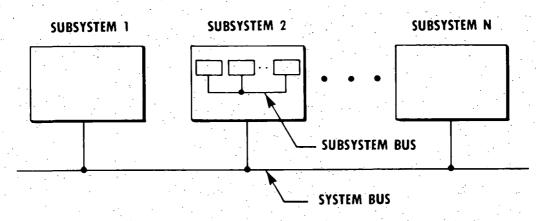

An experimental distributed microprocessor subsystem is currently under development at the Naval Air Development Center as a vehicle to investigate distributed processing concepts with respect to replacing larger computers with networks of microprocessors at the subsystem or node level. Major benefits being exploited include increased performance, flexibility, system availability, and survivability by use of multiple processing elements with reduced cost, size, weight and power consumption.

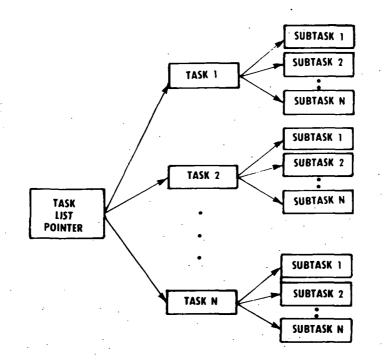

This paper concentrates on defining the distributed processing concept in terms of control primitives, variables, and structures and their use in performing a decomposed DFT (Discrete Fourier Transform) application function. The DFT was chosen as an experimental application to investigate distributed processing concepts because of its highly regular and decomposable structure for concurrent execution. The design assumes interprocessor communications to be anonymous. In this scheme, all processors can access an entire common database by employing control primitives. Access to selected areas within the common database is random, enforced by a hardware lock, and determined by task and subtask pointers. This enables the number of processors to be varied in the configuration without any modifications to the control structure. Decompositional elements of the DFT application function in terms of tasks and subtasks are also described.

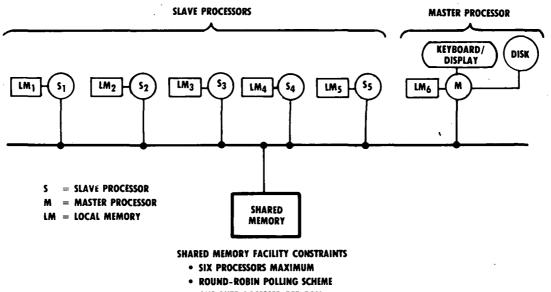

The experimental hardware configuration consists of IMSAI 8080 chassis which are independent, 8-bit microcomputer units. These chassis are linked together to form a multiple processing system by means of a shared memory facility. This facility consists of hardware which provides a bus structure to enable up to six microcomputers to be interconnected. It provides polling and arbitration logic so that only one processor has access to shared memory at any one time. For discussion purposes, five of the processors are designated as slaves and one as a master where each slave contains an identical copy of a control executive and application program tasks. In actual operation, the slave processors cooperate to compute the DFT where the master provides external input, output, and control functions. With this implementation, commands to perform a DFT iteration are provided through the master.

It is expected that this concept will be tested and demonstrated on a laboratory model by the end of 1980. Evaluations will concentrate on areas such as performance comparisons based on varying the number of processors and bus contention factors as a function of local processing and common data base access times. Future work will focus on fault tolerant techniques that can be directly implemented and evaluated on the baseline laboratory model.

# MOTIVATION

AVIONIC PROCESSING SYSTEMS ARE BECOMING MORE DISTRIBUTED IN ORDER TO EXPLOIT THE FOLLOWING MAJOR BENEFITS:

- INCREASED SYSTEM-WIDE REAL TIME PERFORMANCE

- EASE OF ADAPTABILITY TO INTEGRATION AND CHANGE

- HIGH SYSTEM AVAILABILITY

- DECREASED SYSTEM VULNERABILITY

- BECAUSE OF REDUCED SIZE, WEIGHT, POWER CONSUMPTION AND COST ADVANTAGES, MICROPROCESSOR TECHNOLOGY WILL IMPACT AVIONIC PROCESSING SYSTEMS IN THE FOLLOWING AREAS:

- INTERFACE AND HARDWIRED LOGIC REPLACEMENT APPLICATIONS

►

REPLACING LARGER COMPUTERS WITH NETWORKS OF SMALLER COMPUTERS

# MICROPROCESSOR TECHNOLOGY AND DISTRIBUTED PROCESSING

- REASONABLE COST-PERMITS EXPERIMENTING WITH CONCEPTS WHICH WOULD OTHERWISE BE PAPER STUDIES

- REDUCED SIZE, POWER, AND WEIGHT PERMITS APPLICATIONS THAT WOULD OTHERWISE NOT BE FEASIBLE

- LIFE CYCLE COSTS OFTEN MUCH LOWER THAN FORMER SOLUTIONS TO SAME PROBLEM

# **GLOBAL/LOCAL DISTRIBUTION**

### **APPROACH**

- EXPERIMENTAL INVESTIGATION

- LABORATORY MODEL

- OFF-THE-SHELF HARDWARE (MICROPROCESSORS ARE INEXPENSIVE)

- MULTIPLE PROCESSORS

- SHARED MEMORY FACILITY INTERCONNECT

- EXPERIMENTAL CONTROL STRUCTURE

- LOCAL KNOWLEDGE OF EXISTANCE OF OTHER PROCESSORS NOT REQUIRED

- GLOBAL CONTROL AND TASK SCHEDULING VIA HIGHLY RELIABLE SHARED MEMORY

- EXPERIMENTAL WELL-KNOWN APPLICATION-DFT

- DEMONSTRATE CONCEPT FEASIBILITY

- PERFORM TRADE-OFF ANALYSES

- IDENTIFY AND IMPLEMENT FAULT-TOLERANT CONCEPTS

### **EXPERIMENTAL HARDWARE CONFIGURATION**

- ONE BYTE ACCESSED PER POLL

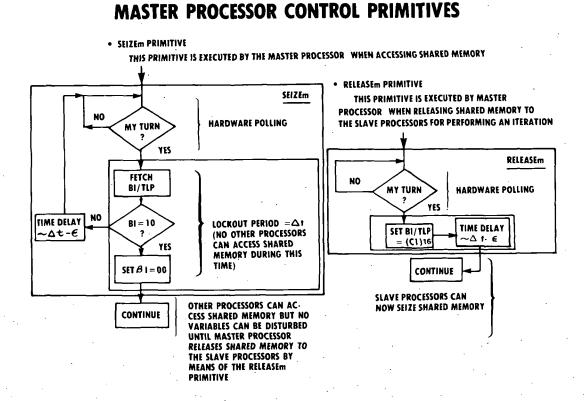

- FIXED LOCK-OUT TIME IN FLAG BLOCK

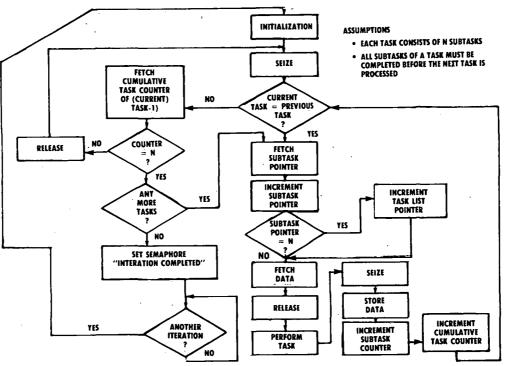

### ASSUMPTIONS

- MASTER PROCESSOR PERFORMS INTERFACE AND DISPLAY FUNCTIONS

- SLAVE PROCESSORS PERFORM APPLICATION FUNCTION CONCURRENTLY AS DIRECTED BY MASTER PROCESSOR

- LOCAL MEMORY

- EACH SLAVE PROCESSOR CONTAINS IDENTICAL COPY OF PROGRAMS

- CONTROL EXECUTIVE

- APPLICATION TASKS

- SHARED MEMORY

- COMMON TO ALL PROCESSORS

- CONTROL VARIABLES

- APPLICATION DATA

- ACCESSED BY CONTROL PRIMITIVES

- ACCESS RIGHTS ENFORCED BY SEMAPHORES

- VARYING NUMBER OF PROCESSORS DOES NOT AFFECT CONTROL STRUCTURE

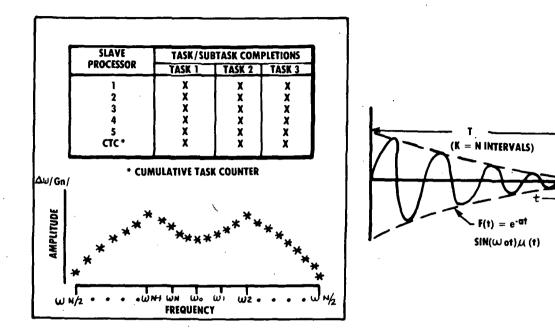

# **TASK STRUCTURE**

£

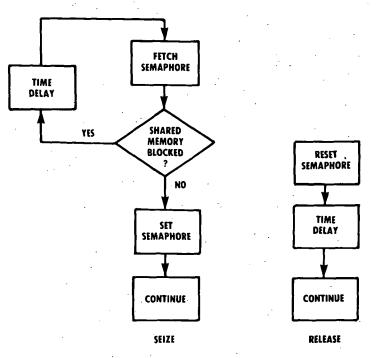

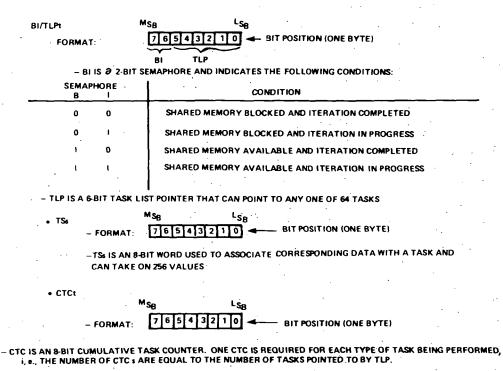

# SYSTEM CONTROL: SEMAPHORES

- ENFORCES ACCESS RIGHTS TO SHARED MEMORY

- USED TO INDICATE CONDITIONS

- SHARED MEMORY BLOCKED

- SHARED MEMORY AVAILABLE

- ITERATION IN PROGRESS

- ITERATION COMPLETED

### **CONTROL PRIMITIVES**

### **CONTROL VARIABLES**

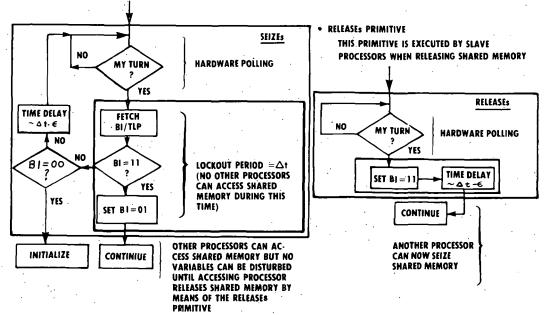

### **SLAVE PROCESSOR CENTROL PRIMITIVES**

#### SEIZES PRIMITIVE

THIS PRIMITIVE IS EXECUTED BY THE SLAVE PROCESSORS WHEN ACCESSING SHARED MEMORY

### **TASK EXECUTION CONTROL**

#### **APPLICATION** DFT

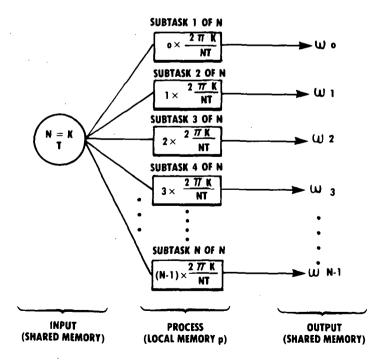

A DFT CAN BE DEFINED IN THE FOLLOWING MATRIX FORM:

#### G = WFIF WE LET:

• n = 0,1,2, ...., N-1 = MATRIX ROW NUMBER AND FREQUENCY STEP • k = 0,1,2, ...., k-1 = MATRIX COLUMN NUMBER AND TIME STEP

• N = k BUT MAINTAINING n AND k NOTATIONS TO DISTINGUISH ROWS FROM COLUMNS

THEN:

• W IS AN N×k MATRIX CONSISTING OF THE TERMS

wn,k = e(-27/j/N)(nk MOD N)

= COS  $\left[\frac{(1,7)}{N}\right]_{nk}$  MOD N)] - j SIN  $\left[\frac{(1,2')}{N}\right]_{nk}$  MOD N)] • F IS A k × I MATRIX REPRESENTING THE FUNCTION F(1k)T/217k OVER THE TIME SPAN T

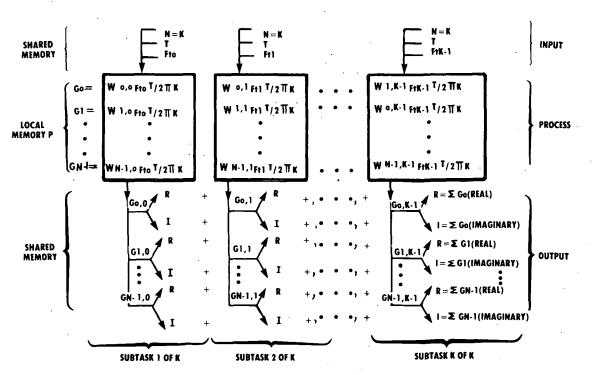

• G IS AN N×I MATRIX WHERE Gn = T/2Tk  $\stackrel{K+1}{\leq}$  wn,k f(tk) in expanded form, g = wf can be written as:  $^{k=0}$

| $ \left(\begin{array}{c} G0\\ G1\\ G2\\ \end{array}\right)= $ | W0,0<br>W1,0<br>W2,0 | W <sup>0</sup> ,K-1<br>W1,K-1<br>W2,K-1 | W0,2<br>W1,2<br>W2,2 | W0, K-1<br>W1, K-1<br>W2, K-1<br>W2, K-1 |  |

|---------------------------------------------------------------|----------------------|-----------------------------------------|----------------------|------------------------------------------|--|

| GN-1                                                          | WN-1,0               | WN-1,K-1                                | ₩N-1,2               | WN-1, K-1 /2 TT K                        |  |

SINCE:

Gn,k (REAL) = COS  $\left\{ \left( \frac{2\Pi}{\Lambda^2} \right) (nk \text{ MOD N}) \right\} F(tk) T/2 \Pi k$

Go, k (IMAGINARY) = - j {SIN  $\left[\left(\frac{2\pi}{N}\right)(nk \mod N)\right]} f(tk) T/2 \pi k$ ι. ×

$$n = n \Delta \omega$$

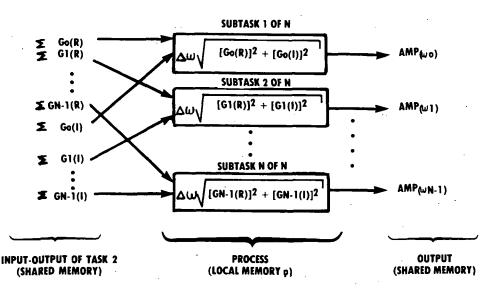

WHERE  $\Delta \omega = \frac{\omega n}{N}$

$$|G_{n}| = \sqrt{\left| \underbrace{k}_{A=0}^{k} G_{n,k} \left( \text{REAL} \right) \right|^{2} + \left[ \underbrace{k}_{A=0}^{k-1} G_{n,k} \left( \text{IMAGINARY} \right) \right]^{2}}$$

THE AMPLITUDE/FREQUENCY VALUES CAN BE OBTAINED AS FOLLOWS:  $AMP(\omega_n) = \Delta \omega |G_n|$

## **INPUT/OUTPUT**

### **DFT DECOMPOSITION FOR TASK 1**

### **DFT DECOMPOSITION FOR TASK 2**

# **DFT DECOMPOSITION FOR TASK 3**

122 -

# **STATUS**

- IMPLEMENTATION

- GCSS SIMULATION

- LABORATORY EVALUATION

- FAULT TOLERANT STUDIES

- **PROCESSOR**

- SHARED MEMORY

- BUS

# 1 OF N PROCESSOR 1 PROCESSOR 2 BUS SHARED MEMORY PROCESSOR N

# **RELIABILITY MODEL**

TAKE ADVANTAGE OF MULTIPLE

PROCESSORS

OPTIMIZE EXISTING CONTROL STRUCTURE FOR FAULT-TOLERANCE PURPOSES

- CURRENTLY SINGLE POINT FAILURES

- STUDIES TO IDENTIFY FAULT TOLERANT

SCHEMES

- POSSIBLE IMPLEMENTATION OF HIGHLY RELIABLE SHARED MEMORY WOULD BE DUPLEXED CONFIGURATION EACH WITH SINGLE ERROR CORRECTION AND DOUBLE ERROR DETECTION