# NOTICE

THIS DOCUMENT HAS BEEN REPRODUCED FROM MICROFICHE. ALTHOUGH IT IS RECOGNIZED THAT CERTAIN PORTIONS ARE ILLEGIBLE, IT IS BEING RELEASED IN THE INTEREST OF MAKING AVAILABLE AS MUCH INFORMATION AS POSSIBLE

N81-12786

(NASA-CR-163802) DEVELOPMENT OF BOOLEAN CALCULUS AND ITS APPLICATIONS Final Report, Aug. 1977 - 31 Dec. 1980 (Miami Univ.) 71 p HC A04/MF A01 CSCL 12A

Unclas G3/64 29385

## DEVELOPMENT OF BOOLEAN CALCULUS AND ITS APPLICATIONS

FINAL REPORT NASA GRANT NO. NSG 1436 AUGUST 15, 1977 DECEMBER 31, 1980

$\odot$

BY

MOIEZ A. TAPIA

PREPARED FOR

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION LANGLEY RESEARCH CENTER HAMPTON, VIRGINIA 23665

ATTENTION:

Ber Same

DR. JERRY H. TUCKER, NASA TECHNICAL MONITOR

DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF MIAMI CORAL GABLES, FLORIDA 33124

1

## INDEX

- 1. INTRODUCTION

- 2. FORMALIZATION OF BOOLEAN CALCULUS

- 3. NEW SYNTHESIS TECHNIQUES

- 4. DEFINITIONS

- 5. SYNTHESIS USING SP COUNTER

- 6. NONCOMBINATIONAL BOOLEAN CALCULUS

- 7. CONCLUSION

7

- 8. PUBLICATIONS GENERATED BY THE GRANT

- 9. REFERENCES

- APPENDIX I

- APPENDIX II

- APPENDIX III

#### DEVELOPMENT OF BOOLEAN CALCULUS

AND

ITS APPLICATIONS (NASA GRANT NSG 1436 1977-1980) FINAL REPORT

MOIEZ A. TAPIA DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF MIAMI CORAL GABLES, FLORIDA 33124

**1.** INTRODUCTION

The report describes the significant results obtained during the NASA GRANT NSG No 1436 period from August 1977 through December 31, 1980. The primary objective of the grant has been to develop Boolean Calculus so that it can be advantageously applied to developing new digital system design methodologies that would be desirable additions to existent methodologies in terms of reducing system complexity, size, cost, speed, power requirements, etc. New synthesis procedures were developed during the tenure of the grant with the above mentioned objectives in mind. These will be described in the following sections. Several publications that resulted from research efforts will be shown in a later section.

### 2. FORMALIZATION OF BOOLEAN CALCULUS:

Formalization of the existent and new concepts and relationships in the area of the Boolean Integral Calculus are given in Appendix I.

### 3. <u>NEW SYNTHESIS TECHNIQUES:</u>

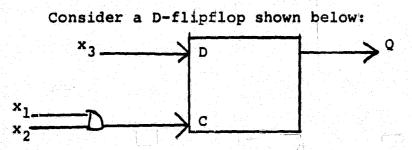

Boolean Calculus has made it possible to synthesize fundamental-mode asynchronous sequential system using clock-triggered flipflops. It has been shown that synthesis techniques that utilize edge-sensitiveness property of flipflops require fewer flipflops and logic gates than conventional techniques do for many systems [11]. In order to describe the new synthesis technique, we need the following definitions:

<u>Definition 2.1</u>: Given a Fundamental Mode Asynchronous(FMA) system, FMAS = (I, S, O, f, g) where

(P

- $I = set of p distinct input conditions = {I_i}$

- $S = set of q states of the system = {S_j}$

- $O = set of outputs = \{O_i\}$

- f = output function

- =  $f(S_k, I_j), \forall_j \text{ and } k$

- $g = g(S_k, I_j), \forall j and k$

- = next state function,

we will need to tranform it to a Differential Mode System, DMS as defined below:  $DMS = (I', I^{*}, S', O', f', g')$ where I' = I, S' = S $\mathbf{I}^{*'} = \{(\mathbf{I}_{j}, \mathbf{I}_{k}) | \mathbf{v}_{j,k}\}$ 0'=0 f' = output function of DMS g' = next state function of DMS  $= g'(S_h, I_j, I_k)$  $S_i$ , if  $g(S_h, I_j) = S_h$ ,  $g(S_h, I_k) = S_j$ and  $g(S_i, I_k) = S_i$  $S_i$ , if  $g(S_h, I_j) = S_h$  and there exist  $S_{i1}, S_{i2}, ---, S_{in} \& S_i$ such that  $g(S_h, I_k) = S_{i1}$ ,  $g(S_{i1}, I_k) = S_{i2}, ---, g(S_{in}, I_k) = S_i$ and  $g(S_i, I_k) = S_i$ . -, if  $g(S_h, I_j) = S_h \& g(S_h, I_k) = -$ ----, if  $g(S_h, I_j) = S_h$  and there exist S<sub>i1</sub>,S<sub>i2</sub>,---,S<sub>in</sub> such that  $g(S_{h}, I_{k}) = S_{i1}, g(S_{i1}, I_{k}) = S_{i2},$  $g(S_{i2}, I_k) = S_{i3}, ---, g(S_{in}, I_n) = -$ --, if  $g(S_h, I_j) \neq S_h$

$f'(S_{h}, I_{j}, I_{k})$   $= \frac{f(S_{i}, I_{k}), \text{ if } g'(S_{h}, I_{j}, I_{k}) = S_{i}}{---'} \text{ if } g'(S_{h}, I_{j}, I_{k}) \text{ is unspecified}$

-- 3 --

It will be assumed that only one input variable can change at a time.

In order to facilitate understanding of DMS construction, an example will be presented.

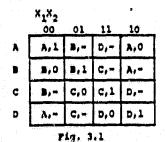

| 00             | 01             | 11                                                                    | 10                                                     |

|----------------|----------------|-----------------------------------------------------------------------|--------------------------------------------------------|

| <b>(A)</b> , 1 | C,—            | <b>(A</b> ), 0                                                        | c, —                                                   |

| <b>B</b> , 0   | D,             | <b>B</b> , 1                                                          | D,                                                     |

| В,—            | ©, 1           | в,—                                                                   | ©, 0                                                   |

| A,—            | <b>D</b> , 0   | A,—                                                                   | D, 1                                                   |

|                | <b>(A)</b> , 1 | (A), 1       C, —         (B), 0       D, —         B, —       (C), 1 | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

Figure 1 (FMA System)

Figure 1 describes an FMA system.

|   | x <sub>1</sub> x <sub>2</sub>                                                                                                                                                                                                     |          |          | e igi shi ka walaan daabida<br>Tarabida | a la constituer especial.<br>A |          |          |          |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-----------------------------------------|--------------------------------|----------|----------|----------|

|   | 00<br>10                                                                                                                                                                                                                          | 00<br>01 | 01<br>11 | 01<br>00                                | 10<br>00                       | 10<br>11 | 11<br>01 | 11<br>10 |

| A | С,О                                                                                                                                                                                                                               | C, 1     |          |                                         | <b></b>                        |          | C,1      | C,0      |

| B | D,1                                                                                                                                                                                                                               | D,0      |          |                                         |                                |          | D,0      | D,1      |

| С | e de la companya de<br>La companya de la comp |          | B,1      | в,0                                     | в,0                            | B, 1     |          |          |

| D |                                                                                                                                                                                                                                   |          | Α,Ο      | A, 1                                    | A,1                            | Α,Ο      | 54<br>   | <b>.</b> |

|   |                                                                                                                                                                                                                                   |          |          |                                         |                                |          |          |          |

Figure 2 (DM System)

Figure 2 describes a DMS system that has been transformed from the FMA system in Figure 1.

Observe that the FMA system table in Figure 1 is in its reduced form.

It can be shown that the method of state reduction normally used for reducing an FMA table can be applied to the next-state and output table for a DMS system. If such a reduction is carried out in

- 4 -

case of Figure 2, one gets the reduced DM system in Figure 3.

| 1 .<br> | <b>x</b> 1 <b>x</b> 2 |          |          |          |          |          |          |          |

|---------|-----------------------|----------|----------|----------|----------|----------|----------|----------|

|         | 00<br>10              | 00<br>01 | 01<br>11 | 01<br>00 | 10<br>00 | 10<br>11 | 11<br>01 | 11<br>10 |

| (A,C) A | Α,Ο                   | A, 1     | B,1      | B,0      | В,О      | B,1      | A, 1     | A, 0     |

| (B,D) B | B,1                   | В,О      | A, 0     | A, 1     | A,1      | Α,Ο      | В,0      | B,1      |

Figure 3 (Reduced DM table)

The next step in the synthesis procedure is to assign state assignments to the states in the system. While doing so, we must ensure that the assignment is such that it allows only one state variable to change during state transition. If the state diagram corresponding to the DM table is not amenable to single-variablechange assignment, we will need to increase the number of states by adding equivalent states in order to accomplish single-variablechange assignment. This problem will be referred to again in the report later. Of course, even in the case of traditional techniques for synthesizing FMA systems, the same technique must be resorted to in order to achieve single-variable-change state assignment.

In order to get a feeling for the problems associated with synthesizing an asynchronous sequential system using clock-triggered flipflops, we will present a complete synthesis example given below:

- 5 -

|   | ×1×2<br>00 | 01   | 11   | 10   | , |

|---|------------|------|------|------|---|

| A | A, 1       | B, — | D,   | В,—— |   |

| B | À, 1       | B, 1 | c,—  | B, 1 |   |

| C | C, 0       | B,—— | C, 1 | D, — |   |

| D | C,——       | A,   | D, 0 | D, 0 |   |

Figure 4

88

3

|   | $\mathbf{x_{1}x_{2}}$ |          |          |           |          |                            |                    |          |

|---|-----------------------|----------|----------|-----------|----------|----------------------------|--------------------|----------|

|   | 00<br>10              | 00<br>01 | 01<br>11 | 01<br>00  | 11<br>01 | 11<br>10                   | 10<br>00           | 10<br>11 |

| A | B, 1                  | B, 1     |          |           |          |                            | *** *** <b>*</b> * |          |

| B |                       |          | C, 1     | A, 1      | 1        | <b>— — — — — — — — — —</b> | A, 1               | C, 1     |

| С | ©<br>D, 0             | B, 1     |          |           |          |                            |                    |          |

| D |                       |          |          | ° <b></b> | A        | D                          | Ø                  | D        |

Figure 5

The system in Figure 4 is an FMA system which is to be synthesized using clock-triggered flipflops. The transformation of the system into DM system is given in Figure 5.

When the table in Figure 5 is reduced, we get the reduced DM system in Figure 6. Observe that the FMA system in Figure 5 is in its reduced form.

6

|         | $\mathbf{x_1}\mathbf{x_2}$ |          |          |          |          |          |          |          |

|---------|----------------------------|----------|----------|----------|----------|----------|----------|----------|

|         | 00<br>10                   | 00<br>01 | 01<br>11 | 01<br>00 | 11<br>01 | 11<br>10 | 10<br>00 | 10<br>11 |

| (A,B) A | A, 1                       | A, 1     | C, 1     | A, 1     | <b></b>  |          | A, 1     | C, 1     |

| (C,D) C | C,0                        | A, 1     |          |          | A,——     | C,—      | c, —     | c, —     |

|         |                            |          |          | Figur    | e 6      | · · ·    |          |          |

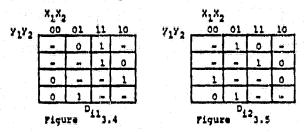

Let y = 0 represent A and y = 1 represent C. The excitation table for the DM system is given in Figure 7.

|   | x <sub>1</sub> x <sub>2</sub> | i.<br>Ko | and the second sec |          |          |          |          |          |

|---|-------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|

|   | 00<br>) 10                    | 00<br>01 | 01<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 01<br>00 | 11<br>01 | 11<br>10 | 10<br>00 | 10<br>11 |

| 0 | 0                             | 0        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0        |          | <b></b>  | 0        | 1        |

| 1 | 1                             | 0        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •        | 0        | 1        | 1        | 1        |

Figure 7

Observe that in the first row y changes when  $x_1$  changes to 1 with  $x_2 = 1$  and when  $x_2$  changes to 1 with  $x_1 = 1$ . In the second row y changes when  $x_2$  changes to 1 with  $x_1 = 0$  and when  $x_1$  changes to 0 with  $x_2 = 1$ . Hence the clock function should go through positive changes when any of these changes occur. Hence we can write down the differential expression for the clock function as follows: dc =  $\overline{y}(x_2dx_1 + x_1dx_2) + y(\overline{x}_1dx_2 + x_2d\overline{x}_1)$ Observe that

$f_{1}dc = \overline{y}(x_{1}x_{2}) + y(\overline{x}_{1}x_{2})$  $f_{0}dc = \overline{y}(\overline{x}_{1}x_{2} + x_{1}\overline{x}_{2}) + y(\overline{x}_{1}\overline{x}_{2} + x_{1}x_{2})$

У

63

Hence  $\int_1 dc \cdot \int_0 dc = 0$  and dc is compatibly integrable.

- 7 -

$f_1 dc = \overline{y}(x_1 x_2) + y(\overline{x}_1 x_2)$  is a possible soulution. Let us, therefore try,

$C = \overline{y}(x_1x_2) + y(\overline{x}_1x_2)$   $\frac{\partial C}{\partial x_1} = \overline{y}x_2 , \quad \frac{\partial C}{\partial \overline{x}_1} = yx_2$   $\frac{\partial C}{\partial x_2} = \overline{y}(x_1) + y(\overline{x}_1), \quad \frac{\partial C}{\partial \overline{x}_2} = 0$   $\frac{\partial C}{\partial y} = (\overline{x}_1x_2), \quad \frac{\partial C}{\partial \overline{y}} = x_1x_2$

Observe that as far as  $x_1$  and  $x_2$  are concerned, no undesired transitions are caused by them. Since  $\frac{\partial C}{\partial Q}$  and  $\frac{\partial C}{\partial y}$  are non-zero, we must make sure that when y changes, it does not cause undesired transitions.  $\frac{\partial C}{\partial y} = x_1 x_2$ . Hence when  $x_1 x_2 = 1$  and y changes from 1 to 0, it will cause a positive change in the value of C. Looking at the excitation table in Figure 7, we see that when input  $x_1 x_2$  changes to 11 (from 01 or 10), y changes from 0 to 1 rather than from 1 to 0. Hence this undesired transition cannot occur.

Consider next  $\frac{\partial C}{\partial y} = \overline{x_1}x_2$ . When  $x_1x_2 = 1$  and y changes from 0 to 1,  $\frac{\partial V}{\partial y}$  C will go through a positive transition. When  $x_1x_2$  changes from 00 or 11 to 01, y changes from 1 to 0, rather than from 1 to 0. Hence, no undesired transition is caused by change in y when  $x_1x_2$ changes from 00 or 11 to 01.

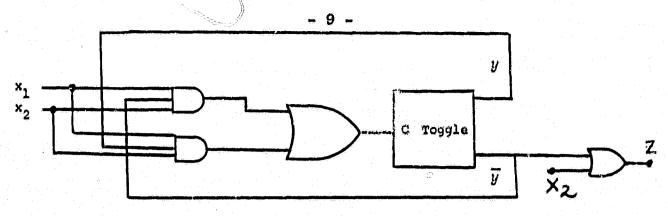

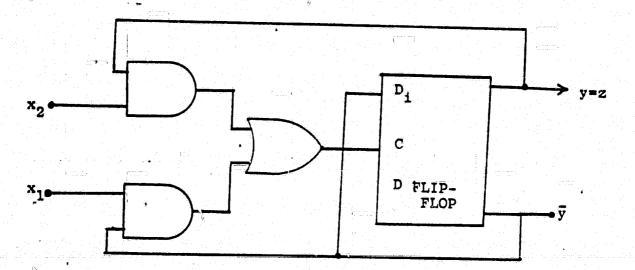

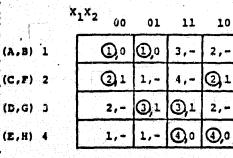

Hence we have no ripple and  $C=\overline{y}(x_1x_2) + y(\overline{x}_1x_2)$  realizes the system. It can be shown that  $z=\overline{y}+x_2$ .

- 8 -

A toggle flipflop is used, since y changes whenever clock transition occurs.

Observe that  $\overline{x}_1 x_2 \Delta y$  and  $x_1 x_2 \nabla y$  are transitions that cannot occur.

#### 4. DEFINITIONS

The following definitions will be needed to describe the results of the reservent:

<u>Definition 4.1</u>:  $m_j(\underline{x} - x_i)$  denotes the product term obtained by deleting the variable  $x_i$  from the jth minterm of variables  $x_1, x_2, \ldots, x_n$ .

<u>Definition 4.2</u>:  $m_j(\underline{x} - x_i) \Delta x_i$  denotes the positive transition when  $m_j(\underline{x} - x_i) = 1$  and  $x_i$  changes from 0 to 1.

<u>Definition 4.3</u>:  $m_j(\underline{x} - x_i) \nabla x_i$  denotes the negative transition when  $m_i(\underline{x} - x_i) = 1$  and x changes from 1 to 0.

<u>Definition 4.4</u>: TP(C<sub>j</sub>) denotes set of all possible positive transitions of C<sub>j</sub> where C<sub>j</sub> is a function of <u>x</u> and <u>y</u>.

The meanings of notations such as  $m_j(\underline{x},\underline{y}-\underline{y}_i)$ ,  $m_j(\underline{x},\underline{y}-\underline{y}_i) \forall \underline{y}_i$ , etc., easily follow from the above definitions and will, therefore, not be defined. Definition 4.5: A differential expression of the form

$$dF = m_{0}(\underline{y}) \sum_{i=1}^{n} (\alpha_{0i}dx_{i} + \beta_{0i}d\overline{x}_{i})$$

+

$$m_{1}(\underline{y}) \sum_{i=1}^{n} (\alpha_{1i}dx_{i} + \beta_{1i}d\overline{x}_{i})$$

+...+  $m_p(\underline{y}) \sum_{i=1}^{n} (\alpha_{pi} dx_i + \beta_{pi} d\overline{x}_i)$

## where $p = 2^m - 1$

is said to be <u>exactly integrable with respect to variables</u>  $\frac{x_1, x_2, \dots, x_n}{\frac{\partial G}{\partial x_i}} = m_0(\underline{y}) \alpha_{0i} + m_1(\underline{y}) \alpha_{1i} + \dots + m_p(\underline{y}) \alpha_{pi}, \&$   $\frac{\partial G}{\partial \overline{x_i}} = m_0(\underline{y}) \beta_{0i} + m_1(\underline{y}) \beta_{1i} + \dots + m_p(\underline{y}) \beta_{pi}, \forall_i.$

If a function G satisfying the above equations does exist, then G is called the <u>exact integral of dF with respect to</u>  $x_1x_2, \ldots, x_n$ . <u>Definition 4.6</u>: I<sub>k</sub> represents the binary vector  $(b_1, b_2, \ldots, b_n)$ such that  $b_i$ 's are 0's or 1's and k is the numerical value of  $(b_1b_2...b_n)$ , when the latter is interpreted as a binary number.

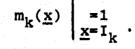

Observe that  $m_k(\underline{x}) = 1$  $\underline{x} = I_k$

<u>Definition 4.7</u>:  $S_k$  represents the binary vector  $(b_1, b_2, \ldots, b_m)$ such that  $b_i$ 's are 0's or 1's and k is the numerical value of  $(b_1, b_2, \ldots, b_m)$ , when the latter is interpreted as a binary number. Observe that  $m_k(\underline{y}) = 1$  $\underline{y} = S_1$ .

<u>Definition 4.8</u>:  $S_{j1}$  and  $S_{j2}$  are said to be  $y_j$ -adjacent to each other, if their representations as defined in Definition 4.7 agree in every bit except the  $j\frac{th}{t}$  one.

<u>Definition 4.9</u>: TP (dF) denotes the set of transitions specified by the differential expression dF which can cause F to change from 0 to 1, if dF is compatibly integrable. If dF is not integrable, TP(dF) is not defined.

<u>Definition 4.10</u>: If a change in the value of state variable  $y_j$  resulting from a change in input causes another state variable  $y_i$ , for some  $i \neq j$ , to change its value, then a <u>secondary trans-</u><u>ition</u> or <u>ripple</u> is said to occur in flipflop that is associated with the state variable  $y_i$ . If in a DM system a ripple cannot occur, the system is called <u>ripple-free</u>.

<u>Definition 4.11</u>:  $m_j(\underline{x} - x_i) \Delta x_i$  and  $m_j(\underline{x} - x_i) \nabla x_i$  defined earlier will also, be denoted by  $m_j(\underline{x} - x_i)dx_i$  and  $m_j(\underline{x} - x_i)d\overline{x}_i$ , respectively.

Definition 4.12:  $\Im_{j}(\underline{x} - x_{i})$  denotes transitions defined in Definitions 4.2 and 4.3 as follows:  $\Im(\underline{x} - x_{i})$  $= -\frac{\overline{m_{j}}(\underline{x} - x_{i}) \Delta x_{i}}{\underline{m_{j}}(\underline{x} - x_{i}) \Delta x_{i}}$ , if  $x_{i}$  is in true form in  $\underline{m_{j}}(\underline{x})$  $= -\frac{\overline{m_{j}}(\underline{x} - x_{i}) \nabla x_{i}}{\underline{m_{j}}(\underline{x} - x_{i}) \nabla x_{i}}$ , if  $x_{i}$  is in complemented form in  $\underline{m_{j}}(x)$

- 11 -

<u>Definition 4.13</u>:  $m_j(\underline{x} - x_i) \bigotimes x_j$  denotes a pair of transitions defined by  $m_j(\underline{x} - x_i) \Delta x_j$  and  $m_j(\underline{x} - x_i) \nabla x_i$ .

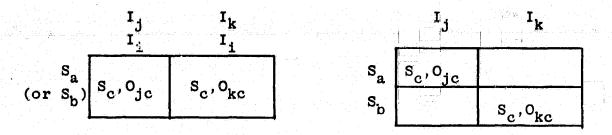

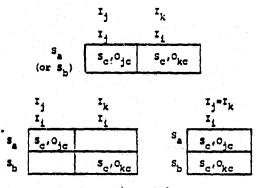

<u>Definition 4.14</u>: A DMS system table is said to be <u>level-wise</u> <u>output-unambiguous</u>, if there exist no input conditions  $I_i$ ,  $I_j$ ,  $I_k$  and states  $S_a$  and  $S_b$ ,  $I_i$  and  $I_k$  being adjacent,  $I_j \neq I_k$  $S_a$  and  $S_b$  not necessarily distinct, such that  $g'(S_a, I_j, I_i)$ ,  $g'(S_b I_k, I_i)$ ,  $f'(S_a I_j, I_i)$  and  $f'(S_b, I_k, I_i)$  are defined and  $g'(S_a, I_j, I_i) = g'(S_b, I_k, I_i) = S_c$  (say)  $f'(S_a, I_j, I_i) = O_{jc} \neq O_{kc} = f'(S_b, I_k, I_i)$ .

A DMS system table which is not level-wise output-unambiguous will be called <u>level-wise-ambiguous</u>.

#### 4.2 BASIC ASSUMPTIONS

All the theorems that follow are pertaining to realization of a DM system table using clock-triggered flipflops. Unless otherwise stated, the following assumptions will be applicable to all our discussion:

- 1. only one input variable can change at a time

- 2. only one state variable is allowed to change during a state transition. This is equivalent to assuming that the specified

table (after state addition if necessary) lends itself to single-variable-change state assignment. This restriction will be removed later,

- 3. all flipflops respond to a positive transition in clock input 4.  $C_i (=C_i(\underline{x},\underline{y}))$  denotes the function defining the input to the clock pin of the flipflop i, i.e., the flipflop associated with variable  $y_i$ , for  $V_i$ ,  $1 \le i \le m$ .

- 5. an input (condition)  $I_k$  corresponds to value of <u>x</u> such that

6. a state (assignment)  $S_k$  represents value of <u>y</u> such that  $m_k(\underline{y}) \begin{vmatrix} z \\ z \\ z \\ z \\ k \end{vmatrix}$ .

7. The number of states in the table is already reduced to minimum possible.

The following theorems establish conditions for realizing a DMS table using clock-triggered flipflops:

<u>Theorem 4.1</u>: Consider a DM system table whose realization exists. Then corresponding to every row (or state)  $S_{i1}$  and input change from  $I_{j1}$  to  $I_{j2}$ ,  $0 \le i \le q-1$ ,  $0 \le j1 \le p-1$ ,  $0 \le j2 \le p-1$ ,  $I_{j1}$  and  $I_{j2}$  being  $x_i$ -adjacent, if the next state function  $g'(S_{i1}, I_{j1}, I_{j2})$ is defined and (4.1.1)  $g'(S_{i1}, I_{j1}, I_{j2}) = S_{i2}$  where

(4.1.2)  $S_{i1}$  and  $S_{i2}$  are  $y_k$ -adjacent, then (4.1.3)  $dC_k m_{i1}(\underline{y}) \cdot \partial(m_{j2}(\underline{x}-\underline{x}_i)), 1 \le k \le m$ The proof is given in reference 14. <u>Theorem 4.2</u>: Any finite-state asynchronous sequential system can be realized using clock-triggered flipflops and logic gates and employing Boolean calculus method.

The proof is given in Semi-Annual Status Report #2 [15].

<u>Theorem 4.3</u>: The complexity of network realization of a finitestate asynchronous sequential system, consisting of clocktriggered flipflops and logic gates obtained by employing Boolean calculus method is no higher than that of a network realization of the same system, consisting of S-R flipflops (without clock inputs) and logic gates obtained by conventional method for synthesis of an FMA system.

When the DMS table admits of a unit-distance state assignment, the realization of the system is possible using any commercially available flipflops. When the DMS table is such that unit-distance state assignment is not possible, then certain relationships among the tune response characteristics of the flipflops must be satisfied so that the different time responses of flipflops do not cause undesired transitions and hazards. These need to be obtained.

Synthesis procedures are illustrated in conference papers given in Appendices II & III.

- 14 -

#### 5. SYNTHESIS USING SP COUNTER

Efforts to explore the possibility of using an SP (synchronous presettable) counter to realize an FMA system were successful. Such an approach significantly reduces the number of IC packages required for the system to be realized, thus reducing network complexity, size and cost.

#### 5.1 SP COUNTER

An SP counter (such as 74LS160) has the following input and output pins of interest to us:

- (1) count-enable inputs P & T, both of which must be high for the counter to count.

- (2) Load input L which, on low level, causes the data on the data input pins to be transferred synchronously to the count output pins when a positive transition of clock pulse occurs.

- (3) Clock input pin CK. Loading or counting occurs synchronously on the positive transition of clock pulse.

- (4) Data input pins  $D_1$ ,  $D_2$ , ...,  $D_n$ . The data on these pins are transferred to count output pins  $Y_1$ ,  $Y_2$ , ...,  $Y_n$  respectively on the positive transition of clock pulse when L = 0.

- (5) Output pins  $Y_1, Y_2, \ldots, Y_n$  give the count output of the counter.

## 5.2 EXAMPLE

Before presenting a formal theory and procedure for synthesis, we will illustrate the procedure with the following example:

Consider the FMA system given in Figure 5.2.1.

|   | $x_1 x_2$     |               |               |                |  |  |

|---|---------------|---------------|---------------|----------------|--|--|

|   | 00            | 01            | 11            | 10             |  |  |

| a | <b>(a),</b> 0 | <b>(a),</b> 0 | b,-           | <b>(a)</b> , 0 |  |  |

| b | a,-           | d,1           | <b>(b</b> , 1 | <b>()</b> , 1  |  |  |

| с | a,-           | a,-           | ©, 0          | ©, 0           |  |  |

| đ | a,-           | @,1           | c,-           | -              |  |  |

|   |               | Figure        | 5.2.1         |                |  |  |

Observe that the system is already minimized. Moreover it does not admit of a unit-distance state assignment using only two state variables. Hence three state variables are needed to realize the system, if conventional synthesis procedure is employed.

Using the transformation equations in Definition 2.1 we get the Differential Mode System (DMS) given in Figure 5.2.2 which is equivalent to the system under consideration.

| <sup>Y</sup> 1 <sup>Y</sup> 2 | 1 2<br>00<br>10 | 00<br>01 | 01<br>11 | 01<br>00 | 11<br>01 | 11<br>10 | 10<br>00 | 10<br>11 |

|-------------------------------|-----------------|----------|----------|----------|----------|----------|----------|----------|

| 00 a                          | a,0             | a,0      | b,1      | a,0      |          |          | a,0      | b,1      |

| 01 b                          |                 | -        | -        | _        | d,1      | b,1      | a,0      | b,1      |

| 11 c                          | •               |          |          | -        | a,1      | c,0      | a,0      | c,0      |

| 10 d                          |                 | •        | c,0      | a,0      | -        |          |          | -        |

<sup>0</sup>Figure 5.2.2

11

Let dC denote the differential expression for the clock function. dC is given by

$$\begin{array}{rcl} (E5.2.1) & dC = \overline{Y}_{1} \overline{Y}_{2} (x_{2} dx_{1} + x_{1} dx_{2}) &+ \overline{Y}_{1} Y_{2} (x_{2} d\overline{x}_{1} + \overline{x}_{2} d\overline{x}_{1}) \\ &+ Y_{1} Y_{2} (x_{2} d\overline{x}_{1} + \overline{x}_{2} d\overline{x}_{1}) &+ Y_{1} \overline{Y}_{2} (x_{2} dx_{1} + \overline{x}_{1} d\overline{x}_{2}) \end{array}$$

Let  $C_1$  be a compatible integral of dC. Then

$$\begin{array}{rcl} \mathbf{E5.2.2}) & \mathbf{C_1} = \overline{\mathbf{Y}_1} \overline{\mathbf{Y}_2} & \mathbf{x_1} \mathbf{x_2} + \overline{\mathbf{Y}_1} \mathbf{Y_2} \overline{\mathbf{x}_1} + \mathbf{Y_1} \overline{\mathbf{Y}_2} \cdot (\mathbf{x_1} \mathbf{x_2} + \overline{\mathbf{x}_1} \overline{\mathbf{x}_2}) & + \mathbf{Y_1} \mathbf{Y_2} (\overline{\mathbf{x}_1}) \\ & = \overline{\mathbf{Y}_2} \mathbf{x_1} \mathbf{x_2} + \mathbf{Y_2} \overline{\mathbf{x}_1} + \mathbf{Y_1} \overline{\mathbf{x}_1} \overline{\mathbf{x}_2} \end{array}$$

Observe that

Ĵ

- $(E5.2.3) \qquad \frac{\partial c_1}{\partial x_1} = \overline{Y}_2 x_2$

- (E5.2.4)  $\partial \frac{c_1}{\partial \overline{x}_1} = \frac{Y_2}{2} + \frac{Y_1}{x_2}$

- (E5.2.5)  $\frac{\partial c_1}{\partial x_2} = \overline{x}_2 x_1$  and

- (E5.2.6)  $\frac{\partial c_1}{\partial \overline{x}_1} = \frac{v_1 \overline{x}_1}{\partial \overline{x}_1}$

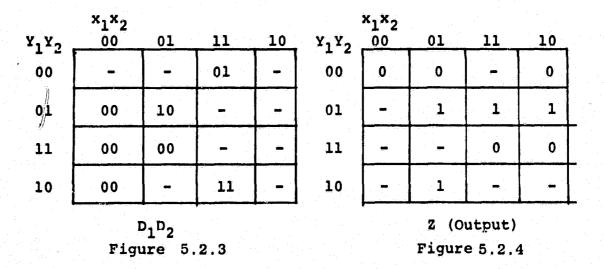

For the positive transitions that occur as shown in equations (E5.2.3) through (E5.2.6), we need to provide the appropriate values to data input pins  $D_1$  and  $D_2$  as shown in Figure 5.2.3.

From Figures 5.2.3 and 5.2.4 we get

$(E5.2.7) \qquad D_1 = \overline{x}_1 x_2 \overline{y}_1 + x_1 y_1$

(E5.2.8)  $D_2 = x_1$  and

(E5.2.9)  $z = Y_1 \oplus Y_2$ .

Equations (E5.2.2), (E5.2.7), (E5.2.8) and (E5.2.9) give the system realization with

(E5.2.10) L = O = P = T.

#### 5.3 SYNTHESIS PROCEDURE

Given an FMA system that is already reduced, the first thing to do is to find an equivalent DMS table using the equations in Definition 2.1. If the table thus obtained is reduced, if it is reducible, then the system may or may not be realizable. The procedure that follows applies to DMS table as obtained after transforming the FMA system. Later we will present the procedure for synthesizing DMS table that is reducible.

0

1. Consider next state for every present state and every input change. If the next state is different than the present state for a given present state and input change, form a differential term that reflects the input change and the present state in which the change is occurring. Taking Boolean sum of all such differential terms, form the differential expression for the clock function.

2. Find a compatible integral, say  $C_1$ , of the differential expression obtained above.

3. Find the Boolean differential  $dC_1$ , of the function  $C_1$  obtained so as to determine all possible positive transitions that can occur in the clock function.

4. Determine the value of next state and hence values of next state variables  $D_1, D_2, \ldots D_n$  corresponding to every differential term in  $dC_1$ . On the Karnaugh map for  $D_i$ ,  $1 \le i \le n$  place the value of  $D_i$  in the cell corresponding to the present state and the value of input that prevails after the input change described in the differential term occurs. The remaining cells are left unspecified. Realize functions  $D_1 D_2, \ldots D_n$ from the Karnaugh maps.

5. Obtain the output function z in terms of input variables and state variables as is usually done.

....

6. The LOAD pin and count enable inputs P and T are grounded. The functions  $C_1$ ,  $D_1$ ,  $D_2$ ,...,  $D_n$  and Z along with an SP counter give the desired network realization.

If the DMS table is reduced, then the conditions in Theorem 5.4.2 must be satisfied for it to be realized as a network with an SP counter in it. If the conditions are satisfied, the procedure mentioned above can be followed for synthesizing the table.

#### 5.4 REALIZABILITY

Next we will consider some theorems pertaining to realizability of a given FMA system using an SP counter.

<u>Theorem 5.4.1</u>: Given a DMS table obtained from an FMA system that has the same number of states as the former, it is realizable using an SP counter. The proof is outlined in reference [18].

<u>Theorem 5.4.2</u>: If the DMS table derived from an FMA system is reduced, then it is realizable using an SP counter if the following conditions are satisfied:

- The differential expression for the clock function for the table is compatibily integrable.

- (2) The table is level-wise next-state- and outputunambiguous.

#### 6. NONCOMBINATIONAL BOOLEAN CALCULUS

In Boolean calculus studied so far it was assumed that a function being studied is the output of a combinational system whose inputs are the arguments of the function. Also, while integrability of a differential expression was studied, it was tacitly assumed that an integral, if it exists, would be realized with a combinational system. An attempt was made to generalize the Boolean calculus that was developed with the limitations shown above. Such calculus, to be referred to, henceforth, as noncombinational Boolean calculus, will help us describe the output, after an input change, of a noncombinational system in terms of changes in the inputs to the system. Also, if the output, after an input change, is specified in terms of changes in inputs, realizability of such a specification using a noncombinational system will be studied. Some results obtained in this direction will be described in what follows. It will be assumed that only one variable can change at a time.

Definition 6.1:  $\Delta x_i$ ,  $1 \le i \le n$ , denotes a change in  $x_i$  from 0 to 1.

(D6.1.1)  $\Delta x_{i} = \begin{cases} 1 \text{ when } x_{i} \text{ changes from 0 to 1} \\ 0 \text{ otherwise} \end{cases}$

$\nabla x_i$ ,  $1 \leq i \leq n$ , denotes a change in  $x_i$  from 1 to 0.

(D6.1.2)  $\nabla x_i = \begin{cases} 1, \text{ when } x_i \text{ changes from 1 to 0} \\ 0, \text{ otherwise} \end{cases}$

<u>Definition 6.2</u>: The terms  $x_i \Delta x_i$ ,  $\overline{x_i} \Delta x_i$ ,  $x_j \nabla x_i$  and  $\overline{x_i} \nabla x_i$  will be defined as follows:

$$(D6.2.1) \qquad x_i \Delta x_i = \Delta x_i$$

- $(D6.2.2) \quad \overline{x_i} \Delta x_i = 0$

- $(D6.2.3) \quad x_{i} \nabla x_{i} = 0$

$(D6.2.4) \quad \overline{\mathbf{x}_{i}} \nabla \mathbf{x}_{i} = \nabla \mathbf{x}_{i}$

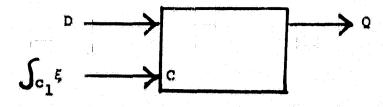

Since the relationship between Q and  $x_1$ ,  $x_2$  and  $x_3$  is not combinational, we cannot express Q in terms of a Boolean function of variables  $x_1$ ,  $x_2$  and  $x_3$ . However we could express the value of Q immediately following any transition of the clock.

Ĥ

- 22 -

Observe that

$$(D6.1.1)$$

$C = x_1 x_2$

so that

(D6,1.2)

$$dC = x_1 dx_2 + x_2 dx_1$$

Since only the positive transitions of clock are of interest, we may describe the positive transitions of clock in terms of changes in  $x_1$  and  $x_2$

(D6.1.3)

$$\Delta c = x_1 \Delta x_2 + x_2 \Delta x_1$$

Let Q(T+) denote the value of Q immediately following any transition of clock. Then by definition

$$(D6.1.4)$$

$Q(T+) = D . \Delta C$

(D6.1.5)  $Q(T+) = Dx_2 \Delta x_1 + Dx_1 \Delta x_2$ If we let

or

(D6.1.6) D = x<sub>3</sub>, then

(D6.1.7) Q(T+) =  $x_2 x_3 \Delta x_1 + x_1 x_3 \Delta x_2$

Equation (D6.1.7) points out that Q is 1 after the following transitions:

(1)  $x_2 = x_3 = 1$  and  $x_1$  changes from 0 to 1. (2)  $x_1 = x_3 = 1$  and  $x_2$  changes from 0 to 1.

Observe that if  $x_3 = 0$  and  $x_1 = 1$  while  $x_2$  changes from 0 to 1, then a transition does occur making Q to remain at or go to 0. This is not to be seen from equation(D6.1.7) if the function D (*i.e.*,  $x_3$  in this case) is not kept separate from the transition terms. Hence a more desirable form for Q(T+) than that shown in

## equation (6.1.7) would be

(D6.1.8)  $Q(T+) = D \cdot [x_2 \Delta x_1 + x_1 \Delta x_2]$ . <u>Definition 6.3</u>: The function Q(T+) as shown in equation (D6.3.1) below will be called <u>next-value</u> function.

(D6.3.1)  $Q(T+) = D \cdot \left[ \sum_{i=1}^{n} (\alpha_{i} \Delta x_{i} + \beta_{i} \nabla x_{i}) \right]$  where D is a function of <u>x</u> and <u>y</u>.

Obviously the function D outside the square bracket refers to the value that Q would assume if and when one of the transition terms inside the square brackets assumes value of 1.

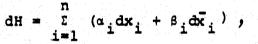

Addressing ourselves to the reverse problem of synthesizing a network that would realize a next-value function Q(T+) of the form

(D6.1.9)  $Q(T+) = D \cdot \int_{i=1}^{n} (\alpha_{i} \Delta x_{i} + \beta_{i} \nabla x_{i}) ],$ where  $\alpha_{i}$  and  $\beta_{i}$  are assumed to be independent of  $x_{i}$ , for all i, without loss of generality (in view of Definition 6.2), all that we need to do is to find the exact integral, if it exists, of the differential expression

(D6.1.10)

$$d\xi = \sum_{i=1}^{n} (\alpha_i dx_i + \beta_i d\overline{x}_i).$$

Of course, if the differential expression is not exactly integrable but compatibly integrable and if

$\int_{c1} d\xi$  is a compatible integral of the differential expression, then

- 24 -

a realization of the form

will provide not only the transitions that are specified in equation (D6.1.9) but, also, some additional transitions.

Theorem 6.1: If the next-value function of a system is given by

(T6.1.1)

$$Q(T+) = D. \left[\sum_{i=1}^{n} (\alpha_{i} \bigtriangleup x_{i} + \beta_{i} \nabla x_{i})\right]$$

where

(T6.1.2)  $D = D_1 \cdot x_{j1} \cdot x_{j2} \cdot \dots \cdot x_{jk}, 1 \le k \le n$

(T6.1.3)

$$F(\underline{x}) = \int_{\mathbf{E}} \left( \sum_{i=1}^{n} \alpha_{i} dx_{i} + \beta_{i} d\overline{x}_{i} \right)$$

and

(T6.1.4)  $F(\underline{x}) = x_{i1} \cdot x_{i2} \cdots x_{ik} \cdot F(\underline{x})$ , then  $Q_1(T+)$  described as (T6.1.5)  $Q_1(T+) = D_1 \cdot \left[\sum_{i=1}^{n} (\alpha_i \Delta x_i + \beta_i \nabla x_i)\right]$ realizes the same next-value function as Q(T+) in equation (T6.1.1) does.

<u>Proof</u>: Suppose due to a transition described by  $\partial m_p(\underline{x} - \underline{x}_q)$ , Q(T+) = 1 if  $\underline{y} = S_0$ . This implies that D = 1 when  $\underline{x} = b_p & \underline{x} = S_0$ Hence when  $\underline{y} = S_0$  and  $\underline{x} = b_p$   $1 = D = D_1 \cdot \underline{x}_{i1} \cdot \dots \cdot \underline{x}_{ik}$ so that  $D_1 = 1$  for  $\underline{x} = b_p & \underline{y} = S_0$

7

Definition 5.3: F is said to be a compatible integral of  $\underline{dH}$ , denoted by  $\int_{C} dH$ , and dH is said to be compatibly integrable if

9.

$$\frac{\partial F}{\partial x_i} = \alpha_i$$

and  $\frac{\partial F}{\partial \overline{x}_i} = \beta_i$  (D5.3.1)

for all  $i$ ,  $1 \le i \le n$ .

Observe that by the definitions given above if dH is exactly integrable, then  $F = \int_{E} dH$  goes through exactly the changes which are described in dH.

In what follows we will obtain ways of finding all possible compatible integrals of dH, if dH is compatibly integrable. To accomplish this we need the following integral operators:

Definition 5.4: The zeroth order integral of dH, denoted by  $\int_{0}^{\infty} dH$ , is defined as

$\int_{0} dH = \sum_{i=1}^{n} (\alpha_{i} \overline{x}_{i} + \beta_{i} x_{i})$ (D5.4.1)

where

Also, the first order integral of dH, denoted by  $\int_1 dH$ , is defined as

$$L^{dH} = \sum_{i=1}^{n} (\alpha_{i} x_{i} + \beta_{i} \overline{x}_{i}). \qquad (D5.4.3)$$

<u>Definition 5.5</u>: A binary point  $b_0 \in B(n)$  is said to be <u>"one"</u> (or "zero") of a function  $F(\underline{x})$  if

$$F(b_0) = 1(or 0)$$

(D5.5.1)

## Lemma 5.1: If the differential expression

$$dH = \Sigma (\alpha_{i} dx_{i} + \beta_{i} d\overline{x}_{i})$$

$$i=1$$

(L5.1.1)

is compatibly integrable and  $F_1$  is a compatible integral of dH, then every "one" of  $\int_1 dH$  is also a "one" of  $F_1$ .

<u>Proof:</u> Since  $F_1$  is a compatible integral, by Definition 5.3

$$\frac{\partial F_1}{\partial x_i} \supseteq^{\alpha} i \tag{L5.1.2}$$

$$\frac{\partial F_1}{\partial \bar{x}_i} \geq \beta_i.$$

(L5.1.3)

Also

and

·SP

Y

$$dF_{1} = \prod_{i=1}^{n} \left( \frac{\partial^{F_{1}}}{\partial x_{i}} dx_{i} + \frac{\partial^{F_{1}}}{\partial \overline{x}_{i}} d\overline{x}_{i} \right) \qquad (L5.1.4)$$

so that the "ones" of  $\frac{\partial F_1}{\partial x_i} \cdot x_i$  (or  $\frac{\partial F_1}{\partial \bar{x}_i} \cdot \bar{x}_i$ ),  $1 \le i \le n$ , are also the "ones" of  $F_1$

From equation (L5.1.2) (or (L5.1.3)) the "ones" of  $\alpha_i x_i$  (or  $\beta_i \overline{x}_i$ ), line 1 are the "ones" of  $\frac{\partial^F 1}{\partial x_i} \cdot x_i$  (or  $\frac{\partial^F 1}{\partial \overline{x}_i} \cdot \overline{x}_i$ ) for all line.

Hence the "ones" of  $(\alpha_i x_i + \beta_i x_i)$ ,  $1 \le i \le n$ , are also the "ones" of  $F_1$ . Hence the "ones" of  $\int_1 dH$  are the "ones" of  $F_1$ .

Arguing on a similar basis, we can establish the following lemma.

Lemma 5.2: If the differential expression  $dH = \sum_{i=1}^{n} (\alpha_i dx_i + \beta_i d\overline{x}_i) \qquad (L5.2.1)$

is compatibly integrable and  $F_1(\underline{x})$  is a compatible integral of dH, then the "ones" of  $\int_O dH$  are "zeroes" of  $F_1$ . Proof: The proof is similar to that of Lemma 5.1.

10.

Theorem 5.1: A necessary condition for compatible integrability of the differential expression

$$dH = \frac{\Sigma_{1}}{\Sigma_{1}} \left( \alpha_{i} dx_{i} + \beta_{i} d\overline{x}_{i} \right)$$

(T5.1.1)

is that

$$(\int_{0} dH)$$

.  $(\int_{1} dH) = 0$  (T5.1.2)

for all  $x \in B(n)$ .

Proof: Suppose dH is compatibly integrable so that there exists  $F_1(\underline{x})$  such that

$$F_1 = \int_C dH$$

(T5.1.3)

Also, suppose that there exists bo such that

$$[(\int_{0} dH) \cdot (\int_{1} dH)] = 1$$

(T5.1.4)

which implies that

$$\begin{pmatrix} \int_{O} dH \end{pmatrix} = 1$$

$x = \frac{b_{O}}{2}$

and

$\begin{pmatrix} \int_{O} dH \end{pmatrix} = 1$

(T5.1.5)

$(J_1^{\alpha n}) = \times = \underline{b_0}$ . From Lemma 5.1 and equation (T5.1.6),

$b_0$  is a "one" of  $F_1$ . (T5.1.7)From Lemma 5.2 and equation (T5.1.5), b<sub>o</sub> is a "zero" of F<sub>1</sub> (T5.1.8)

Statements (T5.1.7) and (T5.1.8) contradict each other. Hence there exists no  $b_0 \in B(n)$  that satisfies equation (T5.1.4). Hence equation (T5.1.2) is a necessary condition for dH to be compatibly integrable.

12.

Lemma 5.3: If the differential expression

$$dH = {}^{n}_{D} (\alpha_{i} dx_{i} + \beta_{i} d\overline{x}_{i}) \qquad (L5.3.1)$$

satisfies the equation

$$(\int_{0} dH) \cdot (\int_{1} dH) = 0 \text{ for all } \underline{x} \leq B(n), \qquad (L5.3.2)$$

then

(a)  $\alpha_{i} \int_{1} dH = \alpha_{i} x_{i}, \qquad (L5.3.3)$

(b)  $\alpha_{i} \int_{0} dH = \alpha_{i} \overline{x}_{i}, \qquad (L5.3.4)$

and

(c)  $\alpha_{i} (\int_{0} dH) = \alpha_{i} x_{i}, \qquad (L5.3.5)$

Proof: From Definition 5.4 and equation (L5.3.2) we have

$0 = (\int_{2}^{n} \int_{2}^{n} (\alpha_{i} \alpha_{j} x_{j} + \beta_{j} \overline{x}_{j})) \cdot (\int_{4}^{n} (\alpha_{i} \overline{x}_{i} + \beta_{i} x_{i}))$

$= \int_{1}^{n} \int_{1}^{n} (\alpha_{i} \alpha_{j} \overline{x}_{i} x_{j} + \beta_{i} \alpha_{j} x_{i} x_{j} + \alpha_{i} \beta_{j} \overline{x}_{i} \overline{x}_{j} + \beta_{i} \alpha_{j} \overline{x}_{i} \overline{x}_{j} + \beta_{i} \beta_{j} \overline{x}_{i} \overline{x}_{j} = 0 \qquad (L5.3.7)$

so that  $\alpha_{i} \alpha_{j} \overline{x}_{i} x_{j} = \beta_{i} \alpha_{j} x_{i} x_{j} = \alpha_{i} \beta_{j} \overline{x}_{i} \overline{x}_{j} = \beta_{i} \beta_{j} \overline{x}_{i} \overline{x}_{j} = \beta_{i} \beta_{j} \overline{x}_{i} \overline{x}_{j} = \beta_{i} \beta_{j} \overline{x}_{i} \overline{x}_{j} = 0 \qquad (L5.3.7)$

so that  $\alpha_{i} \alpha_{j} \overline{x}_{i} x_{j} = \beta_{i} \alpha_{j} x_{i} x_{j} = \alpha_{i} \beta_{j} \overline{x}_{i} \overline{x}_{j} = \beta_{i} \beta_{j} \overline{x}_{i} \overline{x}_{j} = 0 \qquad (L5.3.9)$

Now  $\alpha_{i} \int_{1} dH = \alpha_{i} \left( \int_{2}^{n} \alpha_{j} x_{j} + \beta_{j} \overline{x}_{j} \right) \qquad (L5.3.9)$

$= \alpha_{i} x_{i} + \alpha_{i} \beta_{i} \overline{x}_{i} + \frac{n}{j=1} (\alpha_{i} \alpha_{j} x_{j} + \alpha_{i} \beta_{j} \overline{x}_{i} \overline{x}_{j} + \alpha_{i} \beta_{j} \overline{x}_{$

0

• 🎆

Hence using equations (L5.3.8)- (L5.3.10), we get

$$\alpha_{i}\int_{1}^{dH} = \alpha_{i}x_{i} + \alpha_{i}x_{i} \begin{pmatrix} n \\ z \\ j=1 \\ j\neq i \end{pmatrix} (\alpha_{j}x_{j} + \beta_{j}\overline{x}_{j}) = \alpha_{i}x_{i}. \quad (L5.3.3)$$

By interchanging i and j in equation (L5.3.9), we get

$$\alpha_{i} \int_{O}^{dH} = \alpha_{i} \bar{x}_{i} . \qquad (L5.3.4)$$

Now

$$a_{i}(f_{0}dH)$$

=  $a_{i}(1 \oplus f_{0}dH)$

=  $a_{i} \oplus a_{i} \int_{0} dH$

=  $a_{i} \oplus a_{i} \bar{x}_{i}$  (from equation (L5.3.4))

=  $a_{i} x_{i}$ . (L5.3.5)

Q.E.D.

Theorem 5.2: If the differential expression

$$dH = \sum_{i=1}^{n} (\alpha_i dx_i + \beta_i d\overline{x}_i)$$

(T5.2.1)

satisfies equation  $(\int_0 dH) \cdot (\int_1 dH) = 0$  (T5.2.2)

for all  $\underline{x} \in B(n)$  then F given by

Ì

$$F = \int_{1} dH + \Psi(\int_{0} dH)$$

(T5.2.3)

is a compatible integral of dH, where  $\forall$  is an arbitrary function of  $\underline{x}$ .

<u>Proof</u>: ANDing both the sides of equation (T5.2.3) by  $\alpha_i$ , we have

$$x_{i}F = \alpha_{i}\int_{1}^{dH} + \Psi \alpha_{i} \cdot \overline{\int_{0}^{dH}}$$

$$= \alpha_{i}x_{i} + \Psi \alpha_{i}x_{i} \quad (\text{from Lemma 5.3})$$

$$= \alpha_{i}x_{i} \quad (1 + \Psi)$$

$$= \alpha_{i}x_{i} \quad (T5.2.4)$$

Since  $a_i$  is independent of  $x_i$ , then

$$a_{i}\frac{\partial F}{\partial x_{i}} = \frac{\partial (a_{i}F)}{\partial x_{i}}$$

$$= \frac{\partial (a_{i}x_{i})}{\partial x_{i}} \quad (from equation (T5.2.4))$$

$$= a_{i}\frac{\partial x_{i}}{\partial x_{i}} \quad (T5.2.5)$$

$$= a_{i}$$

$$\frac{\partial F}{\partial x_{i}} \ge a_{i}. \quad (T5.2.6)$$

$$Y \quad \frac{\partial F}{\partial x_{i}} \ge \beta_{i}. \quad (T5.2.6)$$

Similarly

Hence by Definition 5.2, F is a compatible integral of dH.

Q.E.D.

Theorem 5.3: A.differential expression

$$dH = \sum_{i=1}^{n} (\alpha_i dx_i + \beta_i dx_i)$$

(T5.3.1)

is compatibly integrable if and only if

$$(\int_{0} dH) \cdot (\int_{1} dH) = 0$$

(T5.3.2)

for all  $\underline{x} \in B(n)$ .

Proof: The proof follows from Theorems 5.1 and 5.2.

14.

A word regarding the arbityary function  $\Psi(\underline{x})$  in equation (T5.2.3) is in order. If sets  $D_0$  and  $D_1$ ,  $\oint \subseteq D_1 \subseteq B(n)$ , i=0 and 1, are bases (Definition 2.2) of functions  $\int_0 dH$  and  $\int_{-1}^{1} dE$ , then every distinct- $\Psi$  would give rise to a distinct compatible integral provided  $\Psi$  is based on a subset (not necessarily proper) of  $D = \overline{D_0 U D_1}$  In fact if  $\Psi$  is based on a subset of D, then the factor ( $\int_0 dH$ ) that is ANDed with  $\Psi$  in equation (T5.2.3) may be dropped since  $\overline{D_0 > D_0 U D_1} = D$ . Hence we can modify Theorem 5.2 as shown in the next theorem.

Theorem 5.4: Let

$$dH = \sum_{i=1}^{n} (\alpha_i dx_i + \beta_i d\overline{x}_i)$$

(T5.4.1)

be a differential expression.

If (a)

$$\int_{0} dH$$

.  $\int_{1} dH = 0$  for all  $\underline{x} \in B(n)$ , (T5.4.2)

(b)  $D_{0}$  and  $D_{1}$  are bases of  $\int_{0} dH$  and  $\int_{1} dH$  respectively,

(c) the number of distinct points in the set  $D = \overline{(D_0 U D_1)} \text{ is m}, \quad (T5.4.3)$

(d)

$$\theta_{i}(\underline{x})$$

,  $1 \le i \le 2^{m}$ , is a function based on a subset of

$D, \theta_{i}(\underline{x}) \ne \theta_{j}(\underline{x})$  for all  $i, j, i \ne j, 1 \le j \le 2^{m}$  and

(e)  $F_{i} = \int_{1} dH + \theta_{i}$ . (T5.4.4)

then F, is a compatible integral of dH.

<u>Proof</u>: The essence of the proof is outlined in the discussion preceding the theorem. A formal proof can be given using the Tapia-Tucker method [36, 37] for obtaining the complete solution for Boolean equations. We will, now, show an application of the results established in this section, to synthesis of a clock function illustrated in the next example.

## Example 5.1

A clock function  $C(x_1, x_2, x_3)$  is to be realized which goes through, at least, the transitions specified in the differential expression

$$dC = (x_2 \overline{x}_3 + \overline{x}_2 x_3) dx_1 + (x_1 \overline{x}_3) dx_2 + (x_1 x_3) d\overline{x}_2 + (x_1 \overline{x}_2) dx_3 + (x_1 x_2) d\overline{x}_3 (E5.1.1)$$

Find C, if it exists.

We have

and

$$\int_{0} dC = (\bar{x}_{1} x_{2} \bar{x}_{3} + \bar{x}_{1} \bar{x}_{2} x_{3}) + x_{1} \bar{x}_{2} \bar{x}_{3}$$

$$+ x_{1} x_{2} x_{3} + x_{1} \bar{x}_{2} \bar{x}_{3} + x_{1} x_{2} x_{3}$$

$$= \bar{x}_{1} x_{2} \bar{x}_{3} + \bar{x}_{1} \bar{x}_{2} x_{3} + x_{1} \bar{x}_{2} \bar{x}_{3} + x_{1} x_{2} x_{3}$$

$$= x_{1} x_{2} \bar{x}_{3} + x_{1} \bar{x}_{2} x_{3} + x_{1} \bar{x}_{2} \bar{x}_{3} + x_{1} \bar{x}_{2} x_{3}$$

$$= x_{1} x_{2} \bar{x}_{3} + x_{1} \bar{x}_{2} x_{3}.$$

(E5.1.2)

$$(E5.1.2)$$

$$= x_{1} x_{2} \bar{x}_{3} + x_{1} \bar{x}_{2} x_{3} + x_{1} \bar{x}_{2} \bar{x}_{3} + x_{1} \bar{x}_{2} x_{3}$$

$$= x_{1} x_{2} \bar{x}_{3} + x_{1} \bar{x}_{2} x_{3}.$$

(E5.1.3)

Obviously

$$(\int_{O} dC) \cdot (\int_{1} dC) = 0.$$

(E5.1.4)

Hence by Theorem 5.3, a compatible integral does exist.

Also, the term D referred to in equation (T5.4.3) is

$D = \{\overline{D_0 U D_1}\}$ = {(0,0,1), (0,1,0), (1,0,0), (1,0,1), (1,1,0), (1,1,1)}

$= \{ (0,0,0), (0,1,1) \}$ (E5.1.5)

Thus  $\theta_{i}(\underline{x})$ ,  $i \leq i \leq n$ , can be constructed as follows

$\theta_1(\underline{x}) = 0 \tag{E5.1.6}$

$$\theta_2(\mathbf{x}) = \bar{\mathbf{x}}_1 \bar{\mathbf{x}}_2 \bar{\mathbf{x}}_3$$

(E5.1.7)

$$3^{(\underline{x})} = \overline{x}_1 x_2 x_3$$

(E5.1.8)

$$\theta_4(\underline{x}) = \bar{x}_1 \bar{x}_2 \bar{x}_3 + \bar{x}_1 x_2 x_3$$

(E5.1.9)

Also note that there are four solutions by Theorem 5.4:

$$c_1 = \int_1 dc + \theta_1 = x_1 x_2 \overline{x}_3 + x_1 \overline{x}_2 x_3$$

(E5.1.10)

$$c_2 = x_1 x_2 \overline{x}_3 + x_1 \overline{x}_2 x_3 + \overline{x}_1 \overline{x}_2 \overline{x}_3$$

(E5.1.11)

$$C_3 = x_1 x_2 \overline{x}_3 + x_1 \overline{x}_2 x_3 + \overline{x}_1 x_2 x_3$$

(E5.1.12)

and

$$C_4 = x_1 x_2 \overline{x}_3 + x_1 \overline{x}_2 x_3 + \overline{x}_1 \overline{x}_2 \overline{x}_3 + \overline{x}_1 \overline{x}_2 \overline{x}_3 + \overline{x}_1 \overline{x}_2 \overline{x}_3$$

Observe that

13

$$dC_{1} = (x_{2} \oplus x_{3}) dx_{1} + (x_{1}\overline{x}_{3}) dx_{2} + (x_{1}x_{3}) d\overline{x}_{2}$$

+  $(x_{1}\overline{x}_{2}) dx_{3} + (x_{1}x_{2}) d\overline{x}_{3}$  (E5.1.14)

= dC (E5.1.15)

Hence  $C_1$  realizes all the transitions specified in dC and no transitions which are not specified in dC. In fact by Definition 5.2,  $C_1$  is also the exact integral of dC in equation (E5.1.1). Let us now examine  $C_2$ .

$$dc_{2} = (x_{2} \oplus x_{3}) dx_{1} + (\overline{x}_{2}\overline{x}_{3}) d\overline{x}_{1} + (x_{1}\overline{x}_{3}) dx_{2} + (x_{1}x_{3} + \overline{x}_{1}\overline{x}_{3}) d\overline{x}_{2} + (x_{1}\overline{x}_{2}) dx_{3} + (x_{1}x_{3}) \overline{x}_{1}\overline{x}_{2} + (x_{1}\overline{x}_{2}) dx_{3} + (x_{1}x_{3}) \overline{x}_{1}\overline{x}_{2} + (x_{1}\overline{x}_{2}) d\overline{x}_{3}$$

(E5.1.16)

17.

(E5.1.13)

Observe that  $C_2$  realizes the transitions represented by differential terms  $\overline{x}_2 \overline{x}_3 d\overline{x}_1$ ,  $\overline{x}_1 \overline{x}_3 d\overline{x}_2 \in \overline{x}_1 \overline{x}_2 d\overline{x}_3$  which are not specified in dC in equation (E5.1.1). However it does realize all the transitions specified in dC.

As shown above, a differential expression that is exactly integrable is, also, compatibly integrable. Hence the necessary condition that

$(\int_{0} dH) \cdot (\int_{1} dH) = 0$ for all  $\underline{x} \in B(n)$ for  $dH = \sum_{i=1}^{n} (\alpha_{i} dx_{i} + \beta_{i} d\overline{x}_{i})$

$\frac{1}{i=1}$

to be compatibly integrable is also necessary for dH to be exactly integrable. It can be shown that the condition is not sufficient for the differential expression to be exactly integrable.

Preliminary results pertaining to necessary and sufficient conditions for a differential expression to be exactly integrable are given in a recent publication [3]. Additional results on Boolean integrals have been developed and will be published in the near future.

Given a differential expression

if  $(\int_{0} dH0 \cdot (\int_{1} dH) \neq 0$  for some  $\underline{b} \in B(n)$ , then the expression cannot be integrated exactly nor compatibly. However it could be decomposed as sum of several differential expressions, each one of which may be integrable separately as defined below. Definition 5.5 : Let  $dH_j$ ,  $1 \le j \le k$  be a set of Boolean differential expressions given by

$$dH_{j} = \frac{n}{i=1} [(\alpha_{ji}) dx_{i} + (\beta_{ji}) d\bar{x}_{i}]. \qquad (D5.5.1)$$

Then dH, the Boolean sum of all the differential expressions  $dH_{i}$ ,  $1 \le j \le k$  is defined as

$$dH = \sum_{i=1}^{k} dH_{j} \qquad (D5.5.2)$$

$$= \sum_{i=1}^{n} \left[ \begin{pmatrix} k \\ 2 \\ j=1 \end{pmatrix} dk_{i} + \begin{pmatrix} k \\ 2 \\ j=1 \end{pmatrix} dk_{i} \right] (D5.5.3)$$

Definition 5.6: A differential expression dH is said to be integrable by parts if dH can be written as a sum of Boolean differential expressions dH<sub>j</sub>,  $1 \le j \le k$  as defined in equations (D5.5.1) and (D5.5.3) such that dH<sub>j</sub> is compatibly integrable for all j,  $1 \le j \le k$ . Any compatible integral of dH<sub>j</sub>,  $1 \le j \le k$ , will be called a <u>partial integral</u> of dH. A <u>complete set of partial</u> <u>integrals of Boolean differential expression</u> dH is a set of functions,  $\left\{F_1, F_2, ---, F_k\right\}$  where for all j,  $1 \le j \le k$ ,  $dF_j \ge dH_j$ . (D5.6.1)

Observe that k may assume one or more values between 1 and 2n. It will now be shown that any Boolean differential expression is integrable by parts.

Theorem 5.5: Any differential expression

$$dH = \prod_{\substack{\Sigma \\ i=1}}^{n} (\alpha_i dx_i + \beta_i dx_i)$$

(T5.5.1)

is integrable by parts.

(T5.5.2)

(T5.5.3)

**Proof:** Observe that for any i,  $1 \le i \le n$ ,

$$(\int_{\mathbf{1}} \alpha_{\mathbf{i}} d\mathbf{x}_{\mathbf{i}}) \cdot (\int_{\mathbf{0}} \alpha_{\mathbf{i}} d\mathbf{x}_{\mathbf{i}})$$

=  $(\alpha_{\mathbf{i}} \mathbf{x}_{\mathbf{i}}) \cdot (\alpha_{\mathbf{i}} \mathbf{\overline{x}}_{\mathbf{i}})$

and

$$\int_{1} \beta_{i} d\bar{x}_{i} \cdot (\int_{0} \beta_{i} d\bar{x}_{i})$$

(T5.5.2)

so that  $dH_{1, i}$  and  $dH_{2, i}$  given by

$$dH_{1,i} = \alpha_i dx_i$$

and  $dH_{2,i} = \beta_i dx_i$  (T5.5.4)

are compatibly integrable by Theorem 5.3 for all i,  $1 \le i \le n$ .

In view of the fact that we can write dH as

$$dH = \sum_{i=1}^{n} (dH_{1,i} + dH_{2,i}), \quad (T5.5.5)$$

dH is compatibly integrable by Definition 5.6.

Q.E.D.

## 6. APPLICATION TO SYNTHESIS

As shown by Smith and Roth [34], techniques for synthesizing fundamental-mode asynchronous systems utilizing edge-sensitiveness property of clock-triggered flipflops often require fewer flipflops and gates than conventional techniques do.

The Smith and Roth technique [34, 35] requires a generalized edge-sensitive flipflop (as defined in [35]) in their design. We will present a procedure for synthesis of a fundamental-mode asynchronous system that uses a commercially available clocktriggered flipflop.

# EXAMPLE 6.1

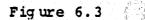

A sequential system with two inputs,  $X_1$  and  $X_2$  and one output, Z is to be designed such that whenever  $X_1$  changes from 0 to 1 the output changes to 1 if the output is 0. The output remains at 1 regardless of the values of  $X_1$  till  $X_2$  changes from 0 to 1. When  $X_2$  changes from 0 to 1, Z goes to 0. After that Z = 0, regardless of the value of  $X_1$ , till, of course, a positive change in  $X_1$  changes the value of Z to 1. Assume that  $X_1=X_2=Z=0$  initially. Taking the conventional approach, we obtain the following reduced flow table for the system.

| X, X  | 2 |     | 01  |               | 1.0              |          |

|-------|---|-----|-----|---------------|------------------|----------|

| (A,B) | 1 | 00  | Φ,0 |               | <u>10</u><br>2,- |          |

| (C,F) |   | · · | 1,- | 4,-           | <b>(2)</b> , 1   | <b>ן</b> |

| (D,G) |   |     |     |               |                  | 1        |

| (E,H) | 4 | 1,- | 1,- | <b>()</b> , 0 | <b>(4)</b> , 0   | ]        |

Figure 6.1

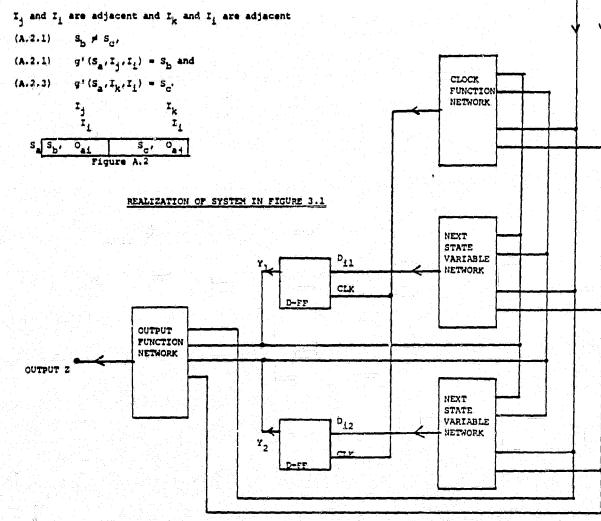

Since the minimal system shown in Figure 6.1 has 4 states, 2 flipflops will be required to realize the system.

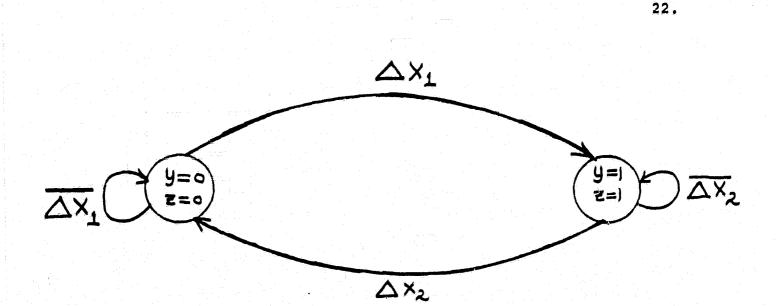

Now it will be shown that if edge-sensitive flipflops are used, one flipflop will be adequate to realize the system. The system under consideration can be described in terms of the state diagram given in Figure 6.2. The symbol  $\Delta X_i$ , i=1 or 2, implies a change in  $X_i$  from 0 to 1.  $\Delta X_i = 1$  if and only if  $X_i$  changes from 0 to 1.  $\Delta X_i = 0$  otherwise. The transition along a directed branch occurs if and only if the variable associated with it assumes the value of 1.

21.

Figure 6.2

Observe that the system must change its state whenever

(a) y=0 and  $X_1$  changes from 0 to 1

or (b) y=1 and  $X_2$  changes from 0 to 1.

÷,

Hence the clock input function, C, must go through a positive transition when any of the changes stated above occurs. These transitions in terms of changes in  $X_1$  and  $X_2$  are described by the differential expression

$$dC = \bar{y}dx_1 + ydx_2$$

. (E6.1.1)

Note that

$$\int_{0} dC \cdot \int_{1} dC = (\bar{y}\bar{x}_{1} + y\bar{x}_{2}) \cdot (\bar{y}\bar{x}_{1} + y\bar{x}_{2}) = 0$$

(E6.1.2)

so that by Theorem 5.3, dC is compatibly integrable and a compatible "integral, say  $C_1$ , of dC is

$$C_1 = \bar{y}x_1 + yx_2$$

(E6.1.3)

In fact since  $\overline{D_0 UD_1} = \emptyset$  (empty set) (E6.1.4) ( $D_0 \in D_1$  defined in Theorem 5.4), by Theorem 5.4 no other compatible integral of dC exists. Let  $C = C = \overline{yx_1} + yx_2$  (E6.1.5) so that  $Q_1(T+) = 1$ . On the other hand if  $Q_1(T+) = 1$ due to a transition  $m_u(\underline{x} - x_v)$  when  $\underline{y} = S_1$ , then  $D_1 = 1$ and  $F(\underline{x}) = 1$  for  $\underline{x} = b_u$  and equation (T6.1.6) implies that  $F(\underline{x}) = 1 = F(\underline{x}) \cdot x_{i1} \quad x_{ik}$  when  $\underline{x} = b_u$ , which implies that  $(x_{i1} \cdot \cdots \cdot x_{ik}) = 1$  when  $\underline{x} = b_u$ . Hence when  $\underline{x} = b_{u,c}$   $\underline{y} = S_1$ ,  $D = D_1 \cdot (x_{i1} \cdot \cdots \cdot x_{ik})$  $= 1 \cdot (\underline{4})$

Hence  $Q(\pi \rightarrow)$  and  $Q_1(\pi +)$  have identical values immediately after any transition.

Q.E.D.

<u>Theorem 6.2</u>: Theorem 6.1 is valid if equations (T6.1.2) (T6.1.4)are replaced by equations (T6.2.2) and (T6.2.4) respectively as given below:

(T6.2.2)  $D = D_1 \cdot \overline{x_{i1}} \cdot \overline{x_{i2}} \cdot \dots \cdot \overline{x_{ik}}$

(T6.2.4)  $F(\underline{x}) = \overline{x}_{i1} \cdot \overline{x}_{i2} \cdot \cdots \cdot \overline{x}_{ik} F(\underline{x})$ .

The next-value functions for different types of flipflops (other than D-type) are currently under study. The results will be reported when the study is completed.

# 7. <u>CONCLUSION</u>

Boolean calculus was developed and formalized with the specific purpose of applying it to digital system synthesis. A procedure was developed to synthesize fundamental mode asynchronous systems using commercially available clock-triggered flipflops and Boolean calculus. It has been shown that synthesis techniques which utilize edge-sensitive property of flipflops judiciously lead to realizations which often require fewer flipflops and logic gates than those obtained by conventional techniques, thus reducing network complexity, size, the number of IC packages, power requirement, cost etc.

It has been established that any fundamental-mode asynchronous (FMA) system can be realized employing the new synthesis procedure proposed here. The procedure is applicable even when unit-distance state assignment is not used. However, in such a case certain relationships among the time response characteristics of the flipflops must be satisfied, which need to be obtained.

It has been shown that the procedure can be extended to synthesis of FMA system using a synchronous presettable counter. Again unit-distance state assignment is not required in this case.

The possibility of using the "dc" inputs of the flipflops in the synthesis procedure has been shown in the Semi-Annual Status Report #3 [14].

The concept of noncombinational Boolean calculus has been introduced. The next-value functions for flipflops are defined in terms of changes in the inputs. The reverse problem of

- 27 -

- 28 -

synthesis is also considered. Considerable work remains to be done in this area.

Establishment of conditions for exact integrability, composition of differential functions, multi-variable-change calculus, methods of augmenting non-realizable DM tables so as to make them realizable, application to fault location and detection, etc. are among the many problems that remain to be solved.

The new results in Boolean calculus as well as the synthesis techniques developed here has opened an avenue for a large class of synthesis problems in which the components used are edgesensitive and therefore present the potential of various economies if the edge-sensitiveness property is judiciously taken advantage of.

The publications that resulted from the research grant are listed next.

# 8. PUBLICATIONS GENERATED BY THE GRANT

- (1) "Boolean Integral Calculus for Digital Systems", revised and submitted to IEEE Computer Transactions.

- (2) "Development of Boolean Calculus and Its Applications", NASA

Langley Basic Research Review Conference, Hampton, Va.

April 1978.

- <u>.</u>.

(3) "Application of Boolean Calculus to Digital System Design",IEEE Southeastcon, Nashville, Tenn. April 14-16, 1980.

(4) Invited to present "Design of Asynchronous System Using a Synchronous presettable Counter", Southeastern Symposium on System Theory, Virginia Beach May 19-20, 1980.

(5) "Synthesis of Asynchronous Sequential Systems Using Edge-

sensitive Flipflops", under preparation.

- 29 -

## REFERENCES

13

- 1. J.H. Tucker, "A Transition Calculus for Boolean Functions", Ph.D. Dissertation, Department of Electrical Engineering, Virginia Polytechnic Institute and State University, Blacksburg, Virginia, May 1974.

- J.H. Tucker and A.W. Bennett, "A Transition Calculus for Boolean Functions", Proceedings of IEEE Southeast-Conf., Orlando, Florida; pp. 296-299, April 1974.

- 3. J.H. Tucker, M.A. Tapia and A.W. Bennett, "Boolean Integration", Proceedings of IEEE Southeast-Conf., Clemson, South Carolina, April 1976.

- . S.B. Akers, "On a Theory of Boolean Functions", J. Soc. Ind. Appl. Math., Vol. 7, pp. 487-498, Dec. 1959.

- 5. F. F. Sellers, M.Y. Hsiao and L.W. Bernson, "Analyzing Errors with the Boolean Difference", IEEE Trans. Computer, Vol. C-17, pp. 676-683, July 1968.

- 6. P.N. Marionos, "Derivation of Minimal Compete Sets of Test-Input Sequences Using Boolean Differences", IEEE Trans. Computer, Vol. C-20, pp. 25-32, Jan. 1971.

- 7. L.W. Bernson and C.C. Carroll, "On the Design of Minimal Length Fault Tests for Combinational Circuits", IEEE Trans. Computer, Vol. C-21, pp. 189-195, February 1972.

- 8. A. Thayse and M. Davio, "Boolean Differential Calculus and Its Application to Switching Theory", IEEE Trans. Computer, Vol. C-22, pp. 409-420, April 1973.

- 9. A.D. Talantsev, "On the Analysis and Synthesis of Certain Electrical Circuits by Means of Special Logical Operators", Automat, Telehekh, Vol. 20, No. 7, pp. 898-907, 1959.

- 10. A. Brown and H. Young, "Toward an Algebraic Theory of the Analysis and Testing of Digital Networks", Paper No. V11G-4, A AAs and ORS Annual Meeting, June 17-20, 1969, Denver, Colorado.

- 11. J.R. Smith, Jr. and C.H. Roth, Jr., "Analysis and Synthesis of Asynchronous Sequential Networks Using Edge-Sensitive Flipflops", IEEE Trans. Computer, Vol. V-20, pp. 847-855, August, 1971.

- 12. Wood, "Switching Theory", McGraw-Hill, 1968.

- 13. Zi Kohavi, "<u>Introduction to Switching and Finite Automata</u> <u>Theory</u>", 1970.

10

- 14. M.A. Tapia, Semi-Annual Report No. 1, "Development of Boolean Calculus and Its Applications", NASA Grant No. 1436, February 1978, University of Miami, Florida.

- 15. M.A. Tapia, Semi-Annual Report No. 2, "Development of Boolean Calculus and Its Applications", NASA Grant No. 1436, August 1978, University of Miami, Florida.

- 16. M.A. Tapia, Semi-Annual Report No. 3, "Development of Boolean Calculus and Its Applications", NASA Grant No. 1436, February 1979, University of Miami, Florida.

- 17. M.A. Tapia, Semi-Annual Report No. 4, "Development of Boolean Calculus and Its Applications", NASA Grant No. 1436, October 1979, University of Miami, Florida.

- 18. M.A. Tapia, Semi-Annual Report No. 5, "Development of Boolean-Calculus and Its Applications", NASA Grant No. 1436, April 1980, University of Miami, Florida.

•

19. T.R. Blakeslee, "Digital Design with Standard MSI and LSI", John Wiley & Sons, Inc.

0

0

3

0

# Appendix I

# BOOLEAN INTEGRAL CALCULUS FOR DIGITAL SYSTEMS

# ABSTRACT

The concept of Boolean integration is introduced and developed. When the changes in a desired function are specified in terms of changes in its arguments, then ways of "integrating" (i.e. realizing) such as a function, if it exists, are presented. Properties of newly defined integral operators are studied. Boolean Calculus has applications in design of logic circuits and in fault analysis. In the former case, it often leads to circuits which utilize fewer flipflops and logic gates than conventional methods.

INDEX TERMS: Boolean algebra, Boolean calculus, direct and inverse partial derivatives, Boolean differential, decompostion of function, Boolean differential expression, Boolean integration, compatible integral, exact integral, integration by parts, edge-sensitive flipflop, asynchronous sequential system synthesis.

## 1. INTRODUCTION

2.

In recent years concepts of Boolean differentiation, difference, derivatives, differential and other logical operators have been introduced, developed and applied to digital network analysis and testing  $\begin{bmatrix} 6-27 \end{bmatrix}$ . Also there has been a growing interest in Boolean integration and its application to synthesis of various types of logic circuits  $\begin{bmatrix} 1-5, 28-35 \end{bmatrix}$ . The use of Boolean calculus in design of asynchronous sequential circuit with edge-sensitive flipflops often leads to simpler circuits utilizing fewer components than conventional techniques  $\begin{bmatrix} 5, 34, 35 \end{bmatrix}$ .

## 2. BOOLEAN FUNCTION AND ITS BASE

Throughout the paper, unless stated otherwise, a Boolean function  $F(x_1, x_2, --- x_n)$  of n Boolean variables  $x_1, x_2$ , ---,  $x_n$  will be assumed. Also, it will be assumed that only one variable  $x_i$ ,  $1 \le i \le n$ , can change at a time. Definition 2.1: The set of  $2^n$  binary vectors or points  $(x_1, x_2, ---, x_n)$  where  $x_i=0$  or 1,  $1 \le i \le n$ , such that  $x_i$  and  $x_j$  may or may not be equal if  $i \ne j$ , will be called the <u>Boolean</u> st of variables  $x_1, x_2, ---, x_n$ , denoted by B(n). The Boolean set of (n-1) variables  $x_1, x_2, ---, x_{i-1}, x_{i+1}, ---, x_n$ , written  $x/x_i$ , will be denoted by B(n/i). Definition 2.2: Given a set  $S, \phi \subseteq S \subseteq B$  (n), a function  $F(\underline{x})$ is said to be based on the set S provided  $F(\underline{x}) = 1$  if and only if  $\underline{b} \in S$ .  $\underline{x}=\underline{b}_{\underline{0}}$

On the other hand, if a function  $F(\underline{x})$  is given, then the set  $S = \left\{ \underline{b} \mid \underline{b} \in B(n) \text{ and } F(\underline{b}) = 1 \right\}$  is called the base of the function  $F(\underline{x})$  and denoted by BASE  $\left\{ F(\underline{x}) \right\}$ .

3. BOOLEAN DIFFERENTIATION

3.

In order to study the effect of change in a variable  $x_i$ , on a function  $F(\underline{x_1}, x_2, \dots, x_n)$  we introduce the concept of decomposition.  $F(\underline{x})$  can be decomposed with respect to  $x_i$ ,

l<i<n, as the sum of 3 functions as

$$P = P_i x_i + Q_i \bar{x}_i + R_i \qquad (3.0.1)$$

such that  $P_i$ ,  $Q_i$  and  $R_i$  are independent of  $x_i$  and

$P_{i}Q_{i} = P_{i}R_{i} = Q_{i}R_{i} = 0$  (3.0.2)

<u>Definition 3.1</u>: A function F that is decomposed as stated above, is said to be the decomposition of F with respect to  $x_i$ ,  $1 \le i \le n$ .

It can be shown that the decomposition of F with respect to  $x_i$ ,  $1 \le i \le n$ , is unique. For any point x with  $x/x_i \in BASE \left\{ P_i \right\}$  $1 \le i \le n$ ,

$F(x) = 1.x_{i} + 0.\overline{x_{i}} + 0 = x_{i} \qquad (D3.1.1)$ so that  $F(\underline{x})$  has the same value as  $x_{i}$  and therefore changes the same way as  $x_{i}$ . Definition 3.2: The direct (or inverse) partial derivative of  $F(\underline{x})$  with respect to  $x_i$ ,  $1 \le i \le n$ , denoted by  $\frac{\partial F}{\partial x_i}$  (or  $\frac{\partial F}{\partial \overline{x}_i}$ ) is  $\frac{\partial F}{\partial x_i}$

defined as a function of (n-1) variables  $x_1, x_2, \dots, x_{i-1}, x_{i+1}, \dots, x_n$  that is based on the union of all possible points  $\underline{x}/x_i$  in the set E(n/i) such that

$F(x) = x_i \text{ (or } \bar{x}_i) \text{ (D3.2.1)}$

The concept of partial derivatives has been reported earlier [33]. We will show some relationships involving the partial derivatives in the following theorem.

<u>Theorem 3.1</u>: The direct and inverse partial derivatives of a function  $F(\underline{x})$  with respect to  $x_i$ ,  $1 \le i \le n$  satisfy the following relationships:

$$\frac{\partial F}{\partial x_{i}} = P_{i} = (F(\underline{x}) | x_{i} = 1) \cdot (F(\underline{x}) | ) = \frac{\partial F}{\partial \overline{x}_{i}} (T3.1.1)$$

$$\frac{\partial F}{\partial \overline{x}_{i}} = Q_{i} = (F(\underline{x}) | x_{i} = 0) \cdot (F(\underline{x}) | ) = \frac{\partial F}{\partial x_{i}} (T3.1.2)$$

$$\frac{\partial F}{\partial \overline{x}_{i}} \cdot \frac{\partial F}{\partial \overline{x}_{i}} = 0 \quad (T3.1.3)$$