# NOTICE

THIS DOCUMENT HAS BEEN REPRODUCED FROM MICROFICHE. ALTHOUGH IT IS RECOGNIZED THAT CERTAIN PORTIONS ARE ILLEGIBLE, IT IS BEING RELEASED IN THE INTEREST OF MAKING AVAILABLE AS MUCH INFORMATION AS POSSIBLE

# JPL PUBLICATION 80-73

(NASA-CR-163986) FAULT-TOLERANT COMPUTER N STUDY Final Report (Jet Propulsion Lab.) 238 p HC A11/MF A01 CSCL 09B

N81-18675

Unclas G3/60 41574

# Fault-Tolerant Computer Study Final Report

David A. Rennels Algirdas A. Avizienis Milos D. Ercegovac

February 1, 1981

National Aeronautics and Space Administration

Jet Propulsion Laboratory California Institute of Technology Pasadena, California

# Fault-Tolerant Computer Study

# **Final Report**

David A. Rennels Algirdas A. Avizienis Milos D. Ercegovac

February 1. 1981

National Aeronautics and Space Administration

Jet Propulsion Laboratory California Institute of Technology Pasadena. California The research described in this publication was carried out by the Jet Propulsion Laboratory, California Institute of Technology, and was sponsored by the Naval Ocean Systems Center, San Diego, California, through an agreement with NASA.

1

Ì

#### ABSTRACT

This report describes a set of building-block circuits which can be used with commercially available microprocessors and memories to implement fault-tolerant distributed computer systems. Each building-block circuit is intended for VLSI implementation as a single chip. Several building blocks and associated processor and memory chips form a self-checking computer module with self-contained input output and interfaces to redundant communications buses. Fault tolerance is achieved by connecting self-checking computer modules into a redundant network in which backup buses and computer modules are provided to circumvent failures.

Included in the report is a discussion of the requirements and design methodology which led to the definition of the buildingblock circuits. This is followed by a set of logic designs for three of the building blocks. These are designs which are being used to construct a laboratory breadboard of a self-checking computer module. The logic designs will be modified and improved as the breadboard is debugged and tested. Further refined designs will become available when the breadboard is completed and tested and again, hopefully, when the VLSI devices are fabricated.

#### ACKNOWLEDGMENT

This study was initiated by the Naval Ocean Systems Center, Code 923, and represents a facet of a block-funded program entitled Integrated Circuit Technology, sponsored by the Naval Electronics Systems Command, Technology Division. The work was performed by agreement with NASA under Contract NAS7-100 at the Jet Propulsion Laboratory of the California Institute of Technology. This program is continuing under NASA sponsorship, and related system studies are being conducted at the University of California, Los Angeles under sponsorship of the Office of Naval Research.

1

١١

A special acknowledgment is due to Reeve Peterson of NOSC for his continued support and encouragement of this effort. We are also indebted to Dick Urban and Ed Holland of NOSC for their guidance and support.

For the continuing effort, which involves the detailed design and implementation of an engineering model of this work, an acknowledgment is owed to Lee Holcomb of the NASA Office of Aeronautics and Space Technology for his support.

An additional acknowledgment is due Jim Bryden of JPL whose help was invaluable in carrying out this study and bringing this final report to parturition.

## **CONTENTS**

5

Beern Bach .

| 1     | SURMARY AND OVERVIEW                              | 1-1  |

|-------|---------------------------------------------------|------|

| 1.1   | SYSTEM REQUIREMENTS                               | 1-1  |

| 1.2   | BUILDING-BLOCK COMPUTER REQUIREMENTS              | 1-2  |

| 1.3   | DESIGN APPROACH                                   | 1-3  |

| 1.4   | THE BUILDING-BLOCK CIRCUITS                       | 1-6  |

| 1.4.1 | The Memory-Interface Building Block (MIBB)        | 1-6  |

| 1.4.2 | The Core Building Block (Core-BB)                 | 1-6  |

| 1.4.3 | The Bus-Interface Building Block (BIBB)           | 1-6  |

| 1.4.4 | 1/0 Building Block (10BB)                         | 1-7  |

| 1.5   | SCCM PROPERTIES                                   | 1-7  |

| 1.6   | THE DISTRIBUTED COMPUTER (SCCM) ARCHITECTURE      | 1-8  |

| 1.7   | SUMMARY                                           | 1-10 |

| 1.8   | REPORT OUTLINE                                    | 1-10 |

| 2     | THE CONCEPTS OF FAULT-TOLERANT COMPUTING          | 2-1  |

| 2.1   | APPROACHES TO THE FAULT PROBLEM                   |      |

| 2.1.1 | Tolerance and Avoidance: Complementary Approaches |      |

|       | to the Fault Problem                              | 2-5  |

| 2.1.2 | Classes of Physical Faults                        | 2-7  |

| 2.2   | TOLERANCE OF PHYSICAL FAULTS                      | 2-10 |

| 2.2.1 | Fault Masking                                     | 2-10 |

| 2.2.2 | Fault Detection                                   | 2-12 |

| 2.2.3 | Recovery                                          | 2-15 |

| 2.3   | FAULT-TOLERANT SYSTEMS                            | 2-17 |

| 2.3.1 | Hardware-Controlled Recovery Systems              | 2-18 |

| 2.3.2 | Software-Controlled Recovery Systems              | 2-19 |

v

| 2.3.3 | Fault-Tolerant Subsystems                                           | 2-21 |

|-------|---------------------------------------------------------------------|------|

| 2.4   | MODELING AND ANALYSIS                                               | 2-22 |

| 2.4.1 | Analytic Modeling: Permanent Faults                                 | 2-23 |

| 2.4.2 | Analytic Modeling: Transient Faults                                 | 2-33 |

| 2.4.3 | Heuristic Approaches: Simulation and Experiments                    | 2-41 |

| 2.5   | TOLERANCE OF MAN-MADE FAULTS                                        | 2-42 |

| 2.5.1 | Design Faults                                                       | 2-43 |

| 2.5.2 | Interaction Faults                                                  | 2-46 |

| 2.6   | CURRENT PROBLEMS AND PROSPECTS FOR THE FUTURE                       | 2-47 |

| 2.6.1 | Reasons for Fault-Tolerance                                         | 2-47 |

| 2.6.2 | A Design Methodology                                                | 2-48 |

| 2.6.3 | Current Roadblocks                                                  | 2-49 |

| 2.6.4 | Goals and Prospects                                                 | 2-51 |

| 3     | OBJECTIVES AND ARCHITECTURE SELECTION                               | 2-1  |

| •     |                                                                     | 3-1  |

| 3.1   | REQUIREMENTS FOR FAULT-TOLERANT BUILDING-BLOCK<br>COMPUTERS (FTBBC) | 2_2  |

| _     |                                                                     |      |

| 3.2   | DISTRIBUTED COMPUTERS                                               |      |

| 3.3   | THE DISTRIBUTED COMPUTER MODEL                                      | 3-7  |

| 3.3.1 | The Intercommunication Bus Structure                                | 3-10 |

| 3.4   | FAULT-TOLERANCE OPTIONS                                             | 3-11 |

| 3.4.1 | The Terminal Modules                                                | 3-11 |

| 3.4.2 | The High-Level Modules                                              | 3-12 |

| 3.4.3 | The Intercommunication Bus System Requirements                      | 3-13 |

| 3.4.4 | Architecture Selection                                              | 3-14 |

| 3.5   | BUILDING-BLOCK DEFINITION                                           | 3-15 |

| 3.5.1 | The Self-Checking Computer Module (SCCM)                            | 3-15 |

÷À.

54 (A.S.)

١

vi

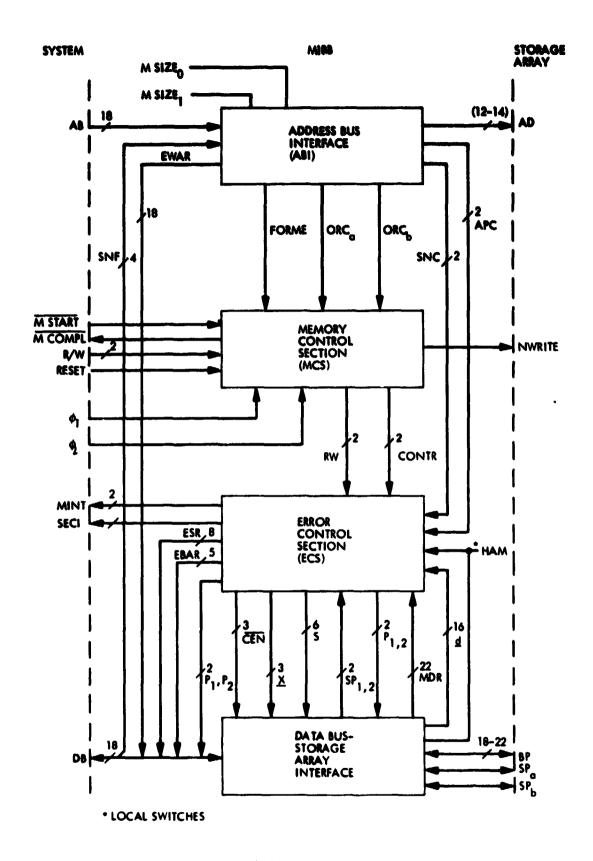

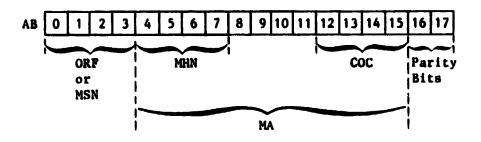

| 3.5.2            | The Memory Interface Building Block (MIBB)   | 3-18  |

|------------------|----------------------------------------------|-------|

| 3.5.3            | The Core Building Block (Core-BB)            | 3-21  |

| 3.5.4            | The Bus Interface Building Block (BIBB)      | 3-23  |

|                  |                                              |       |

| 4                | BUILDING-BLOCK DESCRIPTIONS                  | 4-1   |

| 4.1              | THE MEMORY INTERFACE BUILDING BLOCK          | 4-1   |

| 4.1.1            | Memory Interface Building-Block Requirements | 4-1   |

| 4.1.2            | Memory Interface Building-Block Design       | 4-3   |

| 4.1.3            | Error Control Capabilities                   | 4-20  |

| 4.1.4            | Design of Memory Interface Building Block    | 4-24  |

| 4.1.5            | Estimated Complexity of Implementation       | 4-51  |

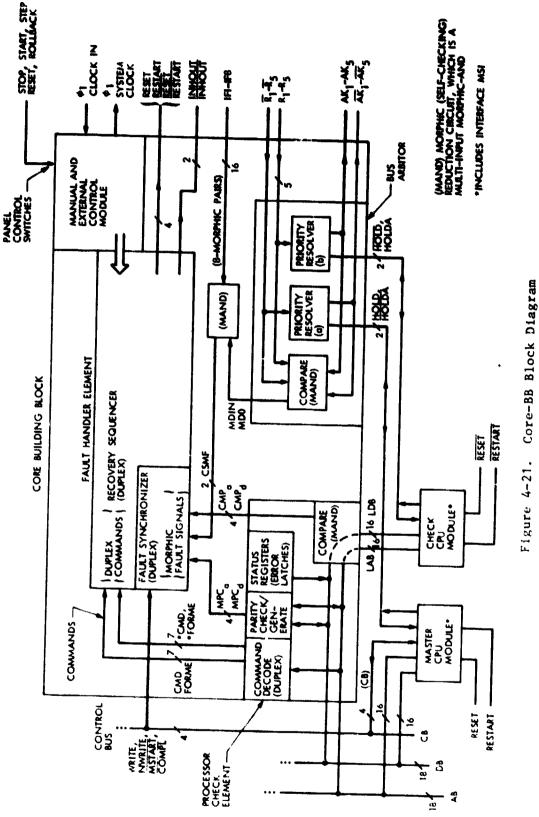

| 4.2              | THE CORE BUILDING BLOCK                      | 4-52  |

| 4.2.1            | Core Building Block Requirements             | 4-52  |

| 4.2.2            | Core Building Block Implementation           | 4-55  |

| 4.3              | THE BUS INTERFACE BUILDING BLOCK (BIBB)      | 4-71  |

| 4.3.1            | Bus System Requirements                      | 4-71  |

| 4.3.2            | Bus Controller Functions                     | 4-76  |

| 4.3.3            | Bus Adaptor Functions                        | 4-79  |

| 4.3.4            | BIBB Implementation                          | 4-82  |

| 4.3.5            | BIBB Microprograms                           | 4-114 |

| BIBLIOGRAPHY 5-1 |                                              |       |

| APPENDIX         |                                              | A-1   |

| Figures          |                                              |       |

# Figures

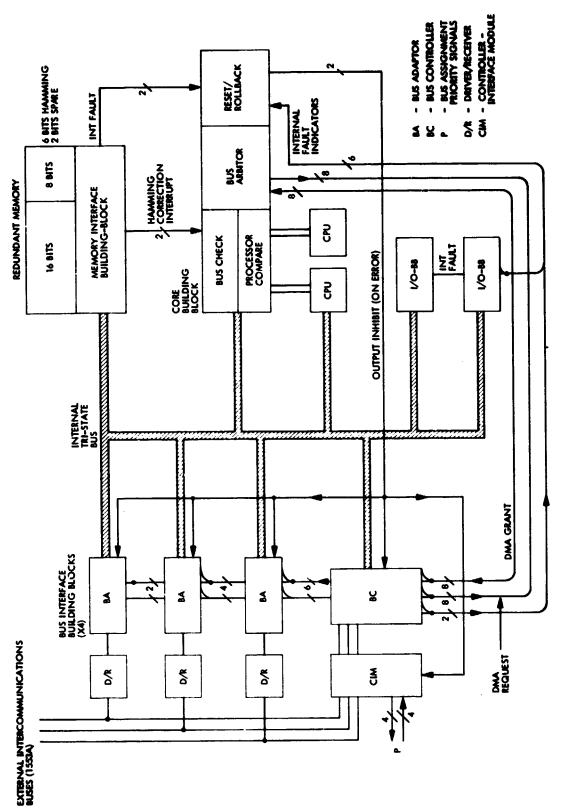

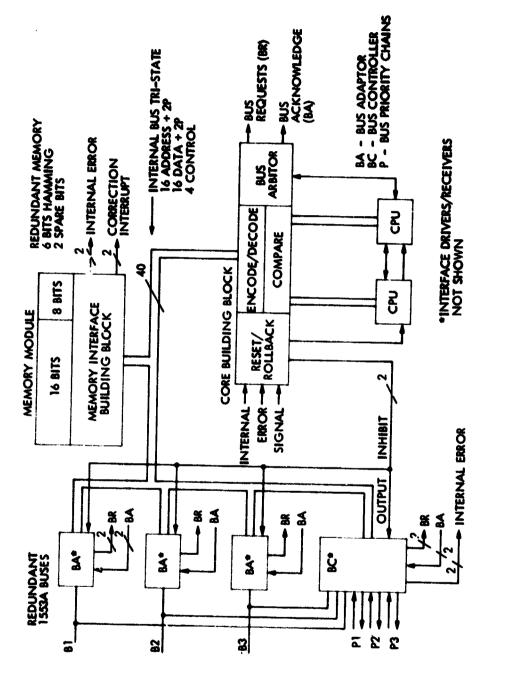

| 1-1 | The Self-Checking Computer Module (SCCM) 1- | 5 |

|-----|---------------------------------------------|---|

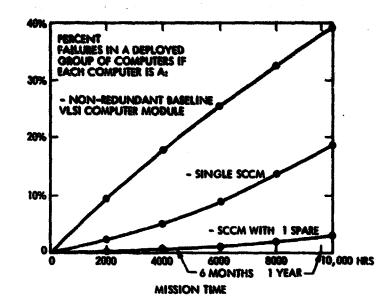

| 1-2 | Reliability Improvement Using SCCMs 1-      | 8 |

ORIGINAL PAGE IS OF POOR QUALIT

1

vii .

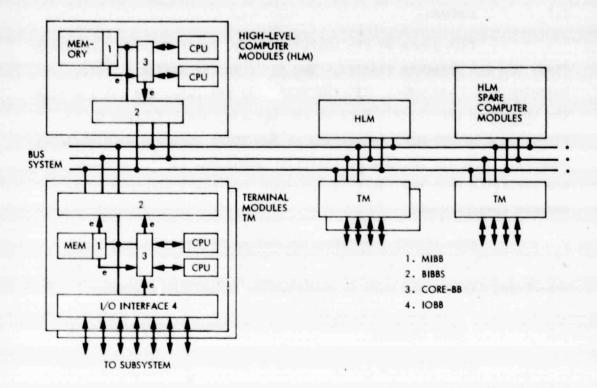

| 1-3  | Distributed Standby Redundant Architecture 1-9                                         |

|------|----------------------------------------------------------------------------------------|

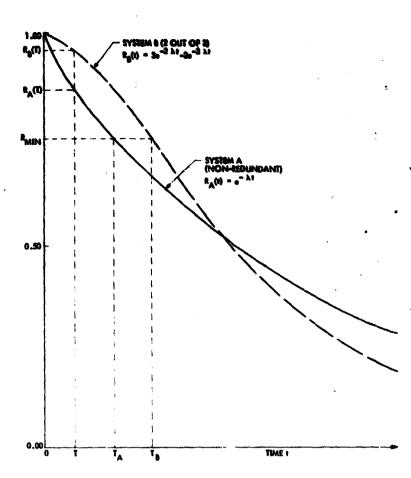

| 2-1  | System Reliability Predictions 2-24                                                    |

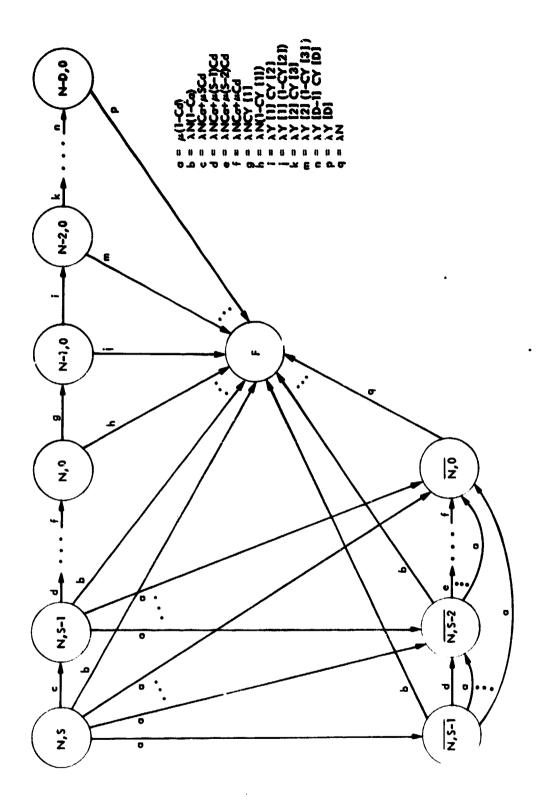

| 2-2  | Markov Reliability Nodel for Closed Systems 2-29                                       |

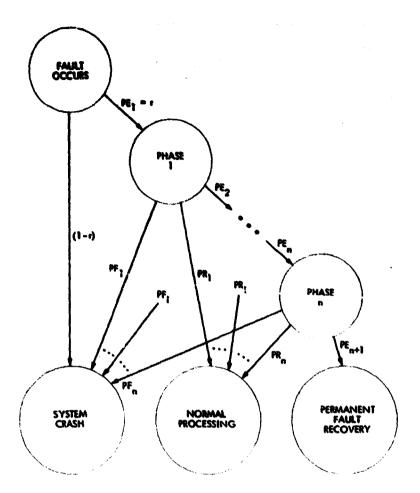

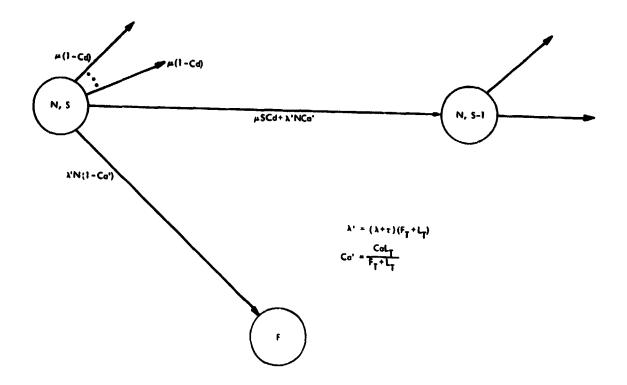

| 2-3  | Transient Fault Recovery Process 2-36                                                  |

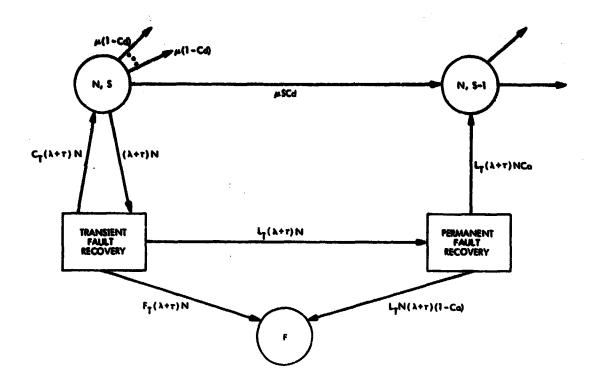

| 2-4  | Transient Recovery in the Markov Model 2-40                                            |

| 2-5  | Equivalent Form of the Markov Model 2-40                                               |

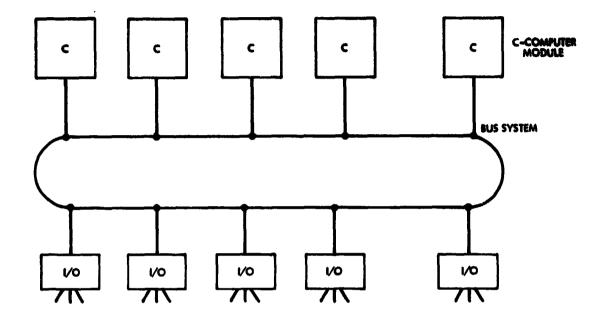

| 3-1  | A Non-Dedicated Distributed Computer Architecture 3-6                                  |

| 3-2  | The Distributed Processing Architecture 3-8                                            |

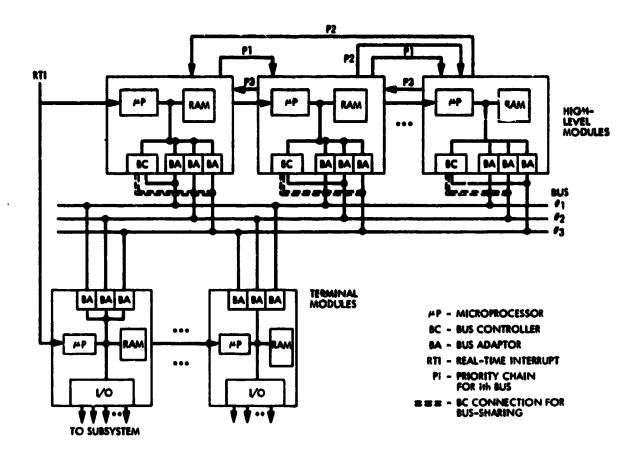

| 3-3  | The Self-Checking High-Level Nodule 3-16                                               |

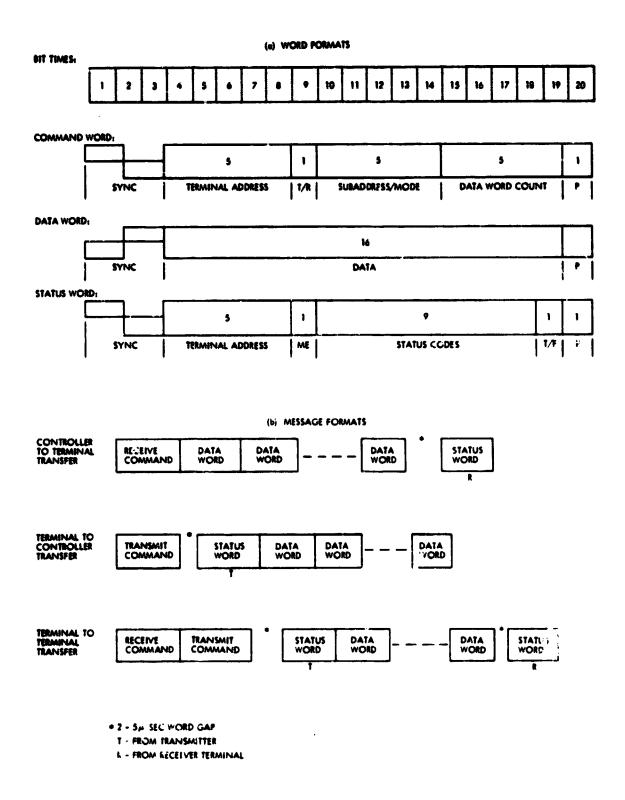

| 3-4  | MIL-STD 1553A Formats 3-24                                                             |

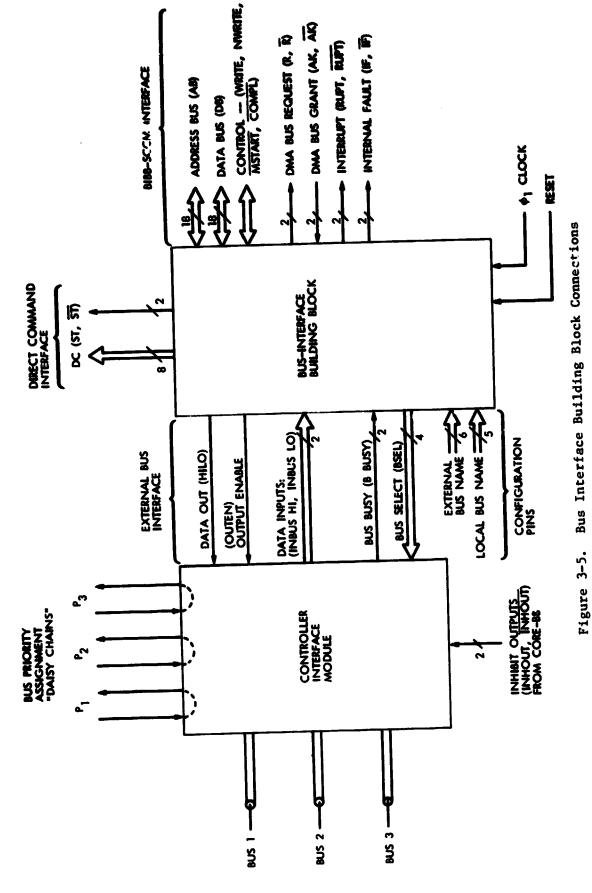

| 3-5  | Bus Interface Building Block Connections 3-26                                          |

| 4-1  | MIBB Subsystems 4-5                                                                    |

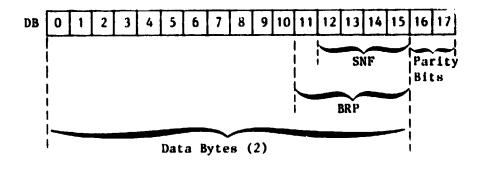

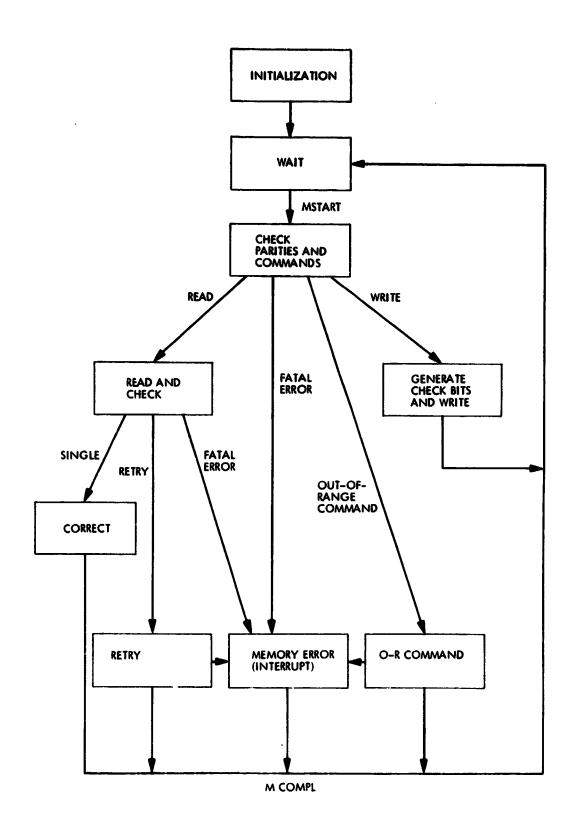

| 4-2  | General Flow Diagram 4-12                                                              |

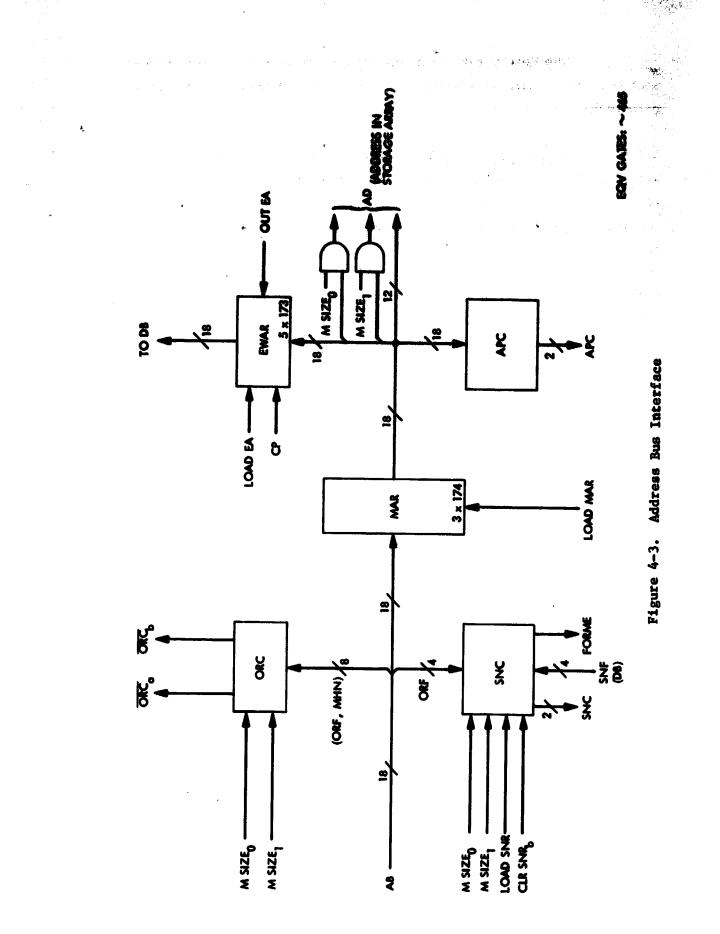

| 4-3  | Address Bus Interface 4-26                                                             |

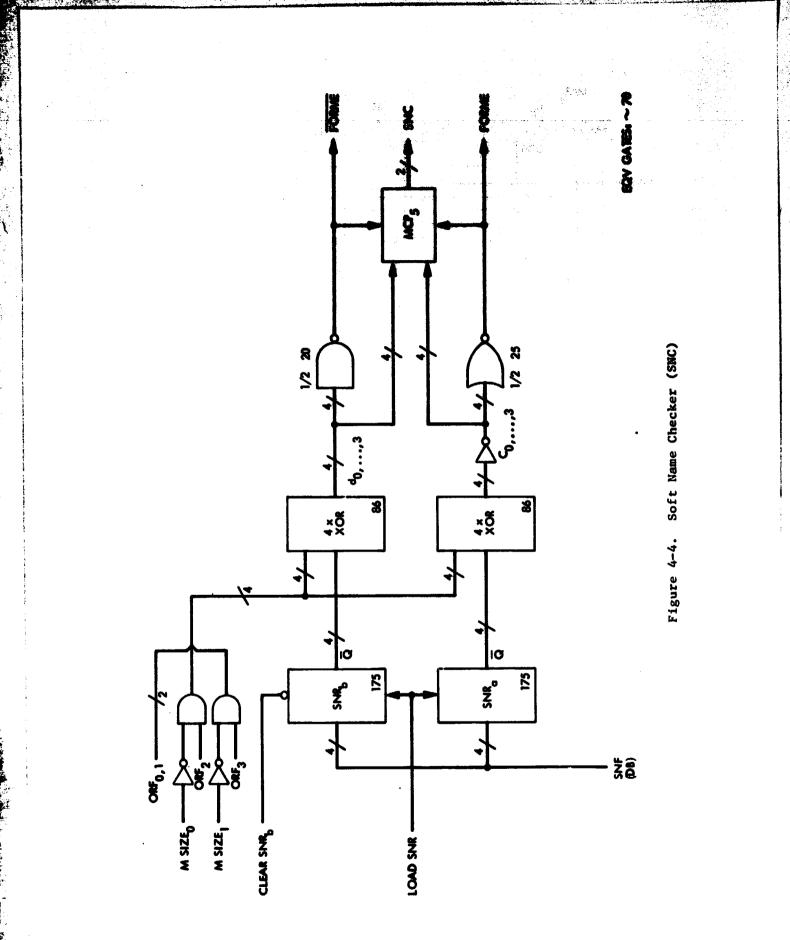

| 4-4  | Soft Name Checker (SNC) 4-27                                                           |

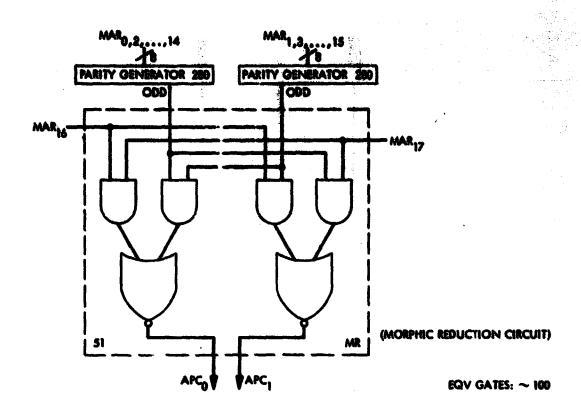

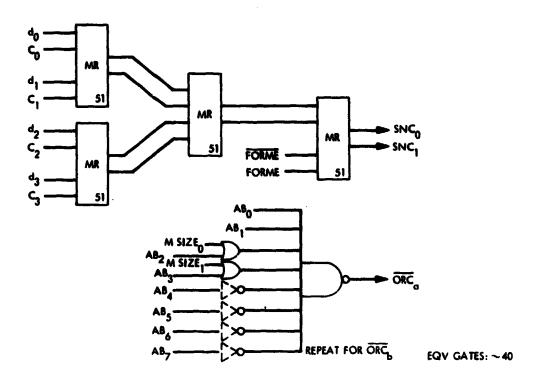

| 4-5  | Address Parity Checker (APC) 4-28                                                      |

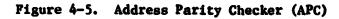

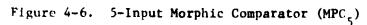

| 4-6  | 5-Input Morphic Comparator (MPC <sub>5</sub> ) 4-28                                    |

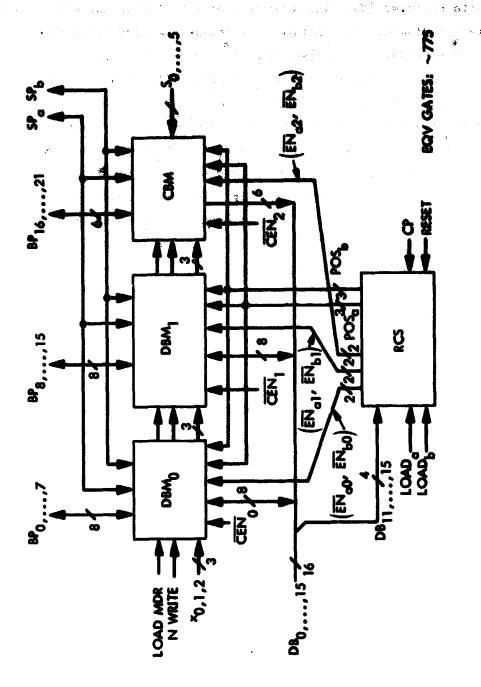

| 4-7  | Data Bus-Storage Array Interface 4-30                                                  |

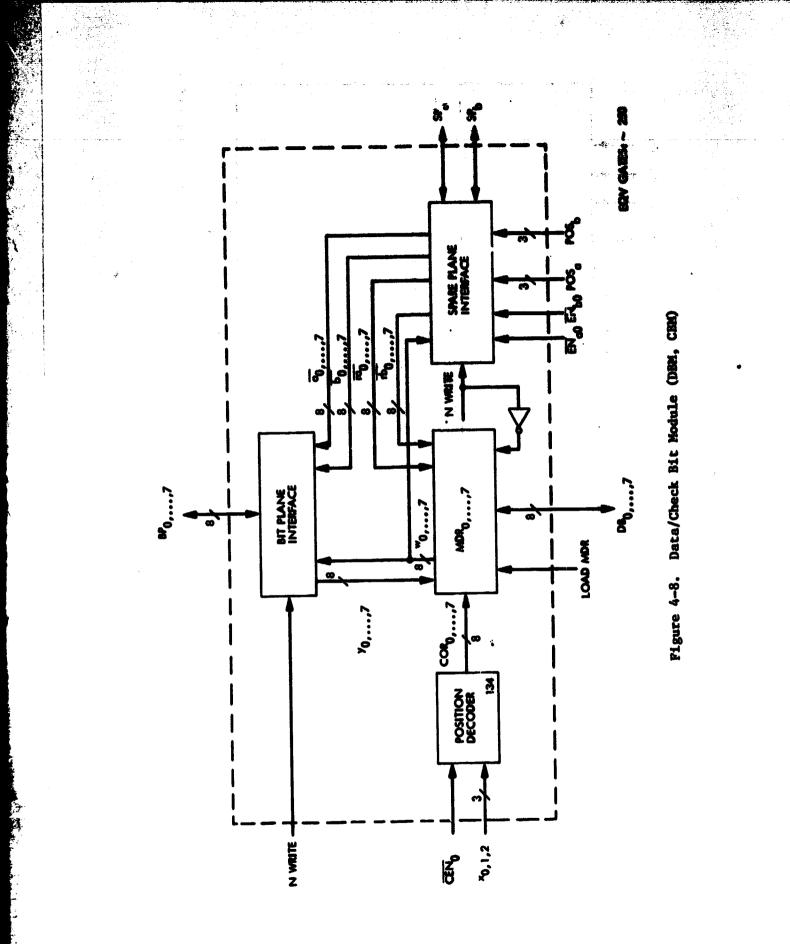

| 4-8  | Data/Check Bit Module (DBM, CBM) 4-31                                                  |

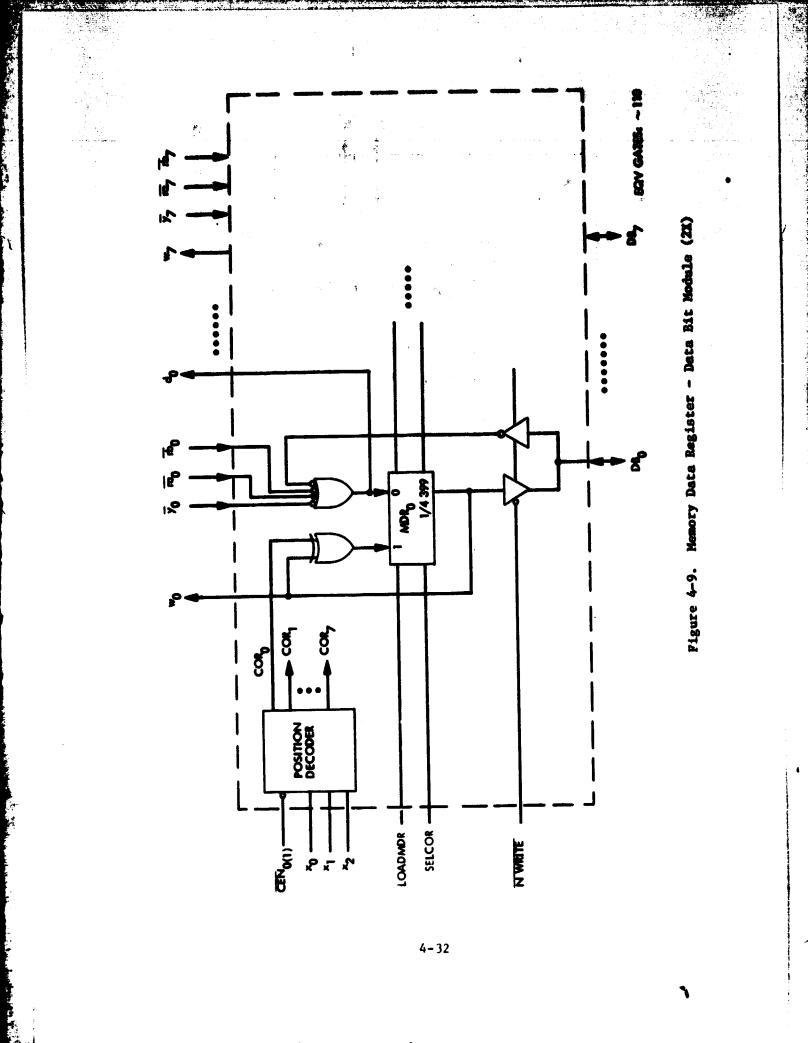

| 4-9  | Memory Data Register - Data Bit Module (2X) 4-32                                       |

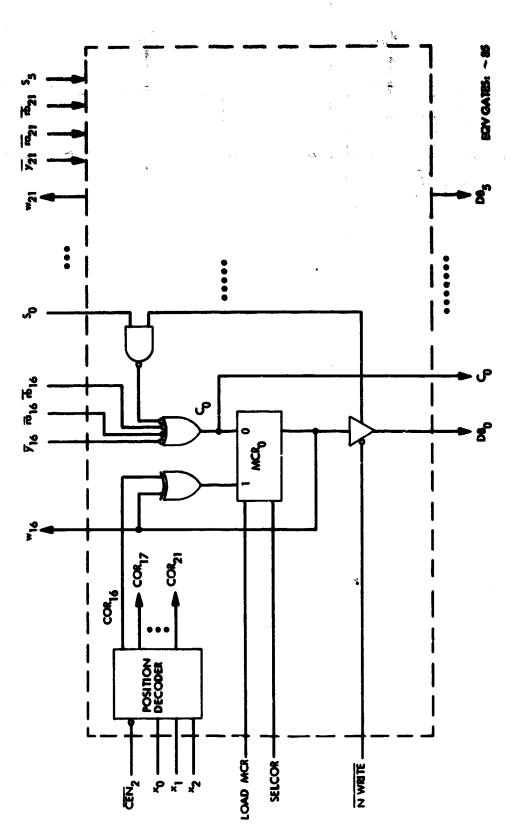

| 4-10 | Memory Data Register - Check Bit Module 4-33                                           |

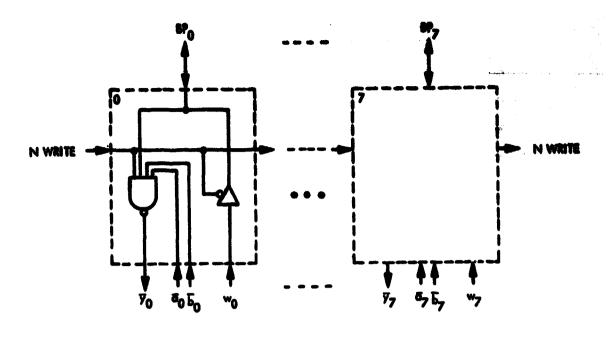

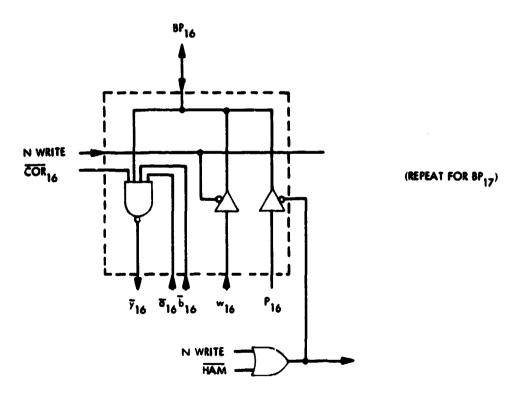

| 4-11 | Bit Interface Module (3X) 4-34                                                         |

| 4-12 | Bit-Plane Interface Module (2X) 4-34                                                   |

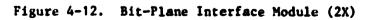

| 4-13 | Spare Plane Interface Module (3X for SP <sub>a</sub> , 3X for SP <sub>b</sub> ) - 4-35 |

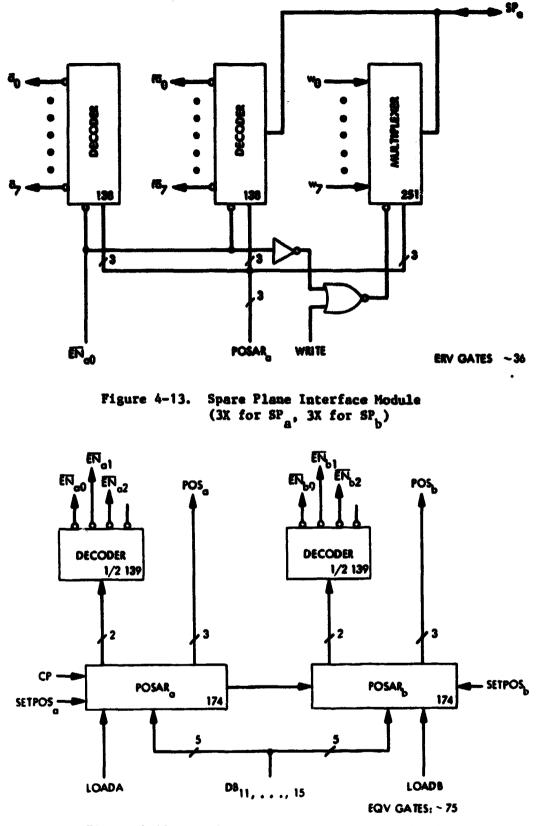

| 4-14 | Replacement Control Section (RCS) 4-35                                                 |

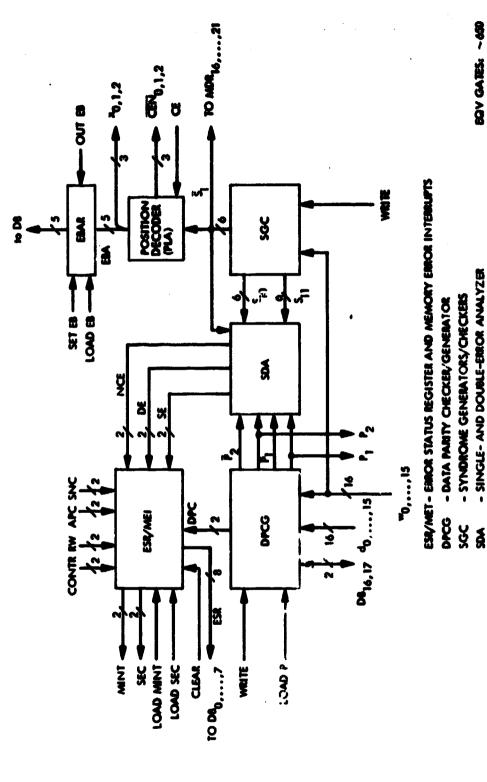

| 4-15 | Error Control Section (ECS) 4-36                                                       |

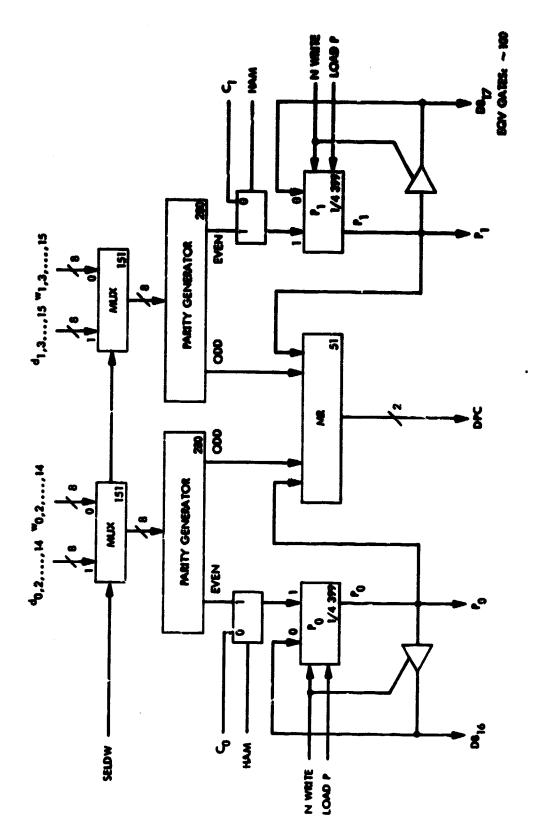

| 4-16 | Data Parity Checker-Generator (DPCG) 4-37                                              |

viii

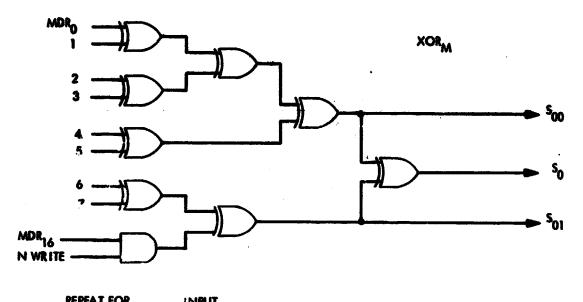

| 4-17          | Syndrome Generators/Checkers (SGC) 6X                                                                                                                         | 4-38  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

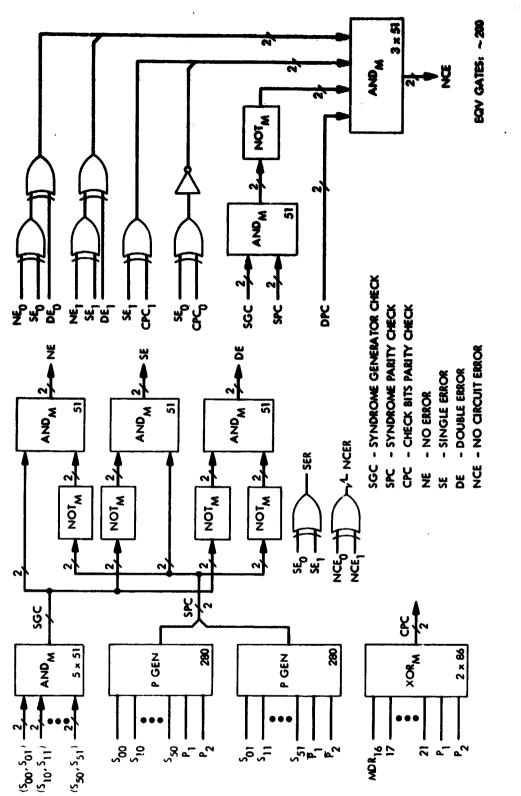

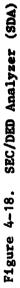

| 4-18          | SEC/DED Analyzer (SDA)                                                                                                                                        | 4-40  |

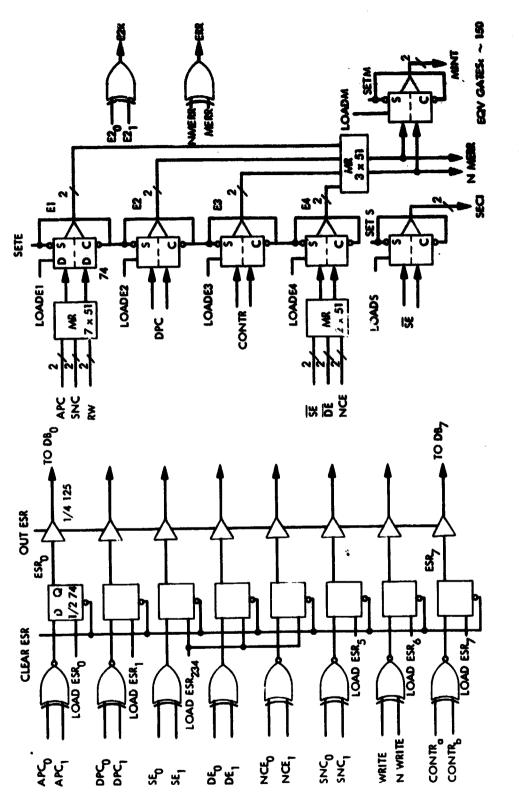

| 4-19          | Error Status Register and Memory Interrupt (RSR/MEI) -                                                                                                        | 4-41  |

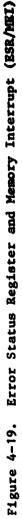

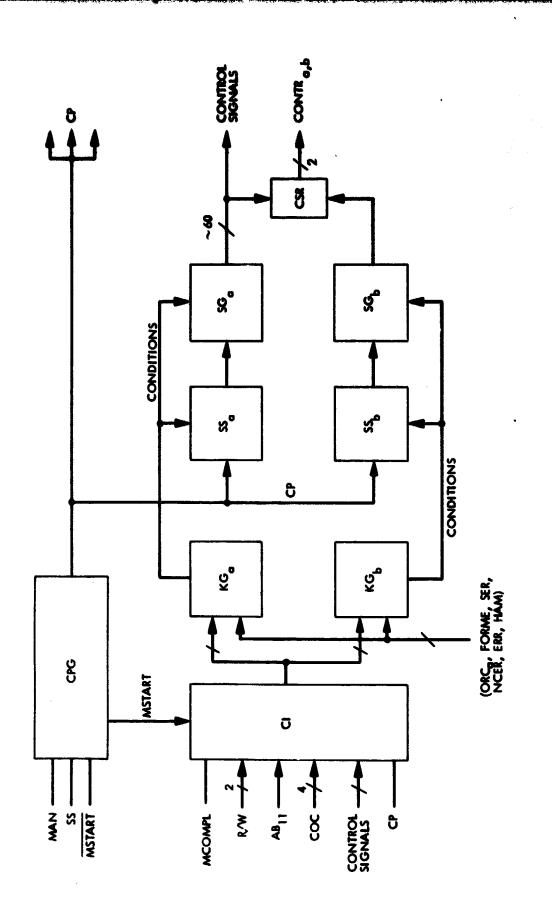

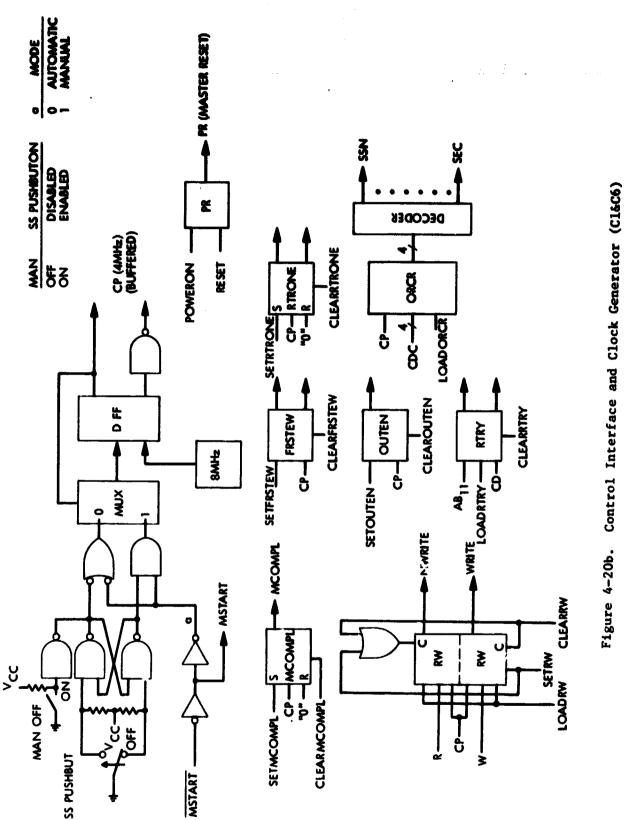

| 4-20 <b>a</b> | Control Section                                                                                                                                               | 4-43  |

| 4-20b         | Control Interface and Clock Generator (C16C6)                                                                                                                 | 4-44  |

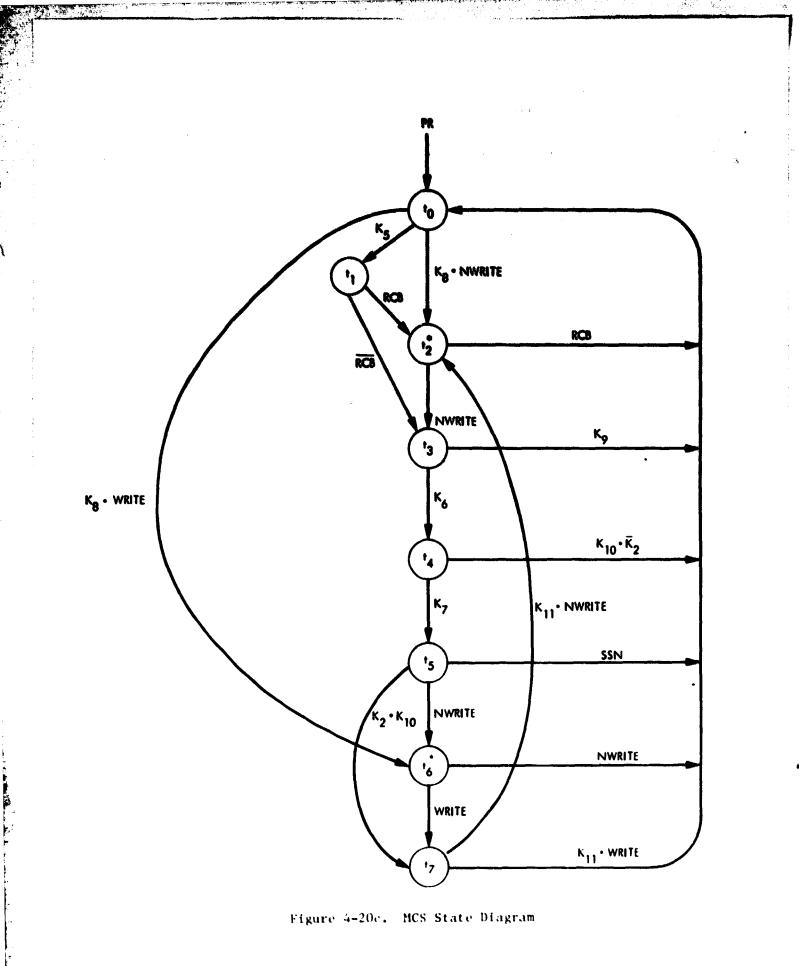

| 4-20c         | MCS State Diagram                                                                                                                                             | 4-45  |

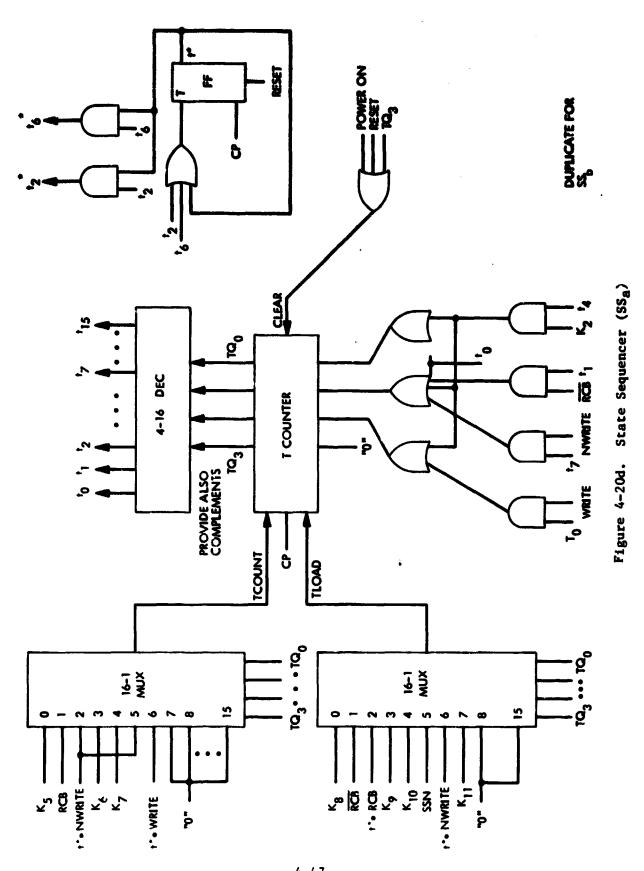

| 4-20d         | State Sequencer (SS)                                                                                                                                          | 4-47  |

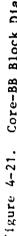

| 4-21          | Core-BB Block Diagram                                                                                                                                         | 4-53  |

| 4-22          | The Processor Check Element                                                                                                                                   | 4-57  |

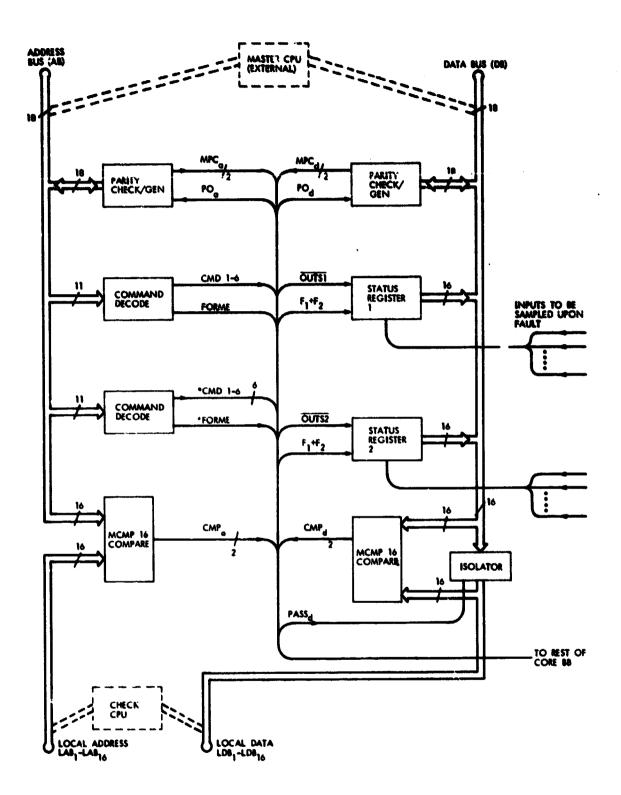

| 4-23          | Processor Check Element Logic: (a) Parity Check/<br>Generate; (b) Morphic Processor Comparison;<br>(c) Isolator; (d) Command Decoder; (e) Status<br>Registers | 4-60  |

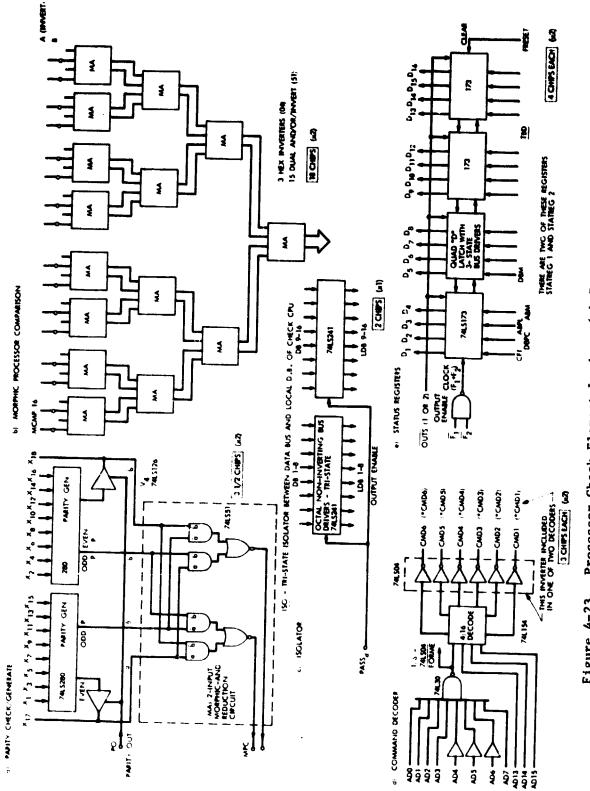

| 4-24          | Bus Arbitor Layout                                                                                                                                            |       |

| 4-25          | Priority Resolver Logic                                                                                                                                       | •     |

| 4-26          | Morphic and Currents: (a) Self-Checking Exclusive,<br>or Reduction Circuit; (b) Reduction Trees                                                               |       |

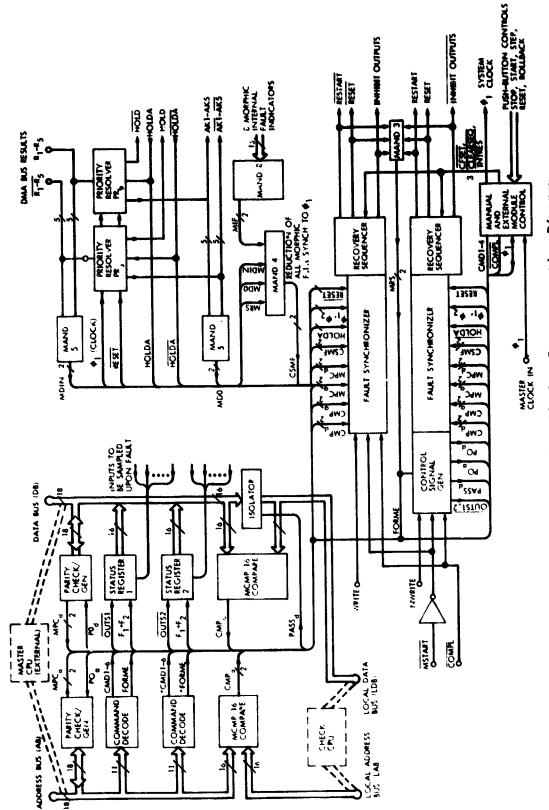

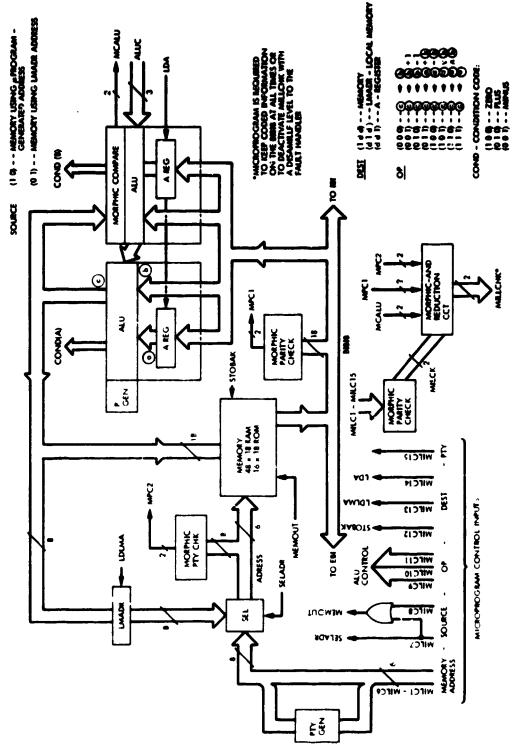

| 4-27          | Core Building Block - Interconnection Diagram                                                                                                                 | 4-67  |

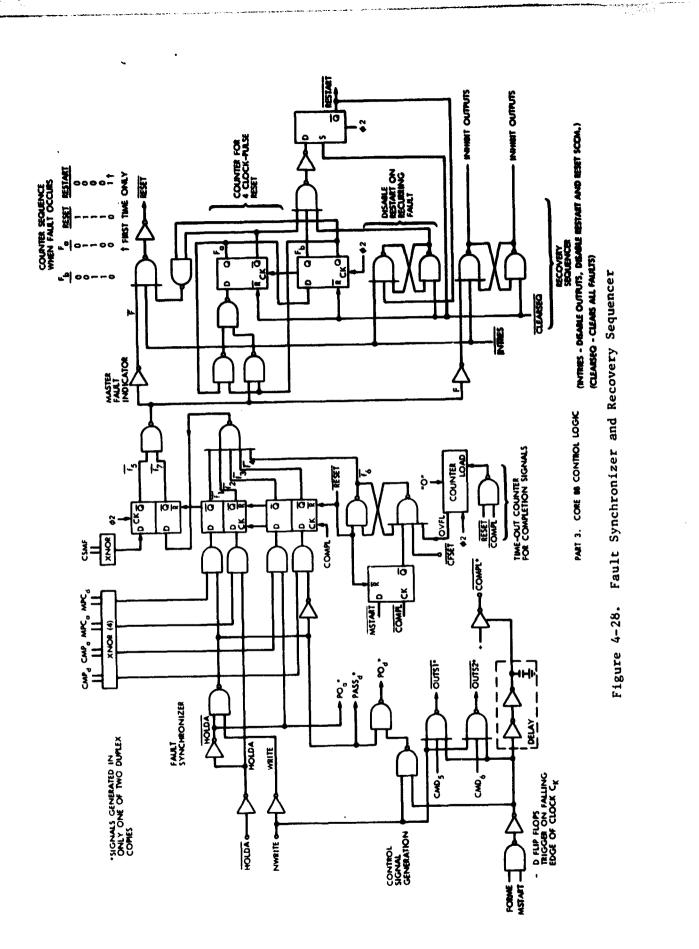

| 4-28          | Fault Synchronizer and Recovery Sequencer                                                                                                                     | 4-68  |

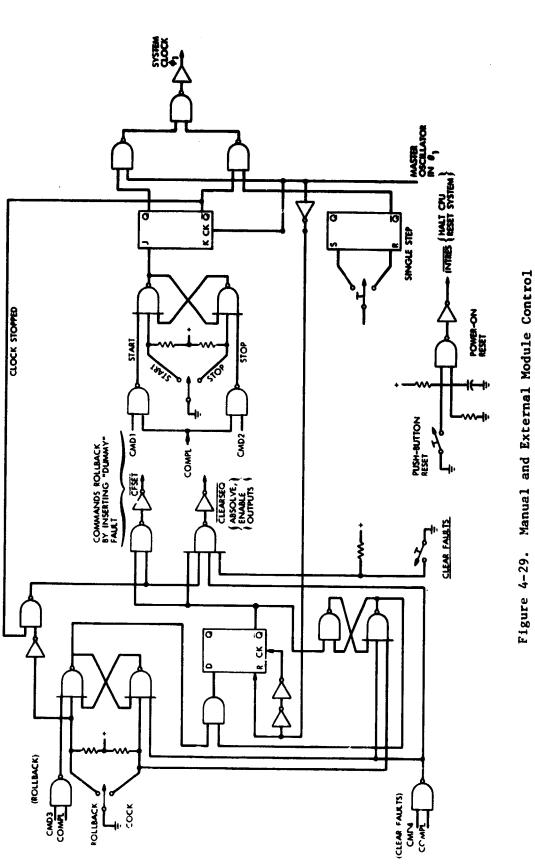

| 4-29          | Manual and External Module Control                                                                                                                            | 4-72  |

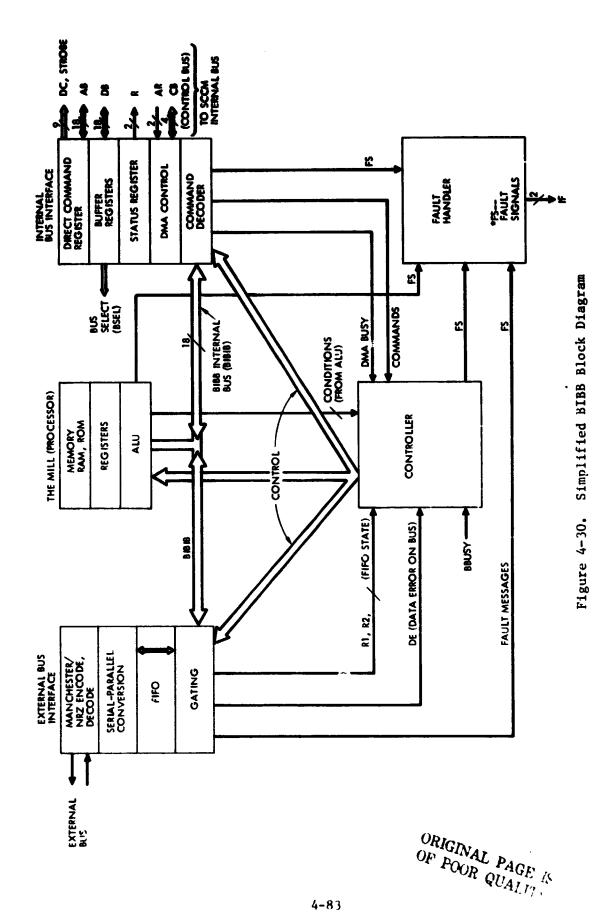

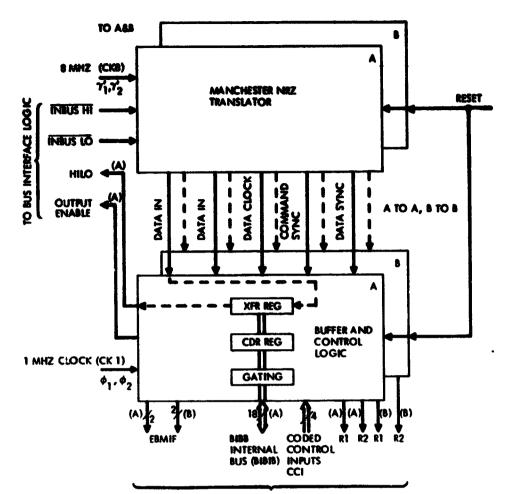

| 4-30          | Simplified BIBB Block Diagram                                                                                                                                 | 4-83  |

| 4-31          | External Bus Manager Block Diagram                                                                                                                            | 485   |

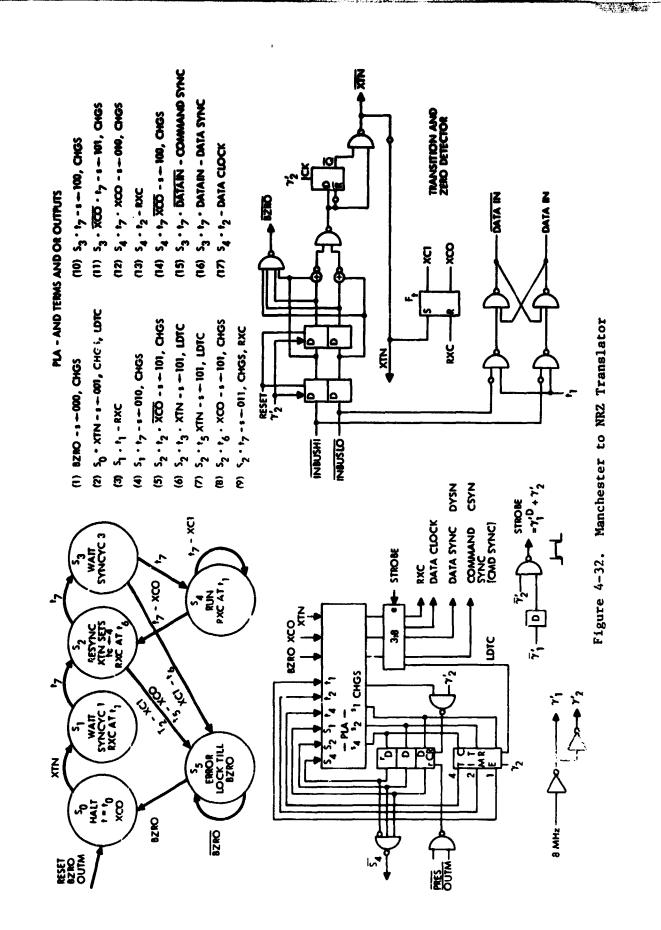

| 4-32          | Manchester to NRZ Translator                                                                                                                                  | 4-88  |

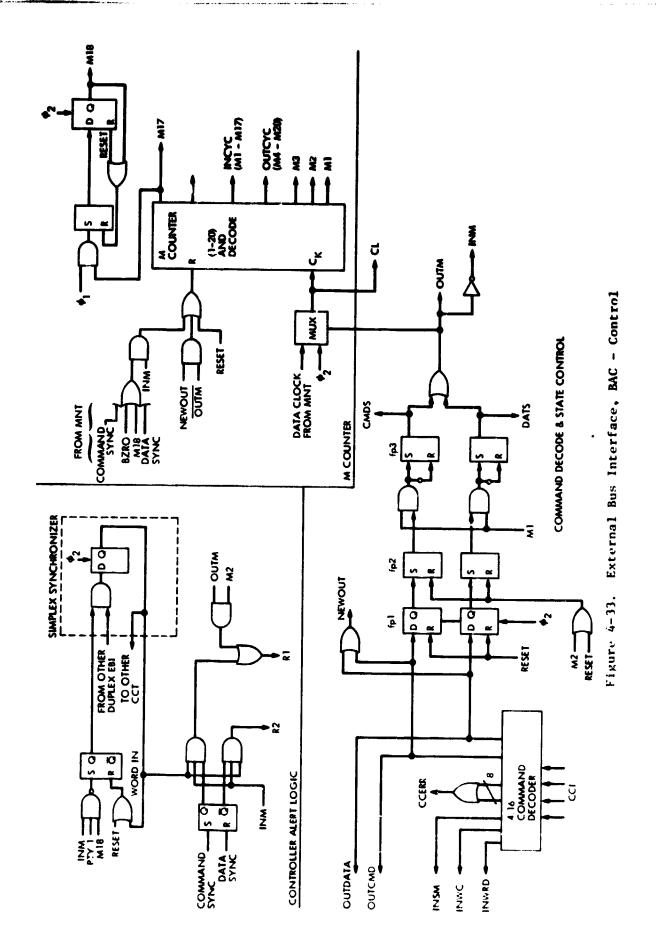

| 4-33          | External Bus Interface, BAC - Control                                                                                                                         | 4-91  |

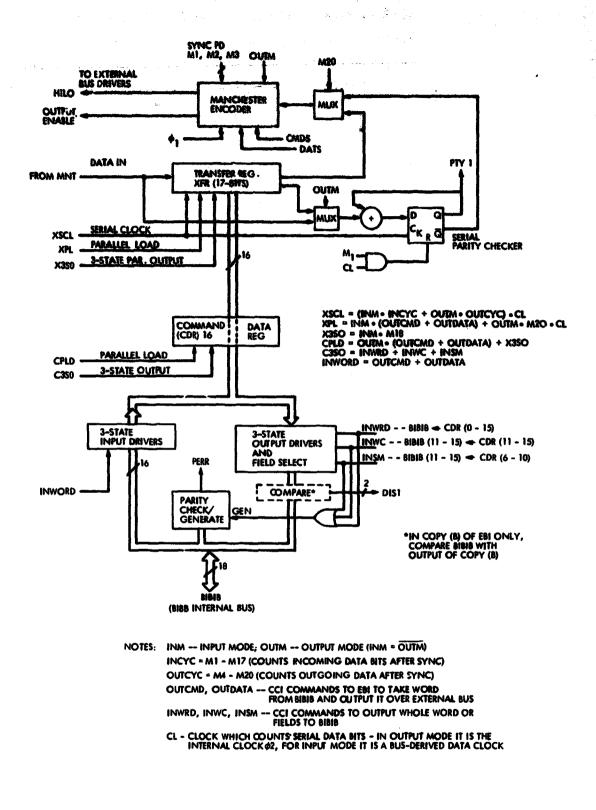

| 4-34          | External Bus Interface, BAC - Data Paths                                                                                                                      | 4-94  |

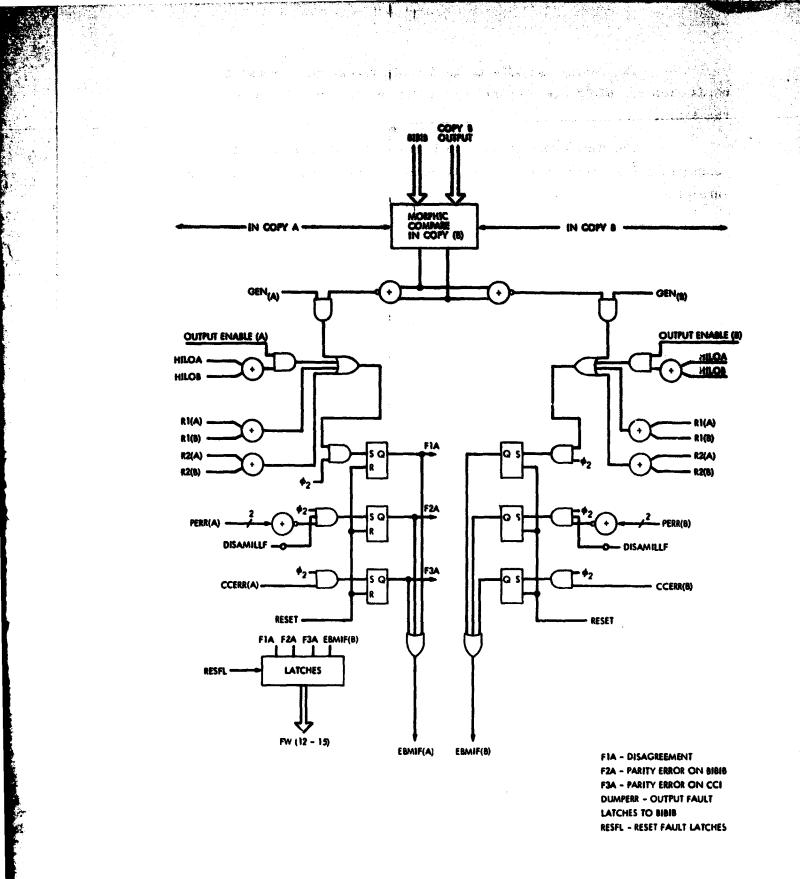

| 4-35          | External Bus Interface, BAC - Fault Detection Logic                                                                                                           | 4-96  |

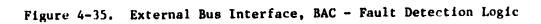

| 4-36          | The Internal Bus Interface                                                                                                                                    | 4-97  |

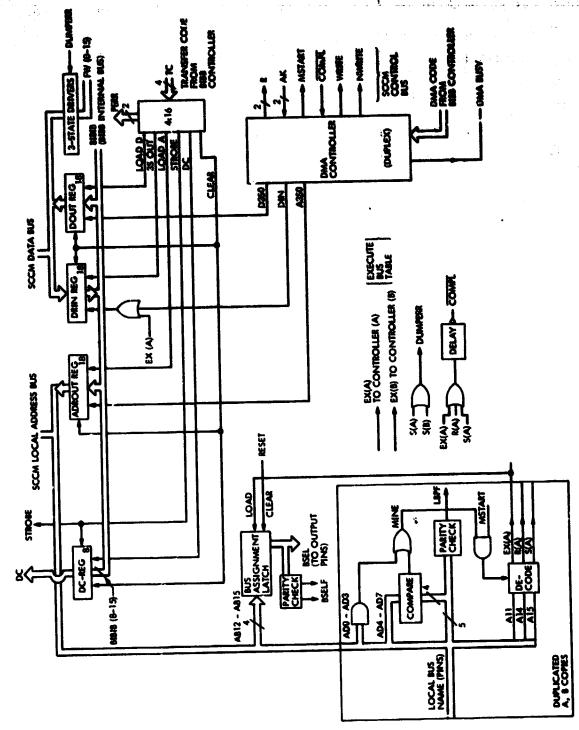

| 4-37          | The IBI - DMA Controller                                                                                                                                      | 4-100 |

| 4-38          | 1BI - Fault Handling Circuits                                                                                                                                 | 4-101 |

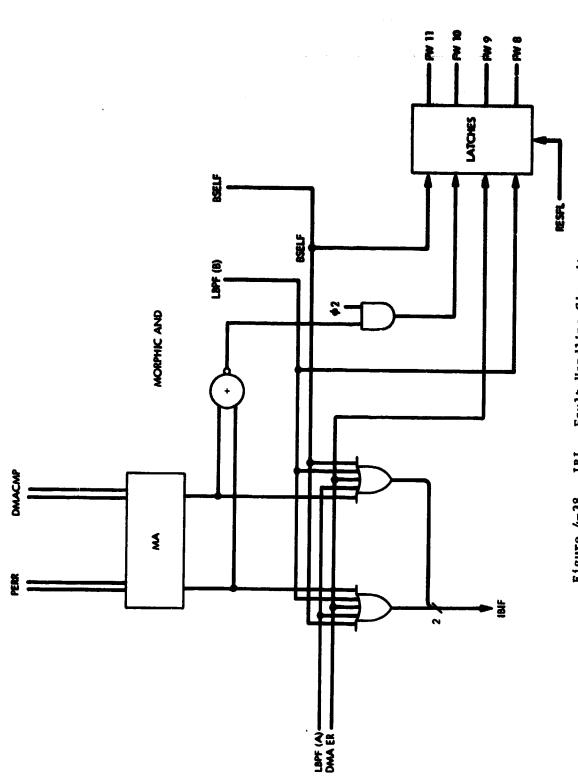

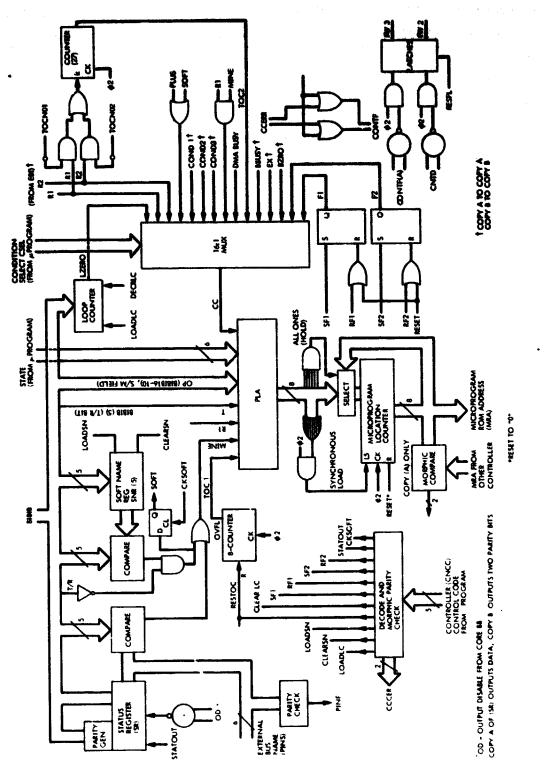

| 4-39(a) | The Mill                                   | 4-104 |

|---------|--------------------------------------------|-------|

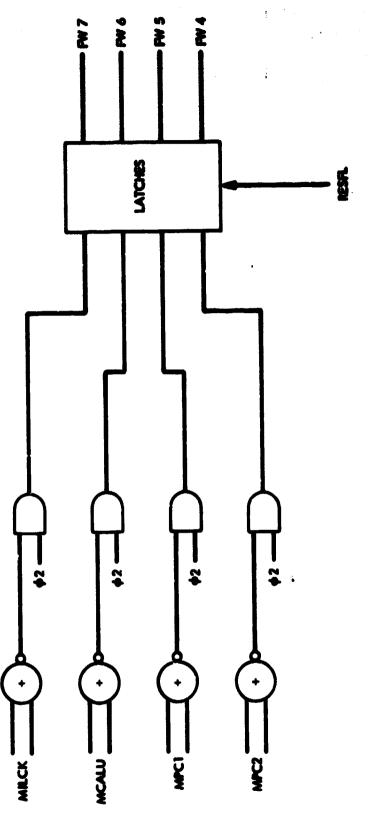

| 4-39(b) | The Mill - Fault Latches for Status Sample | 4-105 |

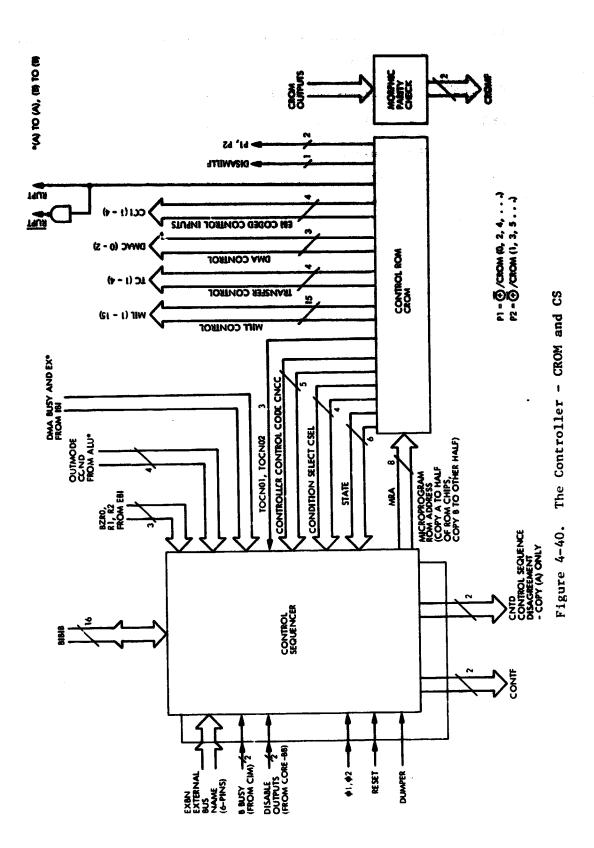

| 4-40    | The Controller - CROM and CS               | 4-107 |

| 4-41    | The Control Sequencer                      | 4-109 |

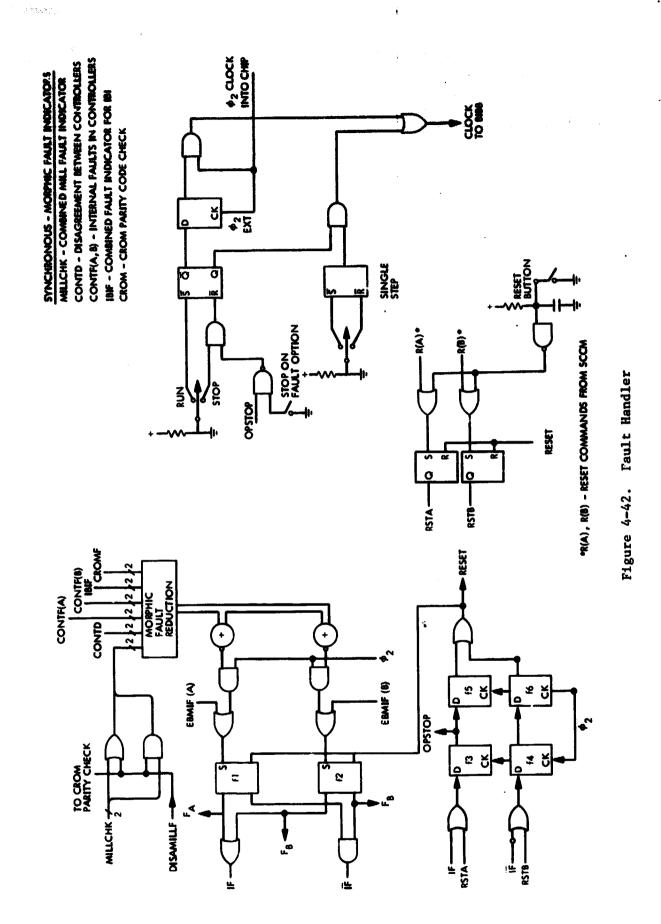

| 4-42    | Fault Handler                              | 4-113 |

一般の

# Tables

S.

| 2-1  | Characterisation of Several Models & Fault-Tolerant<br>Systems | 2-30  |

|------|----------------------------------------------------------------|-------|

| 2-2  | Algorithm for the Components of Matrix A                       | 2-32  |

| 2-3  | Derivation of Transient Reliability Measures                   | 2-38  |

| 4-1  | Odd-Weighted SEC/DED Code                                      | 4-22  |

| 4-2  | Component Count                                                | 4-51  |

| 4-3  | Conditions for Examining Morphic Check Signals                 | 4-69  |

| 4-4  | Memory Mapped BC Commands                                      | 4-76  |

| 4-5  | Bus Control Table Formats                                      | 4-77  |

| 4-6  | IBI Transfer Commands                                          | 4-98  |

| 4-7  | DMA Command Codes (DMAC)                                       | 4-99  |

| 4-8  | Control Sequencer Inputs                                       | 4-106 |

| 4-9  | A Control Sequencing Example                                   | 4-110 |

| 4-10 | Bus Adaptor Microprogram                                       | 4-116 |

| 4-11 | Bus Controller Microprogram                                    | 4-121 |

x

## SECTION 1 SUMMARY AND OVERVIEW

Over the last decade, the methodology of fault-tolerant computing has been developed to increase the reliability of computer systems. Fault-tolerant computers have been designed to contain redundant circuits and, when hardware faults occur, they utilize the redundant circuits to continue correct computation. By and large, these have all been customer-designed computer systems [AVIS 77].

This study was undertaken as part of the NOSC Very-Large-Scale-integrated-Circuit Technology Program to define VLSI buildingblock circuits which can be used with commercially available microprocessors and memories to implement fault-tolerant computer systems. This approach is taken with the view that a wide range of government requirements can be satisfied with commercially developed processors. Thus, the direction of this study is to define the supporting circuits necessary to utilize existing processors in fault-tolerant configurations.

The principal result is a determination that a small number of huilding-block circuits can be developed which will allow construction of both centralized and distributed (multi-computer) computer configurations which are fault tolerant. These building blocks consist of (1) an Error Detecting and Correcting Memory Interface Circuit, (2) a CORE Processor Checker and Fault-Handling Circuit, (3) a Self-Checking Programmable Bus-Interface Circuit, and (4) several 1/0 circuits to perform voting, error checking, and short isolation. The design of the first three building blocks for a feasibility breadboard are described in this report, along with the rationale behind their selection.

#### 1.1 SYSTEM REQUIREMENTS

ì

Reliability is a continuing problem in complex military systems. The cost of unexpected failures shows up in many ways, including reduced operational readiness, and the large number of personnel involved in maintenance. Dollar costs are usually difficult to quantify

because system procurement and costs of ownership are usually parcelled into various areas of responsibility. It can be said, however, that costs of ownership often exceed procurement costs in a large number of major systems.

By increasing testability, maintainability and, in some cases, providing automated redundancy management in the early stages of a system design, it is expected that life-cycle costs can be reduced. This viewpoint advocates moderately increasing initial hardware costs to achieve improved reliability and reduced maintenance during a system's operational lifetime.

The computers within a system provide the starting point for automated maintenance. If computer reliability is assured, the computers can be used for (1) subsystem testing and failure diagnosis, (2) automatically replacing failed subsystems with spare parts, or (3) where no backup spares are available, modifying on-board processing to account for the degraded subsystem state. Stated another way, the computer becomes an automated repairman.

A second area of requirements for fault-tolerant computing occurs when the cost of computer failure becomes clearly unacceptable. Digital flight control of low-flying aircraft is a dramatic example. Although the number of applications of this type is relatively low, they may be expected to increase as the computer is relied upon more heavily.

#### 1.2 BUILDING-BLOCK COMPUTER REQUIREMENTS

The user of a fault-tolerant building-block computer (FTBBC) system should be allowed to specify a maintenance interval and the reliability required over that interval. This has two major implications. First, the FTBBC configurations must allow the modular addition of redundant elements so that the same design, with differing numbers of spares, can economically satisfy both short- and long-life requirements. Secondly, the fault detection and recovery mechanisms of the FTBBC must be nearly perfect. Previous modeling studies have shown that "coverage," (the conditional probability that the system can implement recovery,

given that a fault occurs) must approach 100% for long-term reliability, whether or not a fault-tolerant system is periodically maintained [BOUR 69].

In order to be effective, a fault-tolerant computer must be designed to recover from a comprehensive set of faults, i.e., all the faults that can be reasonably expected to occur. We have attempted to protect against stuck-at faults on a single chip, most massive failures in a single chip or module, and most transient faults which create errors but which are of short duration. We do not expect unrelated hard faults to occur in different modules simultaneously.

The FTBBC architecture must be amenable to easy maintenance. Plug-in replacement modules should require a minimum of contact pins and should not require connectors at high-bandwidth, noise-sensitive points in the computer. Similarly, the computer should be capable of identifying, during routine maintenance, those modules which must be replaced.

The architecture of the building blocks should be capable of supporting a wide variety of processor and memory chips, i.e., the building block designs should not depend upon the peculiar I/O characteristics of any given processor. By initiating all control and I/O functions with out-of-range memory addresses (memory-mapped I/O), this processor independence can be achieved.

For the building-block computers to find wide application they should be consistent with military standardization programs. Thus, external bus interface circuits in the building block architecture use MIL-STD 1553A.

#### 1.3 DESIGN APPROACH

1

After a study of alternative approaches to the design of building-block-implemented, fault-tolerant computing systems, the following architecture was selected. The building-block circuits being developed are used to assemble commercially available microprocessors and memories into Self-Checking Computer Modules (SCCM), as

shown in Figure 1-1. Each SCCM is a small computer with the unusual property that its hardware is capable of detecting a wide variety of internal faults concurrent with normal (user) program execution. It can be connected (through a redundant external busing system), together with other SCCMs into a redundant network, in which backup SCCMs are provided to take over for a computer (SCCM) which has failed.

As shown in Figure 1-1, three of the building blocks interface (1) local memory, (2) the external busing system, and (3) local 1/0 to the processor. These interface building blocks are responsible for detecting faults in the circuits that they interface to the SCCM's processor, and faults in their own internal logic. They send fault indicator signals to the Core Building Block (Core-BB) if such a fault is detected.

The Core Building Block compares the outputs of two CPUs performing identical computations to detect (but not isolate) CPU faults, and it receives the fault signals from the other building blocks. It also checks error-detecting codes which are used to detect errors on the internal busses of the SCCM. The Core is responsible for disabling the SCCM upon detecting a fault anywhere within it. (An optional program rollback may be attempted to recover from some transient faults locally.)

Although the primary means of fault recovery is to use backup SCCMs to replace a SCCM which has failed, it is possible to correct some of the most likely faults in a failed SCCM (by an internal reconfiguration) and reuse it. A SCCM can be reconfigured to recover from at least two local memory faults through use of two spare-bit planes. Redundant external Bus Interface Building Blocks (BIBB) allow communication through alternate buses if a bus interface should fail, and redundant I/O Building Blocks can be used within a SCCM. (A design augmentation currently under consideration, allows one of the two CPUs to be discarded when a disagreement occurs, and computation to continue with only one. This is for non-critical applications since CPU fault detection is no longer available with only one machine.)

į.

-

The second s

### THE BUILDING-BLOCK CIRCUITS

The building-block circuits are briefly described in the following paragraphs.

#### 1.4.1 The Memory-Interface Building Block (MIBB)

This circuit interfaces a set of commercial memory chips to the local bus within a SCCM. It is capable of detecting single faults within the memory, effecting replacement of up to two faulty bit planes with spares, and correcting single bit errors using a (SEC/DED) Hamming code. It generates and checks parity codes to protect information transfer on the SCCM internal bus. Special checking circuits are employed in the MIBB to detect faults in the memory and within the MIBB, and fault signals are sent to the Core.

#### 1.4.2 The Core Building Block (Core-BB)

This circuit provides a continuous comparison between two processors that run synchronously to detect processor faults. It also includes parity generation and checking circuits to interface the processor with the SCCM local bus and to detect faults on that bus. Internal bus allocation (arbitration) is provided between the CPU and competing DMA channels in the other building blocks. Also, the Core is responsible for disabling its host SCCM in the presence of faults and, optionally, attempting rollback/restart procedures. The Core, like all other building blocks, contains internal checking circuitry to detect faults within its own internal logic.

#### 1.4.3 The Bus-Interface Building Block (BIBB)

This circuit can be microprogrammed to perform the functions of either a controller or terminal (adaptor) to an external 1553A bus. Several BIBBs can be used within an SCCM to provide communications over several redundant external buses.

The BIBB provides the hardware interface between an external bus and the internal bus of its host SCCM. Internal fault-detecting circuitry is provided within the BIBB, and the parity and status

1.4

1

messages employed in 1553A are used to verify proper message transmission and reception.

#### 1.4.4 I/O Building Block (IOBB)

A discussion is included later in this report on the various circuits required to provide fault-detection and redundancy in the interfaces between an SCCM and its associated peripheral devices.

#### 1.5 SCCM PROPERTIES

.

Ĭ

A "typical" SCCN would consist of the following integrated circuits: 32 commercial BAM chips, 2 commercial microprocessors, 1 MIBB, 1 Core, 3 BIBBs, two IOBBs, and several additional MSI circuits. A previous report has indicated that its characteristics would approximate those listed below if the building blocks were implemented as VLSI devices. (RENN 78a)

| Power  | 8w                    |

|--------|-----------------------|

| Weight | 1.4 lb*               |

| Volume | 23 in. <sup>3</sup> * |

| Cost   | \$13,600*             |

\*Not including power supply.

The cost represents high reliability production, (e.g., MIL-SID 883B) and could be greatly reduced in large quantities. Figure 1-2 is an estimate of the reliability of a single SCCM, a SCCM backed up by a standby spare, and, for comparison purposes, a nonredundant computer made with similar technology. A simple combinational model was used (see RENN 78a) and it was assumed that a 10,000-gate VLSI device has a failure rate of one failure per million hours. An SCCM costs approximately 50% more in power, weight, volume, and dollars than an equivalent non-redundant machine; but since it can tolerate internal memory faults, its inherent reliability is 2-3 times greater (over the period being modeled). A pair of SCCMs can provide fully fault-tolerant operation with very much improved reliability.

Figure 1-2. Reliability Improvement Using SCCMs

#### 1.6 THE DISTRIBUTED COMPUTER (SCCM) ARCHITECTURE

An architecture has been selected for implementing faulttolerant distributed computing networks made up of SCCMs. The selected architecture consists of a number of computers (SCCMs) performing separate tasks, and which are connected by a redundant multiple bus structure, as shown in Figure 1-3.

There are two classes of SCCMs used within this network, designated Terminal Modules and High-Level modules. Each Terminal Module is embedded within a particular subsystem and performs local control and data gathering tasks. The High-Level computer modules control the functioning of various terminal modules by controlling an intercommunications bus. Using the bus, a High-Level SCCM can move data directly into or out of memories of other computers and thus broadcast commands or gather data for its various processing functions.

In this configuration, several techniques are employed to achieve fault tolerance. First, all of the computers are self-checking (SCCMs) and are designed to detect their own internal faults.

F. .

Line and

Figure 1-3. Distributed Standby Redundant Architecture

Secondly, backup spares are employed to replace faulty computer modules. In the case of High-Level modules, spares are nondedicated. A faulty module disables its own bus control function. Spare modules are programmed to detect the resulting lack of activity and take over the ongoing computations. For a Terminal Module, a failure is indicated through the bus system (by polling), and a High-Level Module effects its replacement by activating a dedicated backup spare module.

Thirdly, a highly redundant bus system is employed so that a faulty bus may be replaced by a spare. In the case of single faulty terminals, individual messages may be rerouted over different buses. Automatic status messages are employed in the bus format to verify proper transmission and reception of messages.

A more detailed description of this architecture can be found in RENN 78b.

#### 1.7 SUMMARY

ľ

and the second

This phase of the building-block, Fault-Tolerant Computing Study has two intended results. The <u>first</u> is the design of three building block circuits: (1) the MIBB, (2) the Core, and (3) the BIBB. The <u>second</u> is the verification of the building-block designs by constructing a breadboard, consisting of two SCCMs employed as high-level modules. This can be done by injecting simulated faults into one SCCM and verifying that the fault is detected, and the other SCCM recovers correct computations.

This report describes the design of the building-block circuits. The designs presented herein have been used for the initial breadboard layout, and will be modified as debugging progresses.

#### **1.8** REPORT OUTLINE

The following two sections (2 and 3) provide background material on the methodology of fault tolerance, and the specific assumptions on technology and application requirements which led to the selection of the building-block SCCM architecture described in this report. The reader who is interested primarily in design details can skip to Section 4, which provides more detailed descriptions of the individual building-block circuits.

## SECTION 2

#### THE CONCEPTS OF FAULT-TOLERANT COMPUTING

The purpose of this section is twofold:

١

Ē

and the second second

- (1) to provide the overall context of fault-tolerant computing as a discipline of computer science and engineering within which the specific results of this study are to be interpreted; and

- (2) to supply a self-contained complete introduction to fault-tolerant computer systems for readers who have not encountered this aspect of computer system design in the past.

A fault is an abnormal condition that appears during the operation of an information processing system. Its manifestation may cause a departure from the expected behavior and force the system into an undesirable (error) state or sequence of states. The arrival at an error state, in turn, leads to a partial or complete failure of the system to execute the specified function, unless provisions exist to cause a return to the expected behavior. Causes of faults are either adverse natural phenomena or human mistakes. Because of their disruptive effect on system operation, the avoidance and/or tolerance of faults are major problem areas in contemporary information-processing activities, including the design, analysis, management, and use of information systems

The word "fault" in the subsequent discussion means "an abnormal condition of hardware, programs, or data that may cause a deviation of the information-processing behavior of some part of the given system from the expected sequence," and "system" comprises all hardware elements, programs and microprograms, input signals, stored information, inter-system communication, and man-machine interaction functions. All these parts of the system have to be considered because in practice they all are affected by faults. As a consequence, the fault problem transcends the traditional "hardware-software" applications boundaries and becomes a global problem of information processing.

The word "expected" is preferred to the word "correct" in the description of fault-free behavior because the question of correct behavior, as it has been specified by the originator or user of the system, exceeds the scope of fault-tolerance considerations. For example, the choice of an unsuitable algorithm by the user will lead to expected behavior that is not correct with respect to the user's ultimate goal.

1

The various types of faults that are encountered during system operation fall into two fundamentally distinct classes: physical faults and man-made faults. <u>Physical faults</u> are faults caused by adverse natural phenomena, such as failures of hardware components, and physical interference originating in the environment. <u>Man-made faults</u> are faults that result from human mistakes, including less than perfect specification, design, production (assembly), and man/machine interaction.

Fault-tolerance is a property of the entire system that allows it to continue the expected behavior regardless of the appearance of certain (explicitly specified) classes of faults (physical, man-made or both) that would otherwise force the system into an error state. The most commonly accepted notion of fault-tolerance refers to physical faults only. The inclusion of man-made faults is a recent generalization that offers a major challenge to investigators and designers of information processing systems.

A complete discussion of fault-tolerance must deal with its three fundamental aspects:

- (1) The pathology of faults, including study of their causes, classification according to their immediate manifestations, and characterization according to the symptoms (errors) observable in system behavior.

- (2) The implementation of tolerance, encompassing the three basic functions of masking, detection, and recovery.

(3) The modeling, analysis, and evaluation (measurement) of fault-tolerance by means of mathematical techniques, simulation, and experimentation with implemented systems.

The goals of this section are: (a) to present a unified view of the many aspects of fault-tolerance; (b) to identify some obstacles that remain to be overcome; and (c) to discuss the prospects for future advances in this field. Fault-tolerance with respect to both physical and man-made faults is considered, with emphasis on the more developed field of tolerating physical faults. The current stateof-the-art in the design and application of fault-tolerant systems is illustrated by examples of existing systems and innovative proposals.

The viewpoint presented here is that the purpose of faulttolerance is to provide the means for the idealized (fault-free) abstract logical structure of a computing system to function successfully while embodied in its fault-susceptible implementation. Conséquently, fault-tolerance attains full significance only when it is incorporated and utilized as an integral function of an information processing system. Outside of this system context, it remains, at best, a potentially applicable exercise for a researcher, and at worst, a tool to support naive or irresponsible promises of near-perfect operation.

#### 2.1 APPROACHES TO THE FAULT PROBLEM

ř S

Ľ

A ANALASSA

While conceptually the digital computer is a logical system for the storage and manipulation of symbols, in practice it is implemented using physical components and exists in an environment in which it is affected by various natural phenomena. Some phenomena, such as physical changes in the components and adverse effects of the environment, disrupt the operation as it is specified by the designers and programmers and lead to deviations from the expected behavior. These deviations have variously been called failures, faults, errors, intermittents, glitches, crashes, etc. They occur because we attempt to

carry out abstract symbol manipulation operations in a physical world which offers less than perfect components and less than completely benign environments.

1

١

The problems of avoiding these phenomena, and of recovering from their effects after they have occurred, have been of interest to the entire community of computer theorists, designers, builders, analysts, and users ever since the first calculating devices were devised. The first pioneers who attempted to implement their ideas were simply overwhelmed by the adversity of the physical world, such as in the case of Babbage's Calculating Engine.

The invention and refinement of electromagnetic relays, vacuum tubes, delay-line and cathode-ray tube storage, paper tape, and punched cards finally made machine computing feasible in the 1940's. However, the history of the early d.ys of machine computing is filled with accounts of the continuing straggle against the imperfections of components and hostility of environments. Ingenious defenses against faults, such as duplicate units, error-detecting codes, etc., are found in most early digital computers. [IRE 53], [EJCC 53].

The advent of the transistor and the magnetic-core storage element in the 1950's brought about a major increase in component reliability and at least temporarily relegated the concern with system reliability into the hands of component experts, and away from the main concerns of system designers and users.

The problem of reliability reappeared as a major issue again in the early 1960's when the applications of computers expanded into the areas of space exploration, real-time system control, and especially manned space-flight, in which the lives of the crew literally depended on successful computer operation.

The reliability of components has continued to improve since that time. However, the expanding range of applications and the growing complexity of systems has kept the reliability problem in the foreground and has led to the evolution of the concept of fault-tolerant computing, which is the designer's and the programmer's method to provide reliable computer operation while using less than perfect components 4

in less than ideal environments [AVIZ 75a]. The major part of this section considers the tolerance of physical faults; the issue of manmade faults is addressed in Section 2.5

## 2.1.1 Tolerance and Avoidance: Complementary Approaches to the Fault Problem

A look at computers of the present and of the immediate past shows that many systems have either very few fault-tolerance features. or none at All. In these cases, reliability with respect to physical faults is sount by means of the fault-avoidance approach (also called "fault-intolerance" in some papers) in which the reliability of computing is assured by a priori elimination of the causes of faults. The elimination takes place before regular use begins, and the resources that are allocated to attain reliability are spent on perfecting the system prior to its field use. Redundancy is not employed, and all parts of the system must function correctly at all times. Since in . practice it has not been possible to assure the complete a priori elimination of all causes of faults, the goal of fault-avoidance is to reduce the unreliability (expressed as the probability of system failure before the end of a specified time interval) of the system to an acceptably low value. To supplement this approach, manual maintenance procedures are devised which return the system to an operating condition after a failure. The cost of providing maintenance personnel and the cost of the disruption and delay of computing also are parts of the overall cost of using the fault-avoidance approach. The procedures which have led to the attainment of reliable systems using this approach are:

- Acquisition of the most reliable components and their testing under various conditions within the given cost and performance constraints.

- (2) Use of thoroughly refined techniques for the interconnection of components and assembly of subsystems.

- (3) Packaging and shielding of the hardware to screen out expected forms of external interference.

(4) Carrying out of comprehensive testing of the complete system prior to its use.

Once the design has been completed, a quantitative prediction of system reliability is made using known or predicted failure rates for the components and interconnections. In a "purely" faultavoiding (i.e., nonredundant) design, the probability of fault-free hardware operation is equated to the probability of correct program execution. Such a design is characterized by the decision to invest all the reliability resources into high-reliability components and refinement of assembly, packaging, and testing techniques. Occasional system failures are accepted as a necessary evil, and manual maintenance is provided for their correction. To facilitate maintenance, some built-in error detection, diagnosis, and retry techniques are provided. This is the most common current practice in computer system design; the trend is toward an increasing number of built-in aids for the maintenance engineer.

The traditional fault-avoidance approach of diagnosis-aided manual repair, however, has proved to be an insufficient solution in many cases because of at least three reasons: the unacceptability of the delays and interruptions of real-time programs (air traffic control, process control, etc.) caused by manual repair action; the inaccessibility of some systems (space, undersea, etc.) to manual repair; and the unacceptably high cost of lost time due to manual maintenance in many installations. The direct dependence of human lives on some computer-controlled operations (air traffic control, manned spaceflight, etc.) has added a psychological reason to object to the fault-avoidance approach: although only one system in a million is expected to fail in a given time interval, all users of the entire million systems are subject to the anticipation that they may be involved in this failure.

An alternate approach which alleviates most of the above shortcomings of the traditional fault-avoidance approach is offered by fault-tolerance. In this approach the reliability of computing is assured by the use of protective redundancy. Faults are expected to be present and to cause errors during the computing process, but their effects are automatically counteracted by the redundancy. Reliable

computing is made possible despite certain classes of hardware failures, external interface with computer operation, and perhaps even some manmade faults in hardware and software. Part of the resources allocated to attain reliability are spent on protective redundancy. The redundant parts of the system (both hardware and software) either take part in the computing process or are present in a standby condition, ready to act automatically to preserve its undisrupted continuation. This contrasts with the manual maintenance procedures which are invoked after the computing process has been disrupted, and the system remains "down" for the duration of the maintenance period.

It is evident that the two approaches are complementary and that the resources allocated to attain the required reliability of computing may be divided between fault-tolerance and fault-avoidance. Experience and analysis both indicate that a balanced allocation of resources between the two approaches is most likely to yield the highest reliability of computing. Fault-tolerance does not entirely eliminate the need for reliable components; instead, it offers the option to allocate part of the reliability resources to the inclusion of redundancy. One reason for the use of a fault-tolerant design is to achieve a reliability or availability prediction that cannot be attained by the purely fault-avoiding design. A second reason may be the attainment of a reliability (or availability) prediction that matches the purely fault-avoiding design at a lower overall implementation cost. A third reason is the psychological support to the users who know that provisions have been made to handle faults automatically as a regular part of the computing process. The fault-avoidance approach clearly was the dominant choice in the 1950's and 1960's. In recent years, the faulttolerance approach has been making significant inroads with respect to physical faults. Its application with respect to man-made faults has remained very limited.

#### 2.1.2 Classes of Physical Faults

Physical faults are caused by three classes of phenomena that affect the hardware of the system during execution of programs. They are permanent failures of hardware components, temporary

malfunctions of components, and external interference with system operation. There are three useful dimensions for the classification of physical faults:

- (1) <u>Duration</u>: transient vs. permanent

- (2) Extent: local vs. distributed

- (3) <u>Value</u>: determinate vs. indeterminate

Transient faults are faults of limited duration, caused either by temporary malfunctions of components or by external interference. The characterization of a transient fault must include a "maximum duration" parameter; faults that last longer will be interpreted as permanent by recovery algorithms. Other characteristics are the arrival model and the duration of transients [AVIZ 75a]. <u>Permanent</u> faults are caused by irreversible failures of components. They are characterized by the failure rate parameter; often two or more failure rates are used for the same components under different conditions according to extent and according to value are applicable to both transient and permanent faults.

The <u>extent</u> of a fault describes how many logic variables in the hardware are simultaneously affected by the fault which is due to one failure phenomenon. <u>Local</u> (single) faults are those that affect only single logic variables, while <u>distributed</u> (related multiple) faults are those that affect two or more variables, one module, or an entire system. The physical proximity of logic elements in contemporary MSI and LSI circuitry has made distributed faults much more likely than in the discrete component designs of the past. Distributed faults are also caused by external interference and by single failures of some critical elements in a computer system, i.e., clocks, power supplies, switches used for reconfiguration, etc.

The <u>value</u> of a fault is <u>determinate</u> when the logic values affected by the fault assume a constant value ("stuck on 0" or "stuck on 1") throughout its entire duration. The fault is <u>indeterminate</u> when it varies between "0" and "1" throughout the duration of the fault, but not in accord with design specifications. The determinacy of a

2-8

ţ

fault depends on the failure mechanism. For example, drift of component values or "shorting together" of two signals are likely to cause indeterminate faults.

It is important to note that the description of fault extent and fault value applies at the origin of the fault; that is, at the point at which the failure phenomenon has actually taken place. The faultcaused introduction of one or more incorrect logic values into the computing process often leads to more extensive fault symptoms farther away (in space and/or in time) from the point of failure. At other times, the presence of incorrect logic value is masked by other (correct) logic variables and no symptoms at all appear at more remote points. Confusion and ambiguity are avoided when the term "fault" is restricted to the change in logic variable(s) at the point of the physical hardware failure. The fault-caused changes of logic variables which are observed farther away on the outputs of correctly functioning logic elements will be called "errors." This choice of terms describes the following causeeffect sequence:

- The <u>failure</u>, which is a physical phenomenon, causes a <u>fault</u>, which is a change of logic variable(s) at the point of failure.

- (2) The <u>fault</u> supplies incorrect input(s) to the computing process and may cause an <u>error</u> to be produced by subsequent operations of failure-free logic circuits.

The number of points that can be observed for the purpose of fault detection is limited because integrated circuits are internally complex, and have relatively few outputs. Digital-logic simulation programs which analyze the behavior of faulty logic circuits and predict the errors that will appear on the outputs (for a given class of faults) are essential tools for the generation of fault-detection tests [SZYG 76]. An illustration of a simulation and analysis program to analyze the behavior of faulty circuits is the Logic Analyzer for Maintenance Planning (LAMP) system [CHAN 74]. In addition, LAMP also performs logic design verification, generates fault-detection tests, evaluates diagnostics, and produces data for trouble-location manuals. LAMP

exemplifies the current trend toward multipurpose simulation systems in digital system design.

#### 2.2 TOLERANCE OF PHYSICAL FAULTS

R'

ŝ

ą

٦

Fault-tolerance functions in computer systems are not necessary (redundant' as long as faults do not occur, and they can be deleted from a perfectly fault-free system without affecting its performance. In fault-susceptible systems they are implemented by the means of <u>protective</u> redundancy, which becomes effective when faults occur.

The implementation of fault-tolerance may be discussed from two viewpoints: according to the functions being performed, and according to the forms of redundancy that are used to provide these functions. From the functional viewpoint we distinguish three classes of faulttolerance functions: masking, detection and recovery. Each class contains several distinct approaches to implementation which will be discussed in this section. The other viewpoint distinguishes different forms of protective redundancy. The redundancy techniques have been developed to enable three different forms: hardware (additional components), software (special programs), and time (repetition of operations).

In this discussion, the functional classification is considered to be most suitable for the exposition of implementation techniques. Each function is discussed separately, outlining the redundancy techniques that are available for its implementation.

#### 2.2.1 Fault Masling

The <u>masking</u> function employs redundancy to assure that the effect of a fault is completely contained within a system module. As long as the redundancy is not exhausted, the fault is concealed within the module and no symptoms whatsoever appear on its outputs. When the redundancy is exhausted or overwhelmed by a fault, module failure results. Separate detection and recovery functions are not identifiable when the module is viewed from outside. Because of this, masking has

been called a static redundancy technique [SHOR 68] and has been used in the design of various structures, e.g., airplane frames, bridges, etc., prior to the appearance of digital systems. Masking is also thought to be the form of fault-tolerance used by the nervous systems of living organisms [VONN 56].

A key question in masking i: choice of the size of the module within which the masking occurs. The smallest module is a set of individual hardware components (e.g., diodes, relay contacts, connections, etc.). On the other extreme, a module may be as large as an entire computing system, in which case the module terminals are the output devices. Theoretical analyses of masking usually do not specify the module size; it depends on the feasibility of implementation.

Ì

In digital systems, masking is usually accomplished by hardware redundancy, i.e., by the replication of hardware elements. The fundamental theoretical analysis of masking is due to von Neumann [VONN 56], and Moore and Shannon [MOOR 56]. Its early appearance can be attributed to the previous use of masking in other disciplines of engineering. The techniques of introducing hardware redundancy have been classified into two categories: static and dynamic [SHOR 68]. The static method implements the masking function, since the redundant components contain the effect of hardware failures within a given hardware module, and the outputs of the module remain unaffected as long as the redundancy is effective. The static technique is applicable against both transient and permanent faults. The redundant replicas of an element are permanently connected and powered; therefore, they provide fault masking instantaneously and automatically. However, if the redundancy is exhausted, or if the fault is not susceptible to masking and causes an error, a delayed recovery is not provided. In practice, we find that two forms of static redundancy have been applied in U.S. space program computers: replication of individual electronic components, and triple modular redundancy (TMR) with voting [CCOP 76]. Several other forms have been studied but were not applied either because of their excessive cost or because they required practically unrealizable special components [SHOR 68].

The use of static hardware redundancy is based on the assumption that failures of the redundant replices are independent. For this reason, use of static redundancy is difficult to justify within integrated circuit packages, in which many failure phenomena are likely to affect several adjacent components. Other disadvantages include the cost of massive replication (3, 4 or more times the number of original system elements), the need to assume independent failures of the replicas, and the absence of a warning when a redundant module finally fails. Thus, masking is close to fault avoidance: while it may postpone the time of failure, the module still fails suddenly and irrecoverably when its internal redundancy is exhausted.

Regardless of these shortcomings, masking still may find application because of its conceptual simplicity and its instant action, entirely ransparent to the user. A promising area of application is in protecting a small "hard core" of a system for which other approaches are extremely costly or altogether impractical. Another area is the application in non-electrical, discrete-component technologies, such as fluidic logic for high-temperature or extreme radiation environments.

## 2.2.2 Fault Detection

ţ

ì

The <u>detection</u> function is the starting point of all faulttolerance implementations except for these that depend exclusively on masking. The most sophisticated recovery methods are only as good as the fault detection scheme which initiates their operation. For the purpose of this discussion we say that fault detection has taken place at the time instant at which a <u>fault signal</u> becomes available to be used by a recovery algorithm. All subsequent fault-location actions are considered to be part of the recovery algorithm. The existence of a <u>false</u> fault signal is also possible. This is a false alarm that is due to a malfunction of the fault detection scheme itself.

Fault detection is implemented by means of all the hardware, software and repetition (time) methods that generate the initial fault signal. All these methods may be conveniently grouped according to the

time of their application with respect to the normal operation of the system as follows:

- (1) <u>Initial testing</u>, which takes place prior to normal use and serves to identify faults hardware elements containing imperfections introduced during the manufacturing or assembly processes.

- (2) <u>Concurrent</u> (on-line) detection, which takes place simultaneously with normal operation of the system.

- (3) <u>Scheduled</u> (off-line) detection, which takes place when normal operation is temporarily interrupted.

- (4) <u>Redundancy testing</u>, which serves to verify that the various forms of protective redundancy are themselves fault-free, and takes place either concurrently or at scheduled intervals.

Initial testing follows the production of individual circuits and serves to eliminate the circuits that contain manufacturing defects [BREU 76]. Computer programs for test generation have become an essential tool to facilitate initial testing [SZYG 76], [CHAN 74]. The great internal complexity and a relatively small number of input/ output points in contemporary LSI circuits (e.g., microprocessors, memories, etc.) have made exhaustive logic-level testing, in many cases economically unfeasible. Recent research has emphasized probabilistic approaches [PARK 76] and combined logic and functional testing [MCPH 76]. Initial testing represents a significant part of the total cost of digital circuits and is likely to remain a high-priority research problem for the foreseeable future.

<u>Concurrent</u> (on-line) fault detection during system operation is implemented by means of special hardware or software that operates concurrently with the regular programs of the system. An important advantage or concurrent detection is that recovery can be initiated before fault-caused errors can cause extensive disruption of programs or damage to the data. <u>Hardware</u> methods for concurrent detection have been

used since the first generation of computers. They include errordetecting codes (parity, etc.) [AVIZ 71a], [DOWN 64], duplication and comparison, [DOWN 64] disagreement detectors with majority voters, [ANDE 67] special circuits to monitor certain critical elements (clocks, power supplies, memory write operation circuits, etc.), [DOWN 64] machine status and completion signals, [AVIZ 71a] self-checking logic circuits, [CART 74] and checksumming, timers, and built-in test equipment of various types.

Ŷ

ì

Software methods for concurrent detection either employ the concurrent execution of two (or more) programs, or they consist of special features interwoven with the single program being executed. In the case of two or more identical programs using separate processors and/or multiple storage in separate memories, a comparison is accomplished by a programmed exchange of results [WENS 76] or checksums, [SKLA 76] rather than by hardware comparators. An alternative is to use a dedicated subsystem (e.g., a "maintenance" minicomputer) which executes monitoring programs to observe the operation of the remaining parts of the system. Fault detection features that can be interwoven with a single program include the use of passwords, acknowledgments ("handshakes"), checksumming, reasonableness checks on results, programmed "watchdog" timers, etc. Compared to hardware methods, faultdetection by software is less prompt and more susceptible to disruption by the fault itself. It is used very widely because it can be superimposed relatively easily on an already existing hardware system.

Scheduled (off-line) fault detection is implemented by means of software and requires the interruption of current programs in order to test for the presence of faults. The presence of errors caused by transient faults can be detected by repeating the execution of the same program (or a program segment) and comparing the results. The detection of permanent faults which may have occurred since the last test period requires the running of diagnostic programs or microprograms [BREU 76], [DOWN 64], [RAMA 72]. In principle they are quite similar to the programs for initial testing. The main differences are: time for testing is usually more strictly limited; testing is executed by the system

itself rather than by another computer; and an interconnected assemblage of various circuits must be tested, rather than one circuit at a time. A "bootstrap" approach is very useful, in which a small part of the system is tested first, and then the tested part is used to run further tests on other parts, etc. Microdiagnostics have very good resolution and are especially suitable for this approach [RAMA 72]. Modern systems also frequently contain special hardware features (e.g., test points) which facilitate diagnostics [CART 64]. Although the present discussion deals with use of diagnostics and microdiagnostics for initial fault detection, we must note that they also often serve to locate detected faults to within a replaceable or discardable module as part of the recovery algorithm.

<u>Redundancy testing</u> is a function that is specifically needed by the fault-tolerance features of a system. Its purpose is to verify that these features will be ready to use when a fault occurs. An especially important aspect is to test that various fault signals are ready to act, i.e., that they are not "stuck" in the "no-fault" state. Self-checking logic [CART 74] and periodic schedule tests of fault signals [CONN 72] are suitable here. A second aspect is the checkout of redundant parts of the system (e.g., standby spares, copies used for masking, etc.). While diagnosis programs are suitable for systems with standby spares [AVIZ 71a], the systems with masking are much more difficult to check out, especially those in which masking is at the component level [COOP 76].

### 2.2.3 Recovery

The recovery algorithm comprises all actions that are initiated by the arrival of a fault signal during normal operation and are concluded by the resumption of normal operation (possibly in a degraded mode), by a systematic shutdown of the system, or by system failure.

The most fundamental difference between various recovery algorithms is whether interaction with a human maintenance operator is or is not required as part of the recovery algorithm. Recovery algorithms that do not require human decision making are automatic; all

other algorithms are <u>manually controlled</u>, although they may contain extensive automatic (programmed) sequences. An automatic recovery algorithm may make use of off-line manual repair which takes place later, as long as resumption of normal operation does not depend on manual intervention. Automatic recovery algorithms are further classifiable (according to the state of the system after recovery has been completed) into three classes: full recovery, degraded recovery, and safe shutdown.

<u>Full recovery</u> means the return of the system (within allowed time limits) to a set of conditions that existed before the fault occurred [AVIZ 71a]. Both the hardware and software possess the same computing capacity as before. Failed hardware modules are replaced by spares. Damaged information (programs and data) are returned to a known good state that existed prior to the fault.

Degraded recovery (often called "graceful degradation," or "failsoft operation") returns the system to a fault-free state, but with a reduced computing capacity [BEUS 69]. This means that some hardware elements have been discarded without replacement, some programs and/or data have been lost, or some functions have taken longer than the allowed time. This approach may be called "partial fault-tolerance," since recovery is not 100% successful with respect to the set of prefault conditions. Various "cold start" procedures belong to this category.

Safe shutdown (also called "fail-safe" operation) is the limiting case for degraded recovery. It is carried out when the remaining computing capacity (if any) is below the minimum acceptable threshold. The goals of shutdown are: to avoid damage to remaining stored information and good system elements; to cease interaction with other systems and/or human users in a specified orderly fashion; and to deliver shutdown messages and diagnostic information to designated systems, users, or maintenance specialists.

Full recovery, degraded recovery, and safe shutdown all require certain subsidiary functions which follow fault detection. They are: fault identification and location, error correction in programs

1

THE P

and data, replacement or exclusion of permanently failed elements, and recording of the observations and actions taken thus far. The final step is either a restart of normal operations, or the completion of the shattand sequence. Both hardware and software techniques have been devised to implement these functions. They are discussed in more detail in the following section.

#### 2.3 FAULT-TOLERANT SYSTEMS

2

The ultimate proof of the effectiveness of fault-tolerance techniques is found in the performance of existing systems. For the convenience of discussion, we make the distinction between <u>fully fault-</u> <u>tolerant</u> (or <u>self-repairing</u>) and <u>manually-controlled</u> systems with faulttolerance features. The former complete their recovery actions without the participation of a maintenance specialist, while the latter depend on human decision making as part of the recovery sequence. These decisions may take place at various stages of the sequence, from the initiation of diagnostics to the operation of the switch which disconnects a failed part of the system.

The fully fault-tolerant systems may be further classified according to the availability of external ("off-line") repair. In <u>closed</u> systems repair is not available, and the system inevitably fails after the redundancy resources have been exhausted. Closed systems are usually found in space applications [COOP 76], [AVIZ 71a], [CONN 72]. In <u>repairable</u> systems, failed parts are automatically identified and excluded from further participation in computing. They are then replaced by an off-line repair action. System failures usually occur either because of imperfect fault detection and recovery algorithms, or because of catastrophic faults (i.e., faults that cannot be handled by the recovery procedures that were provided). A less frequent cause of system failure is exhaustion of redundancy, which occurs when faults occur faster than the repair procedure can handle them. Very prominent examples of repairable systems are the several models of the ESS telephone switching systems [DOWN 64], [BEUS 69].

Finally, fault-tolerance systems may be <u>fixed-capacity</u> or <u>degradable</u>. The former are considered failed if a single specified capacity cannot be maintained, while the latter are allowed to go to one or more configurations of lesser capacity before the system is shut down.

### 2.3.1 Hardware-Controlled Recovery Systems

Another classification of fault-tolerant systems may be based on the implementation of the recovery algorithm. Hardware-controlled systems have dedicated hardware which collects fault indications and initiates recovery, while software-controlled systems depend on special programs to interpret fault indications and to carry out the automatic recovery procedures. The hardware-controlled recovery approach depends on special hardware to carry out fault detection and to initiate the recovery procedures. After the existence of a properly functioning software system has been assured, the completion of recovery is usually transferred to software control. It is evident that further software systems may be superimposed on the hardware-controlled design, leading to a multilevel recovery procedure. A special case of hardwarecontrolled recovery is found in statically-redundant systems in which faults are masked by redundant hardware, and thus remain totally invisible to the software. Two examples of such systems are the OAO data processor which used component redundancy and the CPU of the SATURN V guidance computer, which used TMR protection [COOP 76], [ANDE 67]. Probably the earliest use of TMR (triplication and voting) is found in the SAPO computer, designed by A. Svoboda in 1950-53 [OBLO 62]. SAPO also possesses several other fault-tolerance features, including duplication, parity checking, and retry. A separate software-controlled recovery system is needed in statically-redundant systems if they are to continue operating after the first fault escapes the masking effect and affects the software.

Dynamically redundant systems with hardware control usually depend on a dedicated hardware module that gathers fault signals and initiates recovery. Different uses of duplexing and hardware-controlled

switchover techniques are found in the memory, power supply, and peripheral units of the SATURN V guidance computer in combination with a TMR-protected serial CPU unit [ANDE 67]. Separate fault-detection and switchover-control units were used for every functional unit. Probably the first operational computer with fully hardware-controlled dynamic redundancy was the experimental JPL-STAR computer [AVIZ 71a]. Intended for self-contained multiyear space missions, this computer employs a special Test-And-Repair-Processor (TARP) module to control recovery and self-repair. Software assistance is invoked only to perform memory copying and to resume normal operation after self-repair. The French MECRA computer is another early experimental design [MAIS 71]. A few other hardware-controlled system designs that have not reached operation have been described in recent literature [AVIZ 75a]. [CONN 72]. An interesting recent experiment is the C.vmp multiprocessor, which can operate in a fault-tolerant mode as a TMR configuration of DEC LSI-11 computers [SIEW 77].

The principal advantage of hardware-controlled recovery systems lies in their independence of the operation of any software immediately after the fault has occurred. The recovery process is transferred to software only after its ability to operate has been assured. The relatively late appearance of such systems may be attributed to the need to introduce the recovery module into the design at its inception, thereby requiring an early commitment to the hardware-controlled approach.

### 2.3.2 Software-Controlled Recovery Systems

The software-controlled recovery systems depend on special programs to initiate the recovery action upon the detection of a fault. Fault signals are obtained by both hardware and software methods; for example, parity checkers, comparators, power-leve) monitors, watchdog, timers, test programs, reasonableness checks, etc. The main limitation of these systems is the need for the recovery software to remain operational in the presence of faults, since recovery cannot otherwise be initiated. A significant advantage of the software-controlled approach

is that existing "off-the-shelf" hardware system modules may be used to assemble fault-tolerant organizations. These modules contain various forms of hardware fault detection, which usually are supplemented by further software methods. For this reason software-controlled systems appeared earlier and are currently being used in numerous applications requiring high reliability and availability. While every modern operating system incorporates some recovery features, this report is limited to selected illustrations of historically important and advanced systems.

An important early design of the 1950's that had complete duplication and extensive recovery provisions was the SAGE system [EVER 57]. The IBM System/360 architecture contains very complete serviceability provisions for multi-system operation in order to attain high availability, reconfiguration, and failsoft operation [CART 64]. An early example of a multi-system which includes further extensions or the System/360 design is the IBM 9020 multiprocessing system for air traffic control applications [IBM 67]. Noteworthy are the operational error analysis program and the diagnostic monitor of the 9020. An interesting illustration of extensive use of backup storage and dynamic reconfiguration in a general-purpose time-shared system is found in the MIT Multics System [CORB 72]. The Pluribus is a minicomputer/ multiprocessor system (with extensive fault-tolerance provisions), which serves as a switching node in the ARPA Network [KATS 78]. The TANDEM system is a recently announced commercial multiprocessor system with software-controlled fault-tolerance [TAND 76].

Another direction of software-controlled system development is found in aerospace applications. Representative illustrations of this approach are the SIFT design, [WENS 78] the C.S. Draper Laboratory Symmetric Hultiprocessor [HOPK 78] and the COPRA system, [MERA 76] air of which are in design and development stages. An already operational four-computer fault-tolerant complex is the U.S. Space Shuttle computer system [COOP 76], [SKLA 76].

One other area of application which requires fault-tolerant operation and very high availability for several years of continuous operation is the control of electronic telephone switching systems.

These systems usually employ manual repair by replacement of a failed part as the last (off-line) step of the recovery procedure, while maintaining normal operation by means of the remaining system modules. A well-documented illustration is found in the Electronic Switching Systems (ESS) of Bell Telephone Laboratories. The ESS designs use several hardware techniques (duplication, matching, error codes, and functional monitors) and special software (check routines, diagnostics, audits), as well as boftware and hardware emergency procedures when normal recovery action does not succeed [TOYW 78], [BEUS 69]. The Plessey System 250 is a fault-tolerant multiprocessor system for switching system control [HAME 72].

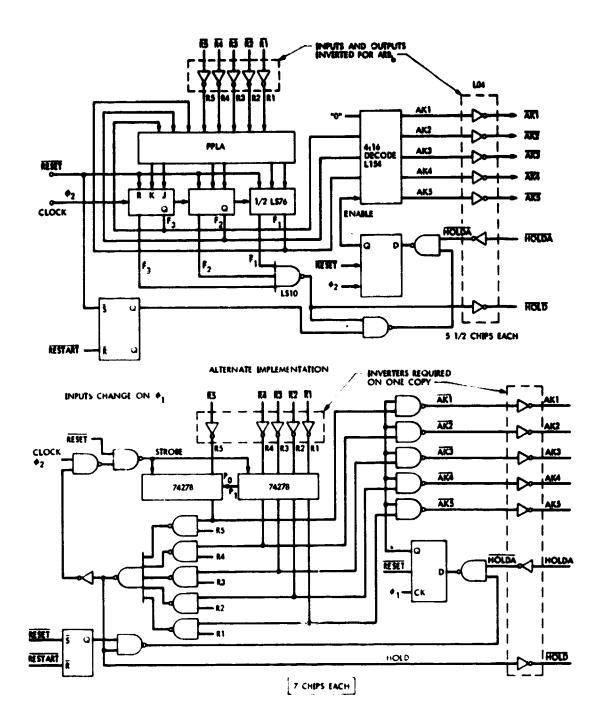

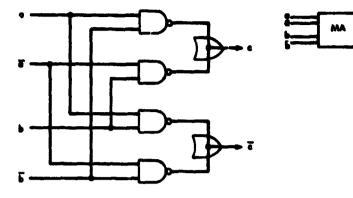

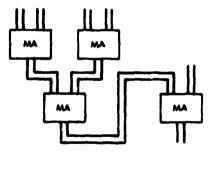

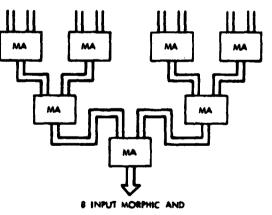

### 2.3.3 Fault-Tolerant Subsystems