NASA Conference Publication 2206

# Ruggedized Minicomputer Hardware and Software Topics - 1981

NASA CP 2206

c.1

LOAN OOPY; RETURN 100 BPWL TECHNICAL LIORANT NIRTLAND AFB, N.M.

Proceedings of a conference held in San Diego, California February 22-25, 1981

NASA Conference Publication 2206

# Ruggedized Minicomputer Hardware and Software Topics - 1981

が開催し

Proceedings of a conference held in San Diego, California February 22-25, 1981

National Aeronautics and Space Administration

Scientific and Technical Information Branch

#### PREFACE

This conference publication contains the proceedings of the Fourth ROLM MIL-SPEC Computer Users Group Conference, held in San Diego, California, February 22-25, 1981. The main purposes of the conference were (1) to promote the interchange of ideas among users of ruggedized minicomputers through description of individual applications, and (2) to report to the computer manufacturer any concerns individual users had relating to the operation of either hardware or software supplied by the manufacturer. While all conference activities related to the use of a single manufacturer's ruggedized computers, many of the novel ideas discussed at this conference have a much wider scope of applicability. None of the company/user interchanges relating to the use of ruggedized minicomputers manufactured by a specific vendor has been included in this publication.

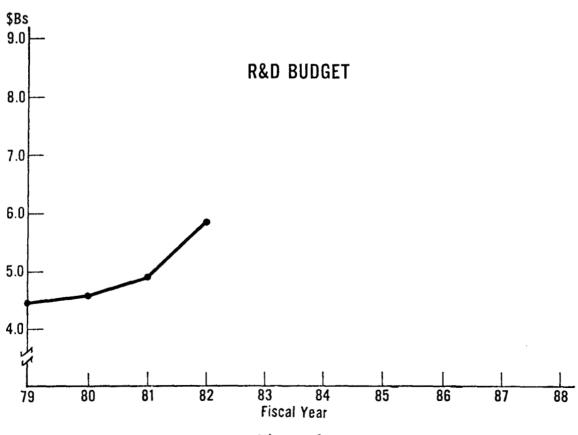

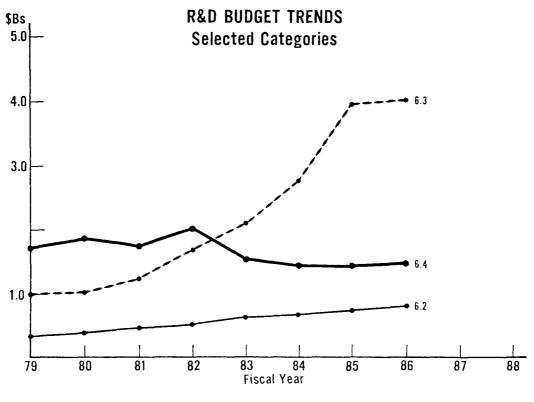

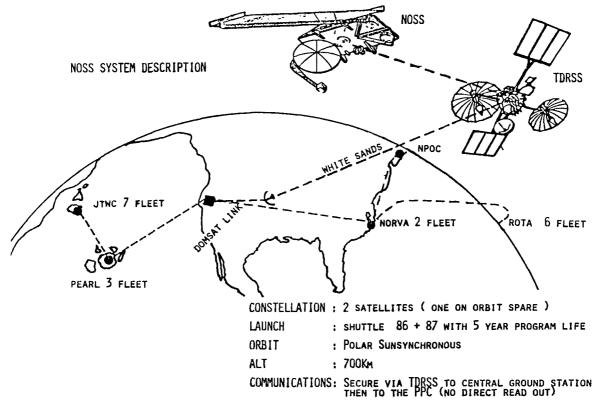

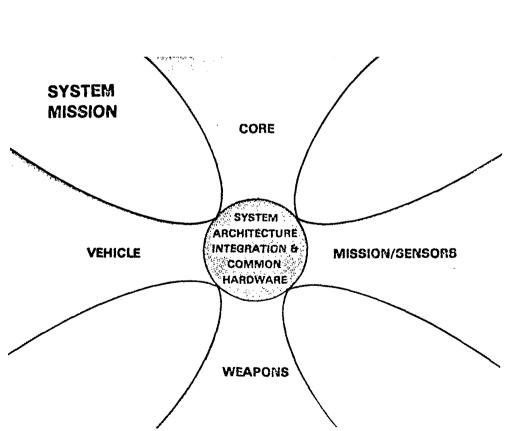

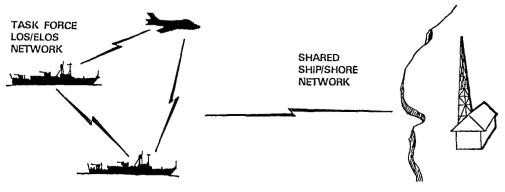

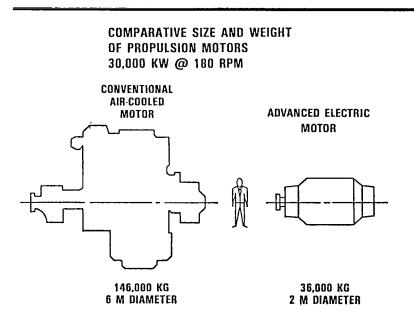

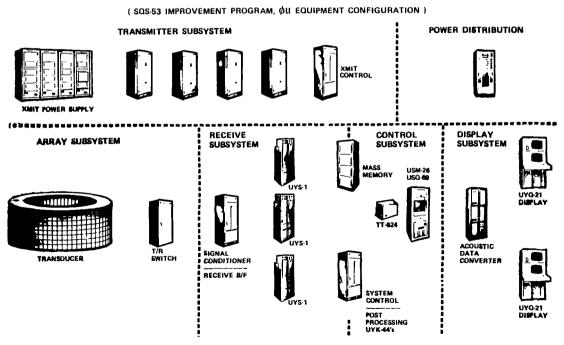

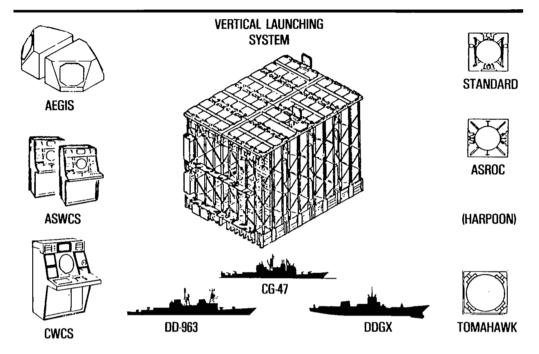

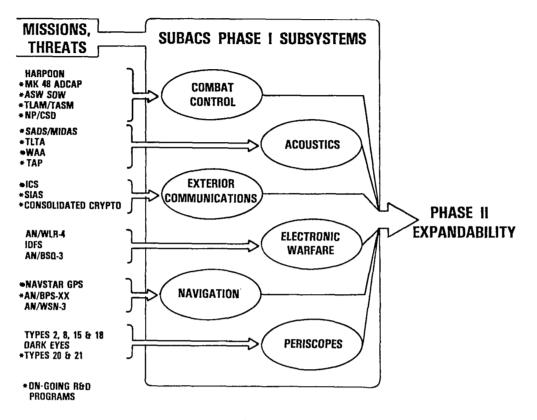

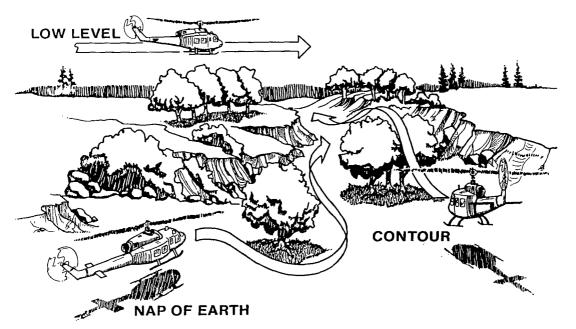

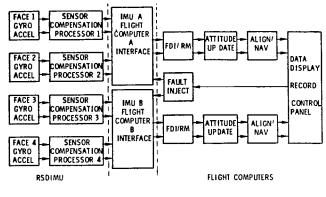

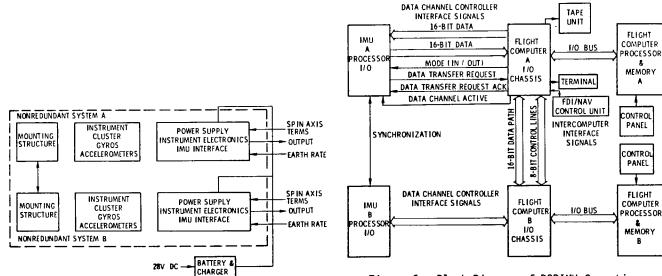

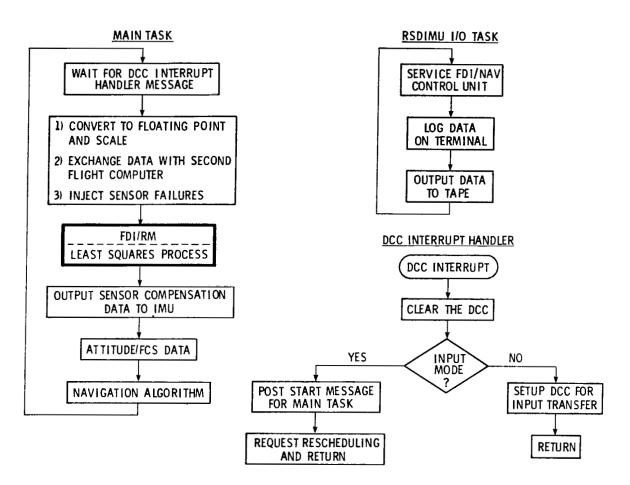

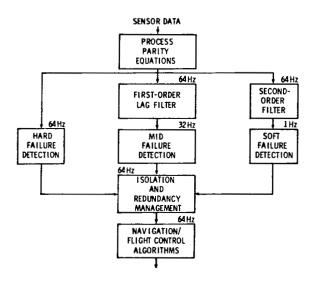

The Fourth Users Group Conference contained presentations covering a wide range of topics, including (1) the role of minicomputers in the development and/ or certification of new commercial or military airplanes in both the United States and Europe, (2) generalized software error detection techniques, (3) realtime software development tools, (4) a redundancy management research tool for aircraft navigation/flight control sensors, (5) extended memory management techniques using a high-order language, and (6) some comments on establishing a system maintenance scheme. In addition, copies of the slides used by the guest speaker detailing areas of new U.S. Navy research and development efforts for 1982 have been included.

The use of trade names or names of manufacturers in this report does not constitute an official endorsement of such products or manufacturers, either expressed or implied, by the National Aeronautics and Space Administration.

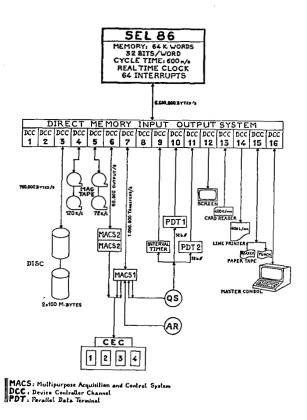

Wayne H. Bryant Eastern Area Vice-President ROLM MIL-SPEC Computer Users Group

#### CONTENTS

「「「「「「「」」」

| PRE | FACE                                                                                                                                | iii · |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1.  | AIRBORNE DATA ANALYSIS/MONITOR SYSTEM                                                                                               | 1     |

| 2.  | ADAMS EXECUTIVE AND OPERATING SYSTEM                                                                                                | 23    |

| 3.  | SYSTEM PERFORMANCE ANALYZER                                                                                                         | 33    |

| 4.  | ON-BOARD COMPUTER PROGRESS IN DEVELOPMENT OF A<br>310 FLIGHT TESTING PROGRAM                                                        | 47    |

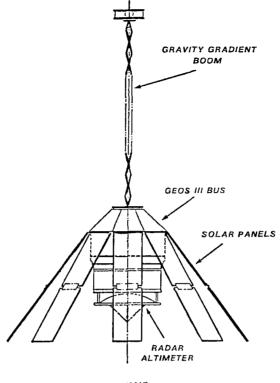

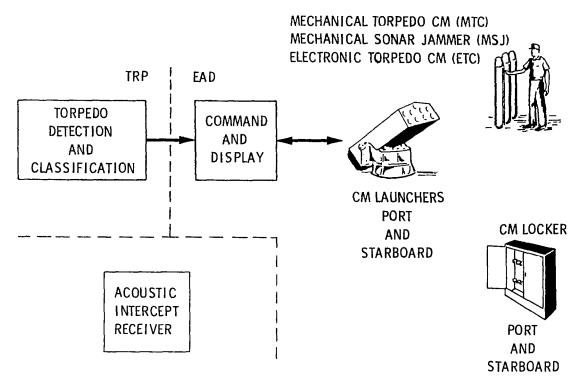

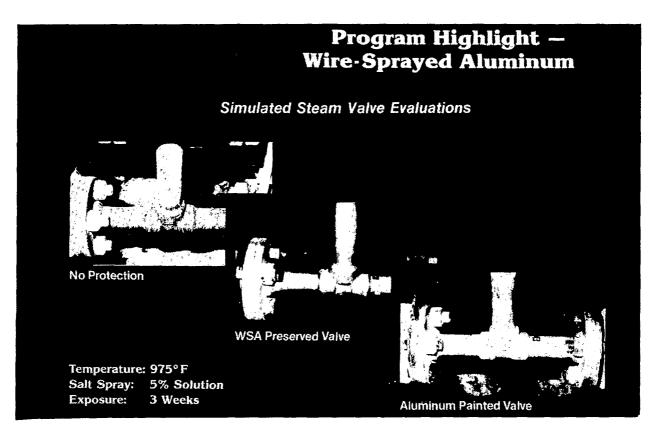

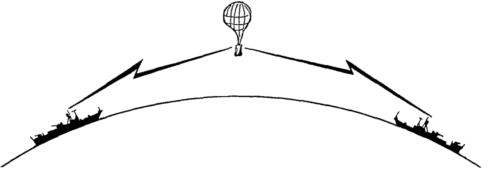

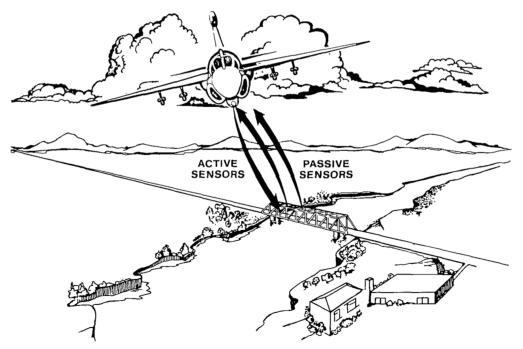

| 5.  | NEW STARTS IN RESEARCH AND DEVELOPMENT 1982                                                                                         | 59    |

| 6.  | SOFTWARE ERROR DETECTION                                                                                                            | 109   |

| 7.  | ARTS BETA TESTING REPORT                                                                                                            | 115   |

| 8.  | REAL TIME SOFTWARE TOOLS AND METHODOLOGIES                                                                                          | 133   |

| 9.  | USE OF SOFTWARE TOOLS IN THE DEVELOPMENT OF<br>REAL TIME SOFTWARE SYSTEMS                                                           | 151   |

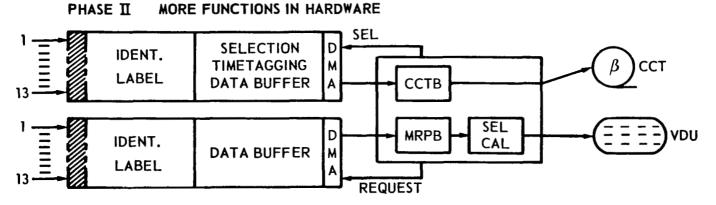

| 10. | ROLM COMPUTERS IN THE FLIGHT TESTING OF THE<br>FOKKER F29 AIRCRAFT                                                                  | 171   |

| 11. | FAULT ISOLATION TECHNIQUES                                                                                                          | 193   |

| 12. | EXTENDED MEMORY MANAGEMENT UNDER RTOS USING FORTRAN                                                                                 | 197   |

| 13. | DESCRIPTION OF A DUAL FAIL-OPERATIONAL REDUNDANT<br>STRAPDOWN INERTIAL MEASUREMENT UNIT FOR<br>INTEGRATED AVIONICS SYSTEMS RESEARCH | 209   |

| ATT | ENDEES                                                                                                                              | 219   |

-- -- -- -

#### AIRBORNE DATA ANALYSIS/MONITOR SYSTEM

#### Darryl B. Stephison Boeing Commercial Airplane Company Seattle, Washington

#### ABSTRACT

The Airborne Data Analysis/Monitor System (ADAMS) is a ROLM 1666 computerbased system installed onboard test airplanes and used during experimental testing of those airplanes. ADAMS provides real-time displays to enable onboard test engineers to make rapid decisions about the conduct of the test. Such decisions have reduced the cost and the time required to certify new model airplanes. These decisions have also improved the quality of data derived from the test, leading to more rapid development of improvements resulting in quieter, safer, and more efficient airplanes. The availability of airborne data processing removes most of the weather and geographical restrictions imposed by telemetered flight test data systems.

ADAMS receives sensory input from a separate onboard data acquisition and recording system. Sensory data is converted to engineering units using automatically selected transform functions matching the characteristics of the data acquisition system. Depending on operator selected options, a variety of more complex data transformations are performed to reduce the large volume of data to more meaningful indicators of data quality, test conduct, and airplane performance. The operator may also select several output devices and/or formats to meet the needs of the particular test. A data base is maintained to describe the airplane, the data acquisition system, the type of testing, and the conditions under which the test is being performed.

In addition to the 1666 computer, the ADAMS hardware includes a DDC System 90 fixed head disk and a Miltope DD400 floppy disk. Boeing has designed a DMA interface to the data acquisition system and an intelligent terminal to reduce system overhead and simplify operator commands. The ADAMS software includes RMX/RTOS and both ROLM FORTRAN and assembly language are used.

#### I.0 INTRODUCTION

The Boeing Commercial Airplane Company is currently unchallenged as the nation's leader in commercial aircraft sales. The company's ability to design, build, and market better airplanes and a greater variety of airplanes is significantly dependent on the ability to prove the airworthiness of those airplanes and to provide data for continuing product improvement. The flight testing of commercial jet airplanes to serve those needs has always been expensive and time consuming. The post-test analysis of flight test data frequently showed that tests had not been performed correctly or that target parameter values had not been reached. This resulted in repeat testing. Boeing is now using onboard digital computer systems for analysis of flight test data in real time. This enables engineers onboard the test aircraft to make rapid decisions about the conduct of the test. Such decisions have reduced the cost and the time required to certify new model airplanes and have improved the quality of data derived from the test. The availability of airborne data processing removes most of the weather and geographical restrictions imposed by telemetered flight test data systems.

#### I.I Background

Boeing first used computer data processing to aid in the analysis of flight test data in the early 1950's as part of the B-52 flight test program. Manual calculations were unsatisfactory, especially for determination of net thrust for an eight-engine airplane. With the introduction of commercial jet transports, Boeing began to record flight test data on magnetic tape. These magnetic tapes were used as input to ground-based computer data processing systems for post test data analysis. Throughout the 707, 727, and 737 projects, improvements were made to the data acquisition, data recording, and data processing systems. Computing techniques were continually developed, progressing from the IBM 701 through the UNIVAC 1103A, the IBM 7094, and the IBM 360.

The concept of an airborne data monitor based on a general purpose minicomputer was introduced in the early 1970's in connection with the Pulse Code Modulation (PCM) data acquisition system to be used in testing of the E3A (AWACS) airplane. The AWACS Preflight and Data Acquisition System (APDAS) was implemented in 1973. This system was based on a Data General NOVA 1220 computer. When a similar system was proposed for commercial airplane testing, the need for a more rugged main frame was identified. Experience with APDAS had shown that more processing could be done in this type of system and the concept of "Application Programs" was introduced. The Airborne Data Analysis-Monitor System (ADAMS) was implemented in 1975 to provide an onboard, real time, data monitor and analysis capability based on the ROLM 1602 Ruggednova.

In 1977, after an extensive review of ADAMS capabilities, problems, and deficiencies, a decision was made to redevelop ADAMS using the most up-todate design and implementation methodologies practical for the project. After a considerable effort to define and document the requirements for the system and a study of hardware and software tools available, a design concept was adopted based on the ROLM 1666 Processor, the DDC System 90 Fixed Head Disk, RMX/RDOS, and ROLM FORTRAN. About the same time a decision was also made to redevelop the ground-based computing system using the IBM 303X Processor and several Digital Equipment Corporation PDP-11 Processors as peripheral processors. The thrust of these redevelopment efforts was the impending 767 and 757 airplane certification test programs scheduled to begin in October of 1981.

A prototype system was installed on an airplane in early 1980 to make an initial test of the system. The system was known to have several bugs and only a subset of the total functions to be included in the final system. While this was expected to prompt many complaints, the single item most vividly identified in this demonstration was the painfully slow system response.

Simple instrumentation (to be presented in another paper) was very helpful in locating the source of our sluggish performance. As much as 80% of all instruction executions were in RMX/RDOS system space. As a result of further investigation, a decision was made to change operating systems in midstream to RMX/RTOS. This involved a considerable conversion effort which was not in the project plan. By late summer, the conversion had been successfully completed. Additional optimizing of RMX/RTOS and our own executive subsystem have brought a reasonable performance level into view.

#### 1.2 Environment

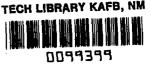

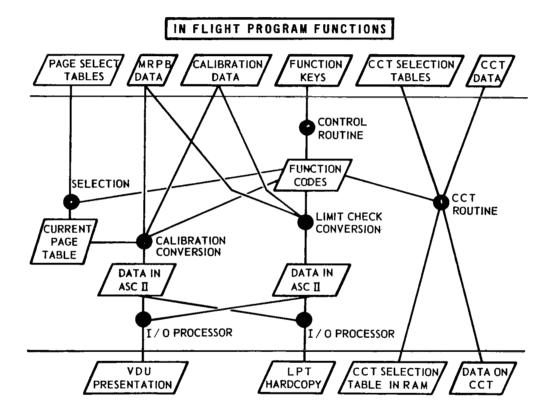

ADAMS is part of a complex data gathering and processing capability as shown in Figure I. Onboard the test airplane, inputs from transducers and electrical/electronic systems in the airplane are combined into serial pulse code modulated bit streams by the Data Acquisition System. The serial bit streams are recorded on magnetic tape and/or input to ADAMS. The magnetic tape is used after the flight as input to the Data Processing Ground Station, the purpose of which is to strip selected parameters from the magnetic tape and pass these to the Test Data Processing System for final processing. Final data is output as graphical displays, tabulations, hardcopy plots, and magnetic tape files. Much support is required in terms of data base parameters to keep all processes running. A large data base is maintained by a Data Base Management System. Data base parameters required to support the airborne systems are written to the appropriate storage media by the Instrumentation Sub-System. This data consists of PROM's to support the Data Acquisition System and floppy disk files for ADAMS.

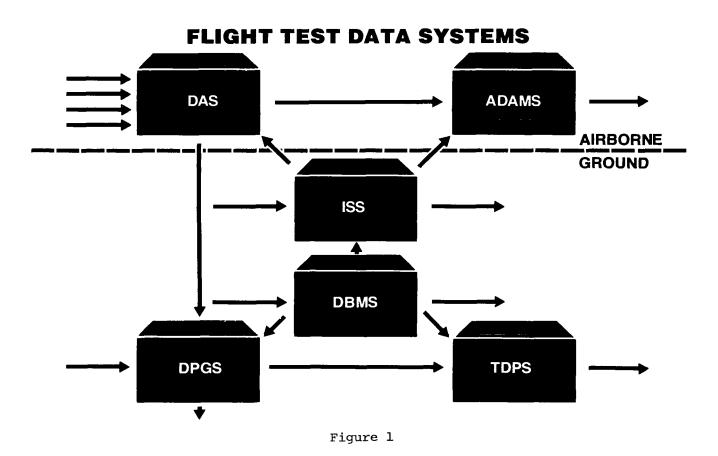

ADAMS thus has four major external interfaces as shown in Figure 2. The primary data flow into the system is the serial PCM code received from the Data Acquisition System. The primary output from the system is display information. The system is transaction driven with most processing being initiated by commands from the operator. Data base files and program files are received from the Instrumentation Sub-System in the form of RMX/RDOS compatible floppy disk files.

#### 2.0 HARDWARE

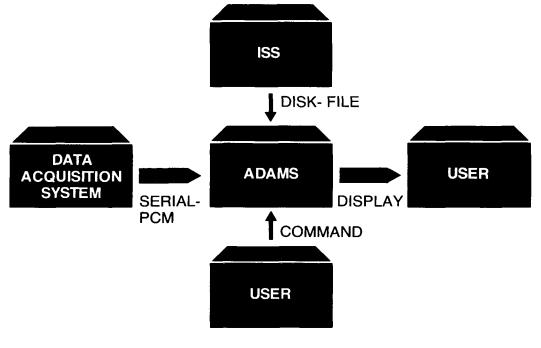

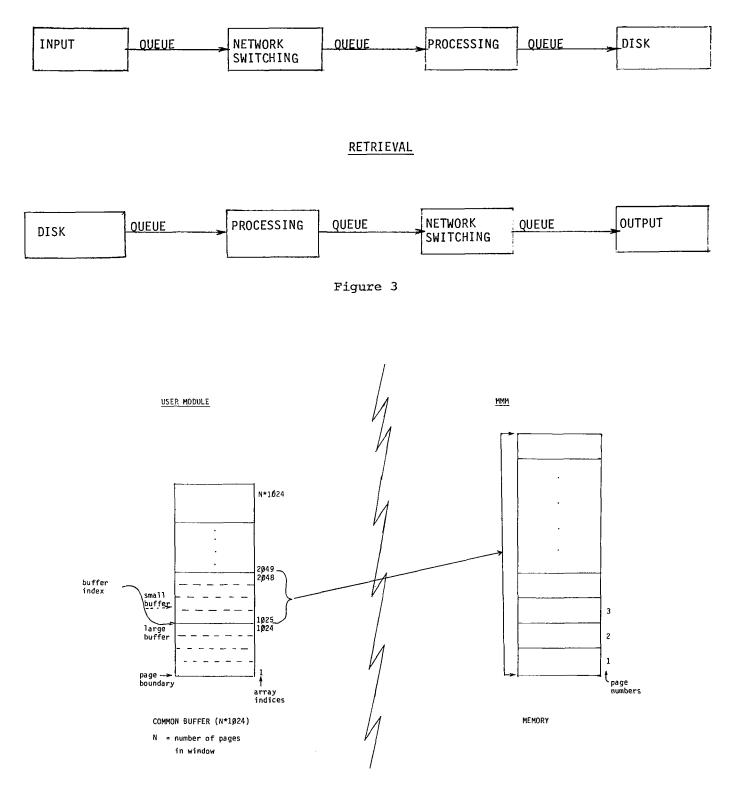

The hardware for ADAMS can be simply viewed as a central processor surrounded by four major types of peripheral equipment corresponding to the four major external interfaces as shown in Figure 3.

#### 2.1 Central Processor

The ADAMS II Central Processor is a ROLM 1666 computer including the main frame, control panel, and 16-slot I/O expansion chassis. The I/O expansion chassis contains an I/O Bus Repeater, a Disk Controller, an Asynchronous Line Multiplexer, a Basic I/O Interface, and a Floppy Disk Interface purchased from ROLM. In addition to these purchased interfaces, Boeing has designed and built an interface for the Datametrics DMC1500 Line Printer and a Measurement Data Bus Interface which is part of our PCM subsystem.

#### 2.2 PCM Input

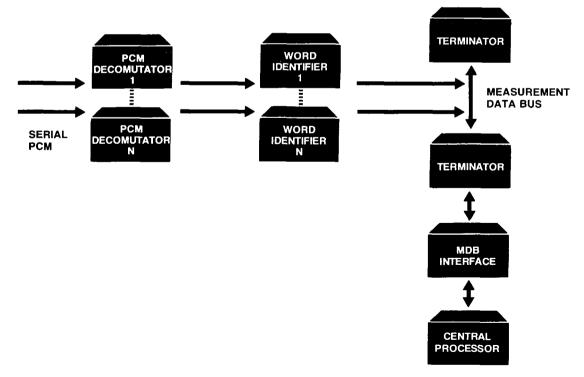

The PCM Input Subsystem is shown in Figure 4. This subsystem converts serial PCM data to parallel data, identifies each word of data and places each data word and its identification on the Measurement Data Bus. Each data word is then transferred to the core memory of the ROLM 1666 by direct memory access. The PCM Decommutator provides bit, frame, and subframe synchronization and converts the serial PCM to parallel data. The Word Identifier provides a unique identification for each word of parallel data. Boeing has designed and built the MDB Interface which deposits the data in core memory based on the identification.

#### 2.3 Display Devices

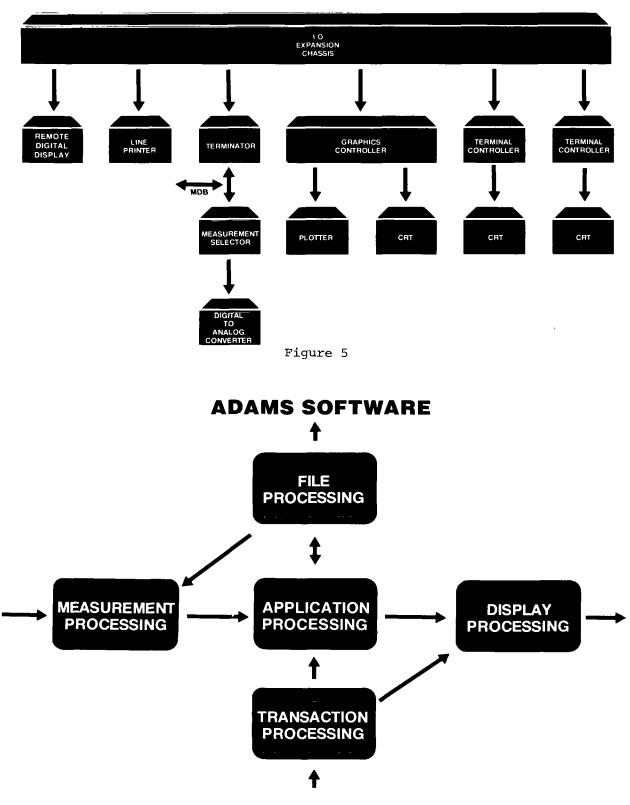

The major Display Devices are shown in Figure 5. There are two operator stations, each consisting of a CRT, keyboard, and terminal controller. Boeing repackaged a commercial CRT to make it suitable for airborne service. The Boeing-designed terminal controller includes an Intel SBC 80/204 single board computer. Typical terminal functions are enhanced by the addition of control functions unique to ADAMS. These functions relieve the Central Processor of overhead processing required for a more generalized terminal. A graphics display capability consisting of a Graphics Controller, CRT and a Plotter is currently being integrated into the system. Analog output from the system is available from a Digital-to-Analog Converter and a Measurement Selector. Connection of these devices to the Measurement Data Bus enables the system to output either selected raw PCM parameters or processed data from the ROLM 1666. The Line Printer gives alphanumeric hardcopy output capability. The Remote Digital Display is a Boeing-designed, five-digit numeric indicator driven by RS232C signals from an ALM port.

#### 2.4 Disk

The mass storage capability of ADAMS consists of a fixed head disk and a floppy disk. The 4M byte fixed head disk has been modified for airborne use by the substitution of a 400 Hz motor and power supply. The two-drive floppy disk is mainly used for transportation of data base and program files from ground based systems to the airplane in preparation for a test flight. During normal operation of ADAMS, only the fixed head disk is accessed.

#### 2.5 Keyboard

The simplest of hardware components in ADAMS is the keyboard. This is a Microswitch Keyboard which has been packaged by Boeing to make it suitable for the airborne environment. The keyboard is connected to the Terminal Controller. In addition to typical keyboard functions, the ADAMS keyboard has a number of fixed string keys and eight user defined string keys. The Terminal Controller handles character echoing and other command processing functions to relieve Central Processor overhead.

#### 3.0 SOFTWARE

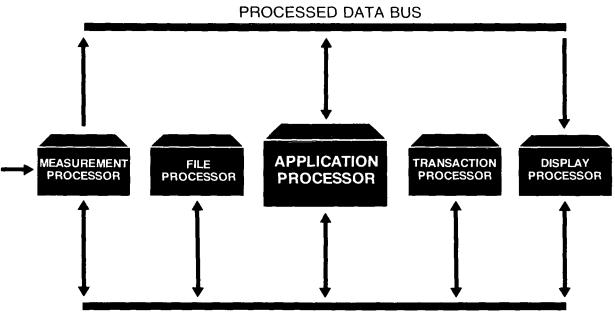

The software within the Central Processor can be viewed as one or more Applications surrounded by peripheral processes as shown in Figure 6. As at the hardware level, each of the peripheral process types is related to one of the four major external interfaces. Measurement processing converts the raw PCM parameters to engineering units parameters (i.e. having units such as degrees, pounds, volts, etc.). Display processing includes device drivers and additional routines to allocate devices to Applications or resolve conflicts when two or more Applications compete for use of a Display Device. Transaction processing accepts operator commands, loads Application program code, schedules Application execution, and passes command arguments to the Applications. File Processing includes disk I/O drivers, a form of data base management, and temporary disk file management.

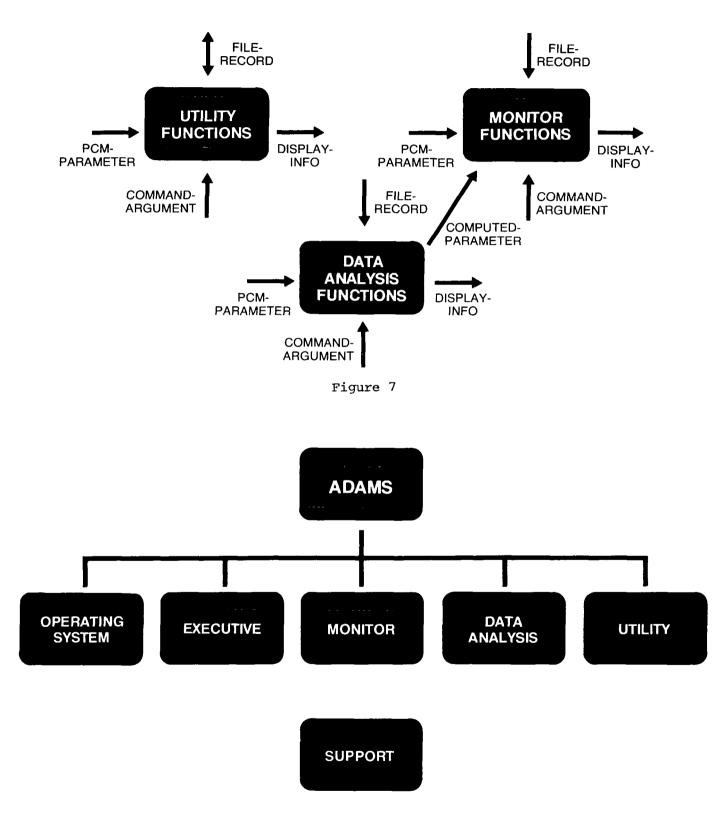

The peripheral processes shown in Figure 6 have been divided into Operating System and Executive functions. The portion of device handling, memory

management, and task management handled by the ROLM RMX/RTOS are called Operating System functions. Additional resource management, measurement processing, transaction processing, file management, data base management, and system initialization functions unique to ADAMS are called Executive. There are three types of Application functions as shown in Figure 7. These are called Monitor, Data Analysis, and Utility functions. Additional "stand-alone" software is also provided with ADAMS. Thus, the breakdown of ADAMS software is shown in Figure 8.

#### 3.1 Operating System

The ADAMS Operating System is basically the ROLM RMX/RTOS. The system has been modified by Boeing with the substitution of an improved terminal driver, an improved ALM driver, an improved line printer driver, an improved real time clock handler, an improved power fail recovery, an improved system error handler, and the addition of a Measurement Data Bus driver. A file manager has been added to allow creation, deletion, opening, reading, and writing of temporary disk files.

#### 3.2 Executive

The Executive performs supervisory functions necessary to support execution of Monitor, Data Analysis and Utility functions performed by ADAMS. The supervisory functions are in areas of measurement processing, device management and allocation, data base management, transaction processing, system initialization, and other miscellaneous processing.

A more detailed discussion of the ADAMS Executive will be presented in another paper.

#### 3.3 Monitor

The ADAMS Monitor functions are the primary display generating functions. These functions are used to generate standard displays of either PCM parameters or computed parameters.

The Quicklook function selectively builds displays of the current engineering units or raw PCM for up to 20 measurements. The update rate of this display is approximately once per second. Measurement identification number, title, and units are also displayed. Measurement values are evaluated against predefined preflight or flight limit values. Displayed measurements exceeding these limits are visibly identified.

The Hardcopy function controls the transfer of data from the operator display screen to the printer in response to a command. No tranformation of data occurs.

The Printer Time History function generates a display on the printer of a tabulated listing of engineering units data for up to ten measurements. Selectable sample rates from one sample in ten seconds to ten samples per second are provided with default to one sample per second. Measurement identification number and units are provided at the beginning of each tabulation. Operator event marking of the output is also provided.

The Analog function selects, scales, and outputs up to 16 engineering units parameters to the digital to analog converter.

The Panel function selects up to 20 engineering units parameters and outputs these parameters to panel display modules. A positive indication is made to the panel display observer if and when the Panel function is not updating. Operator selected panel update rates of from one to five samples per second are provided with default to one sample per second.

The Graphics function selects up to 20 engineering units parameters plus time and formats these for output using the graphics display. Up to seven parameters are displayed in real-time. The remaining parameters are stored for non-real-time plotting. Storage is sufficient for up to 10,000 data values. Plot formats are of two types, X-Y plot or strip chart. Format information is entered manually or on file records created using FTCS. In the strip chart format up to six engineering units parameters are displayed as a function of time in a manner similar to the chart recorder analog output. In this format the storage of the Graphics function is used to store old data which has been "scrolled" off from the display. This old data may be later redisplayed as a nonreal-time plot.

#### 3.4 Data Analysis

The Data Analysis functions convert PCM parameters to computed parameters. In addition, these functions may build special displays. The first three of these functions are fundamental and are prerequisites for operation of several other Data Analysis functions.

The Gross Weight function computes current gross weight of the airplane and fuel density for each engine.

The Basic Airplane function computes various fundamental aerodynamic parameters such as airspeed, altitude, Mach number, ambient air temperature, and lift coefficient.

The Engine Thrust function computes engine net thrust and various other engine performance parameters using generalized engine thrust curves.

The General Calculations function enables the user of ADAMS to define realtime processing to be done by the system with a minimum of design flow time. Definitions are entered in the form of FORTRAN assignment statements.

The Averages function enables the user of ADAMS to define summary processing to be done by the system with a minimum of design flow time. Definitions include averages, minimum, maximum, slopes and integrals.

The Cruise function computes various periodic parameters relevant to cruise performance testing. These parameters are made available for display using the various monitor functions and also stored for later post-condition processing by the Cruise Summary function.

The Cruise Summary program computes slopes and averages for various parameters stored by the Cruise function and uses the results to refine the computations of the Cruise function.

The Take-Off function computes various real-time and summary parameters relevant to take-off and landing performance testing.

The Stalls function computes various real-time and summary parameters relevant to stall performance testing.

The Flight Controls function computes various real-time parameters relevant to stability and control testing.

The Acoustics function computes various real time and summary parameters relevant to aircraft noise testing. Summary parameters are displayed on the screen. The operator is able to "edit" the summary data. The Acoustics function then transmits the summary data to an acoustics data processing system on the ground.

The Loads function is used during structural testing to combine several PCM parameters according to "linear multiple equations" to produce real-time parameters. In addition, this function compares PCM parameters to predefined limits and produces reports of discrepancies.

The Power Plant function computes several real-time and summary parameters relevant to engine evaluation testing.

The Winds function is used during cruise performance testing to determine wind speed and direction and other real-time parameters useful in analyzing cruise data.

The Deviations function is used to compute the deviation of an input parameter from a steady state value.

The Rosette function is used in airplane structural testing to compute total stress from rosette strain gages.

The Pressure Coefficients function is used in pressure survey testing to compute coefficients of port pressures (ratio of port pressure to reference pressure) and to plot pressure distribution as a function of port position both in real time and as a summary average.

The Airspeed Calibration function is used to add position error corrections for a variety of pressure ports on the airplane to a reference pressure (such as trailing cone) and determine the speed of airflow over the pressure ports.

#### 3.5 Utility

The ADAMS Utility functions are primarily used to aid the operator in getting the system ready for a particular in-flight test or condition. Some of these functions are also used to check the operation of the data acquisition system or prepare this system for flight. These functions generate special displays of PCM parameters and/or file records.

The Editor function is the primary function by which the operator may display, modify, insert or remove Data Base file records. This function may be used in flight; however, any time it is used, it is expected to be used to prepare for a specific test or condition.

7

The Help function generates special displays of instructive text which may aid the infrequent or novice operator to make commands controlling the various functions.

The Preflight function assists the operator to perform operational checks of PCM parameters prior to flight and to record the status of parameters checked. This function also performs noise checks on selected PCM parameters and/or compare groups of PCM parameters which may be expected to have the same value to point out deviations from the norm.

The Setup function is used to load the contents of PCM Decommutator and Word ID memories and/or verify the contents of these memories.

The Functional Test function is used to maintain records of checks made on PCM parameters by instrumentation engineers prior to the first flight of an airplane. This function also provides displays of text to instruct the operator on how to make these checks.

The Strain Gage Bridge Response function provides linear regression coefficients to correlate bridge outputs with applied loads during airplane structural calibrations.

The Loads Inertial Correction function computes loads inertia correction constants for each linear multiple equation performed by the loads function.

The Directory Dump function provides the operator with brief listings of Data Base record identifiers.

The Calibration Fit function will compute regression coefficients (linear single section, linear multiple section, or polynomial) for a set of data points obtained during a measurement calibration performed onboard a test airplane.

The Calibration Conversion function will convert lab calibration regression coefficients into coefficients usable by ADAMS in the absence of support from FTCS. This function will also combine calibration coefficients from two or more transducer components to produce a single set of calibration coefficients usable by ADAMS.

#### 3.6 Support Functions

The ADAMS software includes certain "stand-alone" programs which may be run on the system in lieu of the normal ADAMS program. These programs are used to troubleshoot a malfunctioning system or prepare a new system for use.

A version of RMX/RDOS single user BASIC with several assembly language subroutines is supplied to allow the ADAMS user to implement small utility functions of his own design with a minimum of implementation flow time. The implementation of BASIC as a support function detracts from its usefulness because the ADAMS Monitor functions cannot be run at the same time. It is hoped that this can be corrected in future improvements to ADAMS.

Diagnostic programs are provided with ADAMS as necessary to troubleshoot and repair the ADAMS hardware. This includes the ROLM IDMS and those diagnostic programs provided by ROLM which are applicable to ADAMS.

Additional diagnostic programs for ADAMS unique hardware are added to the diagnostic diskette by Boeing. Boeing also plans to enhance the ROLM System Reliability Test by the addition of tests for ADAMS unique hardware.

A Memory Dump module similar to the RMX/RDOS core dump module can be added to the ADAMS software for use in development work. This allows core image files to be written to floppy disk during debugging and software testing. This module is generally not included in delivered systems.

#### 4.0 DATA BASE

The ADAMS Data Base contains parametric data required to support the ADAMS software in the processing of flight test data. These parameters consist of data items subject to change between airplane models or between tests. The primary objective in designing ADAMS to include a Data Base was to make the software airplane and test independent.

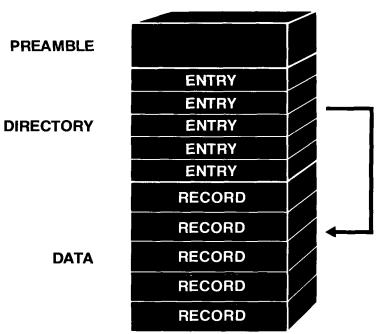

The Data Base consists of several contiguous disk files. These are RDOS files which have been moved from floppy disk to fixed head disk prior to a test. Each file contains a logically related set of parameters. The type of parameter and the logical key are the determinants of which file will contain a parameter. The array of Data Base files is shown in Figure 9.

The MIT (Measurement Information Tables) Data Base file contains information necessary to obtain PCM data, convert the data to engineering units and display the data with standard Monitor functions.

The CONFIG (Configuration Information) Data Base file contains additional measurement information useful in preparing the Data Acquisition System for a test or troubleshooting a malfunctioning measurement.

The LIST Data Base file contains lists of up to 20 measurements which may be displayed by the Monitor functions.

The PRG (Program Information) Data Base file contains initialization and control information necessary to bring the Application functions into execution.

The TCP (Test/Condition Parameters Table) Data Base file contains parameters which define the particular test or condition (a portion of a test) to be performed on the airplane.

The APT (Airplane Parameters Table) Data Base file contains parameters which define the airplane under test.

The GC (General Calculations) Data Base file contains information which defines processing to be done by the General Calculations function. In general, each record in this file is an expression definition consisting of FORTRAN assignment statements.

The AV (Averages) Data Base file contains information which defines processing to be done by the Averages function.

The PCM Data Base file contains tables of control parameters to be loaded into the PCM Decommutator by the Setup function.

9

The WID (Word Identifier) Data Base file contains tables of control parameters to be loaded into the Word Identifier by the Setup function.

The KEYF (Key File) Data Base file contains ASCII strings to be treated as commands in lieu of actual keyboard entries.

The POS (Position) Data Base file contains list position information used by the ADAMS operator to sequence through the display of several lists of measurements.

The HELP Data Base file contains operating instructions and system information to be displayed by the Help function.

The EDIT Data Base file contains record format definitions for the other Data Base files. This information is used by the Editor function to display Data Base file information.

The LOADS Data Base file contains information which defines processing to be done by the Loads function. Each record in this file defines a "linear multiple equation" by which strain gage inputs are combined by the Loads function.

The RELOC (Program Relocation) Data Base file contains information used by the Job Controller to load and relocate Application functions.

The MSG (Message) Data Base file contains error message strings which are displayed on the operator screen in the event of an error.

The FT (Functional Test) Data Base file contains records of functional checks made on the Data Acquisition System prior to the first flight of an airplane. These records are maintained by the Functional Test function.

The FTST (Functional Test Support Text) Data Base file contains text consisting of instructions for completing functional checks and calibrations onboard the airplane prior to first flight.

The MISC (Miscellaneous) Data Base file contains information used by several Application functions such as display formats and initialization constants.

Each Data Base file has three major parts as shown in Figure 10. The first part of a Data Base file is the Preamble. The Preamble contains file identification and applicability information such as file name, airplane model, airplane identification, test identification, date and time of Data Base file generation or modification. The second part of a Data Base file is the Directory. The Directory is used to locate information within the Data Base file. The third and final part of a Data Base file is the Directory is associated with a single Data record. Both the Directory and Data areas are padded with sufficient space to allow addition of a reasonable number of new Entries and Records.

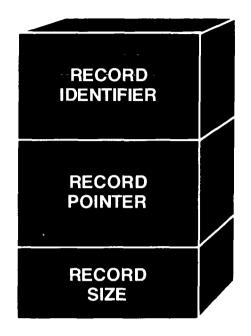

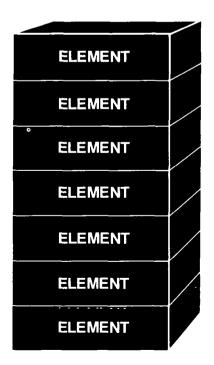

Each Directory Entry as shown in Figure 11 consists of a Record Identifier, a Record Pointer, and a Record Size. Record Identifiers are floating point numbers for some Data Base files and four ASCII characters for others. Record Pointers are double precision byte addresses of the beginning of the associated records relative to the beginning of the file. The Record Size word contains the number of words in the associated Data Record.

Within each Data Record as shown in Figure 12, there may be several Data Elements. These may be floating point numbers, integers or ASCII strings. In some Data Base files, all Data Records have the same format; in other Data Base files the format is dependent on the Application for which they are used.

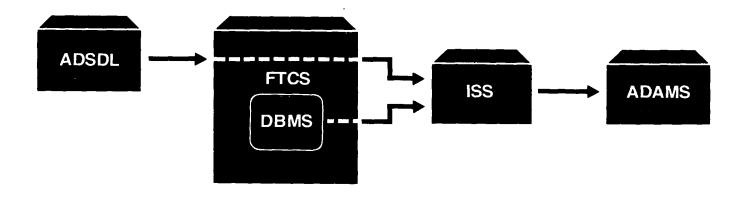

#### 5.0 SUPPORT SYSTEMS

The ground based computer systems supporting ADAMS are unique to Boeing Flight Test and deserve some discussion. These systems are shown in Figure 13. The Airborne Data Systems Development Laboratory (ADSDL) is the software development facility for ADAMS. The Data Base Management System (DBMS), one of two systems referred to collectively as the Flight Test Computing System (FTCS), is used to maintain data base parameters to support all of the Flight Test data processes. The Instrumentation Sub-System (ISS) is used to generate transportable media (floppy disk) to transfer Data Base Files and Program files from the ground based systems to ADAMS.

#### 5.1 Airborne Data Systems Development Laboratory

All the ADAMS software is developed in the Airborne Data Systems Development Laboratory (ADSDL). Permanent installations include two Data General Eclipse computers and two ROLM 1666 computers. The Data General Eclipse \$200 and \$230 share a 200-megabyte disk. Each computer operates in a dual program mode allowing four programmers to have full system capability. A four-drive AED 6200 floppy disk is connected to each computer and a system driver has been written and installed in the ARDOS and ZRDOS systems. ROLM software, including the ROLM FORTRAN Compiler, the Macro Assembler, the Relocatable Loader, and the RMX/RTOS System Generation program, have been purchased in source form, assembled, and installed on the system. This allows programmers to develop software to the core image form (save and overlay files). Programs are then moved to the floppy disk and moved to one of the two ROLM 1666 computers for debugging and software testing. Each of these computers is installed in a nearly complete ADAMS hardware complex (some peripheral equipment is shared). The ability to play back copies of flight data tapes allows a simulation of in-flight conditions. When programs have been satisfactorily demonstrated in the ADSDL and are ready for airborne use, they are transmitted to the Flight Test Computing System (FTCS). This is accomplished by the use of an RJE-HASP link and the running of the Data General HASP Emulator (HAMLET) on the Eclipse S230.

#### 5.2 Flight Test Computing System

The Flight Test Computing System (FTCS) is a large and complex system based on an IBM 3033 computer. A complete discussion of this system is beyond this text; however, the important functions relating to ADAMS are worth noting. The most important function of FTCS relative to ADAMS is the maintenance of data base parameters. The Data Base Management System (DBMS) in FTCS controls a very large collection of parameters to support not only ADAMS but many other functions in Flight Test as well. The DBMS receives data interactively from several operators throughout Flight Test using menu driven display screens. On command from an operations engineer responsible for a particular test airplane, appropriate data base parameters are transmitted to the Instrumentation Sub-Systems (ISS) to be made into Data Base files for use by ADAMS. Transmission is via RJE-HASP links.

In addition to the DBMS function, FTCS performs a sort of packet switching function to distribute ADAMS program files. These program files are treated as binary data sets and are held by FTCS only until valid reception has been acknowledged by each ISS. No transformation of the data is done by FTCS.

#### 5.3 Instrumentation Sub-System

The Instrumentation Sub-Systems (ISS) are DEC PDP-11 computers which are used as intelligent output ports for FTCS. Other local functions are also performed in support of the Flight Test Instrumentation group. Each ISS includes a two-drive AED 6200 floppy disk. System drivers are not used for the floppy disk but rather local drivers in application programs do all I/O to this device. This allows formatting and initialization of floppy disks in RMX/RDOS format and the creation and writing of Data Base and Program files on these diskettes.

#### 6.0 OPERATIONAL SCENARIO

The preparation and operation of the Flight Test data processing systems require coordination of many people, both within and outside of the Flight Test Engineering organization. Much consideration has been given in the design of all of these systems to the diversity of people who must interface with them.

#### 6.1 Preflight

Requests for data are received by the Flight Test Engineering organization from other organizations throughout the Boeing Commercial Airplane Company. These typically include design, research and development, flight simulation and customer support organizations. The Flight Test Analysis engineers analyze these requests as well as current Federal Aviation Administration requirements for airplane certification to determine what parameters must be acquired and recorded and what data processing must be done to satisfy the total data need. As a result of this analysis, a list of instrumentation requirements is developed using the DBMS. Initial receipt of such a list on the ISS prompts Flight Test Instrumentation engineers to begin designing and implementing installations of Data Acquisition and ADAMS hardware. The Analysis engineer may also request new data processing capability for either ADAMS or TDPS. The Airborne Data Processing group analyzes airborne data processing requests and designs and implements new functions as necessary. After satisfactory demonstration of software in the lab, released software is transmitted from ADSDL to FTCS and forwarded to ISS. The Analysis and Instrumentation engineers must work interactively with the DBMS to build data base parameters necessary to support Data Acquisition, ADAMS, DPGS and TDPS. Meanwhile, Flight Test Operations engineers prepare a plan of test which is the script for directing the test.

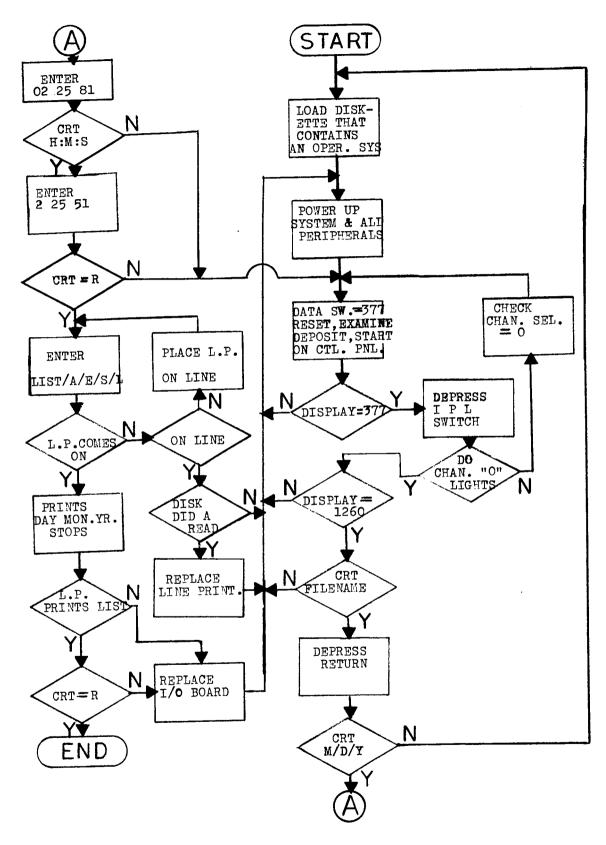

ADAMS is made operational as soon as the installation on an airplane is complete. Diagnostics are run to prove operability and then the system software and Data Base files are moved from floppy disk to fixed head disk. ADAMS is used to check the operation of the Data Acquisition System. Checks are made on each PCM parameter using the ADAMS Monitor functions and records are kept with the aid of the Functional Test function. On-board calibrations are made if necessary, aided by the Calibration Fit and Strain Gage Bridge Response functions. Throughout the installation phase, data base parameters in FTCS are continuously updated by interactive input.

Shortly before first flight and each flight in the test period, the most current Data Base files are installed on the ADAMS disk. Within the data base are indicators of which PCM parameters are required for the current test. Operational checks are made on each of these parameters. The Preflight function aids in this process and is used to maintain a record of the process. When each parameter has been checked and all airplane systems are ready for flight, the airplane is released for flight.

#### 6.2 Flight

Upon release of the airplane, the flight crew boards the airplane. In addition to the pilot, copilot, and flight engineer, the flight crew typically includes Operations Instrumentation and Analysis engineers as necessary to direct, monitor, and evaluate the test. In many cases, representatives of requesting organizations or the FAA are also included.

As the pilot, copilot and flight engineer check the airplane for flight, the Instrumentation and Analysis engineers check the Data Acquisition System and ADAMS. Data Base parameters are displayed and verified. Application functions used for preflight are replaced by Monitor and Data Analysis functions appropriate for the current flight.

When all systems are ready for flight, the flight data recorder is turned on, the engines are started and the test begins. Since all of the systems required to accomplish flight testing are self-contained on the airplane, testing is not restricted to the local area. If the weather or field characteristics in the local area are not suitable for the current test, the airplane may be flown anywhere within its normal flight range.

The conditions for each test (airspeed, altitude, engine settings, etc.) can be accurately adjusted and verified using the Monitor and Data Analysis functions. If the conditions cannot be met, time is not wasted performing tests which might produce questionable data. This type of cost-saving decision can only be made because accurate processed data is rapidly available whenever and wherever the airplane flies.

The conduct of the test is closely monitored to insure that all testing is done strictly according to plan. The real-time data reduction performed by ADAMS condenses a large number of measured parameters to a few of the most significant indicators of test conduct and airplane performance. This enables a few engineers to monitor hundreds of parameters in real time.

As each item on the test plan is completed, the results of testing may be quickly compared to results of previous tests and to design predictions. Output data formats have been designed to maximize the similarity between ADAMS output and ground based final data output. This eases the comparison task. In some cases, target data values are even contained in the ADAMS Data Base to enable Application functions to make these comparisons. If test results should fail to meet design predictions, decisions can be made in flight on whether to continue the line of testing or to suspend the testing until corrections can be made. Again, cost savings are realized because early decisions are made which can only be based on processed data.

#### 6.3 Post-Flight

After completion of a test flight, the flight data tape is normally taken to the Data Processing Ground Station to begin the stripping of usable data from the tape. ADAMS may be used either on the airplane or in a lab to play back the flight data tape. This allows additional analysis of the flight data to determine the extent of usability. Requests for processing by DPGS and the Test Data Processing System are thus minimized, resulting in additional cost savings.

Selected data which has been extracted from the flight data tape and transmitted to TDPS is processed by applications similar in function to ADAMS, but much larger in scope. The absence of time constraints and the availability of very large storage allow much more complex data transformations to be accomplished.

With final data in hand, the Analysis engineers prepare reports to the organizations which requested the data, including the FAA. Meanwhile, on all but a few Boeing owned airplanes, the special equipment is removed and the airplane is prepared for delivery to a customer airline.

#### 7.0 FUTURE SYSTEMS

The future of airborne data processing in Boeing Flight Test is a steadily increasing demand for processing capacity, speed, and reliability. We believe that this demand can be best met by the introduction of a multiple processor system. A possible configuration is shown in Figure 14. Other concepts are being evaluated. Microprocessor technology is being viewed with considerable interest because this could allow the configuration of a system particularly tailored to a specific Flight Test application. A combination of microprocessor elements with the medium scale ROLM 1666 is likely.

# ADAMS EXTERNAL INTERFACES

Figure 2

## **ADAMS HARDWARE**

## ADAMS PCM INPUT SUBSYSTEM

### **ADAMS DISPLAY DEVICES**

Figure 6

# **ADAMS APPLICATIONS**

# **ADAMS II DATA BASE**

i |

\_\_\_

|               |               |        | $\angle$ | /    |       | $\angle$ |  |

|---------------|---------------|--------|----------|------|-------|----------|--|

|               |               | МІТ    | ТСР      | PRG  | GC    | AV       |  |

| DATA          |               | CONFIG | РСМ      | WID  | KEYF  | POS      |  |

| BASE<br>FILES | $\rightarrow$ | LIST   | HELP     | EDIT | LOADS | RELOC    |  |

|               | Ļ             | ΑΡΤ    | MSG      | FT   | FTST  | MISC     |  |

Figure 9

# ADAMS DATA BASE FILE

Figure 10

# **ADAMS DIRECTORY ENTRY**

Figure ll

## ADAMS DATA RECORD

Figure 12

# **ADAMS SUPPORT**

Figure 13

# **ADAMS MULTI-PROCESSOR SYSTEM**

COMMAND AND CONTROL BUS

Figure 14

### ADAMS EXECUTIVE & OPERATING SYSTEM W. D. Pittman Boeing Commercial Airplane Company Seattle, Washington

#### ABSTRACT

The ADAMS Executive and Operating System is a multi-tasking environment under which a variety of data-reduction, display and utility programs are executed. This environment provides a high level of isolation between programs which allows them to be developed and modified independently.

#### INTRODUCTION

The Airborne Data Analysis/Monitor System (ADAMS) was developed to provide a realtime data monitoring and analysis capability on board Boeing commercial airplanes during flight testing. It inputs sensor data from an onboard data acquisition system and converts it to engineering units data, derives airplane performance data by applying transforms to the collected sensor data, and presents this data to test personnel via various display media.

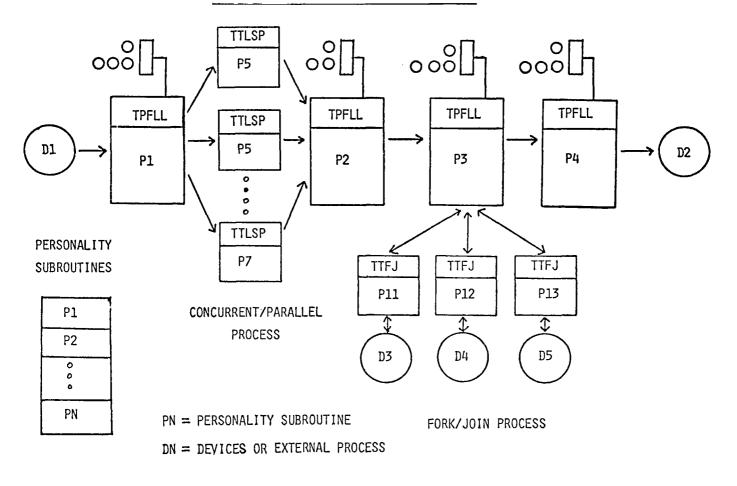

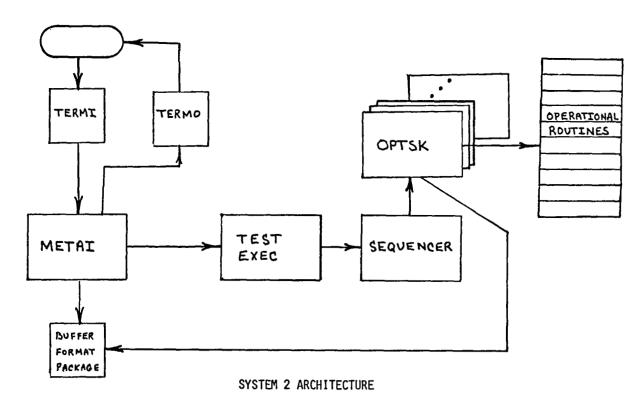

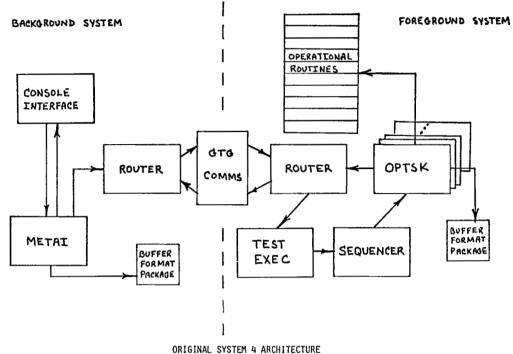

ADAMS is a real time transaction-oriented computing system. ADAMS operators input processing requests at the system consoles as necessary to evaluate flight test conditions (a simplified model of ADAMS is shown in Figure 1). Operator requests are input to the system executive which then schedules the requested processes. Active processes retrieve operator commands, airplane sensor data and support data via the executive, send processed data to the executive for subsequent input to other active processes, and send formatted data to display devices via executive device management software. These processes perform functions such as the collection and display of engineering units data on various output media (line printer, CRT display, graphics display, strip chart recorder); collection and reduction of real time data (data averaging and integration, computation of derived parameters); and support processing (support data display and modification, hardware setup, system checkout).

#### DESIGN CONCEPT

ADAMS is based upon the concept of functionally independent parallel processes which are initiated and controlled by explicit operator commands. Although dozens of processes are available to be invoked by the operator, typically only a subset of the total is selected to run concurrently. The demand for system resources made by these processes is so varied that a suitably versatile program environment was deemed Since it was expected new functions would be added to the system on a necessary. regular basis and that existing functions would be updated and modified frequently, it was also a requirement that the functional capability of ADAMS be quickly adaptable and easily extendable. In order to meet these requirements, it was decided to develop the system around a vendor-supplied operating system and implement ADAMS functions as independent programs written in a high level language. Since the ROLM 1666 was selected as our system processor, RMX/RDOS and ROLM FORTRAN became the operating system and high level language upon which the system was based, although it was expected that the operating system would have to be enhanced or modified in order to implement the program environment which was desired.

One of the goals during the development of ADAMS was that the various application programs be very loosely coupled with one another. Another was to isolate the applications from the hardware and operating system and provide them with very high level interfaces with which to communicate with their environment. The programs would use these interfaces to fetch and store engineering units data, communicate with the operator, fetch and store support data, and output to display devices.

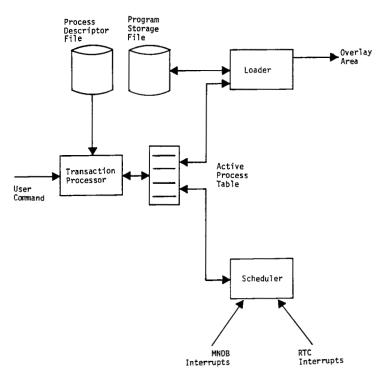

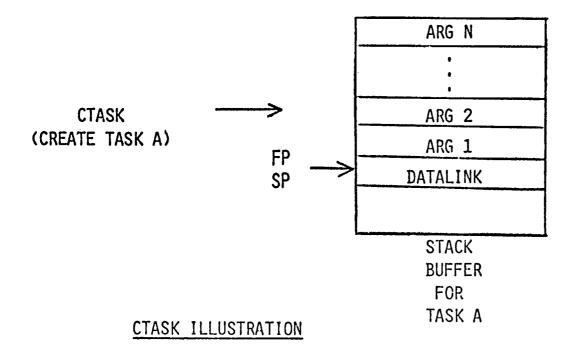

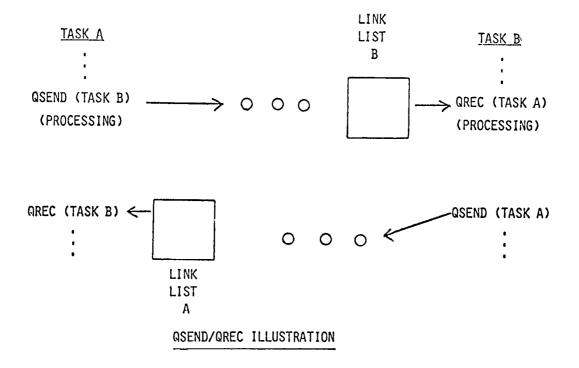

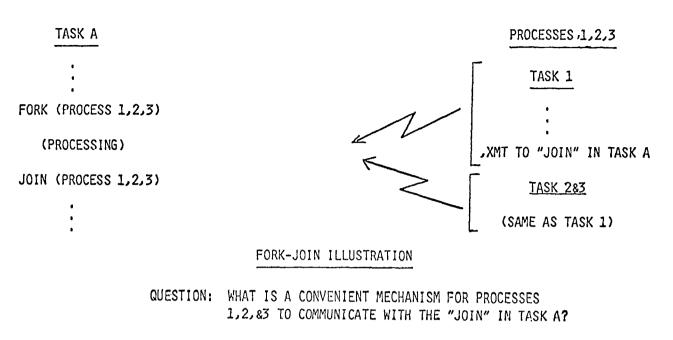

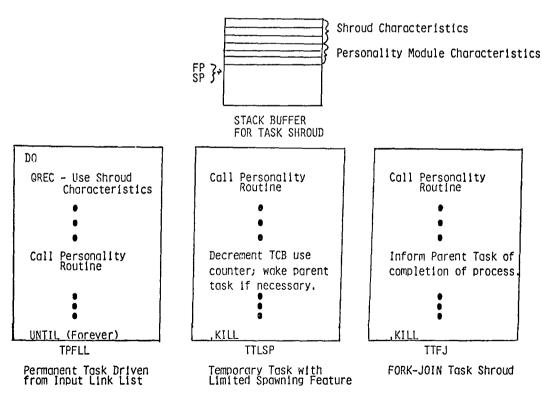

#### SYSTEM DESCRIPTION

The management of ADAMS application programs is accomplished by the transaction processor, scheduler and loader, as shown in Figure 2. The transaction processor accepts and validates user commands for requested processing. If the command was a legal request and the requested process was not active, then the transaction processor will read the process descriptor from disk and install it into the active process table. The process descriptor contains information such as iteration rate, priority, overlay name, status information, and program location, and is used by the scheduler and loader to execute the process as required. The scheduler (via real time clock and measurement data interrupts) determines when each active process is ready to begin execution. If the overlay defined for the process is not in core when the process is ready, then the loader will load the overlay into memory and the process will begin execution, otherwise the process will begin execution when ready.

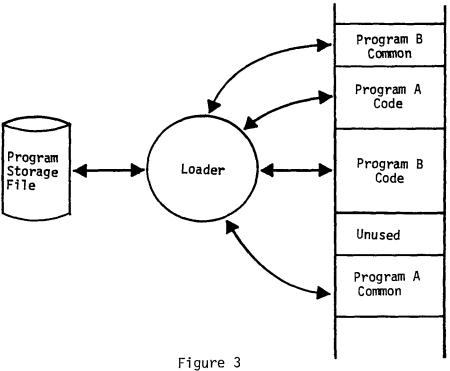

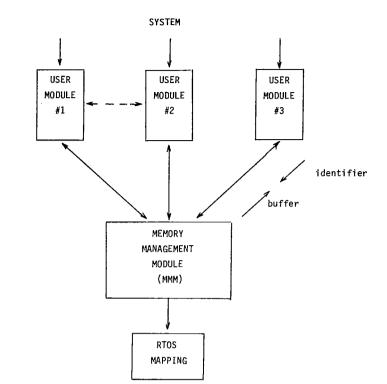

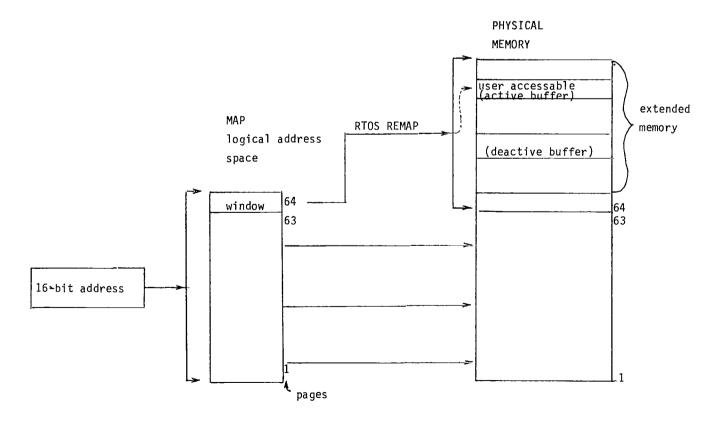

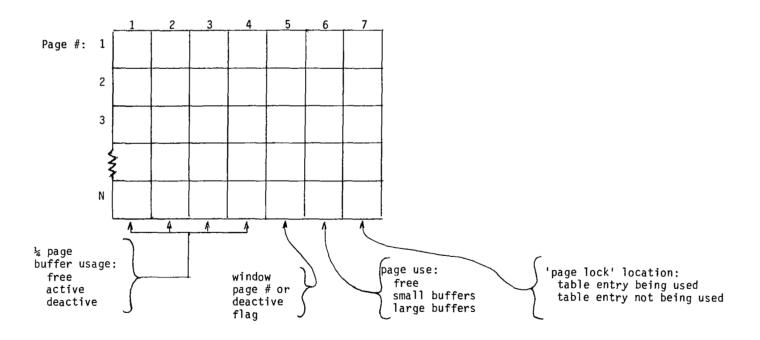

Very early in the design of ADAMS it was recognized that main memory would be a very limited resource. It was anticipated that all of the required ADAMS application programs would not fit in available memory (64K). Furthermore, the likelihood that those programs required to run in parallel would not fit in memory together was very high. The most obvious solution to the problem was to buy the required additional memory; however, it was felt that buying the memory required for 32 systems would not be cost effective. Another alternative was to use the disk overlaying capability provided by the RMX/RDOS operating system, which was rejected because it was too limited to support our processing requirements.

The approach which was adopted relied on a run time program loader to swap ADAMS programs between disk and main memory (Figure 3) and a scheduler to execute the programs. When a program is ready to execute, the loader loads the program's common storage block and code into memory, swapping out any idle programs if necessary to make room. The loader adjusts all references by the program to the common storage block and external routines.

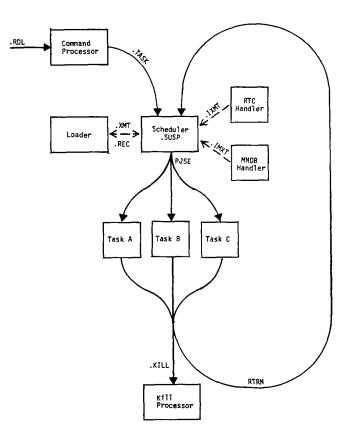

The program scheduler uses many of the facilities of RMX/RTOS to start and maintain the execution of ADAMS programs (Figure 4). An RMX/RTOS task is defined for each active program beginning at the scheduler starting address. When the task begins execution, it calls the loader, which installs the appropriate overlay into memory. The scheduler then executes the overlay as a subroutine, after which time it suspends until restarted by the real time clock handler when its cycle time has expired or by the Measurement Number Data Bus handler when a specified data item is input to the system. Appropriate status words are maintained for each program which allow the loader to move programs to and from disk as required for execution. (Of course if all executing programs fit into available memory, then swapping is not required.) A kill processor releases all system resources held by a program when it is terminated and is initiated either by an UNLOAD command received from the operator, or because the program finished executing a non-cyclic overlay and no cyclic overlay was specified, or because a software malfunction was detected in the program. All data flow to and from ADAMS application programs is controlled by the system executive. Programs are not allowed to directly communicate with each other, nor are they allowed to communicate with the system or the external environment except through the interfaces previously mentioned. These interfaces, which are accessed via FORTRAN subroutine calls, define the data flow through the system and provide a consistent and simplified access method for system resources (Figure 5). Isolating the programs from one another allows them to be developed independently and reduces the risk of unwanted side-effects when application, executive, or operating system software is modified. Isolating the programs from the system resources reduces the risk of the inadvertent corruption of those resources. The access method to system resources reduces much of the effort required to develop application programs and defines a simplified conceptual model of the program environment.

The Measurement Data Generator is the conduit through which all cyclic data is passed through the system. It performs two functions for application programs: fetch engineering units data and save engineering units data. The fetch function retrieves a previously saved data value or fetches the sensor data (which is continuously being DMA'ed into memory) and converts it to engineering units. Conversion and calibration information for each sensor is stored in the support data base. The save function stores a data item for subsequent retrieval by other programs.

The Device Manager interfaces the application programs to the various ADAMS devices such as the line printer and system consoles. It provides high level FORTRAN calls to communicate with the devices and handles contention among application programs for those devices.

The File Manager provides a high level interface to the system disk for application programs and other executive functions. It is an enhancement of the limited RTOS disk support facility and provides routines to create, delete, open, close, read and write disk files. All disk data transfers are buffered by the system in a manner similar to that done by RMX/RDOS.

The Data Base Manager implements the access method by which programs fetch, store and modify the system support data. Each item in the support data base is identified by a unique key which is used by the program to request action on the item.

The application programs alter their own or other programs' execution status via calls to the Job Controller. These calls are used to start and send commands to other programs, change their own or other programs' iteration rate, unload (kill) themselves or other programs, chain to new overlays, or adjust the size of their common storage.

ADAMS is based upon a modified version of the RMX/RTOS operating system. Most of the features of that operating system have been retained, but many of the device drivers have been modified, a disk file management facility was added, the system error and trap handling facility was expanded, and task calls have been added or modified.

Many of the existing RTOS device drivers (TTY, LPT, ALM) have been or are being modified to improve their efficiency or adapt them to accommodate special ADAMS devices. A driver to handle a Boeing-designed data bus interface was implemented and integrated with RTOS, and a real time clock handler was installed to facilitate the scheduling of ADAMS programs.

The system error and trap handler was added to allow ADAMS to attempt recovery from software malfunctions. It gains control of the CPU when a processor trap or system

error is detected (stack overflow, unimplemented instructions, jump zero, etc.). If the error occurred while executing an application program, then that program is killed and all system resources held by that program released. If the error occurred while executing the executive or operating system, then the system is reinitialized (rebooted) and the operator informed of the malfunction.

Two task calls, LOK and UNLOK, have been added to allow processes and system resources to be locked and unlocked. The inclusion of these calls allows the locks to be cleared if the requesting task is killed. Other task calls have been modified to reduce system overhead.

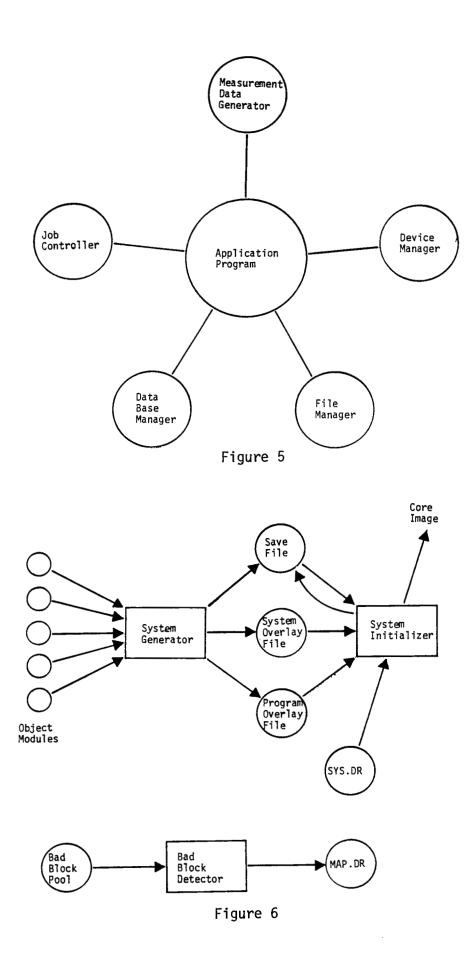

In addition to the executive and operating system software described previously, ADAMS relies on three support programs (Figure 6). The first of these is a system generator which executes on a Data General Eclipse minicomputer. It uses a version of the ROLM relocatable loader and a Boeing developed utility program to link and load all system and application program object modules. It produces an executable save file, a system overlay file, and an application program overlay file. The system overlay file contains position independent system overlays, while the program overlay file contains program overlays and relocation information. The second of these programs, the bad block detector, executes on the ROLM 1666 processor. It searches the bad block pool on the fixed-head disk for bad blocks and sets the appropriate bits in MAP.DR to prevent those blocks from being used. This is necessary because the RMX/RTOS disk driver does not do bad block mapping. The third of these programs, the system initializer, runs under RMX/RDOS on the ROLM 1666. This program searches the disk for all files required during execution of ADAMS and inserts an entry for each into the RTOS disk table in the ADAMS save file, then "boots" the save file, bringing the ADAM System into execution.

#### SYSTEM DEVELOPMENT

During 1979, a prototype of ADAMS was developed which executed in the RMX/RDOS environment. This version was installed on a test airplane early in 1980 to make an initial evaluation of the system. Even though only a small subset of our application programs had been developed up to that point, it was very clear that the performance of the system was far below what was required.

We had fortunately anticipated the need to analyze system performance and had developed instrumentation hardware which allowed us to measure the performance of a program executing in the 1666. This instrumentation enabled us to sample the program counter in the 1666 and thus produce a histogram which displayed a distribution of time versus memory location.

Using the output of our instrumentation we were able to verify that the CPU was saturated and that about 80% of the time was being spent in RMX/RDOS system space, the majority of which appeared to be in swapping system overlays and handling serial I/O. Since by this time ROLM had released the RMX/RTOS operating system, the decision was made to abandon RMX/RDOS and convert the system to run under RMX/RTOS.

The similarities between RMX/RTOS and RMX/RDOS greatly aided the conversion effort, although numerous bugs in the released version of RMX/RTOS required a great deal of effort by our own software engineers to isolate. (We have since decided to maintain our own version of RMX/RTOS.) Although a disk file management capability had to be developed, the ADAMS Executive was converted and was executing under RTOS within three months. The isolation of the application programs from the operating

system had also been a great advantage; except for minor modifications required for one or two programs, the application programs were able to execute in the new environment.

The improvement in performance was dramatic: operating system overhead was reduced from 80% to about 50%, and memory usage of the Executive and Operating System was reduced from about 50K to about 32K. Additional optimization to both the operating system and executive since then has improved their performance to a reasonable level.

#### FUTURE DEVELOPMENT

期前

Experience gained during the development and initial use of ADAMS has revealed limitations in system capability, while ever-increasing requirements for airborne data processing will require improved system performance. Three approaches are now being taken to improve system capability: enhancement of 1666 resident software, increasing the power/performance of the 1666, and distributing the processing load to additional computers.

The 1666 resident software will be enhanced to improve the reliability of the system. The memory protection features of the 1666 will be used to further isolate application programs from each other and from the system executive, thus reducing the risk of an aberrant program corrupting the system. Improvements to the system build process, consisting of a special relocatable loader to build program overlays and a utility to edit the program overlay file, will reduce the time required to generate systems and improve the maintainability of the system.

Development is already underway to improve the performance of the 1666 processor. Since a significant portion of ADAMS' CPU resources is spent servicing the various output displays, the decision was made to develop intelligent general purpose interfaces to handle the system I/O processing. These interfaces, which are planned to replace the TTY, ALM and printer interfaces, will be programmable to enable them to be adapted to a variety of devices, and will handle data transfers to and from the 1666 memory via DMA.

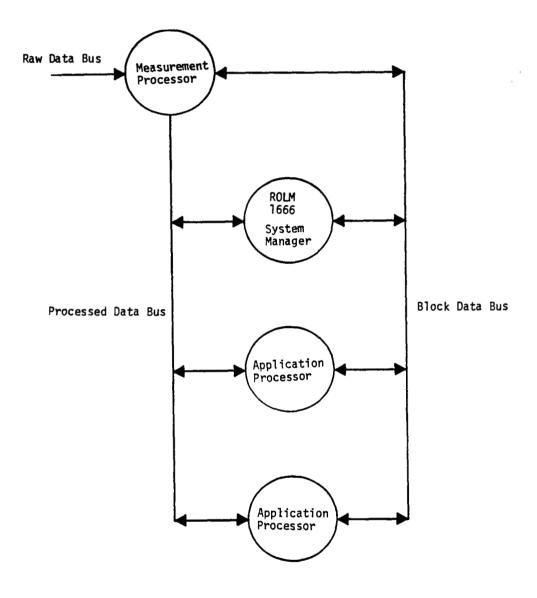

Recent requirements for airborne data processing have increased to the extent that our present 1666 CPU-based system is seriously underpowered. As an example, requirements for one new application program call for computations performed at a rate which is beyond the capabilities of the 1666. In order to be able to meet these and expected future requirements, we have decided to develop a multiprocessor architecture for ADAMS, as shown in Figure 7. This architecture will feature two high-speed buses: a cyclic data bus and a block data bus. The cyclic data bus, developed by Boeing, will carry cyclic sensor and computed data. The block data bus, the Ethernet bus developed by Xerox, will carry burst-type data (such as commands, support data, interprocessor communication, etc.). The ADAMS Executive will be extended to handle the additional processors, which will be connected across the two buses. The 1666 will remain in the system and will manage system resources, and perhaps display processing, while the data reduction and analysis programs will be distributed to other processors, for which we are currently planning to use the new generation of 16 and 32 bit microprocessors.

ADAMS II MODEL

Figure 2

Figure 4

İ

Figure 7

.

·

-

### SYSTEM PERFORMANCE ANALYZER

MUK -

#### H. R. Helbig Boeing Commercial Airplane Company Seattle, Washington

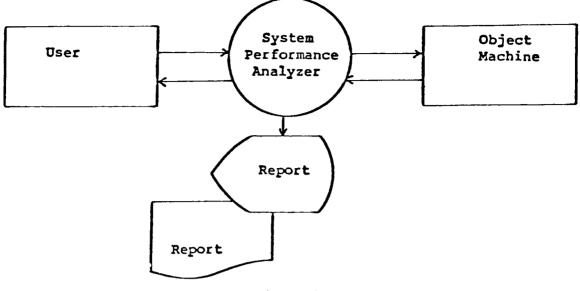

The System Performance Analyzer (SPA) was designed to provide accurate real time information about the operation of complex systems. It is currently being developed for use on the Airborne Data Analysis/Monitor System (ADAMS), a ROLM 1666 based system used by Flight Test.

It uses an external processor to operate an intelligent, simulated control panel. Also provided are functions to trace operations, determine frequency of use of memory areas, and time or count user tasks in a multi-task environment. This augments the information available from the standard debugger and control panel, and reduces the time and effort needed by ROLM 1666 users in optimizing their system, as well as providing documentation of the effect of any changes.

This paper discusses the design of a System Performance Analyzer, a tool to evaluate the operation of a relatively complex computer system. It provides information on the operation and state of the system under study.

The System Performance Analyzer (SPA) is being developed for use with the ADAMS (Airborne Data Analysis/Monitor System) currently in use by the Boeing Company. It is an attempt to integrate the tools now used to provide information about the system. These tools are the control panel, the software debugger, a Boeing-developed timing and instruction counting histogram analyzer, and a commercial trace analyzer.

The ROLM 1666 Control Panel provides a number of functions useful in testing the ADAM System. The address display indicates the area of program running. Status lights show the mode of operation. The data display can be programmed to provide information. Hardware breakpoints can be used to stop program operation without loading the debugger. Unfortunately, it is somewhat awkward and time consuming to use.

The software debugger is also used extensively for system development. It allows the user to examine and change memory locations, accumulators and registers. It also provides eight breakpoints for interrupting a program at a given memory address. It has a number of limitations that severely limit its usefulness. It consumes system resources, does not provide time-dependent information, and often a program will run differently under breakpoint control than when running normally.

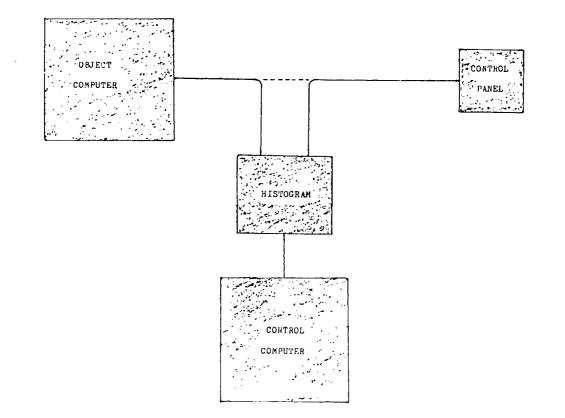

In an effort to provide more information about the dynamic operation of the system, Boeing developed a histogram and timing analyzer. This is a hardware box that connects between the control panel and the CPU of the system and allows a second computer to monitor the system operation (see Figure I). This box provides two functions. In the histogram mode, the analyzer CPU periodically samples the instruction being fetched by the system CPU. A map of memory usage is then built up. This allows the user to see if excessive time is being used by a small section of programming. The timing mode allows the user to monitor the time necessary to run a section of code with a resolution of ten microseconds. This provides the user with the knowledge of what procedures need streamlining. Although it provides only limited information, it demonstrated the ease of use and real time information available by coordinating computer control. A trace analyzer provides a history of operation. By monitoring the bus it becomes possible to see what caused the arrival at a given state. Although this is a useful tool, once again difficulty of use and interpretation limits it to special situations.

The usage of the previous tools pointed out certain things:

- 1) The correct tool must be used to solve a given problem (i.e. the software debugger is not useful for solving timing problems).

- 2) The tool must be easy to use (i.e. the trace analyzer, which must have a number of lines individually connected, is rarely used).

- 3) It must be easily interpreted (the oscilloscope display of the trace analyzer also discourages users).

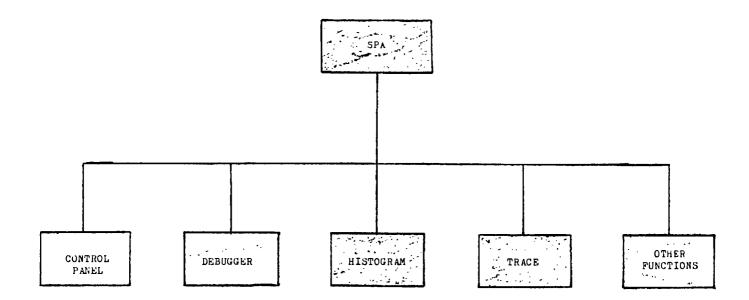

Thus, it became necessary to provide one major easily used tool to provide all the functions previously available (see Figure 2), as well as being flexible enough to meet new ones. The following tables illustrate the primary functions performed.

## TABLE I

## FRONT PANEL

- 1) Monitoring instruction addresses as accessed

- 2) Monitoring data addresses as accessed

- 3) Starting, stopping and continuing execution

- 4) Resetting the status

- 5) Setting and clearing hardware breakpoints

- 6) Executing instructions external to the computer memory

- 7) Examining and loading memory

- 8) Examining and loading the accumulators

- 9) Examining hardware status

- 10) Single stepping through the program

## TABLE 2

## HISTOGRAM

- 1) Counting the number of times instructions in a given area are executed

- 2) Measure time spent in sections of program flow

- 3) Measure time spent in executive and individual user modes

## TABLE 3 DEBUGGER

- 1) Search memory for matching words/bits

- 2) Have multiple, counting breakpoints

- 3) Format data output

## TABLE 4

## TRACE

The analyzer will store IK sequences of instruction addresses, before, after or split on each side of a specified instruction execution.

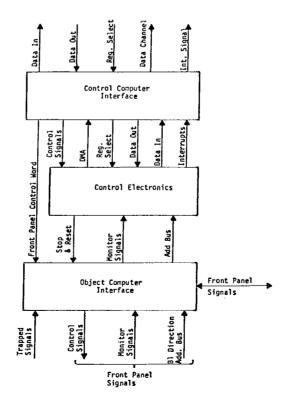

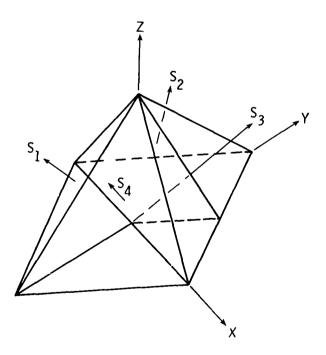

The initial design of the SPA was then undertaken with these considerations. The basic design would be as shown in Figure 3 in order to simplify design and programming. A ROLM 1666 was selected for use as a control computer. Since one ROLM computer would obviously not be fast enough to monitor a second ROLM, the monitor electronics would be built using high-speed, discrete logic. This logic would include its own memory optimized to retain the state of the object machine during operation.

The control electronics were further sub-divided to allow for future changes or expansion. The hardware thus consists of the object computer and its associated peripherals, the object computer interface, the control electronics, the control computer interface, and the control computer with its associated peripherals (see Figure 4). This design permits replacing the control or object computers without redesigning the entire analyzer. Only the interface would need to be replaced.

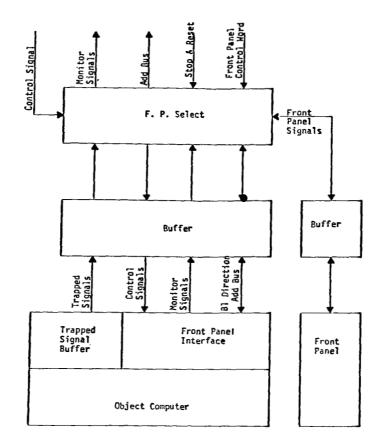

The object computer is slightly modified by the addition of logic to produce necessary signals. These include timing signals, such as the start of an instruction, and condition signals such as the issuance of a program flow change instruction (JST, JMP, RT, etc.). These signals are sensed by monitoring a subset of the microcode instruction lines. Other important timing and condition signals, as well as the address and data bus, are available on the control panel bus. On the control panel bus are control lines that allow command of the object computer (see Figure 5). These are buffered and multiplexed to allow normal display functions of the front panel while making them available to the control electronics. This allows the computer to function normally at full speed while being monitored by the control electronics.

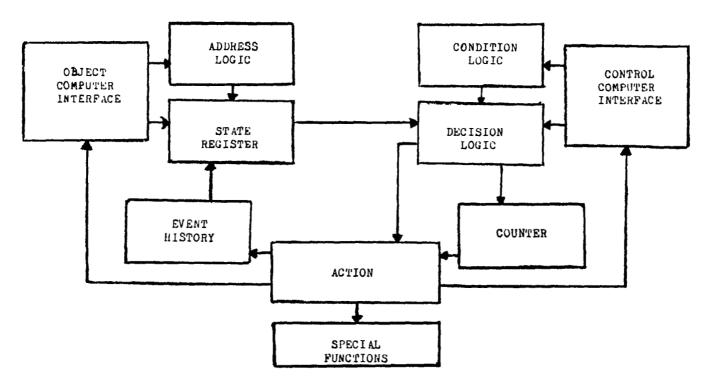

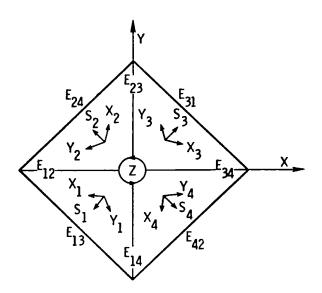

The control electronics are fast enough to respond asynchronously to microcode sequences within a single instruction. The major component is a number of event registers.

The SPA has eight (8) event registers. Each register may be used to define an event on the object computer. An event is said to occur if all of the "conditions" specified in the event register occur simultaneously on the object computer. Each event register may be

set up to recognize all of the following conditions on the object computer as being TRUE, FALSE or DON'T CARE.

- 1) Address within a specified range

- 2) Executive mode or user mode

- 3) Addressing mode (instruction fetch or data addressing)

- 4) Memory write operation (STORE, INCREMENT, etc.)

- 5) Data channel activity

- 6) Interrupt activity

- 7) Floating point processor busy

- 8) Program flow change instruction (JUMP, JSR, INT, etc.)

- 9) Carry bit

- 10) Overflow bit

- 11) Expanded memory

- 12) Interrupt branch mode

An event register may also set a bit to inform the other seven event registers upon the occurrence of an event. This is done with eight additional condition bits. Consequently, there are 20 condition bits associated with event register, the 12 bits described above and the eight bits indicating whether an event has already occurred on any of the eight event registers. The event registers may also be re-enabled by other event registers.

Description of the event alone is by first selecting conditions of interest with a 16-bit mask register. Then the user specifies the <u>values</u> of those conditions which are of interest to him (0,1) and stores these values in the condition register. If address ranges are of interest, it is necessary to set the upper and lower bounds of the address register.

Also associated with each event register is a 16-bit counter which is decremented each time an event occurs and which may be programmed to produce some action when it is decremented through zero. This counter must also be initialized.

Finally, the user must select the action he wishes to take place when the event occurs. These actions are as follows:

- 1) Stop the object machine

- 2) Activate or deactivate a special function (described later)

- 3) Set condition bit informing other event registers of this event

These actions are selected by control bits in a control word. To summarize, an event register consists of the following six components:

- 1) Condition Word (32 bits)

- 2) Condition Mask (32 bits)

- 3) Upper Instruction Address Bound (16 bits)

- 4) Lower Instruction Address Bound (16 bits)

- 5) Upper Data Address Bound (16 bits)

- 6) Lower Data Address Bound (16 bits)

- 7) Data Written (16 bits)

- 8) 16-Bit Auto-Decrementing Counter

- 9) Action Control Bits

The user can think of each event register as operating according to the following logical diagram (Figure 6).

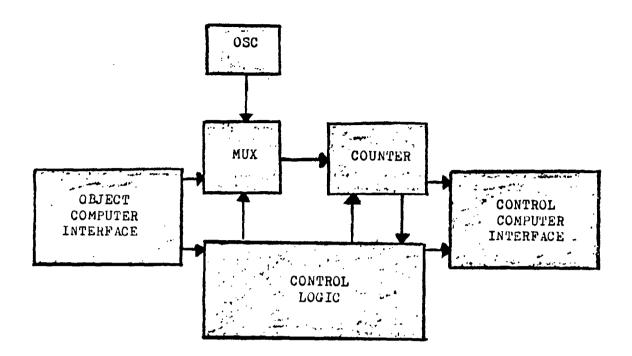

The special functions provided are of three types. One is the timing or counting function. This provides a count of the number of instructions, or the amount of time between two selected events. The two methods of timing are provided to measure activity of the two concurrent processors, the DMA and the floating point (see Figure 7).

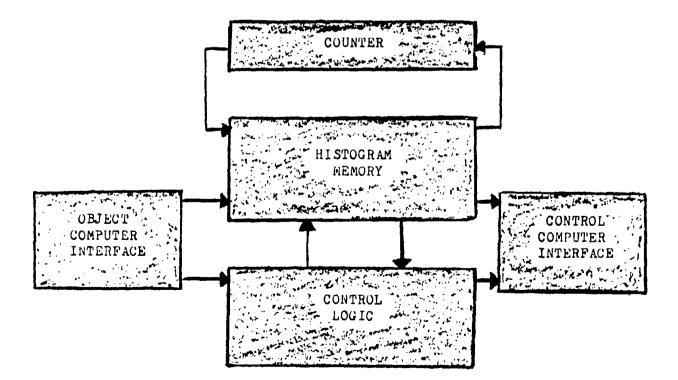

A second function is the histogram. This increments a local memory address representing an area of the object computer's memory (see Figure 8). The histogram count is provided by an event register. This makes it possible to count subsets, such as DMA accesses, separately.

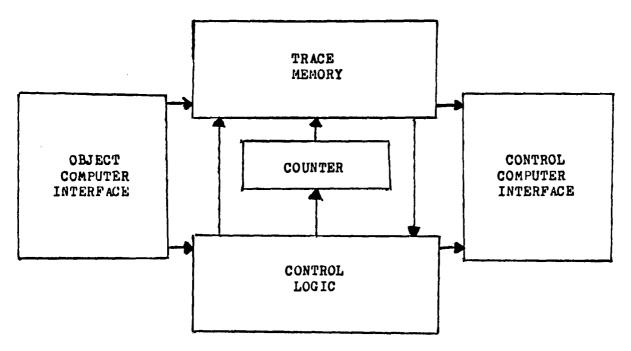

The third major function is a trace analyzer (see Figure 9). This provides a record of addresses accessed. Operating in one of three modes, it will trace all memory accesses, instruction fetches, or program flow changes. The memory is a IK circular buffer, wide enough to hold address and state information. The buffer will sample continuously. When triggered by an event register, it will count up to 1000 more accesses and then freeze the buffer. These special functions can be started and stopped under control of the event registers.

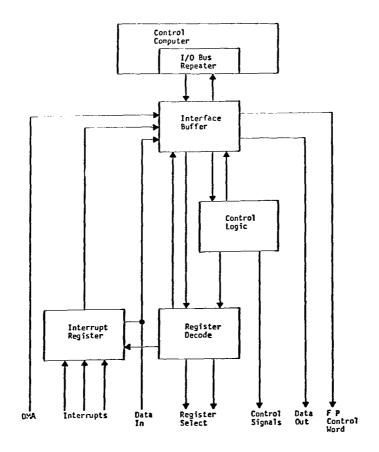

The interface between the control computer and the control electronics is quite simple. An I/O bus repeater in the control computer brings the signals out to the control electronics. Here, the signals are buffered and control logic decodes the appropriate registers to load (see Figure 10). The interface also loads to commands to be transferred through the control panel interface.

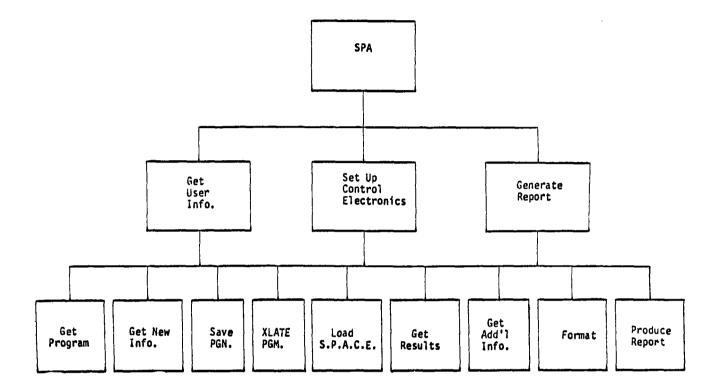

The user interface is a software package resident on the control computer. This allows the user to issue high level commands to set up the control electronics and the object machine, and to format the results according to his needs. This package is shown and explained below and in Figure 11.

The software for the SPA is the SPA software manager (SPASM). This consists of three major modules as shown in Figure 11. The user communicates with the system using the command language and the report generator.

The SPA control electronics will be essentially a passive device under direct control of the control computer. Consequently, the control computer will contain a comprehensive set of software modules which implement the SPA functions. The control computer will also interface directly to the user in an interactive mode of operation. The user will communicate requests to the control computer in a high-level control language and these requests will be translated into commands which will be issued to the SPA control electronics.

The SPA software manager (SPASM) will use named variables and logical constructs to coordinate a series of sequential tasks. Each task will perform one function and will consist of a series of elementary commands to the control electronics.

Certain commands may instruct the SPA control electronics to pass information describing the state of the object machine back to the control computer. For example, the control electronics may be instructed to identify certain user-specified events and to interrupt the control computer upon their occurrence. A set of utilities will exist on the control computer to handle this sort of input from the control electronics and to translate them into a form readable by the user. The SPA software will consist of the following primary components:

- 1) Operating System & Utilities

- 2) Control Electronics Interface Modules

- 3) SPA Software Manager

- 4) User Interface Modules

- 5) Software Modules Specific to SPA Analysis Tasks

Get User Info - This module communicates with the user to control the SPA functions.

<u>Get Program</u> - This module accepts a string of commands from either the console, from memory, or from a disk file.

<u>Get New Info</u> - The program commands are examined and any information or parameters necessry for operation are requested from the user.

Save PCM - The complete program is optionally saved in source format as a disk file.

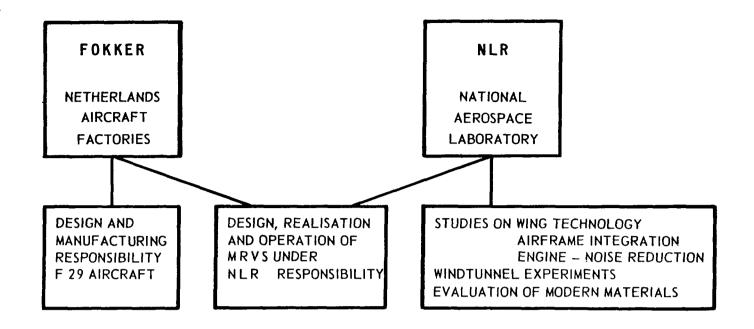

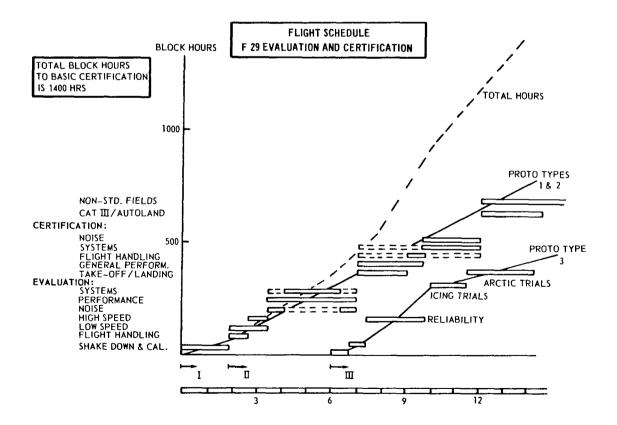

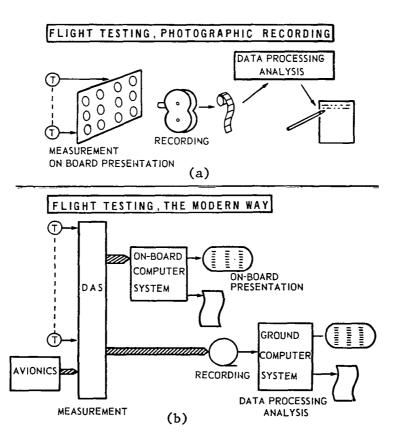

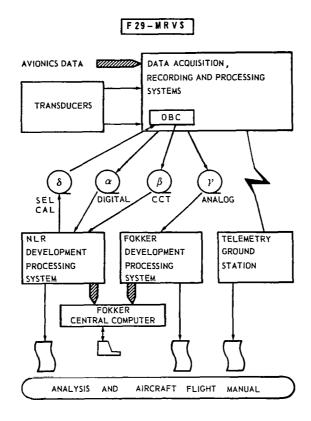

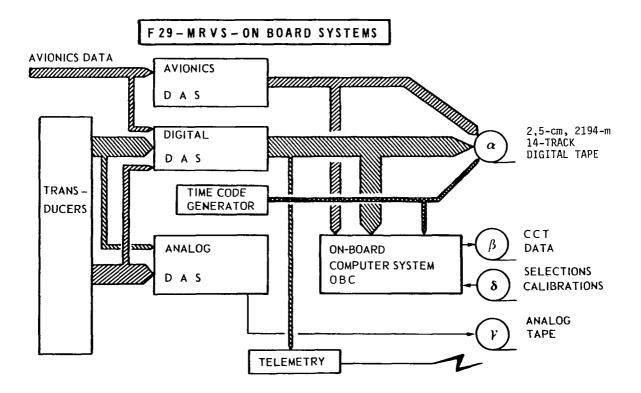

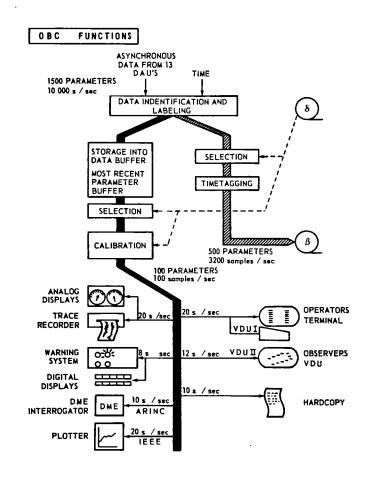

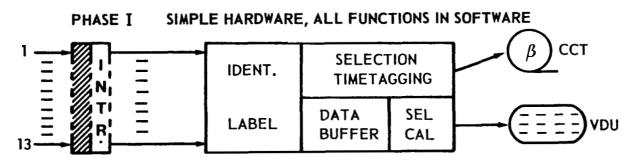

Set-Up Control Electronics - This module manages the SPA control electronics.