## NOTICE

THIS DOCUMENT HAS BEEN REPRODUCED FROM MICROFICHE. ALTHOUGH IT IS RECOGNIZED THAT CERTAIN PORTIONS ARE ILLEGIBLE, IT IS BEING RELEASED IN THE INTEREST OF MAKING AVAILABLE AS MUCH INFORMATION AS POSSIBLE

9950-617

DOE/JPL 954356-80/15 Distribution Category UC-63

(NASA-CR-163476) SILICON-ON CERAMIC

PROCESS: SILICON SHEET GROWTH AND DEVICE

DEVELOPMENT FOR THE LANGE-AREA SILICON SHEET HC AND ACT

TASK OF THE LOW-COST SOLAR ARRAY PROJECT

Pinal (Honeywell Corporate Material Sciences G3/44 08827

#### SILICAN-CH CERAMIC PROCESS

Silicon Sheet Growth and Device Development for the Large-Area Silicon Sheet Task of the Low-Cost Solar Array Project

#### FINAL REPORT

#### Prepared by

B. L. Grung, J. D. Heaps, F. M. Schmit, S. B. Schuldt and J. D. Zook

Period Covered: 10/21/75 - 12/31/80

Published: 3 March 1981

Honeywell Corporate Material Sciences Center 10701 Lyndale Ave. South Bloomington, Minnesota 55420

The JPL Low-Cost Solar Array Project is sponsored by the U.S. Department of Energy and forms part of the Solar Photovoltaic Conversion Program to initiate a major effort toward the development of low-cost solar arrays. This work was performed for the Jet Propulsion Labora (3.7), California Institute of Technology, by agreement between NASA and DOE.

### SILICON-ON CERAMIC PROCESS

Silicon Sheet Growth and Device Development for the Large-Area Silicon Sheet Task of the Law-Cost Solar Array Project

#### **FINAL REPORT**

#### Prepared by

B. L. Grung, J. D. Heaps, F. M. Schmit, S. B. Schuldt and J. D. Zook

Period Covered: 10/21/75 - 12/31/80

Published: 3 March 1981

Honeywell Corporate Material Sciences Center 10701 Lyndale Ave. South Bloomington, Minnesota 55420

The JPL Low Cost Solar Array Project is sponsored by the U.S. Departmen. If Energy and forms part of the Solar Photovoltaic Conversion Program to initiate a major effort toward the development of low-cost solar arrays. This work was performed for the Jet Propulsion Laboratory, California Institute of Technology, by agreement between NASA and DOE.

## PRECEDING PAGE BLANK NOT FILMED

#### PREFACE

This Final Report discusses the investigative results of a silicon-on-ceramic process for producing silicon sheet material. It was performed under the JPL Large-Area Silicon Sheet Task of the Low-Cost Solar Array Project.

The objective of the program was to investigate the technical and economic feasibility of producing solar-cell sheet silicon by coating one surface of carbon zed ceramic substrates with a thin layer of large-grain polycrystalline silicon from the melt. The effort was divided into several areas of investigation in order to most efficiently meet the goals of the program. These areas include: 1) dip-coating; 2) continuous coating; 3) material characterization; 4) cell fabrication; and 5) theoretical analysis. The work in the continuous-coating technology development area was funded directly by Honeywell Inc. from 1 January 1979 to 30 September 1979. Additional support to certain phases of the continuous-coating effort was contributed by the Solar Energy Research Institute (SERI) under the title of "Supported Growth of Polycrystalline Silicon Sheet on Low-Cost Ceramic, Carbon, or Reusable Substrates," SERI contract No. XS-9-8119-1. Results from each of these separately funded efforts are included in this report for completeness.

The work was performed during the period 21 October 1975 to 31 December 1980 at the Honeywell Corporate Technology Center in Bloomington, Minnesota, under JPL contract No. 954356.

During the course of the program, the Project Managers were P.W. Chapman and J.D. Zook, and the Principal Investigators were J.D. Zook, J.D. Heaps, and B.L. Grung. Others who participated in this program are listed in another section of this report.

## PRECEDING PAGE BLANK NOT FILMED

#### TABLE OF CONTENTS

|                                                       | Page       |

|-------------------------------------------------------|------------|

| SUMMARY                                               | 1          |

| INTRODUCTION                                          | 3          |

| TECHNICAL DISCUSSION                                  | 7          |

| Sheet Silicon Coating Facilities                      | 7          |

| Introduction                                          | 7          |

| Dip-Coater No. 1                                      | 7          |

| Dip-Coater No. 2                                      | 12         |

| SCIM-Coater No. 1 (SCIM-I)                            | 16         |

| SCIM-Coater No. 2 (SCIM-II)                           | 23         |

| Heating Chamber (Entrance Tunnel) Results             | 33         |

| Cooling Chamber (Exit Tunnel) Results                 | 35         |

| Temperature Profile Measurement                       | 39         |

| Heater Insulation                                     | 43         |

| Ceramic Substrate Development Effort                  | 45         |

| Introduction<br>Ceramic Material Selection            | 45<br>45   |

| Mullite                                               | 45<br>46   |

| Alumina                                               | 47         |

| Zircon                                                | 48         |

| Cordierite                                            | 48         |

| Silica                                                | 49         |

| Mullite Substrate Development                         | 50         |

| Structure and Properties of Ceramic Substrates        | 51         |

| Characterization of Acid-Leached Mullite Refractory   | 57         |

| Slotted and Large-Area Substrate Development          | 70         |

| Substrate Carbon Coating Effort                       | 72         |

| Sheet Silicon Growth Effort                           | 82         |

| Introduction                                          | 82         |

| Thermal Analysis of Sheet Silicon Growth Processes    | 82         |

| Introduction                                          | 82         |

| Part I: Supported Symmetric Growth                    | 85         |

| Part II: Unsupported Wedge-Shaped (Asymmetric) Growth | 100        |

| Summary                                               | 112        |

| Dip-Coating Results                                   | 115        |

| Introduction                                          | 115        |

| Angle Dip-Coating                                     | 116        |

| Silicon-Ceramic Bonding Seeded Growth                 | 117<br>120 |

| Growth Parameters                                     | 120        |

| Slotted Substrate Coverage                            | 125        |

| Back Surface Field Metallization Study                | 125        |

| Fast Cowth Studies                                    | 128        |

| Physical Properties of Dip-Coated Material            | 131        |

| Electrical Properties of Dip-Coating Material         |            |

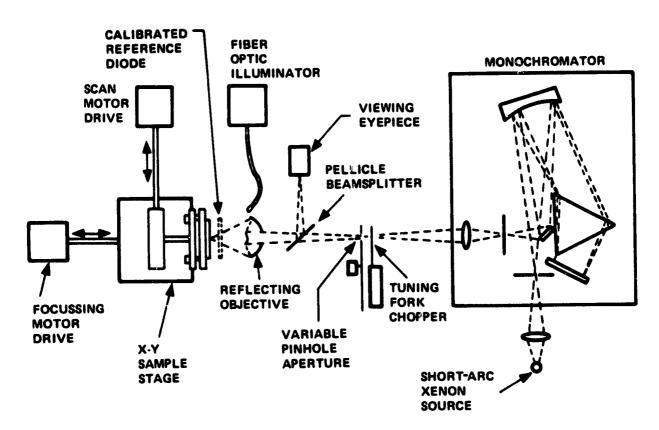

| Evaluation of SOC Material Using LBIC                 | 133        |

| SCIM-Coating Results                                  | 140        |

| Introduction                                          | 145        |

| SCIM-Coated Silicon Layers                            | 145<br>147 |

| SCIM-Coating Growth Parameters                        | 147        |

| Growth Stability                                      | 151        |

| Physical Properties of SCIM Material                  | 151        |

| Electrical Properties of SCIM Material                | 154        |

### TABLE OF CONTENTS (Concluded)

|                                                                               | Page       |

|-------------------------------------------------------------------------------|------------|

| Solar Cell Effort                                                             | 154        |

| Fabrication Procedure                                                         | 154        |

| Solar Cell Performance                                                        | 164        |

| Cost Analysis                                                                 | 182        |

| Introduction                                                                  | 182        |

| Process Summary                                                               | 183        |

| Principal Assumptions for Target Technology                                   | 185        |

| IPEG-2 Estimates for Target Technology                                        | 186        |

| Progress-To-Date Technology                                                   | 188        |

| Price Allocation                                                              | 190<br>191 |

| Summary                                                                       | 191        |

| CONCLUSIONS                                                                   | 193        |

| REFERENCES                                                                    | 196        |

| LIST OF PUBLICATIONS                                                          | 198        |

| RESEARCH PARTICIPANTS                                                         | 199        |

| APPENDIX A EVALUATION OF SILICON-ON-CERAMIC MATERIAL FOR LOW-COST SOLAR CELLS | 201        |

| APPENDIX B PARASITIC RESISTANCE ANALYSIS                                      | 209        |

| ADDRADIA C MONEI CELI DEVELODMENT                                             | 223        |

## LIST OF ILLUSTRATIONS

| Figure | Silicon dip-coating principle.                                                                                  | Page<br>4 |

|--------|-----------------------------------------------------------------------------------------------------------------|-----------|

| 2      | Schematic diagram of the Silicon-Coating-by-an-Inverted-                                                        | 5         |

|        | Meniscus (SCIM) technique.                                                                                      | 8         |

| 3      | Dip-coater No. 1.                                                                                               |           |

| 4      | Dip-coater No. 1 and associated equipment.                                                                      | 10        |

| 5      | Experimental dip-coater.                                                                                        | 13        |

| 6      | Heater assembly in experimental dip-coater.                                                                     | 13        |

| 7      | Photograph showing front and back cooling shees in place in experimental dip-coater.                            | 14        |

| 8      | Schematic showing water and gas flow in cooling shoes.                                                          | 14        |

| 9      | Schematic showing relationship of afterheater, cooling shoes, and crucible assembly in experimental dip-coater. | 15        |

| 10     | Photographs of SCIM-I.                                                                                          | 17        |

| 11     | SCIM-I preheater longitudinal thermal profiles.                                                                 | 19        |

| 12     | Cross-sectional view looking into SCIM-I preheater compartment as viewed from the coating chamber.              | 19        |

| 10     | SCIM-I postheater longitudinal thermal profile.                                                                 | 20        |

| 14     | SCIM-I preheater isotherms.                                                                                     | 20        |

| 15     | SCIM-I postheater isotherms.                                                                                    | 21        |

| 16     | New Trough/substrate heater (also showing quartz crucible/trough piece).                                        | 21        |

| 17     | SCIM-I coating chamber configuration showing combination trough/substrate heater.                               | 22        |

| 18     | SCIM-II exterior showing two side-by-side substrates entering the coater.                                       | 23        |

| 19     | Schematic cross section of SCIM-II.                                                                             | 24        |

| 20     | SCIM-II interior showing water-cooled base and substrates emerging from preheater.                              | 25        |

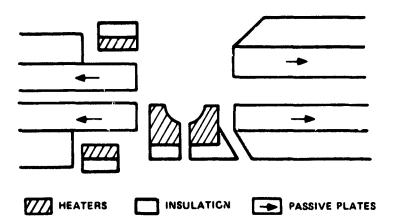

| 21     | Strategy to eliminate effects of thermal stress.                                                                | 28        |

| 22     | Schematic cross section of SCIM-II showing simplified arrangement of various thermal elements used in modeling. | 30        |

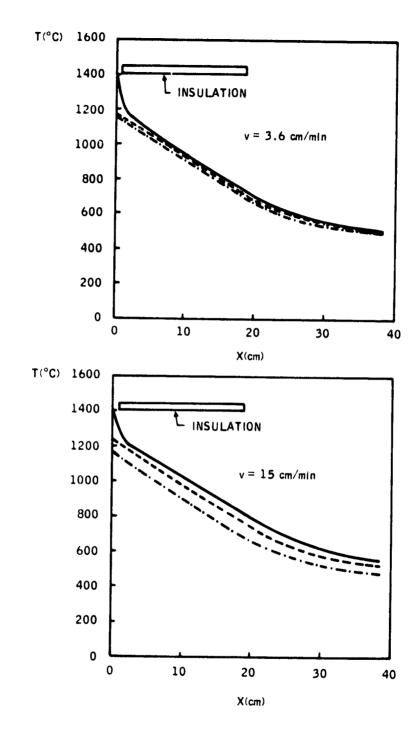

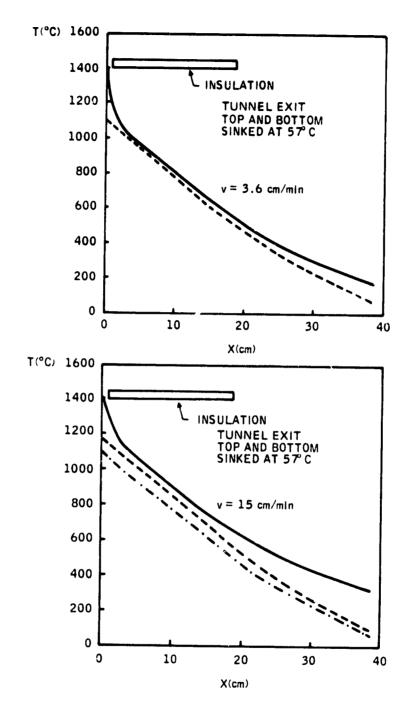

| 23     | Calculated versus experimental exit tunnel temperature with no substrate in chamber.                            | 33        |

| Figure<br>24 | Calculated entrance tunnel profiles corresponding to slow and fast operation.                                                                                                               | Page<br>34 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 25           | Calculated exit tunnel profiles at different speeds with insulation located as indicated (carbon guides are not heat-sunk).                                                                 | 36         |

| 26           | Calculated exit tunnel profiles at different speeds without insulation.                                                                                                                     | 37         |

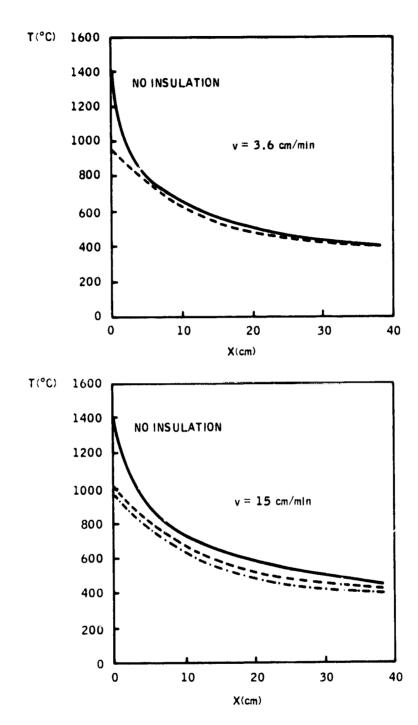

| 27           | Calculated exit tunnel profiles with heat sink at exit end.                                                                                                                                 | 38         |

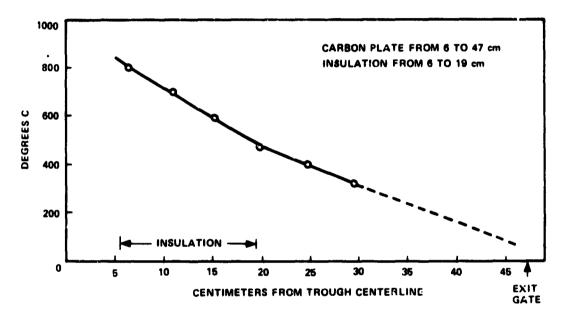

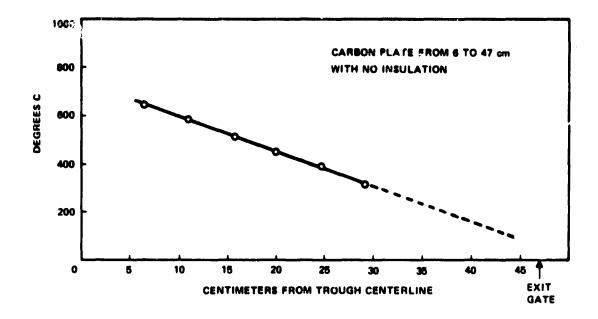

| 28           | Temperature profile of partially insulated exit tunnel.                                                                                                                                     | 40         |

| 29           | Measured profile of uninsulated exit tunnel                                                                                                                                                 | 41         |

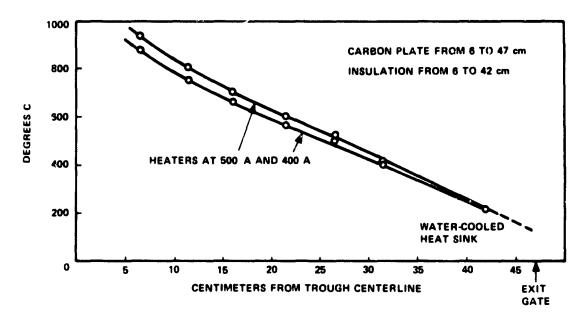

| 30           | Measured profile of exit tunnel with insulation along full length.                                                                                                                          | 41         |

| 31           | Measured profile at two heater powers.                                                                                                                                                      | 42         |

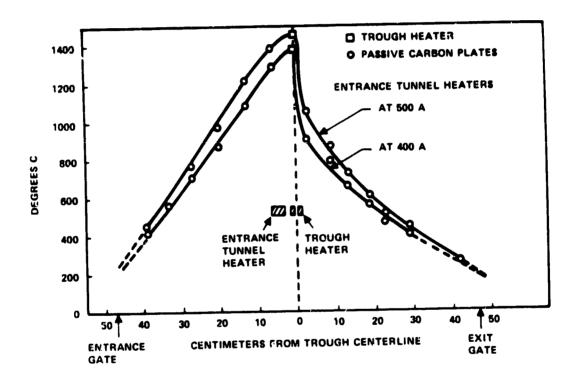

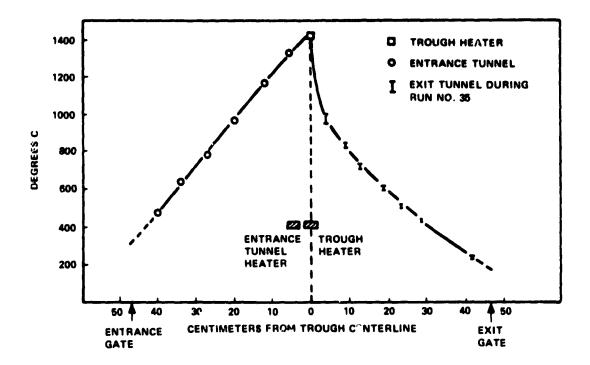

| 32           | Measured profile during a coating run.                                                                                                                                                      | 43         |

| 33           | Schematic cross section of coating zone, including heaters, insulation, and passive plates.                                                                                                 | 44         |

| 34           | Cordierite substrate samples.                                                                                                                                                               | 49         |

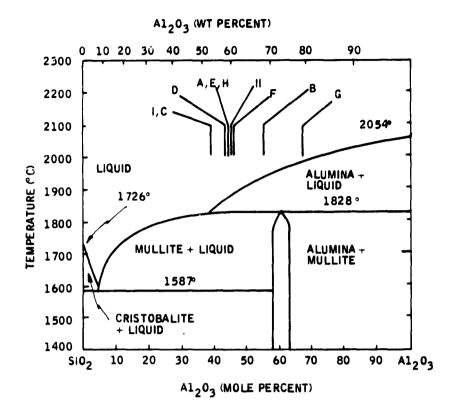

| 35           | Alumina-silica phase diagram.                                                                                                                                                               | 53         |

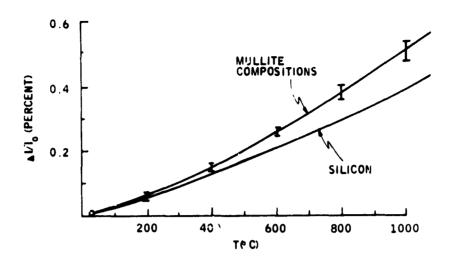

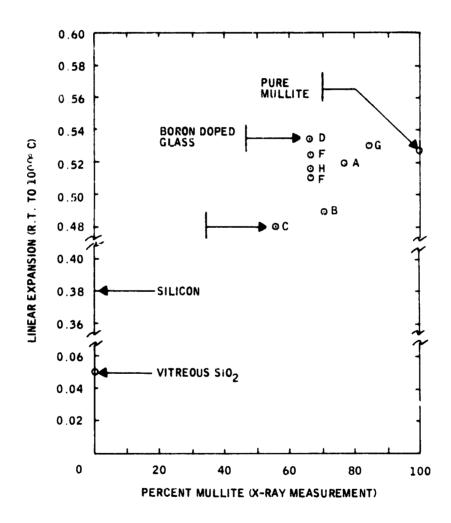

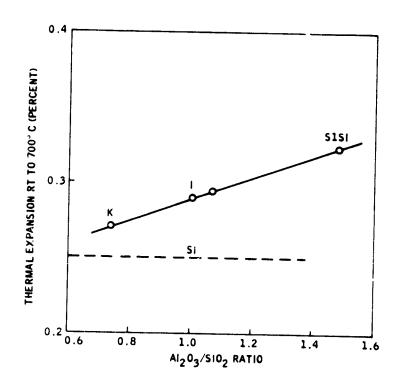

| 36           | Thermal expansion of mullite compared with silicon.                                                                                                                                         | 55         |

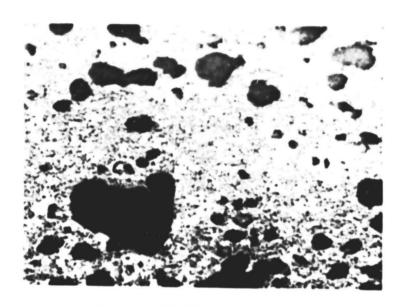

| 37           | Optical micrographs of mullite refractory specimens.                                                                                                                                        | 56         |

| 38           | Optical micrograph of an electrically fused mullite substrate (500x).                                                                                                                       | 57         |

| 39           | Scanning electron micrographs of a fractured surface of an MV-20 sample that had been immersed in HF to leach the glass phase to a depth of approximately one-third the specimen thickness. | 58         |

| 40           | Thermal expansion from $25^{\circ}\text{C}$ to $1000^{\circ}\text{C}$ of experimental substrate materials.                                                                                  | 60         |

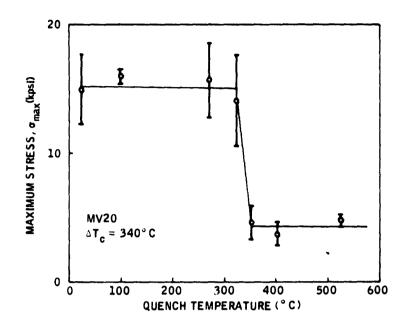

| 41           | Room-temperature fracture strength of MV-20 mullite.                                                                                                                                        | 64         |

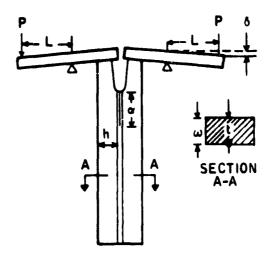

| 42           | Schematic showing specimen and loading arrangement used in the constant-moment test.                                                                                                        | 65         |

| 43           | Photomicrographs of various mullite bodies (magnification $150x$ ).                                                                                                                         | 68         |

| 44           | Thermal expansion of SISI mullite containing excess silica.                                                                                                                                 | 69         |

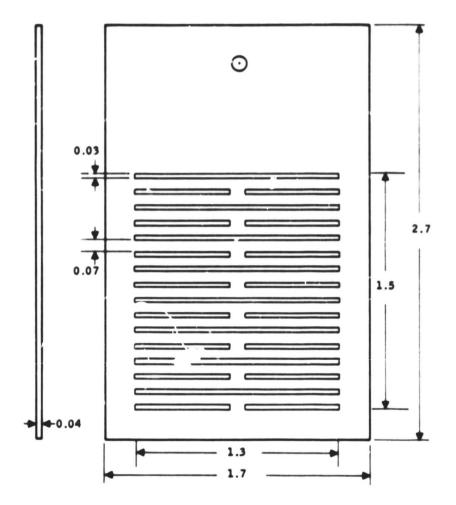

| .15          | Dimensions of slotted substrates produced at Coors                                                                                                                                          | 71         |

| Figure |                                                                                                                    | Page |

|--------|--------------------------------------------------------------------------------------------------------------------|------|

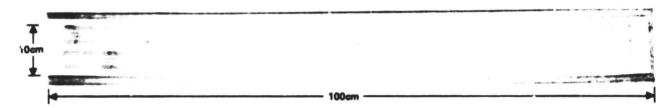

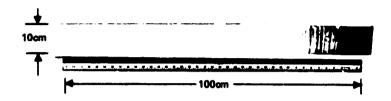

| 46     | 10cm x 100cm slotted substrate produced at Coors.                                                                  | 71   |

| 47     | Blistered and spotty silicon film formation as the result of incomplete drying of Dylon carbon coatings $(1.7x)$ . | 74   |

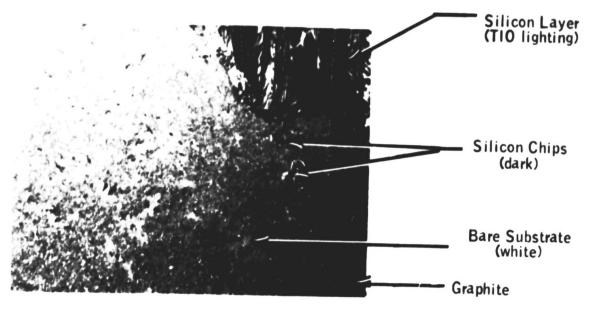

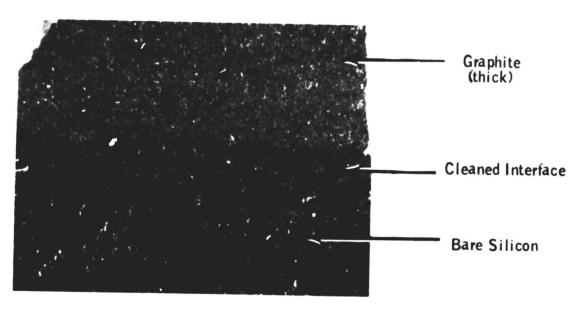

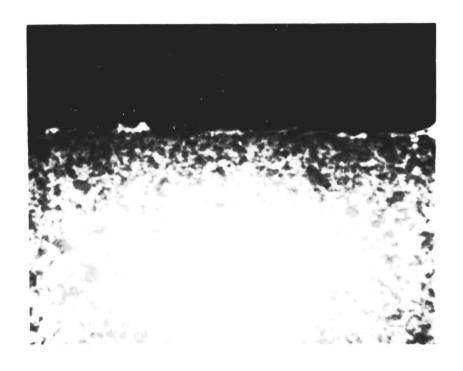

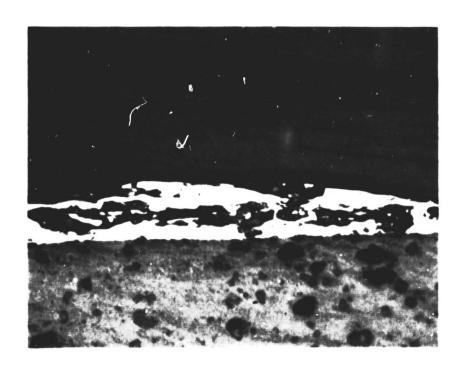

| 48     | Silicon-ceramic interface carbonized with dag 154 (500x).                                                          | 76   |

| )      | Scanning Auger micrographs of the silicon-vitreous graphite interface at 2500x.                                    | 79   |

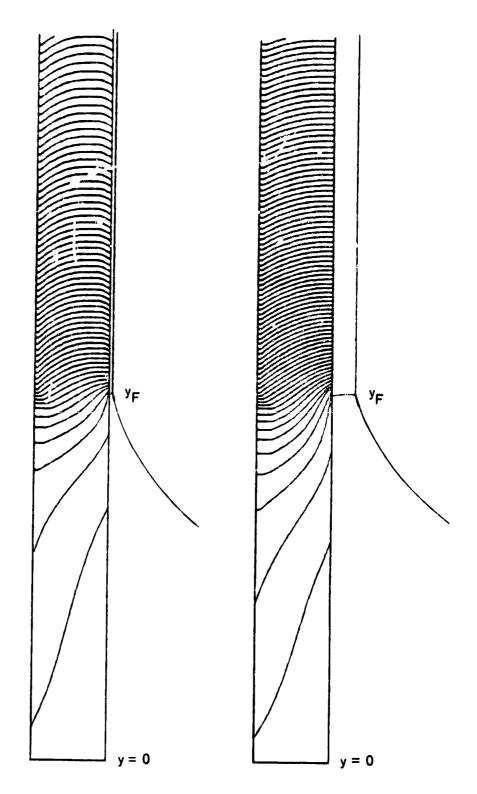

| 50     | Vertical growth of sheet silicon.                                                                                  | 83   |

| 51     | Cross-sectional view of SOC growth.                                                                                | 86   |

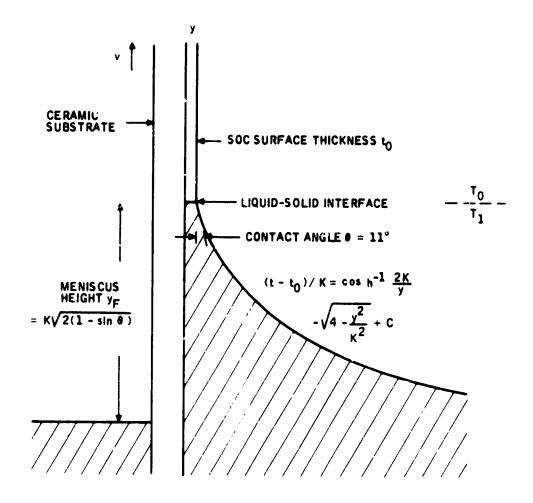

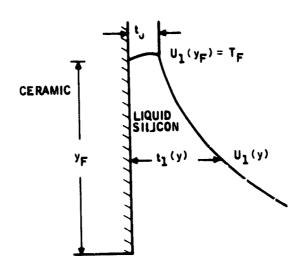

| 52     | Diagram of meniscus region.                                                                                        | 90   |

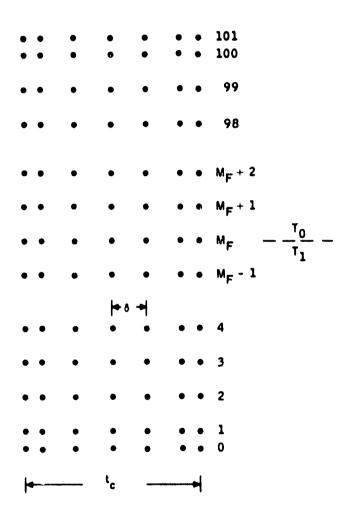

| 53     | Finite-difference array for calculating SOC temperature profile.                                                   | 91   |

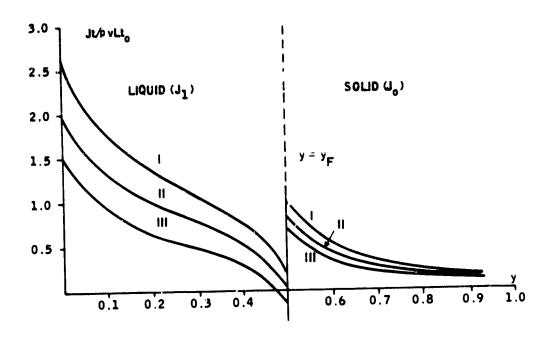

| 54     | Isotherms for $T = T_M$ .                                                                                          | 93   |

| 55     | Normalized thermal flux in liquid and solid parts of the silicon layer at height y above melt surface.             | 94   |

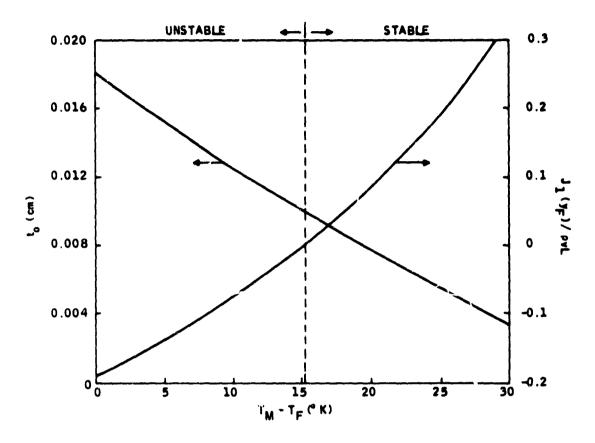

| 56     | Normalized $J_1$ ( $y_F$ ) and silicon thickness as functions of melt temperature.                                 | 95   |

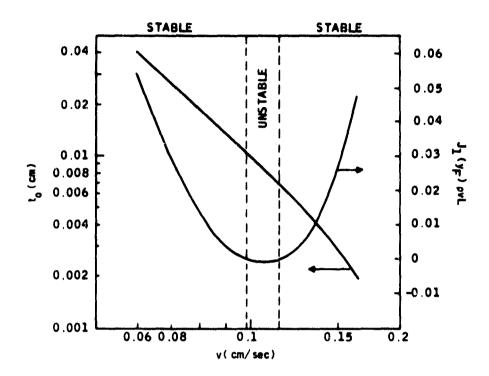

| 57     | Normalized $J_1$ ( $y_F$ ) and silicon thickness as functions of pull speed.                                       | 96   |

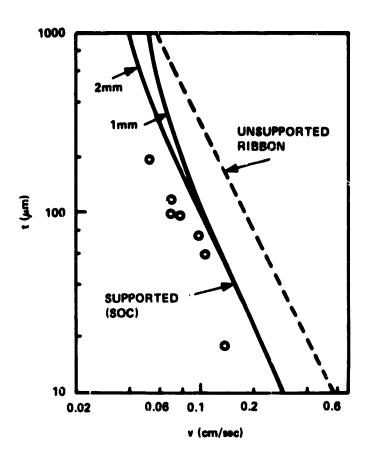

| 58     | Silicon thickness versus pull speed for sup orted (1mm and 2mm substrates) and unsupported growth.                 | 97   |

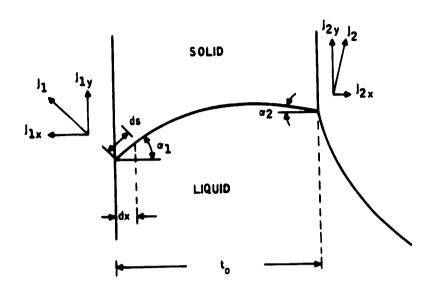

| 59     | Analysis of freezing front shape by means of heat flux components.                                                 | 98   |

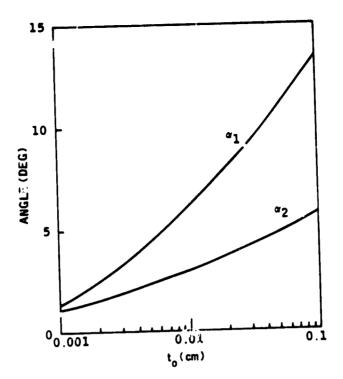

| 60     | Inclinations of freezing isotherm versus silicon thickness.                                                        | 100  |

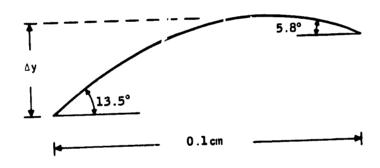

| 61     | Approximate worst-case crystallization front geometry (exaggerated scale).                                         | 100  |

| 62     | Silicon ribbon growth in (a) symmetric and (b) asymmetric modes.                                                   | 101  |

| 63     | Heat fluxes from solidification region (dashed lines) and into downstream region (solid lines).                    | 104  |

| 64     | Nonvertical implementation of asymmetric growth.                                                                   | 104  |

| 65     | Linear temperature distribution in wedge-shaped solidification region.                                             | 106  |

| 66     | Original $(q_0)$ and afterheater-modified $(q)$ temperature gradients for the case $v=0.1$ cm/sec, $t=0.04$ cm.    | 109  |

| 67     | Linear temperature distribution.                                                                                   | 110  |

| Figure    |                                                                                                                                          | Page |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|------|

| 68        | Boundary conditions for numerical integration of Eq. (57).                                                                               | 111  |

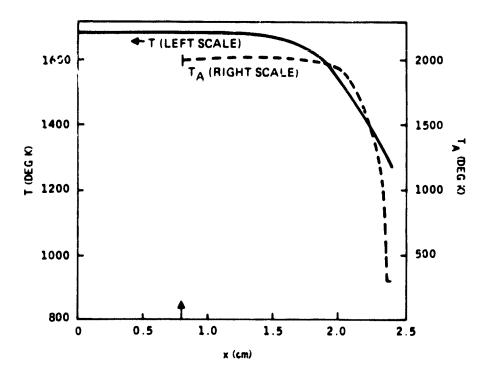

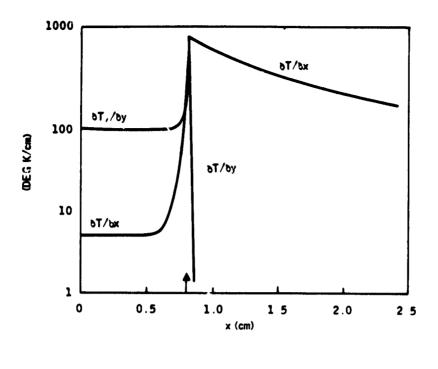

| <b>69</b> | Two-dimensional temperature distribution in silicon ribbon drawn through the heated environment, $T_A(x)$ (dashed curve).                | 113  |

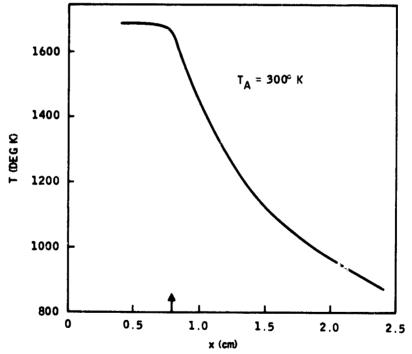

| 70        | Two-dimensional temperature distribution in silicon ribbon with no heated environment.                                                   | 114  |

| 71        | Etched surface of SOC sample.                                                                                                            | 116  |

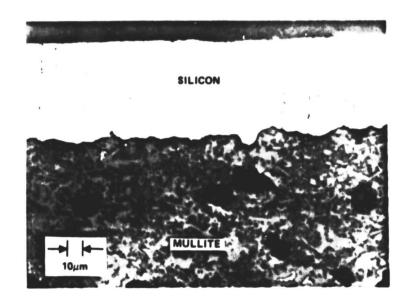

| 72        | Silicon-ceramic interface (unetched) of substrate MR-8.                                                                                  | 118  |

| 73        | Substrate MR-32 and separated layer.                                                                                                     | 119  |

| 74        | Silicon-alumina interface (top) and silicon-pressed mullite interface (200x).                                                            | 121  |

| 75        | Seeded silicon sheet growth.                                                                                                             | 122  |

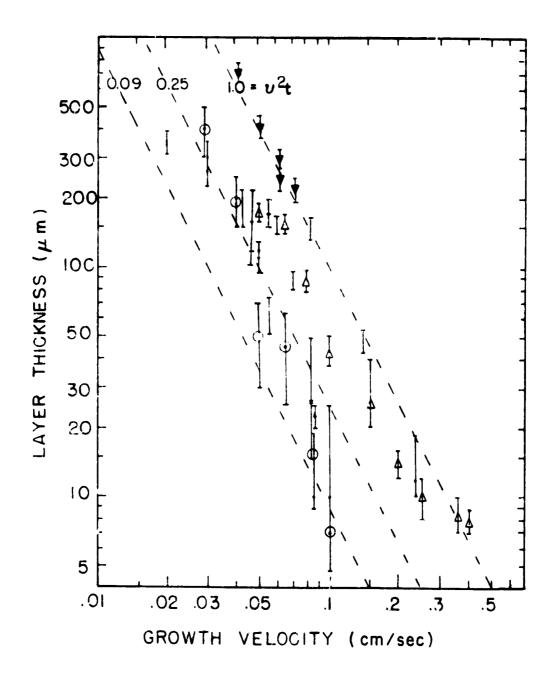

| 76        | SOC layer thickness, t, as a function of growth speed, v, for a number of dip-coating runs under different conditions.                   | 123  |

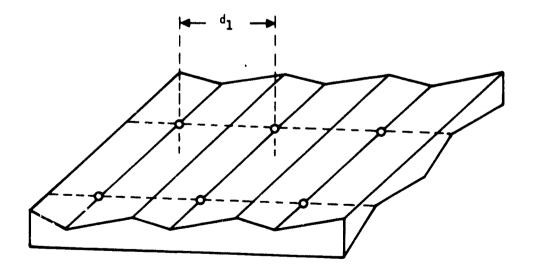

| 77        | Vertically slotted substrate.                                                                                                            | 126  |

| 78        | Horizontally slotted substrate.                                                                                                          | 126  |

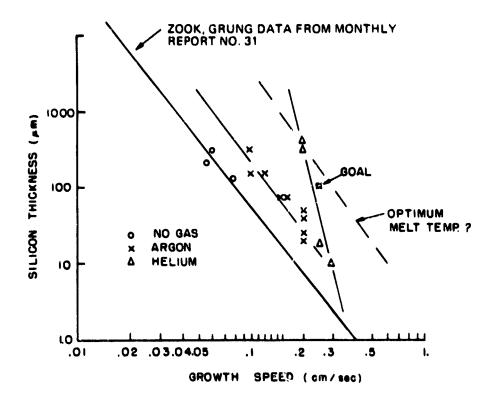

| 79        | Summary of data obtained with dip-coater No. 2 using an "active" afterheater and helium-gas cooling.                                     | 129  |

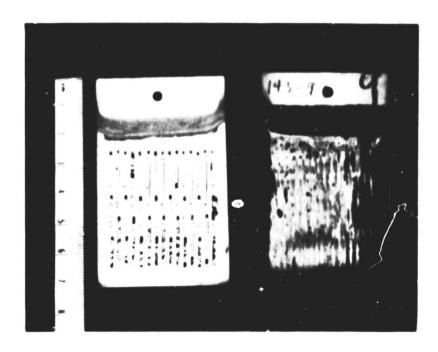

| 80        | Photograph of a slotted substrate coated at 12 cm/min with helium gas directed at (a) the front and (b) the back sides of the substrate. | 130  |

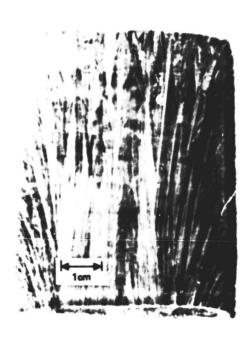

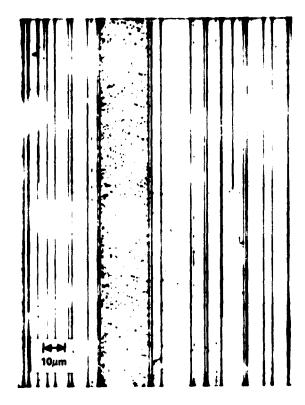

| 81        | Photomicrograph of an etched surface of an SOC sample showing twin boundaries and dislocation distribution.                              | 132  |

| 82        | Photomicrograph of a metallographic cross section of an SOC sample taken perpendicular to the growth direction.                          | 133  |

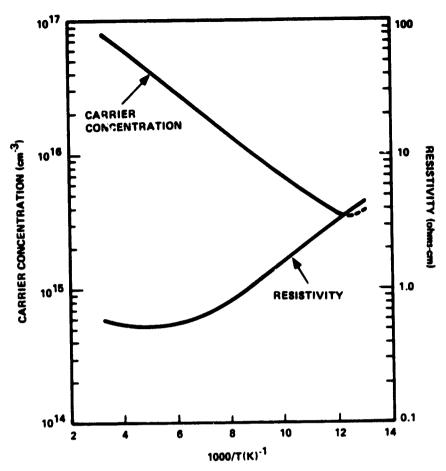

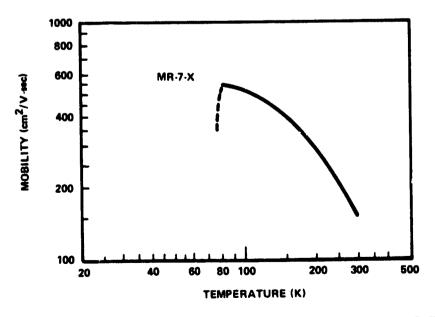

| 83        | Carrier concentration and resistivity vs. $1000/T (deg K)^{-1}$ for sample MR-7-X.                                                       | 136  |

| 84        | Mobility vs. temperature (K) for sample MR-7-X.                                                                                          | 136  |

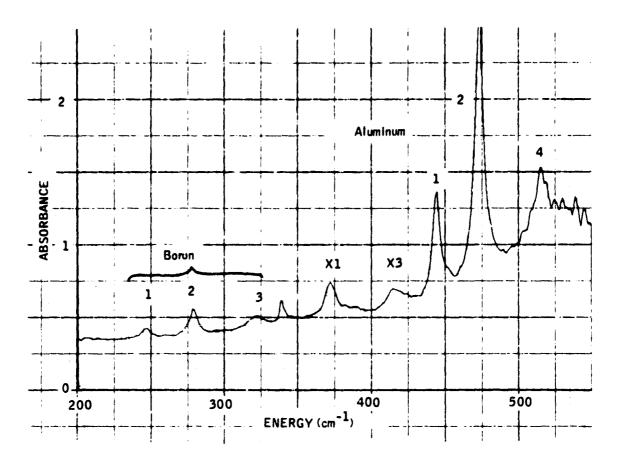

| 85        | Absorbance spectrum of a polycrystalline silicon sample.                                                                                 | 137  |

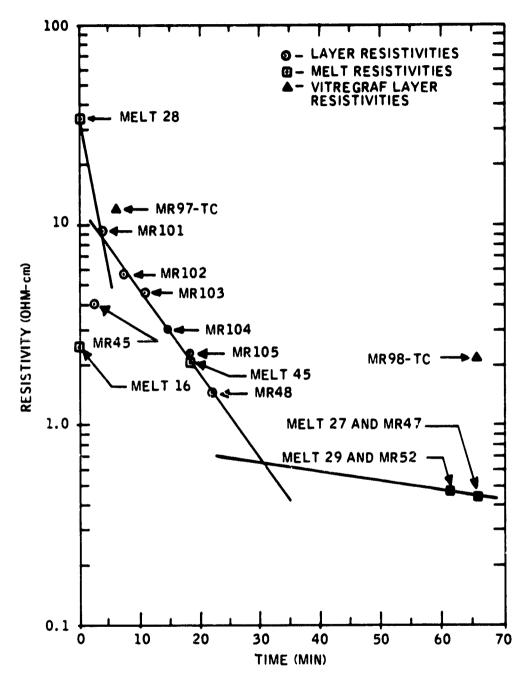

| 86        | Layer and melt resistivities vs. accumulated time that the undoped melts were exposed to mullite.                                        | 139  |

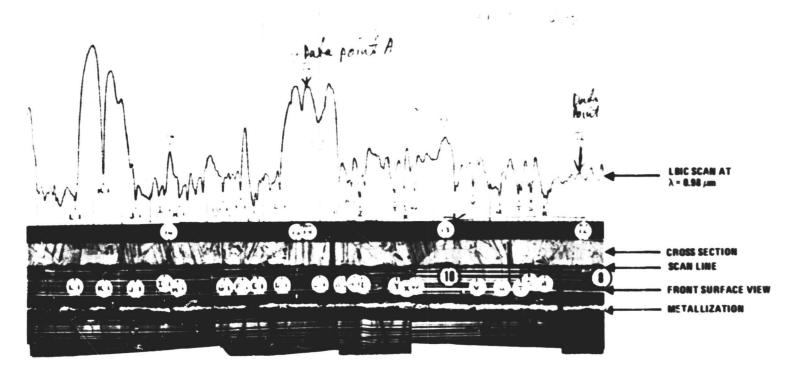

| 87        | Correlation of LBIC scan with structure.                                                                                                 | 143  |

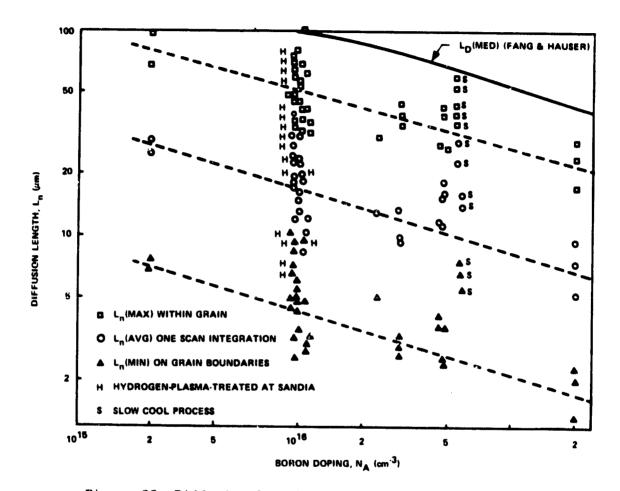

| 88        | Diffusion length as a function of doping and cell processing.                                                                            | 144  |

| 89        | Illustration of molten spillover problem in relation to                                                                                  | 146  |

| Figure |                                                                                                                      | Page |

|--------|----------------------------------------------------------------------------------------------------------------------|------|

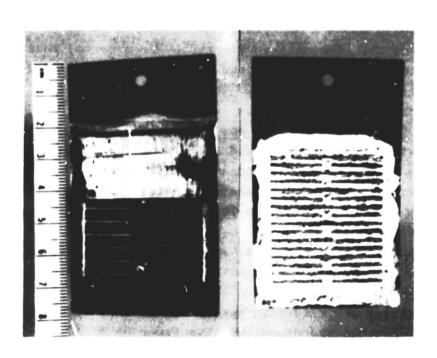

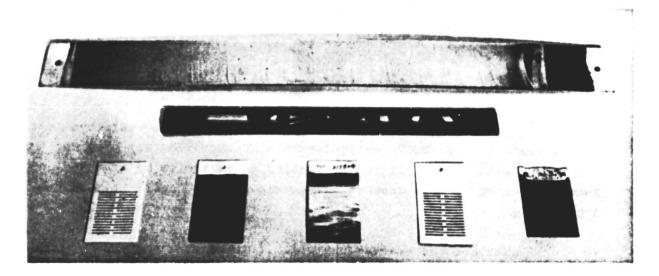

| 90     | Photograph of SOC sheet silicon showing dip-coated and SCIM-coated substrates.                                       | 147  |

| 91     | Photograph of a 10cm x 100cm SCIM-coated SOC layer.                                                                  | 148  |

| 92     | Meniscus shape during conting.                                                                                       | 149  |

| 93     | Silicon coating where argon gas is periodically administered to the meniscus.                                        | 150  |

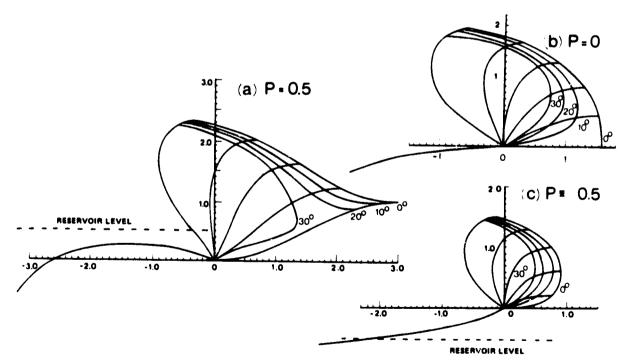

| 94     | SCIM-coating configuration shown with calculated meniscus shapes for a pressure parameter, $P=0.5$ .                 | 152  |

| 95     | Calculated meniscus shapes and loci of constant slope.                                                               | 152  |

| 96     | SCIM-coating configuration shown with calculated meniscus shapes for a pressure parameter $P = -0.5$ .               | 153  |

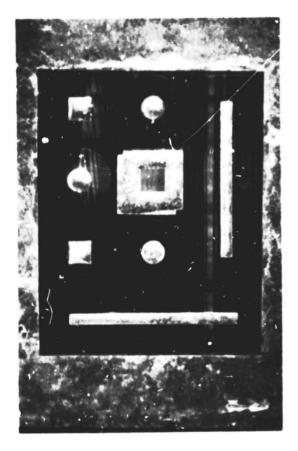

| 97     | SOC solar cells.                                                                                                     | 156  |

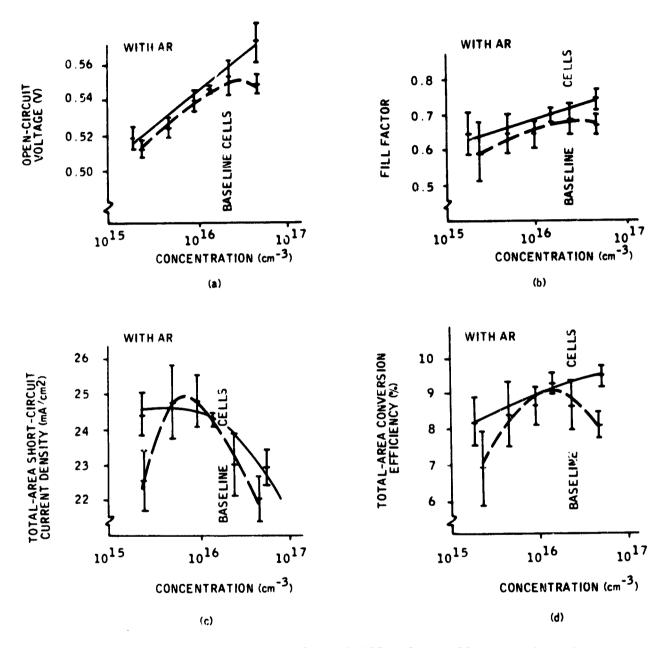

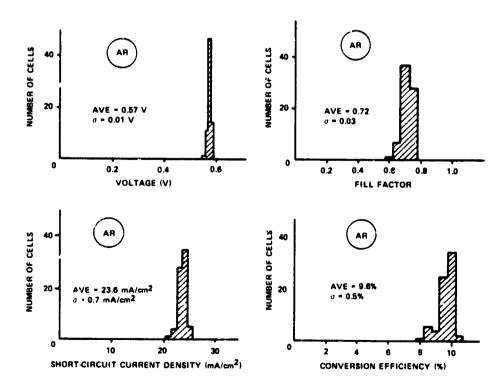

| 98     | Performance of slotted SOC solar cells as a function of base doping concentration, for cells with AR coating.        | 158  |

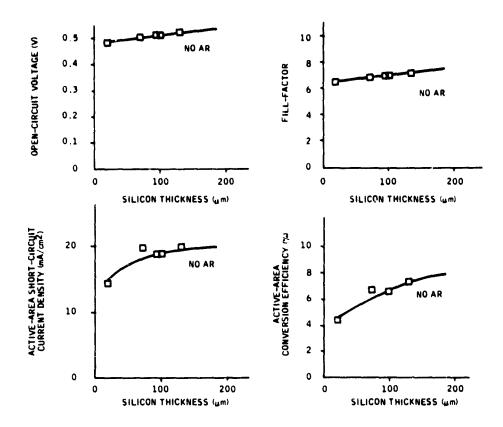

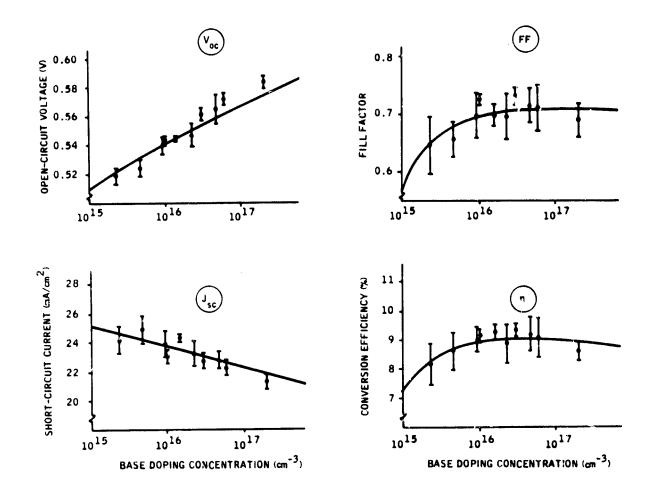

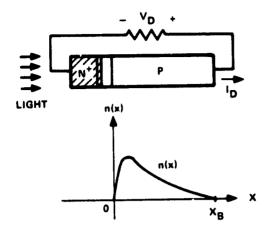

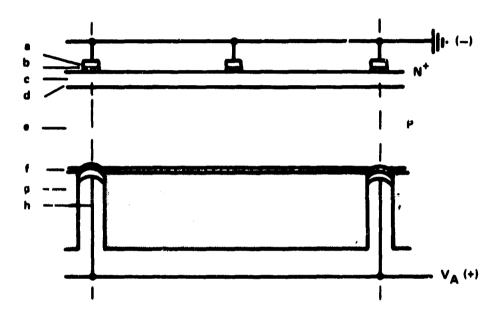

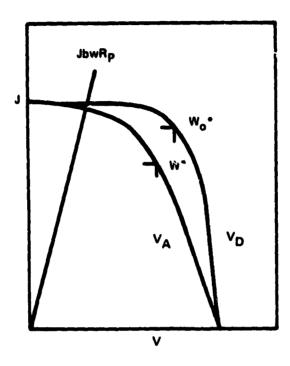

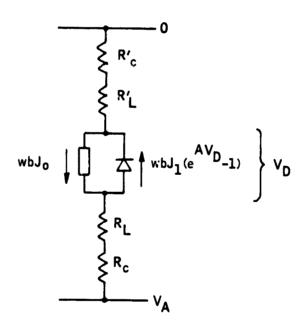

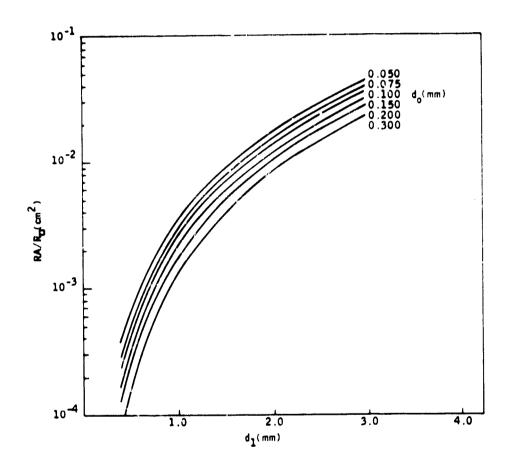

| 99     | Photodiode characteristics as a function of silicon thickness.                                                       | 160  |

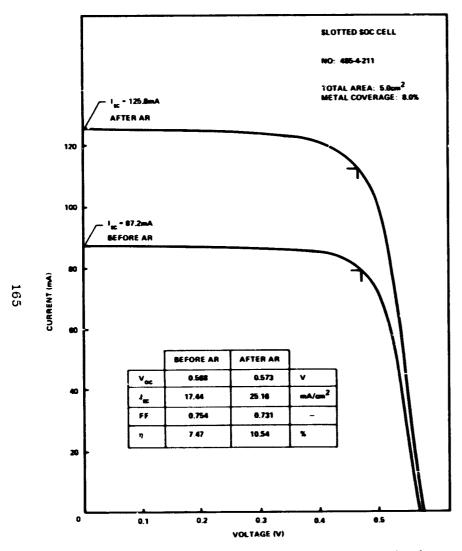

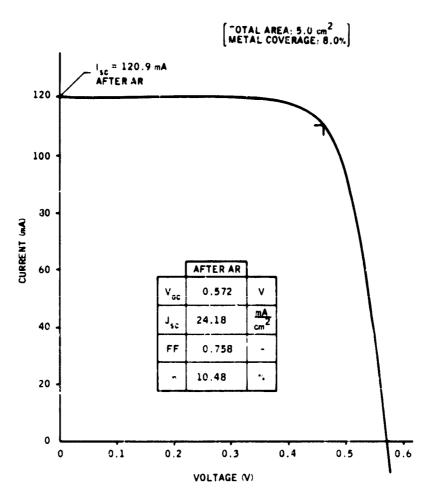

| 100    | Current-voltage characteristics of a slotted cell fabricated from dip-coated material.                               | 165  |

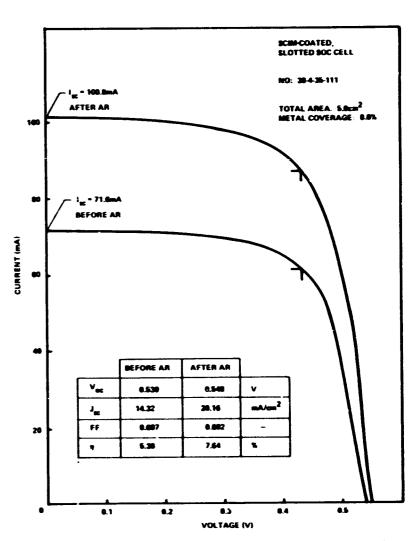

| 101    | Current-voltage characteristics of a slotted SOC cell fabricated from SCIM-coated material.                          | 165  |

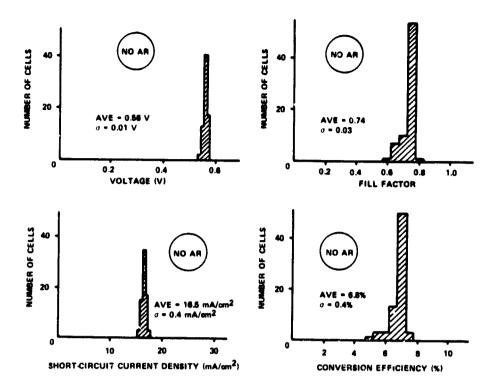

| 102    | Distribution graphs for the 1980 baseline SOC cells for conditions before AR coating.                                | 172  |

| 103    | Distribution graphs for the 1980 baseline SOC cells for conditions after AR coating.                                 | 172  |

| 104    | Cell performance as a function of base doping concentra-<br>tion, for the 1979 baseline cells.                       | 173  |

| 105    | Solar cell configuration and values of constants used in the analysis.                                               | 175  |

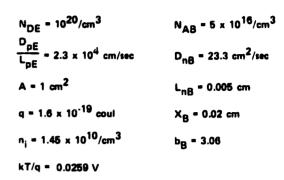

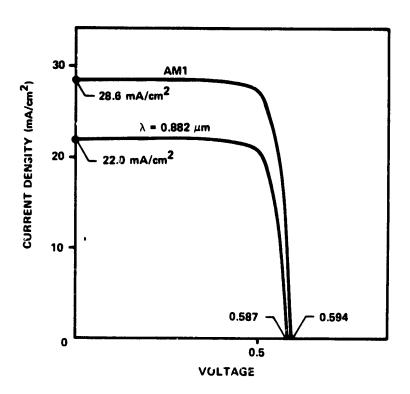

| 106    | Calculated current-voltage characteristics for monochromatic light of wavelength of $0.882 \mu m$ and for AM1 light. | 176  |

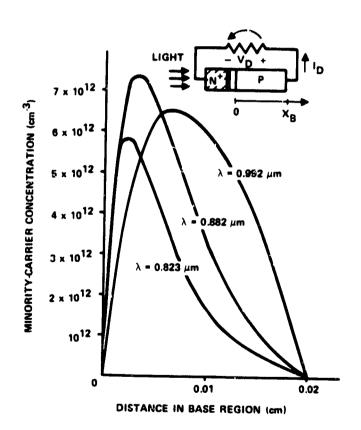

| 107    | Minority-carrier profiles in the base region for three values of wavelength: 0.823, 0.882, and 0.982 $\mu m$ .       | 177  |

| 108    | Minority-carrier profiles for J <sub>sc</sub> , P <sub>max</sub> , and V <sub>oc</sub> .                             | 179  |

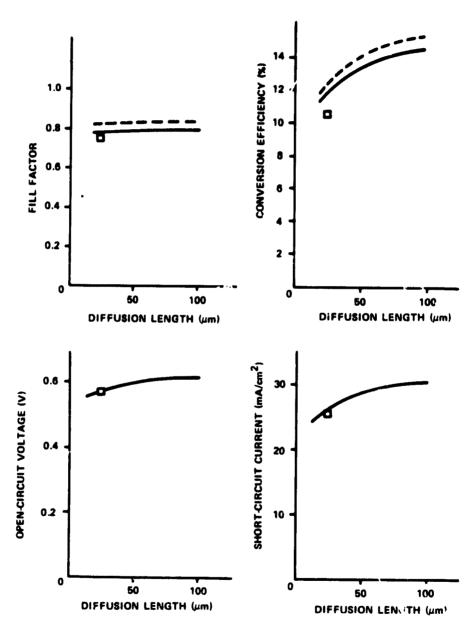

| 109    | Solar cell characteristics as a function of base diffusion length for a base thickness of 200µm                      | 180  |

| 110    | Current-voltage characteristics of cell No. 255-5-211-1.                                                             | 181  |

|               |                                                                               | Page |

|---------------|-------------------------------------------------------------------------------|------|

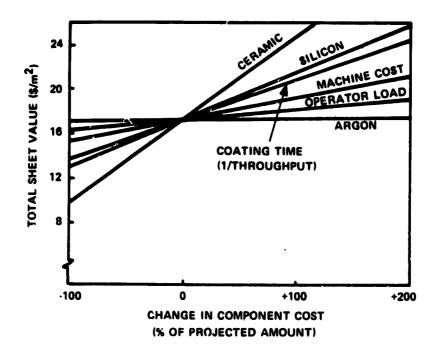

| Figure<br>111 | Sensitivity profiles for total sheet value according to projected technology. | 183  |

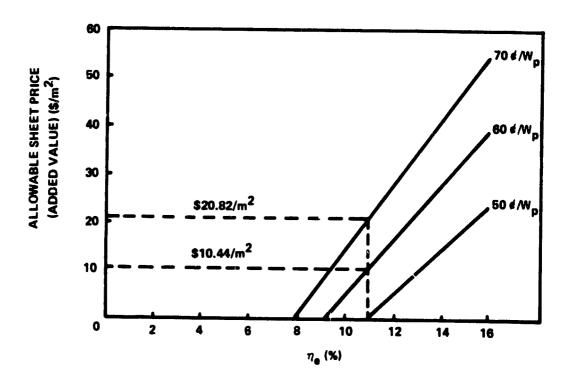

| 112           | Allocated sheet price vs. encapsulated cell efficiency.                       | 192  |

## LIST OF TABLES

| Table | <u> </u>                                                                                              | Page |

|-------|-------------------------------------------------------------------------------------------------------|------|

| 1     | Substrate materials investigated.                                                                     | 46   |

| 2     | Honey all Ceramic Center formulation data.                                                            | 48   |

| 3     | Composition of mullite-based ceramic substrates (in wt.%).                                            | 52   |

| 4     | Properties of mullite-based ceramic substrates.                                                       | 54   |

| 5     | Semiquantitutive emission spectrochemical analysis of mullite substrates (in wt. %).                  | 62   |

| 6     | Room-temperature fracture strength and critical quench temperature for mullite refractory substrates. | 63   |

| 7     | Fracture touchness measurements on mullite substrate materials                                        | . 65 |

| 8     | Composition of the second series of Coors experimental substrates.                                    | 67   |

| 9     | Spectrographic analysis results of colloidal carbon suspensions from Acheson Colloid Co.              | 75   |

| 10    | Typical carbon sheet resistivities.                                                                   | 77   |

| 11    | Sheet resistivity of silicon coatings (first dip run).                                                | 80   |

| 12    | Sheet resistivity of silicon coatings (second dip run).                                               | 81   |

| 13    | Summary of SOC with glassy carbons.                                                                   | 81   |

| 14    | Nomenclature and numerical data.                                                                      | 88   |

| 15    | Values for silicon parameters for Part II.                                                            | 103  |

| 16    | Single-crystal diodes with aluminum back contacts.                                                    | 127  |

| 17    | Slotted SOC diodes with sintered aluminum past back contacts.                                         | 127  |

| 18    | Summary of 300K electrical properties.                                                                | 134  |

| 19    | Best cell summary data.                                                                               | 155  |

| 20    | Experiments for increasing cell performance.                                                          | 160  |

| 21    | Conversion efficiencies of the 1980 baseline SOC cells.                                               | 166  |

| 22    | Characteristics of recent AR-coated SOC cells.                                                        | 168  |

| 23    | Notation used for modeling of the SOC cell structure.                                                 | 175  |

| 24    | Cost data for target technology.                                                                      | 186  |

| 25    | Cost data for progress-to-date technology.                                                            | 189  |

#### SUMMARY

The objective of this Research and Development program was to investigate the technical feasibility of producing solar-cell-quality sheet silicon to meet the Department of Energy (DOE) 1986 overall price goal of \$0.70/watt. With the silicon-on-ceramic (SOC) approach, a low-cost ceramic substrate is coated with large-grain polycrystalline silicon by unidirectional soldification of molten silicon. This R&D effort was divided into several areas of investigation in order to most efficiently meet the goals of the program. These areas include: 1) dip-coating; 2) continuous ccaring-designated SCIM-coating, an acronym for Silicon Coating by an Inverted Meniscus; 3) material characterization; 4) cell fabrication and evaluation; and 5) theoretical analysis.

Both coating approaches were successful in producing thin layers of large-grain, solar-cell-quality silicon. The dip-coating approach was initially investigated and considerable effort was given to this technique. The SCIM technique was adopted later because of its scale-up potentiality and its capability to more conveniently produce large areas of SOC.

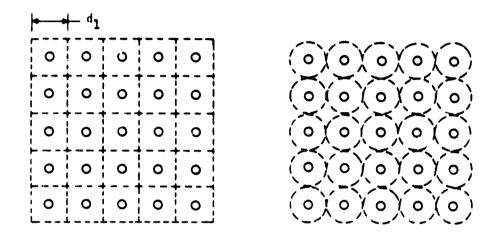

Large (10 cm x 100 cm) ceramic substrates were developed by Coors Porcelain Co. for the purpose of this investigation. The substrates contained slot openings for making electrical contact to the bottom surface of the silicon coating. Mullite was the ceramic selected. It was compositionally modified to be thermally compatible with silicon.

By virtue of unidirectional solidification, the thin (50 to 250µm) silicon layers contain columnar grains as large as 5mm in width and several centimeters long. The single grains are heavily twinned with their boundaries, as well as the normal boundaries, generally normal to the surface of the layer. Thus, the layers are, in general, only one crystal thick. The silicon-to-ceramic bond is mechanical in nature and has proven to be reliably secure in practice.

It was determined that substrate slot openings which are oriented perpendicular to the growth direction perturb the silicon structure to a lesser extent than those which are parallel to the direction of growth. In either case, coverage with silicon is satisfactory. The thickness of the layer is inversely related to the melt temperature and is also proportional to the inverse of the coating speed squared, when the heat of fusion is removed

from the growing layer by radiation alone. It was experimentally demonstrated, however, that the growth rate can be substantially enhanced by the addition of convective cooling, and coating rates commensurate with project's economic goals can be achieved in this manner.

The mullite substrates are slightly soluble in molten silicon, causing the melt to become progressively contaminated using the dip-coating process. This is minimized with the SCIM technique by reducing the contact time and area the substrate has with the melt.

The surfaces of SOC coatings are smooth and shiny and need no further preparation other than a standard clearup procedure prior to forming the p-n junction.

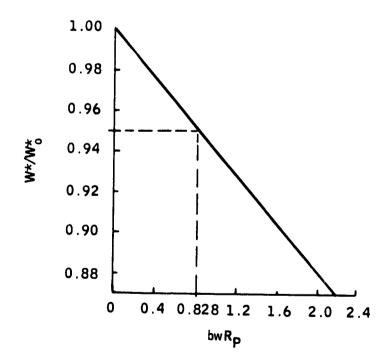

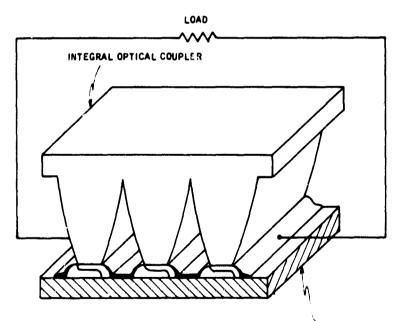

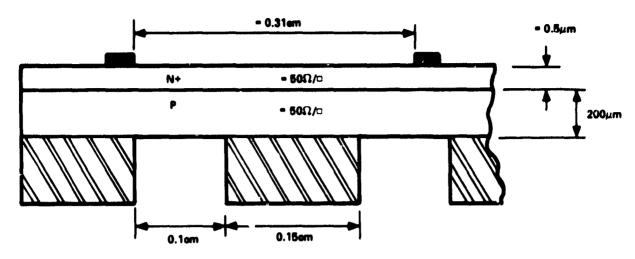

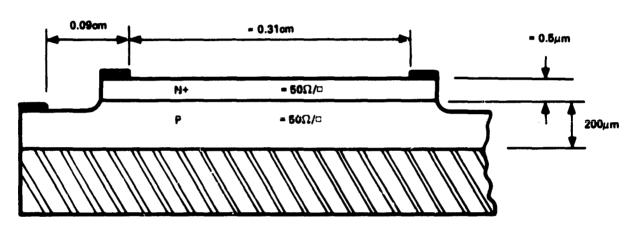

SOC solar cells can be exproducibly produced with an average conversion efficiency of 9.6% (AM1, AR). The slot openings in the ceramic substrates, however, must cover approximately 50% of the total substrate area to achieve this level of cell performance. The need for this large slot opening ratio is to minimize internal series resistance in the cell, a fact that resulted from a supporting analysis of parasitic resistance. The highest conversion efficiency for a dip-coated SOC cell was 10.54% (AM1, AR) and the highest efficiency for a SCIM-coated SOC cell was 7.6% (AM1, AR). The higher efficiencies are produced with a PH3 diffusion at 850°C, followed by a slow cooldown at about 5°C/min.

4

Theoretical modeling of SOC solar cells shows that present cell performance is limited by diffusion length, and that 13% SOC cells are possible with a diffusion Length of  $50\mu m$ .

The average diffusion length, L, in SOC material is 15 to 25µm. The diffusion that the average diffusion length closely spaced grain boundaries, high dislocation densities, and subsurface grain boundaries have been identified as structural causes of the reduction in L.

Cost estimates of the SOC process are \$13/m $^2$  added value, or \$17.25/m $^2$  including silicon at \$14/kg. Based on 11% module efficiency, this corresponds to a sheet price of \$0.125/W $_p$  added value, and \$0.166/W $_p$ , including silicon. The analysis shows that the cost of ceramic is the largest cost driver in the SOC process.

#### INTRODUCTION

This R&D program began 21 October 1975. Its purpose was to investigate the technical and economic feasibility of producing solar-cell-quality sheet silicon by coating inexpensive ceramic substrates with a thin layer of polycrystalline silicon. The coating methods developed were directed toward a minimum-cost process for producing solar cells with a terrestrial conversion efficiency of 11% or greater. At this period in time, sheet silicon, for the most part, was produced by growing cylindrical singlecrystal ingots and slicing them into round wafers. This slicing effort not only requires labor and time, but is accomplished by a costly diamond-edged saw which in turn produces a kerf loss of expensive silicon. The sliced wafers are then mechanically polished and subsequently chemically etched to remove surface damage. For the purpose of safe handling, these wafers are made thicker than is necessary to produce solar cells of a reasonable conversion efficiency. Once this type of solar cell is fabricated, much less than half of the starting silicon material plays a role in the photovoltaic conversion of solar energy. The numerous processes required are labor-intensive and the round geometry of the final cell does not contribute to an area-efficient solar module.

The silicon-on-ceramic approach, on the other hand, eliminates man of the above costly features. With the SOC process, a graphite coating is applied to one surface of an inexpensive ceramic substrate, causing molten silicon to wet, upon contact, only that suface of the substrate to produce a uniform, thin layer of large-grain polycrystalline silicon. With this process, nearly all of the silicon consumed is used in energy conversion.

The surfaces of these thin layers are smooth and shiny and need no further preparation other than a cleanup before being processed into solar cells. Such layers are coated onto large areas of rectangular substrates, thereby maximizing the active-area/total area ratio of a final solar module.

During the course of this program, two silicon coating techniques were investigated:

- Dip-coating

- Continuous SCIM-coating (SCIM is an acronym for Silicon Coating by Inverted Meniscus)

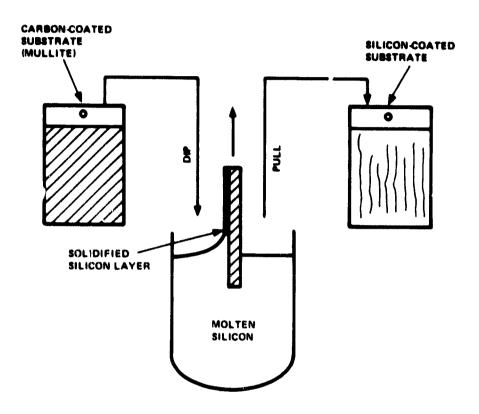

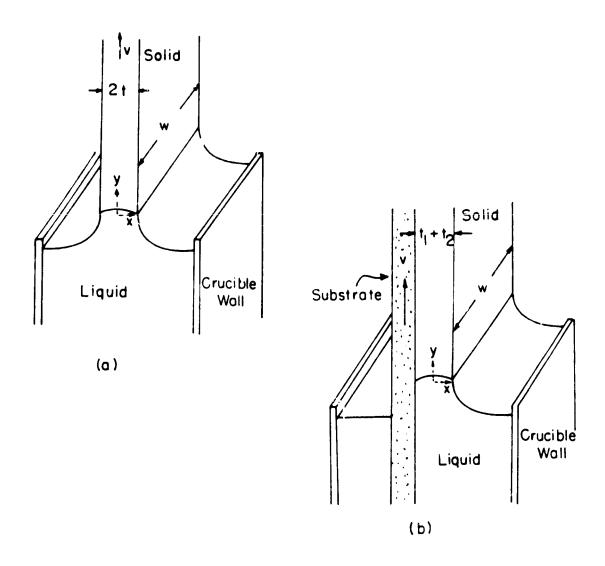

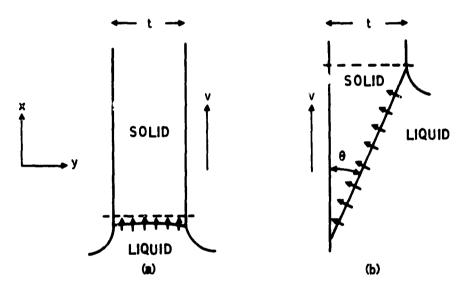

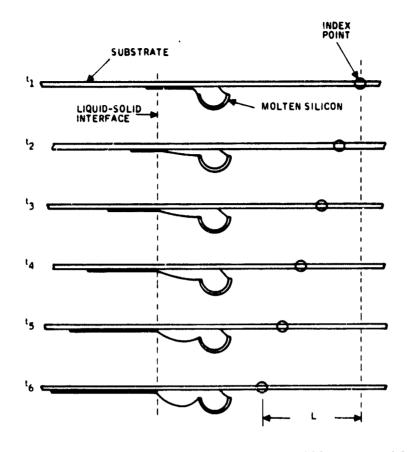

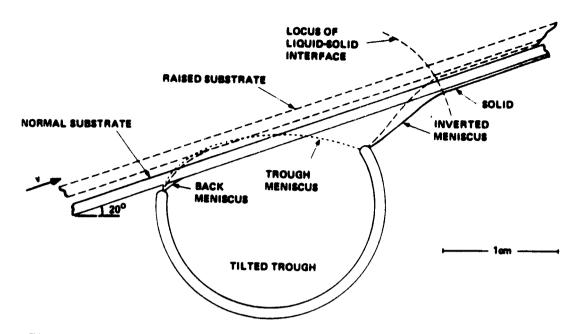

Figure 1 illustrates the principle of dip-coating. A carbon or graphite coating is applied to one face of a ceramic substrate. The substrate is then dipped into and pulled from a crucible of molten silicon. As the substrate is withdrawn from the melt, unidirectional solidification occurs on the carbon-coated face of the substrate, forming a thin layer having large columnar silicon grains.

Figure 1. Silicon dip-coating principle.

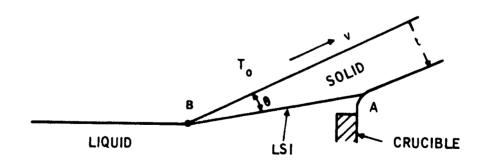

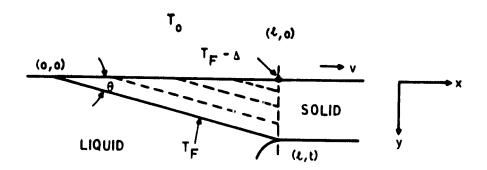

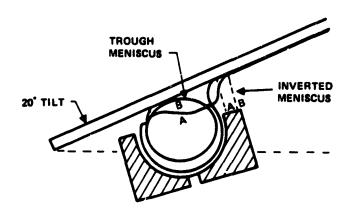

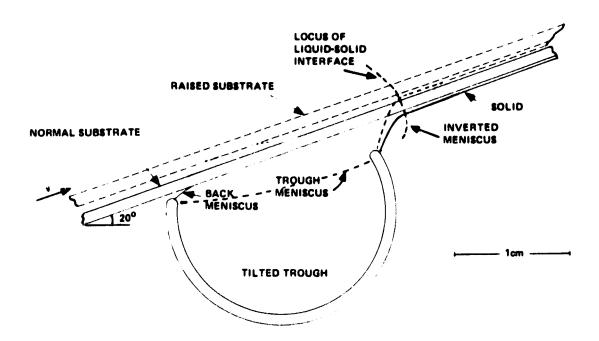

The continuous SCIM technique is illustrated in Fig. 2. Molten silicon is contained in a fused-silica crucible having an attached trough as shown. A plunger is lowered into the crucible, displacing molten silicon along the trough to form a raised meniscus. As the ceramic substrate passes over this trough, the meniscus contacts the carbon-coated side of the substrate, forming a thin silicon layer which is virtually identical to that of the dip-coating technique. Since only the carbon-coated side of the ceramic comes into contact with the melt, there is, in principle, no direct contact between the ceramic and the melt. Thus, contamination of the melt is greatly reduced as compared with that obtained from the dip-coating technique.

Figure 2. Schematic diagram of the Silicon-Coating-by-an-Inverted-Meniscus (SCIM) technique.

In support of this program, Coors Porcelain Co. of Golden, Colorado, developed cost-effective large-area (10cm x 100cm) mullite substrates whose composition was modified to be thermally compatible with that of silicon. These substrates contained slot openings for the purpose of making electrical contact to the bottom side of the silicon layer.

During this investigation, two dip-coating facilities and two SCIM-coating facilities were constructed. The second SCIM-coating facility is capable of simultaneously coating, side by side, two 12.5cm wide by 100cm long slotted substrates in a continuous manner.

The investigation demonstrated that antireflection (AR)-coated solar cells having an average conversion efficiency of 9.6% could be routinely produced from SOC material. The highest efficiency achieved was 10.54% (AM1, AR).

The economic analyses conducted throughout the investigation clearly show that if a coating throughput of  $350~{\rm cm}^2/{\rm min}$  can be achieved, the process can produce silicon sheet within DOE's 1986 goal (with 11% efficient modules).

This report discusses the results of this 5+ years of work along with the approaches used in determining the results.

### PRECEDING PAGE BLANK NOT FILMED

#### TECHNICAL DISCUSSION

#### SHEET SILICON COATING FACILITIES

#### Introduction

The silicon dip-coating technique, discussed in the introductory section of this report, initially provided the basis for this R&D program.

To satisfy the earlier needs of the program, two dip-coating facilities were designed, constructed, and successfully used in pursuit of the work. As the program progressed, other sheet silicon coating techniques were considered and the SCIM technique (also previously discussed) was adopted and successfully developed. In pursuit of this work, two SCIM-coating facilities were also designed and constructed.

This portion of the report addresses the purpose and function along with a detailed description of these four coating facilities.

#### Dip-Coater No. 1

To perform systematically an investigation of growth parameters which affect grain size, dislocation density, and layer purity, a versatile and reliable dip-coating facility was assembled. To the greatest extent possible, the facility was designed and constructed in such a way that its characteristics did not further complicate the problems to be solved. Since modifications were expected from time to time, sufficient design flexibility permitted such modifications to be performed with minimum time and expense. Once the necessary modifications were made, however, which permitted this coater to routinely produce good reproducible sheet silicon coatings, its design was for the most part frozen and it was then used for providing sheet silicon for the solar cell development effort.

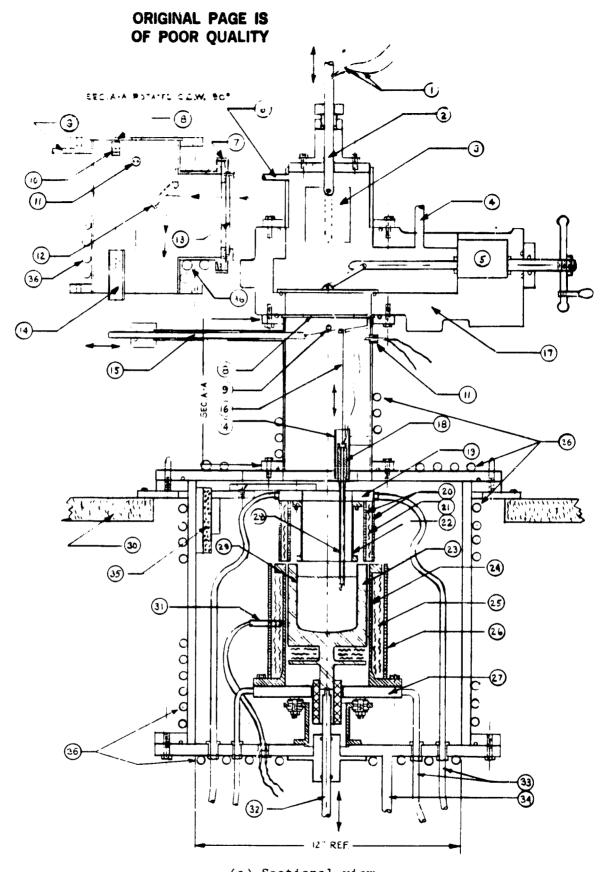

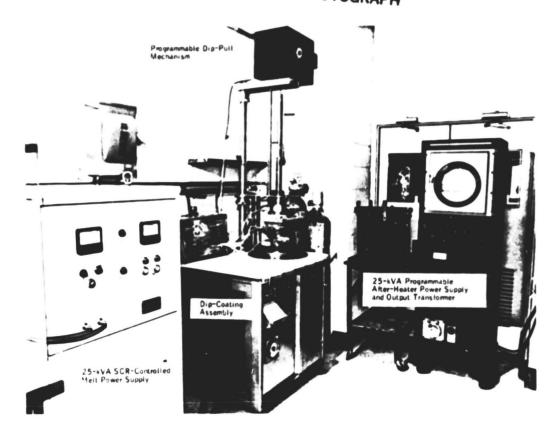

A sectional drawing of the facility is shown in Fig. 3 and a photograph of the assembled facility is shown in Fig. 4.

(a) Sectional view.

Figure 3. Dip-coater No. 1.

- (1) Substrate Thermocouple Lead Wires

- (2) Dip-Pull Quartz Tube

- (3) Ceramic Substrate

- (4) Gas Lock Chamber Pumping Port

- (5) Gate Valve Gear Box

- (6) Gas Lock Chamber Gas Outlet

- (7) Vacuum Connector Clamp

- (8) Stainless Steel or Moly Heat Shield

- (9) Melt-Dipping Chamber Gas Outlet

- (10) Melt Thermocouple Wire Guide

- (11) Melt Thermocouple Feed-Thru

- (12) 45-degree Chromium Plated Mirror

- (13) Quartz Window

- (14) Melt Thermocouple Weight Guide

- (15) Melt Thermocouple Positioning Rod

- (16) Nichrome Wire

- (17) Vacuum Gate Valve

- (18) Melt Thermocouple Weight

- (19) Water-Cooled "After Heater" Base Plate

- (20) Graphite Heat Shields ("After Heater")

- (21) Carbon Felt Insulation ("After Heater")

- (22) Graphite "After Heater"

- (23) Crucible Holder (Graphite)

- (24) Graphite Silicon Melt Heater

- (25) Carbon Felt Insulation (Silicon Melt Heater)

- (26) Graphite Heat Shield (Silicon Melt Heater)

- (27) Water-Cooled Silicon Melt Heater Base Plate

- (28) Quartz-Covered Melt Thermocouple

- (29) Quartz Crucible

- (30) Dip-Coating Facility Main Frame

- (31) Silicon Melt Heater Control Themiocouple

- (32) Crucible Positioning Rod

- (33) Water-Cooled Heater Electrical Leads

- (34) Melt-Dipping Chamber Pumping Port

- (35) Ceramic Insulation

- (36) Water-Cooled Surfaces

#### (b) Nomenclature.

Figure 3. Dip-coater No. 1 (concluded).

# ORIGINAL PAGE BLACK AND WHITE PHOTOGRAPH

Figure 4. Dip-coater No. 1 and associated equipment.

#### The coater included the following features:

- A melt crucible (item No. 29) capable of dip-coating 6.5cm x 5.0cm substrates. This capability permitted us to produce sheet silicon coatings in excess of the 20cm<sup>2</sup> JPL requirement.

- A purified graphite silicon melt heating element (item No. 24) powered by a temperature-controlled 25kW power supply. The heater assembly is mounted on a water-cooled copper base (item No. 27) and has only purified graphite cylinders item No. 26 and carbon felt (item No. 25) for insulation. This reduces melt chamber chemical contamination to a minimum.

- A Honeywell three-mode, precision temperature controller.

- A water-cooled, stainless-steel melt chamber (item No. 36) and viewing port assembly. This water cooling is needed to offset the lack of heater-element insulation. This feature also contributes to a low level of chemical contamination. The cleanable viewing port is used for observing the substrate as it is entering and leaving the melt.

- A gas-lock chamber (item No. 4) which permits the operator to load uncoated substrates and remove coated ones without shutting down the melt power. This feature is made possible by a large vacuum gate valve (item No. 5) which is located between the dip-coating chamber and the gas-lock chamber. The gas-lock chamber is readily purged with argon prior to opening the gate valve.

- A programmable, variable-speed dipping and pulling mechanism.

- A two-pen Honeywell electronic-type chart recorder for recording substrate position and temperature, both with reference to the melt. To efficiently characterize the optimum growth parameters it was mandatory that the growth conditions be accurately recorded for each sample substrate that was dip-coated. By doing so, as the physical properties of each coated sample were analyzed with respect to their particular growth conditions, positive direction could be given to the investigation. To provide this capability, the dipping and pulling mechanism was designed to provide an electrical readout which, when combined with the recorder's chart speed, provided dip-pull rate information.

- An afterheater (item No. 22), if needed, located immediately above the silicon melt. This heater, however, was never used for layers grown at normal (3 to 6 cm/min) pull rates, but was used later in the program for fast (> 12 cm/min) growth studies.

- A capability for orienting the substrate at an angle while performing the dip-pull operation. There were no well-defined theories which suggested that angle dipping may enhance grain size, but intuitively we expected that dipping an angle-oriented substrate would modify the liquid-solid interface, perhaps in a beneficial way. Future experiments, however, demonstrated that this was not the case.

- Two adjustable gas flowmeters, one for regulating and monitoring the gas flow through the melt chamber and another for purging the gas-lock assembly.

- A two-way gas valve for transferring from the argon gas cylinder to another cylinder should another type gas be desirable during a particular run.

- A water failure shutdown switch.

- A control panel for operating the facility.

#### Dip Coater No. 2

As the program progressed and dip-coater No. 1 was producing excellent large-grain sheet silicon coatings, we became reluctant to further modify No. 1 for experimental purposes. Dip-coater No. 2 was then designed and constructed to perform future experimental functions. The major task for this coater was to define the optimum conditions necessary to grow reasonably thick (i.e., 100µm) films at high rates (i.e., 9 to 18 cm/min). The design of this experimental dip-coater closely resembled that of dip-coater No. 1 with a few major exceptions. Dip-coater No. 2 was larger to allow more access around the liquid-solid interface and to allow special afterheaters to be used. The initial attempts to improve the growth rate while maintaining a film of reasonable thickness would involve the use of cold fingers to increase the temperature gradient at the liquid-solid interface. Dip-coater No. 2 had more access ports to accommodate the extra heating and/or cooling equipment necessary to grow at higher rates. The main experimental approach used to increase growth rates is to remove the latent heat of solidification by forced convective and radiative cooling through the use of cooling shoes placed near the liquid-solid interface. As will be discussed below, when this is done, an afterheater must also be used to prevent fracture of the coated substrate during cooling.

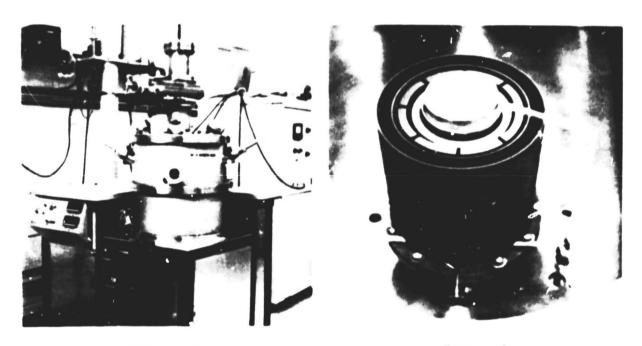

A photograph of dip-coater No. 2 is shown in Fig. 5. There are four access ports in the central portion of the chamber. Two are aligned at 30° to the geometrical center of the parting plane between the upper and lower chambers. There are four access ports in the top of the chamber that also point to the center of the parting plane and are inclined at an angle of 60°. During a run, the melt surface is typically level with the parting plane.

#### ORIGINAL PAGE

#### BLACK AND WHITE PHOTOGRAPH

The heater assembly is shown in Fig. 6. A silicon charge is shown inside a fused-silica crucible in a graphite crucible holder. The crucible holder in turn is situated inside a graphite resistance heater which is surrounded by a heat shield consisting of two concentric graphite cylinders spaced with graphite wool. The heat shield, heater, and crucible holder can be independently positioned. The glass tube on the right of the heater is used to blow argon gas over the melt surface during some runs to minimize SiO formation on the silicon coating when cooling shoes are not use. The heater is a picket-fence design considered to be more rugged than the thin-wall neater used in the other coater.

Figure 5. Experimental dip-coater.

Figure 6. Heater assembly in experimental dip-coater.

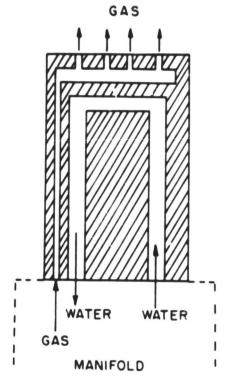

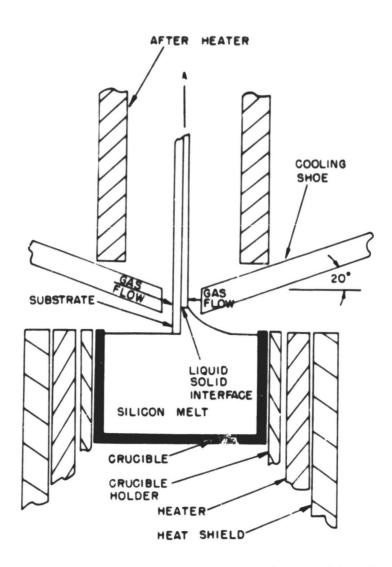

The position of front and back cooling shoes with respect to the substrate and heater assembly is shown in Fig. 7. The cooling shoes are machined from nickel and contain passages for both water cooling and gas flow. The cooling and gas flow in a cooling shoe is shown in Fig. 8. The gas exits through holes drilled in the end of the shoe. This was not an acceptable situation because the nonuniform cooling on the silicon results in coatings with ver-

## ORIGINAL PACE BLACK AND WHITE PHOTOGRAPH

tical striations. Examples will be shown later. On the other hand, nonuniform gas coverage clearly shows the effects of gas cooling on the growth pattern during dip-coating. Future modifications of the cooling shoes provided more even gas coverage over the surface of the substrate.

When forced convective cooling is provided at the liquid-solid interface during dip-coating, the thermal shock is almost always sufficient to fracture the substrate particularly at higher pull rates. To minimize thermal stresses in the coated substrate, an afterheater must be used. Early attempts with "passive" afterheaters (i.e., those heated only by conduction or radiation from the melt zone) were not satisfactory and an independently powered graphite resistance afterheater was eventually installed.

Figure 7. Photograph showing front and back cooling shoes in place in experimental dip-coater.

Figure 8.

Schematic showing water and gas flow in cooling shoes.

The heater is a thin-wall, cylindrical, split-resistance element similar to those used early in the program as crucible heaters. The heater is powered by unregulated a-c current through two transformers in series. The relation-

ship of the crucible, cooling, and afterheater is shown in Fig. 9. The cooling shoes are inclined at an angle of  $20^{\circ}$  to the melt surface. The arrows on the sketch indicate the direction of gas flow in each shoe. Note that in the shoe facing the uncoated side of the substrate, the holes are drilled parallel to the axis of the shoe, while the holes in the other shoe are drilled perpendicular to the substrate surface. This arrangement allows the back side of the substrate to be cooled slightly below the liquid-solid interface, while the front side is cooled above the interface. Typically, the gas flow rate on the back side of the substrate is four times that through the front shoe.

Figure 9. Schematic showing relationship of afterheater, cooling shoes, and crucible assembly in experimental dip-coater.

#### SCIM-Coater No. 1 (SCIM-I)

It was recognized early in the program that even though the dip-coating technique was successfully producing thin, smooth sheet silicon coatings of solar-cell quality, the method, nevertheless, was not easily adaptable to a continuous coating technique. In addition to this, experimentation had shown that the silicon melt was being progressively economicated with each successive substrate that was silicon-coated. In an effort to overcome these disadvantages, the SCIM technique (described in the Introduction of this report) was adopted as a promising continuous-coating method. The principal advantages of the SCIM technique are:

- Its coating principle vastly reduces the area of, and the time that the substrate is in contact with, the silicon melt. This feature lessens the possibility of the melt being progressively contaminated by the substrate.

- This technique permits the use of much larger substrates, which should allow the individual c. ystalline grains to develop larger in size.

- The scale-up coating throughput of this method is potentially superior because it eliminates the dipping and soaking time required with the dip-coating technique.

- The thermal stability of the solidification zone of a continuous coater should also be superior to a dip-coater, since the melt temperature would not be constantly upset by the immersion of unheated substrates.

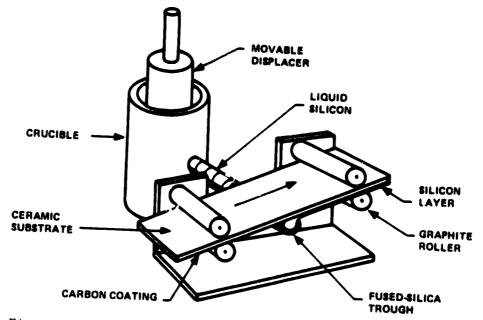

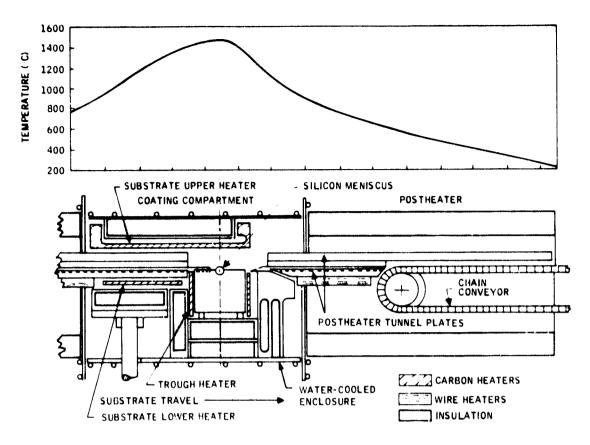

Figure 10 shows photographs of the SCIM-I facility. The coater is divided into five sections: (1) a compartment for substrate loading; (2) a preheater section for bringing the substate up to temperature; (3) a silicon coating compartment; (4) a postheater section for cooling the substrate; and (5) a compartment for substrate removal. During a coating run, these compartments are flushed ith an inert gas, most generally argon. The coater is powered by four temperature-controlled power supplies, two of which power the upper and lower preheaters. The third supply powers the main melt furnace and the fourth supply the coating trough furnace.

# ORIGINAL PAGE BLACK AND WHITE PHOTOGRAPH

(a) SCIM coater No. 1 during operational run.

(b) SCIM coater No. 1 showing bus bars from remotely located power supplies.

Figure 10. Photographs of SCIM-I.

Three of these four heaters are shown in Fig. 11. The preheater assembly consisted of a long graphite tunnel through which the substrates pass. A longitudinal temperature gradient was created along the tunnel by heating one end of the tunnel with the upper and lower proheater elements. This tunnel assembly was subsequently surrounded by a dual-walled insulated housing, also shown in Fig. 11. A cross-sectional view of the preheater assembly is illustrated in Fig. 12. The postheater is similar to the proheater except that it is slightly longer and passively heated by the coating trough and preheater. Figures 11 and 13 show the longitudinal thermal profiles which existed with this heating configuration. Initially, SCIM-I's transport mechanism consisted of stainless-steel chain convoyors which carried the substrates to, through, and from the growth chamber. The chain conveyors were driven by a "Digilok"-controlled, variable-speed drive system which was adjustable for growth velocities of tenths of cm/min to many cm/min. Given a relatively flat substrate, the fore and after chain conveyors were spaced to allow the substrate's center of gravity to carry it from one conveyor to the other. Special silicone rubber end gates permitted substrates to pass through the coater with a minimum of gas leakage. While the facility was primarily designed to horizontally coat substrates, provision was made for tilting the entire facility through about + 30°. This proved to be a valuable feature, since it was never possible to successfully coat substrates in the horizontal position.

The isotherms shown in Figs. 14 and 15 illustrate that the transverse temperature uniformity near the coating trough was very bad. Likewise, with this furnace configuration, the longitudinal temperature profile shown in Fig. 11 did not indicate a sharp enough temperature drop in the solidification zone of the coater. To correct both of these thermal inadequacies, a new type of trough-heater assembly was installed in the coater.

This heater was fabricated in such a way that the graphite trough holder itself was an active resistive element of the assembly (see Fig. 16). The rectangular legs of this heating assembly served the final substrate heating requirement. The power density of each leg was graduated in such a way that the substrate temperature never exceeded the melting point of silicon. Contrary to the original approach (see Fig. 11), the heating zone now terminated abruptly at the downstream edge of the trough.

Figure 11. SCIM-I preheater longitudinal thermal profiles.

Figure 12. Cross-sectional view looking into SCIM-I preheater compartment as viewed from the coating chamber.

Figure 13. SCIM-I postheater longitudinal thermal profile.

Figure 14. SCIM-I preheater isotherms.

### ORIGINAL PAGE IS OF POOR QUALITY

Figure 15. SCIM-I postheater isotherms.

Figure 16.

New trough/substrate heater

(also showing quartz crucible/

trough piece).

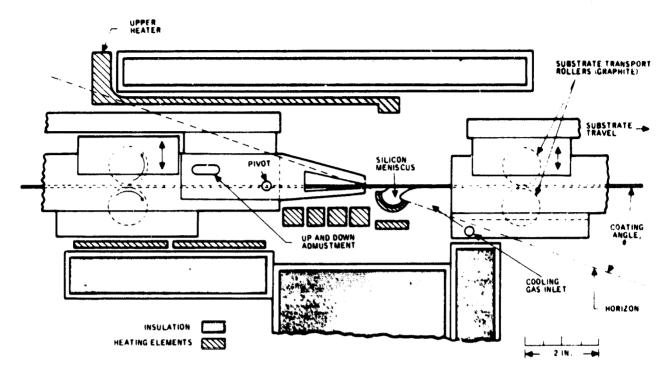

As shown in Fig. 17, the upper substrate heater was shortened, thereby shifting the peak temperature in an upstream direction.

Figure 17. SCIM-I coating chamber configuration showing combination trough/substrate heater.

Following the above modifications, the liquid-solid interface, if desired, could now be shifted until solidification occurred at the edge of the trough. This is the dip-coating equivalent of having the surface of the melt freeze around the substrate as it is being withdrawn from the melt. The temperature of this shorter heater was now a critical coating parameter. If too hot, solidification, as usual, occurred too far downstream. If not hot enough, the substrate would freeze to the melt. In spite of this fact, the solidification position could now be controlled.

The original chain-conveyor transport mechanism proved to be inadequate. Therefore, while the above furnace modifications were being implemented, a multiple-roller-type mechanism was installed in the coater. The lower roller was driven, whereas the upper roller served as an idler to maintain the alignment of the substrate. The rollers were made of graphite, since two sets of them operated at temperatues as high as 1200°C. The addition of these transport rollers required a modification to be made in the pre-

## ORIGINAL PAGE BLACK AND WHITE PHOTOGRAPH

heater and postheater assemblies, also shown in Fig. 17. It was with this coating configuration that the first successful continuous coating was performed.

#### SCIM-Coater No. 2 (SCIM-II)

In the last year of this contract, a second continuous-coating system (designated SCIM-II) was designed, constructed, and made operational. Its primary function was to demonstrate the capability of producing silicon sheet at a throughput rate of 350 cm<sup>2</sup>/min.

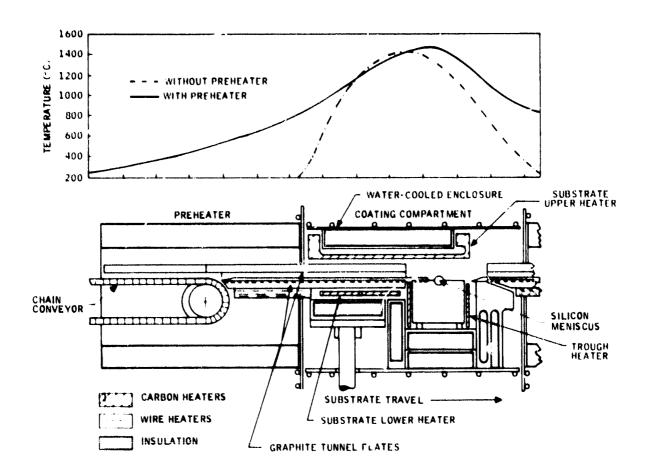

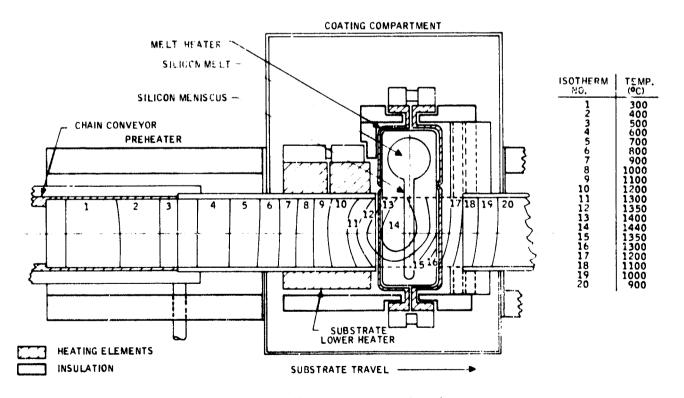

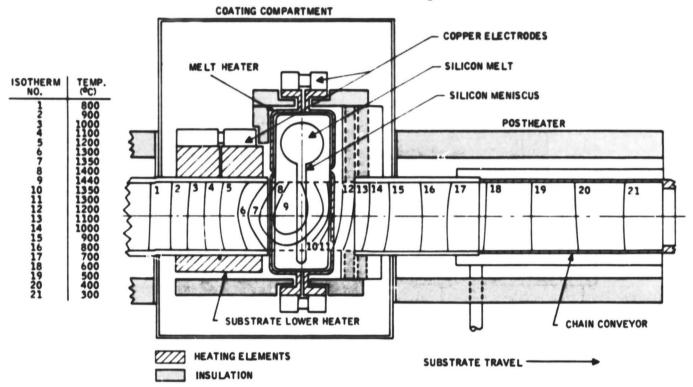

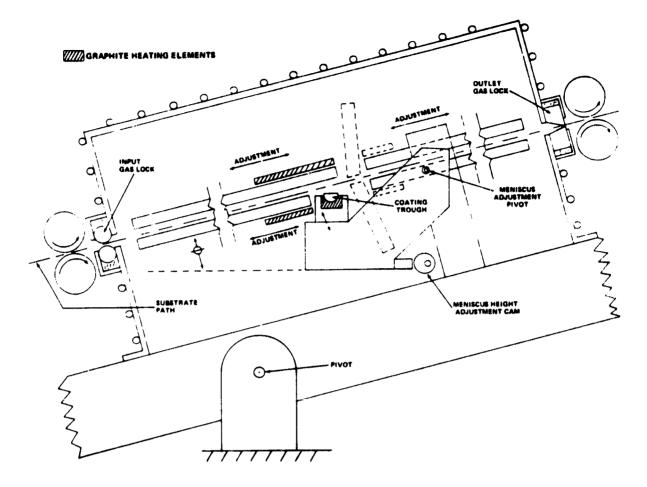

To achieve this goal, the coater was designed as shown in Fig. 18 to simultaneously coat (side-by-side) two 12.5cm-wide x 100cm-long mullite substrates. The coating experience acquired using SCIM-I was a valuable asset in the design of SCIM-II. The design of this new coater is shown schematically in Fig. 19.

Figure 18. SCIM-II exterior showing two side-by-side substrates entering the coater.

There are several key features which are different from the SCIM-I system. They are:

1) All assemblies within the coater are attached to a common water-cooled chassis (see Fig. 20). This assures us that proper alignment of key

Figure 19. Schematic cross section of SCIM-II.

parts will be maintained irrespective of operating temperature.

- 2) All metallic parts within the coater are water-cooled to improve the purity of the silicon layer, and the majority of the remaining parts are fabricated from graphite which can be purified prior to assembly.

- 3) The melt crucible and trough are contained in a graphite cradle assembly which permits convenient adjustment of trough-to-substrate distance during operation.

- 4) Side heaters powered by a separate power supply were installed to improve the transverse temperature uniformity in the substrate preheater. These side heaters, however, have proven so far not to be a necessary feature.

Figure 20. SCIM-II interior showing water-cooled base and substrates emerging from preheater.

5) The substrate transport mechanism consists of aluminum rollers which are fitted with several silicone rubber "O"-rings. The upper, as well as the lower roller, is driven by a loosely coupled spur gear. The entrance and exit rollers are positioned external to the cover containing the inert atmosphere needed for growth. In operation, they have proven to be very effective in performing the transport function. With this method of substrate transport, however, the substrate used must be at least as long as the distance (97cm) between the rollers. This can be a problem if a substrate breaks during coating. In this respect, the multiple-roller method used in SCIM-I is superior. However, the numerous rollers in SCIM-I, some of which operate at temperatures as high as 1200°C, proved to be only marginally dependable.

6) The water-cooled cover on SCIM-II serves only the function of containing the inert gas. As such, when this cover is removed, the inner walls are easy to clean. Likewise, when removed, the entire inner-workings of the coater are easily accessible for maintenance.

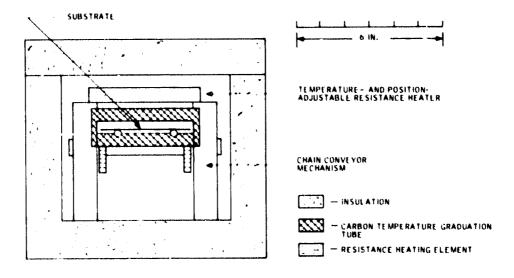

The preheater and postheater design used in SCIM-II was fashioned after that of SCIM-I. This design was used because these functions in SCIM-I performed well. The purpose of the preheater is to bring the substrate from room temperature to the melting point of silicon in a manner which neither fractures nor warps the substrate. This is done by using a narrow graphite tunnel through which the substrate passes. One end of the tunnel is heated by a graphite resistance heater, and thermal conduction along the tunnel creates the needed temperature gradient. The postheater is similarly constructed. It, however, is a passive element deriving its heat from the preheater and the coating trough. This coating configuration produces a temperature profile with a rapid fall in temperature immediately downstream from the coating trough, thus creating the required thermal environment for solidification. To ensure that the coated substrate will emerge from the machine at a temperature of less than 232°C (the maximum operating temperature of the silicone rubber "O"-rings), a water-cooled heat sink is attached to the downstream end of the postheater. The thermal modeling contributing to this design is discussed later in this report. In order to achieve a uniform transverse temperature, the preheater and postneater are substantially wider than the width of the side-by-side substrates being coated.

The trough heater and the fused-silica trough-crucible assembly are also fashioned after the design used in SCIM-I. The quartz trough nestles in an electrically active trough heater. The cross section of this heater is reduced at the electrode end in order that additional power can be generated to offset losses by conduction to the water-cooled copper electrodes and by radiation through the viewing port. The trough heater is also made purposely long for temperature uniformity reasons.

As with SCIM-I, SCIM-II can also be tilted to coating angles up to  $20^{\circ}$  to provide the necessary meniscus stability. To date, 10cm-wide substrates have been coated at angles of  $10^{\circ}$  and  $20^{\circ}$  these results are included elsewhere in this report.

The most obvious problem during the initial operation of SCIM-II was the

buckling and/or breakage of the coated substrates. Experiments were performed without silicon in the system to clarify the situation. Initial experiments quickly showed that at high speed (15 cm/min) there was only minor buckling, but at lower speeds, the buckling became more severe, and below 6 cm/min the substrates broke. The results were qualitatively the same regardless of the silicon coating and regardless of whether one side of the substrate was carbon-coated.

The original design of the entrance and exit tunnels was based on a design speed of 15 cm/min. The most interesting result is that at this high speed there has been little warping and no cracking of any substrates. This is true of the original design as well as all subsequent modifications.

The problem is that without forced convective cooling or use of an asymmetric growth mode, there is no chance of getting the desired silicon thickness at high speed. The thickness is needed to demonstrate slot coverage and cell performance. Thus, we wanted to do initial coatings in the range of 4 to 6 cm/min. At these lower speeds, the substrates have warped, buckled, or cracked. The proposed explanation is that the longitudinal temperature profile must be the cause of the problem. At high speeds, the longitudinal profile is smoother than at low speeds because the heat capacity of the substrate causes a temperature lag. Thus, the purpose of the changes in tunnel design has been to linearize the temperature profile. Fortunately, this has reduced the problem at low speeds, and has not created any problem at high speeds.

The explanation in terms of thermal stresses caused by longitudinal temperature gradients is the same as that proposed by Surek for edge-defined, film-fed ribbon growth or EFG. The origin of thermal stress and the strategy to avoid it are discussed in SOC Quarterly Report No. 15, published 31 July 1980.

As discussed by Surek, 1 the equation for the stress is

$$\sigma_{xx} = \frac{\alpha_E b^2}{\sigma} \left( 1 - \frac{3_y^2}{b^2} \right) \frac{d^2 T}{dx^2}$$

(1)

in the case where the second derivative of the temperature is significant. Here,  $\alpha$  is the expansion coefficient, E is young's modulus, and b is one-half the substrate width. The solution is positive at the center (y = 0) and

A. D. Morrison, et al., "Large-Area Silicon Sheet by EFG," Mobile Tyco Energy Corporation Annual Progress Report, September 15, 1976.

negative at the edges (y = ± b), indicating tension and compression, respectively, when  $d^2 T/dx^2$  is positive. At the ends of the substrate, the solution is not valid, since  $\sigma_{xx} = 0$ . Thus, in the vicinity of the end, there are  $\sigma_{yy}$  and  $\sigma_{xy}$  stresses which can also be derived analytically.

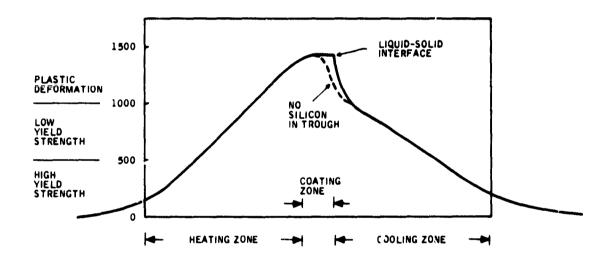

It is obvious that the temperature profile cannot be entirely linear in any substrate which is heated and then cooled and that both types of non-linearities must be encountered, as shown in Fig. 21. Thus, thermal stress must always exist. However, there is a strategy which, at least in principle, can reduce the residual thermal stress to zero. This strategy is detailed in Fig. 21. The idea is to have the concave portions of the profile in regions with high yield stress. Thus, thermal stresses do exist, but they result only in elastic deformation so that when the sample is again in a  $d^2T/dx^2 = 0$  region, the residual thermal stress is zero.

Figure 21. Strategy to eliminate effects of thermal stress. In the high-temperature regions, the ceramic can deform without buckling or cracking, and stress in the silicon is annealed as it is generated. At low temperatures, only elastic deformation occurs. The intermediate temperature ranges are critical, and the temperature profile must be linear.

At sufficiently high temperatures, the yield strength of both the ceramic and the silicon is low so that the sample can undergo plastic deformation with no buckling or cracking. Stress relaxation studies in silicon show that at 1000°C the stress relaxation time is a few seconds. Thus, in the vicinity of the trough and especially at the liquid-solid interface, the

presence of large nonlinearities in the temperature gradient will not have harmful effects.

In summary, the strategy is to consider the problems in terms of three temperature zones. The following strategy applies to both the heating and cooling zones:

- a) The high-temperature zone (T  $\gtrsim 1000^{\circ}$ C) can tolerate large nonlinearities in the temperature profile.

- b) The intermediate-temperature zone ( $1000^{\circ}C \ge T \ge *70^{\circ}C$ ) must have a very linear profile.

- c) The low-temperature zone  $(500^{\circ}\text{C} \gtrsim T)$  can tolerate large nonlinearities such that the thermal stress does not exceed the elastic limit of silicon on ceramic.

According to the design strategy based on stress analysis (Fig. 21), a linear longitudinal temperature profile is sought for the temperature range of low yield strength, from 500 to  $1000^{\circ}$ C. The linear profile is necessary in both heating and cooling in order to eliminate or at least greatly reduce residual stresses in the coated ceramic panels. A second requirement is to provide rapid initial cooling of the coated substrate, as prescribed by heat balance at the silicon liquid-solid interface. The second requirement will not be in conflict with the first one if rapid cooling is restricted to the plastic deformation region, as indicated in Fig. 21.

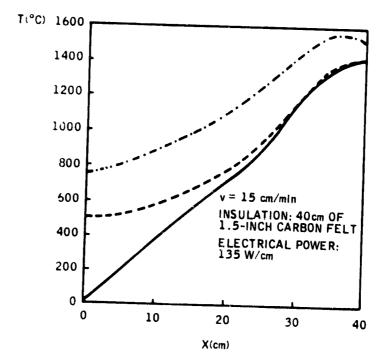

It is expected that the thermal design of a production coater can be optimized for a given fixed feed rate. In the experimental growth system, thermal design is complicated by the need to accommodate more than one feed rate; an ideal temperature profile is difficult to maintain over a wide range of feed rates. At low speed, the substrate is likely to heat up over-rapidly on first entering the heating chamber. At higher speeds, this is moderated by the thermal inertial time lag. On the other hand, high-speed panels tend to emerge from the cooling chamber insufficiently cooled. The first problem can be eliminated by heat-sinking at the entrance to the heating chamber, whereas the second problem is relieved by heat-sinking at the exit from the cooling chamber. A more flexible means of accommo-

dating different speeds is to vary the amount of insulation placed in the respective chambers.

A great deal of insight into these and other aspects of the thermal design problem has been provided by a mathematical analysis of the heating and cooling chambers. A brief thermal description of the mathematical models follows.

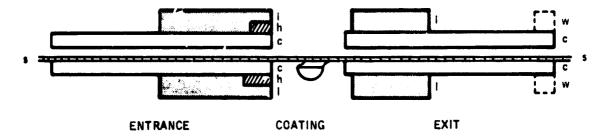

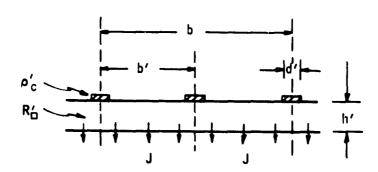

The substrate panels are transported at ambient temperature to the heating chamber, which is shown in schematic cross section in the left half of Fig. 22. This is made up of pairs of active heaters, carbon guides (also functioning as the passive heaters), and insulating layers. The lmm-thick ceramic substrates move left to right between the guides, acquiring heat by radiation from the guides, so that they reach 1693K when they arrive at the right end of the tunnel. At this temperature, the melting point of silicon, they are ready for silicon coating in the chamber immediately to the right. It will be noted that the moving substrates extract a total of  $\rho$ Cwt $\Delta$ T joules of heat per centimeter of length, where  $\rho$  and C are the density and specific heat, w and t are panel width and thickness, and  $\Delta T$ is the temperature rise. If the panel feed rate is v cm/sec, the active heaters then must supply energy at a rate greater than oCwtoT watts. The "greater than" may be made to approach "equal to" if wasted heat is minimized; that is, the quantity and placement of insulation are such as to prevent significant losses to the water-cooled case.

Figure 22. Schematic cross section of SCIM-II showing simplified arrangement of various thermal elements used in modeling. h = resistive heater; c = carbon (guide); i = insulation; w = heat sink (when present); s = substrate.

After the silicon coating step, the substrates traverse a cooling chamber (right half of Fig. 22) of similar geometry to the entrance tunnel. The important difference is the omission of the active heaters. However, the water-cooled case and variable insulation are essential. Inasmuch as cooling is passive with the case being the heat sink, the carbon guides are a hindrance to cooling though needed for mechanical support. The guides act like heat shields, interrupting the radiative transfer from silicon-coated panels to the case. The important heat escape path is vertical from substrate to guide to case, with a lesser contribution by way of longitudinal conduction through the guides.

The need for design flexibility is reflected in the variable structure of the mathematical models; provisions are included also for experimental calibration:

- The amount of insulation used in the heating and cooling chambers can be varied. Adjusting insulation may be the quickest and easiest way to set up different substrate speeds.

- The far ends of the cooling chamber guides have tended to reach excessively high temperatures in both theory and practice. The theoretical model includes an optional heat sink at these ends.

- "Standby" versions of the models have been provided. These represent heating and cooling chamber with heaters active but no substrate resent. The main purpose for these versions is to calibrate the models against temperature measurements, which are normally taken with the chambers empty.

Only longitudinal temperature profiles are analyzed here, since these are believed to be associated with warping and breakage. Transverse temperature variations also occur and are discussed elsewhere. The main problem caused by transverse variations is coating nonuniformity, and this is being successfully attacked by heater redesign.

The physical relationship upon which the thermal models are based will next be summarized. All temperature profiles are assumed to be one-dimensional; thus, variations in the transverse direction are ignored. Several thermal elements interact with one another (Fig. 22) so that as many as five coupled heat equations must be solved. Basically, the electrical input produces heat in the resistive heaters (h), and this heat spreads along both heating

chamber guides (c) by thermal conduction. In the steady state, the heated guides release part of this energy by radiation to the entering substrate(s) and the rest is lost by radiation and conduction to the ambient. The model includes a convective heat transfer coefficient, but this has been set equal to zero in the calculations reported here. A significant portion of the heat loss takes place from insulated surfaces due to the limited thicknesses of carbon felt. The substrate(s) acquires heat from the guides so that its temperature increases from approximately ambient at the left to the coating temperature (1420°C).

In the cooling chamber, the process is essentially reversed. The substrate is progressively cooled by radiation to the cooling chamber guides and by conduction in the downstream direction. Because of the heat-shield effect, the cooling rate is lower than it would be in the case of direct radiation to the 300K ambient. The cooling problem is further aggravated at the far (right) end because thermal conduction within the guides tends to elevate the temperature at that end. This effect can be greatly relieved by heat-sinking (w).

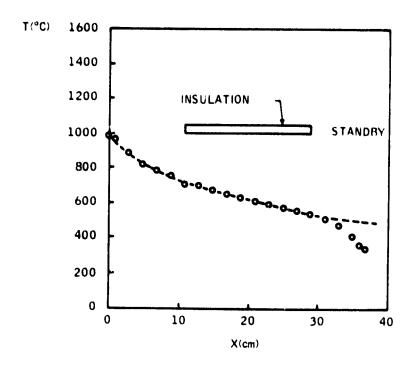

End effects are found to be significant and are included both at the external end facing the cool environment, and the internal ends facing the coating chamber. Not only the actual ond surfaces are affected but also parts of the internal surfaces close to the ends. The moving substrate is not completely cooled when it emerges from the cooling chamber. It is important that enough cooling has taken place at this point to avoid a further precipitous temperature drop outside of the chamber. In the numerical calculations, a practical approximation is required for the boundary condition at infinity. We use T = T<sub>O</sub> (room temperature) at a point some distance (a few cm) beyond the tunnel end. Over this distance, the radiation environment is assumed to be at temperature T<sub>O</sub>. It is easily verified that the approximate boundary condition does not affect the numerical solutions for the temperature within the chamber. Figure 23 shows calibration of the model against measurements taken by using a thermocouple instead of the substrate.

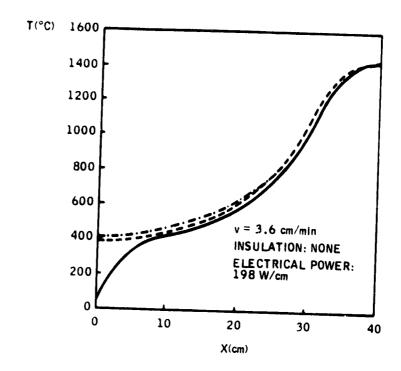

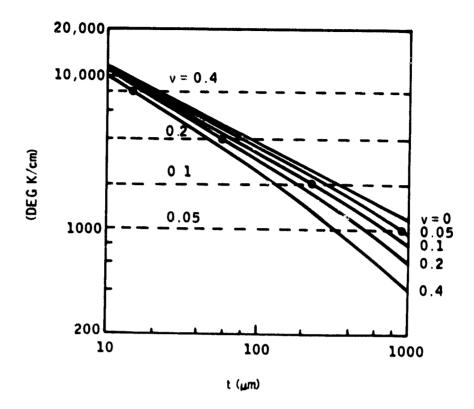

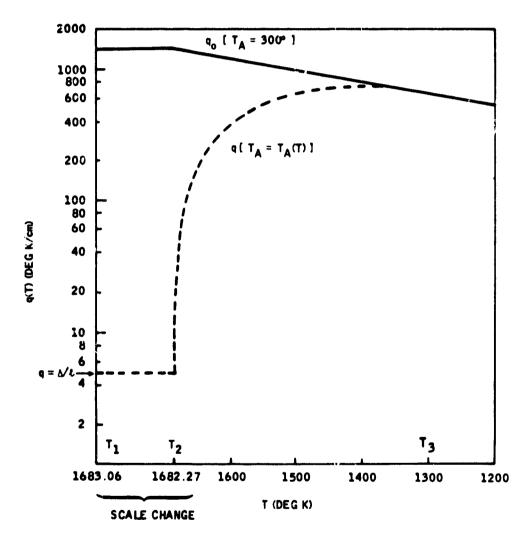

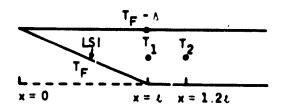

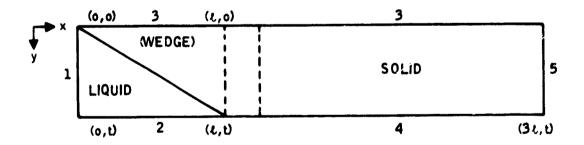

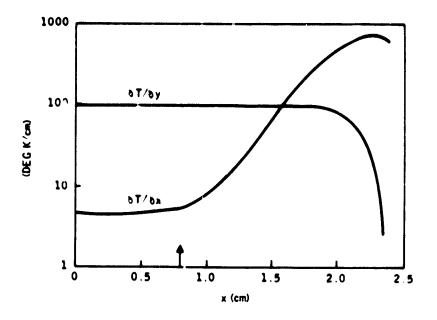

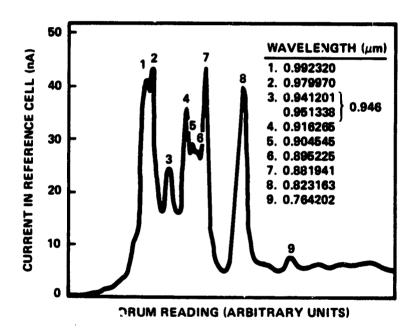

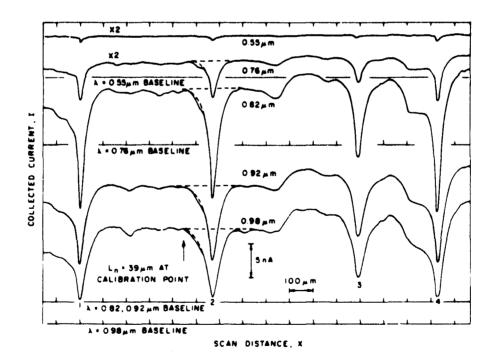

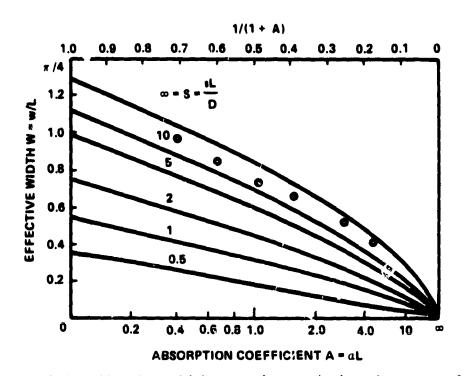

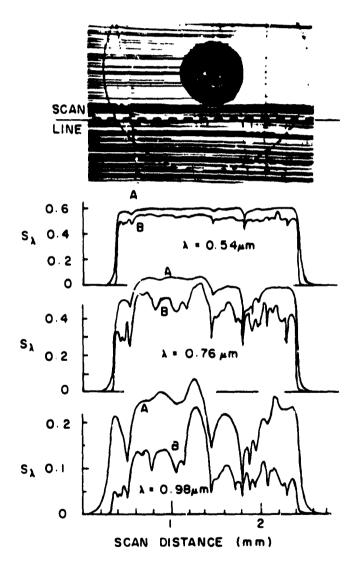

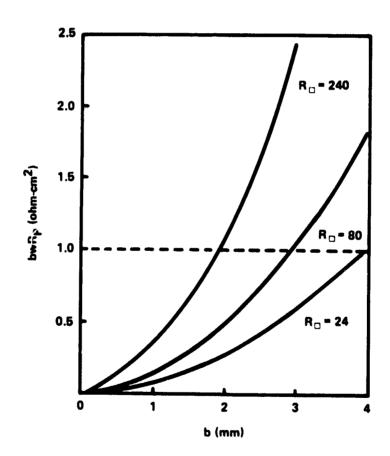

The finite-difference grid for the heating chamber represents 1cm increments in longitudinal position, or 41 points for a 40cm tunnel. Since there are five coupled layers (two heater-insulation layers, two guides, and one substrate), there are  $5 \times 41 = 205$  nodel equations which are solved by a