### NOTICE

THIS DOCUMENT HAS BEEN REPRODUCED FROM MICROFICHE. ALTHOUGH IT IS RECOGNIZED THAT CERTAIN PORTIONS ARE ILLEGIBLE, IT IS BEING RELEASED IN THE INTEREST OF MAKING AVAILABLE AS MUCH INFORMATION AS POSSIBLE

Proceedings of the Conference on High Temperature Electronics, Held at Tucson, Arizona on March 25-27, 1981

Arizona Univ. Tucson

Prepared for

National Science Foundation Washington, DC

1981

U.S. Department of Commerce National Technical Information Service

### **PROCEEDINGS**

OF THE CONFERENCE ON

### HIGH TEMPERATURE ELECTRONICS

March 25-27, 1981 Tucson, Arizona

#### SPONSORED BY

IEEE Industrial Electronics and Control Instrumentation Group

**IEEE Solid State Circuits Council**

**National Aeronautics and Space Administration**

Department of Energy

Division of Engineering, Mathematics, and Geosciences

Nuclear Regulatory Commission

Division of Reactor Safety Research

**National Science Foundation**

**Los Alamos National Laboratory**

The University of Arizona

REPRODUCED BY

NATIONAL TECHNICAL

INFORMATION SERVICE

U.S. DEPARTMENT OF COMMERCE

SPRINGFIELD, VA 22161

| REPORT DOCUMENTATION PAGE                                                                                        | 1. REPORT NO.<br>NSF/ECS-81007                                                                                                                                  | 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3. Recipient's Access                                                                                                |                                             |  |  |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|

| . Title and Subtitle                                                                                             | 42L\ E03_0100\                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PB8Z 1 1                                                                                                             | 44 T A                                      |  |  |

| High Temperature Electronics, Proceedings of the Conference on (Tucson, Arizona, March 25-27, 1981)              |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |                                             |  |  |

|                                                                                                                  |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.                                                                                                                   |                                             |  |  |

| D.J. Hamilton, J.B.                                                                                              | 8. Performing Organi<br>81CH1658-                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |                                             |  |  |

| 9. Performing Organization Name a                                                                                | and Address                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10. Project/Task/Wo                                                                                                  |                                             |  |  |

| University of Arizon                                                                                             | 18                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |                                             |  |  |

| Tucson, AZ 85721                                                                                                 |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11. Contract(C) or Gr                                                                                                | ant(G) No.                                  |  |  |

|                                                                                                                  |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                    | 7                                           |  |  |

|                                                                                                                  |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (G) ECS810803                                                                                                        | /<br>                                       |  |  |

| 12. Sponsoring Organization Name<br>Directorate for El                                                           |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13. Type of Report &                                                                                                 | 13. Type of Report & Period Covered         |  |  |

| National Science                                                                                                 |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Proceedin                                                                                                            | Proceedings                                 |  |  |

| 1800 G Street, N.V                                                                                               |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14.                                                                                                                  | 14.                                         |  |  |

| Washington, DC 20                                                                                                | <u> </u>                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |                                             |  |  |

| Submitted by: Comm                                                                                               | nunications Program (OP                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |                                             |  |  |

|                                                                                                                  | ional Science Foundatio                                                                                                                                         | n .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                      |                                             |  |  |

|                                                                                                                  | nington, DC 20550                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |                                             |  |  |

| 16. Abstract (Limit: 200 words)                                                                                  | organized to re-evalua                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |                                             |  |  |

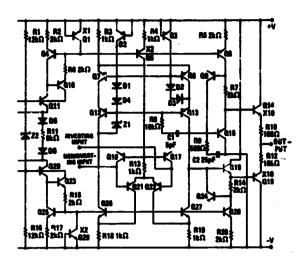

| terials and devices<br>and an example of a<br>Temperature Electron<br>two sessions): Pass<br>Systems: Process Cl | e efforts. More than he rather than circuits paper presented in each nics Applications in Spaive Components for Higharacteristics and Desiresently Available En | and systems. Control of the session are (  bace Exploration of the session of the | onference session ti<br>l) User Requirements<br>s; (2) Devices (incl<br>peration; (3) Circui<br>a 300 degree QUAD or | tles<br>: High-<br>uded<br>ts and<br>: AMP; |  |  |

| 17. Document Analysis a. Descrip                                                                                 |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Materials                                                                                                            |                                             |  |  |

| Proceedings<br>Electronics                                                                                       | Electronic pack<br>Semiconductors                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MATORIALE                                                                                                            |                                             |  |  |

| Electric devices                                                                                                 |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      | <del> </del>                                |  |  |

| Design                                                                                                           | Circuits                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Transistors<br>Metallizing                                                                                           |                                             |  |  |

| b. Identifiers/Open-Ended Term                                                                                   | Circuits                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Transistors                                                                                                          | · ·                                         |  |  |

| High-temperature ele<br>Research and develo<br>User needs                                                        | ectronics                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Transistors                                                                                                          |                                             |  |  |

| Research and develo                                                                                              | ectronics                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Transistors                                                                                                          |                                             |  |  |

| Research and develo<br>User needs                                                                                | ectronics                                                                                                                                                       | (materials)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Transistors<br>Metallizing                                                                                           | No. of Pages                                |  |  |

| Research and develo<br>User needs<br>c. COSATI Field/Group                                                       | ectronics                                                                                                                                                       | (materials)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Transistors Metallizing  Class (This Report) 21.                                                                     | No. of Pages                                |  |  |

#### PAPERS PRESENTED

at the conference on

### HIGH TEMPERATURE ELECTRONICS

March 25-27, 1981 Tucson, Arizona

#### CONFERENCE CHAIRMAN

Dr. J. Byron McCormick Los Alamos National Laboratory

#### COCHAIRMEN

Dr. D. J. Hamilton

Dr. W. J. Kerwin

The University of Arizona

Dr. J. A. Narud

Los Alamos National Laboratory

#### SPONSORED BY

IEEE Industrial Electronics and Control

Instrumentation Group

IEEE Solid State Circuits Council

National Aeronautics and Space Administration

Department of Energy

Division of Engineering, Mathematics, and

Geosciences

Nuclear Regulatory Commission

Division of Reactor Safety Research

National Science Foundation

Los Alamos National Laboratory

The University of Arizona

81CH1658-4

Any opinions, findings, conclusions or recommendations expressed in this publication are those of the author(s) and do not necessarily reflect the views of the National Science Foundation.

Library of Congress Catalog Card Number: No LC

#### TABLE OF CONTENTS

| PREFACE     | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                              | ٧  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| SESSION I.  | USERS REQUIREMENTS                                                                                                                                                                                   |    |

| Chaice      | man: Dr. John C. Rowley, Los Alamos Scientific Laboratory                                                                                                                                            |    |

| I           | digh-Temperature Electronics Applications in Space Explorations                                                                                                                                      | 3  |

| •           | W. W. Managan, Argonne National Laboratory                                                                                                                                                           | 9  |

| E           | High Temperature Electronics Utilization for Present and Future Nuclear Instrumentation M. Marx Hintze, E G & G Idaho, Incorporated                                                                  | 11 |

| ı           | High Temperature Electronic Requirements in Aeropropulsion Systems                                                                                                                                   | 13 |

|             | Present and Future Needs in High Temperature Electronics for the Well Logging Industry N. H. Sanders, Dresser Industries                                                                             | 17 |

| SESSION II. | . DEVICES                                                                                                                                                                                            |    |

| Chair       | man: Dr. S. W. Depp, IBM Research Laboratory                                                                                                                                                         |    |

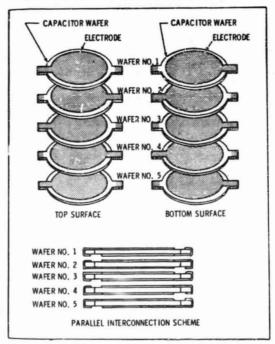

| I           | Passive Components for High Temperature Operation                                                                                                                                                    | 21 |

| I           | Cevelopment of an 1100°F Capacitor                                                                                                                                                                   | 25 |

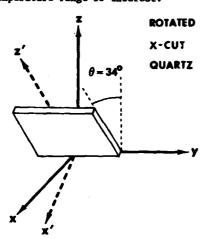

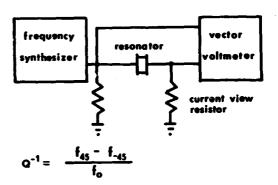

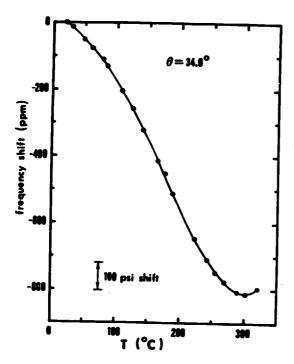

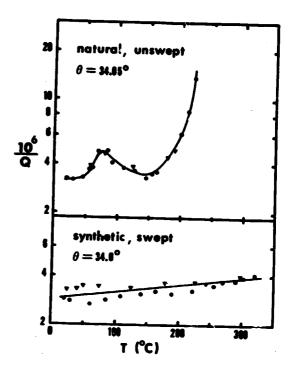

| ŀ           | High-Temperature Measurements of Q-Factor in Rotated X-Cut Quartz Resonators                                                                                                                         | 29 |

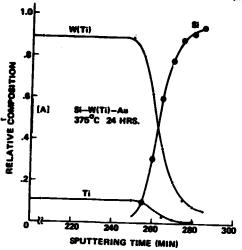

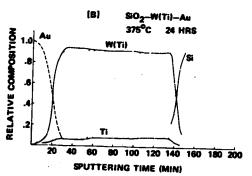

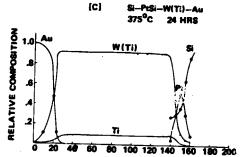

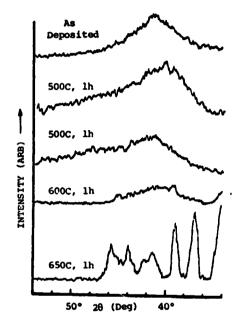

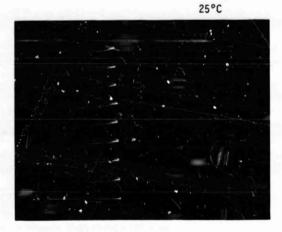

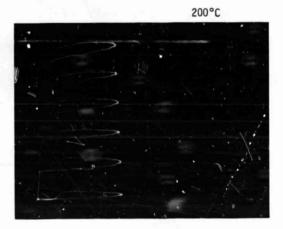

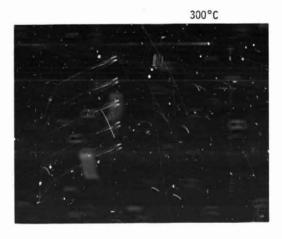

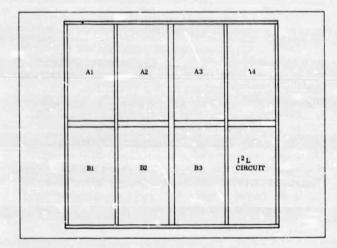

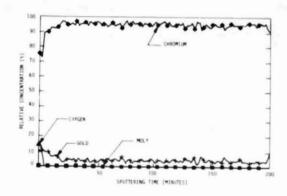

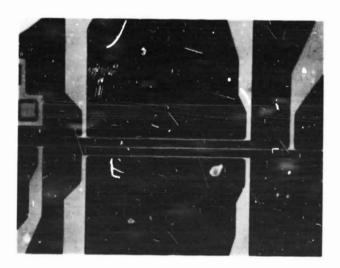

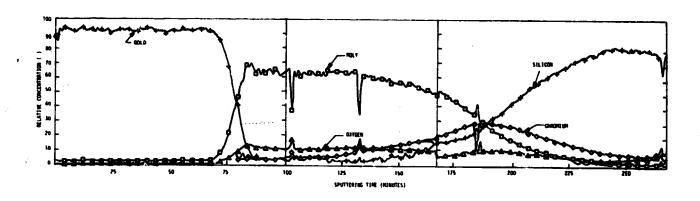

|             | Assessment of High Temperature Metallizations for I <sup>2</sup> L and CMOS Technologies                                                                                                             | 33 |

|             | Amorphous Metallizations for High-Temperature Semiconductor Device Applications J. D. Wiley, J. H. Perepezko, and J. E. Nordman, University of Wisconson;<br>G. Kang-Jin, Chinese Academy of Science | 35 |

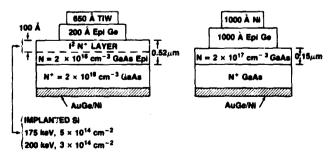

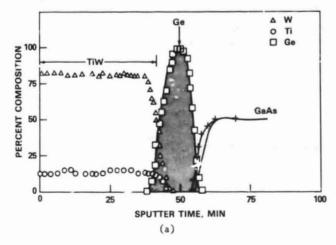

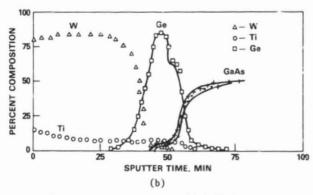

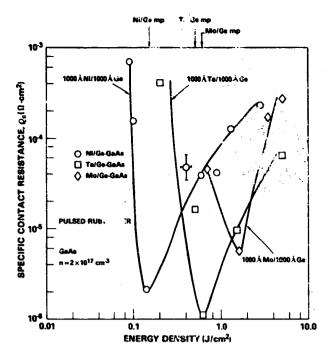

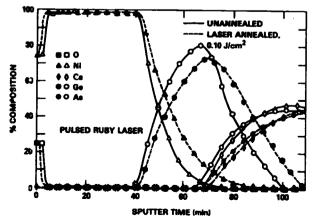

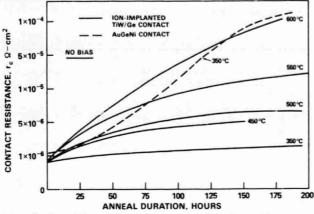

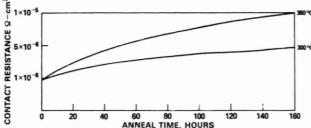

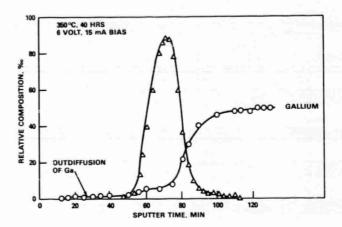

|             | Ohmic Contacts to GaAs for High-Temperature Device Applications                                                                                                                                      | 39 |

| SESSION III | I. DEVICES (cont'd)                                                                                                                                                                                  |    |

| Chairm      | man: Dr. S. W. Depp, IBM Research Laboratory                                                                                                                                                         |    |

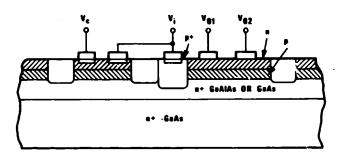

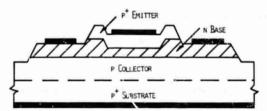

|             | Pabrication and High Temperature Characteristics of Ion-Implanted GaAs Bipolar Transistors Transistors and Ring-Oscillators                                                                          | 45 |

| I           | Development of Integrated Thermionic Circuits for High-Temperature Applications                                                                                                                      | 49 |

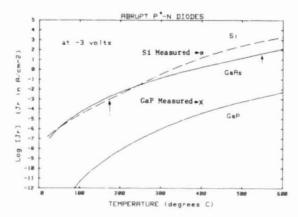

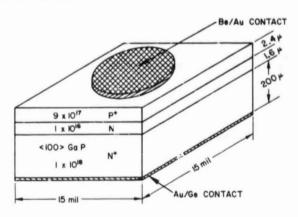

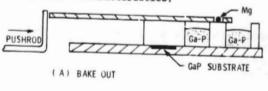

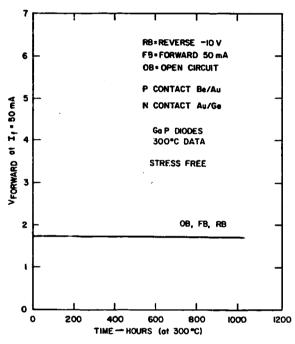

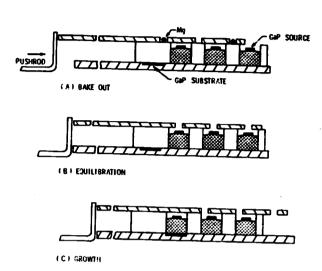

| ď           | Gallium Phosphide High Temperature Diodes                                                                                                                                                            | 55 |

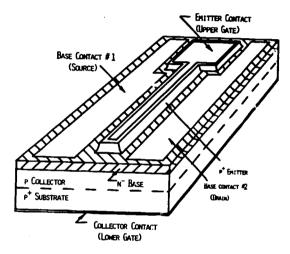

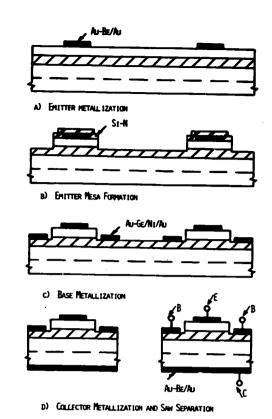

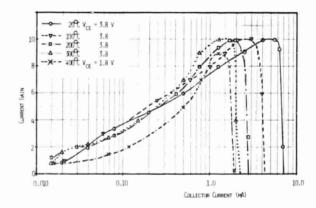

| A           | Gallium Phosphide High-Temperature Bipolar Junction Transistor                                                                                                                                       | 59 |

| 1           | Reliability Study of Refractory Gate Gallium Argenide MESFETS                                                                                                                                        | 63 |

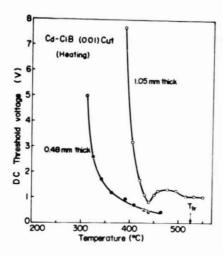

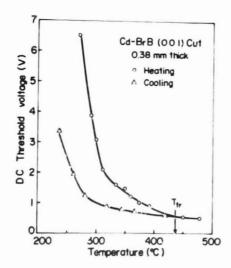

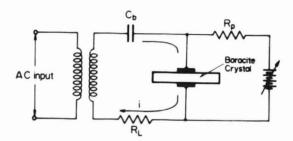

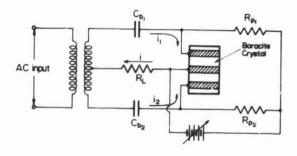

| I           | Rectrical Switching in Cadmium Boracite Single Crystals                                                                                                                                              | 67 |

| ī           | Thatever Happened to Silicon Carbide                                                                                                                                                                 | 71 |

|         | IV. CIRCUITS AND SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                            |                   |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|