## NOTICE

THIS DOCUMENT HAS BEEN REPRODUCED FROM MICROFICHE. ALTHOUGH IT IS RECOGNIZED THAT CERTAIN PORTIONS ARE ILLEGIBLE, IT IS BEING RELEASED IN THE INTEREST OF MAKING AVAILABLE AS MUCH INFORMATION AS POSSIBLE

TIASA GR- 166791

The University of Tennessee Department of Electrical Engineering Knoxville, Tennessee 37916

(NASA-CR-160791) A STUDY OF UNIVERSAL N82-25420 MODULATION TECHNIQUES APPLIED TO SATELLITE DATA COLLECTION Final Report (Tennessee Univ.) 176 p HC A09/MF A01 CSCL 17B Unclas G3/32 21917

#### A STUDY OF

#### UNIVERSAL MODULATION TECHNIQUES

#### APPLIED TO SATELLITE DATA COLLECTION

Final Report

December 1980

Contract No. NAS5-24250

Prepared for

National Aeronautics and Space Administration Goddard Space Flight Center Greenbelt, Maryland 20771

#### PRECEDING PAGE BLANK NOT FILMED

#### Abstract

A scheme for a universal modulation and frequency control system for use with data-collection platform (DCP) transmitters is examined. The final design discussed can, under software/firmwave control, generate all of the specific digital data modulation formats currently used in the NASA satellite data-collection service and can simultaneously synthesize the proper RF carrier frequencies employed.

A novel technique for DCP time and frequency control is presented. The emissions of NBS radio station WWV/WWVH are received, detected, and finally decoded in microcomputer software to generate a highly accurate time base for the platform; with the assistance of external hardware, the microcomputer also directs the recalibration of all DCP oscillators to achieve very high frequency accuracies and low drift rates versus temperature, supply voltage, and time.

The final programmable DCP design also employs direct microcomputer control of data acquisition, data reduction, formatting, transmitter switching, and system power management. The system hardware and software was described in detail. Finally, future techniques for PDCP design, projected tasks for PDCP field units, and the anticipated capabilities of new units to handle these jobs are presented.

**iii**

### CONTENTS

| SECT ION |      |                                          | PAGE |

|----------|------|------------------------------------------|------|

| 1        | INTR | ODUCTION                                 | 1-1  |

|          | 1.1  | Background and Purpose                   | 1-1  |

|          | 1.2  | Design Philosophy                        | 1-2  |

| 2        | DIGI | TAL OSCILLATOR SYSTEM                    | 2-1  |

|          | 2.1  | System Concepts                          | 2-1  |

|          | 2.2  | Digital Oscillator Theory                | 2-2  |

|          | 2.3  | Software Implementations                 | 2-11 |

|          |      | 2.3.1 Demonstration Software for 1802    | 2-14 |

|          |      | 2.3.2 Demonstration Software for 8080A   | 2-27 |

|          | 2.4  | Hardware Design Considerations           | 2-37 |

|          |      | 2.4.1 Original PDCP/UM Design Parameters | 2-39 |

|          |      | 2.4.2 Modified Hardware Configuration    | 2-48 |

| 3        | MICR | OPROCESSOR BOARDS                        | 3-1  |

|          | 3.1  | Introduction                             | 3-1  |

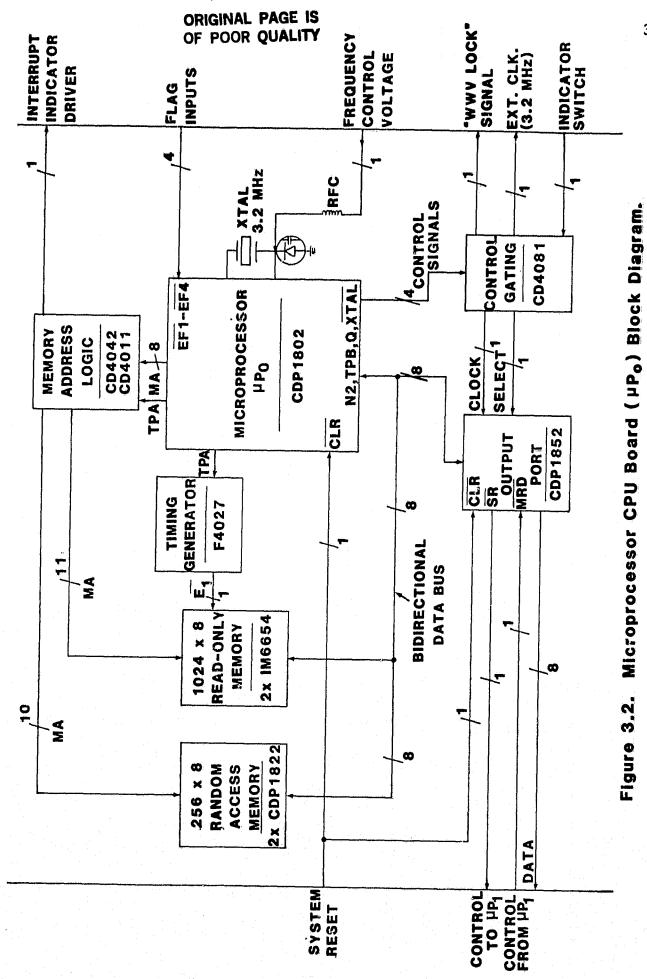

|          | 3.2  | CPU Board - $\mu P_0$                    | 3-4  |

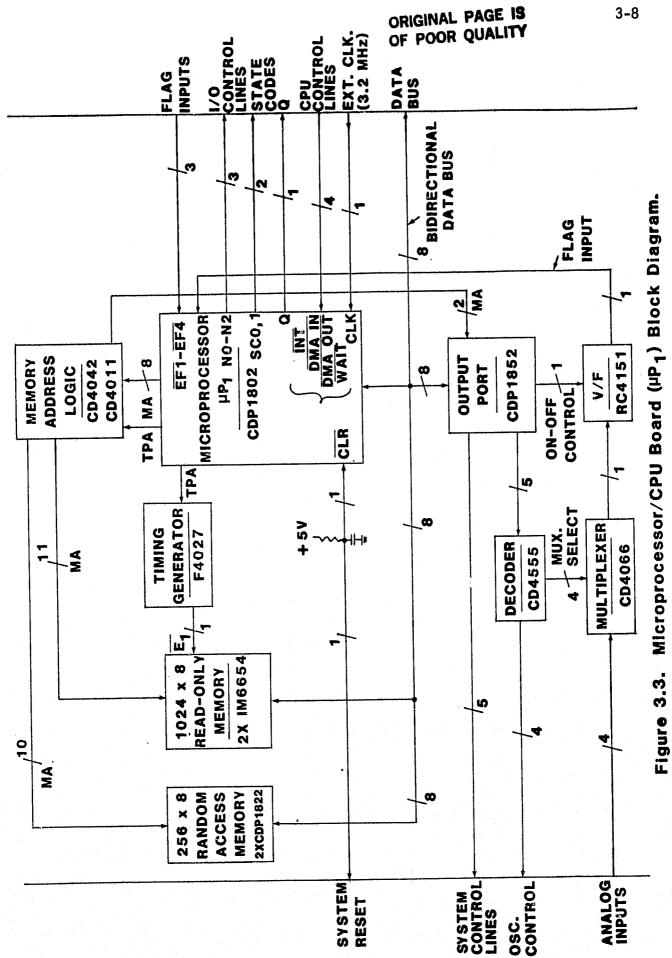

|          | 3.3  | CPU Board - $\mu P_1$                    | 3-7  |

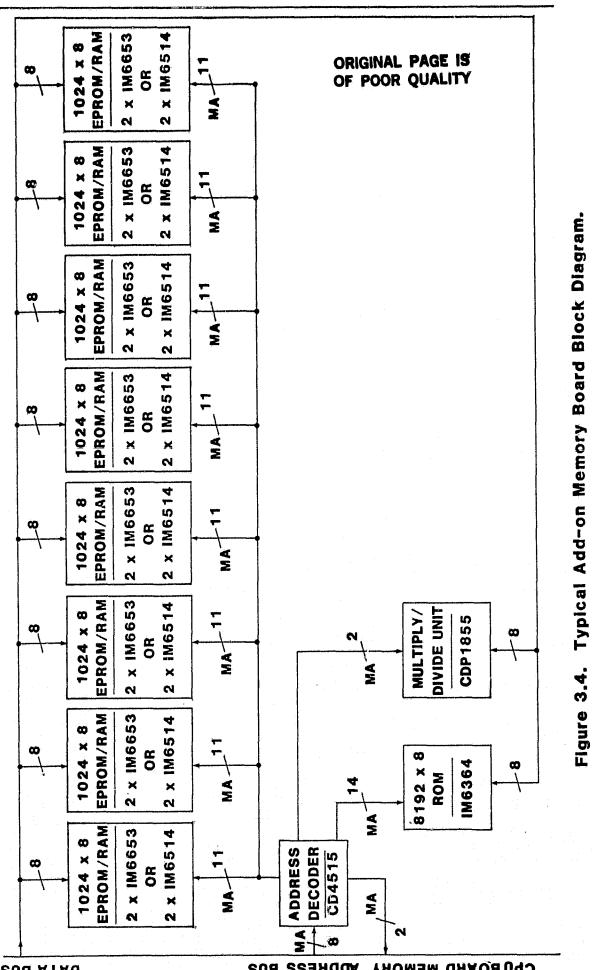

|          | 3.4  | Expansion Memory Board                   |      |

| 4        | RF B | OARD                                     | 4-1  |

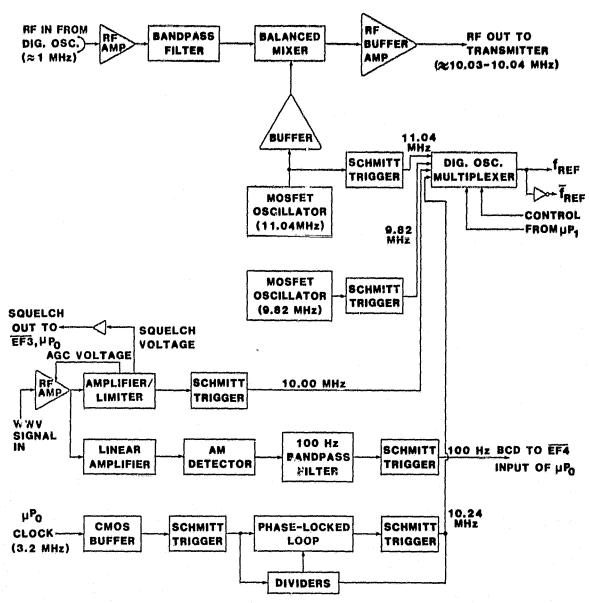

|          | 4.1  | Introduction                             | 4-1  |

|          | 4.2  | RF Filter/Frequency-Translator Chain     | 4-4  |

|          | 4.3  | RF Oscillators                           | 4-6  |

|          | 4.4  | WWV Receiving System                     | 4-12 |

|          | 4.5  | Phase-Locked Oscillator System           | 4-13 |

# CONTENTS (continued)

| SECTION |      |           |                                                        |          |   |   |   |     | PAGE |

|---------|------|-----------|--------------------------------------------------------|----------|---|---|---|-----|------|

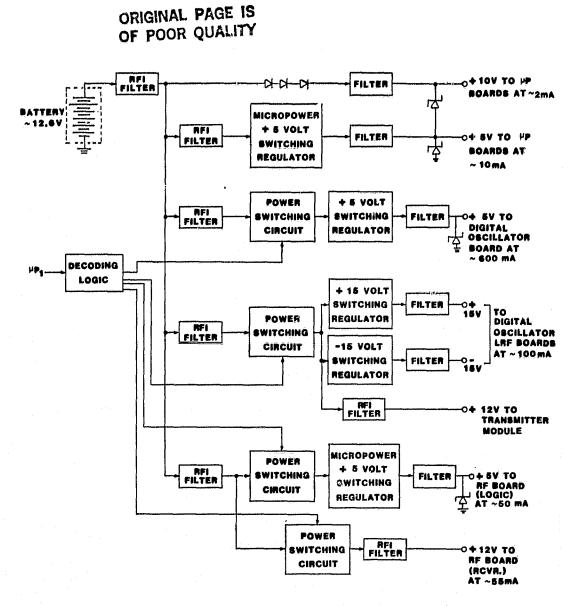

| 5       | POWE | R SUPPLY  | /INTERFACE BOARD                                       | •        | • | ٠ | ٠ | •   | 5-1  |

|         | 5.1  | General   |                                                        | •        | • | • |   | •   | 5-1  |

|         | 5.2  | Power Su  | upplies                                                | •        | • | ٠ | • | •   | 5-1  |

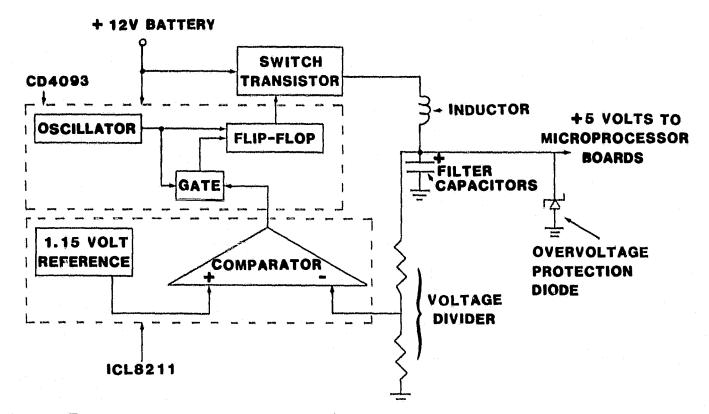

|         |      | 5.2.1 0   | )igital Oscillator Power Supply .                      | •        | • | , | • | •   | 5-2  |

|         |      | 5.2.2     | Dual-Polarity 15-Volt Power<br>Supply and Power Switch | •        | • |   | ٠ | •   | 5-4  |

|         |      | 5.2.3 M   | licroprocessor Power Supplies .                        | •        | • | • | • | •   | 5-5  |

|         |      | 5.2.4 F   | RF Board Power Supplies                                | •        | • | ٠ | • | €.  | 5-7  |

|         | 5.3  | Interfac  | ce Circuits                                            | •        |   | • | • | •   | 5-9  |

|         |      | 5.3.1 5   | Standard DCP Transmitter Interface                     | <u>}</u> |   | £ |   | *   | 5-9  |

|         |      | 5.3.2 1   | Telephone Audio Interface                              | •        | • | • | ٠ | •   | 5-12 |

| 6       | SYST | EM SOFTWA | ARE                                                    | •        | • | ٠ | ٠ | •   | 6-1  |

|         | 6.1  | System F  | Perspective                                            | •        | • | • | • | •   | 6-1  |

|         | 6.2  | Executiv  | ve Control Programs for $\mu P_0$                      | •        | • | ٠ | ٠ | ٠   | 6-2  |

|         |      | 6.2.1 0   | Overview                                               |          | • | ÷ | • | ٠   | 6-2  |

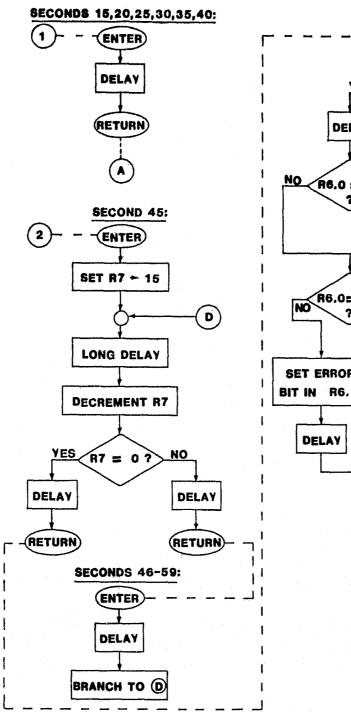

|         |      | 6.2.2 M   | lain/Real-Time Clock Program                           | •        | • | ۲ | • | ٠   | 6-5  |

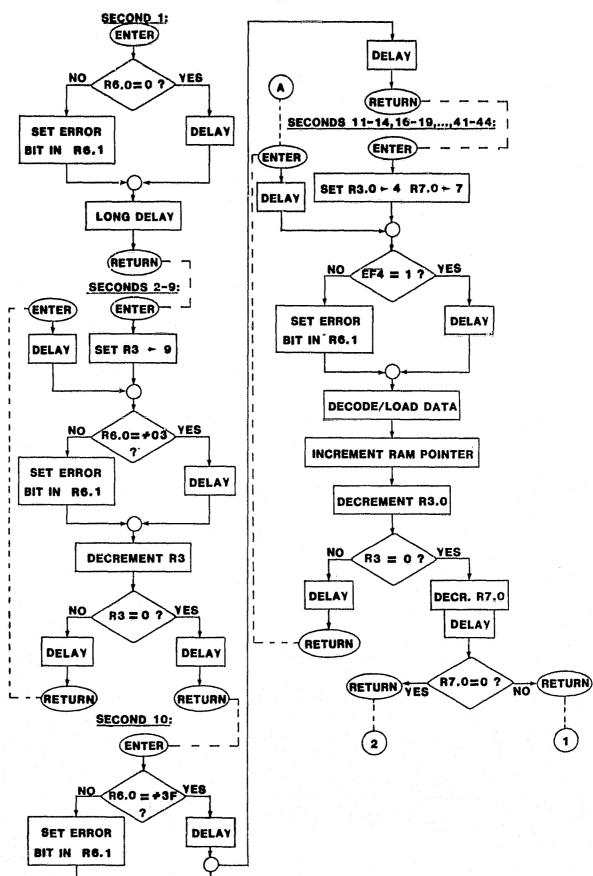

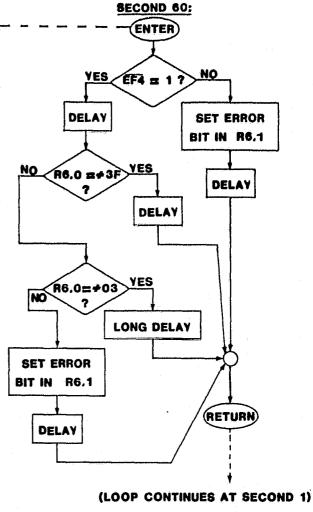

|         |      | 6.2.3 1   | WV Time-Decode Routine                                 | •        | • | • | · | •   | 6-17 |

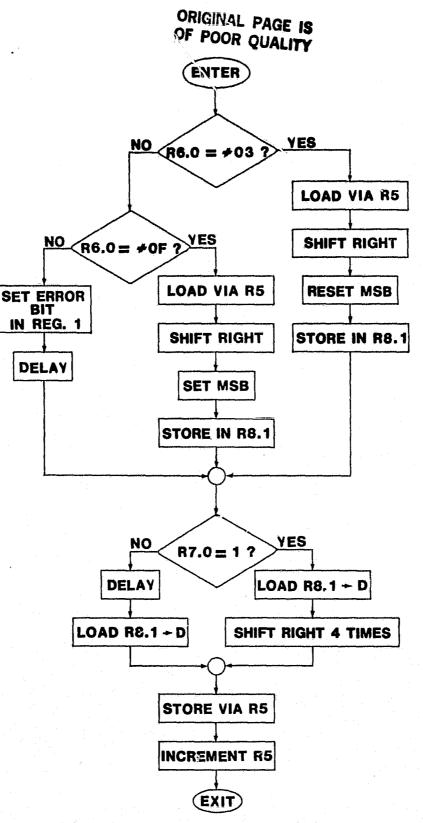

|         |      | 6.2.4 E   | Event Timing/Selection Routine                         | •        | • | • | • | •   | 6-24 |

|         |      | 6.2.5 0   | Overall $\mu P_0$ Software Timing                      | •        | • | • | • | •   | 6-26 |

|         |      | 6.2.6     | System Initialization Program                          | •        | • | ٠ | ٠ | •   | 6-26 |

|         | 6.3  | DATA PRO  | DCESSING/TRANSMITTING ROUTINES FOR                     | <b>γ</b> | P | • | ٠ | ٩   | 6-28 |

|         |      | 6.3.1 0   | Overview                                               | •        | • | ٠ | • | •   | 6-28 |

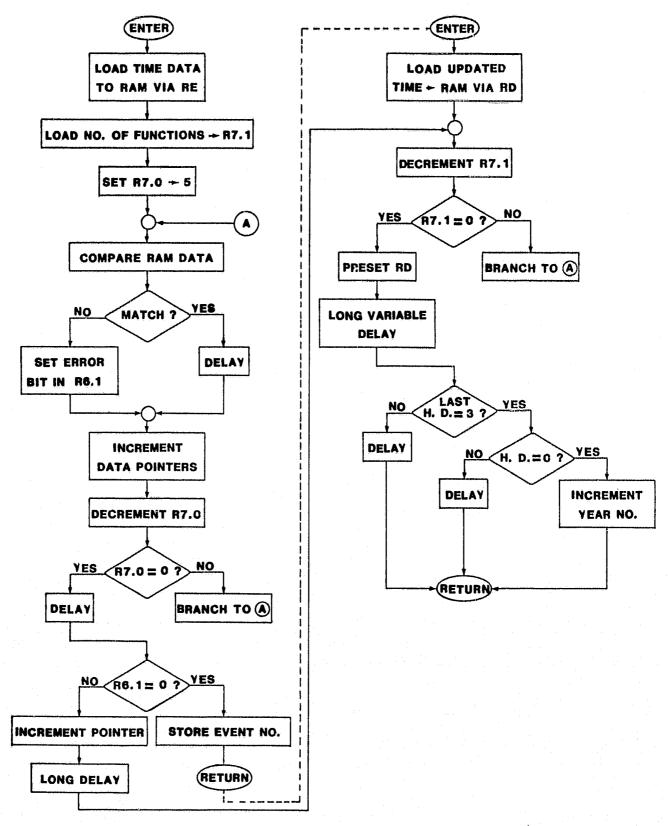

|         |      | 6.3.2 F   | PDCP Transmitting Routines                             |          | • | • | • | ٠   | 6-31 |

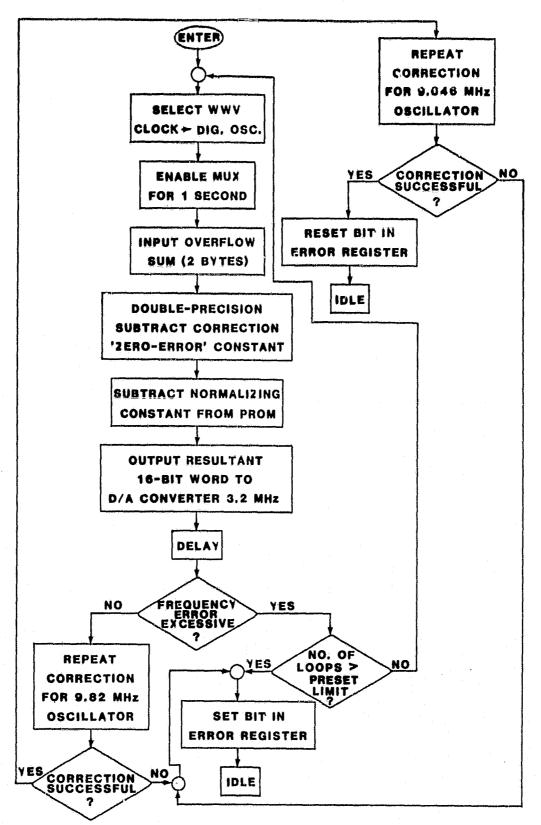

|         |      | 6.3.3 V   | WW Frequency-Correction Software                       |          |   | • |   | • 1 | 6-43 |

## CONTENTS (continued)

| SECTION |      |        |                                                                  |   | PAGE |

|---------|------|--------|------------------------------------------------------------------|---|------|

| 7       | FUTU | RE DCP | TECHNIQUES                                                       | • | 7-1  |

|         | 7.1  | DCP De | sign Trends                                                      | • | 7-1  |

|         | 7.2  | Techno | logical Trends in DCP Design                                     | • | 7-6  |

|         |      | 7.2.1  | Digital Integrated Circuit Technology                            | • | 7-6  |

|         |      | 7.2.2  | Microcomputer Component Technology                               | • | 7-8  |

|         |      | 7.2.3  | Proposed DCP Simplifications                                     | • | 7-10 |

|         |      | 7.2.4  | Proposed New Integrated Circuits for DCP Use                     | • | 7-15 |

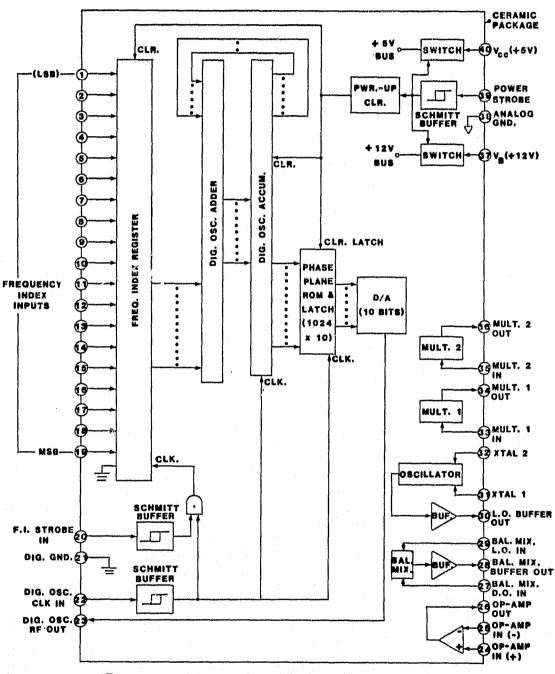

|         |      |        | 7.2.4.1 Digital Oscillator Chip                                  | • | 7-15 |

|         |      |        | 7.2.4.2 Proposed Thermally-Stabilized<br>Crystal Oscillator Chip | • | 7-18 |

|         | 7.3  | Projec | tions on DCP Designs and Uses                                    | • | 7-22 |

|         |      | 7.3.1  | Semiconductor Technology Forecasts                               | • | 7-22 |

|         |      | 7.3.2  | Future DCP Uses                                                  |   | 7-24 |

### LIST OF FIGURES

| FIGURE  |                                                      | PAGE |

|---------|------------------------------------------------------|------|

| 2.2.1   | Basic Digital Oscillator-Block Diagram               | 2+3  |

| 2.2.2   | Enhanced Digital Oscillator System -                 |      |

|         | Block Diagram                                        | 2-8  |

| 2.3.1   | Basic Flow Chart for 1802 MSK/PSK Demonstration      |      |

|         | Program                                              | 2-16 |

| 2.3.2   | Basic Flow Chart for 8080A MSK/PSK Demonstration     |      |

|         | Program                                              | 2-28 |

| 3.2     | Microprocessor CPU Board $(\mu P_0)$ Block Diagram   | 3-6  |

| 3.3     | Microprocessor CPU Board ( $\mu P_1$ ) Block Diagram | 3-8  |

| 3.4     | Typical Add-on Memory Board Block Diagram            | 3-12 |

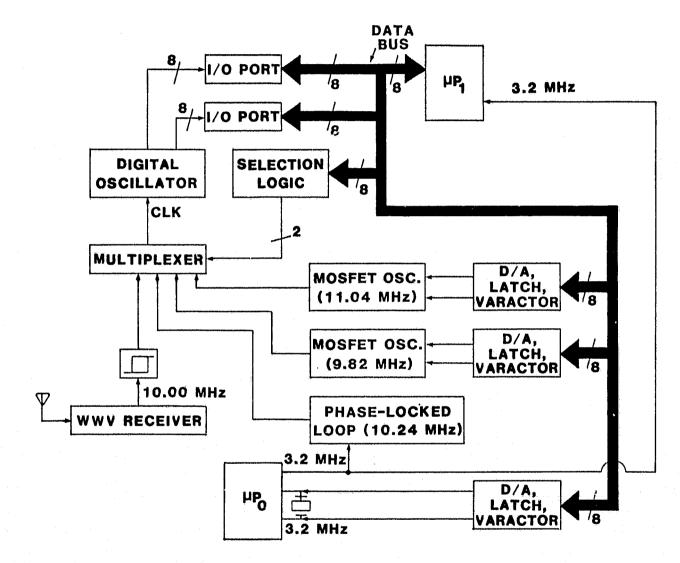

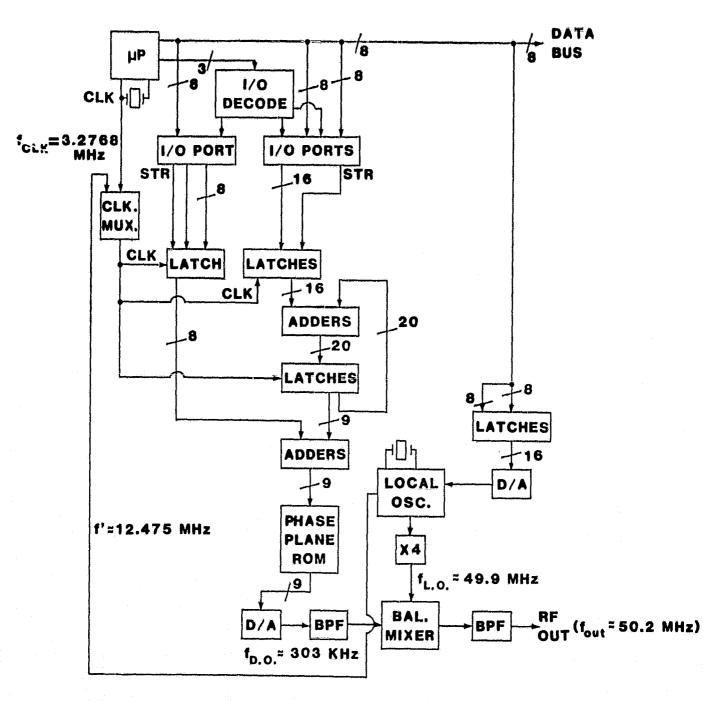

| 4.1     | Block Diagram of RF Board                            | 4-2  |

| 4,3     | Microprocessor-Based Oscillator AFC System           | 4-10 |

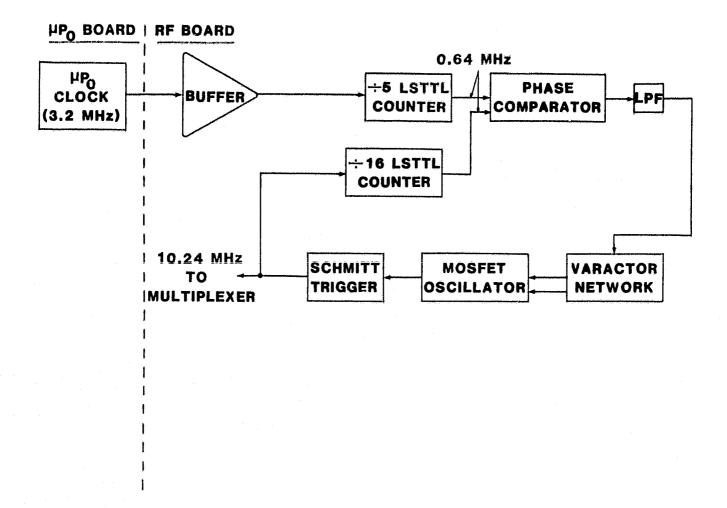

| 4.5     | Block Diagram of Phase-Locked Oscillator System      | 4-15 |

| 5,2     | Block Diagram of Power Supply System                 | 5-3  |

| 5.2.3   | Block Diagram of Micropower +5 Volt Switching        |      |

|         | Regulator                                            | 5-8  |

| 5.3     | Block Diagram of Interface Circuitry                 | 5-10 |

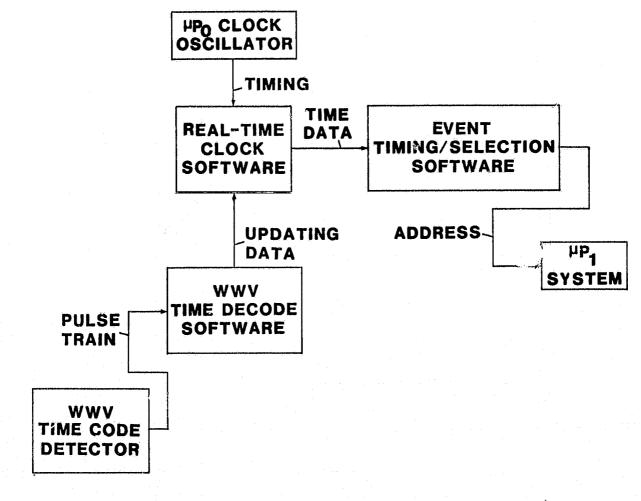

| 6.2.1   | Program Information Flow                             | 6-4  |

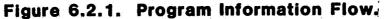

| 6.2.2.1 | Flow Diagram for $\mu P_0$ Main Program/Real-Time    |      |

|         | Clock Routine                                        | 6-8  |

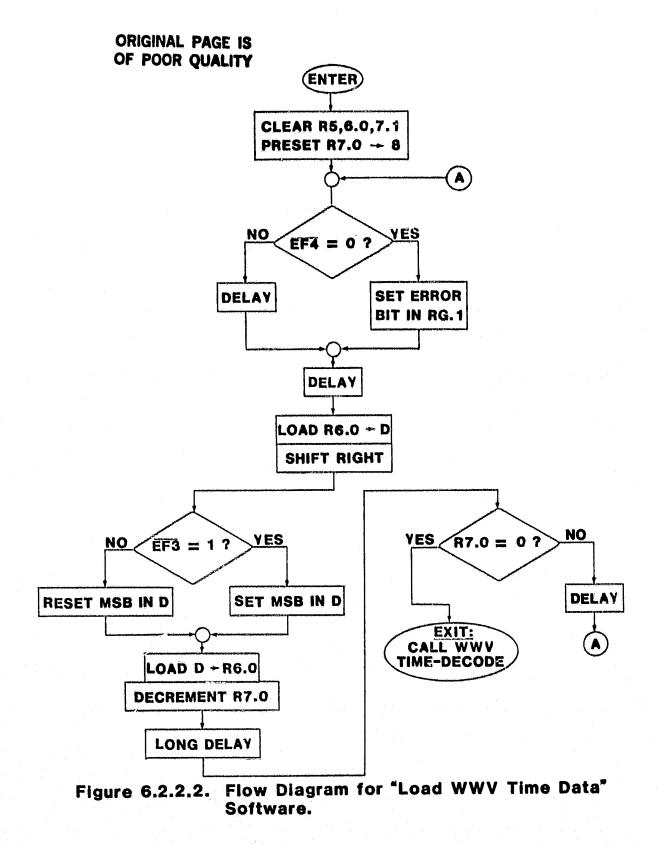

| 6.2.2.2 | Flow Diagram for "Load WWV Time Data" Software .     | 6-9  |

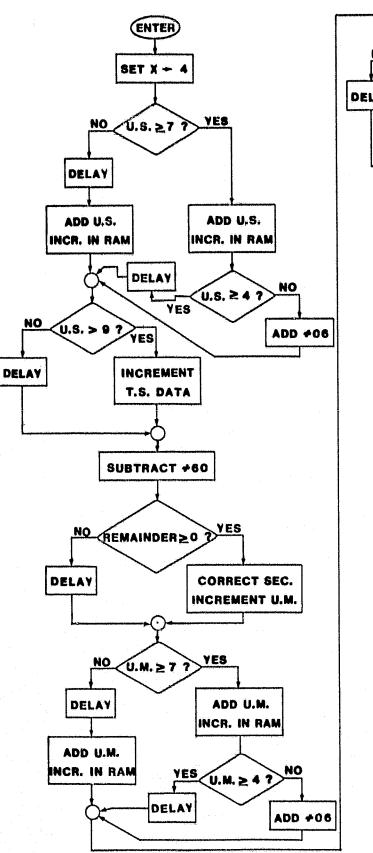

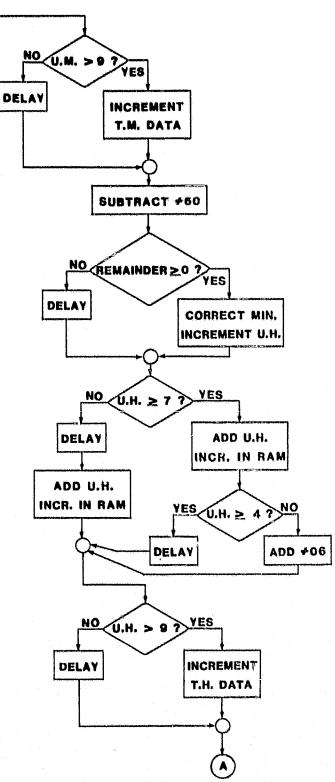

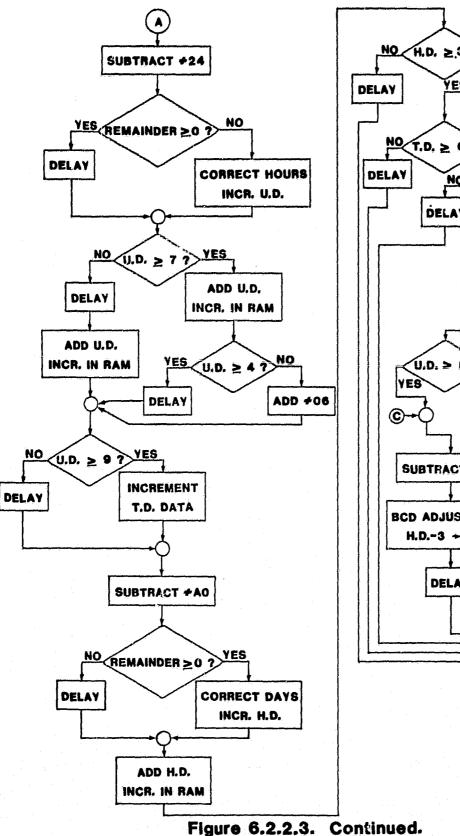

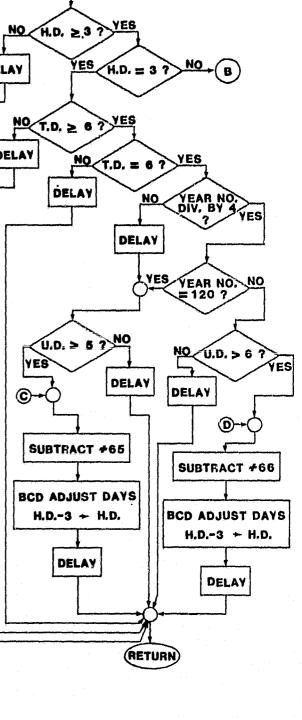

| 6.2.2.3 | Flow Diagram for Time-Update Subroutine              | 6-12 |

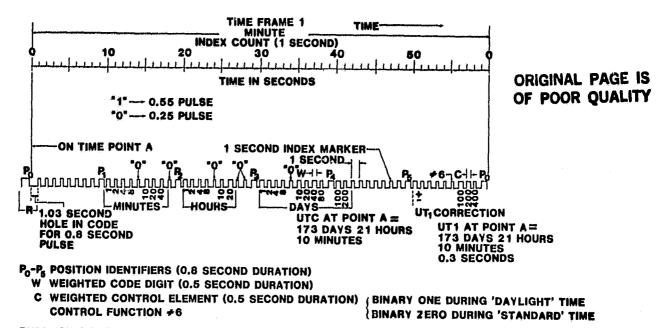

| 6.2.3.1 | Chart of time code transmissions from NBS radio      |      |

|         | stations WWV and WWVH                                | 6-18 |

# LIST OF FIGURES (cont.)

| FIGURE    |                                                 | PAGE |

|-----------|-------------------------------------------------|------|

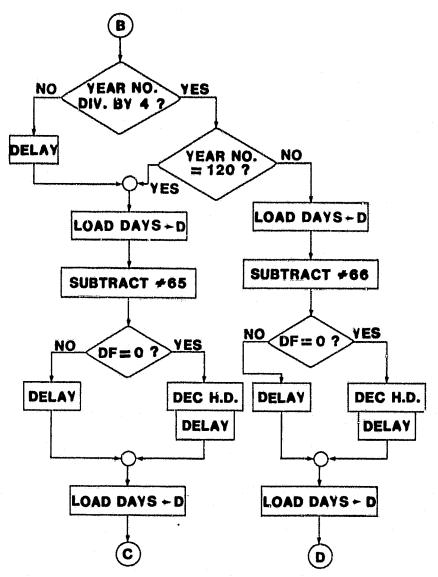

| 6.2.3.2   | Flow Diagram for WWV Time-Decode Program        | 6-20 |

| 6.2.3.3   | Flow Diagram for "Decode/Load Data" Routine     | 6-22 |

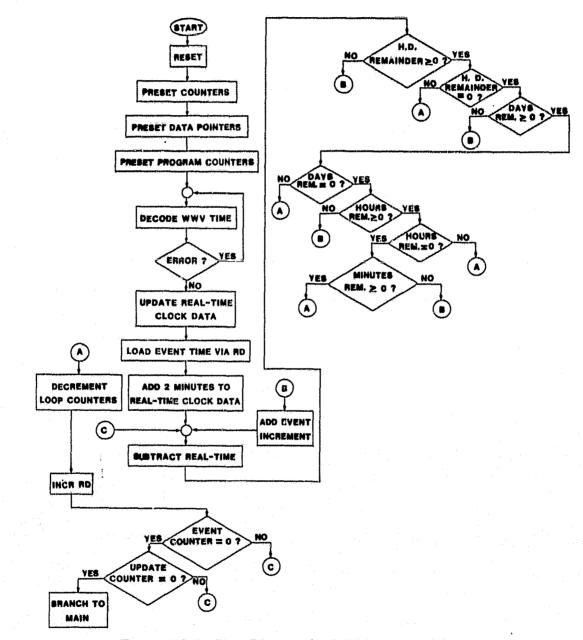

| 6.2.4     | Flow Diagram for Event Timing/Selection Routine | 6-25 |

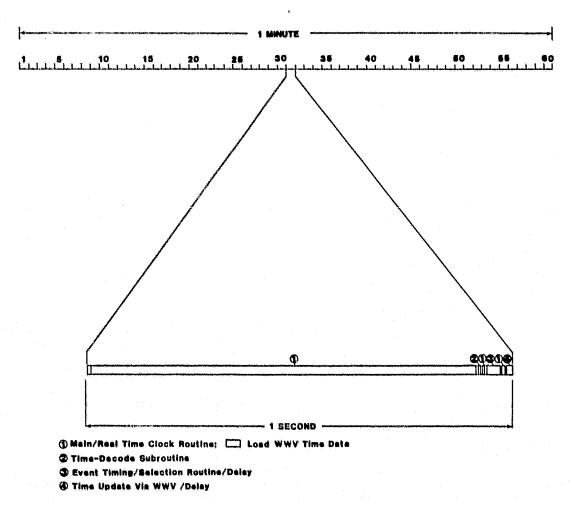

| 6.2.5     | Diagram of Relative $\mu P_0$ Software Timing   | 6-27 |

| 6.2.6     | Flow Diagram for Initialization Program         | 6-29 |

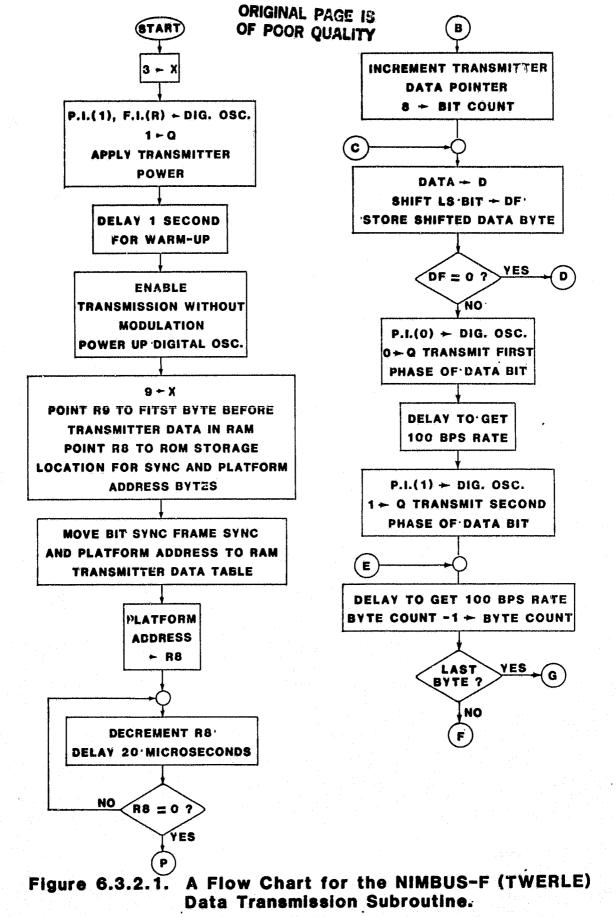

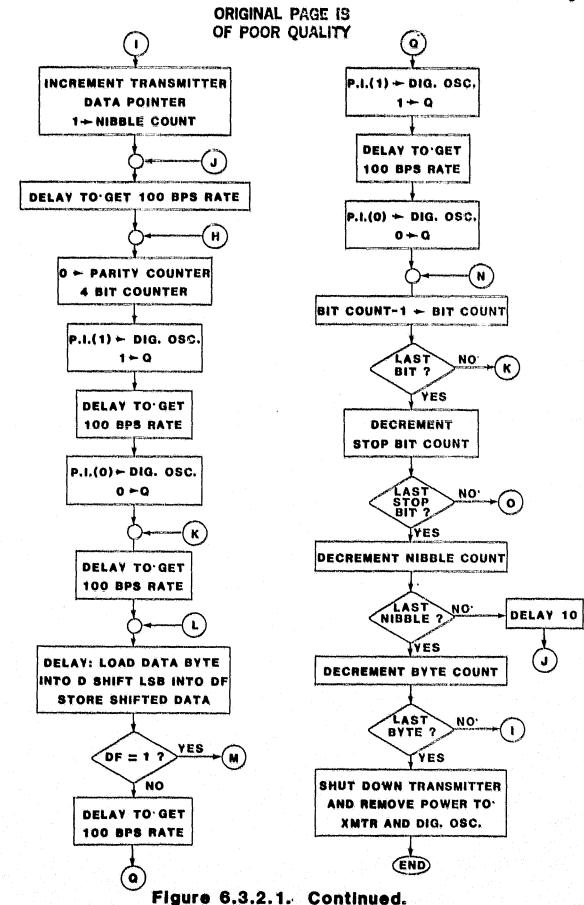

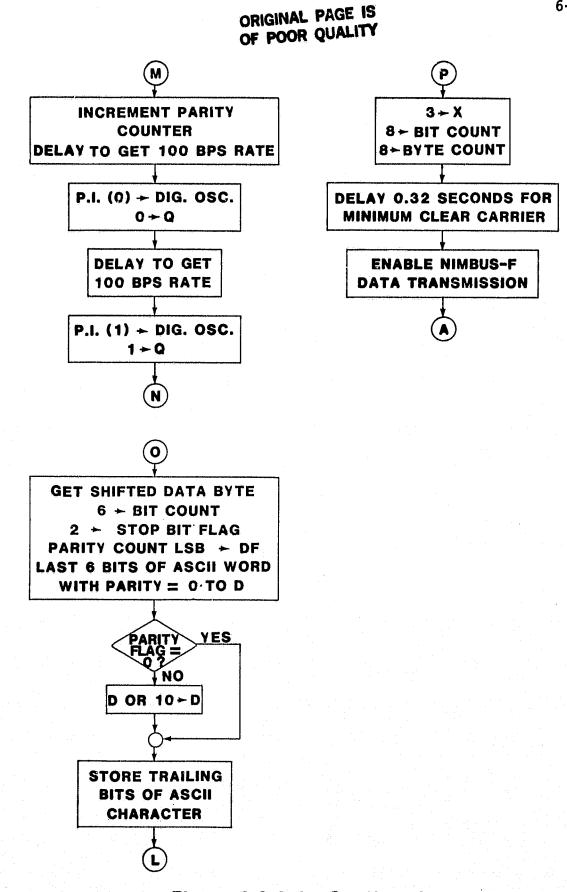

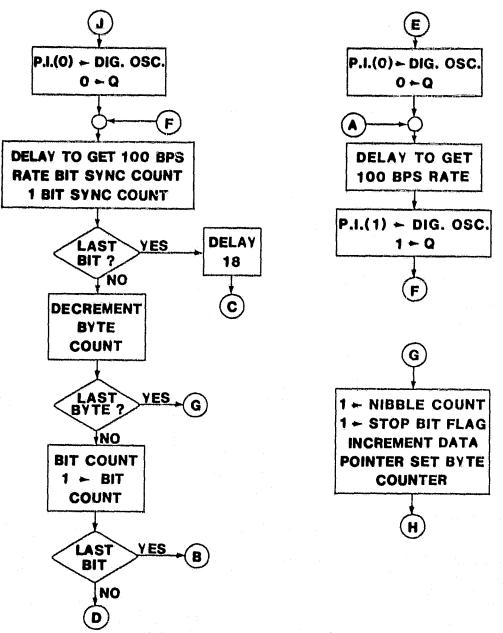

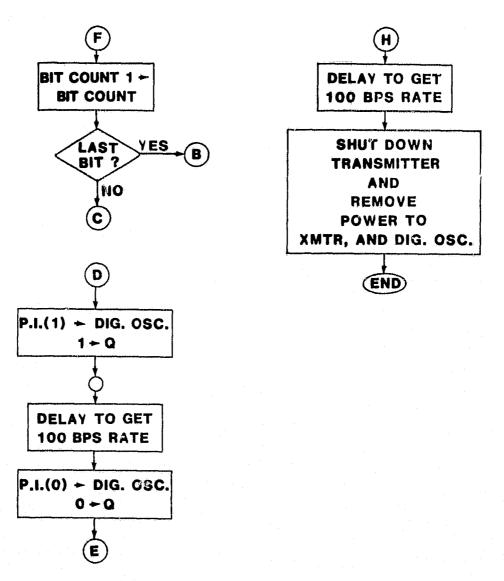

| 6.3.2.1   | A Flow Chart for the NIMBUS-F (TWERLE) Data     |      |

|           | Transmission Subroutine                         | 6-33 |

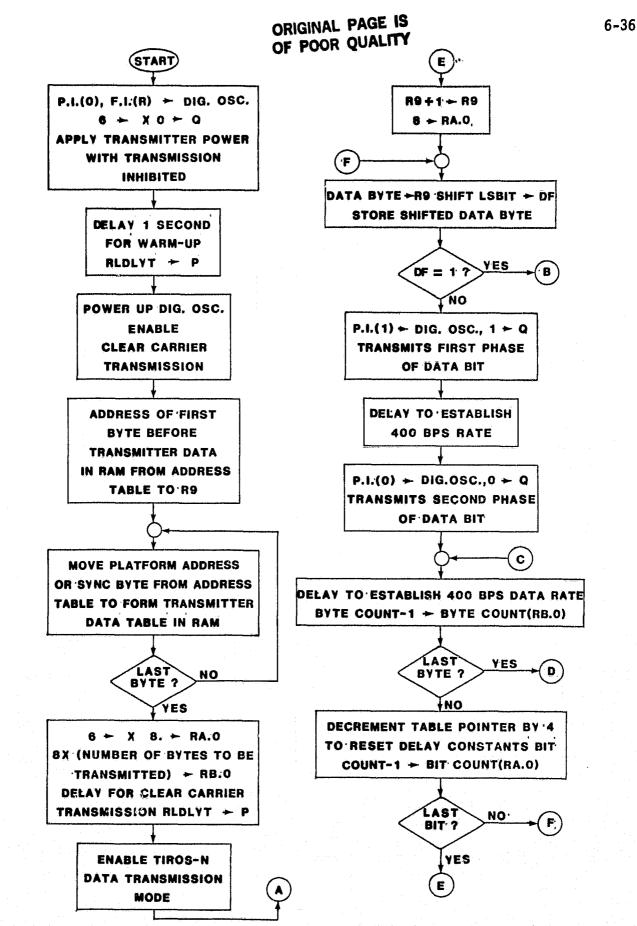

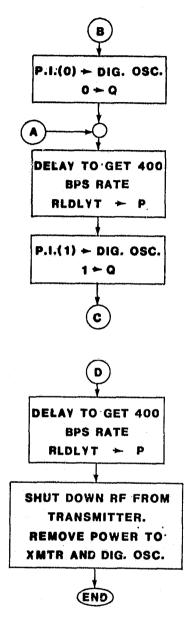

| 6.3.2.2   | A Flow Chart for the TIROS-N Transmission       |      |

|           | Subroutine                                      | 6-37 |

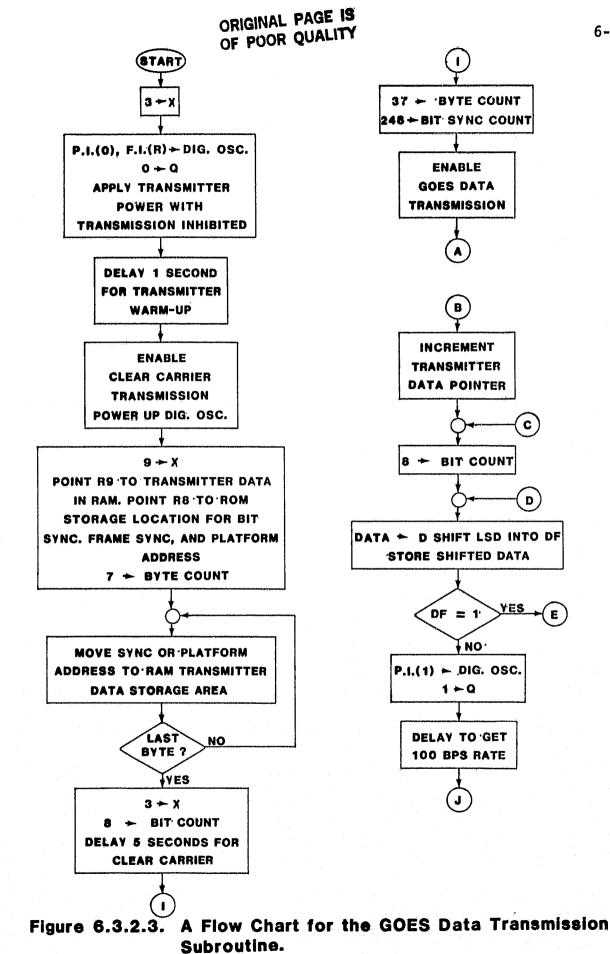

| 6.3.2.3   | A Flow Chart for the GOES Data Transmission     |      |

|           | Subroutine                                      | 6-40 |

| 6.3.3     | Flow Diagram for WWV Frequency-Correction       |      |

|           | Software                                        | 6-45 |

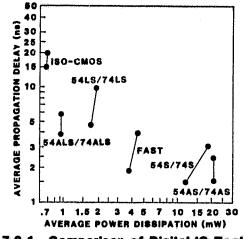

| 7.2.1     | Comparision of Digital IC Technologies          | 7-7  |

| 7.2.3     | Simplified Digital Oscillator System Block      |      |

|           | Diagram                                         | 7-12 |

| 7.2.4.1   | Proposed Digital Oscillator I.C.                | 7-16 |

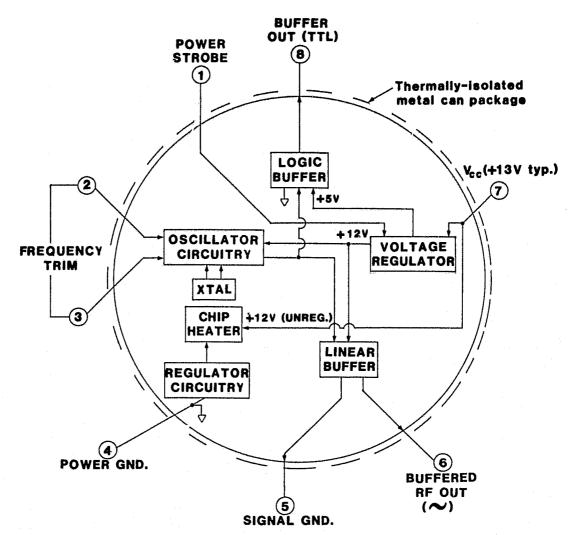

| 7.2,4.2,1 | Block Diagram of Proposed Crystal Oscillator    |      |

|           | Chip , . , . ,                                  | 7-19 |

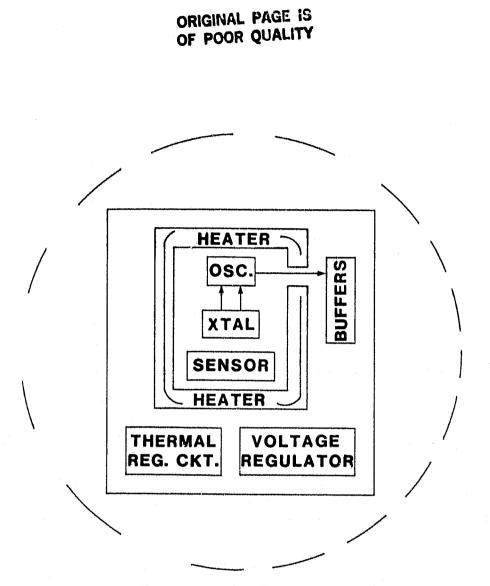

| 7,2,4.2,2 | General Physical Layout of Proposed Chip        | 7-20 |

|           |                                                 |      |

## LIST OF TABLES

| TABLE   |                                                   | PAGE |

|---------|---------------------------------------------------|------|

| 2.3.1   | Microprocessor Speed Comparisons , , , , , , , ,  | 2-13 |

| 2,3,2   | Restart Locations and Parameters for 8080A        |      |

|         | Demonstration Software                            | 2-38 |

| 2.4     | Basic Requirements for PDCP/UM System             | 2-40 |

| 2.4.1.1 | Current Satellite Standards for DCPs              | 2-41 |

| 2.4.1.2 | GOES Satellite Channel Frequencies                | 2-43 |

| 2.4.1.3 | Parameters for Original PDCP/UM Configuration .   | 2-47 |

| 2.4.2.1 | Parameters for Modified PDCP/UM Configuration .   | 2-50 |

| 5.3.1   | Power Supply/Interface Control Function Decoding  | 5-11 |

| 6.2.2   | Register Assignments for $\mu P_0$                | 6-6  |

| 6.3.2.1 | NIMBUS-F (TWERLE) Data Transmission Sequence      |      |

|         | Specifications                                    | 6-32 |

| 6.3.2.2 | TIROS-N Data Transmission Sequence Specifications | 6-36 |

| 6,3.2.3 | GOES Data Transmission Sequence Specifications .  | 6-39 |

| 7.2.3   | Parameters for Simplified Digital Oscillators     |      |

|         | (MSK Mode)                                        | 7-14 |

| 7.3.1   | Status of Semiconductor Technology                | 7-23 |

ix

#### 1. INTRODUCTION

#### 1.1 BACKGROUND AND PURPOSE

The major impetus for this project was the desire of NASA personnel at Goddard Space Flight Center, particularly Mr. J. Earle Painter, to develop a universally applicable data-collection platform (DCP) which would be capable of acquiring various types of analog and digital data, formatting and storing this information, and then through a standard RF transmitter relaying the digital data stream to an overhead satellite for transmission to a central data receiving station[1].

Perhaps the major difficulty in implementing such a universal datacollection system is the considerable variation from satellite to satellite in their requirements for data bit rates, transmission burst lengths, data formats, modulation parameters, modulation types, and final RF frequencies employed in the DCP-to-satellite uplinks. For this reason DCP's have been implemented for specific satellites only; only through substantial hardware and/or crystal changes (normally done at the depot or factory level) could a platform for a specific satellite be converted for use with another [2]. In addition, the DCPs available at present are quite costly for the data-collection end-user to purchase, thus precluding many potential DCP users from getting into the field. As a result, satellites are frequently underutilized and their capacity for public service is curtailed. NASA personnel have therefore greatly encouraged the development of a system which will not only fulfill the operational requirements of a universal DCP but which will be moderate in cost, highly reliable, and simple for the end-user to operate successfully in the field.

The system developed by the Electrical Engineering Department at the University of Tennessee meets these requirements by utilizing the vast flexibility of a microprocessor-controlled DCP developed by U-T for NASA under Contract No. NAS5-22495 [3] and augmenting this concept with several new and cost-effective techniques for modulation and frequency control. The net result should provide unprecedented DCP performance and versatility at quite moderate cost, thus enabling many more agencies and groups to acquire the benefits of NASA's satellite data-collection facilities.

#### 1.2 DESIGN PHILOSOPHY

The specific intent of the project, as designated by the contract title, was to develop a "universal modulator" system which could receive a previously-encoded data bit stream and translate it into the proper RF modulation format and frequency for use with any NASA data-collection satellite either currently in use or to be employed in the foreseeable future. A fundamental property of the universal modulator was that it should accomplish all the desired modulation and frequency-control tasks as much as possible via microprocessor software/firmware and with an absolute minimum of external hardware. The output waveform was to be stored in digital form in a high-speed read-only memory to facilitate generation of the desired output signal by microprocessor control.[4].

An additional requisite for the "universal modulator" approach was that it be compatible with the format of the previously developed U-T PDCP system, in order to retain the technological advantages of that implementation. The universal modulator system was therefore designed to interface with the PDCP setup as directly as possible by use of standard I/O -

port devices controlled by the PDCP microproces. .... The extensive array of U-T software was retained with only minor modifications to accomodate the added control algorithms necessary to handle the universal modulator functions.

The basic U-T software package has been rearranged within the program-storage ROMs in the form of blocks of code which as either primary or secondary subroutines can be called by the main operating program in any combination or order desired by the user. The principal advantage of this concept is that the data-collection end-user is free to select only those data-processing routines which are pertinent to his own project; additionally, he can readily add his own special-purpose routines to those already provided in the general data collection package in order to meet his specific requirements. The main operating program is largely transparent to the user; it is necessary to specify only that portion of the control program which determines the desired sequence of subroutines to be employed in the data collection/data processing task. All platform programs are stored in low-power CMOS EPROM arrays which can readily be erased and reprogrammed if the user's requirements for the DCP change.

In addition to the explicit requirements mentioned previously, there were several other basic factors included in the total system design which had considerable bearing on the final form of the implementation. First, since the vast majority of DCPs are deployed at remote sites which cannot be easily serviced, it is normally necessary to power the units with storage batteries, solar panels, or a combination of the two. It therefore becomes imperative to keep overall DCP power consumption to an absolute minimum if the system is to operate unattended for extended periods of time (e.g., up to a year). The DCP microprocessor system and related components must employ very low-power chips whenever possible, or else perform power management functions to turn off the power except when absolutely necessary to those circuits which have substantial power drains in normal operation (e.g., the RF transmitter). The control microprocessor implements the power-management function by incorporating into the normal sequence of instructions additional program steps which through auxiliary I/O ports turn on and off the various sections of DCP circuitory in a predetermined order to minimize the overall system energy drain while simultaneously providing proper system transmission lengths and intervals.

The second basic area of consideration in the system design procedure was that of economics. The components selected had to be relatively inexpensive; exotic and costly components were to be avoided whenever possible. In the course of component selection for the oscillator circuits it was discovered that although high-quality oscillator modules were available from several vendors, the typical price of three to four hundred dollars each made use of these assemblies economically unfeasible for the DCP systems, especially since the overall system required three of the high-stability oscillators but was to have a final cost of no more than \$1500 to \$2000. Thus it was a simple matter of expense that prompted the decision to develop the WWV dynamic frequency-correction scheme in order to employ much cheaper oscillators which could be satisfactorily corrected to the high degree of accuracy required by the DCP.

A third concern was that of reliability. Obviously, a data-collection system in a remote location must be able to perform unattended for long periods and should be able to do so with little or no periodic or emergency maintenance if it is to be attractive to end-users. The high cost of electronic maintenance precludes placing units which drift or otherwise malfunction and therefore require expensive field service. In addition, conversations with personnel from NASA's National Space Testing Laboratory at Bay St. Louis, Mississippi revealed an undesirably high incidence of currently deployed DCPs which in the course of a few months to a year of unattended service drift out of their assigned frequency bands and into adjacent ones, causing harmful interference to other DCPs on nearby channels. Still other DCPs drift out of their assigned time slots and thereby interfere with other co-channel units. The control scheme employed on the U-T system provides for standard-frequency acquisition from WWV which will enable the system clocks to stay well within tolerances sufficient to guarantee on-channel operation of the DCP; standard NWV time code is also decoded to facilitate proper timing of system functions, typically to better than +15 milliseconds.

The final consideration was that of ease of use; the data-collection customer must be able to program and set up the platform with a minimum of special training and/or effort. To that end, the U-T unit has been designed to be simple to install and, once set up, to be essentially automatic in operation for the life of the power source. Considerable effort has been expended to make the system control features transparent to the user and to ensure that the programming procedure is as straightforward as possible.

For these reasons the U-T DCP system should represent a commercially feasible system of high quality which offers the potential user a higher performance/price ratio than is available currently. It is therefore

hoped that the system can be of substantial benefit to NASA and the public in general by expanding the applications and usefulness of satellite datacollection to many new areas.

#### REFERENCES

- 1. <u>Request for Proposal</u>. NASA-Goddard Space Flight Center, RFP Number 5-45587-254, January, 1977,

- Instruction Manual for the Convertible Data Collection Platform (CDCP) and Related Equipment. LaBarge, Incorporated, Tulsa, Oklahoma, 1976, p. 2-5.

- 3. <u>Programmable Data Collection Platform System</u>, Phase II. University of Tennessee, NASA Contract NAS5-22495, May, 1978.

- 4. Document for Contract NAS5-24250. NASA-Goddard Space Flight Center, Greenbelt, Maryland, July 14, 1977.

#### 2. DIGITAL OSCILLATOR SYSTEM

#### 2.1 SYSTEM CONCEPTS

The basic intent of the digital oscillator concept, first demonstrated for NASA by Texas Instruments, Incorporated, was the synthesis of a digitally-controlled FSK waveform with special characteristics for use in satellite communication systems.[1], In order to more efficiently utilize available RF spectrum space it is always desirable to restrict signal bandwidths, commensurate, obviously, with very low to negligible bit-error rates. Narrow-bandwidth signals, when employing some form of angle modulation such as FSK or PSK, are extremely useful in relatively low signal-to-noise reception conditions such as normally occur in satellite data transmission systems. In addition, these angle-modulated signals are relatively simple to generate, are capable of being amplified without distortion by high-efficiency class-C transmitting stages, and can be efficiently demodulated using such devices as feedback detectors, phase-locked loops, and pulse-counting discriminators. The overall usefulness and superiority of FSK and PSK modulation for digital RF transmission has been well established for many years; indeed, these forms of modulation are the worldwide standards for digital communications via satellite.

Newer, more refined forms of FSK and PSK have emerged as a result of the desire to minimize spectral bandwidth requirements, average bit errors, interference to adjacent communication channels, and transmitter power levels required to overcome channel noise.[2]. Although Manchester-encoded, biphase PSK is currently the most popular modulation scheme in use with satellite data-collection systems, NASA has been keenly interested in the

particular type of FSK known as MSK (minimum-shift keying), which is a special form of CPFSK (continuous-phase frequency-shift keying). CPFSK is notable in that its frequency transitions are generated with continuous-phase zero-crossings; i.e., no discontinuities in phase are allowed to occur. It can be demonstrated mathematically that any fast phase transitions or discontinuities in the RF signal waveform give rise to sideband components of considerable amplitude which lie at integral multiples of the basic data bit rate away from the RF center frequency. If these fast shifts in frequency (and phase) are eliminated, a useful improvement in average occupied signal bandwidth (for a given data bit stream) can be realized; moreover, a substantial reduction in instantaneous peak frequency deviations results. Significantly, it is these occasional wideband bursts which contribute to the majority of bit errors encountered in units receiving on channels adjacent to the one in question. This crosstalk therefore is a significant consideration in the selection of any modulation format which is to be utilized in a tightly-packed frequency-multiplexed system such as a data-collection satellite setup, particularly when the costs of system equipment and the relative economic value of collected data are so high. With narrower effective channel bandwidths, a given satellite transponder is capable of handling more channels of data with the same error rates or else reducing the bit error rates due to crosstalk on the existing number of channels.

#### 2.2 DIGITAL OSCILLATOR THEORY

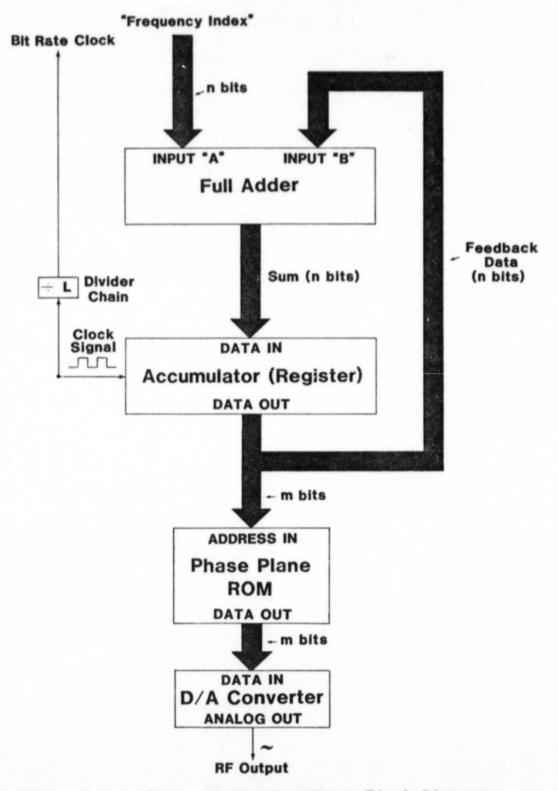

The basic digital oscillator system, as developed by Texas Instruments for NASA, is pictured in block diagram form in Figure 2.2.1.

In the drawing, the heavy lines represent a multi-bit parallel

ORIGINAL PAGE BLACK AND WHITE PHOTOGRAPH

Figure 2.2.1. Basic Digital Oscillator-Block Diagram.

digital data bus; all of the indicated data bus paths are either n bits wide (inputs to the adder and accumulator) or m bits (inputs to the phase plane ROM and D/A converter). As can be seen, the two inputs to the full adder block are n-bit data words which represent the frequency number (into input "A") and the accumulator output (into adder input "B"). The sum of "A" and "B" (without the carry bit) is generated at the adder output and is fed into the accumulator. On each positive transition of the clock signal, the register inputs are transferred to the outputs and thus to the address inputs of the phase plane ROM and back to the "B" inputs of the full adder.

The overall operation of the system is as follows: on command from the system clock, the accumulator gates data from the full adder circuits into its registers. This output digital word then (after progation delays) is presented to the full adder, along with the "frequency index" (F.I.). The adder, after its propagation delays, generates the sum of F.I. and the register output word, which immediately appears at the accumulator inputs. Upon the next system clock pulse, the entire process repeats itself. The net effect of all this is that, assuming an initial count of zero and F.I. equal to one, the register outputs count up from a value of all zeros to a value of all ones. The count increments by one each clock pulse, until with the register output word = 11111 ... 111 the next clock pulse causes the adder result to overflow to 000 ... 000. In this circuit the highest carry (overflow) bit is ignored, and only a certain number of bits are retained. Since the count progresses linearly (with clock pulses) from all zeroes to all ones and then suddenly changes to all zeros, it numerically represents a ramp function with a periodic reset to zero. The length of

time required for one complete cycle of this function is simply the clock period times  $2^n$ , where n is the number of bits (width) of the accumulator. In addition, if F.I. is chosen to be some number of ( $\leq$  n binary bits) other than one, the output period will also change. For instance, if F.I. is set to two (...00010), then the result will increment to all 1's twice as fast (since on each clock pulse the result will increase by two) and thus the output frequency will be double that of the original case. The output frequency ( $f_{OUT}$ ) can therefore be related to the clock frequency ( $f_{CLK}$ ), the frequency index (F.I.), and the register size of n bits by the equation

$$f_{OUT} = \frac{(f_{CLK})(F.I.)}{2^n}$$

, (Eqn.2.2.1)

Thus by varying either n, F.I., or  $f_{CLK}$  one can change the output frequency. The minimum frequency change attainable with the digital oscillator is given by

$$\Delta f_{\min} = \frac{f_{\text{CLK}}}{2^n}, \qquad (\text{Eqn.2.2.2})$$

where  $\Delta f_{min}$  represents the frequency resolution or frequency step size of the system. In a multichannel communications setup,  $\Delta f_{min}$  may be set equal to the desired unipolar CPFSK frequency deviation (or a submultiple thereof) or perhaps equal to the desired interchannel spacing when the digital oscillator is used as a frequency synthesizer. By changing the value of F.I. one may therefore digitally select either the FSK deviation and/or the center channel frequency. The minimum frequency increment, as can be seen from Equation 2.2.2, is directly proportional to the clock frequency but varies inversely with 2<sup>n</sup>, where n is the number of accumulator bits. Thus a higher clock rate produces a higher output frequency and larger step frequency increment, whereas increasing the register width has the opposite effect.

Another constraint of the MSK-generation process is that the data bit transitions must be synchronous with the system clock. This ensures that no glitches or races in the logic will occur, as might happen for a non-synchronous data change; more specifically, the reference clock must be an integral multiple of the effective bit rate frequency in order to produce the desired continuous-phase zero crossings of the final analog output waveform. Also, since MSK has been defined as the special case of CPFSK with the modulation index ( $\beta$ ) of 0.25, the effective unipolar final carrier frequency shift  $|\Delta f|$  must be exactly one-half the bit rate frequency. This condition also places constraints on the following system RF circuitry, as will be discussed later.

There are two other fundamental constraints in the digital oscillator proper which govern its timing. The first is the ratio of the reference clock frequency to the generated output frequency. The higher this ratio is, the finer the level of quantization in time of the output waveform occurs; this determines the effective number of samples per cycle of the output wave. A reasonable level of accuracy is provided when the clock is roughly an order of magnitude higher in frequency than the output; this yields about ten samples per cycle, or one sample every 36° in phase. This waveform in itself is not very "clean", i.e., there is considerable energy near the sample (clock) frequency and its harmonics, but nonmally this undesired energy is removed in a bandpass filter immediately following the output D/A converter.

The second basic limitation is the maximum bit rate. As mentioned previously, the effective bit rate must be exactly an integral submultiple of the clock frequency. Furthermore, since the principal advantage of MSK is its relatively small effective bandwidth, it is reasonable to assume that the effective deviation is quite small compared with the center frequency of interest. Thus, the modulating (bit rate) frequency must also be much less than the carrier frequency. A practical limit for narrowband signal bandwidth is roughly one per cent of carrier frequency, so if the bit rate is set at no greater than one-hundreth of the output frequency for the digital oscillator, the output frequency-modulation index will be <1.0 and the narrowband requirement is thus satisfied.

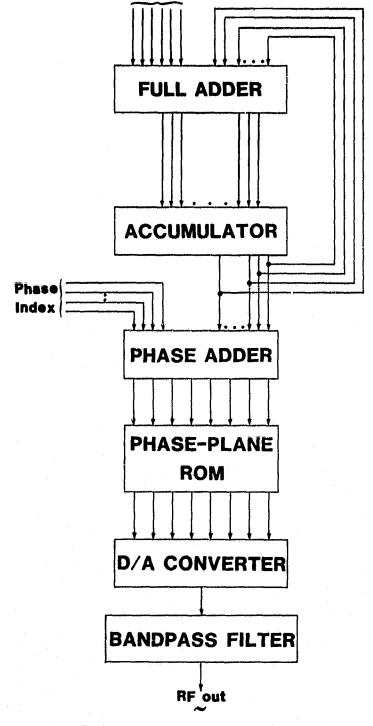

The digital oscillator may also be used indirectly as a phase modulator for digital input signals. This ability of the circuit to generate PSK was developed at The University of Tennessee as part of the effort to minimize the hardware requirements for the "Universal Modulator" system. The circuit is basically an enhancement of the original digital oscillator concept, in which an additional full adder block is inserted between the accumulator output and the address inputs of the phase plane ROM, as shown in Figure 2.2.2. The phase shift is produced by adding a fixed number (designated the "Phase Index", P.I.), to the m highest output bits of the accumulator in accordance with the data bit to be transmitted. The actual value of the P.I. will depend on the desired phase shift needed from the digital oscillator. For instance, if the phase-plane ROM has 256 words, then each phase step will represent  $\frac{360^\circ}{256}$  = 1.40625°. Thus, if a  $\pm$  1 radian phase shift (approx.  $\pm$  56.25°) is desired at the digital oscillator carrier output frequency, then the P.I. would be  $\frac{\pm 56.2500^\circ}{1.40625}$  =  $\pm 40_{\rm D}$ . If the rest phase is arbitrarily assigned a P.I. of zero, then P.I.

**4** ″

Figure 2.2.2. Enhanced Digital Oscillator System-Block Diagram.

would be  $40_D$  ( $28_H$ ) for a data bit 1 and the two's complement of  $40_D$  ( $D8_H$ ) for a data bit 0. When the P.I. is changed, the result is a jump in the phase plane address (by the specified amount) which in turn causes a phase shift in t  $\odot$  analog signal emerging from the D/A converter output. The following bandpass filter removes extraneous high frequency (e.g., clockrate) and low-frequency (e.g., bit-rate) signals from the carrier output to ensure the spectral purity of the transmitted RF signal. The positive P.I. causes the phase of the output waveform to advance, while the two's complement form produces a retarded-phase output, thus producing the desired PSK modulation. The phase deviation may be defined as any integral multiple of  $\pm$  1.40625° up to  $\pm$  180°, simply by specifying the positive and negative (two's complement) values of the P.I.

As with MSK, the digital oscillator configuration experiences certain limitations with respect to the generation of PSK. Due to the digitization of both the output amplitude and phase, there are quantizing errors associated with the output RF waveform. Since amplitude errors are inherently not a significant consideration in angle-modulated communication systems, the use of an 8-bit data word in the phase plane and the resultant 8-bit resolution from the D/A converter presents no real problem to the accurate transmission of digital data. However, the discrete time intervals at which values for the output waveform are defined are significant in determining the ultimate time or phase accuracy of theroutput. Specifically, the zero-crossing points should be very accurate, or else phase jitter will be the apparent result. Appendix I gives a detailed consideration of this effect, which is perhaps the most confining limitation of the digital oscillator concept.

The 8-bit ROM phase plane data essentially represents one complete cycle of a sine wave, with an added dc offset. The offset is added to allow a continuous, unipolar analog signal to be produced by the following D/A converter. Although in some applications it has proven feasible to represent the sinusoid as a single quadrant and employ count-up/count-down addressing and analog output phase-inversion switching to generate an accurate waveform with a smaller ROM requirement, in the digital oscillator setup this leads to several difficulties. First, the phase-switching circuitry can cause timing errors in the critical region around the zeroaxis crossings of the wave. Secondly, with the digital oscillator it is difficult to implement both count-up and count-down functions simultaneously. Therefore it is both more convenient and more accurate (phase-wise) to store the entire cycle. In addition, the algorithm used employs a dynamic range of 255 rather than the full 256 capability of the ROM. The purpose of this is to guarantee a symmetrical range of values for the output wave, thus minimizing the generation of even-order harmonics of the desired RF signal. The actual algorithm is given by

$V(\phi) = [128_{D} + 127_{D} \sin n\alpha]_{H}, \alpha = 1.40625^{\circ}$  (Eqn.2.2.3)

In the formula, V( $\phi$ ) represents the equivalent hexadecimal value, rounded to the nearest whole number, of the bracketed expression. The phase increment  $\alpha$  is simply 360°/2<sup>8</sup>, or  $\frac{360^{\circ}}{256 \text{ steps}}$ ; n is any integral value from 0 to 255, inclusive. The maximum value (corresponding to 90°) is 255; the minimum (at 270°) is one. Note that the values at 0° and 180° are precisely 128, which is the equivalent dc offset; thus the output wave zero-crossings are explicitly specified, thereby reducing the effects of amplitude round-off error on the final phase jitter of the RF output signal.

The digital oscillator system when used as a frequency synthesizer has very good inherent frequency stability (normally same as the clockfrequency source); the integrated phase jitter over a long period is zero, since the average value of the jitter error signal is zero. As seen from Eqn. 2.2.2, the size of the minimum frequency step is dependent solely on  $f_{CLK}$  and the overflow value of the accumulator, namely  $2^n$ . The relationship between the attainable frequency resolution  $\Delta f_{min}$  and the number of parallel accumulator bits n is given by

$$\Delta f_{\min} \propto 2^{-n}$$

(Eqn. 2,2.4)

It can thus be seen that there is a fixed relationship between bit rate, resolution, and accumulator width.

The essential design equations for the digital oscillator system are powerful tools for the analysis of system performance and facilitate the necessary trade-off studies of attainable bit rates, output frequencies, deviations, and phase performance. The analysis in Appendix I relates system phase jitter and frequency resolution to the basic system parameters and provides an index of system performance for a wide variety of hardware and/or software configurations.

#### 2.3 SOFTWARE IMPLEMENTATIONS

The basic digital oscillator scheme previously described can also be implemented via software programs in a standard microprocessor. In fact, the technique utilized in the digital oscillator could be useful in a wide variety of frequency-synthesis and waveform-generation applications.

The only major limitation of the method when used in microprocessor-based systems is the ultimate output frequency attainable, and that in turn is dependent upon the instruction cycle time of the particular machine under consideration.

As an example, the digital oscillator system, including the phase plane, was implemented in software for an 1802-based microcomputer system to determine the feasibility at this point in time for direct software implementation of the MSK/PSK generation technique. The basic program loop consists of a 16-bit add cycle (which is comprised of one 8-bit straight addition and one 8-bit add with carry) and a simple 8-bit add instruction. The 16-bit add routine takes the desired Frequency Index and adds it to the 16-bit number stored in the accumulating register. The second add utilizes the high-order 8 bit portion of the accumulator and adds to it the 8-bit Phase Index. The sum of this operation, neglecting the carry bit, is then used to address the previously-stored phase plane data; this data is then outputted to a D/A converter which produces the actual MSK/PSK modulated carrier.

This basic program was written for several types of microprocessors to ascertain the maximum output frequencies available. Bit-slice units were considered, as was a 16-bit NMOS unit, and the various speeds and power dissipations compared. The condensed results are found in Table 2.3.1. Included for comparison purposes are the parameters for various hardware-type implementations with the standard 16-bit accumulator width. The test conditions assume a standard +5V supply for the LSTTL,  $I^2L$ , and NMOS chips and a V<sub>DD</sub> supply of +10V for the CMOS units. It is also assumed that  $f_{CLK} \approx 10f_{OUT} \approx 1000 f_{BR}$ .

| ٠    |

|------|

|      |

| ຕ່   |

| 2    |

|      |

| a    |

| D.   |

| , ro |

|      |

Microprocessor Speed Comparisons

| APPROX.<br>MAX.<br>BIT RATE        | 1500Hz                   | J5kHz              | бкнг                 | <b>JOKHz</b>        | 2kHz                | 140Hz            | 20Hz          |

|------------------------------------|--------------------------|--------------------|----------------------|---------------------|---------------------|------------------|---------------|

| APPROX.<br>MAX.<br>fout            | 150kHz                   | 1.5MHz             | 600kHz               | 1.0MHz              | 200kHz              | 14kHz            | 2kHz          |

| APPROX.<br>MAX. ADD<br>RATE (fcik) | 1.5MHz                   | 1 SMHz             | 6MHz                 | ZHMOL               | 2MHz                | 140kHz           | 20kHz         |

| APPROX.<br>POWER<br>DISSIPATION    | 225mW                    | 800mW              | 4.0W                 | 6.0W                | 800mW               | 500mW            | 20mM          |

| CHIP<br>NOS.                       | 45181<br>45182<br>74C174 | 74LS283<br>74LS174 | 2902<br>2902<br>2909 | 10800               | SBP0400A<br>SBP401  | 0066             | 1802          |

| CHIP<br>TYPES                      | Adders/Registers         | Adders/Registers   | Bit-slice µP         | 4-Bit-slice $\mu P$ | 4-Bit-slice $\mu P$ | 16-bit $\mu^{p}$ | $8-bit \mu^p$ |

| LOGIC<br>TYPE                      | CMOS                     | LSTTL              | <b>LSTTL</b>         | ECL                 | 1 <sup>2</sup> L    | SOMN             | CMOS          |

From the results in Table 2.3.1 it is evident that in general, except for the bipolar units, the microprocessors are much too slow to produce the desired 300kHz-1MHz carrier output frequency. Since in currently operational satellite DCP systems (e.g., LANDSAT) the bit rate may be as high as 5kHz, the bipolar bit-slice units are sufficiently fast but will in operation consume roughly as much power as the entire RF transmitter assembly. Obviously, this is unsatisfactory for battery-powered systems since this fact alone would double the required battery capacity for the DCP system. Thus at this juncture, the LSTTL hardware approach offers the most useful balance between power consumption and speed for implementation of the complete digital oscillator system.

Nevertheless, for demonstration purposes, digital oscillator simulation programs have been written for the 1802 and the 8080A microprocessors. These programs take a prestored array of data bits, convert them to a serial data stream, and then (by means of changing the "Frequency Index" number) alter the output frequency being sent from an 8-bit parallel port which is then translated to a continuous audio-frequency sinusoid by a final D/A converter.

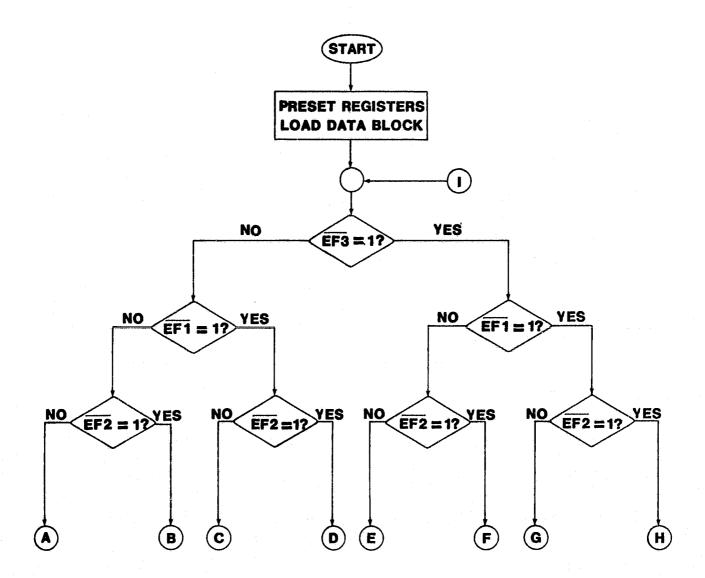

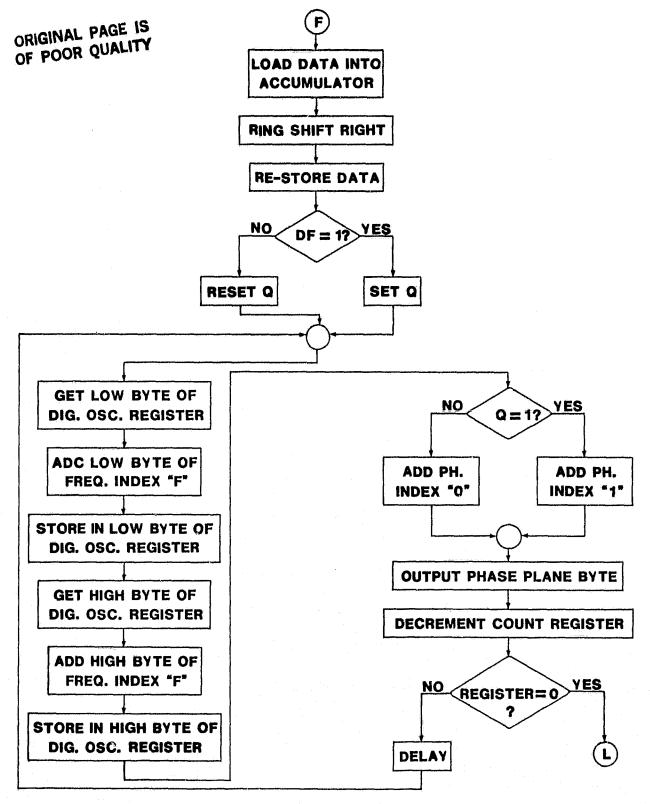

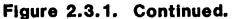

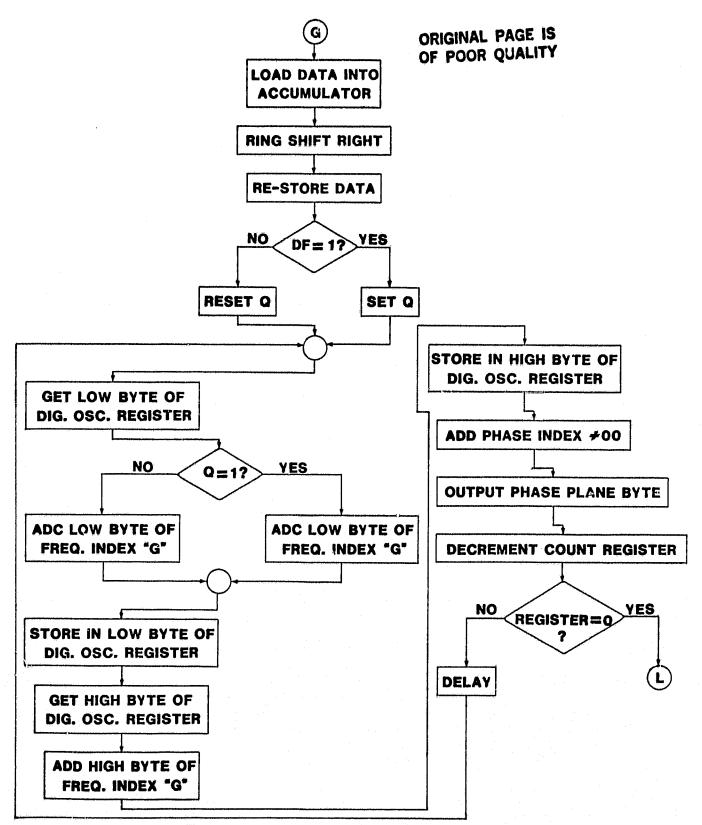

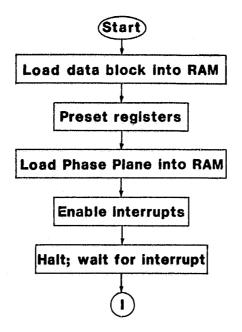

#### 2.3.1 Demonstration Software for 1802

The 1802 demonstration program utilizes the register-oriented structure of the machine to efficiently address the prestored Frequency Index number, use it with the 16-bit accumulated value to perform the digital oscillator-type add function, and then perform the appropriate 8-bit phase-control addition. This result is then used to address a byte in the phase-plane array stored in RAM; the byte is then loaded into an output port which feeds the D/A converter. The basic flow diagram for the 1802 demonstration program is shown in Fig. 2.3.1.

The flag inputs EFT, EF2, and EF3 are used by the program to determine the desired modulation parameters. Flag EFT selects the modulation type (PSK or MSK); flag EF2 determines when the carrier is modulated by the data stream; and EF3 is sampled in order to determine the output center frequency, to simulate how a microprocessor under software or firmware control could select different transmitting channels. The digital output is converted to a nearly sinusoidal wave by the action of the phase plane and D/A converter and its associated bandpass filter. The output audiofrequency signal is monitored through a small loudspeaker. The technique allows the nontechnical personnel witnessing the demonstration to readily perceive the effects of frequency shift, sideband structure, and bit rates on the MSK and PSK signals. In addition, this audio tone (roughly 600-700Hz) may be recorded on a standard cassette or transmitted via telephone for dissemination of these modulation techniques to a wide range of satellite data-collection system users and potential users.

The first major task of the demonstration program, after register initialization and data storage, is to sample the three external flag  $(\overline{\rm EF})$  inputs to determine which set of modulation conditions is desired by the operator. The flag decoding routine shown at the top of Figure 2.3.1. sequentially determines the flag states and then branches to one of eight subroutines, A through H, according to the frequency, operation, and modulation type desired. The MSK function is implemented as CPFSK with a modulation index of exactly 0.25; the PSK is synthesized by causing a jump of  $\pm 60.47^{\circ}$  ( $\pm 43$  steps) in the phase plane. The effects of the two modulation forms are easily detected by ear and serve to underscore the

### ORIGINAL PAGE IS OF POOR QUALITY

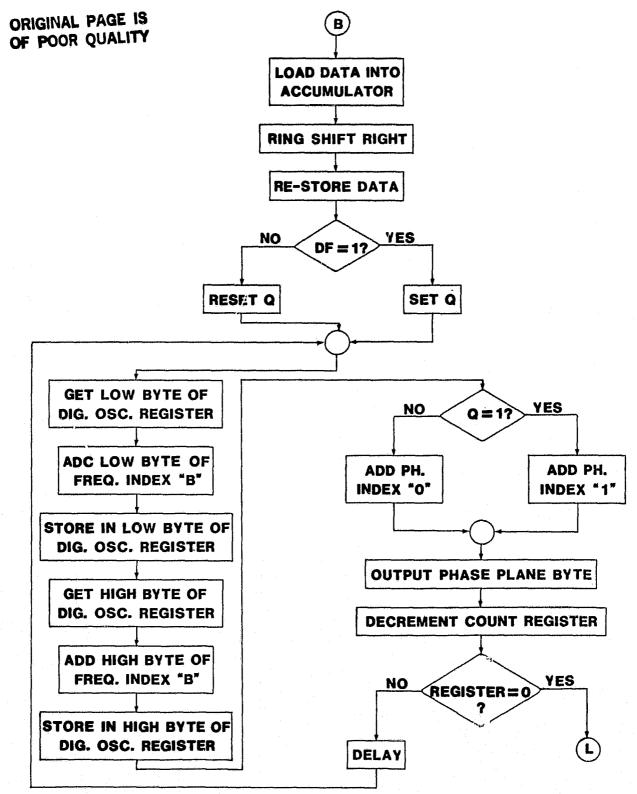

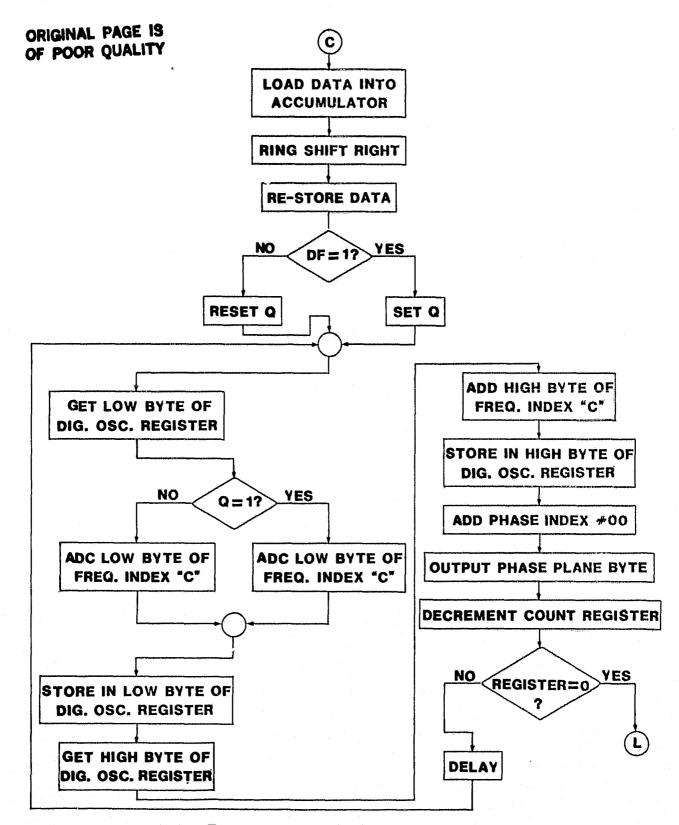

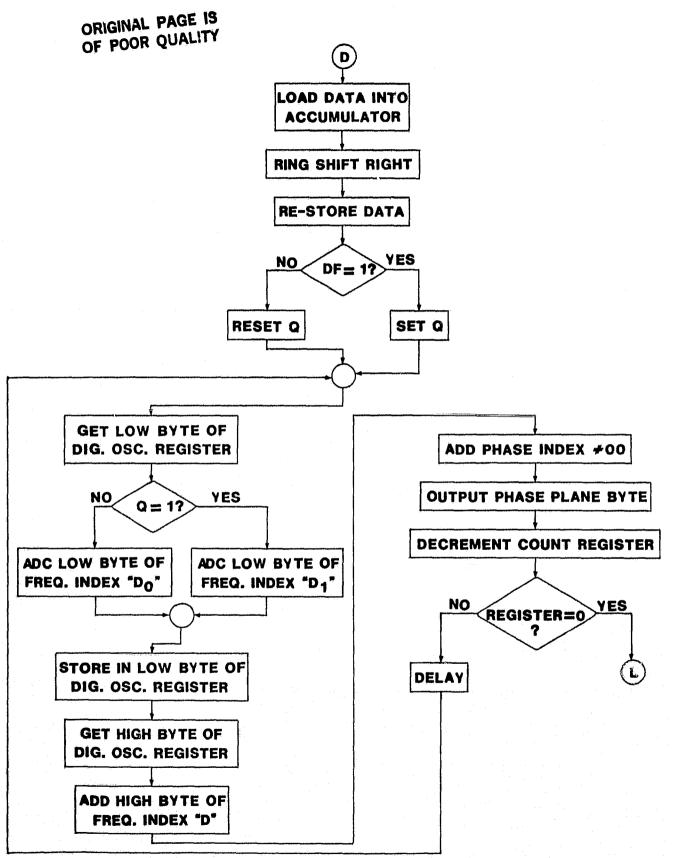

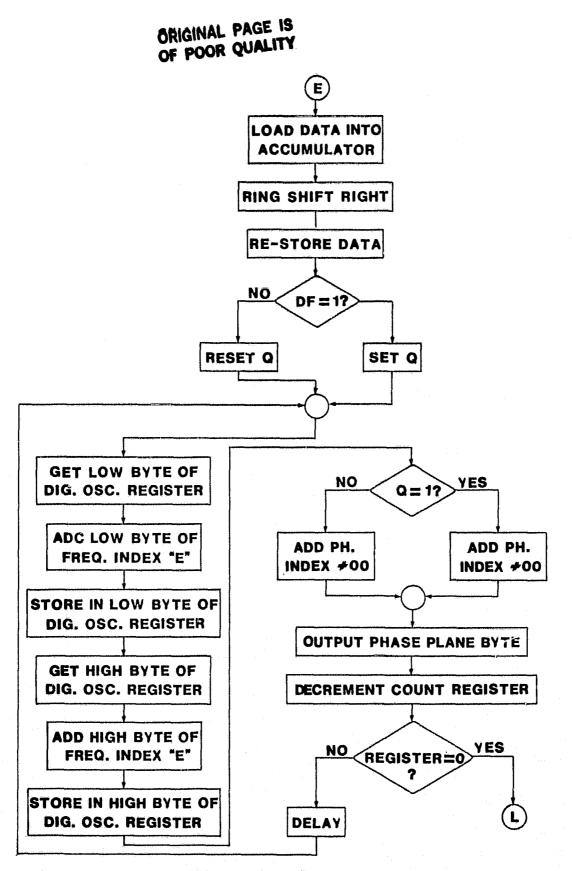

Figure 2.3.1. Basic Flow Chart for 1802 MSK/PSK Demonstration Program.

Figure 2.3.1. Continued.

Figure 2.3.1, Continued.

Figure 2.3.1. Continued.

Figure 2.3.1. Continued.

Figure 2.3.1. Continued.

## Figure 2.3.1. Continued.

Figure 2.3.1. Continued.

Ś.

Figure 2.3.1. Continued.

fundamental bandwidth superiority of MSK over PSK for a given bit rate.

The total digital oscillator subroutine loop requires 60 machine cycles, or 150 $\mu$ S; this results in an effective f<sub>CLK</sub> of 6.667kHz for the 16-bit wide simulated digital oscillator. The output carrier frequency is roughly one decade lower, or 665Hz. The output frequency is determined by the position of the  $\overline{EF3}$  switch (f<sub>L0</sub>/f<sub>HI</sub> select) and the  $\overline{EF2}$  width (rest/operate select); in the "operate" mode the EF3 function selects a "low" (approx. 651 Hz) or "high" (682Hz) carrier frequency. Furthermore, in the MSK mode the output frequency is shifted with continuous phase to a higher or lower value, depending on the data bit just read from the data block in RAM. The MSK deviation number represents 64 steps in frequency; 1024 add cycles of the digital oscillator function occur per data bit period. All frequency-and phase-control loops (A through H) are timed to cause synchronous transitions of data and oscillator clock signals to ensure that all transitions are continuous-phase and glitch-free. The Q flip-flop output from the microprocessor is available for monitoring the actual data bit train, although its transitions are slightly advanced in time compared with the changes in phase-plane output bytes.

As can be seen from Figure 2.3.1, subroutines A through H are each very similar in format. The only differences are in the actual values of Frequency Index and Phase Index numbers entered in each case. Also, routines A, B, E, and F switch the Phase Index according to the data bit value and thereby generate PSK; analogously, routines C, D, G, and H vary the Frequency Index according to the data bit and thus create MSK modulation.

In the main program, RO is the program counter; R6 serves as the digital oscillator clock loop counter. The data block pointer is R7; R8

is used as the 16-bit digital oscillator accumulator; and R9 is the phase plane pointer [3],

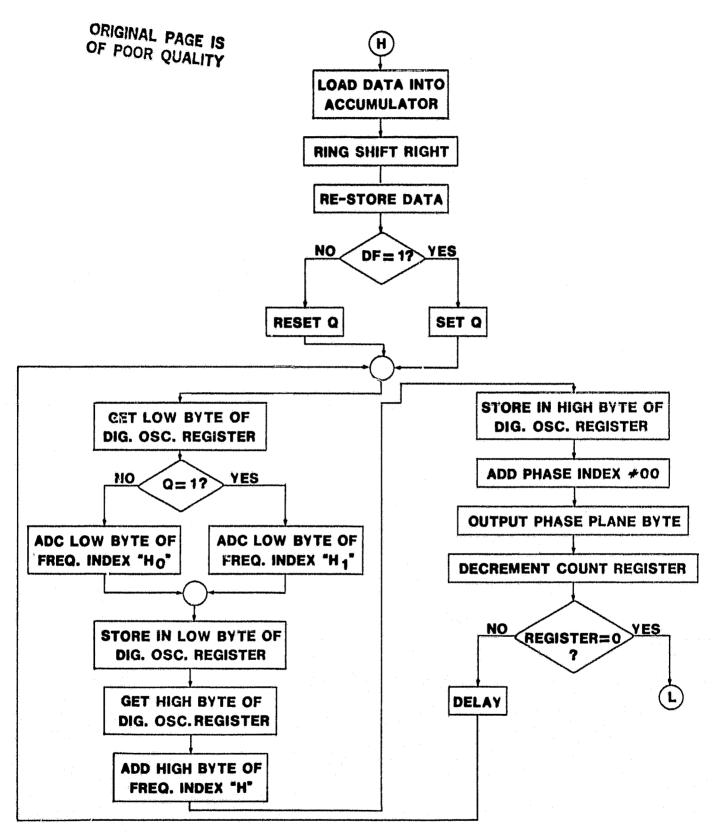

### 2.3.2. Demonstration Software for 8080A

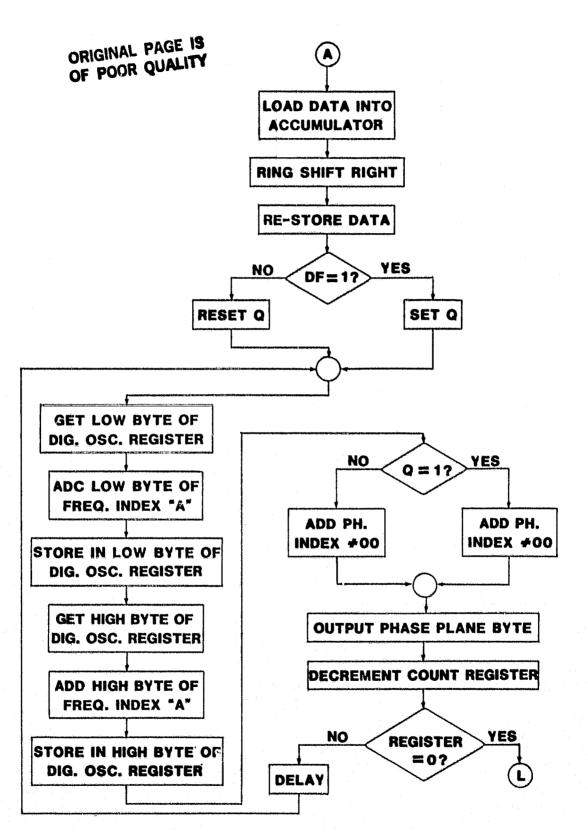

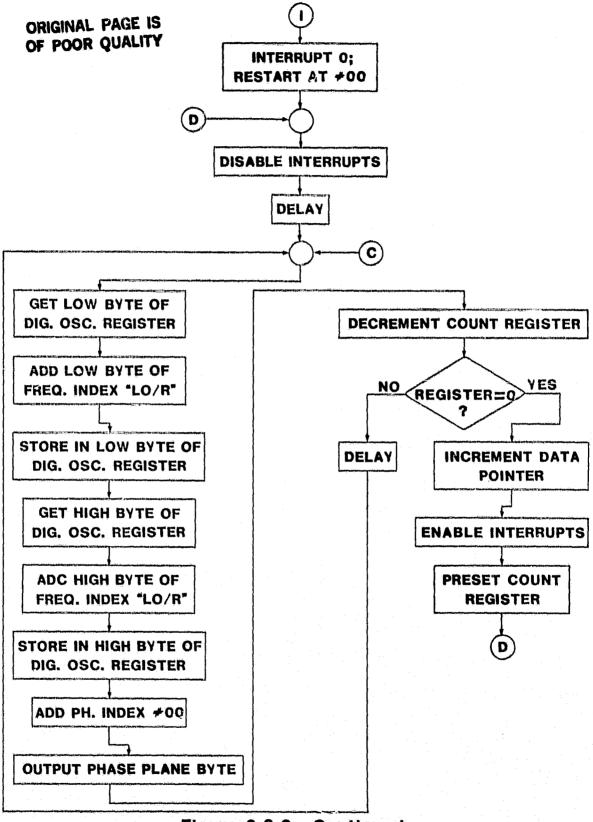

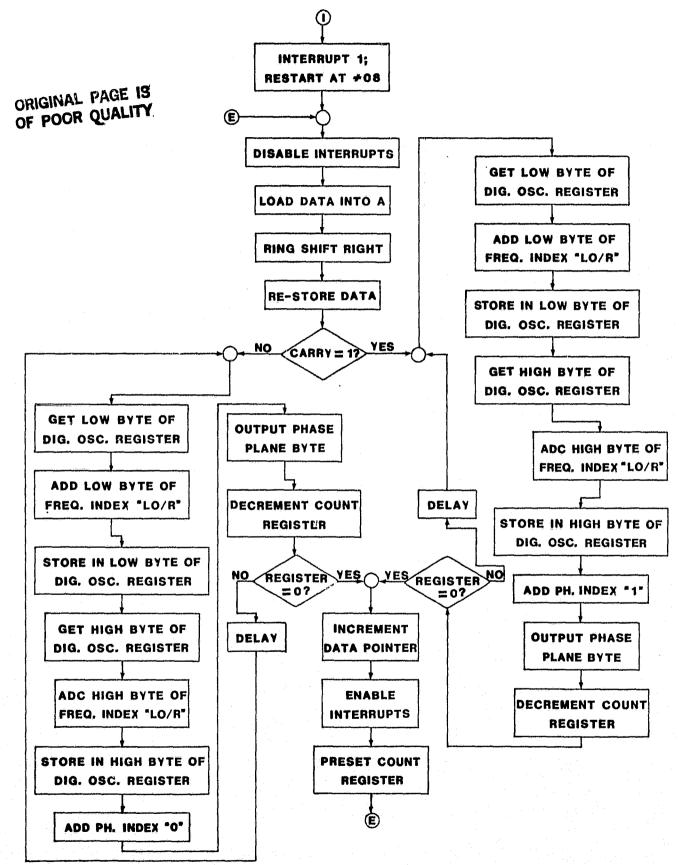

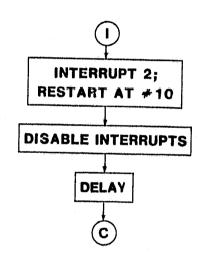

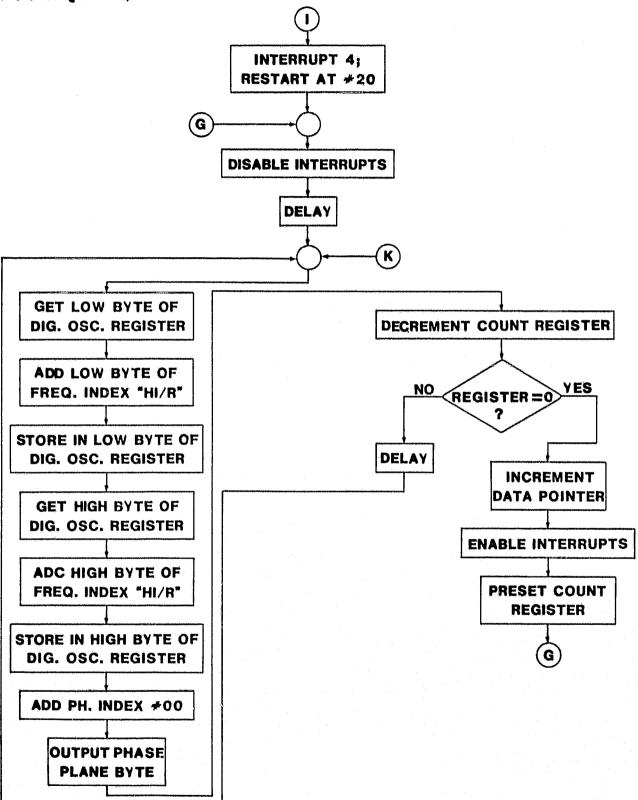

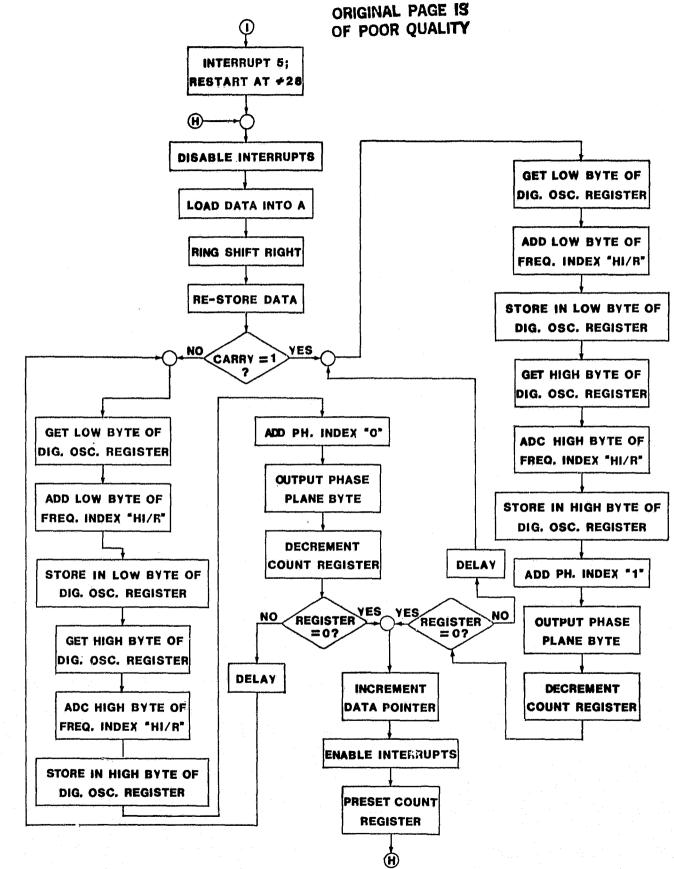

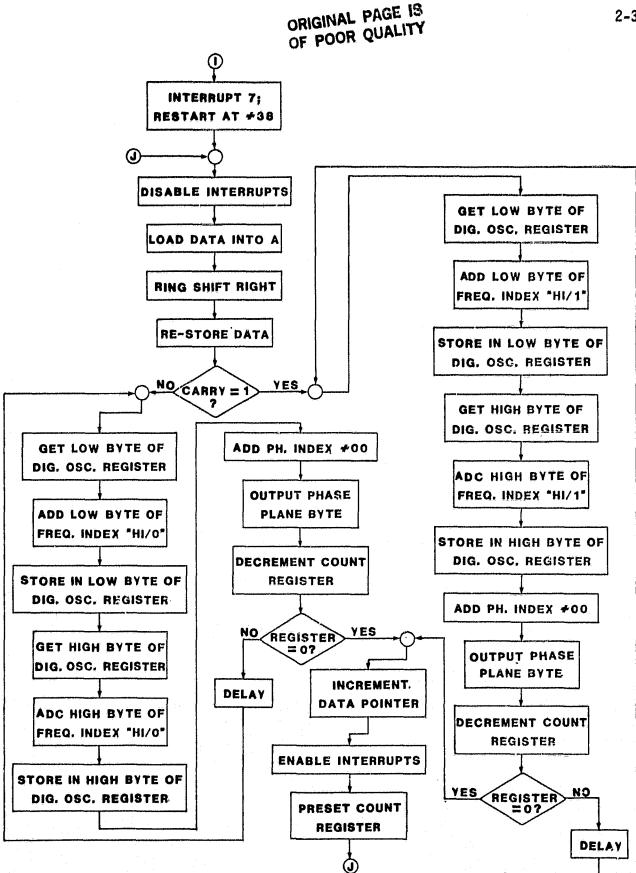

To facilitate demonstration of the Universal Modulator functions on commonly available hardware, a routine to simulate the digital oscillator technique of MSK/PSK generation has been developed for use on the 8080A microprocessor. The program has been written specifically for the Intel Intellec MDS-800 system, but it may be run (with minor modifications to accomodate system hardware implementation differences) on any 8080A/Z-80 based system [4]. The basic flow charts are shown in Figure 2.3.2.

The basic program functions are similar to the previously mentioned 1802 routines. The data is retrieved from a block stored in RAM, shifted to convert the parallel-formatted storage to a serial stream, and finally used to select the appropriate Frequency Index and Phase Index numbers for the digital oscillator routine.

The 8080A register pairs are used in several modes to produce as efficient a code as possible. The D&E register pair serve as the pointer for the phase plane RAM block; B&C serve as the digital oscillator accumulator; and H&L combine functions as the data pointer and as a clock loop counter. Since the 8080A does not have external flag inputs comparable to  $\overline{EFT}$  through  $\overline{EF4}$  on the 1802, the various routines are selected by front-panel interrupt switches (0-7) on the Intellec system. Each interrupt switch via hardware causes a vectored restart to one of eight locations (#00, #08, #10, #18, #20, #28, #30, or #38) which in turn force an unconditional jump to one of eight control subroutines. Each of these subroutines, although similar to the others, has unique Frequency Index

\*

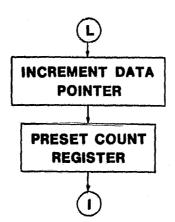

Figure 2.3.2. Basic Flow Chart for 8080A MSK/PSK Demonstration Program.

Figure 2.3.2. Continued.

ORIGINAL PAGE IS OF POOR QUALITY

Figure 2.3.2. Continued.

Figure 2.3.2. Continued.

Figure 2.3.2. Continued.

Figure 2.3.2. Continued.

## ORIGINAL PAGE IS OF POOR QUALITY

Figure 2.3.2. Continued.

Figure 2.3.2. Continued.

and Phase Index constants which specify the mode of modulation, operating frequency, and the rest/operate state of the system. As with the 1802 demonstration package, the 8080A routine outputs the phase plane values to an 8-bit parallel output port which feeds a digital-to-analog converter that produces the desired analog output. For demonstration of the MSK/PSK generation technique this analog output may be amplified and applied to a loudspeaker in the same manner as with the 1802 setup.

As noted in Table 2.3.2, routines 0 through 3 operate at a lower carrier output frequency than routines 4 through 7. The even-numbered routines are standby programs which produce a clear (unmodulated) carrier, whereas the odd-numbered ones provide for MSK or PSK modulation. Routines 1 and 5 generate PSK; MSK is produced by branching to subroutines 3 and 7. Each subroutine is structured to provide a constant execution time for each program loop; in addition, all the subroutines have identical overall execution times since the effective bit rate must remain constant. Each routine samples for interrupts once per bit period; if no interrupt is detected, the routine in control continues. The delays inserted at various positions in the flow diagrams are used to equalize the loop times to meet the constant bit-rate requirement.

### 2.4 HARDWARE DESIGN CONSIDERATIONS

The actual clock frequencies, register lengths, and bit rates required from the digital oscillator system are functions of the specific applications of the DCP. In particular, the four principal satellites currently in service have specific RF frequencies, data formats, modulation forms, and bit rates which must be accomodated by the overall PDCP/UM unit. The task of synthesizing the proper data bit streams via the 1802

| <u>Interrupt</u> | Function                     | <b>Restart Location</b> |

|------------------|------------------------------|-------------------------|

| 0                | f <sub>LO</sub> /PSK/Rest    | #00                     |

| 1                | f <sub>LO</sub> /PSK/Operate | #08                     |

| 2                | f <sub>LO</sub> /MSK/Rest    | #10                     |

| 3                | f <sub>LO</sub> /MSK/Operate | #18                     |

| 4                | f <sub>HI</sub> /PSK/Rest    | #20                     |

| 5                | f <sub>HI</sub> /PSK/Operate | #28                     |

| 6                | f <sub>HI</sub> /MSK/Rest    | #30                     |

| 7                | f <sub>HI</sub> /MSK/Operate | #38                     |

Table 2.3.2.

Restart Locations and Parameters for 8080A Demonstration Software. microprocessor has been successfully achieved at the University of Tennessee [5]. The major impetus for the "Universal Modulator" task was to utilize the 1802 in the generation of the several useful forms of data modulation as well as control by microprocessor of the final RF transmitting frequencies.

At the outset of this contract NASA personnel offered a list of basic features or specifications which were desirable for the satellite data collection service. Table 2.4 summarizes these requirements, which represent systems used currently as well as in the forseeable future. As can be seen, MSK is anticipated to be the dominant form of modulation in future DCP systems, followed by PSK. Since the Landsat satellite has no apparent successor, it seems that the narrowband, low-bit-rate systems are destined to dominate the data-collection field. In addition, personnel from the National Space Testing Laboratory at Bay St. Louis, Mississippi have suggested that MSK may be tried on the GOES satellite in the near future, which further strengthens the position that MSK is the wave of the future.

### 2.4.1 Original PDCP/UM Design Parameters

The original hardware requirements for the PDCP/UM system were based on the current group of operational data-collection satellites (TIROS-N, GOES, LANDSAT, and NIMBUS-F) and on the projected availability of a snap-diode frequency multiplier which could convert a 50MHz signal to roughly 400MHz for use in the satellite band. Table 2.4.1.1 gives the satellites, types of modulation, and RF frequencies required. On the basis of the snap-diode unit's frequency multiplication factor of eight, the

| System Parameter                                | Current Specification | Future Specifications     |

|-------------------------------------------------|-----------------------|---------------------------|

| (1) Output frequency                            | 401.2 - 401.85MHz     | 400 - 403MHz              |

| (2) Output power                                | 2 - 5 Watts           | 2 - 5 Watts               |

| (3) Modulation types                            | FSK, PSK              | MSK,PSK,FSK,CW            |

| (4) Modulated bit rates                         | 200Hz - 5kHZ          | 100Hz - 10kHz             |

| (5) Number of channels                          | 1 - 99 per satellite  | approx. 100 max, per sat. |

| (6) Operational life                            | <u>1</u> - 1 year     | 1 - 2 years min.          |

| (7) Dominant modulation<br>mode                 | PSK                   | MSK                       |

| (8) Power consumption                           | $\sim$ 100mW avg.     | < 100mW avg.              |

| (9) Frequency control                           | hardware (xtal)       | software (µP)             |

| (10) Modulation control                         | hardware system       | software (µP)             |

| <pre>(11) Automatic frequency<br/>control</pre> | none                  | via WW                    |

| (12) Programmable operation                     | no                    | yes                       |

| (13) Automatic emergency operation              | no                    | yes                       |

| (14) Overall cost (\$K)                         | approx, 5-10          | approx, 2-4               |

| (15) Reliability (overall)                      | good                  | excellent                 |

|                                                 |                       |                           |

Table 2.4. Basic Requirements for PDCP/UM System

| Satellite            | Frequency            | Modulation<br>Format | Effective<br>Bit Rate | Approx.<br>Trans.<br>Power |

|----------------------|----------------------|----------------------|-----------------------|----------------------------|

| NIMBUS-F<br>(TWERLE) | 401.20MHz            | PSK, <u>+</u> 60°    | 200Hz                 | 600mW                      |

| TIROS-N<br>(ARGOS)   | 401.65MHz            | PSK, <u>+</u> 60°    | 800Hz                 | 3W                         |

| LANDSAT<br>(ERTS)    | 401.55MHz            | FSK, ±5kHz           | 5kHz                  | 5W                         |

| GOES<br>(SMS)        | 401.70-<br>401.85MHz | PSK, <u>+</u> 60°    | 200Hz                 | 5W                         |

Table 2.4.1.1. Current Satellite Standards for DCPs.

desired system parameters were calculated from Equations 2.2.1 and 2.2.2 to give the final output frequencies and deviations.

As noted from Equation 2,2,2, the minimum frequency increment is given by

$$\Delta f_{\min} = \frac{f_{CLK}}{2^n},$$

where n is the number of digital oscillator accumulator bits. For a 16bit-wide accumulator,  $2^{n}$  = 65,536. Now the clock frequency can be determined from the output frequency constraints:

$$f_{RF} = 8 \cdot \Delta f_{OUT}$$

(Eqn. 2.4.1.1)

$$\Delta f_{RF} \stackrel{\sim}{=} 1499 Hz$$

(GOES) (Eqn. 2.4.1.2)

$$\Delta f_{RF} = 5000 Hz (LANDSAT)$$

(Eqn. 2.4.1.3)

$$\Delta f_{OUT} = \frac{1}{8} \cdot \Delta f_{RF}$$

(Eqn. 2.4.1.4)

The average interchannel frequency spacing for the GOES satellite is 1499.97143Hz; this becomes a constraint on the step size  $\Delta f_{OUT}$  and thus the clock frequency  $f_{CLK}$ . Another requirement is that the CPFSK frequency deviation for the LANDSAT system is 5kHz. Obviously, these two constraints cannot be satisfied accurately by a single clock frequency, so two different clocks must be employed - one for GOES, NIMBUS-F, and TIROS-N, and the other for LANDSAT. For the former,

$$\Delta f_{OUT_1} = \frac{1}{8} \cdot 1499.07143Hz = 187.38393Hz \quad (Eqn. 2.4.1.5)$$

$$f_{CLK_1} = \Delta f_{OUT_1} \cdot 2^{16} = \quad (Eqn. 2.4.1.6)$$

$$(187,38393)(65,536) \stackrel{\sim}{=} 12,280393MHz$$

## ORIGINAL PAGE IS OF POOR QUALITY

| CHANNEL<br>NUMBER          | OUTPUT<br>FREQUENCY<br>MH2                                              | CHANNEL<br>NUMBER    | OUTPUT<br>FREQUENCY<br>MHZ                               |

|----------------------------|-------------------------------------------------------------------------|----------------------|----------------------------------------------------------|

| 1                          | 401.700,996                                                             | 51                   | 401,775,949                                              |

| 2                          | 401.702,495                                                             | 52                   | 401,777,449                                              |

| 3                          | 401.703,994                                                             | 53                   | 401,778,948                                              |

| 4                          | 401.705,493                                                             | 54                   | 401,780,447                                              |

| 5                          | 401.706,992                                                             | 55                   | 401,781,946                                              |

| 6                          | 401.708,491                                                             | 56                   | 401.783,445                                              |

| 7                          | 401.709,990                                                             | 57                   | 401.784,944                                              |

| 8                          | 401.711,489                                                             | 58                   | 401.785,443                                              |

| 9                          | 401.712,989                                                             | 59                   | 401.787,942                                              |

| 10                         | 401.714,448                                                             | 60                   | 401.789,441                                              |

| 11                         | 401.715,987                                                             | 61                   | 401.790,940                                              |

| 12                         | 401.717,486                                                             | 62                   | 401.792,430                                              |

| 13                         | 401.718,985                                                             | 63                   | 401.793,938                                              |

| 14                         | 401.720,484                                                             | 64                   | 401.795,437                                              |

| 15                         | 401.721,983                                                             | 65                   | 401.796,935                                              |

| 16                         | 401.723,482                                                             | 66                   | 401.798,435                                              |

| 17                         | 401.724,981                                                             | 67                   | 401.799,935                                              |

| 18                         | 401.726,480                                                             | 68                   | 401.801,434                                              |

| 19                         | 401.727,979                                                             | 69                   | 401.802,933                                              |

| 20                         | 401.729,478                                                             | 70                   | 401.804,432                                              |

| 21                         | 401.730,977                                                             | 71                   | 401.805,931                                              |

| 22                         | 401.732,476                                                             | 72                   | 401.807,430                                              |

| 23                         | 401.733,976                                                             | 73                   | 401.808,929                                              |

| 24                         | 401.735,475                                                             | 74                   | 401.810,428                                              |

| 25                         | 401.736,974                                                             | 75                   | 401.811,927                                              |

| 26                         | 401.738,473                                                             | 76                   | 401.813,426                                              |

| 27                         | 401.739,972                                                             | 77                   | 401.814,925                                              |

| 28                         | 401.741,471                                                             | 78                   | 401.816,424                                              |

| 29                         | 401.742,970                                                             | 79                   | 401.817,923                                              |

| 30                         | 401.744,469                                                             | 80                   | 401.819,422                                              |

| 31                         | 401.745,968                                                             | 81                   | 401.820,922                                              |

| 32                         | 401.747,467                                                             | 82                   | 401.822,421                                              |

| 33                         | 401.748,966                                                             | 83                   | 401.823,920                                              |

| 34                         | 401.750,465                                                             | 84                   | 401.825,419                                              |

| 35                         | 401.751,964                                                             | 85                   | 401.826,918                                              |

| 36                         | 401.753,463                                                             | 86                   | 401.828,417                                              |

| 37                         | 401.754,962                                                             | 87                   | 401.829,916                                              |

| 38                         | 401.756,462                                                             | 88                   | 401.831,415                                              |

| 39                         | 401.757,961                                                             | 89                   | 401.832,914                                              |

| 40                         | 401.759,460                                                             | 90                   | 401.834,413                                              |

| 41                         | 401.760,959                                                             | 91                   | 401.835,912                                              |

| 42                         | 401.762,458                                                             | 92                   | 401.837,411                                              |

| 43                         | 401.763,957                                                             | 93                   | 401.838,910                                              |

| 44                         | 401.765,456                                                             | 94                   | 401.840,409                                              |

| 45                         | 401.766,955                                                             | 95                   | 401.841,908                                              |

| 46<br>47<br>48<br>49<br>50 | 401.768,454<br>401.769,953<br>401.771,452<br>401.772,951<br>401.774,450 | 96<br>97<br>98<br>99 | 401.843,408<br>401.844,907<br>401.846,406<br>401.847,905 |

# Table 2.4.1.2 GOES Satellite Channel Frequencies

For the latter,

$$\Delta f_{OUT_2} = \frac{1}{8} \cdot 5000 \text{Hz} = 625 \text{Hz}$$

(Eqn. 2.4.1.7)

$f_{CLK_2} = \Delta f_{OUT_2} \cdot 2^{16} = 40.96 \text{MHz}$  (Eqn. 2.4.1.8)

In the first calculation,  $\Delta f_{OUT_1}$  has been assumed to be one step and the resultant  $f_{CLK_1}$  is a reasonable value. However,  $f_{CLK_2}$  is too high a frequency to be handled by low-power hardware, so  $\Delta f_{OUT_2}$  is now assumed to be four steps in digital oscillator frequency. The new clock frequency is:

$$\Delta f_{OUT_2} = \frac{1}{8} \cdot \frac{1}{4} \cdot 5000 \text{Hz} = 156.25 \text{Hz} \qquad (Eqn. 2.4.1.9)$$

$$f_{CLK_2} = \Delta f_{OUT_2} \cdot 2^{16} = 10.24 \text{MHz} \qquad (Eqn. 2.4.1.10)$$

which is more suitable. Note that both clock frequencies satisfy the general constraints of Section 2.2 in that both are roughly 1000 times greater than the highest desired data rate ( $\approx$  10kHz) and about an order of magnitude greater than the desired digital oscillator output frequency of roughly 1MHz. This figure was chosen principally as a compromise between ease of generation and the need to ensure that any image frequencies generated by the translation/multiplication process following the digital oscillator will not fall within the satellite band of interest. Since the digital oscillator produces a roughly 1MHz output with channel spacings of one-eighth the desired final RF frequency steps, the D/A output must be mixed with a local oscillator signal before being multiplied up to the 401MHz band, Using the above values for  $f_{CLK_1}$  and a typical GOES transmitting frequency from Table 2.4.2, the local oscillator frequency will be:

Input to X8 Multiplier = 50.22180625MHz (Eqn. 2.4.1.12)

$$f_{OUT} = \frac{(F.I.)(f_{CLK_1})}{2^{16}} = \frac{(5503)(12.28039315MHZ)}{65,536} \approx 1.03117376MHz(Eqn. 2.4.1.13)$$

$$f_{L.0.} = 50.22180625 - 1.03117376 = 49.19063249MHz(Eqn. 2.4.1.14)$$

The local oscillator is simply used to translate the digital oscillator signal up to the 50.22180625MHz frequency which feeds the X8 multiplier system. This multiplier may be implemented by either exotic methods such as microwave snap diodes or may simply be three cascaded frequency-doubler stages using standard UHF biolar or field-effect transistors.

A basic constraint of this approach to generating the operating frequency is that of the image frequencies produced in the mixing process. From Equation 2.4.14 it is evident that the sum-frequency output of the mixer is the desired signal (at 50.22180625MHz), but the difference (image) frequency at 48.15945873MHz is also present and is applied to the multiplier block just as the desired signal is. The final result will be a spanious signal, somewhat attenuated by the RF selectivity of the transmitter, which lies at 385.2756698MHz, some 16.49878MHz below the desired signal on GOES channel 50.

Four benefits are obtained from this separation in frequency of the main and image signals. First, the image lies outside the standard satellite DCP transmitting band and thus presents no danger of interference to other DCPs. Second, the image is sufficiently removed from the main channel that a simple transmission-line trap may be applied if necessary to effectively notch out the image. Third, since the signal is aimed essentially upward from the ground, there would be little possibility of harmful interference to land-based communications. Finally, there is probably no need for an expensive high-selectivity filter following the mixer stage; this would help keep system costs low.

Using the previously determined values for the various system oscillator frequencies, the system parameters for several satellite channels can be enumerated and are presented in Table 2,4,1,3. Included are data for the LANDSAT, TIROS-N, NIMBUS-F frequencies and three typical channels on the GOES system.

From a quick examination of the table it is evident that the local oscillator and clock frequencies have been tailored to the requirements of the GOES satellite, since due to its 99 channels it is the most sensitive of the four systems to transmitter frequency errors. The other units, being somewhat more forgiving in this respect, are still served with frequency errors of no more than 0.75ppm. In addition, the CPFSK produced for LANDSAT use yields previsely the ±5000Hz frequency deviation required by the satellite; in addition, the +60Hz offset in center frequency is negligible compared with the Doppler shifts present with LANDSAT. Interestingly enough, by using one-fourth the normal deviation, MSK can be directly synthesized for use on LANDSAT with absolutely no change in hardware.

The F.I. and P.I. figures indicate the decimal values and the actual equivalent hexadecimal numbers gated into the digital oscillator by the data-handling microprocessor to effect the modulation- and frequency-control functions. The phase increments of  $\pm 5$  units generate  $\pm 7,03125^{\circ}$  phase shifts at the digital oscillator output; this phase deviation is then multiplied by eight in the succeeding RF circuitry to generate  $\pm 56,25^{\circ}$  of phase shift at the final RF carrier frequency, which is within 6,25% of the nominal  $\pm 60^{\circ}$ deviation and is well within the specification limits of current DCP transmitters, fclk1 = 12.28039315MHz (GOES/TIROS-N/NIMBUS-F)

$f_{CLK_2} = 10.2400000 \text{MHz} (LANDSAT)$

fL.0. = 49.19063249MHz

Multiplication factor = 8

| /HEX)                |                         | ORIC<br>OF F               |                |                        |                        |                        |

|----------------------|-------------------------|----------------------------|----------------|------------------------|------------------------|------------------------|

| P.I.(DECIMAL/HEX     | 0/00<br>-5/FB<br>+5/05  | 0/00<br>-5/FB<br>+5/05     | 00/0<br>00/0   | 0/00<br>-5/FB<br>+5/05 | 0/00<br>-5/FB<br>+5/05 | 0/00<br>-5/FB<br>+5/05 |

| F.I.(DECIMAL/HEX)    | 5420/152C               | 5120/1400                  | 6420/1914      | 5454/154E              | 5503/157F              | 5552/1580              |

|                      | 5420/152C               | 5120/1400                  | 6416/1910      | 5454/154E              | 5503/157F              | 5552/1580              |

|                      | 5420/152C               | 5120/1400                  | 6424/1918      | 5454/154E              | 5503/157F              | 5552/1580              |

| DIG. OSC. FREQ.(MHz) | 1.01562089              | 0.95940571                 | 1,00321500     | 1,02199195             | 1.03117376             | 1.04035557             |

|                      | 1.01562089              | 0.95940571                 | 1,00250000     | 1,02199195             | 1.03117376             | 1.04035557             |

|                      | 1.01562089              | 0.95940571                 | 1,00375000     | 1,02199195             | 1.03117376             | 1.04035557             |

| FREQ. ERROR          | +27Hz<br>+27Hz<br>+27Hz | +306Hz<br>+306Hz<br>+306Hz | zH09+<br>zH09+ | 0Hz<br>0Hz<br>0Hz      | 0Hz<br>0Hz<br>0Hz      | 0Hz<br>0Hz<br>0Hz      |

| OUTPUT FREQ(MHz)     | 401.650027              | 401.200306                 | 401.550060     | 401.700996             | 401.774450             | 401.847905             |

|                      | 401.650027              | 401.200306                 | 401.545060     | 401.700996             | 401.774450             | 401.847905             |

|                      | 401.650027              | 401.200306                 | 401.555060     | 401.700996             | 401.774450             | 401.847905             |

| SATELLITE            | TIROS-N(Rest)           | NIMBUS-F(Rest)             | LANDSAT(Rest)  | GOES#1(Rest)           | GOES#50(Rest)          | GOES#99(Rest)          |

|                      | (Bit=0)                 | (Bit=0)                    | (Bit=0)        | (Bit=0)                | (Bit=0)                | (Bit=0)                |

|                      | (Bit=1)                 | (Bit=1)                    | (Bit=1)        | (Bit=1)                | (Bit=1)                | (Bit=1)                |

Table 2.4.1.3 Parameters for Original PDCP/UM Configuration.

k }

1.14.14

### 2.4.2 Modified Hardware Configuration

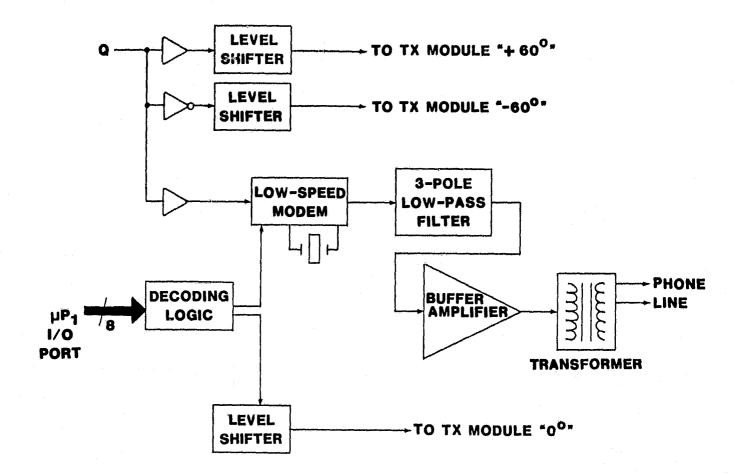

At the request of Goddard personnel, the previously discussed design was modified in order to utilize a currently available NIMBUS-F DCP transmitter manufactured by Handar[6]. This unit is configured as a chain of RF amplifier/multiplier stages which takes a master oscillator input signal of a few milliwatts at 10,03MHz and multiplies the frequency by a factor of 40 to get to the 401.2MHz satellite channel. Phase-shift control inputs for  $\pm 60^{\circ}$  deviation are provided to allow the DCP to modulate the RF outputs; application of +12 volts to the appropriate terminals will produce RF with  $-60^{\circ}$ ,  $0^{\circ}$ , or  $+60^{\circ}$  phase, respectively[7].

With the overall RF frequency multiplication ratio set to 40, the digital oscillator clock and local oscillator frequencies must be altered to provide the desired output frequencies and deviations from the PDCP/UM system. Analogously to Equations 2.4.1.5 - 2.4.1.14, the resulting calculations are:

| $\Delta f_{OUT_1} = \frac{1}{40} \cdot 1499.07143Hz = 37.47678575Hz$                    | (Eqn. 2.4.2.1) |