N84-34024 9950-923

DOE/JPL-955640-84/10 DISTRIBUTION CATEGORY UC-63

DEVELOPMENT AND FABRICATION OF A SOLAR CELL JUNCTION PROCESSING SYSTEM

> Final Technical Report **JUNE 1984**

THE JPL LOW-COST SOLAR ARRAY PROJECT IS SPONSORED BY THE U.S. DEPARTMENT OF ENERGY AND FORMS PART OF THE SOLAR PHOTO-**VOLTAIC CONVERSION PROGRAM TO** INITIATE A MAJOR EFFORT TOWARD THE DEVELOPMENT OF LOW-COST SOLAR ARRAYS. THIS WORK WAS PERFORMED FOR THE JET PROPULSION LABORATORY. CALIFORNIA INSTITUTE OF TECHNOLOGY BY AGREEMENT BETWEEN NASA AND DOE.

> Prepared Under Contract No. 955640 for: JET PROPULSION LABORATORY CALIFORNIA INSTITUTE OF TECHNOLOGY PASADENA, CALIFORNIA 91109

(NASA-CR-173948) DEVELOPMENT AND FABRICATION OF A SOLAR CELL JUNCTION PROCESSING SYSTEM Draft Final Report (Spire Corp., Bedford, Mass.) 135 p HC A07/MF A01

N84-34024

Unclas CSCL 10A G3/44 23914

This report was prepared as an account of work sponsored by the United States Government. Neither the United States nor the United States Department of Energy, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, expressed or implied, or assumes any legal liability or responsibility for the accuracy, completeness or usefulness of any information, apparatus, product or process disclosed, or represents that its use would not infringe privately owned rights.

### DEVELOPMENT AND FABRICATION OF A SOLAR CELL JUNCTION PROCESSING SYSTEM

Report Number FR-10073 Draft Final Report

December 1983

This work was performed for the Jet Propulsion Laboratory, California Institute of Technology, sponsored by the National Aeronautics and Space Administration under contract NAS7-100.

SPIRE CORPORATION

Patriots Park

Bedford, MA 01730

#### ABSTRACT

A program was undertaken to develop, construct and deliver to JPL a processing system capable of producing solar cell junctions by ion implantation followed by pulsed electron beam annealing. The machine was to be capable of processing 4-inch diameter single-crystal wafers at a rate of 10<sup>7</sup> wafers per year. A microcomputer-controlled pulsed electron beam annealer with a vacuum interlocked wafer transport system was designed, built and demonstrated to produce solar cell junctions on 4-inch wafers with an AMI efficiency of 12%. Experiments showed that a non-mass-analyzed (NMA) ion beam could implant 10 keV phosphorous dopant to form solar cell junctions which were equivalent to mass-analyzed implants. A NMA ion implanter, compatible with the pulsed electron beam annealer and wafer transport system was designed in detail but was not built because of program termination.

#### TABLE OF CONTENTS

| Section | <u>Pa</u>                                                                          | ge |

|---------|------------------------------------------------------------------------------------|----|

| 1       | INTRODUCTION AND SUMMARY                                                           | l  |

|         | 1.1 Objective                                                                      |    |

|         | 1.2 Tasks                                                                          | l  |

|         | 1.2.1 Task 1 - Development of Pulsed Electron  Beam Subsystem                      | 1  |

|         | Beam Subsystem                                                                     |    |

|         | 1.2.3 Task 3 - Ion Implanter Development                                           |    |

|         | 1.2.4 Task 4 - Junction Processing System                                          |    |

|         | Integration                                                                        | 4  |

|         | 1.2.5 Task 5 - Junction Processing System Cost Analyses                            | ,  |

|         | ,                                                                                  | •  |

|         | ,,                                                                                 | t  |

|         | 1.3.1 Task 1 - Development of Pulsed Electron  Beam Subsystem                      | 4  |

|         | 1.3.2 Task 2 - Wafer Transport Development                                         |    |

|         | 1.3.3 Task 3 - Ion Implanter Development                                           |    |

|         | 1.3.4 Tasks 4 and 5 - System Integration and                                       |    |

|         | Cost Analyses                                                                      | 5  |

| 2       | TASK I - DEVELOPMENT OF PULSED ELECTRON BEAM                                       |    |

| Z       | SUBSYSTEM                                                                          | 1  |

|         | 2.1 General                                                                        |    |

|         | 2.2 Developmental Testing                                                          |    |

|         | 2.2.1 Solid Phase Annealing Experiments                                            |    |

|         | 2.2.2 Overlapping of Pulse-Annealed Regions                                        | -  |

|         | 2.2.3 Beam Control Experiments 2-1                                                 |    |

|         | 2.2.4 Wafer Preheat Experiments 2-6                                                |    |

|         | 2.3 Pulser Design and Fabrication                                                  |    |

|         | 2.3.1 Design Calculations                                                          |    |

|         | 2.3.3 Pulser Subsystem Design                                                      |    |

|         | 2.3.4 Pulser Subsystem Fabrication and Assembly 2-1 2.3.5 Pulser Subsystem Testing |    |

|         | 2.3.6 Pulse Generator Tests                                                        |    |

|         | 2.3.7 Electron Beam Diode Tests                                                    |    |

|         | 2.4 Annealing Experiments                                                          | 23 |

|         | 2.4.1 Preliminary Experiments                                                      | 26 |

|         | 2.4.2 Detailed Annealing Experiments 2-2                                           | 27 |

| 3       | TASK 2 - WAFER TRANSPORT SYSTEM DEVELOPMENT 3-1                                    | 1  |

| ,       |                                                                                    |    |

|         | 3.1 General                                                                        |    |

|         | 3.2.1 Design                                                                       |    |

|         | 3.2.2 Fabrication                                                                  |    |

|         | 3.2.3 Operation                                                                    |    |

|         | •                                                                                  |    |

#### TABLE OF CONTENTS (Concluded)

| Section |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <u>Page</u>       |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 4       | TASK 3 - ION IMPLANTER DEVELOPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-1               |

|         | <ul><li>4.1 General</li><li>4.2 Design Concept</li><li>4.3 NMA Ion Implanter Test Facility</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-1<br>4-2<br>4-2 |

|         | 4.3.1 Beam Steering and Defocusing Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-2               |

|         | for Ion Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-10              |

|         | Ion Beams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-14              |

|         | <ul><li>4.4 Design of NMA Ion Implanter</li><li>4.5 Fabrication and Testing</li><li>4.6 Control of the control</li></ul> | 4-16<br>4-19      |

|         | 4.5.2 Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-19<br>4-19      |

| 5       | TASKS 4 AND 5 - JUNCTION PROCESSOR SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |

|         | INTEGRATION AND COST ANALYSES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 <b>-</b> 1      |

|         | 5.1 System Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-1<br>5-1        |

| 6       | CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6 <b>-</b> 1      |

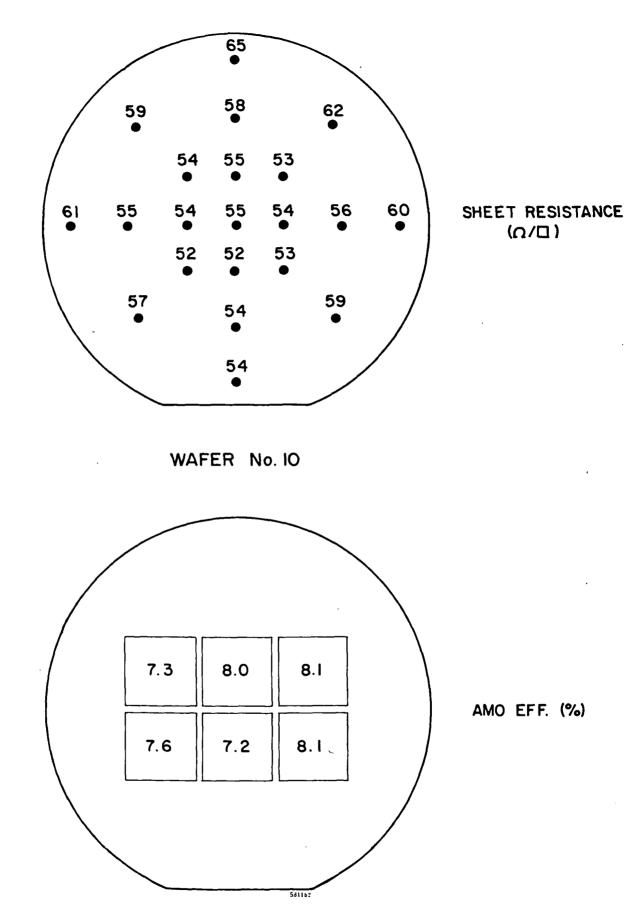

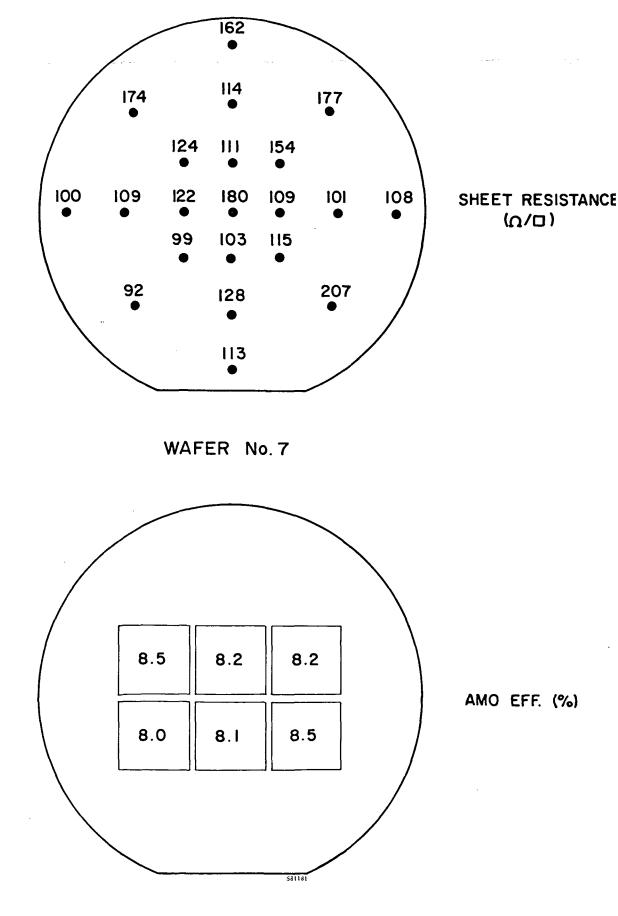

|         | APPENDIX 1 - Summary of Sheet Resistivity Mapping of Pulse Electron Beam Annealed Wafers and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A 1 1             |

|         | Performance Evaluation of Solar Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A1-1              |

|         | APPENDIX 2 - Pulsed Electron Beam/Wafer Transport Systems Operations and Maintenance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A2-1              |

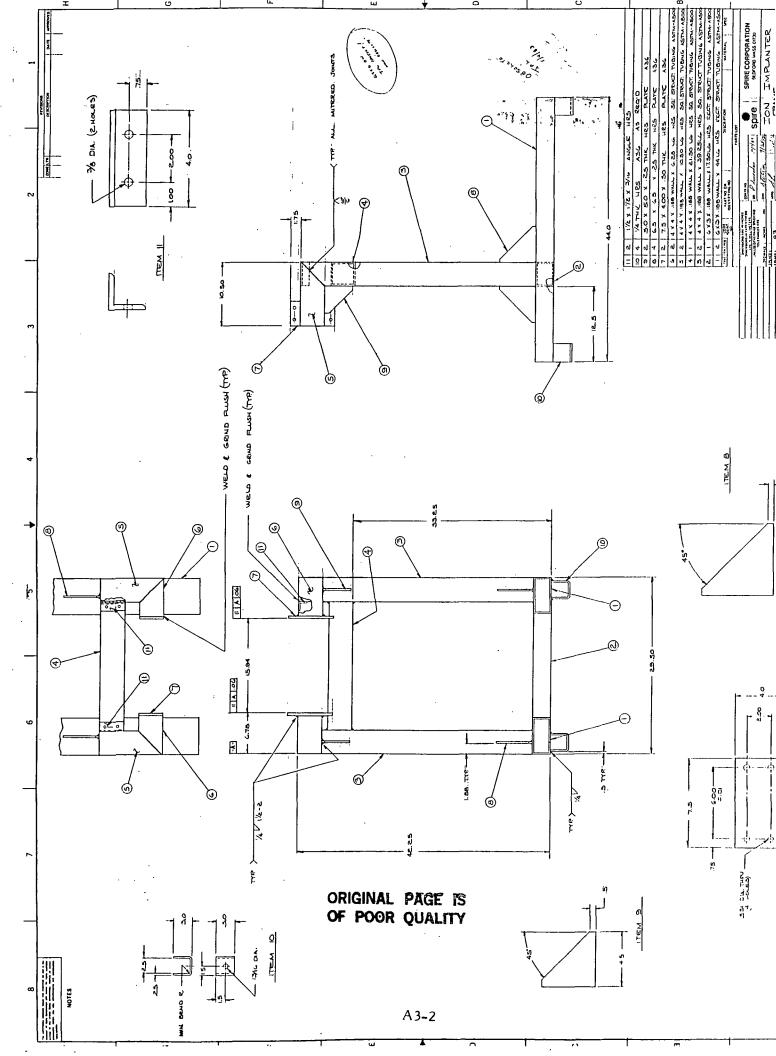

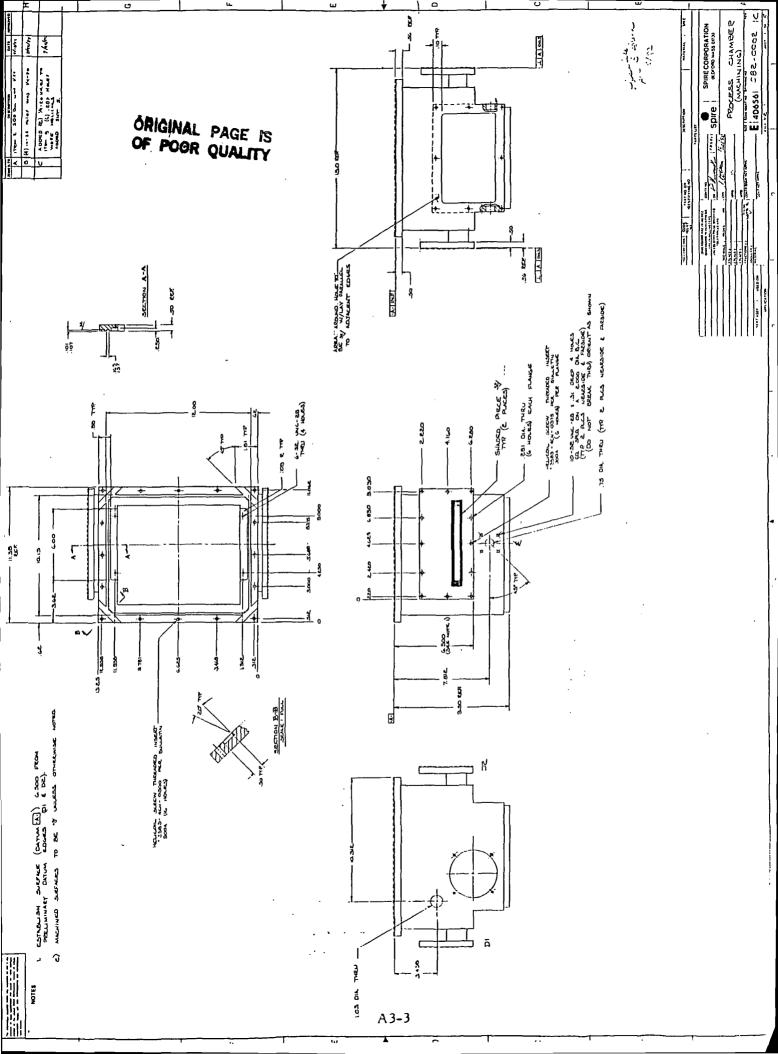

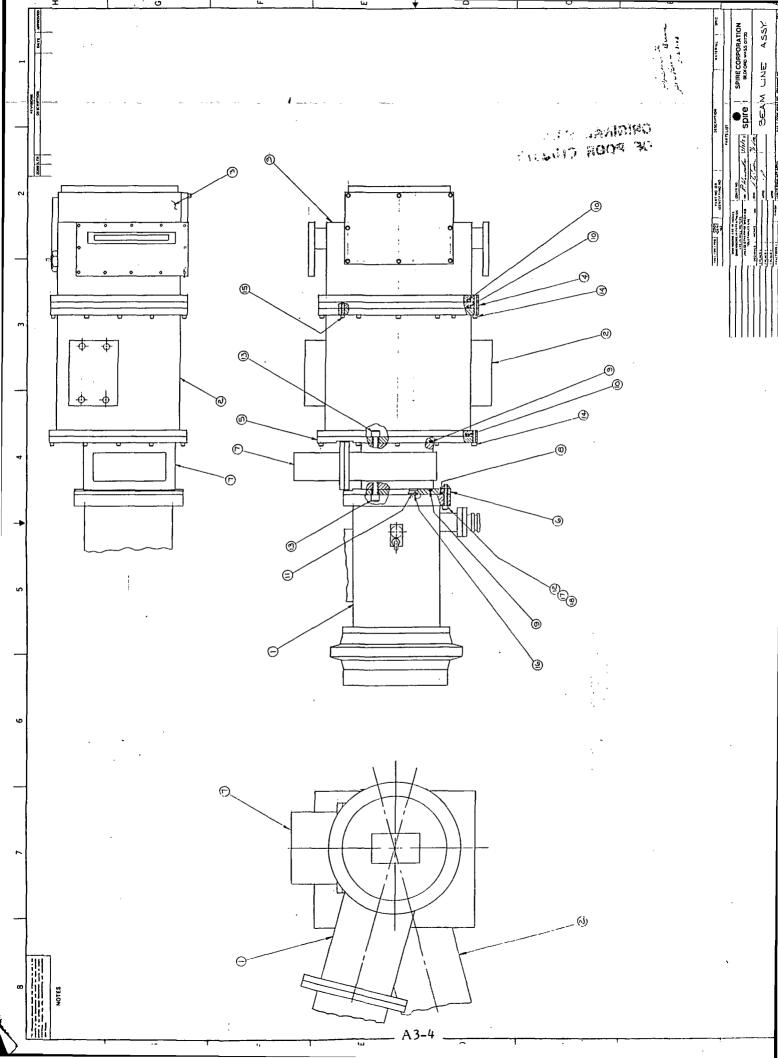

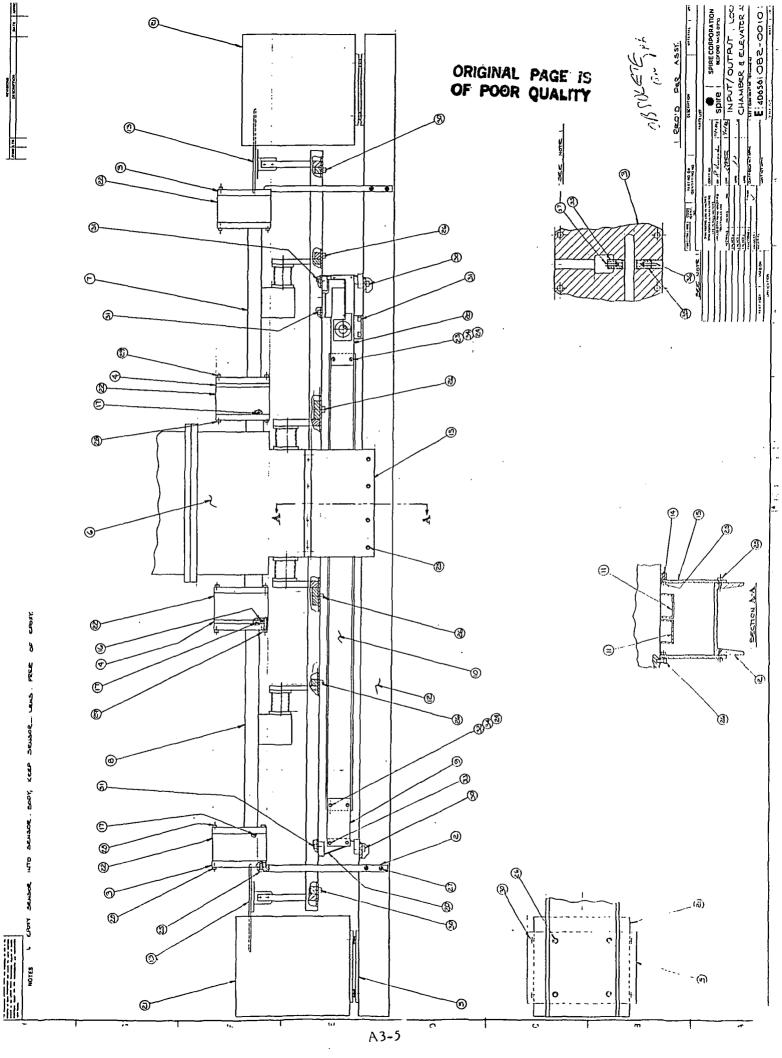

|         | APPENDIX 3 - Layout Drawings of Ion Implanter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A 3_1             |

#### LIST OF ILLUSTRATIONS

| Number  |                                                                                                 | Page |

|---------|-------------------------------------------------------------------------------------------------|------|

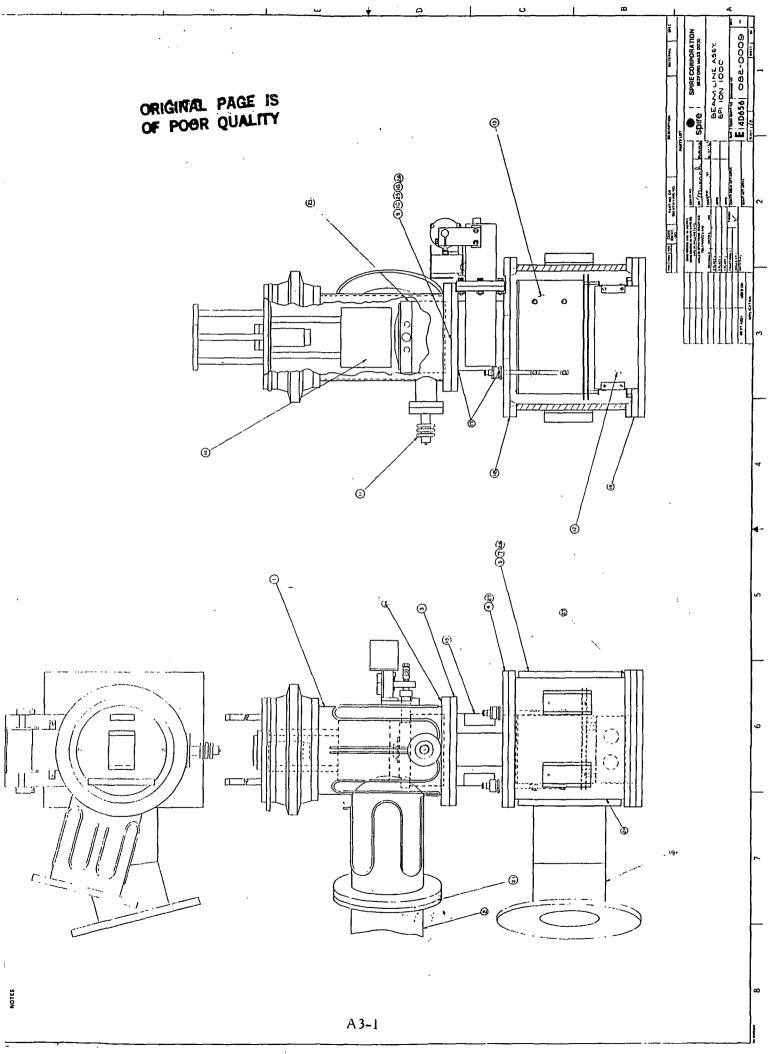

| 1-1     | Artist's Conception of Spire/JPL Junction Processor                                             | 1-2  |

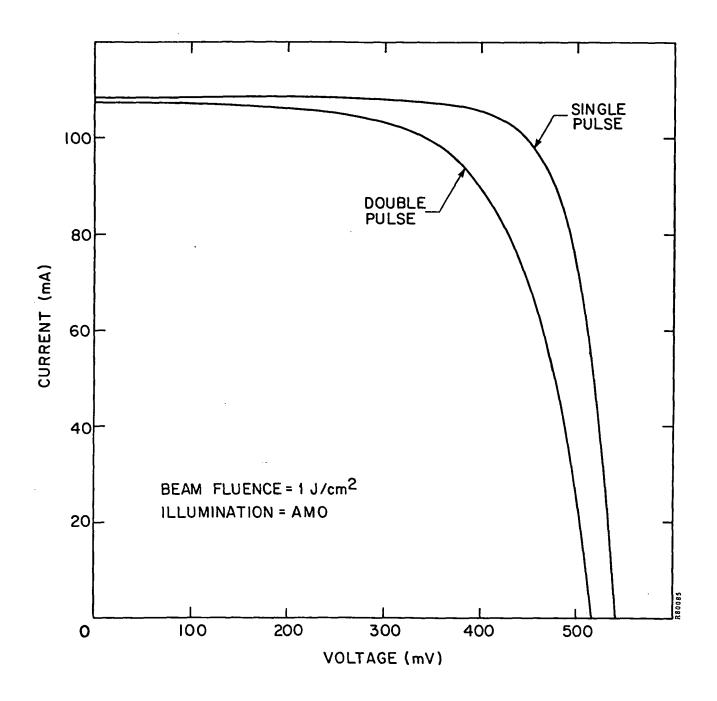

| 2-1     | Voltage-Current Characteristics of Single- and Double-Pulse Annealed Solar Cells                | 2-3  |

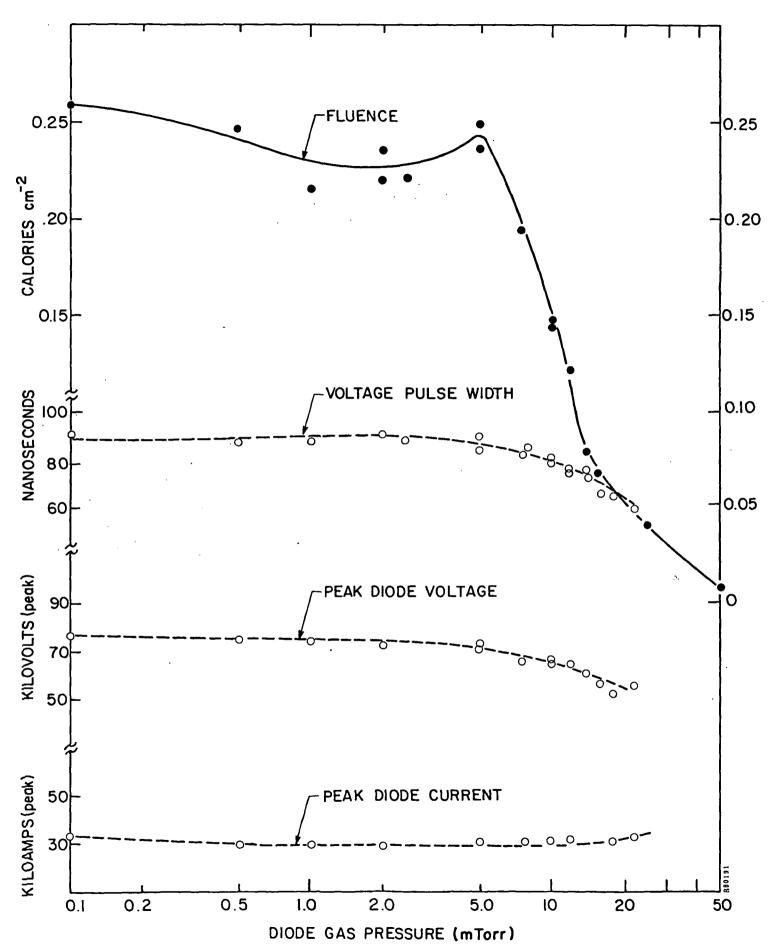

| 2-2     | Beam Parameters Versus Gas Pressure                                                             | 2-5  |

| 2-3     | Limited Parameter Circuit Model of Pulsed Electron Beam Annealer                                | 2-8  |

| 2-4     | Results of Electrical Modeling of Pulsed Electron Beam Annealer                                 | 2-9  |

| 2-5     | Schematic of Multiple-Line Energy Store and Parallel Charging and Discharging Systems           | 2-11 |

| 2-6     | SPI-PULSE 7000 Schematic Diagram                                                                | 2-13 |

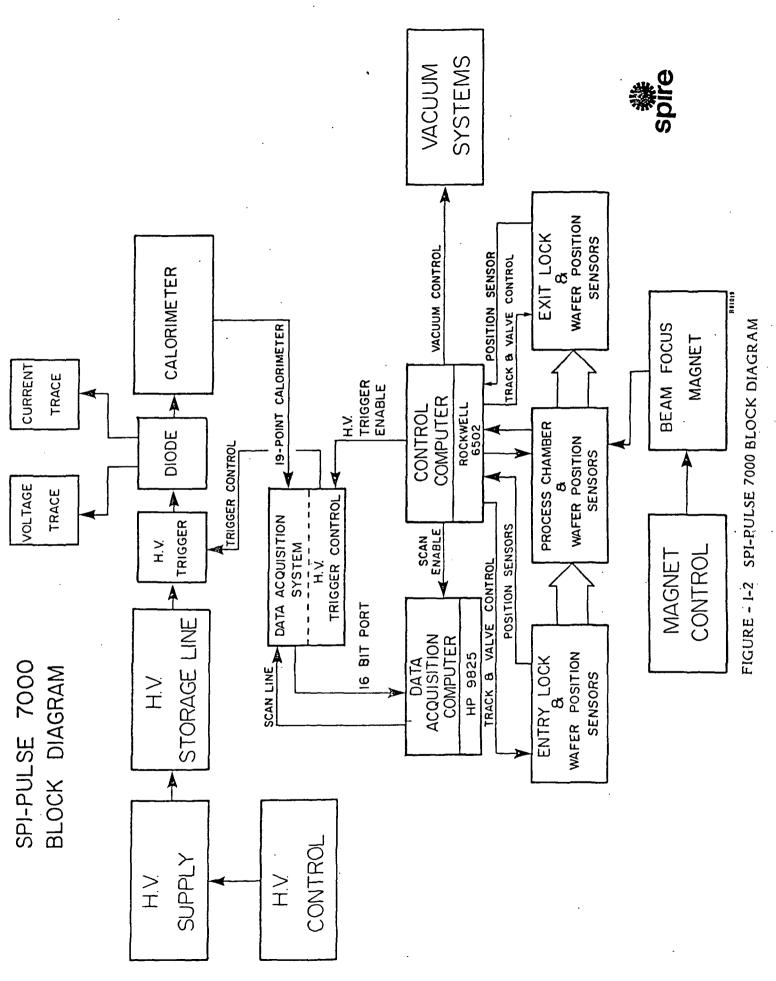

| 2-7     | SPI-PULSE 7000 Functional Block Diagram                                                         | 2-14 |

| 2-8     | Photograph of SPI-PULSE 7000 Pulsed Electron Beam Subsystem                                     | 2-15 |

| 2-9     | View Through Front Port of Wafer Processing Chamber                                             | 2-16 |

| 2-10    | Beam Guiding Field Coil and Yoke Before Assembly of Pulser Subsystem                            | 2-17 |

| 2-11    | Calorimeter Array and Readout                                                                   | 2-20 |

| 2-12(a) | Current Signal From Pulse Generator With the Diode Shorted                                      | 2-21 |

| 2-12(b) | Equivalent Circuit Model for Pulse Generator With Measured Parameters from (a)                  | 2-21 |

| 2-13    | Typical Corrected Diode Voltage, Current and Electron Energy Spectral From Computer Code EBSPEC | 2-24 |

| 2-14    | Measured and Modeled Diode Perveance for Pulse Shown in Figure 2-13                             | 2-25 |

| 2-15    | Cell Efficiency Versus Sheet Resistance - Low Values                                            | 2-29 |

| 2-16    | Cell Efficiency Versus Sheet Resistance - High Values                                           | 2-30 |

#### LIST OF ILLUSTRATIONS (Concluded)

| Number |                                                                        | Page |

|--------|------------------------------------------------------------------------|------|

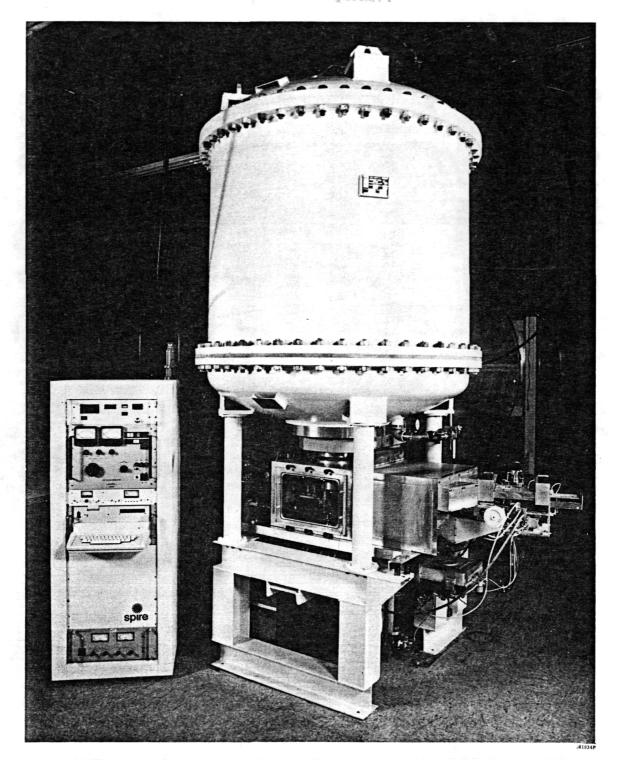

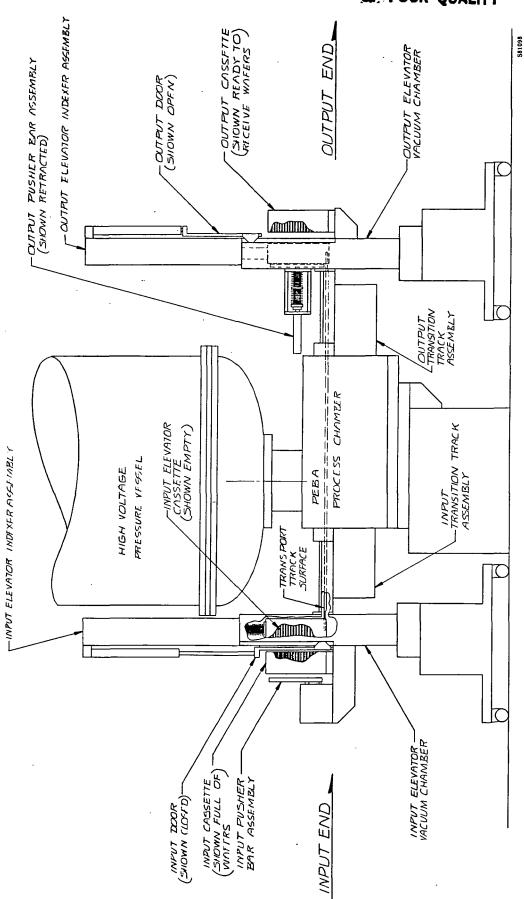

| 3-1    | Pulsed Electron Beam Annealer (PEBA) and Interim Wafer Handling System | 3-3  |

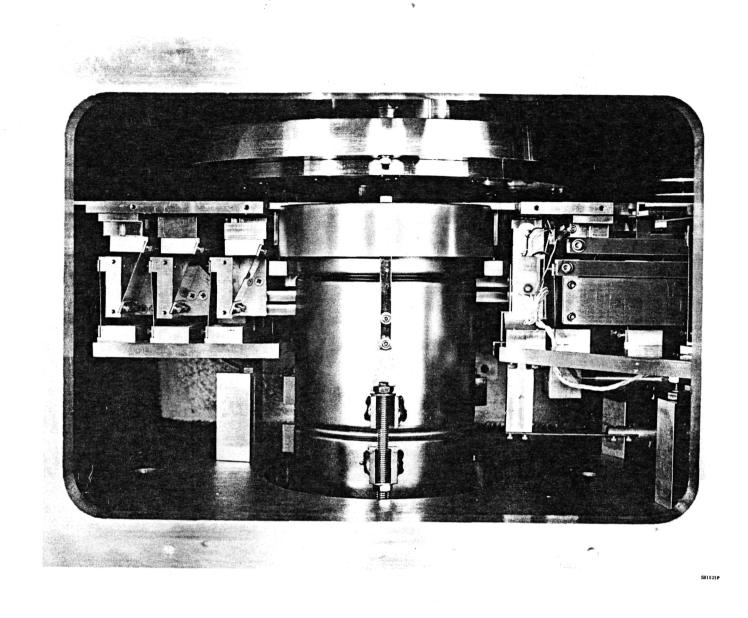

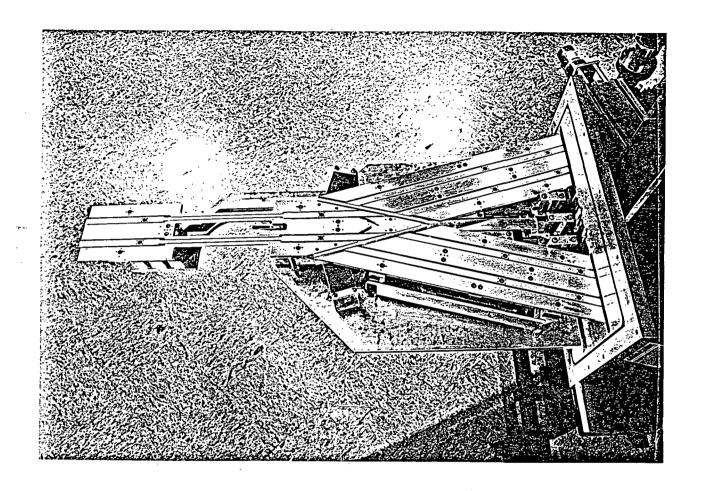

| 3-2    | Plan View of Process Chamber and Interim Transport System              | 3-4  |

| 3-3    | Interim Wafer Transport "Y" Track Section                              | 3-5  |

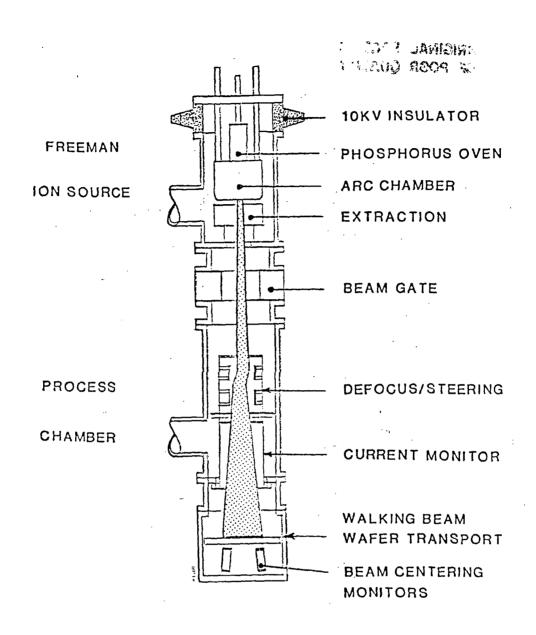

| 4-1    | Conceptual Design of Non-Mass-Analyzed Ion Implanter                   | 4-3  |

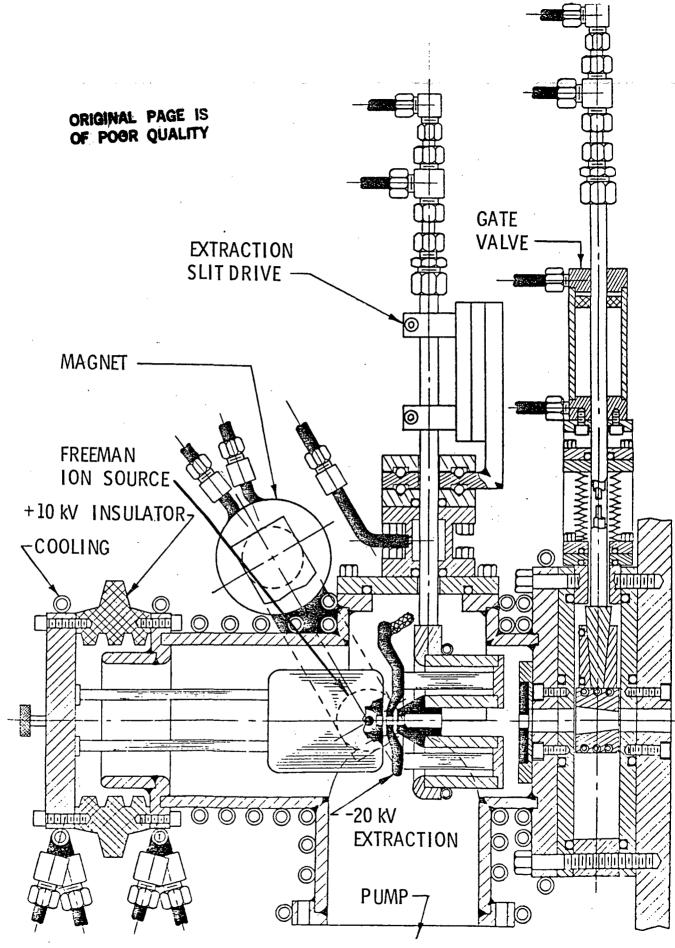

| 4-2    | Design Layout of NMA Ion Source                                        | 4-4  |

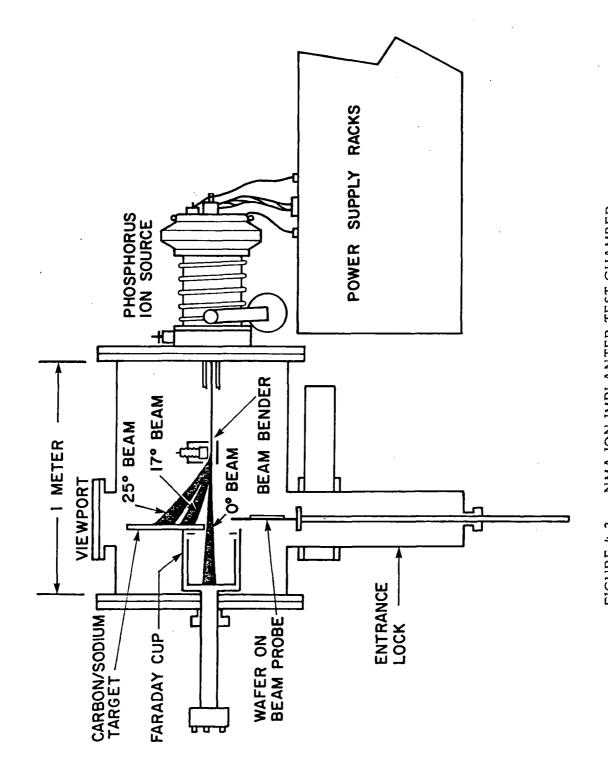

| 4-3    | NMA Ion Implanter Test Chamber                                         | 4-5  |

| 4-4    | Test Model Beam Steering Device                                        | 4-7  |

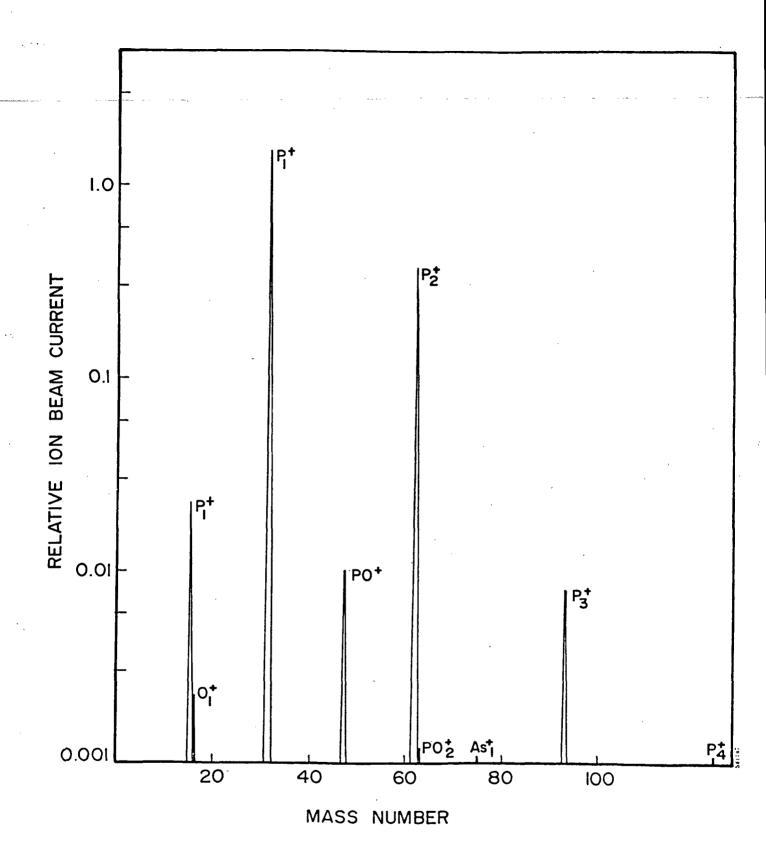

| 4-5    | Ions Produced by Commercial Grade Solid Phosphorus                     | 4-8  |

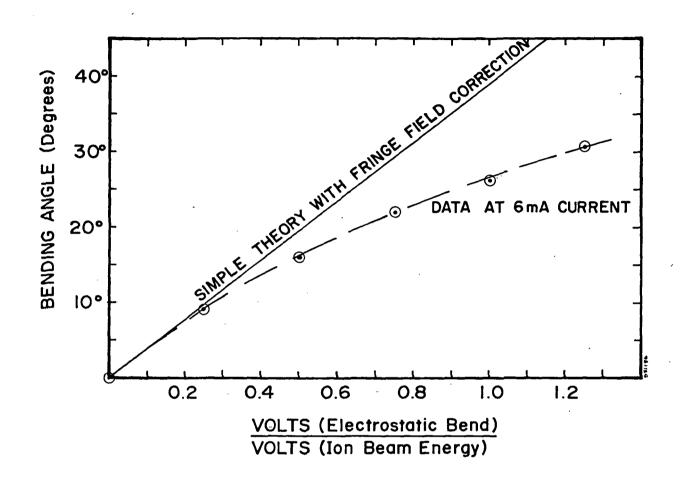

| 4-6    | Electrostatic Beam Bending at High Current                             | 4-9  |

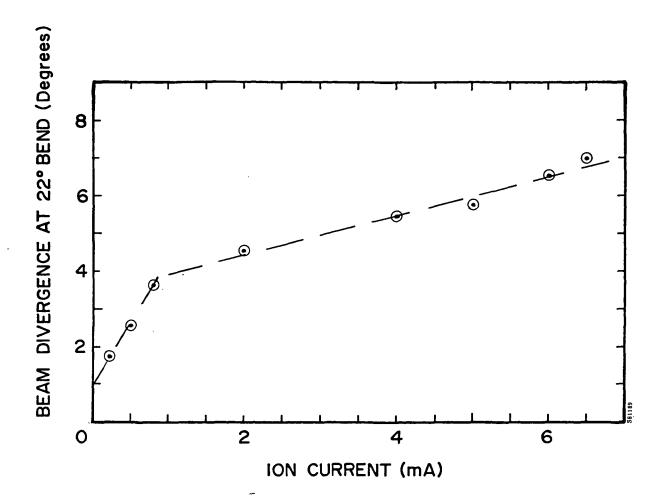

| 4-7    | Ion Implanter Beam Spread After Bend/Defocus                           | 4-11 |

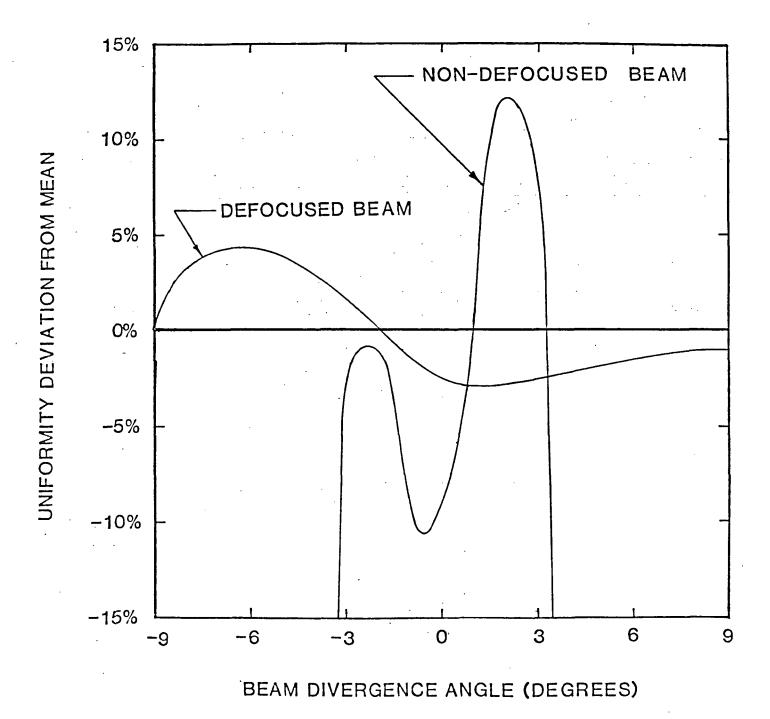

| 4-8    | Design Adopted for Electrostatic Beam Bending and Defocusing           | 4-12 |

| 4-9    | Uniformity Improvement with Defocus                                    | 4-13 |

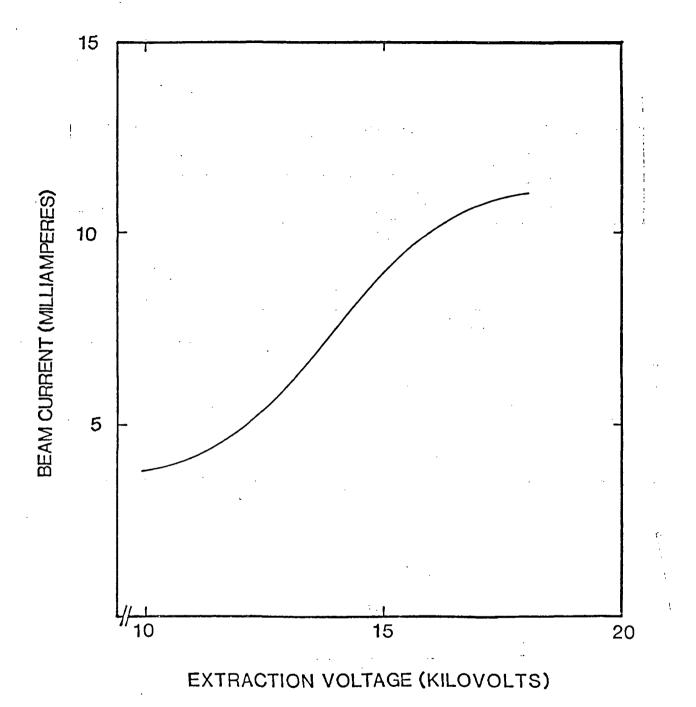

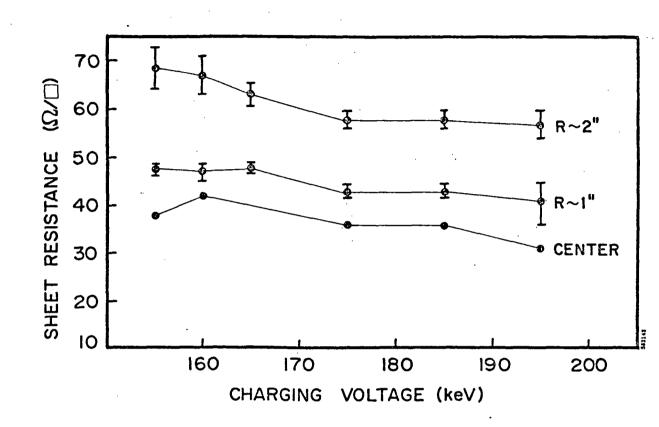

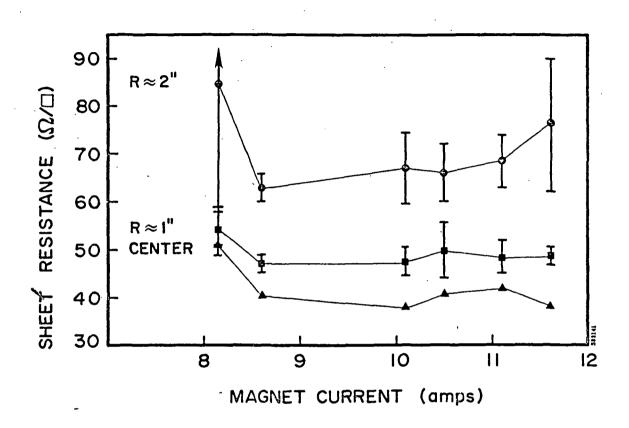

| 4-10   | Phosphorus Ion Current as a Function of Extraction Voltage             | 4-15 |

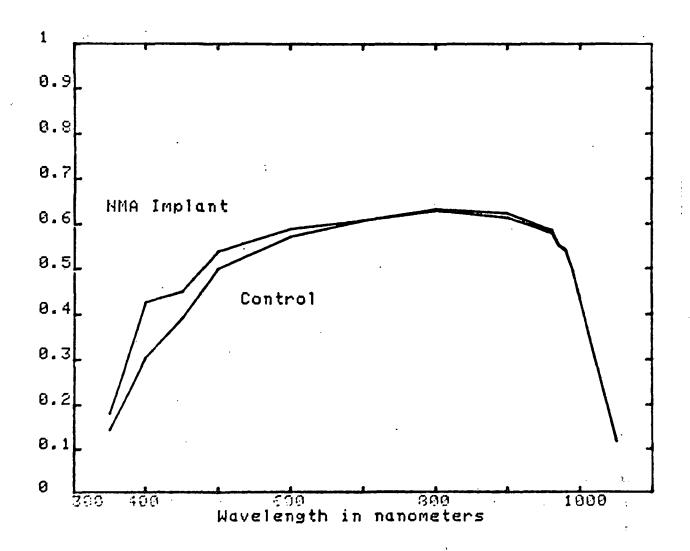

| 4-11   | Comparison of Quantum Efficiency for NMA Implant and Control           | 4-17 |

| 4-12   | Design Layout of NMA Ion Implanter                                     | 4-18 |

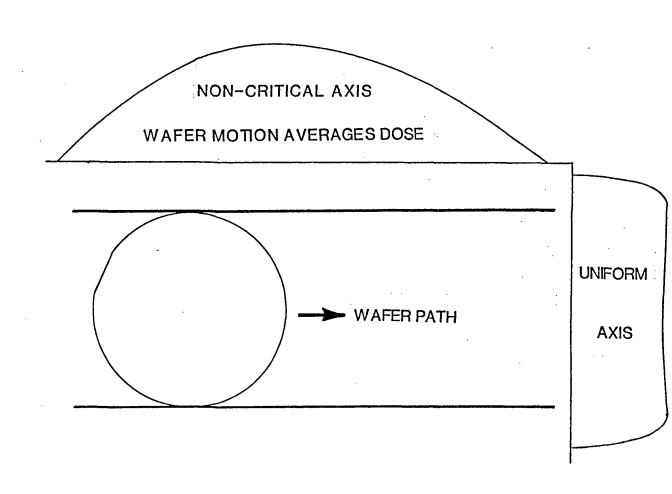

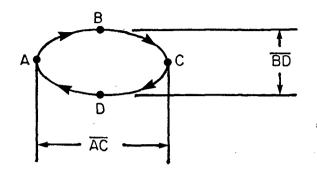

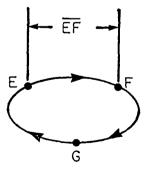

| 4-13   | Uniformity Requirements With Walking Beam Track                        | 4-20 |

### SECTION I INTRODUCTION AND SUMMARY

#### 1.1 OBJECTIVE

The overall objective of Spire's effort was to develop, construct and deliver to JPL a processing system capable of producing solar cell junctions by ion implantation followed by pulsed electron beam annealing. The machine was to be capable of processing 4-inch (101.6 mm) diameter single-crystal Czochralski wafers at a rate of 10<sup>7</sup> wafers per year (approximately 1 wafer every 2 seconds). An artist's conception of the junction processor is shown in Figure 1-1.

The wafers were to be P-silicon (boron) with a maximum bulk resistivity of 2 ohm-cm and maximum thickness of 0.010 inches (0.25 mm). The wafers were to be carried by a transport mechanism into and out of the vacuum chambers where the ion implantation and pulsed electron beam annealing processes take place.

Spire was to integrate, test and demonstrate the system prior to delivery; and detailed operating and maintenance manuals were to be prepared for the machine. Based on the manufacturing experience and other inputs, estimates of component lifetimes and costs were to be prepared. This information was to be used for a comprehensive analysis, in accordance with the Solar Array Manufacturing Industry Costing Standards (SAMICS), of the costs associated with the use of the junction processor.

#### 1.2 TASKS

The objectives of the program were to be satisfied by the performance of 5 tasks, each with a detailed set of subtasks.

#### 1.2.1 Task 1 - Development of Pulsed Electron Beam Subsystem

The pulsed electron beam subsystem was to be capable of annealing the damage caused by ion implantation into the crystalline lattice of 4-inch silicon wafers and of electrically activating the implanted dopant material. Before building the subsystem, however, Spire was required to select the optimum method of removing the ion

FIGURE 1-1. ARTIST'S CONCEPTION OF SPIRE/JPL JUNCTION PROCESSOR.

implantation damage among four alternatives: (1) single-pulse, full wafer coverage; (2) single-pulse, partial wafer coverage - liquid epitaxy with step-and-repeat to achieve full coverage; (3) multiple-pulse, full wafer coverage - solid epitaxy; and (4) multiple-pulse, partial wafer coverage - solid epitaxy with step-and-repeat to achieve full wafer coverage.

After determining the best pulsed electron beam annealing method, Spire was then to design and fabricate the pulsed annealer to satisfy the requirements presented above. The initial design was to be a "stand-alone" system whose operation could be demonstrated independently.

#### 1.2.2 Task 2 - Wafer Transport Development

Spire was to develop a wafer handling and transport subsystem capable of transporting 4-inch diameter silicon wafers through the junction processor at a rate of  $10^7$  wafers per year. The option was available for using single or batch (cassette) wafer transfer between the ion implantation and pulsed electron beam subsystems. The wafer transport system also was to include handling mechanisms for correctly orienting the wafers during the ion implantation and pulsed anneal processes as well as interlocked vacuum valves to prevent accidental loss of vacuum in the ion implanter and pulsed annealer subsystem.

#### 1.2.3 Task 3 - Ion Implanter Development

The initial objective of this task was to modify the Government-owned ion implanter, Varian/Extrion Model 200-100, located at Spire to be capable of processing 4-inch diameter silicon wafers at a rate of  $10^7$  per year. The ion implanter was to provide a fluence of at least  $2.5 \times 10^{15}$  ions/cm<sup>2</sup> of 10 keV phosphorous with a uniformity across the wafer of less than  $\pm 10\%$ .

Later in the program, it was determined that the best approach to this task was to develop a new ion implanter design utilizing a non-mass-analyzed (NMA) ion accelerator which would satisfy the technical requirements with reduced technical complexity and costs.

#### 1.2.4 Task 4 - Junction Processing System Integration

The pulsed electron beam annealer, wafer transport, and ion implanter subsystems developed in Tasks I, 2, and 3 were to be integrated, tested and demonstrated by processing wafers at the rated throughput. Selected wafers were to undergo sheet resistivity mapping by Spire and formed into solar cells. The performance of these solar cells were to be evaluated by Spire as a part of this task. Additionally, operating and maintenance manuals of the junction processing equipment were to be written.

#### 1.2.5 Task 5 - Junction Processing System Cost Analyses

Spire was to estimate component lifetimes and failure rates for the junction processing system as part of a cost analysis for the total system. The estimates were to be derived from established data sources and from experience gained during the development, integration and testing phases of the system. This information was to be used in a cost analysis of the junction processor performed in accordance with the Solar Array Manufacturing Industry Costing Standards (SAMIS).

#### 1.3 SUMMARY OF ACTIVITIES

#### 1.3.1 Task 1 - Development of Pulsed Electron Beam Subsystem

A series of annealing experiments showed that the optimum pulsed electron beam annealing technique was single-pulse, liquid epitaxy with full coverage over the 4-inch diameter wafer. The electron beam pulser design was then based on this method of annealing.

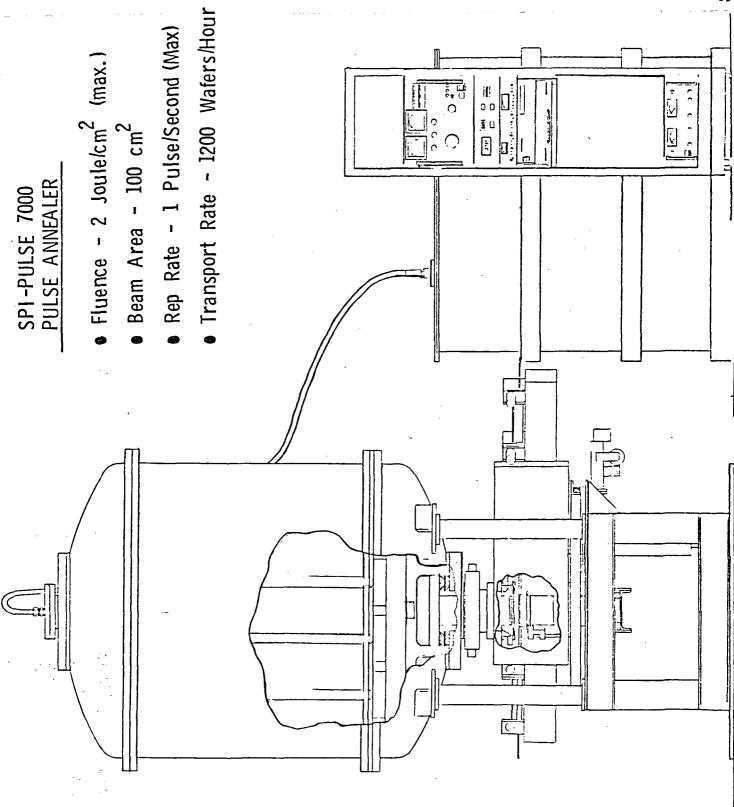

A pulsed electron beam annealer, designated SPI-PULSE 7000 was designed, fabricated and successfully tested at a rate of 1 wafer every 2 seconds. Single electron beam pulses were used to anneal 4-inch diameter ion implanted silicon wafers over their entire surface.

Surface resistivity maps were made of several pulse-annealed silicon wafers and solar cells made from the wafers. This information was presented in a report which is included in Appendix I. The cell characterization indicated that the AMI efficiency attainable with this technology is approximately 12% over a 4-inch wafer. This average efficiency could be improved by improvements in the metalization on the front of the cell.

#### 1.3.2 Task 2 - Wafer Transport Development

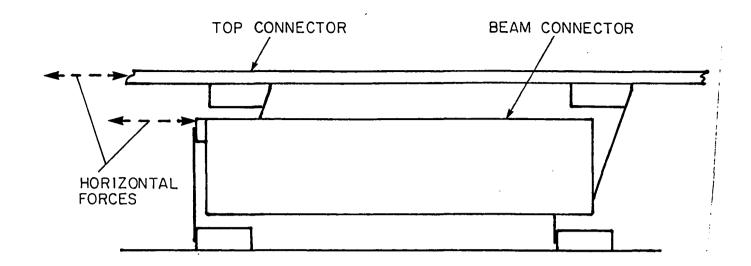

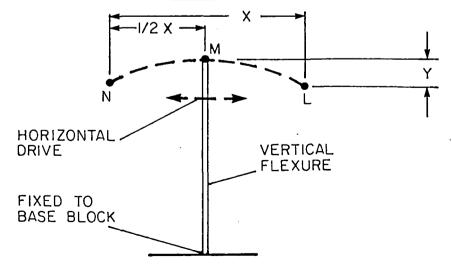

A vacuum-locked walking beam wafer transport was designed and built by a subcontractor to Spire, and the interim system was installed on the SPI-PULSE 7000 electron beam pulser. Spire designed and built cassette elevators and wafer input and output mechanisms for the transport and a wafer lifter device for the pulse annealing station. These systems were demonstrated to operate at a rate of I wafer every 2 seconds.

A vacuum-locked walking beam transport system was designed for the ion implanter subsystem which is compatible with the interim transport system of the pulsed annealer. Although detailed design drawings were made, no fabrication was initiated because of the termination of the junction processor development program.

#### 1.3.3 Task 3 - Ion Implanter Development

A series of experiments were conducted using an ion implanter test facility which demonstrated that a non-mass-analyzed (NMA) phosphorous ion implantation gives solar cell performance which is as good, if not better, than conventional, mass-analyzed ion implants. Based on these results, a new NMA ion implanter was designed and some components fabricated.

Beam control experiments were performed in the test facility and ion beam steering and defocusing demonstrated to satisfy the dose uniformity requirements across 4-inch diameter wafers.

Detailed drawings of all components of the ion implanter were made. The program was terminated after the fabrication of a limited number of the components.

#### 1.3.4 Tasks 4 and 5 - System Integration and Cost Analyses

The development program was terminated before the system integration and cost analysis could be performed. An operation and maintenance manual for the pulsed electron beam annealer was written and is included in Appendix 2 of this report.

## SECTION 2 TASK 1 - DEVELOPMENT OF PULSED ELECTRON BEAM SUBSYSTEM

#### 2.1 GENERAL

The development of the pulsed electron beam subsystem consisted of three subtasks. First, developmental testing to determine the best approach for annealing 100-mm diameter silicon wafers, electron beam control experiments, and wafer preheat experiments. Second, design and fabrication of the electron beam pulser. Third, testing and evaluation of the pulsed annealer subsystem, including large area annealing experiments, testing of pulser lifetime and reliability, and cell processing. Each of these subtasks was performed successfully.

#### 2.2 DEVELOPMENTAL TESTING

#### 2.2.1 Solid Phase Annealing Experiments

Experiments were carried out to determine the feasibility of pulse-annealing ion implantation damage by a series of low-fluence pulses from a large-area electron beam. This method of annealing would have the advantage of requiring a smaller beam energy per pulse than single-step, liquid-phase regrowth of the amorphous layer formed by ion implantation.

Using Spire's SPI-PULSE 5000 accelerator, it was found experimentally that multiple pulses by an electron beam with a fluence less than about 0.5 J-cm<sup>-2</sup> produced polycrystalline regrowth of the amorphous layer if the wafer was allowed to cool between pulses. Increasing the total fluence by using a pulse duration greater than 100 ns (up to 1 microsecond) resulted in damage to the wafer by surface cracking. This effect could be avoided only by heating the wafer to 300°C or greater during the pulse annealing process.

Based on these experiments, it was concluded that solid-phase annealing by a series of short, low-fluence pulses or by single, low-power pulses of microsecond duration is not practical for the pulsed electron beam processor. Liquid-phase annealing, on the other hand, has been demonstrated conclusively to form solar cell junctions which are of nearly equal performance to those formed by furnace annealing.

#### 2.2.2 Overlapping of Pulse-Annealed Regions

An experiment was conducted to evaluate the effect of overlapping high-fluence pulses of electrons on ion-implanted silicon solar cell junctions. The experiment simulated the conditions which would be encountered in the fabrication of solar cells which were annealed by multiple pulses of overlapping electron beams. Wafers of 10-ohm-cm, p-type silicon were implanted with  $2.5 \times 10^{15} \, \text{cm}^{-2}$  of 10-keV  $^{31} \text{p}^{+}$  ions and pulse annealed at a fluence of  $1 \, \text{J-cm}^{-2}$ . Half the wafers were subjected to a second pulse of the same fluence. The annealed regions of the wafers were then formed into  $2 \times 2$ -cm solar cells and the voltage-current characteristics of the cells were measured under AMO illumination. For test purposes, these cells were not constructed with an antireflection coating or a back-surface-field structure. The efficiency of the single- and double-pulsed cells was as follows:

|          | Single-Pulsed Cells |  |  |  |

|----------|---------------------|--|--|--|

| Cell No. | Efficiency (%)      |  |  |  |

| l        | 8.1                 |  |  |  |

| 2        | 8.3                 |  |  |  |

| 3        | 8.2                 |  |  |  |

|          | Double-Pulsed Cells |  |  |  |

| 4        | 6.7                 |  |  |  |

| 5        | 6.7                 |  |  |  |

| 6        | 6.3                 |  |  |  |

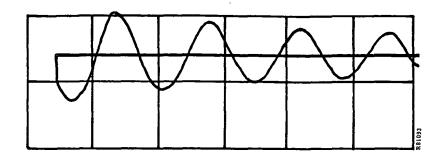

The voltage-current characteristics of cells No. 3 and No. 4 are shown in Figure 2-1. The efficiency of the single-pulsed cells, although low because the cell formation process was not optimized, is clearly greater than the efficiency of the double-pulsed cells. The loss of efficiency is attributed to increased junction depths and damage from thermal stresses caused by the second pulse onto the already annealed structure of the cell. It seems clear from these and earlier experiments at Spire that solar cells with large overlapping areas of pulsed electron beam annealing would be inferior to single-pulsed cells.

FIGURE 2-1. VOLTAGE-CURRENT CHARACTERISTICS OF SINGLE-AND DOUBLE-PULSE ANNEALED SOLAR CELLS.

We have also observed that implanted wafers annealed by several abutting, nonoverlapping pulses have a high risk of shorting the photovoltaic junction. The shorting occurs along grain boundaries of the polycrystalline region which is formed at the low-fluence edge of the pulsed electron beam. Complete regrowth of the polycrystalline region between the abutting areas would require special processing which would greatly increase the cost and complexity of the annealer.

We concluded from these tests that the use of a single pulse of electrons to cover the entire surface of the wafer is the preferable technique for pulse annealing in the junction processor. On this basis, we made the decision to develop a pulsed electron beam subsystem which is capable of annealing 10-cm-diameter wafers in a single pulse.

#### 2.2.3 Beam Control Experiments

With pulsed electron beam currents approaching 50 kA in the annealer, the conduction of this current away from the wafers during the annealing step is an important design consideration. If the electron beam could propagate in a low-density plasma, partial space charge and current neutralization of the beam would be provided by the low-energy ions and electrons in the plasma. Thus a lower net current would be carried to the surface of the wafer.

A series of experiments was performed on the SPI-PULSE 5000 in which argon gas was introduced into the diode region of the pulser. Modifications to the standard carousel vacuum-process chamber met the experimental requirement of maintaining a controlled and measured gas pressure in the diode region.

The argon was leaked into the back of the chamber through an ultrafine needle valve. The diffusion pumps were throttled down to maintain steady pressure values from 0.1 to 40 microns. The pressure was measured using a McLeod gauge for the higher pressure values and a calibrated thermocouple gauge for values below 10 mTorr.

Before conducting experiments, the effect of the gas pressure on the beam was measured. Diode voltage and current monitor traces were used to determine the peak voltage, current and voltage pulse width, as shown in Figure 2-2. A carbon calorimeter

FIGURE 2-2. BEAM PARAMETERS VERSUS GAS PRESSURE.

was used to measure the fluence on the beam axis, and ion-implanted test wafers were used as witness plates to determine the beam profile. At a "maximum" pressure the charging voltage and magnetic field were varied to obtain a uniform anneal for constant fluence experiments.

Experiments were first performed using a standard 2-inch-beam setup with a 90 mil anode-to-cathode gap and a sample spacing of 5 mm. Calorimetry data was taken for pressures from 0.5 to 14 mTorr at a 150 kV charging voltage. The uppermost curve in Figure 2-2 presents the results of this data. Test wafers were shot at high vacuum, then at argon pressures from 6 to 22 mTorr. The high-vacuum anneal showed some weak spots. At 6 mTorr a weak center surrounded by an annular annealed region appeared and grew until fluence was almost totally lost at 22 mTorr. The outline of the anneal became more circular at 8 mTorr and remained so for higher pressures. These experiments showed that with an argon background gas, process chamber pressures higher than 14 mTorr would result in loss of useful beam fluence. Even though these experiments did not show a significant improvement in beam uniformity with increased diode gas pressure, another variable for beam control was identified to match the pulse generator load for large diode gaps.

#### 2.2.4 Wafer Preheat Experiments

During ion implantation in a large-volume production line, the wafers would be heated to temperatures close to 100°C by the ion beam. Since this heating could influence the pulse annealing process, a number of experiments using a specially designed infrared wafer heater were conducted. The SPI-PULSE 5000 accelerator was used to carry out these tests. The infrared substrate heater allowed the test wafers to be heated in vacuum to temperatures through 400°C with only a 1°C per second temperature drop after heater turnoff. Early tests indicated that preheating followed by a cooldown period before pulsed electron beam annealing does not offer any advantage. However, wafers directly annealed by a pulsed electron beam while hot showed a somewhat more uniform anneal. Finished cell characteristics were identical for wafers pulsed cold or heated, if followed by a 400°C contact sinter. Further preheat testing is necessary to determine whether preheat may raise the damage threshold level. As a result of these experiments, no specific provisions for wafer preheating were included in the design of the pulsed electron beam annealer.

#### 2.3 PULSER DESIGN AND FABRICATION

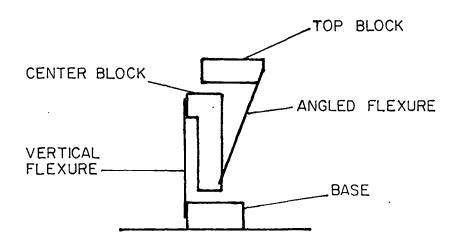

Based on the results of the developmental experiments, the pulsed electron beam subsystem, designated SPI-PULSE 7000, was designed and fabricated. The pulser includes an electron accelerator which can be discharged once every 2 seconds for single-pulse annealing of 10-cm-diameter silicon wafers. An interim wafer handling system was also designed and built (see Section 3) to move wafers into and out of the vacuum chamber which houses the electron accelerator and beam control apparatus.

#### 2.3.1 Design Calculations

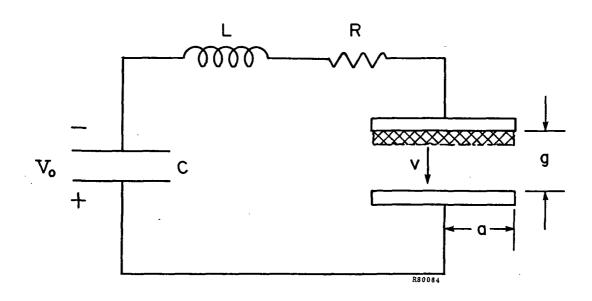

The electrical parameters of the pulsed annealer were investigated using a simple computer model which has been shown to predict the operation of existing accelerators at Spire rather closely. Lumped circuit parameters were used to model the pulser system, and the electron beam accelerator was represented as a space-charge-limited diode with an anode-cathode gap which closes at constant speed. The circuit model used in the calculations is shown in Figure 2-3, where R, L, C and V<sub>o</sub> are, respectively, the series resistance, inductance, capacitance and initial charging voltage of the capacitor. The field-emission diode has a radius, a, a gap, g, and an expansion velocity of the cathode plasma, v.

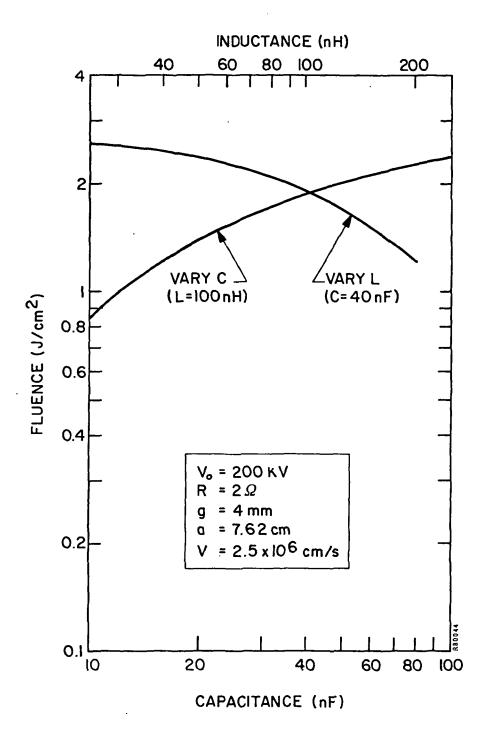

Results of calculations of the energy fluence at the surface of a 10-cm-diameter wafer as a function of store capacitance (inductance held fixed) and series inductance (capacitance held fixed) is shown in Figure 2-4. The crossover point at a fluence of 1.8 J-cm<sup>-2</sup> is the design-point chosen for the SPI-PULSE 7000. The computer model indicates that the average energy of the electrons is 18.6 keV under these conditions.

On the basis of the computer calculations and the past experience at Spire in annealing smaller diameter wafers, the electrical parameters chosen for the SPI-PULSE 7000 are as follows:

Total Capacitance:

40 nF

Front-End Inductance:

100 nH (approx.)

Maximum Charging Voltage:

300 kV

FIGURE 2-3. LIMITED PARAMETER CIRCUIT MODEL OF PULSED ELECTRON BEAM ANNEALER.

FIGURE 2-4. RESULTS OF ELECTRICAL MODELING OF PULSED ELECTRON BEAM ANNEALER.

Operating Charging Voltage: 200 kV

Maximum Charging Current: 15 mA

Pulse Repetition Rate: 0.5 to 1 s<sup>-1</sup>

#### 2.3.2 Design of Energy Store

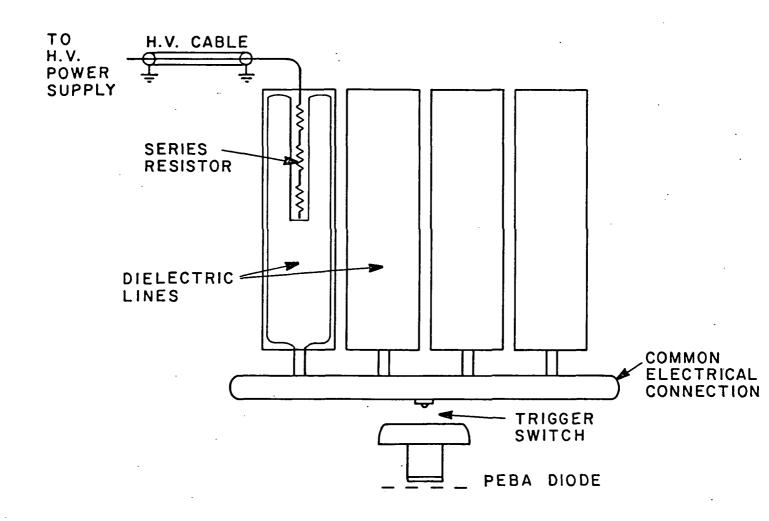

Because of the high charging voltages and the low circuit inductance required in the pulser, we decided to break down the energy store into several separate capacitors charged and discharged in parallel. A schematic diagram of this arrangement is shown in Figure 2-5. The modular nature of the energy store gives the possibility of varying circuit parameters and eases the problems of mechanical assembly and disassembly.

The capacitive energy store consists of as many as 19 parallel-charged transmission lines. The characteristics of the individual lines are as follows:

| Capacitance:          | 2.9 nF           |

|-----------------------|------------------|

| Inductance:           | 14.2 nH          |

| Electrical Length:    | 104 cm           |

| Overall Length:       | 135 cm           |

| Diameter:             | 24.1 cm          |

| Dielectric Thickness: | 0 <b>.</b> 79 cm |

The dielectric material of the line is a high-strength epoxy which is cast around an aluminum cylinder, the central electrode of the coaxial line. The outer conductor is a conductive coating placed on the dielectric after casting.

The lines are placed vertically in a hexagonal arrangement in a vessel which is pressurized with dielectric gas. The capacitor array is charged by a high-voltage electronic power supply and discharged into the accelerator by a mechanically actuated switch as shown in Figure 2-5.

FIGURE 2-5. SCHEMATIC OF MULTIPLE-LINE ENERGY STORE AND PARALLEL CHARGING AND DISCHARGING SYSTEMS.

#### 2.3.3 Pulser Subsystem Design

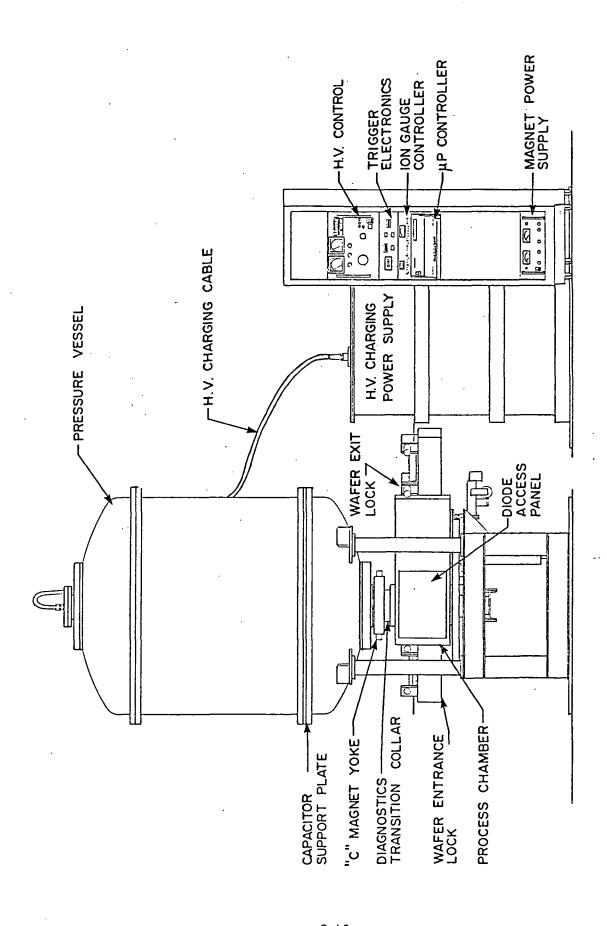

The major elements of the pulsed electron beam subsystem are shown schematically in Figure 2-6. The pressure vessel contains the capacitative energy store discussed in Section 2.3.2; the vacuum process chamber contains the electron beam diode, the magnetic beam guiding structure, and the wafer handling and transport mechanism. Figure 2-7 is a functional block diagram of the elements of the subsystem; all of these elements were designed to be controlled by a microprocessor controller.

#### 2.3.4 Pulser Subsystem Fabrication and Assembly

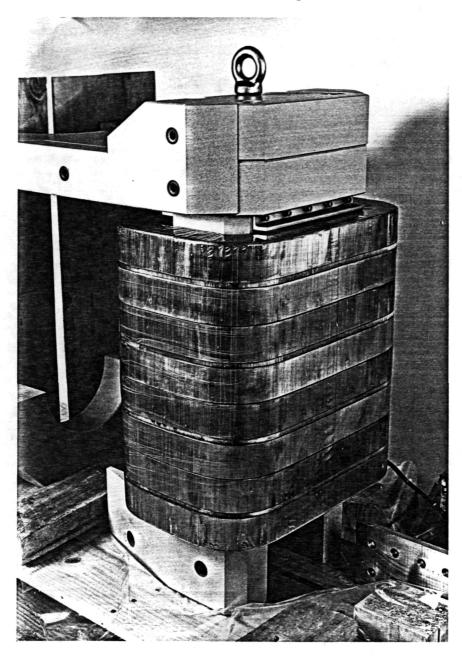

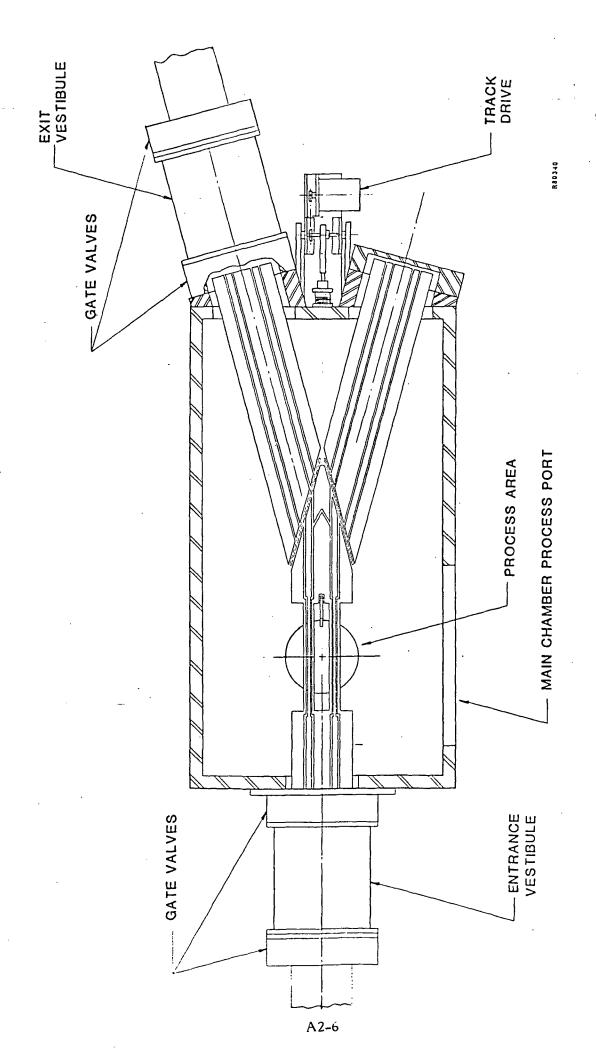

Following the design computations and a number of experimental verifications of design principles, the pulsed electron beam subsystem and an interim wafer transport system were designed and fabricated. The transport systm is described in Section 3. Figure 2-8 shows the pulser subsystem after all components were fabricated and assembled. An interior view of the processing chamber, Figure 2-9, shows one of the pole pieces of the beam guiding field electromagnet (center), a part of the wafer transport track (sides), lifter mechanism (center), and the anode structure (above) of the electron beam accelerator diode. Figure 2-10 shows the guiding field electromagnet coil and yoke before assembly on the pulser. The electromagnet is located behind the vacuum chamber and is not visible in Figure 2-8.

#### 2.3.5 Pulser Subsystem Testing

The pulsed electron beam annealer is comprised of seven separate subsystems. These are the vacuum system, wafer transport, insulating gas supply for the high voltage tank, magnet and its power supply, high voltage power supply, diagnostic equipment and electronic controls. Each subsystem was tested both separately and under coordinated operation. The microprocessor control system was used for all tests. It was not adversely affected by triggering of the pulse generator or operation of any other part of the pulser system.

#### Vacuum System

Full operation of the cryopumped vacuum system was accomplished with an average indicated pressure in the process chamber at  $2 \times 10^{-6}$  torr. Pressures in the  $10^{-7}$  torr range were commonly measured after a few hours of pumping.

FIGURE 2-6. SPI-PULSE 7000 SCHEMATIC DIAGRAM.

FIGURE 2-8. PHOTOGRAPH OF SPI-PULSE 7000 PULSED ELECTRON BEAM SUBSYSTEM.

FIGURE 2-9. VIEW THROUGH FRONT PORT OF WAFER PROCESSING CHAMBER.

## ORIGINAL PAGE IS OF POOR QUALITY

FIGURE 2-10. BEAM GUIDING FIELD COIL AND YOKE BEFORE ASSEMBLY OF PULSER SUBSYSTEM.

THIA . WOR TO

#### Interim Wafer Transport

The interim wafer transport, described further in Section 3, and the mechanism to lift the wafers into place for pulsed annealing were demonstrated to operate at a rate of one wafer every 3 seconds. The magnetic field in the region of the lifter causes no adverse effects on the operation of the transport.

#### Insulating Gas System

The energy store and high-voltage switch were designed to operate with 100 psi of insulating gas. A mixture of nitrogen and carbon dioxide was found to give satisfactory charging and switching at voltages up to 180 keV. The addition of a few percent of  $SF_6$  was required to prevent arcing at voltages above 180 kV.

#### Magnetic Field System

The magnet was tested for power consumption, cooling and field strength. This system is required for uniform electron beam irradiation of the samples. The maximum field is limited by saturation effects, particularly above 2.5 kG. However, annealing experiments have shown that the optimal field is below 2 kG. At this 2 kG level the magnet draws only 130 watts, significantly below the 3 kW first estimated for this subsystem in an early SAMICS analysis of the pulsed electron beam annealer. This represents a significant savings in total power and cooling requirements.

#### High-Voltage Power Supply

The first high-voltage power supply for the pulser was tested up to its maximum, no-load voltage rating of 180 kV. At 160 kV, this power supply had a demonstrated output of 5 mA. Later in the program, this power supply was replaced by a 300 kV, 17 mA unit so that tests at higher charging voltages could be performed. The new supply performed satisfactorily over all of its voltage and current range.

#### Beam Diagnostics

Diagnostic equipment for the electron beam pulser includes diode voltage and current monitors and an electron beam calorimeter. The diode voltage monitor, a capacitive voltage divider measured directly on the diode "shank", was calibrated using a

low-voltage pulser and found to have a calibration factor of 1710 volts per signal volt output. The current monitor, which uses a chain of shunt resistors in the diode current path, was measured to have a calibration factor of 73 amperes per signal volt.

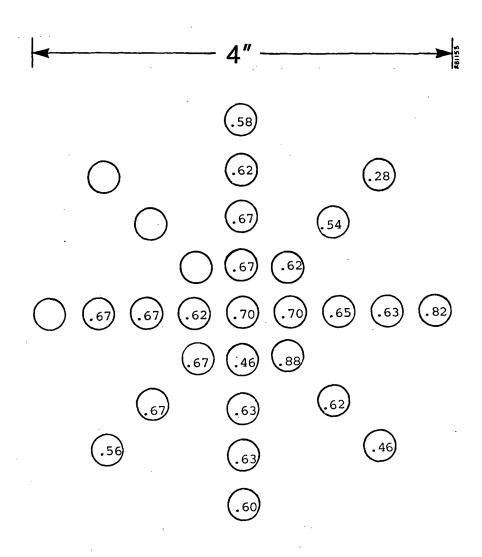

The calorimeter consists of 29 disks arranged in the pattern shown in Figure 2-11. When irradiated by the electron beam, the disk rises in temperature about 4-6°C and cools slowly with typical time constants exceeding 8 seconds. The disks are within  $\pm 5\%$  of the average calibration which is corrected for energy radiated away when the surface temperature is high, immediately after the pulse. Carbon is the only material which can be used which will not melt or spall from this radiation.

The calorimeter has an electronics package which multiplexes the readout from 25 probes for digitization every 0.5 seconds. The signal from the probes is grounded on one side in three places and filtered to remove RF noise. The digitized signals are analyzed by a microcomputer which extrapolates the temperature profiles to time zero, accounting for average initial readings and the varying delay in the multiplexer. A sample of the corrected data from the computer is shown in Figure 2-11.

#### 2.3.6 Pulse Generator Tests

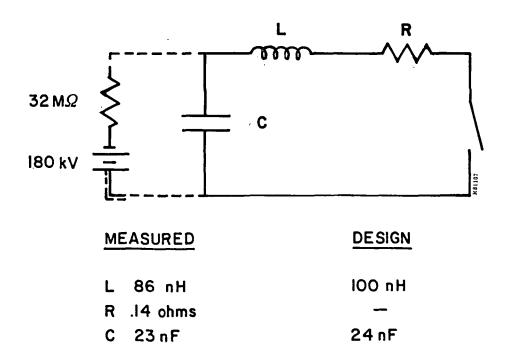

Tests of the electrical characteristics of the pulse generator were conducted by shorting the electron beam diode through a plate with minimal inductance. Figure 2-12(a) shows a typical signal on the diode current monitor under this condition. This trace can be used to define the equivalent electrical parameters of the pulse generator, using the LRC circuit model shown in Figure 2-12(b). The current follows an equation of the form:

$$I = I_0 \exp [-(R/2L)t] \sin [(LC)^{1/2} t]$$

where the exact solution to the circuit model was simplified, since  $(L/R)^2 >> LC$ . Here L is the total inductance of the pulse generator with the largest contribution from the switch and collector plate. The total capacitance C is that of the energy store plus stray contributions. The total resistance R is believed to be mostly from the arc in the switch.

# AVERAGE READING ON ALL POINTS .64±.09 J/cm<sup>2</sup>

FIGURE 2-11. CALORIMETER ARRAY AND READOUT.

FIGURE 2-12(a). CURRENT SIGNAL FROM PULSE GENERATOR WITH THE DIODE SHORTED; 50 kV CHARGE, 34.5 kA/div, 50 ns/div.

FIGURE 2-12(b). EQUIVALENT CIRCUIT MODEL FOR PULSE GENERATOR WITH MEASURED PARAMETERS FROM (a).

The parameters R, L and C were determined from Figure 2-12(a), giving the total charge initially in the energy store (corrected for experimental decay) and the value of C = 23nF ( $\pm 5\%$ ). The period of the oscillation is 280 ns ( $\pm 5\%$ ), which is equal to 2 (LC)  $^{1/2}$ , or L = 86 nF ( $\pm 10\%$ ). The total resistance was determined from measurement of successive peaks on the curve, and R = 0.14 ohms ( $\pm 10\%$ ). These values are close to the design parameters of 24 nF (8 storage lines) and 100 nH.

#### 2.3.7 Electron Beam Diode Tests

The first setup used for diode tests was determined by the original design model (see Section 2.3.1). Diode parameters were then varied in a stepwise approach to the optimum electron beam required for annealing.

The variable parameters are cathode radius, cathode-anode gap, sample-anode gap, applied magnetic field and charging voltage on the energy store. Table 2-1 lists the variations of these parameters during the test of the diode.

TABLE 2-1. PARAMETRIC MATRIX FOR DIODE TESTS

| Exp't | Cathode radius (in.) | Cathode-<br>anode gap<br>(in.) | Sample<br>anode gap<br>(in.) | Magnet<br>field<br>(kG)            | Charging<br>voltage<br>(kV) |

|-------|----------------------|--------------------------------|------------------------------|------------------------------------|-----------------------------|

| 1     | 6                    | 0.098<br>0.197                 | 0.092<br>0.215               | 0 2.0                              | 25, 50,<br>100, 125         |

| 2     | 4                    | 0.116                          | 0.188                        | 0, 1.6                             | 25, 50,<br>100, 125         |

| 3     | 4                    | 0.092, 0.110<br>0.135          | No anode                     | 0, 2.0                             | 140                         |

| 4     | 4                    | 0.098                          | 0.212<br>0.171               | 0, 0.18,<br>0.36, 0.72<br>1.0, 2.0 | 140, 150<br>160             |

| 5     | 4.5                  | 0.108                          | 0.171                        | 0.7, 1.0                           | 150, 160<br>170, 180        |

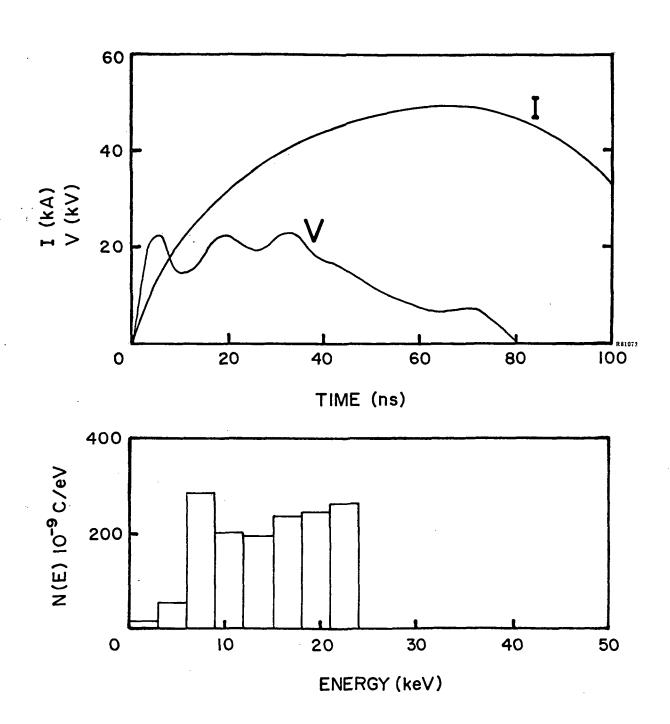

An example of the beam voltage and current traces and the electron beam energy spectrum determined from them (corrected for inductive effects) is shown in Figure 2-13. The average energy of the electrons is about 13 keV.

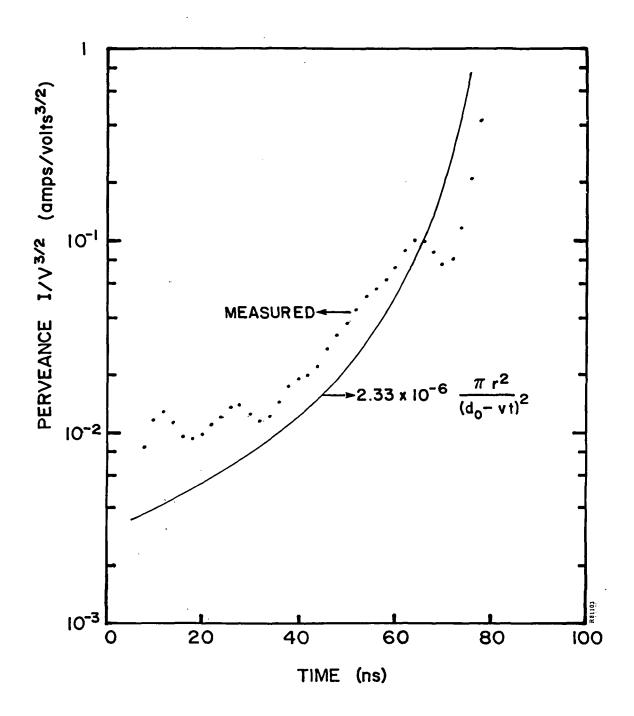

Correct functioning of the diode was verified by measurements of beam perveance. The perveance is defined as  $I/V^{3/2}$ , and is a geometrically determined quantity for planar, nonrelativistic, space-charge-limited electron beam diodes. For MKS units (amperes, volts, meters) its value is given by:

$$I/V^{2/3} = 2.33 \times 10^{-6} \pi r^2/d^2$$

where I and V are the diode current and voltage, respectively, r is the cathode radius, and d is the cathode-anode gap. As shown in Figure 2-14, the perveance is a time-dependent function. This arises from the plasma which forms at the cathode at the start of the pulse and drifts to the anode at nearly constant velocity. In higher power diodes a plasma may also form at the anode and drift in the opposite direction. Thus the value of the cathode-anode gap should be written as:

$$d = d_o - vt$$

where  $d_0$  is the initial gap, v is the closure velocity due to plasma drift and t is time. The value of v is approximately 2.5 x  $10^4$  m/s, and the theoretical curve is plotted in Figure 2-14 using this value. Agreement between the curves indicates that the diode is operating as expected.

The successful demonstrations of the operation of the electron beam pulse subsystem allowed the commencement of silicon wafer annealing experiments discussed in Section 2.4.

#### 2.4 ANNEALING EXPERIMENTS

As soon as the pulser was capable of forming an electron beam, experiments on annealing ion implantation damage in silicon wafers were initiated. Two general types of experiments were conducted, "qualitative" and "quantitative". The qualitative tests involved literally hundreds of electron beam pulses onto ion implanted silicon wafers for approximate optimization of the accelerator parameters. The change of the shiny

FIGURE 2-13. TYPICAL CORRECTED DIODE VOLTAGE, CURRENT AND ELECTRON ENERGY SPECTRA FROM COMPUTER CODE EBSPEC.

FIGURE 2-14. MEASURED AND MODELED DIODE PERVEANCE FOR PULSE SHOWN IN FIGURE 2-13.

amorphous surface to the characteristic blue-gray color of crystalline silicon gave a good qualitative indication of the size and uniformity of the beam. Visually apparent surface damage on the wafer indicated "hot spots" in the electron current density.

Quantitative tests involved mapping of the surface resistivity of the annealed wafer and, in many cases, the actual formation and characterization of solar cells. The quantitative tests were performed only after the electron beam parameters appeared to be optimized qualitatively. For brevity, only the quantitative tests will be discussed here.

# 2.4.1 Preliminary Experiments

Samples for the initial annealing tests were 100 mm diameter silicon wafers with a polished surface and as-cut backs, 0.020 inch thick. They were cleaned, implanted with 2.5 x  $10^{15}$  ions/cm<sup>2</sup> of 10 keV phosphorus, cleaned a second time and delivered to the junction processor test station. Typical wafer resistivity was 10 ohm-cm. Some samples with etched surfaces, 0.013 inch thick and 1 ohm-cm were tested to see the effects of different wafer parameters.

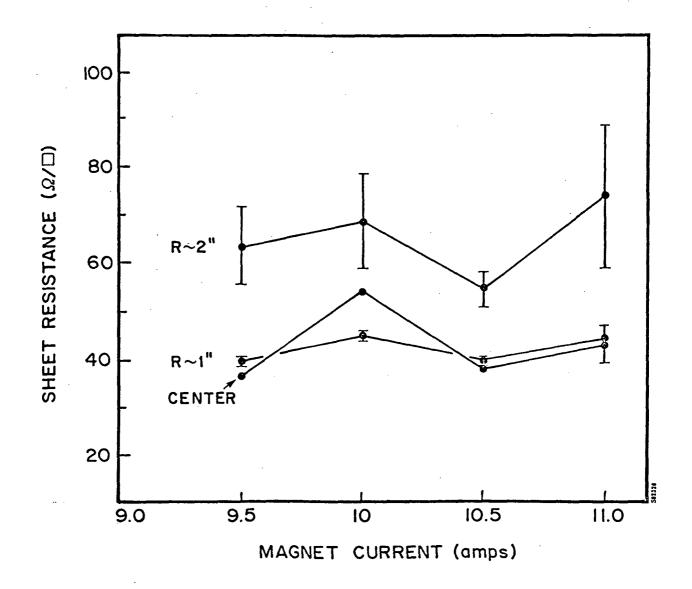

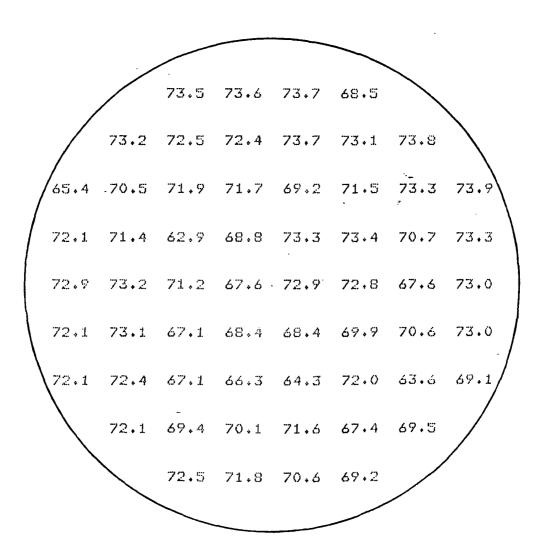

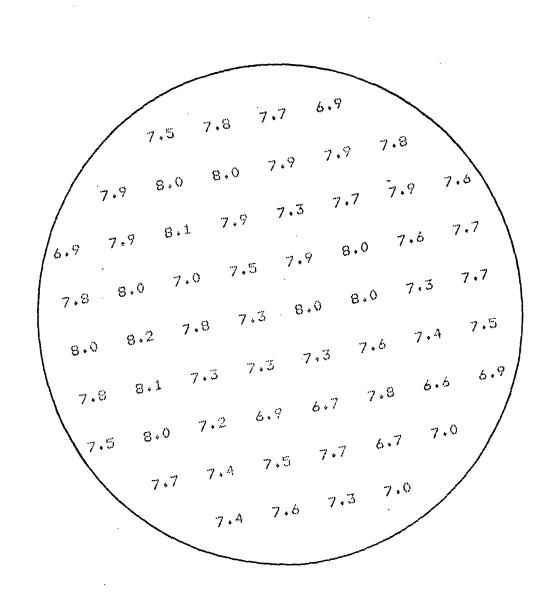

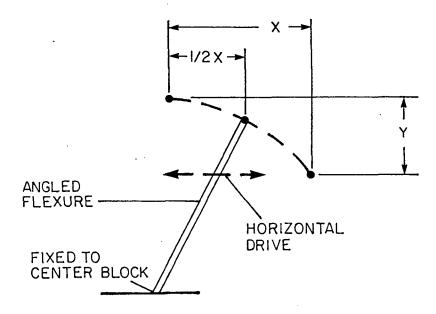

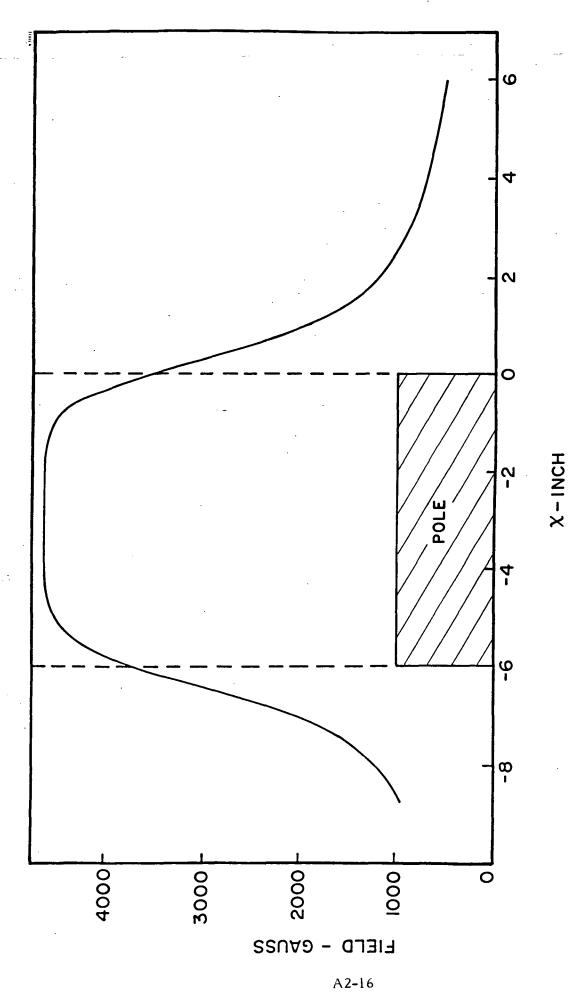

These samples showed small-scale non-uniformities (typical spatial variation approximately 1 mm) which would not show on calorimeter tests. The entire surface of a wafer pulsed at a magnetic field of 1.2 kilogauss was annealed, however, there was some surface damage, believed to be slip in the worst case, in the center of the wafer. At a magnetic field of 2.6 kilogauss, the surface was uniformly spotted with small areas of damage adjacent to small areas (approximately 1 mm o.d.) of unannealed material. The fine scale variations in the beam fluence were caused largely by shaddowing by the wire structure of the anode mesh. There were no apparent differences in the results for the wafers with other surface, thickness or resistivity parameters.