# **General Disclaimer**

# One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some

of the material. However, it is the best reproduction available from the original

submission.

Produced by the NASA Center for Aerospace Information (CASI)

IN- (1+6)

JPI PUBLICATION 84-83

(NASA-CR-175662) PROCEEDINGS OF THE COLD ELECTRONICS WORKSHOP (Jet Propulsion Lab.) 108 p HC A06/MF AC1 CSCL 090

N85-24220 THRU N85-24226 Unclas

G3/33 14789

# Proceedings of the Cold Electronics Workshop

October 4-5, 1983 Pasadena, California

E. Tward R. Kirschman Editors

November 15, 1984

Prepared for

Department of the Navy Office of Naval Research

Through an Agreement with

National Aeronautics and Space Administration

by

Jet Propulsion Laboratory

California Institute of Technology

Pasadena, California

# Proceedings of the Cold Electronics Workshop

October 4-5, 1983 Pasadena, California

E. Tward R. Kirschman Editors

November 15, 1984

Prepared for

Department of the Navy

Office of Naval Research

Through an Agreement with

National Aeronautics and Space Administration

by

Jet Propulsion Laboratory

California Institute of Technology Pasadena, California This publication was prepared by the Jet Propulsion Laboratory, California Institute of Technology, under a contract with the National Aeronautics and Space Administration.

### ABSTRACT

The Proceedings of the Cold Electronics Workshop held at the Jet Propulsion Laboratory on October 3 and 4, 1984 are documented. Papers presented and discussions centered on the benefits and problems of the use of cold semiconductor electronics and the research and development effort required to bring cold electronics into more widespread use.

The report includes an overview of the status of cold electronics usage and research, summaries of the invited presentations and workshop discussions, recommendations for future research and development and copies of papers which were submitted by the invited speakers.

#### PREFACE

This report documents the proceedings of the Cold Electronics Workshop held at the Jet Propulsion Laboratory in Pasadena, California on October 4 and 5, 1983. The workshop was sponsored by the Office of Naval Research through Dr. E. A. Edelsack and by the Jet Propulsion Laboratory. The opinions, findings and conclusions expressed are those of the authors solely, who have attempted to represent to the best of their ability the discussions of the participants.

The workshop was organized in four half-day sessions and included presentations by invited speakers on a variety of relevant topics. Following the presentations, three topical discussion sessions and a final main discussion session were held in order to ascertain the viewpoints of the participants with respect to the potential for significant technical progress in cold electronics and the research and development efforts required for this progress to be achieved.

Because of the nature of the meeting, it was not advertised. All participants were invited personally by the undersigned, who takes all the blame for being unaware of other worthy contributors. The success of the meeting is due to the 65 participants whose efforts are gratefully acknowledged. I especially wish to thank Mrs. Genevieve McKay for her excellent help in organizing the conference.

E. Tward Conference Chairman

# CONTENTS

| I.         | INT | RODUCTION 1                                                                                                                                                                                                                                                                                 |   |  |  |  |  |

|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|

| II.        | COL | D ELECTRONICS - AN OVERVIEW 3 V                                                                                                                                                                                                                                                             | / |  |  |  |  |

|            |     | R. Kirschman                                                                                                                                                                                                                                                                                |   |  |  |  |  |

| III.       | SUM | MARY OF PRESENTATIONS                                                                                                                                                                                                                                                                       |   |  |  |  |  |

| IV.        | SUM | MARY OF THE DISCUSSION SESSIONS 260                                                                                                                                                                                                                                                         |   |  |  |  |  |

|            |     | A. Silver                                                                                                                                                                                                                                                                                   |   |  |  |  |  |

| ٧.         | NEE | DED RESEARCH AND DEVELOPMENT                                                                                                                                                                                                                                                                |   |  |  |  |  |

| APPENDICES |     |                                                                                                                                                                                                                                                                                             |   |  |  |  |  |

|            | A.  | COLD ELECTRONICS WORKSHOP PROGRAM 330                                                                                                                                                                                                                                                       |   |  |  |  |  |

|            | В.  | LIST OF PARTICIPANTS 350                                                                                                                                                                                                                                                                    |   |  |  |  |  |

|            | С.  | WRITTEN CONTRIBUTIONS OF SPEAKERS 39                                                                                                                                                                                                                                                        |   |  |  |  |  |

|            |     | <ol> <li>Recent Developments in Semiconductor Research</li> <li>M. Yoder, Office of Naval Research 40</li> </ol>                                                                                                                                                                            | _ |  |  |  |  |

|            |     | <ol> <li>Physical Electronics of Cooled Operation of<br/>Very Short Compound Semiconductor Transistors         <ul> <li>F. Eastman, School of Engineering,</li> <li>Cornell University and National Research<br/>and Resource Facility for Submicron<br/>Structures.</li> </ul> </li> </ol> |   |  |  |  |  |

|            |     | 3. The Effects of Cooling on Delay-Time Limits in IC's R. Grondin and D. K. Ferry, Center for Solid State Electronics Research, Arizona State University                                                                                                                                    | / |  |  |  |  |

|            |     | 4. Si MOS Devices at Low Temperatures A. Kamgar, AT & T Bell Laboratories 83                                                                                                                                                                                                                | / |  |  |  |  |

|            |     | 5. Cryogenically-Cooled, Low-Noise Receivers Present Status and Future Needs S. Weinreb, National Radio Astronomy Observatory                                                                                                                                                               | / |  |  |  |  |

#### I. INTRODUCTION

Cooling of electronics to cryogenic temperatures is a commonly used procedure in a number of scientific areas. Semiconductor devices have been operated below room temperature to temperatures as low as 1 K. Superconducting devices are operated at temperatures below approximately 20 K where the phenomenon of superconductivity exists. The Cold Electronics Workshop focussed on the use of semiconductor devices at cryogenic temperatures and did not discuss superconductivity.

The meeting was held because it was apparent to the organizers that there was no common forum for discussion for both the users of cold electronics and those wishing to advance the state of the art in this field. The users in fields such as radio astronomy, infrared sensing and nuclear physics have themselves traditionally found a way to satisfy their special needs for essentially special purpose devices. These applications make use of cold semiconductor devices to take advantage of either low noise properties or the need for close coupling of the devices. For some applications, e.g., infrared sensing, the sensors themselves must be cooled as well and therefore an independent cooling system for the electronics is not required. For other applications, e.g., microwave receivers, the antennae are warm but the front end receivers are cooled and therefore require their own cooling systems.

The formal presentations and workshop discussions attempted to cover the field of cold electronics as broadly as possible. The topics addressed included novel fabrication techniques, new promising devices (e.g., HEMT), the status of cold Si devices, refrigeration, and the needs of users. A copy of the program is appended in Appendix A. The invited participants were drawn from industry, government laboratories and academia. A list of attendees is appended in Appendix B. Included in Appendix C are papers or summaries of presentations from the presenters who responded to the seductive entreaties of the editors to do more than their initial commitment to speak. Their additional efforts in providing these materials are gratefully acknowledged.

The broad scope of the program reflects the situation of a field in its infancy, with great promise for technical pay-off and wide ranging opportunity and need for research and development. The technical promise of cold electronics lies in its potential for yielding improved performance and reliability. For example, for VLSI devices, lowering operating temperatures can provide increased speed due to higher carrier mobilities, lowered interconnection resistances, improved heat removal, lowered power dissipation, and orders of magnitude improvement of reliability due to reduction of thermally activated degradation mechanisms. For many IR sensor applications, low noise requirements of amplifiers dictates the use of low temperatures. For microwave receivers high frequency response and low noise are

prime considerations for applications in radio astronomy.

In any event, in most applications where cold electronics is in use or is being considered for use, the enhancement of device characteristics results from the basic improved physical properties of the materials at low temperatures. For this reason there is a great need for basic research into the properties of materials as well as device design and engineering for low temperature operation.

In order to put into context the present status of the field, we include in the report an overview of cold electronics which includes a bibliography as a starting point for those who wish to investigate the field in greater depth.

# DI

#### II. COLD ELECTRONICS - AN OVERVIEW

#### R. Kirschman

The present trends in electronics toward ultraminiaturization and higher performance are intimately tied in with lower temperature operation. As materials are made purer and more ordered, as structures are made smaller, and as signal levels are reduced in electronic devices and circuits, thermal effects can become increasingly important and hence reducing the temperature can lead to correspondingly greater benefits.

Cold electronic systems in use or contemplated range from single-transistor amplifiers to computer systems employing many VLSI integrated circuits. The primary areas, as described in this overview, are listed in Table I. Generally speaking, several roles are seen for low temperatures in electronics:

As a means of extracting better performance from existing technology, avoiding expense and delay required for the advances in design or fabrication which would be needed to achieve the same performance at room temperature.

As a necessity in the quest for improved performance, to counteract detrimental effects which arise as technology is pushed to extremes.

As an opportunity to take advantage of effects made available by low temperature operation, and to develop new devices based on them. 1

The object of this overview is to briefly describe the various devices, applications, and performance factors involved in cold electronics, and how these relate to materials and technology. The electronic devices and circuits treated in this overview are those based on semiconductivity. Superconductive devices and circuits are not included; information on these can be found in references 2 through 10.

As is reasonable to expect, most work on cold electronics has been along the lines of adapting and extending existing technology. The potential of devices and circuits which are designed and optimized with low-temperature operation in mind from the outset is still largely unknown and unexplored.

TABLE I

COLD SEMICONDUCTOR ELECTRONICS

| Material    | Device          | Temperatures            | Applications                                                          |

|-------------|-----------------|-------------------------|-----------------------------------------------------------------------|

| Ge          | Bipolar         | > 100 K                 |                                                                       |

|             | discrete JFET   | liquid helium and above | low frequency amplifiers, oscillators                                 |

|             |                 |                         |                                                                       |

| Si          | Bipolar         | > 100 K                 |                                                                       |

|             | discrete JFET   | liquid helium and above | low frequency amplifiers, oscillators                                 |

|             | discrete MOSFET | liquid helium and above | low frequency amplifiers, oscillators                                 |

|             | VLSI MOSFET     | liquid nitrogen         | high-speed logic (proposed)                                           |

| 0.4         | Was Magaza      | 00 % 1 1                |                                                                       |

| GaAs        | discrete MESFET | 20 K and above          | low-noise microwave amplifiers                                        |

|             | LSI/VLSI MESFET | liquid nitrogen         | high-speed logic and<br>fast/high frequency<br>instruments (proposed) |

|             |                 |                         |                                                                       |

| GaAs/AlGaAs | discrete HEMT   | 20 K and above          | <pre>low-noise microwave amplifiers (proposed)</pre>                  |

|             | LSI/VLSI HEMT   | liquid nitrogen         | high-speed logic and fast/high-frequency instruments (proposed)       |

## MATERIALS AND DEVICES

The use of semiconductor materials for cold electronics by and large reflects the situation at room temperature. The principal material is Si, with GaAs showing promise, and Ge being used for a few specialized purposes. Other materials, 11 as well as devices other than those discussed below, might be valuable for low-temperature electronics, but it is unlikely that the considerable effort needed to develop their fabrication technologies would be undertaken solely on the basis of low-temperature applications.

Nearly all active semiconductor devices being used and considered for cold electronics are of the FET (field-effect transistor) family. Bipolar transistors are not now being considered to any degree because those made with standard techniques and materials do not function satisfactorily at temperatures below about 100 K.  $^{12-15}$

Almost since their commercial appearance about twenty years ago, discrete Si and Ge JFETs (junction FETs) and Si MOSFETs (metal-oxide-semiconductor FETs) have been evaluated at low temperatures and used in experimental research involving low temperatures. A prime example is the system in the Infrared Astronomical Satellite (IRAS), 22,23 which uses Si JFETS as the active elements in low-frequency impedance-matching preamplifiers for the infrared detectors which are cooled to liquid-helium temperatures.

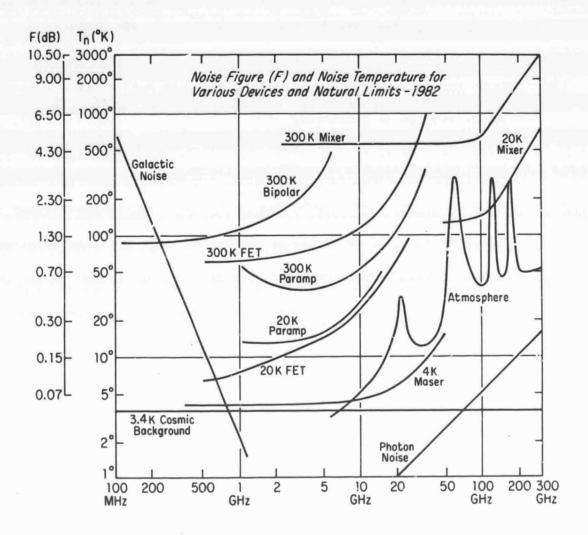

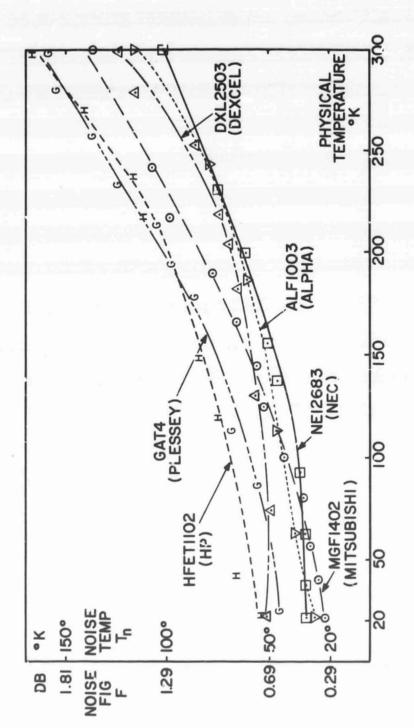

Cooled GaAs MESFETs (metal-semiconductor FETs) have provided outstanding results in low-noise receivers at microwave frequencies for applications such as radio astronomy. The HEMT, a recently developed type of FET described below, is predicted to yield even better performance, approaching that of MASERs.

GaAs MESFETs are also being considered for high-speed digital ICs expected to be several times faster than those based on Si.<sup>12</sup> Experiments indicate that their performance improves at low temperatures.<sup>27</sup> Cold GaAs could provide high performance for specialized applications feasible with low-complexity ICs. At present GaAs is not capable of the integration complexity attainable with Si since its fabrication has not matured; however, such technology is being developed rapidly.

At this time the Si MOSFET is the prime candidate for low-temperature digital applications because of its predominance in room-temperature IC technology coupled with the fact that MOS devices work at low temperatures and exhibit increased speed. 15,28,29 Conventional depletion-mode devices have exhibited undesirable threshold voltage behavior and other effects related to freeze-out of threshold-adjusting impurities, 14,30,31 which has been an impediment to cold NMOS.

Although these difficulties could probably be overcome, interest has shifted to CMOS, which is based on enhancement-mode devices and is coming to the forefront in room-temperature electronics. Enhancement-mode devices exhibit better behavior at low temperatures <sup>14,32</sup> and p- and n-channel types can be made to exhibit symmetrical threshold variation with temperature, allowing CMOS logic circuits to function from room temperature down to liquid-helium temperatures.<sup>33</sup> Thus, it is likely that Si CMOS will be the leading technology for cold electronics for computers.

When bulk CMOS circuits are operated at low-temperature, latch-up is suppressed because the gains are reduced in the parasitic bipolar structures.  $^{28,33,34}$  On the other hand charge trapping in insulators, such as  $\mathrm{SiO}_2$  which is a key ingredient in MOS technology, and consequent unacceptable shifts in device characteristics can become exaggerated at low temperatures.  $^{32,35,36}$

# DEVICE SPEED

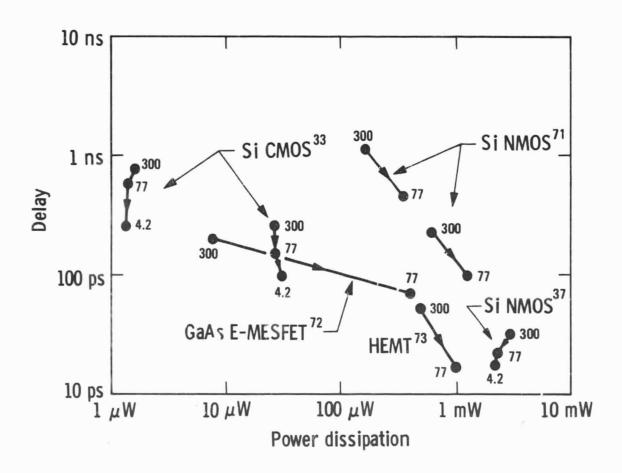

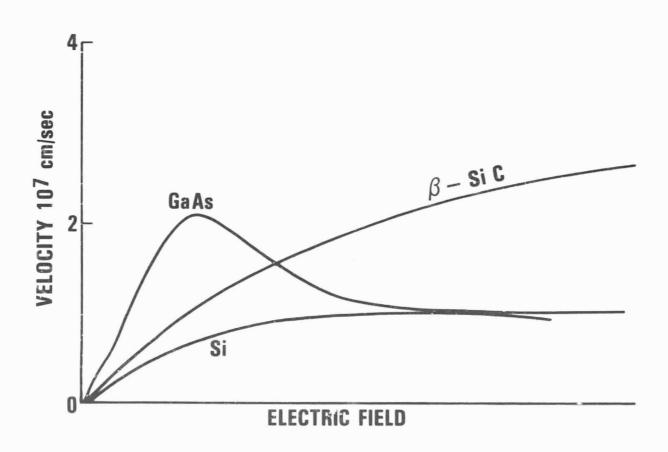

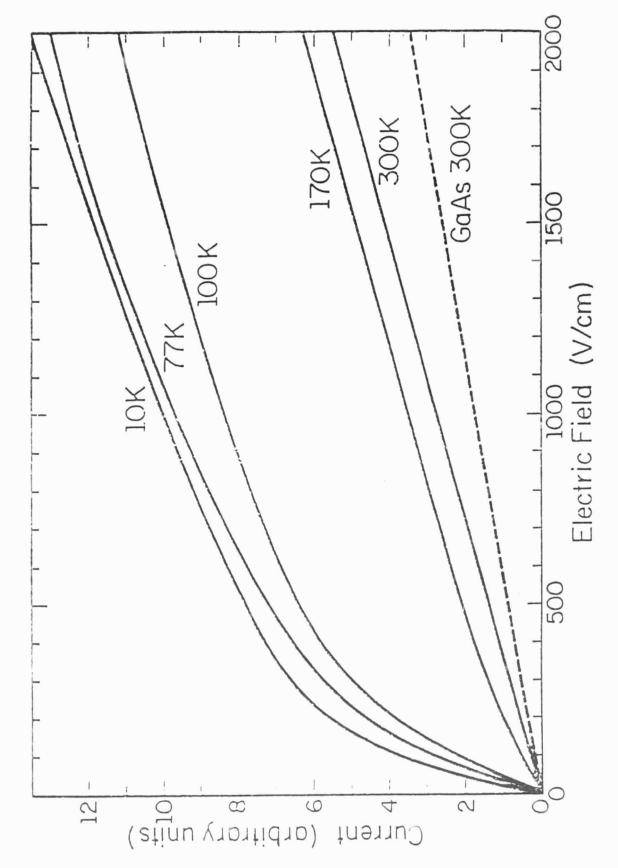

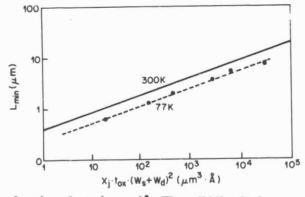

The switching speed of semiconductor devices, a central concern for digital applications, can be increased by lowering their temperature (Fig. 1). Increased device speed is useful only in the context of an integrated circuit, and here too, reduced temperatures could provide benefits related to the interconnections, heat removal, and power as described later. The temperature most frequently considered in this context is that of liquid nitrogen since it is convenient and can provide significant improvements in performance.

Higher speed in FET devices at low temperatures results from higher mobility and transconductance which in turn result from reduced thermal scattering of carriers. Factors of 2 to 3 improvement in speed have been demonstrated in Si MOSFETs 14,28,29,33,37,38 as well as GaAs MESFETs.27,38

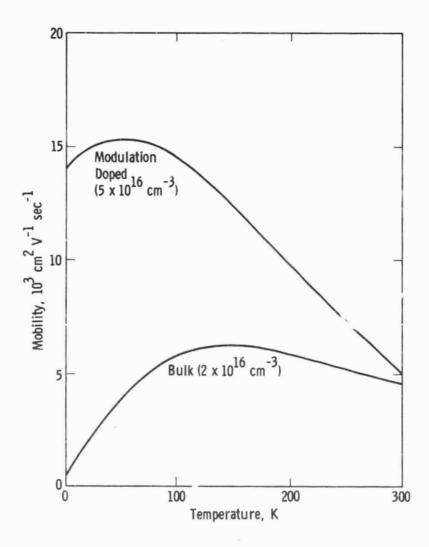

In conventional FETs this improvement occurs primarily on cooling to liquid nitrogen temperatures, with relatively little increase in speed for further reduction in temperature.<sup>38</sup> This is because carrier flow is still disrupted by non-thermal scattering, such as from ionized impurities, which persists at low temperatures.

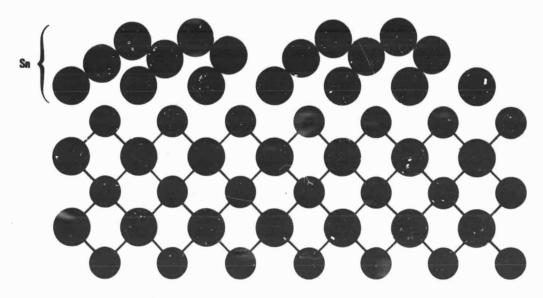

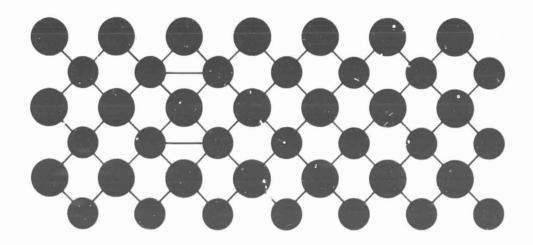

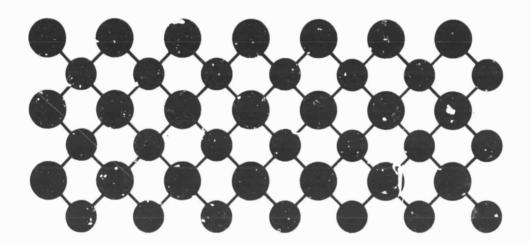

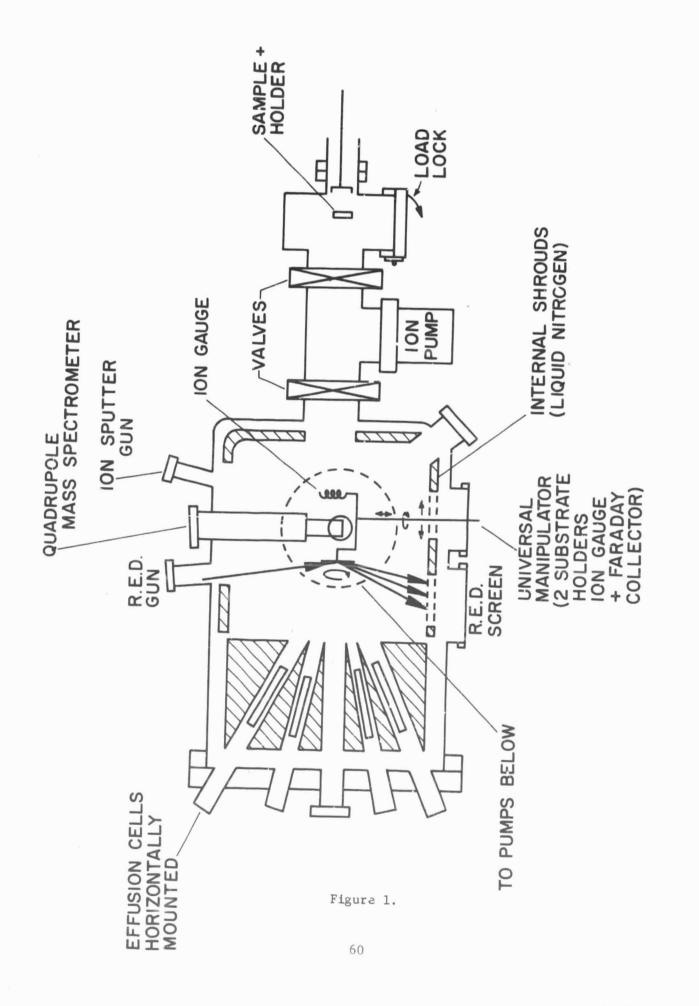

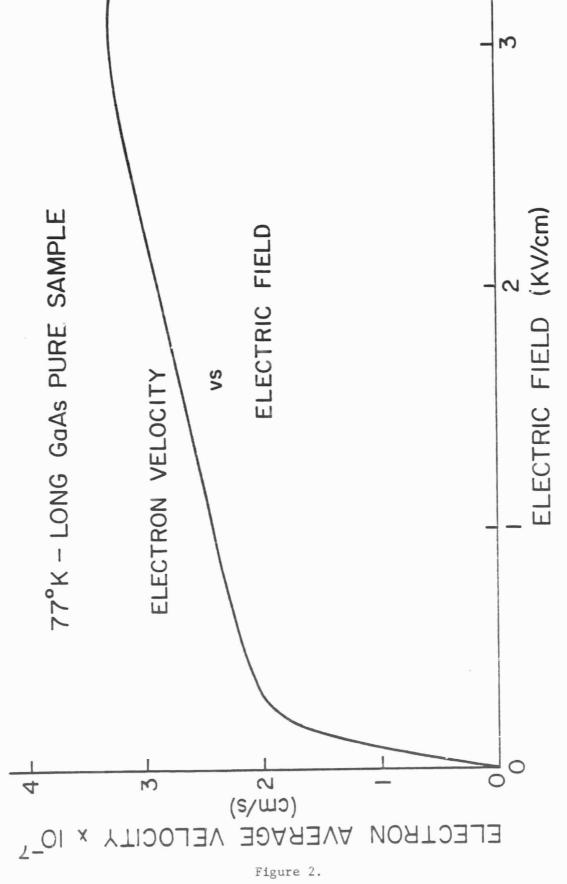

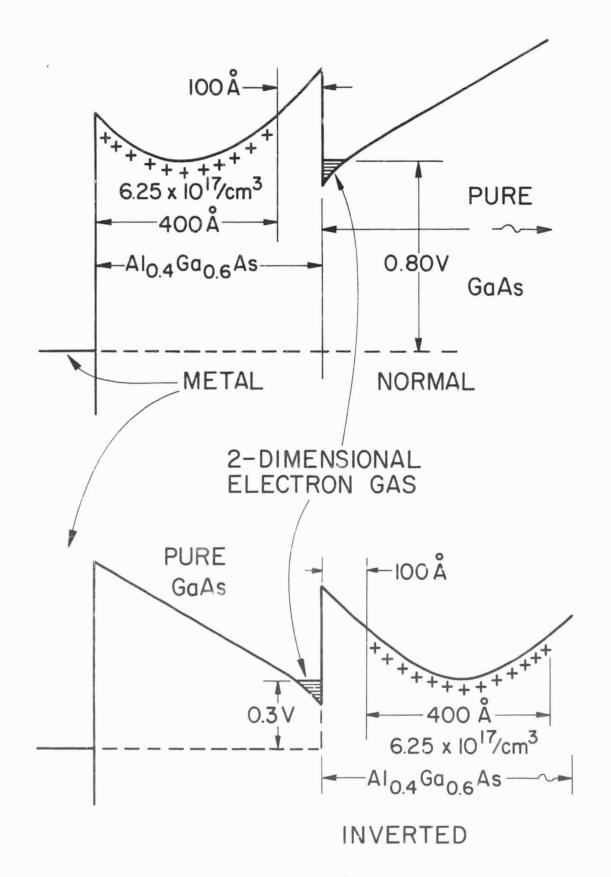

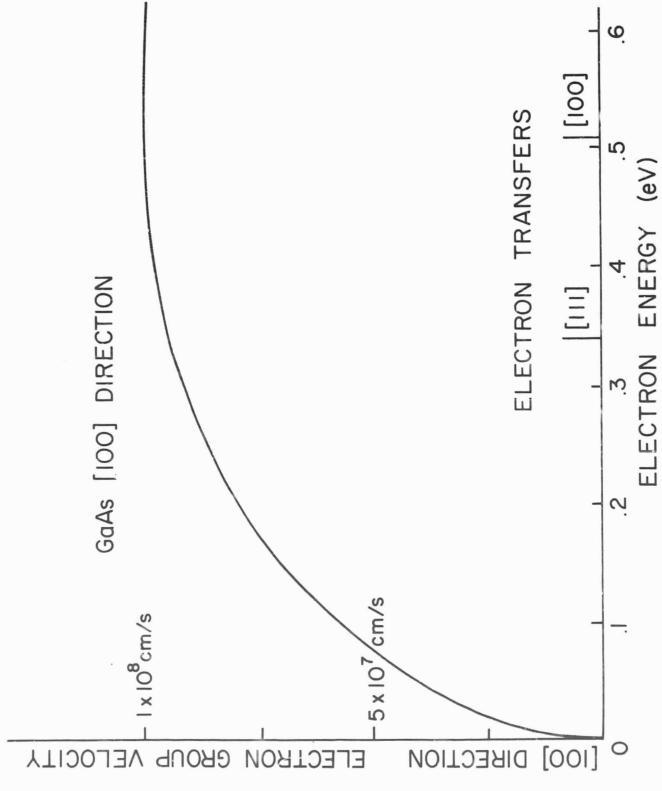

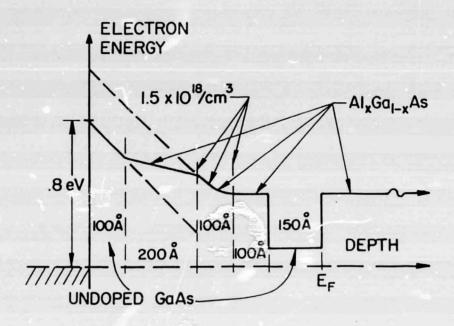

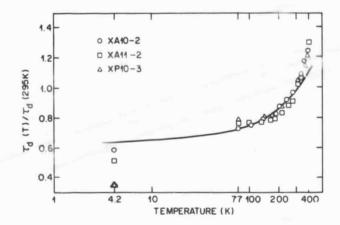

The situation can be improved by spacially separating the carriers from the impurities necessary for their generation, so that non-thermal scattering is drastically reduced (Fig. 2).39-41 This is achieved in the HEMT (high electron-mobility transistor), 42 a recently-developed FET device which is faster than a conventional FET even at room temperature, and improves rapidly as temperature is lowered. A switching time of 13 ps at liquid-nitrogen temperature has been reported. 12,43 As mentioned

Fig. 1. Effect of reduced temperature on speed and power for logic gates based on semiconductor devices. Small numbers next to data points indicate temperatures in K.

Fig. 2. Comparison of electron mobility at low temperatures for modulation-doped GaAs/AlGaAs structure, as used in the HEMT, and uniformly doped bulk GaAs, as used in conventional FETs. 41

earlier, the HEMT also shows great promise for low-noise microwave amplification,  $^{25}$  with predicted 12-GHz noise figures of a fraction of a db even when cooled only to liquid-nitrogen temperatures.

The present realization of the HEMT is with GaAs technology; but its fabrication is more complicated than that of a conventional GaAs FET, requiring the sophisticated techniques of molecular-beam epitaxy (MBE) or organo-metallic vapor-phase epitaxy (OMVPE) to deposit the layers essential to the device's operation. Thus, at present, the technology is in its infancy; however, it is likely that development will be pursued vigorously because of the HEMT's superior performance at room temperature.

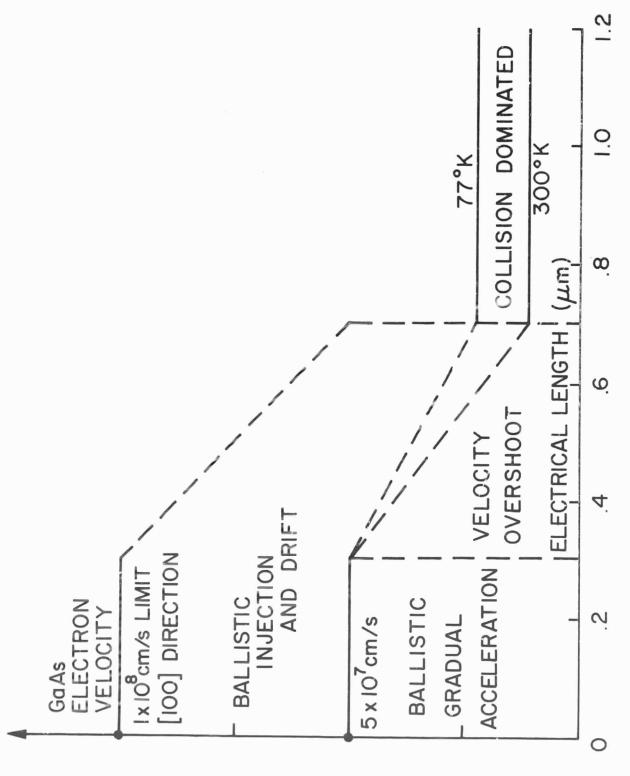

Under certain conditions, one of which is low temperature, carrier transport in these devices may not reach steady state, and the effects of velocity overshoot and "ballistic" transport become important. Investigations in this area are still in the early stages, but could lead to even faster, lower-noise devices.  $^{39}$

### INTERCONNECTIONS

As individual device speed increases, interconnections between devices on an IC chip become no less important than the devices themselves in determining the overall speed in complex digital circuits. 12,47 Particularly so since as devices shrink, ICs are expected to become more dense and at the same time larger, resulting in interconnecting lines of smaller cross section and greater length.

Thus, ultimately it may not matter which device or semiconductor material is chosen for complex ICs since the speed could be limited by the parasitic resistance and capacitance of interconnections rather than by the inherent speed of the individual devices.

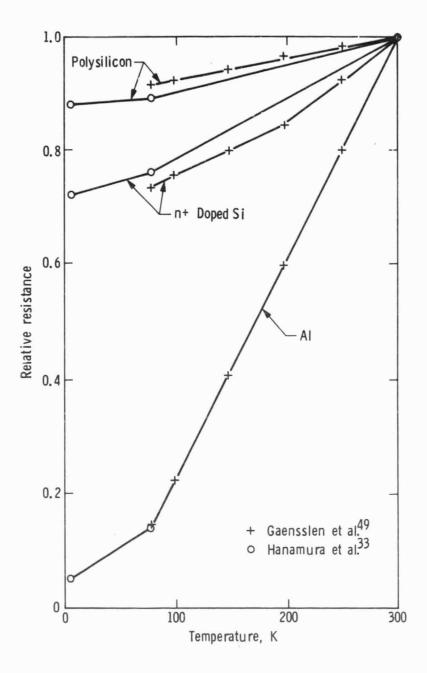

Whether the speed is interconnection limited or not, reducing the temperature is seen as a possible means to improve performance because it lowers the resistance of interconnecting materials. The experimental data available (Fig. 3) indicate about an order of magnitude reduction of resistance of aluminum lines of the type used in integrated circuits and slight reduction for polysilicon and for doped silicon such as used in device contacts. No. 33,49 These results are for dc; none are available for fast pulses and high frequencies found in high-speed logic and microwave applications. Likewise, data are lacking for more recently developed metallization and contacting schemes such as those incorporating refractory metals and silicides, or those used with newer semiconducting materials such as GaAs.

Fig. 3. Resistance as a function of temperature for some materials commonly used as interconnections in integrated circuits. The resistance data are normalized to their room temperature values.

An attractive possibility for circuits operating at temperatures below about 20 K is the use of superconducting interconnections for highly efficient conduction and signal transmission. 7,48,50

Dielectric characteristics of materials used in ICs also affect the propagation of signals and circuit performance. Although capacitance is not expected to change significantly, dielectric losses should decrease at low temperatures.

# HEAT REMOVAL

To achieve high speed in digital ICs the circuit elements must be close together to keep signal propagation times short; however, an increase in the density of circuit elements is accompanied by an increase in power density, and for room temperature this has become a limiting factor in circuit performance because of the difficulty of heat removal. 12

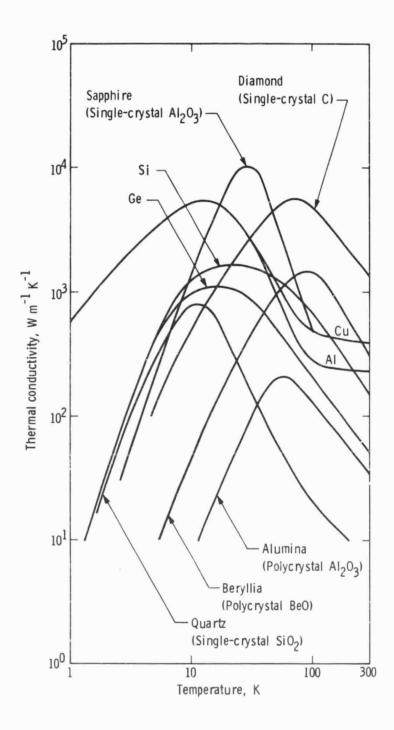

Even for room temperature electronics, improvements in heat removal can be made; <sup>51</sup> additional improvement may be possible at lower temperatures by taking advantage of the fact that many materials used in electronics exhibit an increase in thermal conduction. This is the case for fairly pure, ordered materials; those commonly encountered in electronics include single-crystal semiconductors-Si, Ge, GaAs; single crystal dielectric materials-sapphire, quartz, diamond; some polycrystalline materials-alumina and beryllia; and relatively pure metals-copper or aluminum, usually. As shown in Fig. 4, their thermal conductivity increases as temperature is reduced and peaks at as high as an order of magnitude or more times its room temperature value. <sup>52,53</sup> How much practical use can be made of this effect in actual electronic systems remains to be seen.

Unfortunately, the thermal conductivity of many of the other materials commonly used in electronics, including metal alloys, glasses, and polymers, decreases monotonically as temperature is lowered.  $^{52}$  In any case, careful attention to packaging will be required for cold electronics as it is for room temperature systems.

Liquids might also be employed in heat removal either by direct contact with circuit chips or indirectly. However, the amount of heat that can be removed by this means is reduced at low temperatures, being approximately proportional to the absolute emperature.  $^{48}$

#### POWER

Besides improving heat removal, another approach is to attack the thermal problems of dense circuits at their source and reduce power dissipation. Hence, reduction of power, besides

Fig. 4. Behavior of thermal conductivity at low temperatures for various materials which might be used in cold electronics. 53 These curves only indicate general trends since the low-temperature thermal conductivity of a material is very sensitive to its form and purity.

being desirable in itself, has also become a central issue in attaining higher speed.

One means of reducing power is through lowering operating voltages. Operating temperature becomes a factor because voltages in logic circuits must remain large compared to the thermal voltage kT/e.  $^{12,27,38}$  Consequently, if circuit voltages are to be reduced beyond a certain point, about 1 volt, temperature must be reduced also.

Another effect pertinent to power consumption is that leakage in p-n junctions and insulators is significantly reduced as temperature is lowered. Thus, for example, memories based on p-n junctions or MOS capacitors will require less power to maintain stored data.  $^{28,34,54}$

## NOISE

Although noise has non-thermal as well as thermal origins, substantial improvements have been made in some circumstances by means of cooling. A prime example is the use of GaAs FET microwave amplifiers at about 20 K for radio astronomy as mentioned earlier.  $^{25-26}$  In some cases such as these the improvements also result partly from changes in device parameters such as transconductance which effectively reduce the noise.

Low frequency noise measurements on discrete Si and Ge JFETs and Si MOSFETs have yielded mixed results, frequently showing an increase in noise at low temperatures. A 1/f dependence is commonly observed. Overall, JFETs appear to exhibit lower noise than MOSFETs. 16,17,20,21,55-58

## LIMITATIONS

There are bounds to the improvements in performance that can be derived from the effects described above. Lowering of operating temperature along with reduction of dimensions, voltages, and energies can only be carried so far before limitations of a non-thermal nature appear. 12,27,28,47 Scattering of carriers by impurities or defects has been mentioned; other examples are (1) statistical variation in device characteristics which limits the extent to which voltages can be reduced if noise margins are to be retained, (2) cross-talk as spacings of devices and interconnections shrink, and (3) quantum effects.

### RELIABILITY

Since nearly all degradation mechanisms in electronic devices, such as interdiffusion, corrosion, and electromigration, have a thermal-activation component and an exponential dependence on temperature, orders-of-magnitude improvement in reliablity is expected upon cooling.

Although the effect of temperature on reliability has been thoroughly verified empirically for elevated temperatures, it is difficult to demonstrate that it holds true for reduced temperatures as well because of the extremely low rates involved. However, electronic devices now being developed with circuit patterns smaller than  $1\,\mu\text{m}$  and layers 10 nm thick may provide the testing ground. Such devices may exhibit an unacceptably high failure rate for room temperature operation and storage. Thus, reduced temperatures may prove essential in maintaining the structure and characteristics of advanced electronic circuits as the drive to ever-smaller dimensions continues.

# THERMAL CYCLING

In actual practice the predicted improvement in reliability outlined above is offset by the detrimental effect of mechanical stresses and strains which result from differences in thermal expansion of the various materials used in electronic components, coupled with local and overall temperature differences arising when the system is taken from room temperature to the lower operating temperature or vice versa.

Such effects are already well known for the temperature excursions experienced by conventional electronics, and although troublesome, means have been developed of effectively dealing with them. Thus, although the problem is more severe for cold electronics because of the greater temperature differences, it is reasonable to believe that it can likewise be dealt with effectively if appropriate development is undertaken.

Some background is already available as a result of Josephson computer development, 60,61 as well as from work on non-electronic cryogenic equipment.

A Josephson computer would probably need the ability to survive several hundred cycles for commercial practicality. Of Systems based on semiconducting devices might not require as many cycles since, unlike Josephson devices, it is feasible to design them to function at room temperature as well as at their lower operating temperature. Thus, many basic tests could be performed at room temperature both during initial testing and for maintenance, although testing of ultimate performance would require cooling to the operating temperature.

#### COOLING

Realizing the potential of cold electronics means that a cold environment must be provided. In some situations this environment is already available, such as for preamplifiers used with sensors which must operate at reduced temperatures, or possibly for spacecraft where heat can be radiated to space. 63,64 However, for the remaining systems cooling is a major concern.

Heat loads range from a few milliwatts for a single electronic device or small component to an estimate of about a hundred watts for the electronic system of an advanced computer.

For most applications, "open-cycle" cooling by consumption of a liquid cryogen is seen as impractical, leaving as the only alternative at present the mechanical refrigerator. Although other means of cooling exist, for one reason or another they are not considered suitable.

A variety of mechanical refrigeration units is available to cover the range of heat load and temperature requirements for cold electronics; however, further development is needed, primarily along the lines of further improvement in reliability, efficiency, and low-temperature capability (below about  $20~\rm K)$ .  $^{65-68}$  Present designs also exhibit some undesirable characteristics including: (1) mechanical vibration, (2) magnetic interference, and (3) a periodic temperature fluctuation or "ripple".

A cryogenic refrigeration system is not a major obstacle in the case of an advanced computer since it is a relatively large, fixed piece of hardware. Besides which, such computers already incorporate sophisticated cooling systems.

The concept of the hybrid cooling system has been proposed for cold electronic systems such as computers. <sup>69</sup> In this system the electronics package is immersed in a liquid cryogen bath which is maintained by a closed-cycle refrigerator. The undesirable characteristics of direct mechanical refrigeration mentioned above can be minimized and it also provides: (1) good heat transfer since the electronics may be directly immersed in the cryogen, (2) greater dependability since the cryogen bath would remain cold if the refrigerator malfunctioned or the power failed, and (3) easier maintainability since either the refrigerator or the electronics package could be removed for maintenance without shutting down the remainder of the system.

For smaller-scale systems such as instruments, the widespread use of cold electronics is hindered by a scarcity of suitable small, self-contained coolers, particularly for the lower temperatures, and by lack of experience with those that are available. The Peltier effect, which provides cooling by passing an electric current through a semiconductor, is an attractive method since the cooler is small and has no moving parts. Although it has been established as a practical means for cooling electronic components, the temperatures possible with present materials are not low enough for most of the applications discussed in this overview. Joule-Thomson 67,70 coolers are a possibility if continuous, closed-cycle operation can be developed.

Because refrigeration for the temperatures appropriate for cold electronics is characterized by low efficiency, <sup>05,60</sup> it is important that the heat load be minimized. A significant portion of the heat load can arise from leakage through electrical and mechanical interfaces which couple the cold electronics with room temperature. Electrical connections carrying signals are particularly troublesome, since they need low electrical resistance without high thermal conductance. In the case of high-speed or high-frequency measuring instruments it is also a major challenge to preserve an input signal to be analyzed while transferring it from room temperature to the cold electronics. A proposed means of signal transfer which could prove advantageous is the use of optoelectronic techniques.

## CONCLUSION

Cold electronic devices and circuits have already provided substantial benefits in certain applications, and theory and experiment indicate additional benefits to be derived from wider use of reduced temperatures, although a great deal of research and development remains in overcoming the technical hurdles to achieve practicality. Overall, it appears that lower operating temperatures will go hand-in-hand with other advances in electronic device and circuit technology for a variety of applications requiring the highest performance and reliability.

# ACKNOWLEDGEMENTS

In addition to the references indicated, many of the ideas in this overview originated in the discussion sessions, formal and informal, at the Workshop. The manuscript was reviewed by E. Tward and V. Hadek, of the Jet Propulsion Laboratory, D. Ferry and R. Grondin of Arizona State University, S. Weinreb of the National Radio Astronomy Observatory, F. Gaensslen and P. Solomon of IBM Corporation, W. Steyert of Air Products and Chemicals, and M. Nisenoff of the Naval Research Laboratory, who provided valuable comments. Support for the preparation of this overview was provided by the Office of Naval Research (Dr. E. Edelsack).

#### REFERENCES

- 1. J. Lambe, "Novel Low Temperature Devices", this Workshop.

- 2. Antonio Barone and Gianfranco Paterno, <u>Physics and Applications of the Josephson Effect</u>, Wiley-Interscience, New York, 1983.

- 3. T. Van Duzer and C. W. Turner, Principles of Superconductive Devices and Circuits, Elsevier, New York, 1981.

- 4. Donald G. McDonald, "Superconducting Electronics", Physics Today, Vol. 34, #2, p 36, February 1981.

- 5. Donald B. Sullivan, Clark A. Hamilton, and Richard L. Kautz, "Recent Progress in Cryoelectronics", <u>IEEE Transactions on Instrumentation and Measurement</u>, Vol. IM-29, #4, p 319, December 1980.

- 6. Theodore Van Duzer, "Josephson Digital Devices and Circuits", IEEE Transactions on Microwave Theory and Techniques, Vol. MTT-28, #5, p 490, May 1980.

- 7. Richard E. Harris, "Space Applications of Superconductivity: Digital Electronics", <u>Cryogenics</u>, Vol. 20, #4, p 171, April 1980.

- 8. Tushar Gheewala, "The Josephson Technology", Proceedings of the IEEE, Vol. 70, #1, p 26, January 1982.

- Arthur L. Robinson, "New Superconductors for a Supercomputer", <u>Science</u>, Vol. 215, #4528, p 40, 1 January 1982.

- W. Anacker, "Computing at 4 Degrees Kelvin", <u>IEEE Spectrum</u>, Vol. 16, #5, p 26, May 1979.

- Robert W. Keyes, "Low Temperature High Mobility Transistor Materials", <u>Comments on Solid State Physics</u>, Vol. 8, #2, p 37, 1977.

- 12. Paul M. Solomon, "A Comparison of Semiconductor Devices for High-Speed Logic", <u>Proceedings of the IEEE</u>, Vol. 70, #5, p 489, May 1982.

- 13. William P. Dumke, "The Effect of Base Doping on the Performance of Si Bipolar Transistors at Low Temperatures", IEEE Transactions on Electron Devices, Vol. ED-28, #5, p 494, May 1981.

- 14. Fukunobu Oosaka and Tetsuo Nakamura, "Low-Temperature Operation of Bipolar and MOS Devices", Fujitsu Scientific and Technical Journal, Vol. 14, #3, p 53, September 1978.

- B. Lengeler, "Semiconductor Devices Suitable for Use in Cryogenic Environments", <u>Cryogenics</u>, Vol. 14, #8, p 439, August 1974.

- 16. R. F. Arentz, D. W. Strecker, J. H. Goebel, and C. R. McCreight, "A Brief Characterization of Germanium Junction FETs at 77, 4, and 1.8K", <u>Proceedings of the SPIE</u>, Vol. 364, p 141, 1982.

- 17. G. H. Rieke, E. F. Montgomery, M. J. Lebofsky, and P. R. Eisenhardt, "High Sensitivity Operation of Discrete Sclid State Detectors at 4 K", Applied Optics, Vol. 20, #5, p

- 814, 1 March 1981.

- G. Mossuz and J. J. Gagnepain, "Quartz Crystal Oscillator at Very Low Temperature", <u>Cryogenics</u>, Vol. 16, #11, p 652, November 1976.

- 19. Hisao Yagi, Masasi Inoue, Takashi Naito, and Toshiaki Tatsukawa, "NMR Marginal Oscillator with MOS-FET Operating at Low Temperature", Japanese Journal of Applied Physics, Vol. 12, #11, p 1794, November 1973.

- 20. P. T. Anderson, B. Bertman, and R. R. Wagner, "Low Level Signal Amplifiers at Cryogenic Temperatures", Cryophysics and Cryoengineering, Bulletin de l'Institute International du Froid, Supplement 1970-2, p 211, 1970.

- 21. M. D. Daybell, "Field Effect Transistors for Sub-MHz Applications at Temperatures Below 4.2 Kelvins", Cryophysics and Cryotechnology, Bulletin de l'Institute International du Froid, Supplement 1970-2, p 215, 1970.

- 22. F. Low, "Cryogenic Amplifiers for IR Detection", this Workshop.

- 23. F. J. Low, "Application of JFETs to Low Background Focal Planes in Space", <u>Proceedings of the SPIE</u>, Vol. 280, p 56, 1981.

- Charles A. Liechti and Roderic B. Larrick, "Performance of GaAs MESFET's at Low Temperatures", <u>IEEE Transactions on Microwave Theory and Technique</u>, Vol. MTT-24, #6, p 376, June 1976.

- 25. S. Weinreb, "Cryogenically-Cooled Low Noise Microwave Receivers--Present Status and Future Needs", this Workshop.

- 26. Sander Weinreb, "Low-Noise Cooled GASFET Amplifiers", IEEE Transactions on Microwave Theory and Techniques, Vol. MTT-28, #10, p 1041, October 1980.

- 27. Richard C. Eden, "Comparison of GaAs Device Approaches for Ultra-High-Speed VLSI, <u>Proceedings of the IEEE</u>, Vol. 70, #1, p 5, January 1982.

- 28. F. H. Gaensslen, "Why Consider MOSFET Operation in Liquid Nitrogen?", this Workshop.

- 29. A. Kamgar, "SiMOS Devices at Low Temperatures", this Workshop.

- 30. F. H. Gaensslen and R. C. Jaeger, "Temperature Dependent Threshold Behavior of Depletion Mode MOSFETs--Characterization and Simulation", Solid-State Electronics,

- Vol. 22, #4, p 423, April 1979.

- 31. Richard C. Jaeger and Fritz H. Gaensslen, "Simple Analytical Models for the Temperature Dependent Threshold Behavior of Depletion-Mode Devices", <u>IEEE Transactions on Electron Devices</u>, Vol. ED-26, #4, p 501, April 1979.

- 32. S. K. Tewksbury, "N-Channel Enhancement-Mode MOSFET Characteristics from 10 to 300 K", <u>IEEE Transactions on Electron Devices</u>, Vol. ED-28, #12, p 1519, December 1981.

- 33. S. Hanamura, M. Aoki, T. Masuhara, O. Minato, Y. Sakai and T. Hayashida, "Operation of Bulk CMOS Devices at Very Low Temperatures", IEEE 1983 Symposium on VLSI Technology, Digest of Papers, p 46, Maui, Hawaii, 13-15 September 1983 (IEEE 83 CH 1873-9).

- 34. F. H. Gaensslen, "MOS Devices and Integrated Circuits at Liquid Nitrogen Temperature", <u>IEEE</u> 1980 <u>International</u> Conference on Circuits and Computers, p 450, 1980.

- 35. Manabu Itsumi, "Electron Trapping in Thin Films of Thermal SiO<sub>2</sub> at Temperatures between 30 and 300 K", <u>Journal of Applied Physics</u>, Vol. 54, #4, p 1930, April 1983.

- 36. J. R. Davis, "Degradation Behaviour of n-Channel MOSFETs Operated at 77 K", <u>IEE</u> <u>Proceedings</u>, Vol. 127, Pt. I, #4, p 183, August 1980.

- 37. Avid Kamgar and R. L. Johnston, "Delay Times in Si MOSFETs in the 4.2--400 K Temperature Range", Solid-State Electronics, Vol. 26, #4, p 291, April 1983.

- 38. Ph. Coeure, "Cryogenic Devices", 11th European Solid State

Device Research Conference/6th Symposium on Solid State

Device Technology, p 153, Toulouse, France, 14-17 September

1981.

- 39. L. F. Eastman, "Physical Electronics of Cooled Operation of Very Short Compound Semiconductor Transistors", this Workshop.

- 40. L. C. Witkowski, T. J. Drummond, S. A. Barnett, H. Morkoc, A. Y. Cho and J. E. Greene, "High Mobility GaAs-A1<sub>x</sub>Ga<sub>1-x</sub>As Single Period Modulation-Doped Heterojunctions", <u>Electronics</u> Letters, Vol. 17, #3, p 136, 5 February 1981.

- 41. R. Dingle, H. L. Stormer, A. C. Gossard and W. Wiegmann, "Electron Mobilities in Modulation-Doped Semiconductor Heterojunction Superlattices", Applied Physics Letters, Vol. 33, #7, p 665, 1 October 1978.

- 42. Satoshi Hiyamizu, Takashi Mimura, Toshio Fujii, Kazuo

- Nanbu and Hisao Hashimoto, "Extremely High Mobility of Two-Dimensional Electron Gas in Selectively Doped GaAs/n-A1<sub>x</sub>Ga<sub>1-x</sub>As Heterojunction Structures Grown by MBE", <u>Japanese</u> <u>Journal of Applied Physics</u>, Vol. 20, #4, p L245, April 1981.

- 43. Masayuki Abe, Takashi Mimura, Naoki Yokoyama and Hajime Ishikawa, "New Technology Towards GaAs LSI/VLSI for Computer Applications", IEEE Transactions on Electron Devices, Vol. ED-29, #7, p 1088, July 1982.

- 44. "Submicron Circuits Beat Josephson Chips", High Technology, Vol. 3. #2. p 62. February 1983.

- 45. Stephen Lewis Teitel and J. W. Wilkins, "Ballistic Transport and Velocity Cvershoot in Semiconductors: Part I--Uniform Field Effects", IEEE Transactions on Electron Devices, Vol. ED-30, #2, p 150, February 1983.

- 46. A. Ghis, E. Constant and B. Boittiaux, "Ballistic and Overshoot Electron Transport in Bulk Semiconductors and in Submicronic Devices", <u>Journal of Applied Physics</u>, Vol. 54, #1, p 214, Janury 1983.

- 47. R. Grondin, "Effect of Cooling on Delay Time Limits in Integrated Circuits", this Workshop.

- 48. Robert W. Keyes, Erik P. Harris and Karl L. Konnerth, "The Role of Low Temperatures in the Operation of Logic Circuitry", Proceedings of the IEEE, Vol. 58, #12, p 1914, December 1970.

- 49. Fritz H. Gaensslen, V. Leo Rideout, E. J. Walker, and John J. Walker, "Very Small MOSFETs for Low Temperature Operation", IEEE Transactions on Electron Devices, Vol. ED-24, #3, p 218, March 1977.

- 50. R. L. Kautz, "Picosecond Pulses on Superconducting Striplines", <u>Journal of Applied Physics</u>, Vol. 49, #1, p 308, January 1978.

- 51. D. B. Tuckerman and R. F. W. Pease, "High-Performance Heat Sinking for VLSI", <u>IEEE Electron Device Letters</u>, Vol. EDL-2, #5, p 126, May 1981.

- 52. J. G. Hust, "Thermal Conductivity and Thermal Diffusivity", Ch. 4 of Materials at Low Temperatures, Ed. by Richard P. Reed and Alan F. Clark, American Society for Metals, Metals Park, OH, 1983.

- 53. Y. S. Touloukian, R. W. Powell, C. Y. Ho, and P. G. Klemens, "Thermal Conductivity", Vols. 1 and 2 of <u>Thermophysical</u> Properties of Matter, Plenum Press, New York, 1970.

- 54. Robert W. Keyes, "Semiconductor Devices at Low Temperatures", Comments on Solid State Physics, Vol. E, #3, p 47, 1977.

- 55. R. F. Arentz, V. Hadek and V. L. Hoxie, "A New Cryogenic P-Channel MOSFET with Optimized Doping Yielding Performance Superior to the G-118, W-164, and 3N165 at 77 K, 4 K, and 1.8 K", Proceedings of the SPIE, Vol. 364, p 132, 1982.

- 56. Steve S. Sesnic and George R. Craig, "Thermal Effects in JFET and MOSFET Devices at Cryogenic Temperatures", <u>IEEE Transactions on Electron Devices</u>, Vol. ED-19, #8, p 933, 1972,

- 57. James W. Haslett and E. J. M. Kendall, "Temperature Dependence of Low-Frequency Excess Noise in Junction-Gate FET's", IEEE Transactions on Electron Devices, Vol. ED-19, #8, p 943, August 1972.

- 58. Francois M. Klaassen and John R. Robinson, "Anomalous Noise Behavior of the Junction-Gate Field-Effect Transistor at Low Temperatures", <u>IEEE Transactions on Electron Devices</u>, Vol. ED-17, #10, p 852, October 1970.

- M. Yoder, "Recent Developments in Semiconductor Research", this Workshop.

- 60. Syamal K. Lahiri, H. Randall Bickford, Pieter Geldermans, K. R. Grebe, Paul A. Moskowitz, Menachem Natan, M. J. Palmer, Sampath Turushothaman, John Sokolowski, Bernard J. C. van der Hoeven, David F. Waldman, Run-Han Wang, C. T. Wu, and Tadashi Yogi, "Packaging Technology for Josephson Integrated Circuits", IEEE Transactions on Components, Hybrids, and Manufacturing Technology, Vol. CHMT-5, #2, p 271, June 1982.

- 61. Alan V. Brown, "An Overview of Josephson Packaging", IBM Journal of Research and Development, Vol. 24, #2, p 167, March 1980.

- 62. H-C. Ward Huang, Suryadevar Basavaiah, Charles J. Kircher, Erik P. Harris, Masanori Murakami, Stephen P. Klepner, and James H. Greiner, "High-Reliability Pb-Alloy Josephson Junctions for Integrated Circuits", IEEE Transactions on Electron Devices, Vol. ED-27, #10, p 1979, October 1980.

- 63. Allan Sherman, "History, Status, and Future Applications of Spaceborne Cryogenic Systems", Advances in Cryogenic Engineering, Vol. 27, p 1007, 1981.

- 64. M. J. Donohoe, A. Sherman, and D. E. Hickman, "Radiant Coolers---Theory, Flight Histories, Design Comparisons

- and Future Applications", AIAA 13th Aerospace Sciences Meeting, Pasadena, CA, 20-22 January 1975 (AIAA paper 75-184).

- 65. R. Radebaugh, "Refrigeration", this Workshop.

- 66. Ray Radebaugh, "Refrigeration Fundamentals: A View Toward New Refrigeration Systems" in <u>Applications of Closed-Cycle Cryocoolers to Small Superconducting Devices</u>, NBS Special Publication 508, p 7, 1978.

- M. Nisenoff and E. A. Edelsack, "U.S. Navy Programme in Small Cryocoolers", <u>Cryogenics</u>, Vol. 23, #7, p 353, July 1983.

- 68. A. L. Johnson, "Spacecraft Borne Long Life Cryogenic Refrigeration Status and Trends", Cryogenics, Vol. 23, #7, p 339, July 1983.

- 69. R. C. Longsworth, "Interfacing Small Closed-Cycle Refrigerators to Liquid Helium Cryostats", <u>Small Cryogenic Refrigerator Symposium</u>, Oxford, England, 23 March 1983.

- 70. Robert M. Duboc, Jr., "Low Cost Microminiature Refrigerators for Large Unit Volume Applications", Refrigeration for Cryogenic Sensors, NASA Conference Publication 2287, p 431, 1983.

- 71. Robert H. Dennard, Fritz H. Gaensslen, Edward J. Walker and Peter W. Cook, "1  $\mu$ m MOSFET VLSI Technology: Part II—Device Designs and Characteristics for High-Performance Logic Applications", IEEE Journal of Solid-State Circuits, Vol. SC-14, #2, p 247, April 1979.

- 72. T. Mizutani, N. Kato, M. Ida and M. Ohmori, "High-Speed Enhancement-Mode GaAs MESFET Logic", <u>IEEE Transactions on Microwave Theory and Techniques</u>, Vol. MTT-28, #5, pp 479, May 1980.

- 73. Takashi Mimura, Kazukio Joshin, Satoshi Hiyamizu, Kohki Hikosaka and Masayuki Abe, "High Electron Mobility Transistor Logic", <u>Japanese Journal of Applied Physics</u>, Vol. 20, #8, p L598, August 1981.

#### III. SUMMARY OF PRESENTATIONS

The first session of presentations included three on advanced semiconductor materials and devices and one on refrigeration.

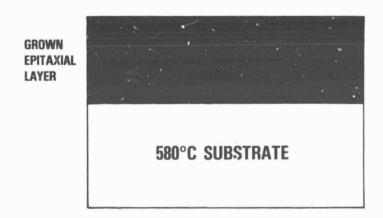

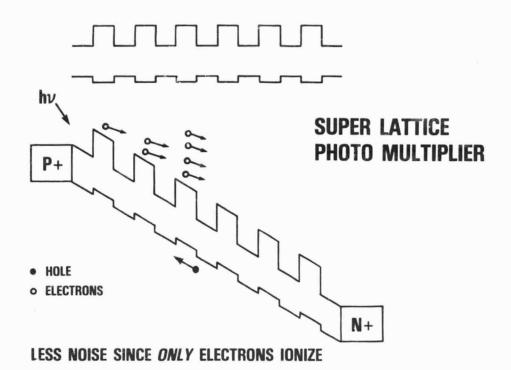

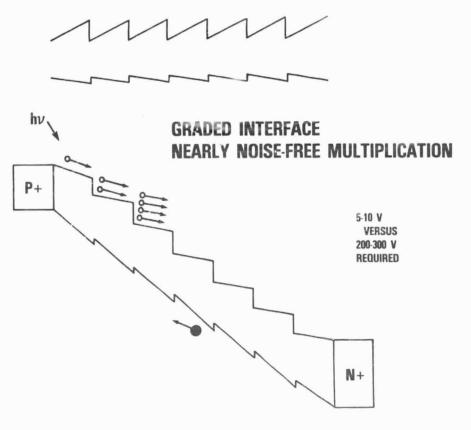

# M. YODER--Recent Developments in Semiconductor Research

M. Yoder from the Office of Naval Research presented some advanced topics in semiconductor materials and devices. A new technique called "atomic layer epitaxy" is claimed to produce crystalline films of certain semiconductor or other materials with exceptional purity, uniformity, and control of structure. A reliability problem is emerging for advanced electronic devices incorporating extremely small geometries and thin crystal layers, since diffusion, even at room temperatures, is sufficient to alter their structure and properties. Possible solutions are reduced temperatures or impeding the motion of impurities by complexing them. Recent advances in growing single-crystal  $\beta$ -SiC would make possible its wider use in electronic devices to take advantage of its excellent stability under adverse environments and high temperatures.

## J. LAMBE--Novel Low Temperature Devices

J. Lambe of the Jet Propulsion Laboratory discussed the conditions under which quantum size effects would play a dominant role in electronic structures and how these might be employed in novel devices. An example is a "Stark-effect" transistor, a quan'um-well structure in which the transfer characteristics arise from a shifting of the energy levels by an electric field from a control electrode. It is conceivable that devices could employ quantum effects even at liquid nitrogen temperatures.

### R. RADEBAUGH--Refrigeration

R. Radebaugh of the National Bureau of Standards gave an overview of refrigeration principles and technology. There are a variety of refrigeration cycles and designs applicable to electronics, of which the most popular are variations of the Stirling and Gifford-McMahon. Effort is being devoted to improving reliability. Refrigeration becomes less efficient the lower the temperature and the smaller the capacity of a refrigerator; also, heat transfer in materials and to liquids is difficult at low temperatures. Proposed systems for cooling electronics include not only existing commercial refrigerators, but also a hybrid of mechanical refrigerator and liquid cryogen bath and novel methods such as closed cycle Joule Thomson refrigerators.

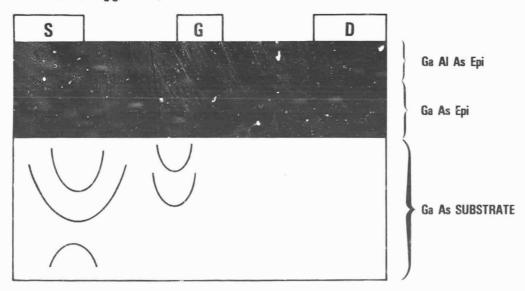

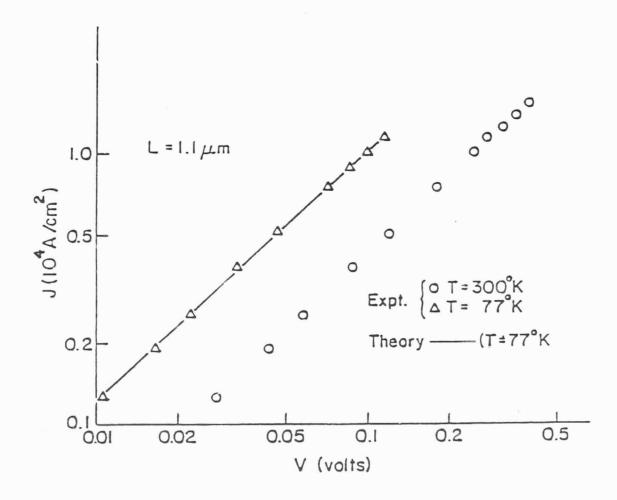

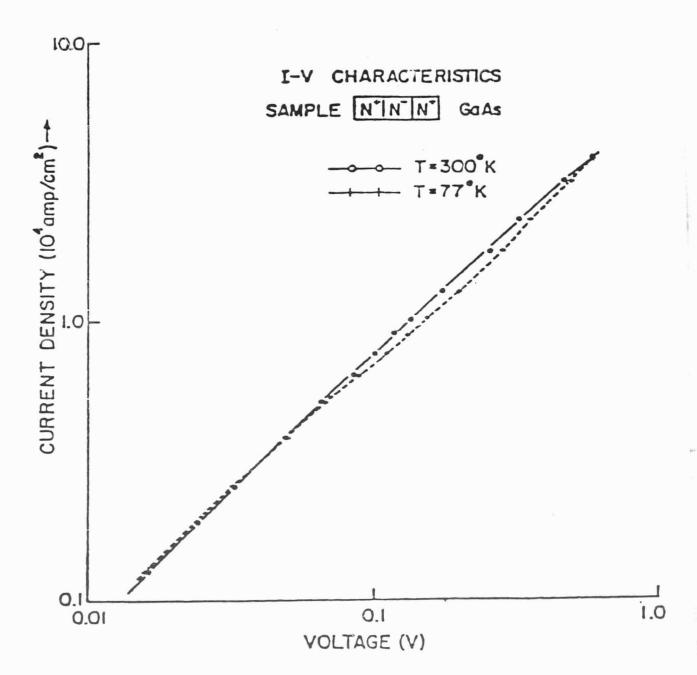

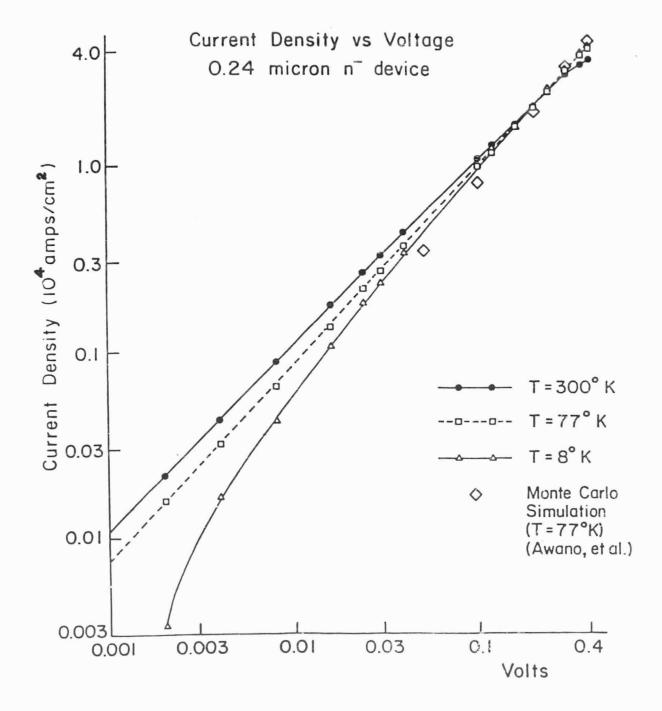

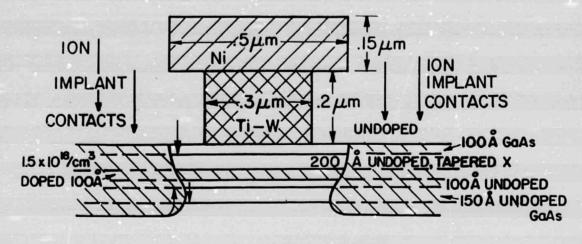

# L. EASTMAN--Physical Electronics of Cooled Operation of Very Short Compound Semiconductor Transistors

L. Eastman of Cornell University described the dynamics of electron motion in short compound-semiconductor FET devices, and its bearing on their performance. Advanced fabrication techniques and low-temperature operation are expected to increase the already excellent high-frequency, low-noise capabilities of FETs. Of particular interest is the modulation-doped heterojunction (HEMT) device, in which extremely high electron velocities and mobilities have been obtained. Noise figures at liquid nitrogen temperatures of a fraction of a db at 12 GHz are predicted.

Session 2 contained three presentations on topics related to large-scale digital integrated circuits.

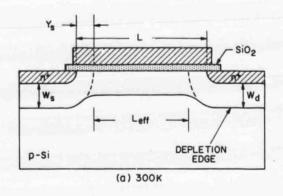

# F. GAENSSLEN--Why Consider MOSFET Operation in Liquid Nitrogen?

F. Gaensslen of IBM described some of the reasons for cooling MOSFET devices to liquid nitrogen temperatures. When MOS devices are scaled down in size, some characteristics, such as subthreshold current, do not scale. These effects become a problem at about 1  $\mu m$  gate length, but can be counteracted by a reduction in temperature. Reduced temperatures can also help to suppress latch-up as CMOS circuits are scaled down and to reduce leakage in p-n junctions which allows higher efficiency in semiconductor memory circuits. Advantage can also be taken of increased electrical and thermal conductivity at low temperatures.

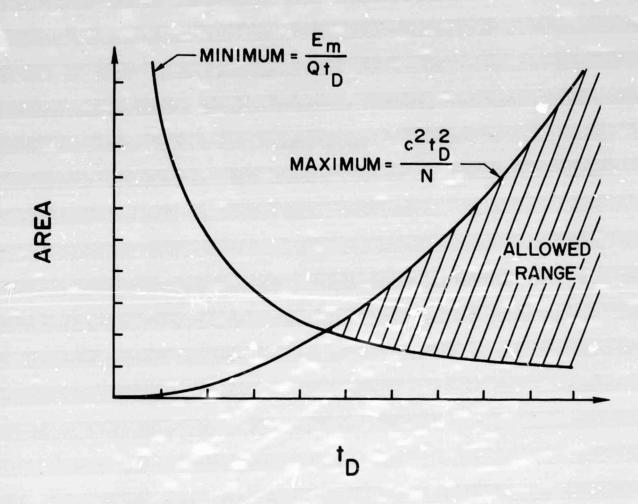

# $\frac{\text{R.}}{\text{GRONDIN---}} \underbrace{\text{Effect of Cooling on Delay Time Limits in}}_{\text{Integrated Circuits}}$

R. Grondin of Arizona State University examined various factors which limit the highest speed attainable in integrated circuits. Speed is not only determined by the device technology and material, but also depends on heat removal and characteristics of the on-chip interconnections, particularly so as devices become smaller and IC chips become larger as the level of integration increases. In such situations speed may be increased by reducing the voltage, which in turn requires that the temperature be reduced also. In principle, this would allow a substantial increase by cooling to liquid nitrogen temperatures and another order of magnitude for liquid helium temperatures.

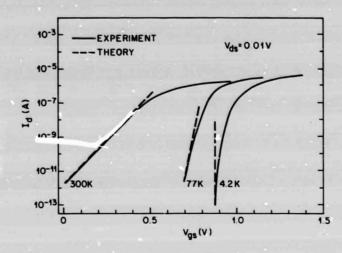

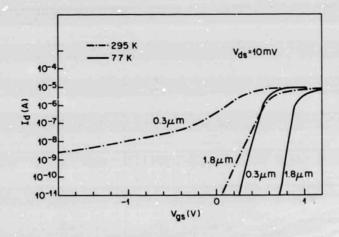

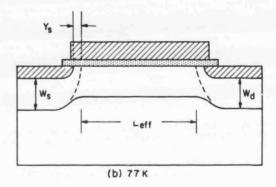

#### A. KAMGAR--SiMOS Devices at Low Temperatures

A. Kamgar of A T & T Bell Laboratories described improvements in the characteristics of silicon MOS devices which occur as temperature is reduced. Subthreshold slope increases so that less gate voltage swing is needed, especially for short-

channel devices. Punchthrough current in short-channel MOSFETs is also reduced. Measurements at liquid nitrogen temperatures of switching speed show about a factor 2 increase with a corresponding increase in power dissipation when compared to room temperature.

Session 3, the final two presentations, described the applications of cold devices and circuits to astronomy.

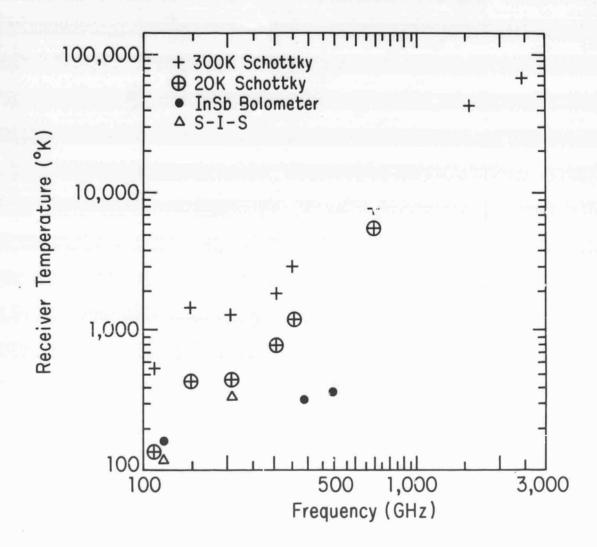

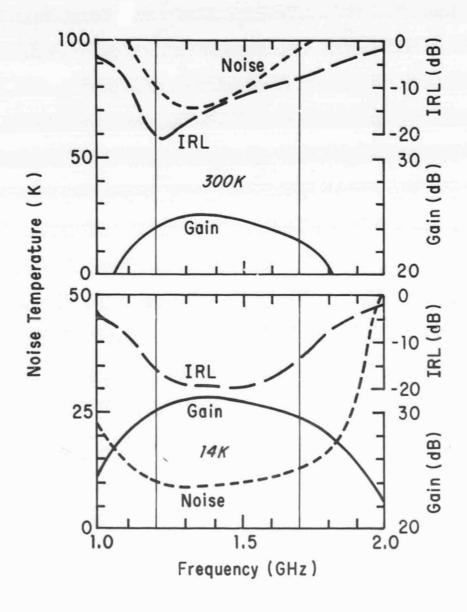

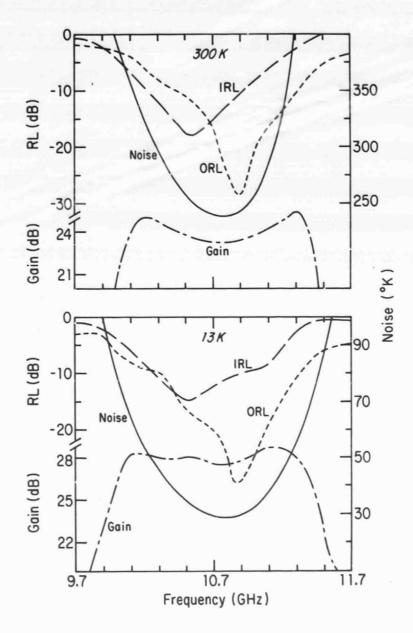

# S. WEINREB--Cryogenically Cooled Low Noise Microwave Receivers-Present Status and Future Needs

S. Weinreb of the National Radio Astronomy Observatory reviewed the current status of low-noise electronics used in adio astronomy. Above about 100 GHz the SIS (superconductor-insulator-superconductor) device is being used as a mixer. For lower frequencies GaAs FETs are providing excellent results in receivers, when cooled to approximately 20 K to achieve ultra-low noise amplification. To make the actual receivers a number of technical problems with materials and electronic components had to be solved: for example, achieving minimum microwave signal loss while interfacing between 300 K and 20 K. The newly developed HEMT (high electron-mobility transistor) promises to provide outstanding low-noise performance and plans are under way to evaluate it for microwave applications.

# F. LOW--Cryogenic Amplifiers for IR Detection

F. Low of the University of Arizona described the preamplifiers used with infrared detectors in the Infrared Astronomical Satellite (IRAS). The preamplifiers are based on silicon JFETs operating at approximately 60 K and are mounted adjacent to the IR detectors which are cooled to 2 K. Work is under way on a device with improved characteristics.

### IV. SUMMARY OF THE DISCUSSION SESSIONS

#### A. Silver

Specialized technical presentations occupied the first part of the workshop. Three topical discussion sessions were organized on the second day:

- 1. Silicon and VLSI,

- 2. Non-silicon materials (principally GaAs),

- 3. Refrigeration.

The topical sessions discussed the material which was presented in the plenary sessions and developed a consensus. The conclusions were reported back to the workshop as a whole. The context in which the conclusions were discussed was:

- a) advantages and disadvantages of cooling semiconductor electronics,

- other technology which will be required to implement cold semiconductor electronics, and

- c) recommendations for emphasis in R & D support.

The workshop covered widely diverse topics ranging from cooling production CMOS near 77 K for computing machines, to cooling commercial Si JFET's to 60 K for IR detectors, quasiparticle tunnel junctions to 4 K for millimeter and submillimeter wave detectors, and cooling GaAs HEMTs to 20 K. The separate discussion sessions extrapolated from the technical presentations to discuss other materials, processes, and applications.

Josephson technology was not a topic of this workshop, although passive superconductivity was discussed in the context of lower temperature semiconductors. The anomalous absence of this subject (Josephson technology) at a workshop on cold electronics was noted in the discussion session. Superconductive electronics was interpreted as a discinct technical area already receiving considerable interest and attention. The recent IBM project achieved notable successes in developing high performance logic at the 10<sup>3</sup> gates per chip level and a 1 K RAM using 2.5 micron lithography. The development of the technology at this point, particularly at IBM, points to near-term development of Josephson technology for small system applications rather than large general-purpose computing machines.

### SILICON AND VLSI

Silicon CMOS can yield improved performance with existing manufacturing facilities if the devices and circuits are cooled to approximately 77 K (this temperature is chosen because it is

the boiling temperature of liquid nitrogen, commonly available in research and development laboratories and is above the carrier freezeout temperature of Si devices). The improvement is an increase of 2 to 3 in speed, with a corresponding increase in power dissipation. The use of cryogenic cooling to attain this improvement would be most likely to occur at the point of redesigning the circuitry for submicron lithography in order to achieve the next level of improvement in LSI, i.e., it may prove to be more desirable to redesign the 1.5 micron chip for cryogenic operation as compared to producing a submicron technology given the investment required in both chip design and production facilities. In addition, latching in CMOS will be greatly alleviated by cooling. Refrigeration for operation at liquid nitrogen temperatures (LN2) for a mainframe digital computer may not present a significant penalty in total cost, size, and reliability when compared to the contemporary use of air conditioning equipment. One can expect to be able to test at room temperature in production, and reliability should be enhanced with respect to thermally activated failure mechanisms.

In addition to  $LN_2$  operation of CMOS to achieve the increase in speed which would also be provided by submicron technology, there may be unknown advantages in operation of silicon devices at much lower temperatures below carrier freezeout. This will require new research and possibly novel devices in silicon. One motivation for this endeavor is the need for integration of low temperature sensors, both Si and other materials, with the associated signal processing circuitry. Variations in dopant can alter the carrier freezeout temperature. One may find new dependencies on such effects as fluctuation in doping concentration, radiation hardness dependence on lower temperatures, and possibly replacement of oxide insulators with nitrides.

Disadvantages in low temperature operation revolve about the refrigerator, access to the electronic system, reduced heat removal ability in LN $_2$  compared to fluorocarbons coupled with increased heat dissipation for faster logic, and the added problem of cryocooling for small digital systems.

Topics recommended for R & D reflected the areas of interest and possible improvement in silicon devices, low temperature CMOS, "carrier freezeout" devices, low temperature effects on radiation hardness, possible process technology changes for low temperature devices, and the design and process changes which might further enhance reliability through reduction in thermally activated degradation mechanisms.

# NON-SILICON MATERIALS, PRINCIPALLY GaAs

This discussion session covered a wide range of materials and structures including III-V and II-VI compound semiconductors, epi-technologies and heterojunction devices, and both analog and

digital electronics. Since silicon is the established electronic technology, suggestions were tested by comparison to silicon, and to cooled silicon as presented at this workshop.

GaAs is presently finding a niche in analog microwave circuitry. Cooling to low temperatures lowers the device noise. except for 1/f noise, which will permit either deployment of smaller antennas or greater probability of intercept for weak signal transmissions. One may be able to develop a viable insulated gate technology at low temperatures in non-silicon because the surface state problems may be alleviated by extremely long lifetimes. Better noise margins in low noise devices may permit reduction of the digital voltage swings and hence lower power dissipation in digital circuitry. Coupled with the much greater mobilities of these materials, this could lead to faster real-time digital signal processors. This large mobility increase will also lead to higher frequency operation of microwave devices. As with silicon, reliability is expected to improve by reduction of thermal degradation mechanisms. Since many of these materials continue to improve in a significant manner well below 77 K, the reliability improvement should be substantially better than in Si. Compared with Si. carrier freezeout is much less of a problem, leading to the possibility of both FET and bipolar devices.

As with silicon, the disadvantages of cooling are the inconvenience of the refrigerator, the reduced heat removal rate, the difficulty of optimizing designs and testing at the low temperature, and the thermal cycling of the associated structures. In addition, the problems of optimizing thermal transition designs are more severe in analog applications where one is required to minimize both thermal conductance and microwave signal attenuation. Compared with silicon, where the application of cooling appears to be large main frame computers, the application of other cold semiconductors is projected in smaller analog and digital systems. Thus, the refrigerator is not merely a replacement for a conventional cooling system, but an added burden on system integration. Nevertheless, in areas of significant improvement this burden can be accommodated. An example of this is the present trend in high performance radio astronomy receivers which use both superconducting quasiparticle mixers and cooled GaAs low noise amplifiers.

Recommendations for R & D in the area of non-silicon materials relate to materials, processes, and system problems. Specifically included were heterojunction structures such as modulation doped and high- $\beta$  bipolar devices. Of particular interest here were processing technology, noise performance, and bandwidth. In the area of materials technology, epi-techniques are used to significantly improve material purity, uniformity, and stoichiometry, and to eliminate alloy scattering. Ternary materials with improved transport properties, traveling wave devices, and semiconductor insulators were suggested as

potentially productive areas. Other materials which should be considered are small bandgap semiconductors because of their high mobility and low voltage operation. This could include InAs, InSb, and Ge, and also IGFET structures. The problem of both intra-chip and inter-chip signal propagation was recognized as one pushes to higher frequency or greater speed with high density lithography. Both optical and superconducting interconnects were suggested as possible solutions, particularly if monolithic structures could be developed.

# REFRIGERATION

The introduction of cryogenic refrigeration will be a major step required for cold semiconductor electronics. The availability of closed-cycle cryocoolers will extend the operating temperature to 77 K, 20 K, and even below 4 K, depending on the semiconductor technology and application. Generally speaking, at least in the near-term, silicon computers would expect to operate near 77 K, with GaAs amplifiers and signal processors near 20 K, and detectors and sensors at the lowest temperatures. The nature of the refrigerator will depend strongly on the application and the operating environment-commercial, military, or space.

Refrigeration design choices will depend on the required reliability, allowable service interval, and acceptable cost, size, weight, and efficiency. Cryocoolers for large main frame computers at 77 K fall into the Gifford-McMahon (G-M) type and are available based on existing technology. This technology can also provide cooling down to 10 K at the 1 W refrigeration level; a combination of Joule-Thomson (J-T) and G-M cycles can provide cooling below 10 K and down to the 1 W power level in an office or laboratory environment with existing technology. Below 1 W, the split Stirling provides cooling to 15 K and 100 mW capacity. The region bounded by 1 W capacity and 15 K temperature is presently unsupported by existing technology and requires development for small system application. The very low power region may be satisfied by "plastic split Stirling" and small J-T machines.

A major problem with long continuous operation of a cryocooler is contamination of the working gas, commonly from seals or the compressor. Characteristically, regenerative systems are less sensitive to contaminants than J-T. It is desirable to keep the operating cryostat gas separate from the refrigerator gas, and to avoid a common vacuum. For operational purposes, it is desirable to have a liquid cryogen reservoir. The entire refrigerator should be designed and constructed as a self-contained unit.

Recommendations include a continuation of R & D on regenerative cycles to achieve 4 K operation at the 10 mW to 1 W power level, on closed cycle J-T systems, and on compressor

development for low power, continuous operating systems. LaNi $_5$  hydride  $\rm H_2$  solid state compressors, magnetic cold stages, and pulse tubes were cited as examples of alternative approaches to new refrigerator components.

#### V. NEEDED RESEARCH AND DEVELOPMENT

A primary goal of the Cold Electronics Workshop was to serve as a forum for recommendations of needed research and development. As a result of the Workshop, the following areas for future work were identified:

- 1. Basic investigations should be carried out on low-temperature properties of conductive and insulating materials used in integrated circuits to complement the work done on device characteristics. Systematic studies of resistivity and electromigration are needed for conductors, particularly for the newer metallization schemes being adopted in advanced-design ICs, and of dielectric properties and charge trapping for insulators.

- 2. Experimental confirmation of predicted improvements in reliability of electronic devices and circuits at low temperatures should be undertaken.

- 3. The tolerance at low temperatures of semiconductor devices and circuits to ionizing radiation should be investigated since it is suspected that reducing the temperature will have a detrimental effect.

- 4. Development should be continued and expanded on applications of cold electronics for use in conjunction with low-temperature sensors. Small-to-medium scale electronic systems for processing of signals from IR detectors, superconducting magnetometers, and similar scientific instruments would be valuable for both earth-based and spacecraft-borne applications.

- 5. Research and development on devices and circuits should be pursued vigorously, since they constitute the heart of any electronic system. Evaluation of their low-temperature applicability and performance should be continued as technological advances are made for room-temperature electronics, such as those arising from improved capabilities related to device dimensions coupled with control of crystal growth on an atomic scale. Equally important, additional research should be undertaken on materials, devices, and fabrication methods more suitable or optimized for low temperatures, many of which might not be useful for room temperature electronics. Quantum effects which could be troublesome in conventional devices might be taken advantage of in novel device designs.

- 6. Development of assembly and packaging materials and techniques is necessary to realize satisfactory performance in practical electronic systems at low temperatures. The electrical, thermal, and mechanical properties of materials at low temperatures need to be considered to take full advantage of the potential for improved performance of cold electronics. Techniques for effective electrical and mechanical interfaces

between cold electronics and room temperature electronics are needed.

7. Refrigeration must continue to be developed concurrently in order to make practical use of developments in cold electronics. New techniques are needed to provide cooling for measuring instruments for use outside the cryogenics laboratory and by persons who do not have a background in cryogenic techniques. For such applications, a need exists for the development of coolers that are compact, convenient, and reliable. In addition, many applications cannot tolerate the vibration, and temperature and magnetic fluctuations common in available designs. Cooling methods other than those based on mechanical systems and gas-liquid phases should be investigated.

Finally, the many interesting opportunities for fundamental research provided by electronic structures and devices at low temperatures should not be overlooked. For example, there are effects related to quantum behavior, "collisionless" carrier dynamics, superlattices, and confined particles.

#### APPENDIX A

#### COLD ELECTRONICS WORKSHOP

#### PROGRAM

## Tuesday, October 4, 1983

| 9:00 a.m. | Welcome to JPL                                                                                  | T. Cole<br>JPL                            |

|-----------|-------------------------------------------------------------------------------------------------|-------------------------------------------|

| 9:10      | A Word From Our Sponsor                                                                         | E. Edelsack<br>ONR                        |

| 9:15      | Recent Developments in Semi-<br>conductor Research                                              | M. Yoder<br>ONR                           |

| 9:55      | Novel Low Temperature Devices                                                                   | J. Lambe<br>JPL                           |

| 10:35     | coffee break                                                                                    |                                           |

| 10:55     | Refrigeration                                                                                   | R. Radebaugh<br>NBS                       |

| 11:35     | Physical Electronics of Cooled<br>Operation of Very Short Compound<br>Semiconductor Transistors | L. F. Eastman<br>Cornell University       |

| 12:15     | lunch                                                                                           |                                           |

| 1:30      | Why Consider MOSFET Operation in<br>Liquid Nitrogen?                                            | F. H. Gaensslen<br>IBM                    |

| 2:10      | Effect of Cooling on Delay Time<br>Limits in Integrated Circuits                                | R. Grondin<br>Arizona State Univ.         |

| 2:50      | coffee break                                                                                    |                                           |

| 3:10      | SiMOS Devices at Low Temperatures                                                               | A. Kamgar<br>A T & T<br>Bell Laboratories |

| 4:15      | Tour of JPL                                                                                     |                                           |

| 7:00      | Reception and Dinner                                                                            | Holiday Inn                               |

## Wednesday, October 5, 1983

| 9:00 a.m. | Cryogenically Co<br>Microwave Receiv<br>Status and Futur | S. Weinreb<br>NRAO         |                             |  |

|-----------|----------------------------------------------------------|----------------------------|-----------------------------|--|

| 9:40      | Cryogenic Amplif<br>Detection                            | F. Low<br>Univ. of Arizona |                             |  |

| 10:15     | coffee break                                             |                            |                             |  |

| 10:35     | Individual Discu                                         |                            |                             |  |

| locations | Si and VLSI: 180-10;                                     | Refrigeration 230-115      | Other Materials 264-739     |  |

| 12:15     | lunch                                                    |                            |                             |  |

| 1:30      | Main Discussion 180-101                                  | Session                    | Chairman:<br>A. Silver, TRW |  |

Workshop Organizer: E. Tward (818) 354-6581 Secretary: Genevieve McKay (818) 354-2301

#### APPENDIX B

#### LIST OF PARTICIPANTS

Richard L. Anderson University of Vermont Burlington, VT 05405 (802) 656-3330

Michael Balister

National Radio Astronomy

Observatory

2015 Ivy Road

Charlottesville, VA 22903

(804) 296-0365

Juan Javier Bautista JPL M.S. 238-737 (818) 354-6994

James A. Beall Division 724.03 National Bureau of Standards 325 Broadway Boulder, CO 80303 (303) 497-5989

Richard Brandt

Office of Naval Research

1030 E. Green

Pasadena, CA 91106

(818) 795-5971

A. Carlan (Aerospace Corporation) 4951 Rock Valley Rd. Rancho Palos Verdes, CA 90274 (213) 377-8273

C. K. Chan JPL M.S. 183-901 (818) 354-2777

Frank Chang MRDC, 1049 Camino Dos Rios P.O. Box 1085 Thousand Oaks, CA 91360 (805) 498-4545, x. 198 Robert C. Clauss JPL M.S. 264-801 (818) 354-3398

Terry Cole JPL M.S. 180-500 (818) 354-5458

Larry R. Cooper Code 414 Office of Naval Research Arlington, VA 22217 (202) 696-4214

Michael W. Cromar Division 724.03 National Bureau of Standards 325 Broadway Boulder, CO 80303 (303) 497-5375

Lester Eastman 425 Phillips Hall Cornell University Ithaca, NY 14853 (607) 256-4369

Edgar Edelsack Code 414 Office of Naval Research 800 N. Quincy Street Arlington, VA 22217 (202) 696-4218

F. H. Gaensslen IBM Corporation Old Orchard Road Armonk, NY 10504 (914) 765-3125

Robert Grondin Arizona State University Tempe, AZ 85287 (602) 965-5954 Victor Hadek JPL M.S. 183-401 (818) 354-7054

Richard E. Harris Division 724.03 National Bureau of Standards 325 Broadway Boulder, CO 80303 (303) 497-3776

H. W. Jackson JPL M.S. 183-401 (818) 354-6598

Richard C. Jaeger 207 Dunstan Hall Auburn University, AL 36849 (205) 826-4330

Dean Johnson JPL M.S. 238-737 (818) 354-4952

A. Kamgar Room 213-306 A T & T Bell Laboratories Murray Hill, NY 07946 (201) 582-3924

John H. Ketzler 4290 Fernwood Avenue St. Paul, MN 55112 (612) 482-3830

Randall K. Kirschman P.O. Box 391716 Mountain View, CA 94039 (415) 369-7531

Peter Kittel M.S. 244-7 NASA-Ames Research Center Moffett Field, CA 94035 (415) 965-6525 W. A. Kleinhans (Rockwell International) 2545 N. Hesperian Santa Ana, CA 92706 (714) 835-3491

Clifford M. Krowne Code 6851 Naval Research Laboratory Washington, D.C. 20375 (202) 767-3526

Al Kudirka JPL M.S.157-102 (818) 354-2738

John Lambe JPL M.S. 122-123 (818) 354-8238

Chien-Ping Lee Rockwell International - MRDC 1049 Camino Dos Rios Thousand Oaks, CA 91360 (805) 498-4545 x 119