Contractor Report Number: CR180817

# ONBOARD PROCESSING SATELLITE NETWORK ARCHITECTURE AND

CONTROL STUDY

**FINAL REPORT**

NASA CONTRACT NAS3-24886

**JUNE 1987**

PREPARED BY

S. JOSEPH CAMPANELLA

**BENJAMIN A. PONTANO**

AND

HARVEY CHALMERS

COMSAT LABORATORIES

CLARKSBURG, MARYLAND

### ABSTRACT FINAL REPORT

## ONBOARD PROCESSING SATELLITE NETWORK ARCHITECTURE AND CONTROL STUDY CONTRACT NAS3-24886

S. JOSEPH CAMPANELLA BENJAMIN PONTANO HARVEY CHALMERS

COMSAT LABORATORIES CLARKSBURG, MARYLAND

For satellites to remain a vital part of future national and international communications, new system concepts that use their inherent advantages to the fullest must be created. This study is devoted to exploring new network architectures that take maximum advantage of satellites equipped with onboard processing.

New satellite generations must accommodate various services for which satellites constitute the preferred vehicle of delivery. Such services tend to be those that are widely dispersed and present thin to medium loads to the system. Typical services considered are thin and medium route telephony, maritime, land and aeronautical radio, VSAT data, low bit rate video teleconferencing and high bit rate broadcast of high definition video. The study considers delivery of services by TDMA and FDMA multiplexing techniques and combinations of the two for individual and mixed service types. Onboard processing is an essential part of the system architecture as it applies to the switching to rearrange the uplink signals into the downlink signals and serving hopping pencil beams. The possibilities offered by onboard circuit switched and packet switched architectures are examined and the results strongly support a preference for the latter. The memory used in the switch is designed to minimize its size by using advantageously the storage of signals in the space immediately in front of the antenna. A detailed design architecture encompassing the onboard packet switch and its control, the related demand assigned TDMA burst structures, and destination packet protocols for routing traffic are presented. Important features such as distributed network control, acquisition and synchronization, demand assignment, and advantageous use of voice and data activity to achieve channel multiplication are considered. Fundamental onboard hardware requirements comprising speed, memory size, chip count, and power are estimated. The study concludes with identification of key enabling technologies and identifies a plan to develop a POC model.

# ONBOARD PROCESSING NETWORK ARCHITECTURE AND CONTROL STUDY FINAL REPORT

#### TABLE OF CONTENTS

| 1.  | Introduction | n                                         | 1.1 |

|-----|--------------|-------------------------------------------|-----|

| 1.1 | Networks a   | and Services                              | 1.1 |

|     | 1.1.1        | Spot Beam Considerations                  | 1.1 |

|     | 1.1.2        | Demand Assigned, Multiple Access Networks | 1.2 |

|     | 1.1.3        | Intersatellite Links                      | 1.3 |

|     | 1.1.4        | Summary Of Objectives                     | 1.3 |

| 1.2 | Summary of   | of Contract Tasks                         | 1.3 |

|     | 1.2.1        | Task 1 - Network Architecture             | 1.3 |

|     | 1.2.2        | Task 2 - Network Control                  | 1.5 |

|     | 1.2.3        | Task 3 - Technology Challenges            | 1.6 |

| 2.  | Network A    | rchitectures                              | 2.1 |

| 2.1 | Services C   | arried                                    | 2.1 |

|     | 2.1.1        | Identification Of Services                | 2.1 |

|     | 2.1.2        | Categories Of Services                    | 2.2 |

| 2.2 | Future Cor   | nmunications Satellite Payloads           | 2.4 |

|     | 2.2.1        | International Services And Extrapolations | 2.5 |

|     | 2.2.2        | Domestic Services And Extrapolations      | 2.6 |

| 2.3 | Network O | ptions                                                  | 2.7  |

|-----|-----------|---------------------------------------------------------|------|

|     | 2.3.1     | Simple Global Beam Networks                             | 2.7  |

|     | 2.3.2     | Regional Beam Networks                                  | 2.8  |

|     | 2.3.3     | Spot Beam Networks                                      | 2.9  |

|     | 2.3.3.1   | Spot Beam Advantages                                    | 2.9  |

|     | 2.3.3.2   | Spot Beam Connectivity                                  | 2.9  |

|     | 2.3.3.3   | Hopping Spot Beams                                      | 2.10 |

|     | 2.3.4     | Onboard Switching And Storage                           | 2.10 |

|     | 2.3.4.1   | Operating Without Onboard Storage                       | 2.10 |

|     | 2.3.4.2   | Operating With Onboard Storage                          | 2.11 |

|     | 2.3.4.3   | Comparing Operation Without And With<br>Onboard Storage | 2.11 |

|     | 2.3.4.4   | Examples Of Operating Without And With Onboard Storage  | 2.12 |

|     | 2.3.5     | Intersatellite Links                                    | 2.15 |

| 2.4 | Transmiss | ion Configurations                                      | 2.16 |

|     | 2.4.1     | FDMA                                                    | 2.16 |

|     | 2.4.2     | TDMA                                                    | 2.16 |

|     | 2.4.3     | MF/TDMA                                                 | 2.17 |

|     | 2.4.4     | CDMA                                                    | 2.18 |

|     | 2.4.5     | Transmission Configurations                             | 2.19 |

|     | 2.4.5.1   | FDMA-FDMA Operation                                     | 2.19 |

|     | 2.4.5.2  | FDMA-TDM/TDMA Operation                             | 2.22 |

|-----|----------|-----------------------------------------------------|------|

|     | 2.4.5.3  | TDMA-TDMA Operation                                 | 2.23 |

|     | 2.4.5.4  | TDMA-TDM/TDMA Operation                             | 2.24 |

|     | 2.4.5.5  | MF/TDMA-TDM/TDMA Operation                          | 2.24 |

|     | 2.4.5.6  | MF/TDMA-MF/TDMA Operation                           | 2.25 |

| 2.5 | Computer | And Data Communications                             | 2.26 |

|     | 2.5.1    | Packet Communications On ACTS                       | 2.26 |

|     | 2.5.1.1  | Circuit Switched Operation                          | 2.26 |

|     | 2.5.1.2  | Stationary Preassigned Channel Operation            | 2.27 |

|     | 2.5.1.3  | Future Onboard Packet Node                          | 2.28 |

|     | 2.5.2    | Configurations For Computer And Data Communications | 2.29 |

|     | 2.5.2.1  | Circuit Switched Operation                          | 2.29 |

|     | 2.5.2.2  | Random Access With Preassigned Circuits             | 2.31 |

|     | 2.5.2.3  | Onboard Packet Node Data Transmission               | 2.32 |

|     | 2.5.2.4  | Comparison Of The Data Communications<br>Techniques | 2.33 |

| 2.6 | Advanced | Satellite Telecommunications Options                | 2.38 |

|     | 2.6.1    | Advanced Network Control                            | 2.38 |

|     | 2.6.1.1  | Call Processing On Board The Satellite              | 2.38 |

|     | 2.6.1.2  | Destination Directed Onboard Switching              | 2.39 |

|     | 2.6.2    | Memory In Space                                     | 2.40 |

|     | 2.6.3                    | Integrating In Other Services                | 2.41 |

|-----|--------------------------|----------------------------------------------|------|

|     | 2.6.3.1                  | Capability To Accommodate Different Services | 2.41 |

|     | 2.6.3.2                  | Synchronization Among Different Services     | 2.41 |

|     | 2.6.3.3                  | Source Coding Considerations                 | 2.42 |

| 3.  | Destination<br>Architect | n Directed Packet Onboard Processing ture    | 3.1  |

| 3.1 | System De                | esign                                        | 3.1  |

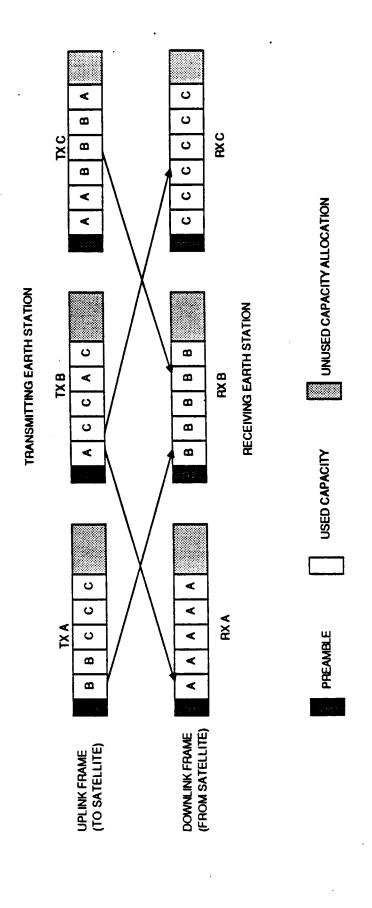

|     | 3.1.1                    | Demand Assignment of Capacity                | 3.1  |

|     | 3.1.1.1                  | Destination Addresses Packet Message         | 3.2  |

|     | 3.1.2                    | Method of Operation                          | 3.3  |

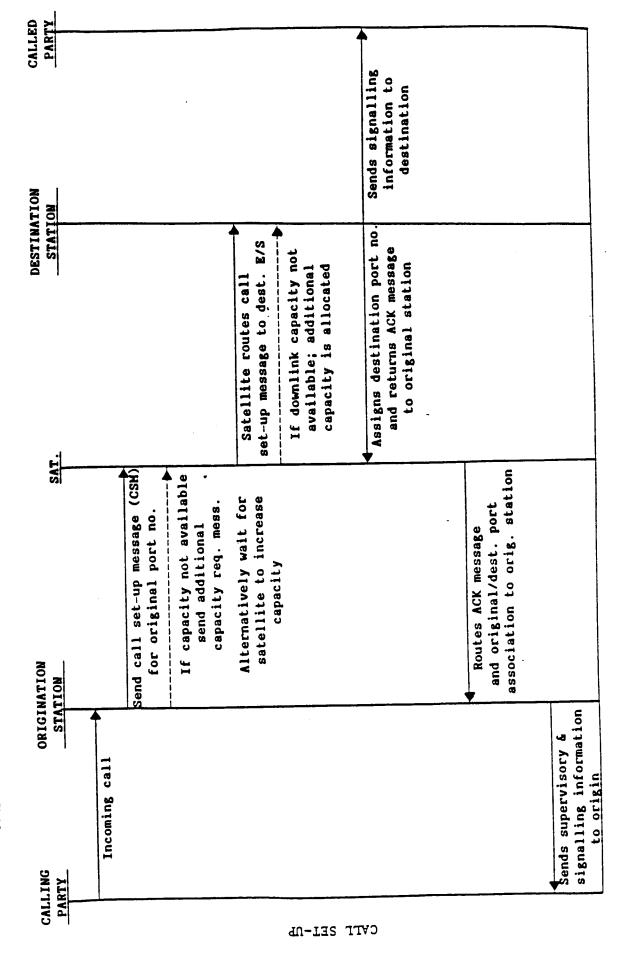

|     | 3.1.2.1                  | Call Set-Up Procedure                        | 3.3  |

|     | 3.1.2.2                  | Call In Progress Procedure                   | 3.4  |

|     | 3.1.2.3                  | Call Termination                             | 3.5  |

|     | 3.1.2.4                  | Mapping Functions                            | 3.5  |

|     | 3.1.2.5                  | Detailed Call Set-Up Procedure               | 3.6  |

|     | 3.1.2.6                  | Detailed Call In Progress Procedure          | 3.6  |

|     | 3.1.2.7                  | Detailed Call Termination Procedure          | 3.9  |

|     | 3.1.3                    | Packet Frame Efficiency                      | 3.9  |

|     | 3.1.4                    | Digital Speech Interpolation                 | 3.10 |

|     | 3.1.5                    | Acquisition and Synchronization Control      | 3.10 |

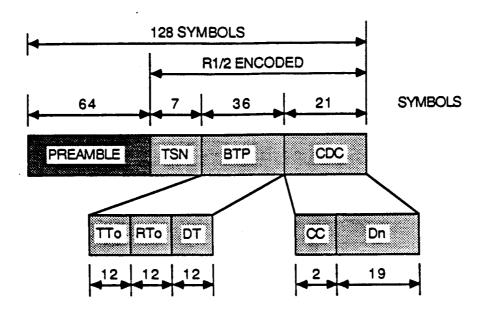

|     | 3.1.5.1                  | Reference Bursts                             | 3.11 |

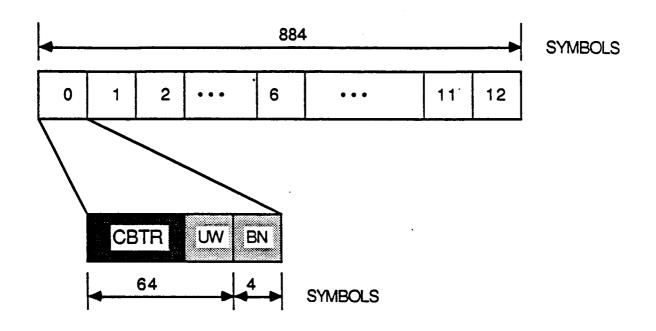

|     | 3.1.5.2                  | Uplink Request Bursts                        | 3.12 |

PAGE 4

|     | 3.1.5.3     | Acquisition and Synchronization Procedure            | 3.12 |

|-----|-------------|------------------------------------------------------|------|

|     | 3.1.6       | Overall Frame Efficiency                             | 3.13 |

|     | 3.1.7       | Onboard Switch Architectures                         | 3.15 |

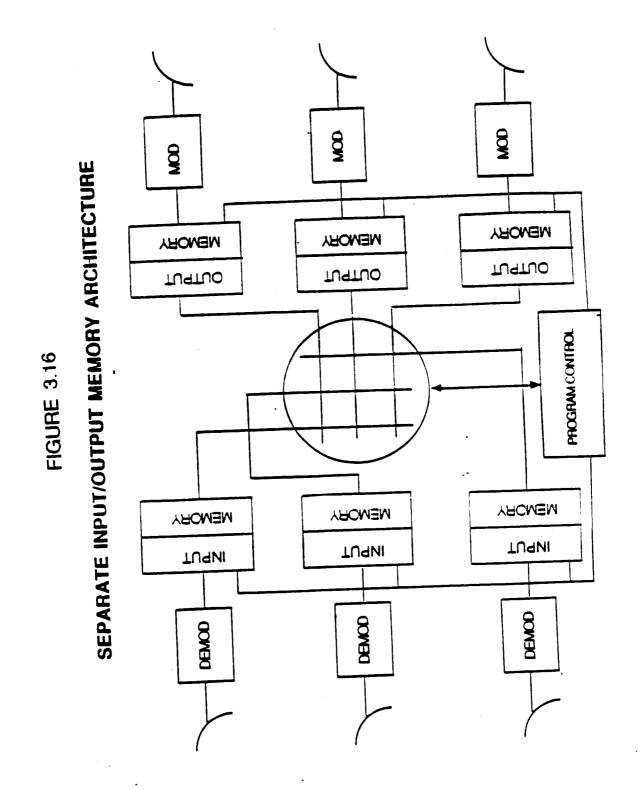

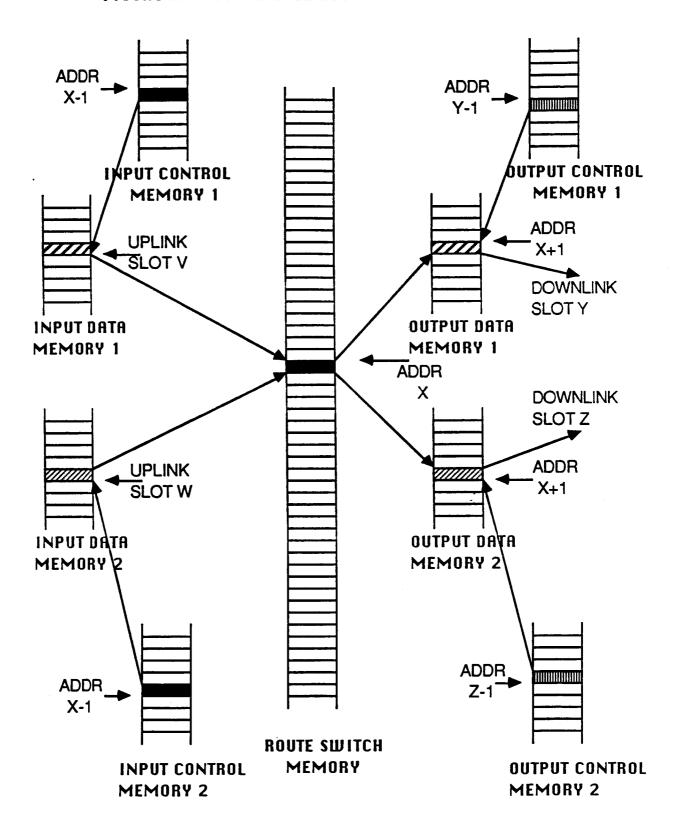

|     | 3.1.7.1     | Separate Input/Output Memory Architecture            | 3.15 |

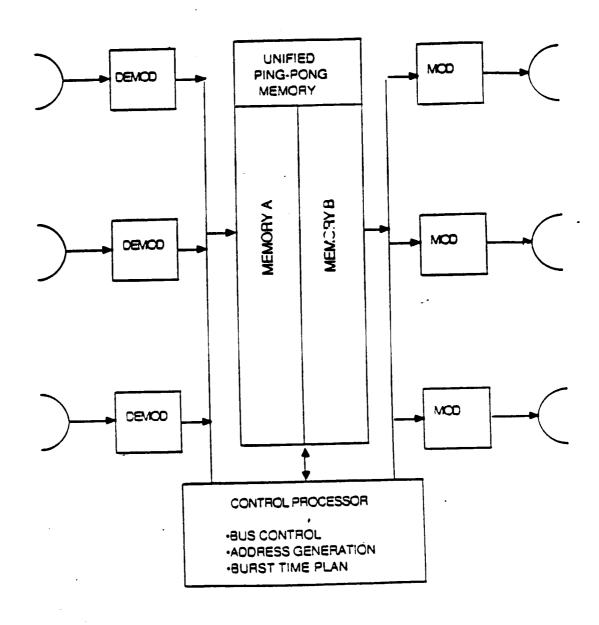

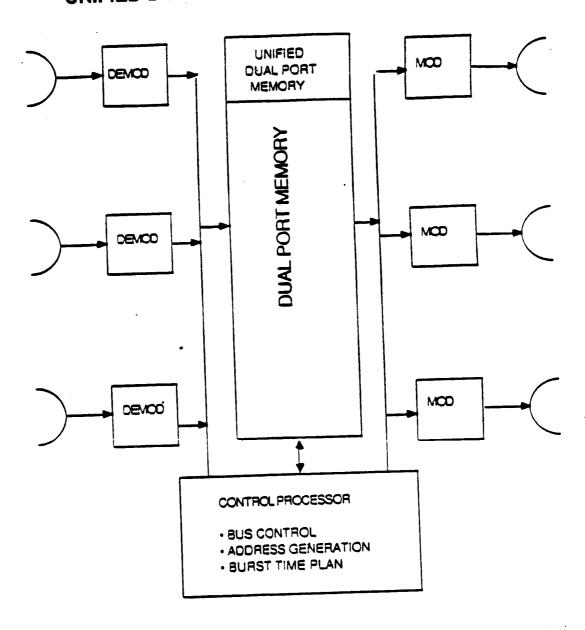

|     | 3.1.7.2     | Unified Memory Architecture                          | 3.16 |

| 3.2 | Baseband I  | Processing Implementation                            | 3.19 |

|     | 3.2.1       | Separate Input/Output Memory Architecture            | 3.19 |

|     | 3.2.1.1     | Separate Input/Output Memory Hardware Implementation | 3.21 |

|     | 3.2.1.1.1   | System Memory Requirements                           | 3.22 |

|     | 3.2.1.1.1.1 | Input/Output Memory Requirements                     | 3.23 |

|     | 3.2.1.1.1.2 | Control Memory Requirements                          | 3.24 |

|     | 3.2.1.1.1.3 | Switch State Memory Requirements                     | 3.25 |

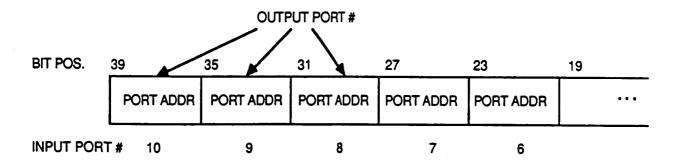

|     | 3.2.1.1.1.4 | Packet Header Memory and Control                     | 3.26 |

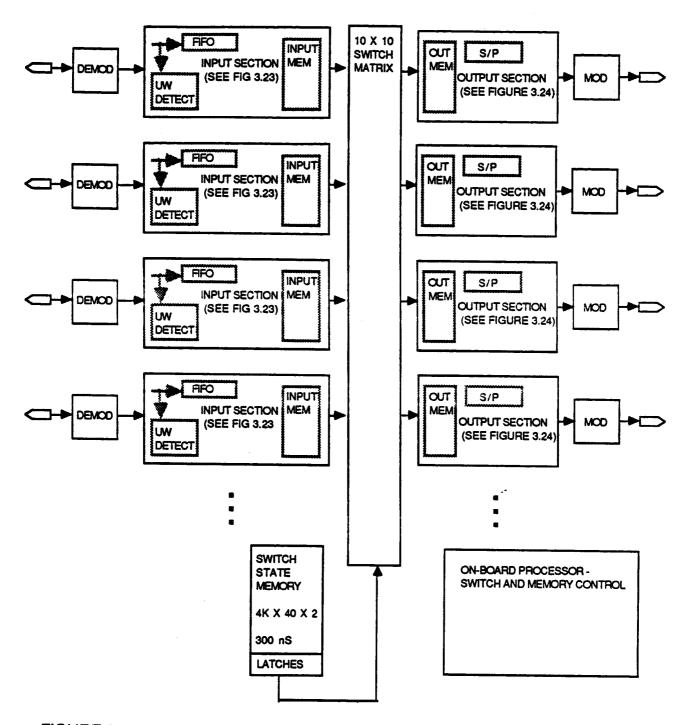

|     | 3.2.1.1.2   | Separate Memory System Block Diagram                 | 3.27 |

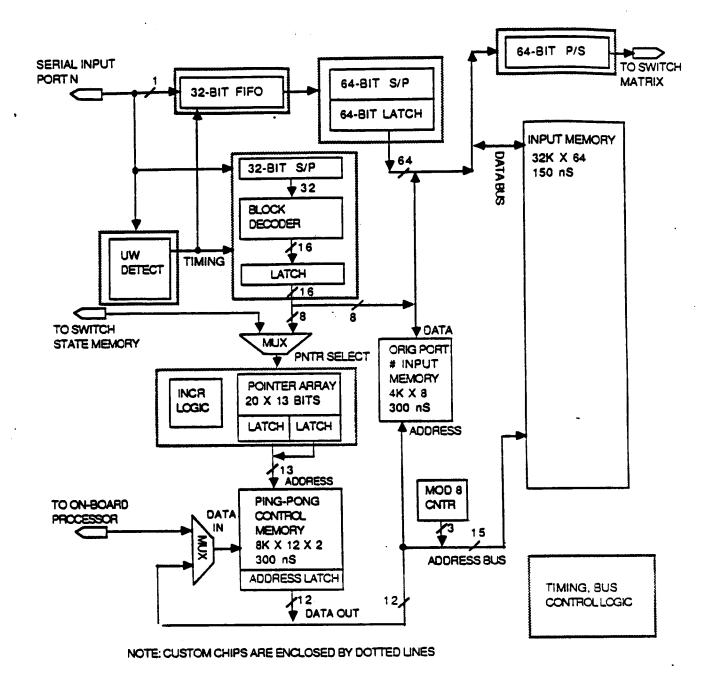

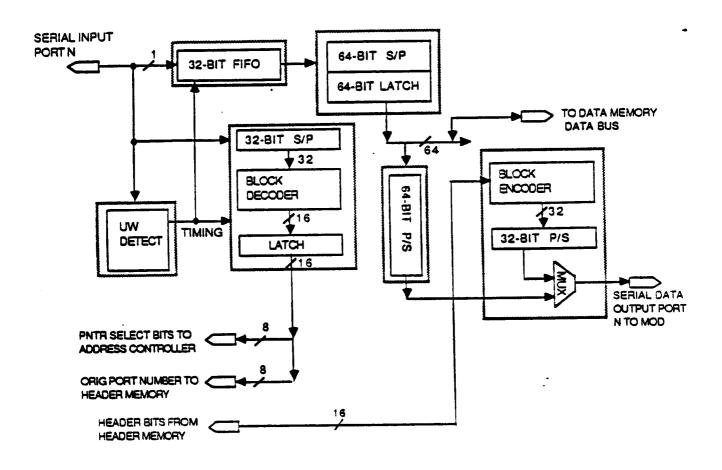

|     | 3.2.1.1.2.1 | Input Subsystem Block Diagram                        | 3.28 |

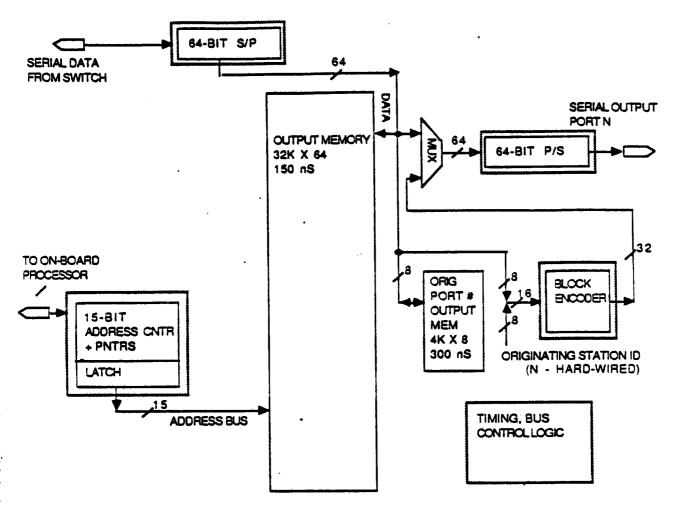

|     | 3.2.1.1.2.2 | Output Subsystem Block Diagram                       | 3.29 |

|     | 3.2.1.2     | Conclusions - Separate Memory Architecture           | 3.31 |

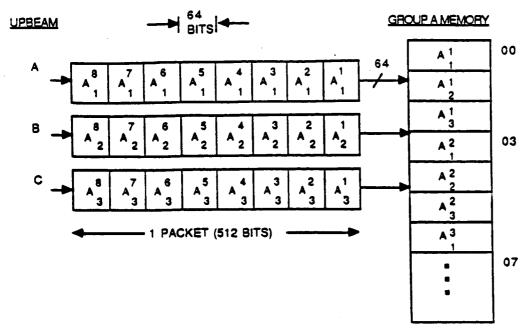

|     | 3.2.2       | Unified Memory Architecture                          | 3.32 |

|     | 3.2.2.1     | Unified Memory Hardware Implementation               | 3.35 |

|     | 32211       | System Memory Requirements                           | 3 35 |

|     | 3.2.2.1.1.1 | Unified Data Memory Requirements                              | 3.36 |

|-----|-------------|---------------------------------------------------------------|------|

|     | 3.2.2.1.1.2 | Unified Header Memory Requirements                            | 3.36 |

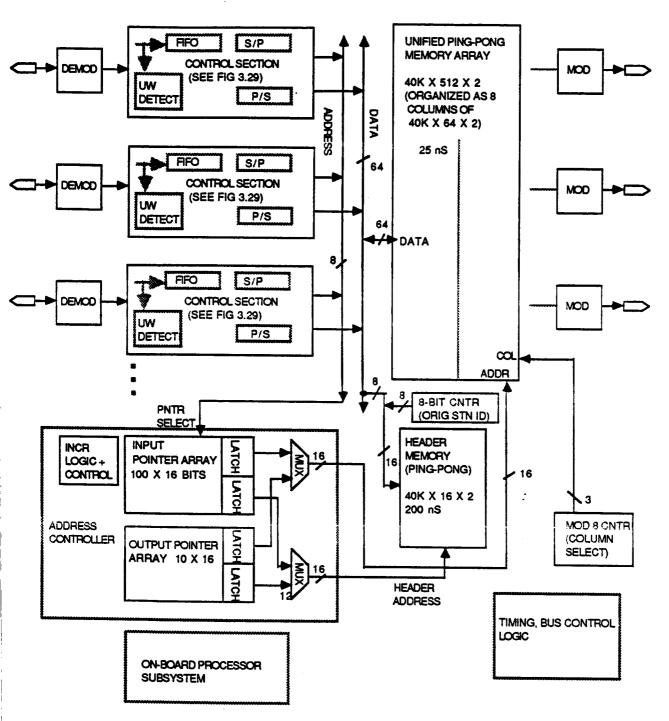

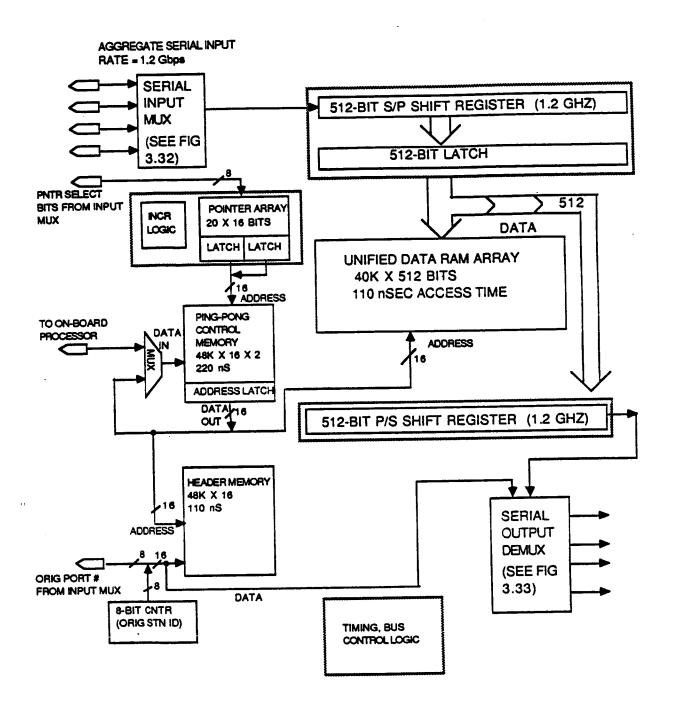

|     | 3.2.2.1.2   | Unified Memory System Block Diagram                           | 3.37 |

|     | 3.2.2.1.3   | Unified Memory Control Subsystem<br>Block Diagram             | 3.39 |

|     | 3.2.2.2     | Conclusions - Unified Memory Architecture                     | 3.39 |

|     | 3.2.3       | Alternative Unified Memory Architecture                       | 3.40 |

|     | 3.2.3.1     | Alternative Unified Memory Hardware<br>Implementation         | 3.41 |

|     | 3.2.3.1.1   | System Memory Requirements                                    | 3.43 |

|     | 3.2.3.1.2   | Alternative Unified Memory Hardware<br>Block Diagram          | 3.44 |

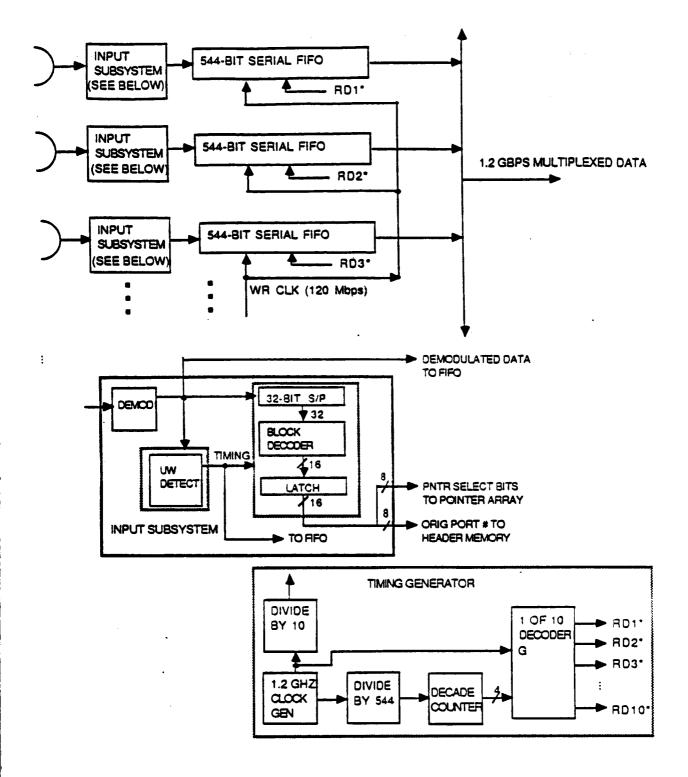

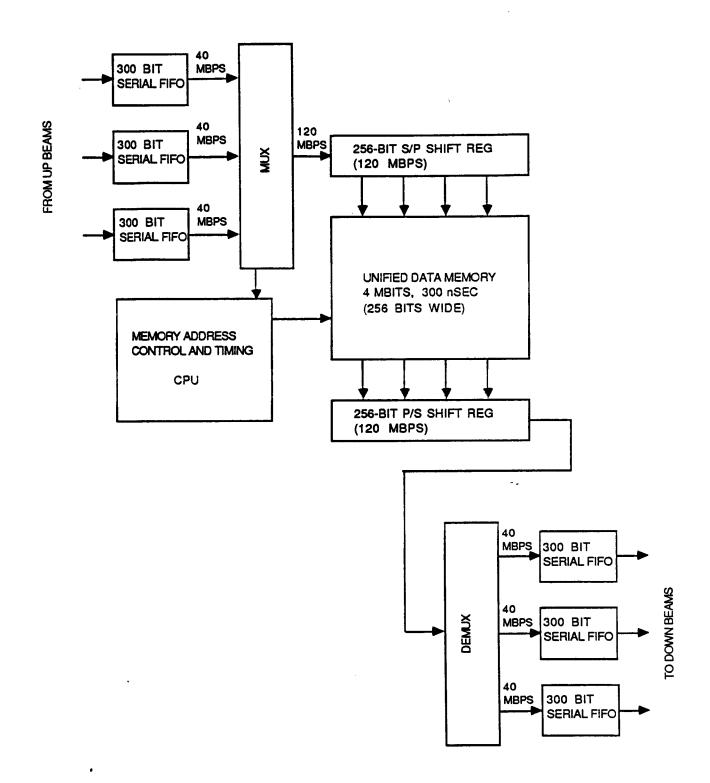

|     | 3.2.3.1.2.1 | Alternative Unified Memory Serial Input<br>Mux Block Diagram  | 3.45 |

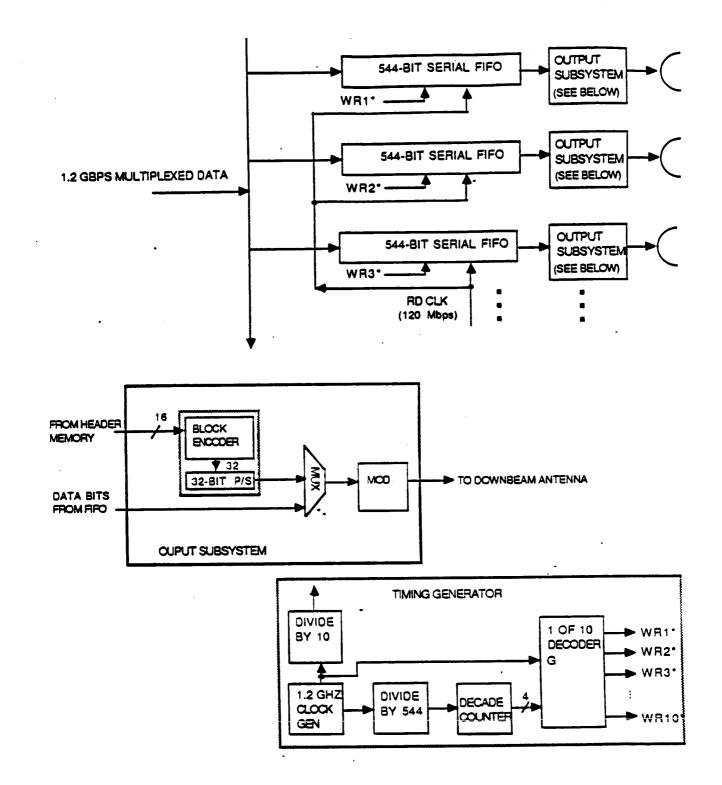

|     | 3.2.3.1.2.2 | Alternative Unified Memory Serial Output<br>Mux Block Diagram | 3.45 |

|     | 3.2.3.2     | Conclusions - Alternative Unified Memory                      | 3.48 |

| 4.  | Integration | Of Other Services                                             | 4.1  |

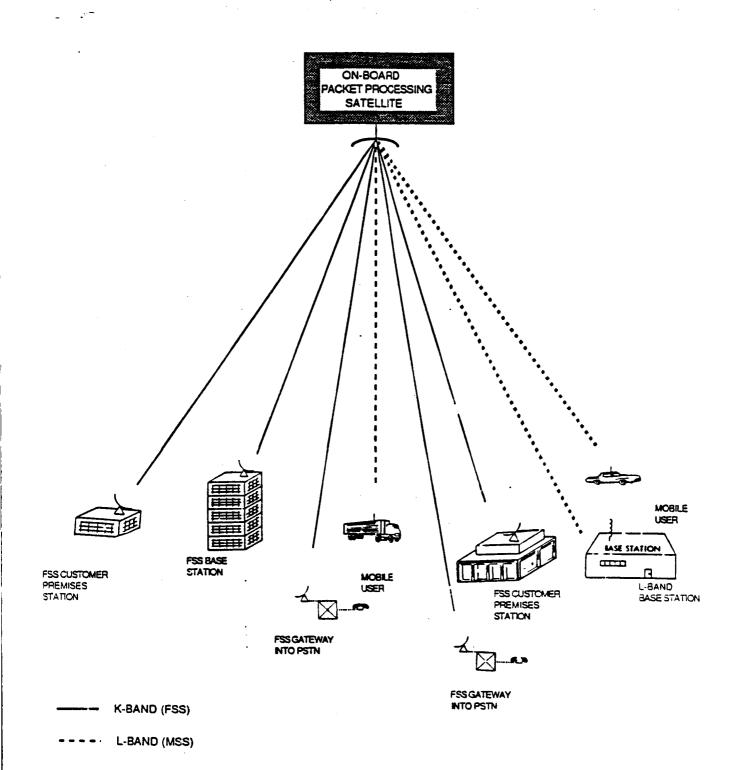

| 4.1 | Mobile Sate | ellite Service                                                | 4.1  |

|     | 4.1.1       | Integrated Fixed Satellite and Land Mobile Satellite Services | 4.1  |

|     | 4.1.2       | System Characteristics                                        | 4.2  |

| 4.2 | Call Set-Up | o Procedures                                                  | 4.3  |

|     | 4.2.1       | Calls Originating at MT to BS or Gateway                      | 4.3  |

|     | 4.2.2                | Calls Originating at BS or Gateway to MT                | 4.4 |

|-----|----------------------|---------------------------------------------------------|-----|

|     | 4.2.3                | Calls Originating at a MT Destined to a MT              | 4.4 |

| 4.3 | Impact on            | the OnBoard Packet Processor                            | 4.5 |

|     | 4.3.1                | Integration Of FSS and MSS                              | 4.5 |

|     | 4.3.2                | MSS Implementation                                      | 4.5 |

|     | 4.3.3                | Difference In Traffic Bit Rates Of MSS/FSS<br>Links     | 4.6 |

| 4.4 | Intersatelli         | te Link Operation                                       | 4.7 |

| 5.  | _                    | y Forecast For Static Ram and<br>Development            | 5.1 |

| 5.1 | Technolog            | y Forecast For Static Rams                              | 5.2 |

| 5.2 | Technolog<br>Logic A | rays                                                    | 5.4 |

| 6.0 | Technolog            | y Development Requirements                              | 6.1 |

| 6.1 | Key Device           | e Development                                           | 6.1 |

|     | 6.1.1                | Custom Logic Devices                                    | 6.2 |

|     | 6.1.2                | Memory Development                                      | 6.2 |

| 6.2 |                      | on Directed Packet Onboard Processing sture Development | 6.2 |

| 6.3 | Destination          | n Directed Packet Network Control Test Bed              | 6.3 |

|     | 6.3.1                | Critical Features To Be Investigated                    | 6.3 |

|     | 6.3.2                | Proposed POC Test Bed Breadboard                        | 6.3 |

| 7   | Reference            | os.                                                     | 7.1 |

#### Appendices

| <b>A.1</b> | Onboard Baseband Switch Call Processing         | A1.1 |

|------------|-------------------------------------------------|------|

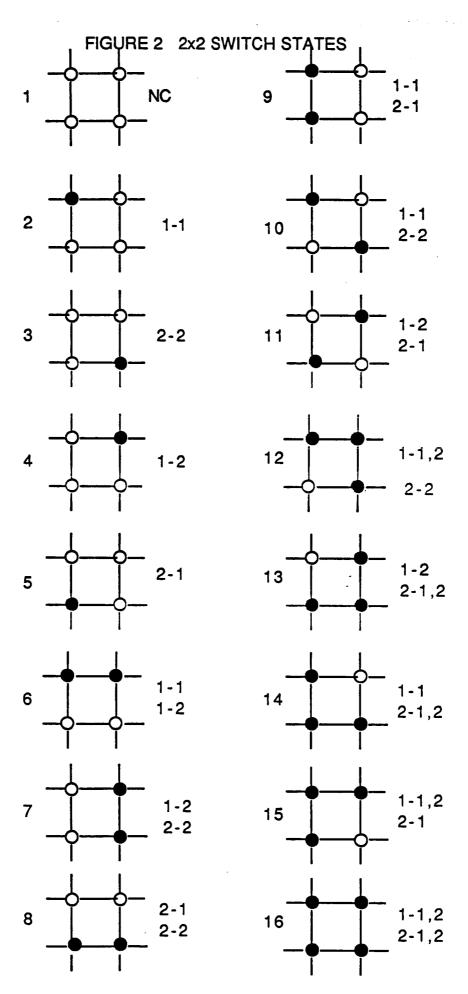

| A.2        | Number of Possible Switch States for MxN Switch | A2.1 |

#### LIST OF FIGURES

| Figure 1.1  | Multi-Service Switching and Routing Satellite Gateway        | 1.7  |

|-------------|--------------------------------------------------------------|------|

| Figure 1.2  | Extended World Coverage With Inter-<br>Satellite Link        | 1.8  |

| Figure 2.1  | Intelsat V Beam Connections                                  | 2.44 |

| Figure 2.2  | Intelsat VI Beam Connections                                 | 2.45 |

| Figure 2.3  | Intelsat VI Beam Connections Using 6X6 MS                    | 2.46 |

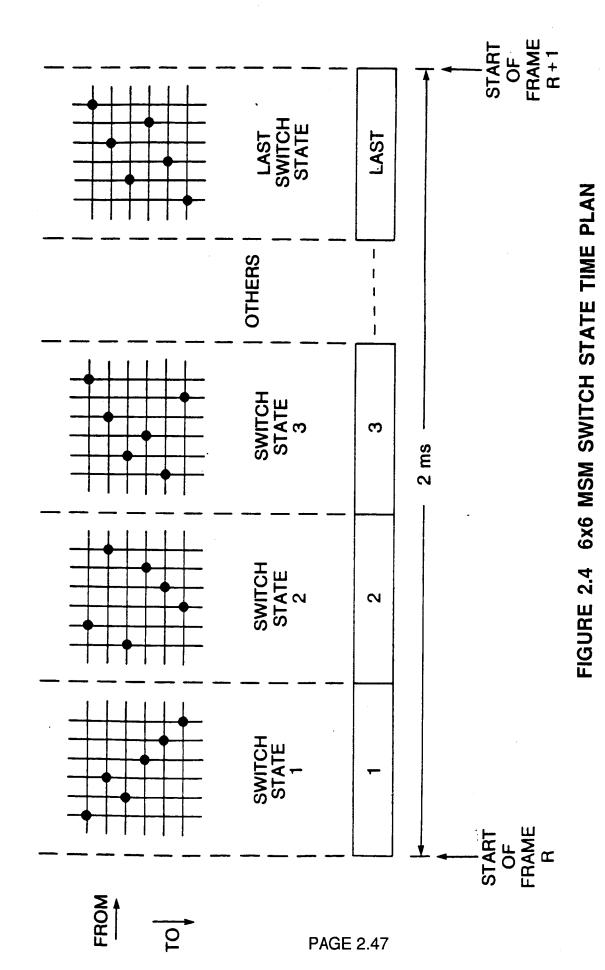

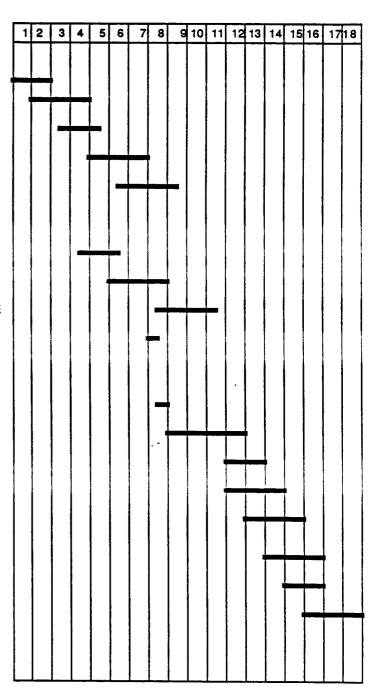

| Figure 2.4  | 6X6 MSM Switch State Time Plan                               | 2.47 |

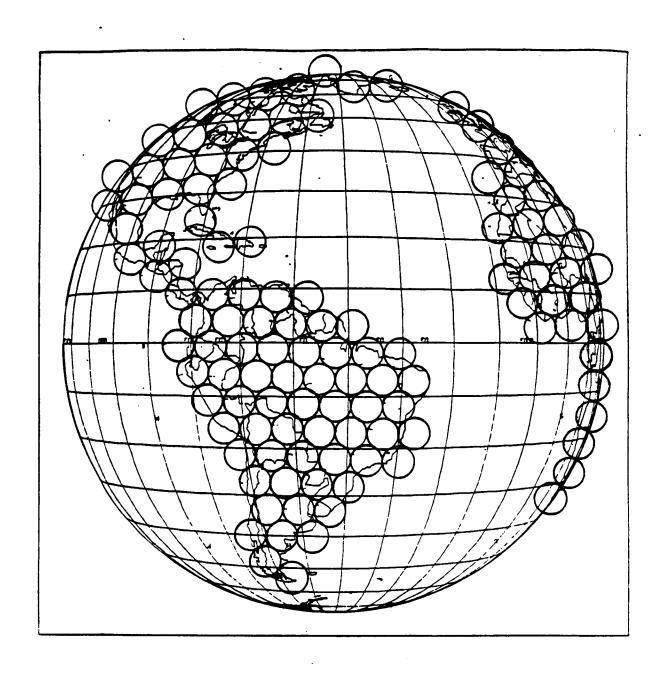

| Figure 2.5  | Spot Beam Antenna Coverage of Atlantic Ocean Basin Countries | 2.48 |

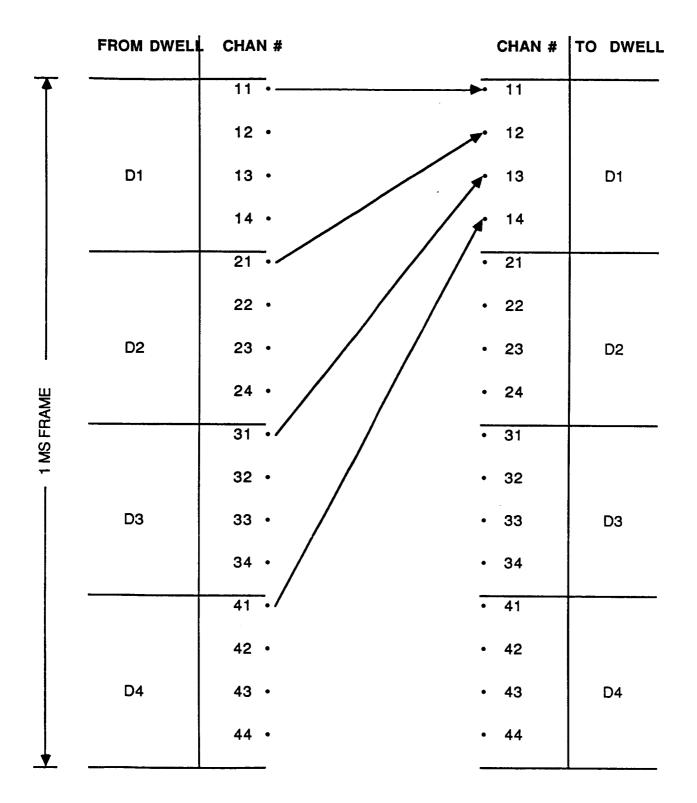

| Figure 2.6  | Preassigned Routes for Random Access TDMA                    | 2.49 |

| Figure 2.7  | Single Down Beam Dwell                                       | 2.50 |

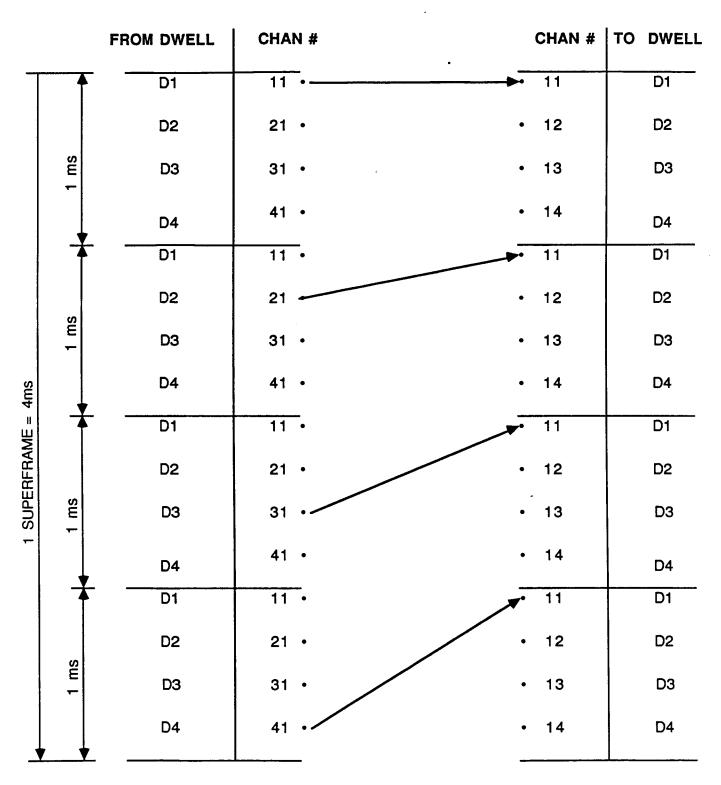

| Figure 2.8  | Preassigned Routes in Superframe For Random Access           | 2.51 |

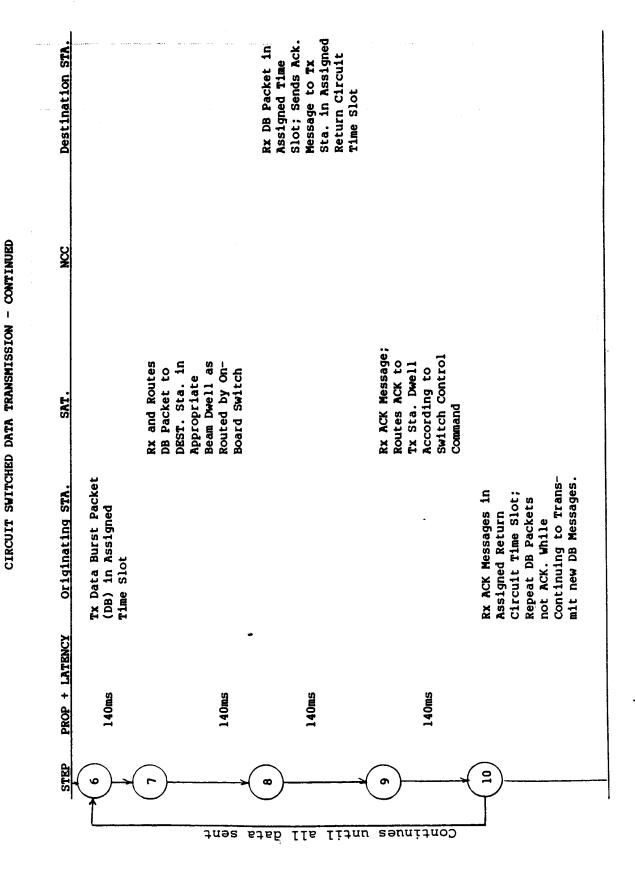

| Figure 2.9  | Circuit Switching Data Transmission                          | 2.52 |

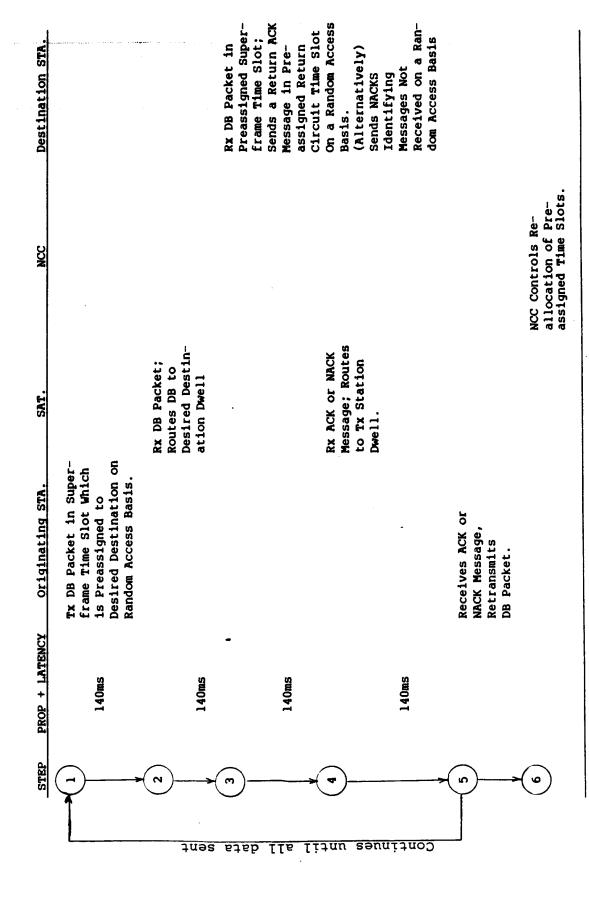

| Figure 2.10 | Random Access Data Transmission with<br>Preassigned Channels | 2.54 |

| Figure 2.11 | On-Board Packet Node Data<br>Transmission                    | 2.55 |

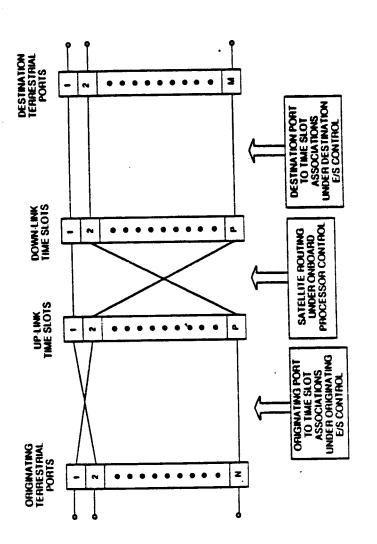

| Figure 3.1  | TDMA/DAMA System with Onboard Processor                      | 3.50 |

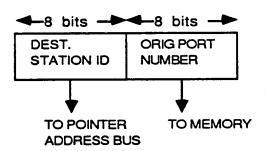

| Figure 3.2  | Uplink Capacity Reallocation                                 | 3.51 |

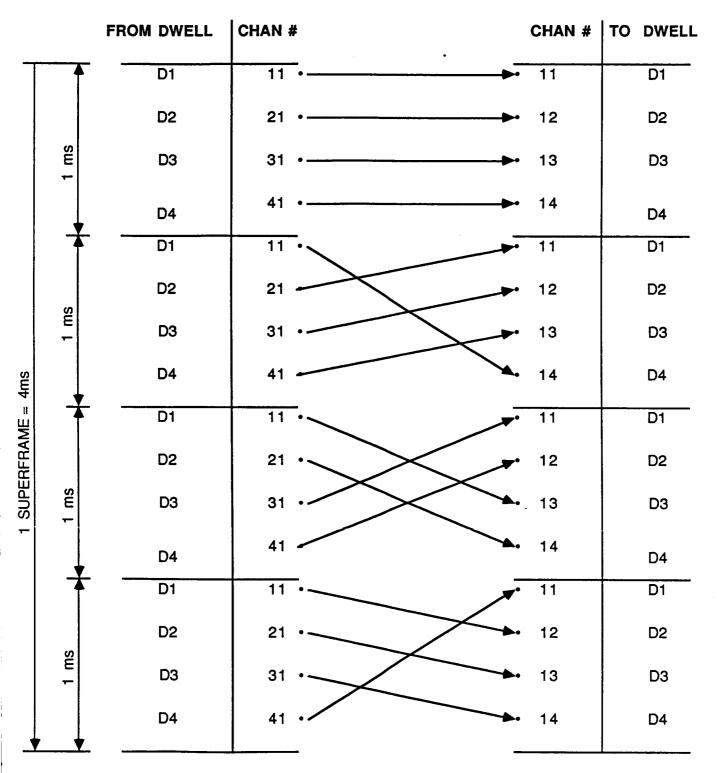

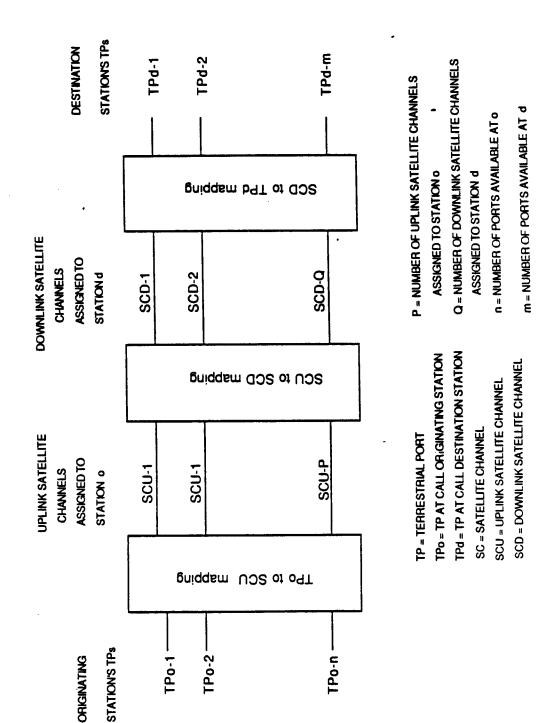

| Figure 3.3  | Onboard Satellite Channel Mapping                                                                                                            | 3.52 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 3.4  | Terrestrial Port to Time Slot Mapping<br>and Up-Link to Down-Link Satellite<br>Channel Mapping For Destination<br>Directed Message Switching | 3.53 |

| Figure 3.5  | Destination Directed Packet System  Mapping                                                                                                  | 3.54 |

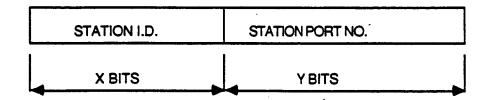

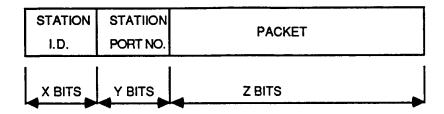

| Figure 3.6  | Packet Header Structure                                                                                                                      | 3.55 |

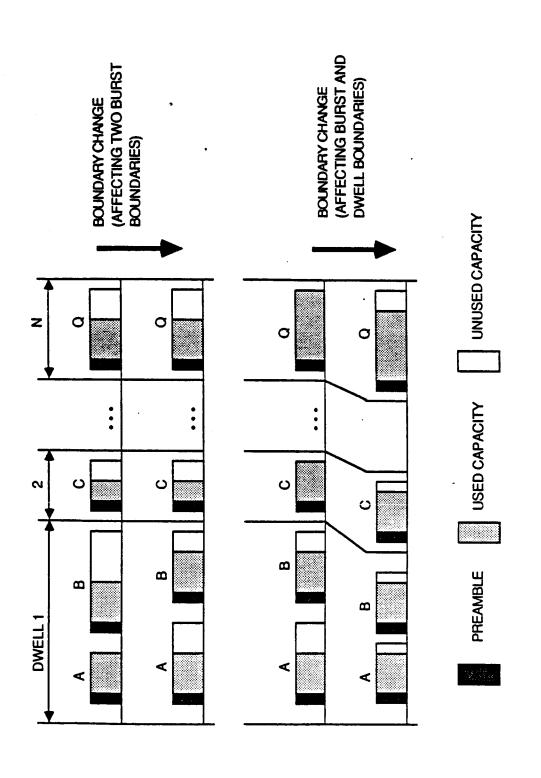

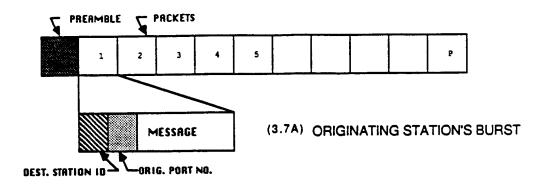

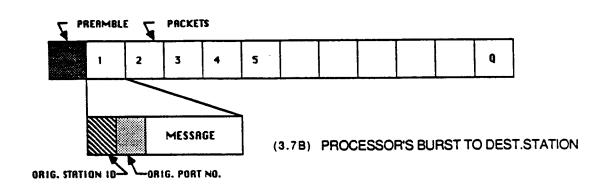

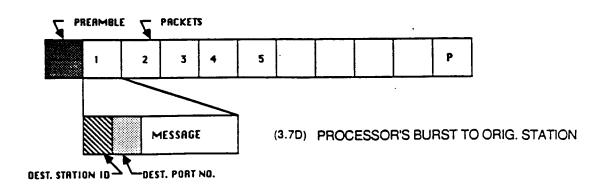

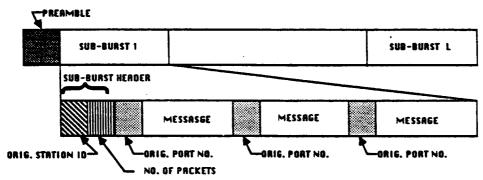

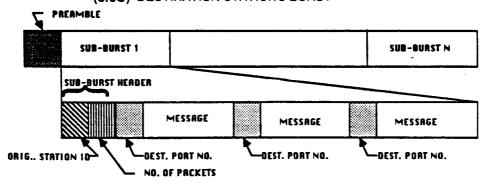

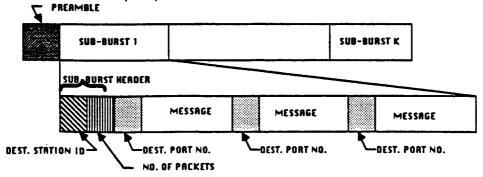

| Figure 3.7  | Traffic Bursts for Packet Routing                                                                                                            | 3.56 |

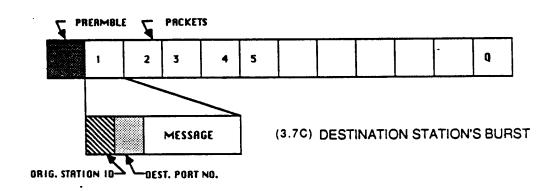

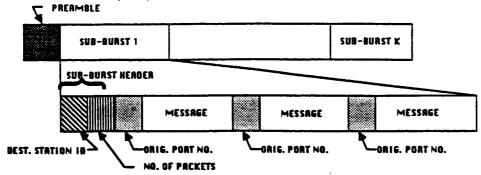

| Figure 3.8  | Traffic Bursts for Sub-burst Routing                                                                                                         | 3.57 |

| Figure 3.9  | Packet Header Efficiency for Individual Packet Routing                                                                                       | 3.58 |

| Figure 3.10 | Packet Header Efficiency for Sub-Burst Packet Routing                                                                                        | 3.59 |

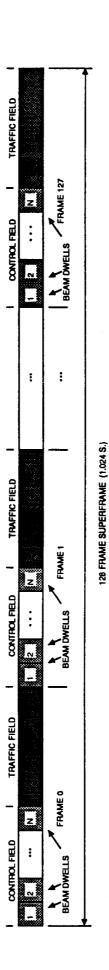

| Figure 3.11 | Frame Format                                                                                                                                 | 3.60 |

| Figure 3.12 | Superframe Structure                                                                                                                         | 3.61 |

| Figure 3.13 | Reference Burst Format                                                                                                                       | 3.62 |

| Figure 3.14 | Request Burst (RQB) Structure                                                                                                                | 3.63 |

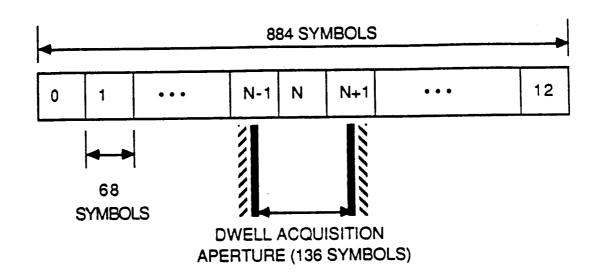

| Figure 3.15 | Relationship Between Beam Dwell and Sub-Burst                                                                                                | 3.64 |

| Figure 3.16 | Separate Input/Output Memory Architecture                                                                                                    | 3.65 |

| Figure 3.17 | Unified Pingpong Memory Architecture                                                                                                         | 3.66 |

| Figure 3.18 | Unified Dual Port Memory Architecture                                                                                                        | 3.67 |

| Figure 3.19 | Onboard Dual Port Switch Operation                                                                                                           | 3.68 |

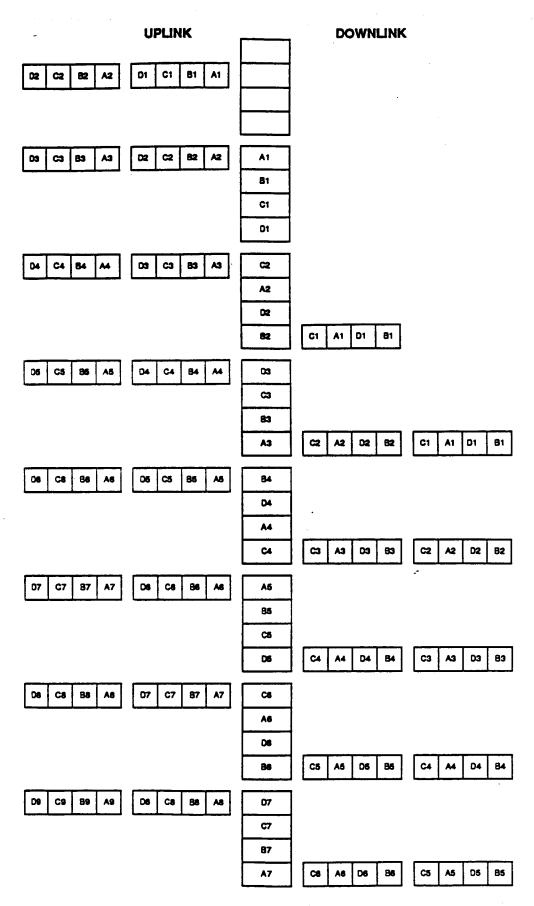

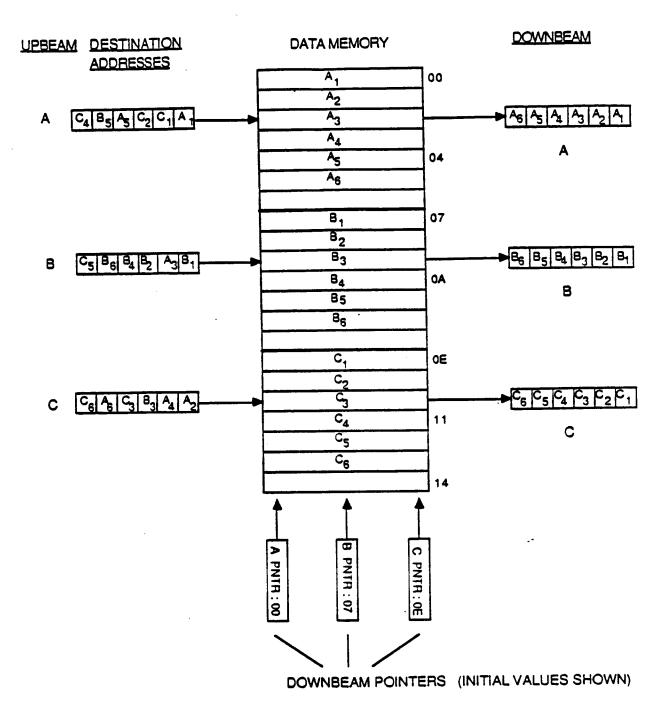

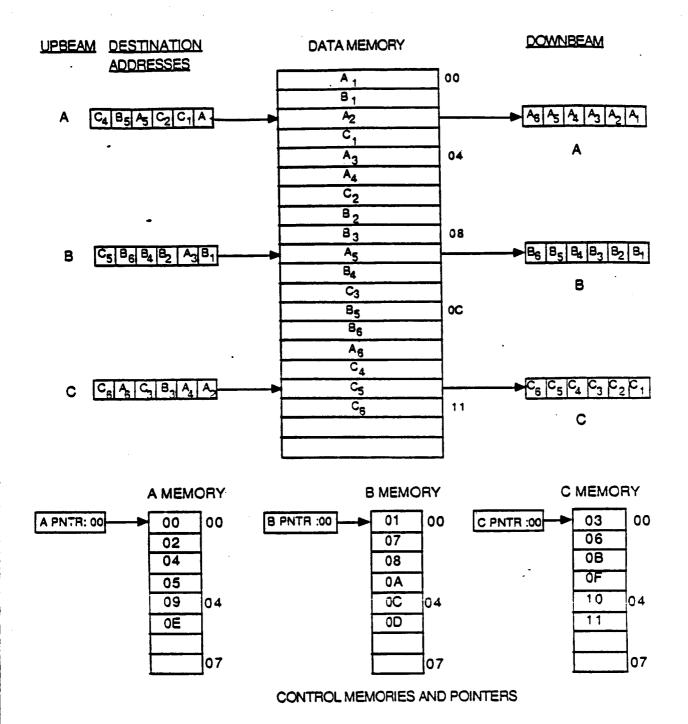

| Figure 3.20 | Signal Flow for Separate Memory Architecture Destination-Directed Switching Between Beams      | 3.69 |

|-------------|------------------------------------------------------------------------------------------------|------|

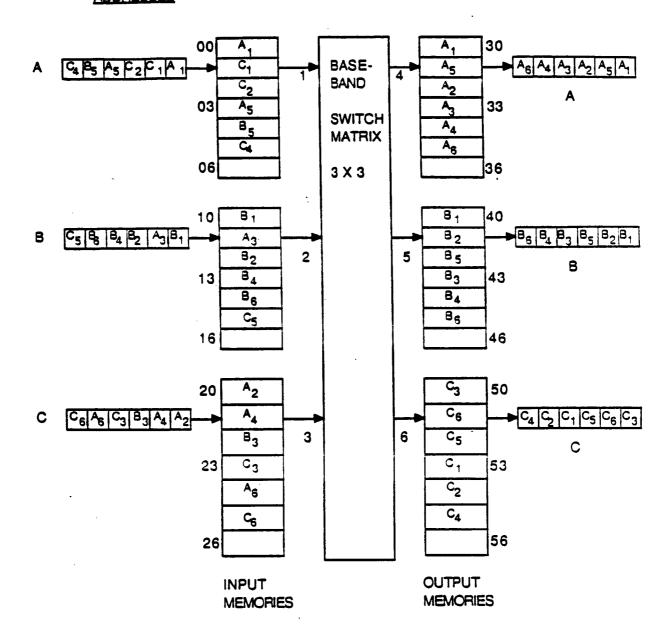

| Figure 3.21 | Control Memory Maps and Pointers for Separate<br>Memory Architecture of Figure 3.20            | 3.70 |

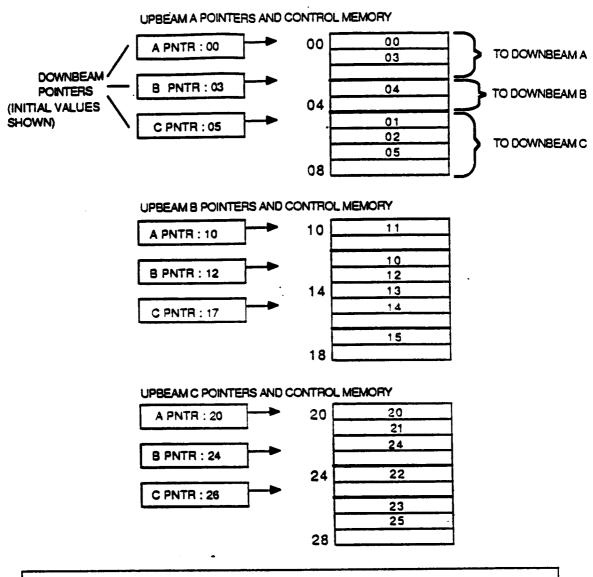

| Figure 3.22 | Separate Memory Architecture Hardware<br>Block Diagram                                         | 3.71 |

| Figure 3.23 | Detailed Hardware Block Diagram of<br>Input Section                                            | 3.72 |

| Figure 3.24 | Detailed Hardware Block Diagram of<br>Output Section                                           | 3.73 |

| Figure 3.25 | Signal Flow for Unified Memory Architecture<br>Destination-Directed Switching Between<br>Beams | 3.74 |

| Figure 3.26 | Scrambling Problem with 64-bit Bus                                                             | 3.75 |

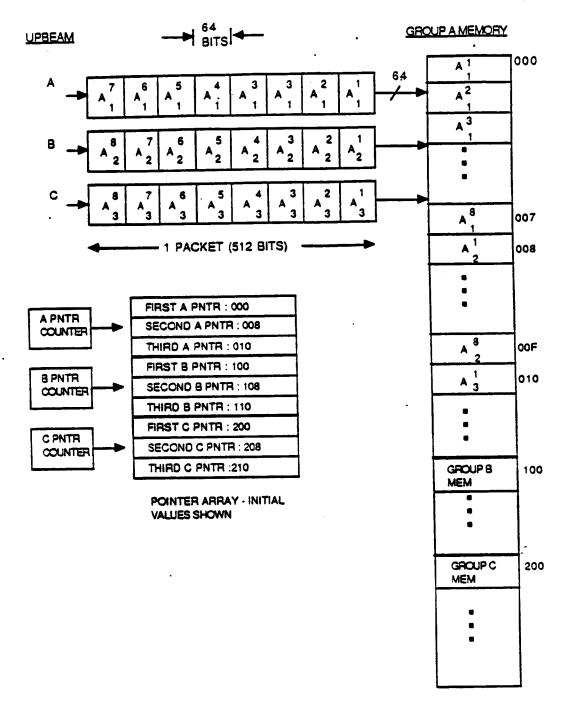

| Figure 3.27 | Diagram of Pointer Array to Solve<br>Scrambling Problem                                        | 3.76 |

| Figure 3.28 | Unified Memory Architecture Hardware<br>Block Diagram                                          | 3.77 |

| Figure 3.29 | Detailed Hardware Block Diagram of<br>Control Section Unified Memory<br>Architecture           | 3.78 |

| Figure 3.30 | Alternative Signal Flow for Unified  Memory Architecture                                       | 3.79 |

| Figure 3.31 | Alternative Unified Memory Hardware Block Diagram                                              | 3.80 |

| Figure 3.32 | Block Diagram of Serial Input Mux                                                              | 3.81 |

| Figure 3.33 | Block Diagram of Serial Output Demux                                                                               | 3.82 |

|-------------|--------------------------------------------------------------------------------------------------------------------|------|

| Figure 4.1  | Network Elements of An Integrated FSS and MSS Satellite System                                                     | 4.9  |

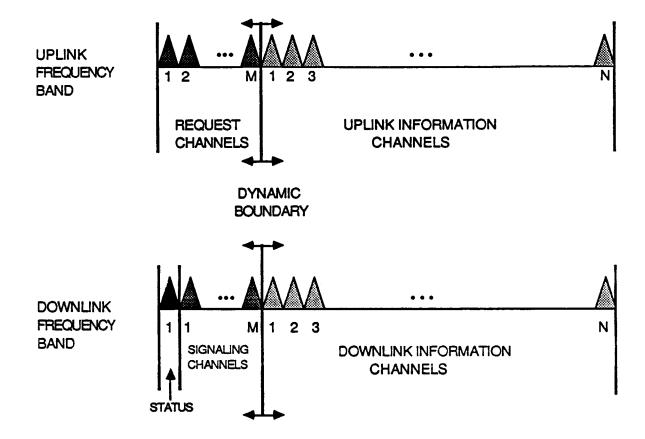

| Figure 4.2  | MSS Frequency Plans                                                                                                | 4.10 |

| Figure 4.3  | Onboard Packet Processor For<br>Integrated FS & MS Services                                                        | 4.11 |

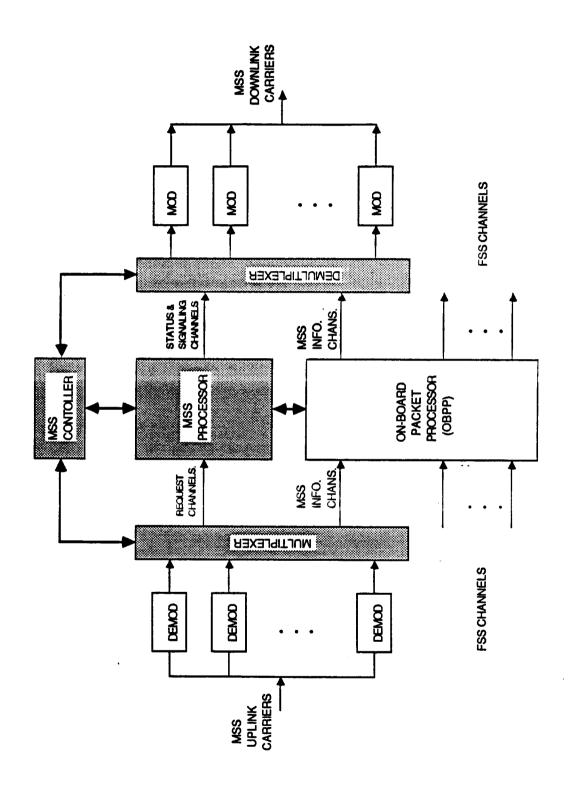

| Figure 4.4  | MSS Processor                                                                                                      | 4.12 |

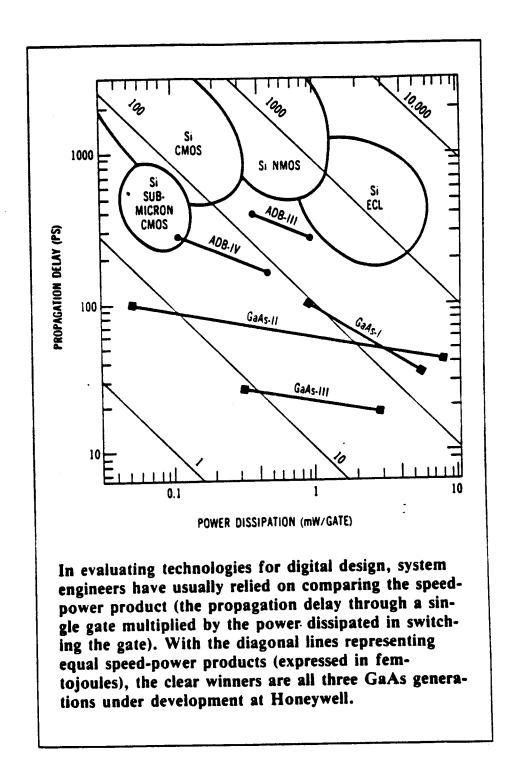

| Figure 5.1  | Speed-Power Products of Various Digital IC Technologies (Source: N. Mokhoff, Computer Design, p 77, Oct. 15, 1985) | 5.8  |

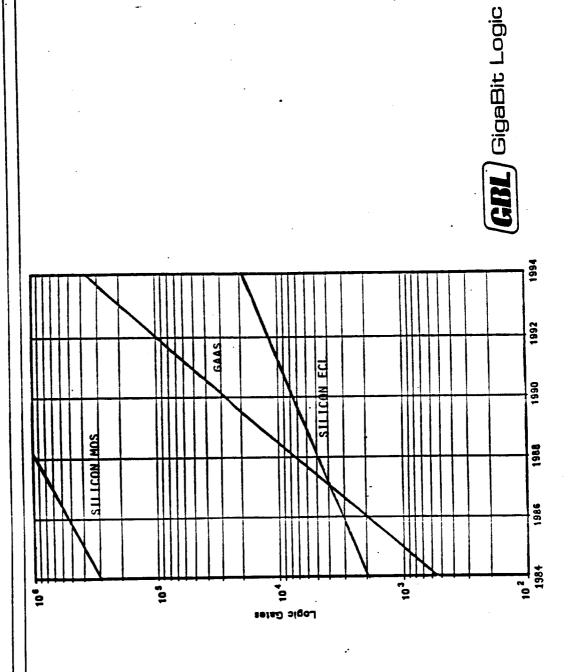

| Figure 5.2  | Forecast of Commercial GAAS Digital<br>Logic IC Gate Complexity vs. Commercial<br>Silicon IC's                     | 5.9  |

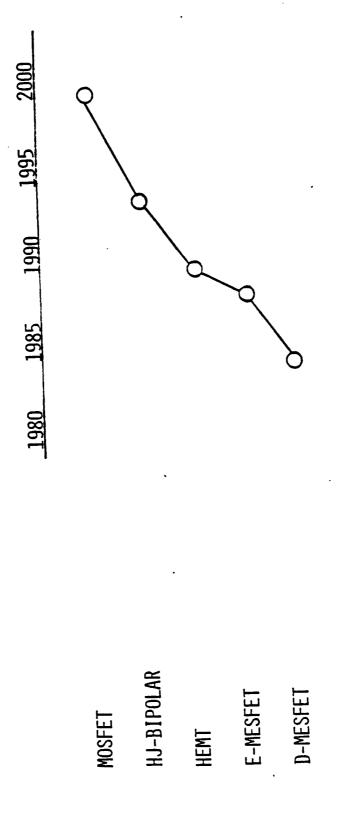

| Figure 5.3  | GaAs Device Technology                                                                                             | 5.10 |

| Figure 6.1  | Destination Directed Packet Switching Test Bed Block Diagram                                                       | 6.6  |

| Figure 6.2  | Test Red Program Plan                                                                                              | 6.7  |

#### LIST OF TABLES

| Table 1.1 | Objectives                                                                                   | 1.4            |

|-----------|----------------------------------------------------------------------------------------------|----------------|

| Table 2.1 | Satellite Services and Attributes                                                            | 2.3            |

| Table 2.2 | Comparison of Beam Hopping Parameters with and without Onboard Memory                        | 2.12           |

| Table 2.3 | Example 1 of the Comparison of Beam<br>Hopping Parameters with and without<br>Onboard Memory | 2.13           |

| Table 2.4 | Example 2 of the Comparison of Beam<br>Hopping Parameters with and without<br>Onboard Memory | 2.14           |

| Table 2.5 | Example of the Comparison of Beam Hopping Parameters With and Without Onboard Memory         | 2.15           |

| Table 2.6 | Uplink and Downlink Transmission Configurations                                              | 2.21           |

| Table 2.7 | Comparison of three Onboard Switch Implementations                                           | 2.36           |

| Table 3.1 | System Operation for Destination Addressed Message Packet System                             | 3.3(A<br>3.3(B |

| Table 3.2 | Call Set-Up Procedure                                                                        | 3.7            |

| Table 3.3 | Memory Requirements for Separate Architecture, Total for 10 120 MBPS Beams                   | 3.27           |

| Table 3.4 | Subsystem Device Count and Power Dissipation                                                 | 3.30           |

| Table 3.5 | Memory Requirements for Unified Memory<br>Architecture, Total for 10 120 MBPS Beams                                   | 3.36       |

|-----------|-----------------------------------------------------------------------------------------------------------------------|------------|

| Table 3.6 | Subsystem Device Count and Power Dissipation - Unified Memory Architecture                                            | 3.38       |

| Table 3.7 | Memory Requirements for Alternative Unified Memory Architecture, Total for 10 120 MBPS Beams                          | 3.43       |

| Table 3.8 | Subsystem Device Count and Power Dissipation - Alternative Unified Memory Architecture (Based on 1987 Technology)     | 3.47       |

| Table 5.1 | Subsystem Device Count and Power Dissipation - Alternative Unified Memory Architecture (Based on 1990-1992 Technology | 5.1<br>5.2 |

| Table 5.2 | SRAM Technology Rankings According To McDonnell Douglas Study                                                         | 5.3(A      |

| Table 5.3 | Summary of Future Custom Chip Requirements For Alternative Unified Memory Architecture                                | 5.5        |

## ONBOARD PROCESSING SATELLITE NETWORK ARCHITECTURE AND CONTROL STUDY FINAL REPORT

#### 1. INTRODUCTION

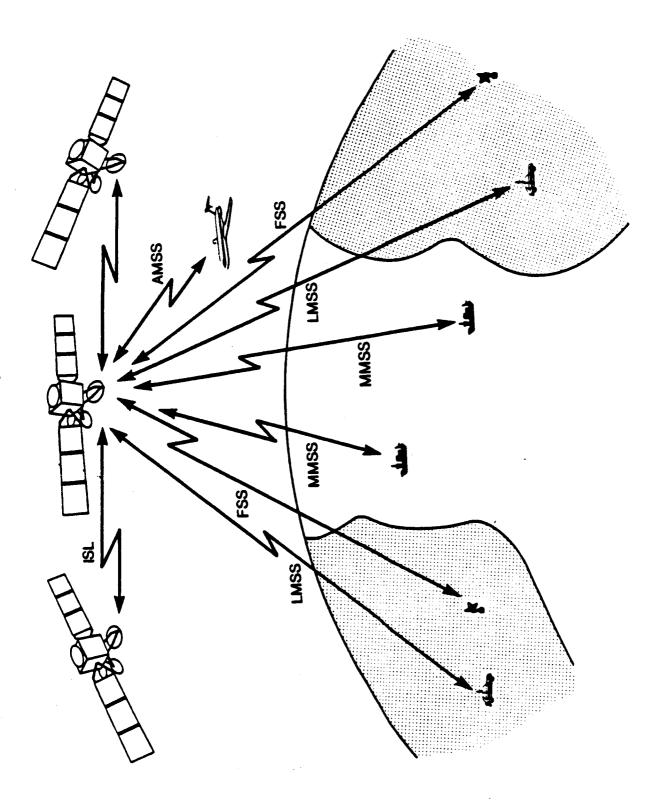

Satellites, as a consequence of the natural forces of the market place over more than two decades of application, have been applied to a variety of services incorporating a variety of transmission means. Figure 1.1 illustrates the generic services delivered by satellite systems. These include fixed satellite services (FSS), maritime mobile services (MMSS). land mobile services (LMSS), aeronautical mobile satellite services (AMSS) and intersatellite link (ISL). By far the greatest use lies in the FSS area which supports domestic and international multiple trunk, SCPC and DAMA SCPC telephone and data. Also FSS supports the broadcast distribution of television for the major TV networks and for cable TV. The mobile satellite services currently constitute a small fraction of the total and this resides principally in the MMSS; however because of the changing complexion of the satellite communication industry which will accentuate the prime advantages of satellites (which are multiple access and demand assignment of the space segment) and the expansion of AMSS and LMSS the mobile fraction is expected to grow significantly. The ISL has been used in the TDRSS and some military satellites but has not yet been used in a commercial application. This is expected to change as regional gateway switching satellites appear and interconnection of these gateways to exchange traffic between regions occurs. Any new generation of satellites should be capable of accommodating these services. It is important to bear in mind that the competition from terrestrial transmission media, in particular high capacity, low cost lightquides operating at digital transmission rates per individual fiber potentially approaching a Gigabit per second, are forcing satellite systems to adopt technologies that lead to significantly reduced cost. Such cost reduction must consider the balance of cost between the space segment and the earth segment.

#### 1.1 NETWORKS AND SERVICES

#### 1.1.1 SPOT BEAM CONSIDERATIONS

The most economical satellite system results when the space segment is enhanced to provide high e.i.r.p. and gain to noise temperature (G/T) ratios and the earth segment uses this space segment to advantage by using small, low power stations to deliver the service. This leads to a

space segment that has large aperture antennas and consequently narrow spot beams. However, the narrow spot beams reduce the coverage area of any one beam requiring either that many such spot beams be used simultaneously or that a few beams hop to various regions and dwell in each long enough to accommodate the traffic. The spot beams can be fixed if the region they cover carries sufficient traffic to fill the beam. This is suitable for regions that encompass areas of high population density. However, in regions where the density is sparse the beam must hop about to accumulate sufficient traffic to fill it. In the study reported here, this type of system receives the principal attention. The system studied also interconnects with a larger beam.

The services carried over satellites have evolved as a consequence of a selection process that uses the inherent properties to greatest advantage. In this regard, the most attractive property of the satellite is its ability to view almost half the earth's surface from a single vantage point 22300 miles above the equator. Any station in sight of the satellite can communicate to any other station in sight of the same satellite no matter where it is located. Satellites also provide large bandwidth any portion of which, when desired, can be divided into narrow channels. These capabilities have resulted in the world wide distribution of broadcast quality TV and the distribution of demand assigned services for individual telephone and data circuits by both FDMA single channel per carrier techniques and by TDMA techniques for both national (domestic) and international services.

#### 1.1.2 DEMAND ASSIGNED, MULTIPLE ACCESS NETWORKS

Demand assigned multiple access use of satellites which permits space segment capacity to be used when needed and returned for use by another when not needed by any user in view of the satellite constitutes the most powerful communications networking concept known. This property is most valuable for thin route users each of whom uses only a small fraction of an Erlang, but it remains useful for traffic intensities of several Erlangs between destinations. For example, a network of 1000 stations, each serving a traffic intensity averaging 0.2 erlangs can be accommodated with only 250 space segment circuits. The power of demand assignment diminishes on routes bearing traffic intensities greater than 20 Erlangs between destinations. Thus, high intensity routes such as those carrying telephone traffic between the major industrial countries of the North Atlantic Region do not enjoy the DAMA advantage. However on such routes, another advantage, namely that of distributed origins and destinations in which the traffic can be initiated near or at its

origin and delivered near or at its destination thus minimizing use of or bypassing all together terrestrial links, is realized. This latter satellite advantage will become very significant in the competitive race between cables and satellites in the international and national arenas provided the cost of satellite earth stations can be very significantly reduced by introduction of a proper space segment that also has reasonable cost.

#### 1.1.3 INTERSATELLITE LINKS.

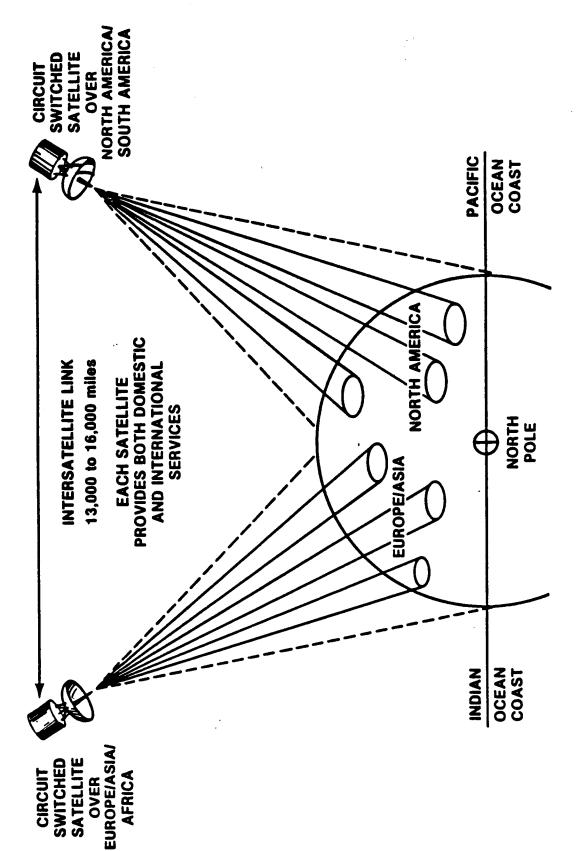

Intersatellite links provide direct connections between satellites. A question frequently asked is "what use can be made of the intersatellite in commercial satellite applications?" One answer is to bridge between two satellites one located over the North/South America continents and the other over Europe/ Middle East/Africa continents to provide a combination of domestic and international traffic. If these satellites are positioned approximately 57° apart (i.e. 13000 miles apart) in the geostationary orbit as illustrated in Figure 1.2 then individually each can serve domestic and North/South international traffic for the continents beneath it and the intersatellite link can provide East/West international connections. The added one way propagation delay time is 72 ms which will extend the round trip propagation time from the present nominal value of 550 ms to 694 ms. This is a small increase that should not greatly change conversational user subjective reaction. Also the impact on data should be unchanged compared to that experienced on the nominal single hop delay path.

#### 1.1.4 SUMMARY OF OBJECTIVES

The satellite system of the future must fulfill the objectives set forth in Table 1.1 to make the most effective use of its inherent advantages and be competitive in the new market place.

#### 1.2 SUMMARY OF CONTRACT TASKS

The work under the contract is divided into three tasks:

#### 1.2.1 TASK 1 - NETWORK ARCHITECTURE

Segment the market for telecommunications services into user classes having similar transmission requirements and hence similar network architectures.

### TABLE 1.1 OBJECTIVES

- A) DEVELOP SATELLITE NETWORKING ARCHITECTURES THAT WILL ACCOMMODATE A VARIETY OF DIFFERENT SERVICES. TYPICAL SERVICES INCLUDE: TRUNK TELEPHONE; THIN ROUTE TELEPHONE; LAND, MARITIME AND AERONAUTICAL MOBILE TELEPHONE; DATA PACKET; AND VIDEO TELECONFERENCING AND BROADCAST VIDEO.

- B) INCORPORATE A VARIETY OF MULTIPLE ACCESS METHODS SELECTED TO BE THE MOST SUITABLE FOR DELIVERY OF EACH TYPE OF SERVICE.

- C) CONSIDER THE SYSTEM AS COMPOSED OF SUBNETWORKS, EACH CHARACTERIZED BY ITS USERS. INTERCONNECTION OF THESE WILL BE ACCOMPLISHED BY A BASEBAND PROCESSOR WHICH CONTAINS A MESSAGE CHANNEL ROUTING SWITCH.

- D) INCLUDE SS/TDMA IN A SWITCHED BENT PIPE MODE THAT IS MOST USEFUL FOR HIGH VOLUME TRUNK TELEPHONE OR DIGITAL TV DISTRIBUTION.

- E) ALL SIGNALS USED IN THE SYSTEM ARE CONSIDERED TO BE DIGITAL AND ARE DEMODULATED AND REMODULATED ON BOARD THE SATELLITE.

- F) DEPENDING ON THEIR PROPERTIES SOME USERS, SUCH AS MOBILE, WILL EMPLOY CONTINUOUS TRANSMISSION TECHNIQUES, WHILE OTHERS SUCH AS TRUNK TELEPHONE OR DATA PACKET WILL EMPLOY BURST TRANSMISSIONS.

- G) THE SATELLITE WILL NECESSARILY EMPLOY A COMBINATION OF CONTINUOUS CARRIERS OPERATING IN FIXED BEAMS AND BURST CARRIERS OPERATING IN FIXED AND HOPPING BEAMS. BOTH FDMA AND TDMA TRANSMISSION TECHNIQUES WILL BE USED.

- H) ALL SERVICES WITHIN EACH SUB NETWORK WILL BE DEMAND ASSIGNED. FURTHERMORE THE INTERCONNECTION OF CALLS BETWEEN THE SUBNETWORKS IS TO ALSO BE DEMAND ASSIGNED.

- I) INTERSATELLITE LINKS WILL INTERCONNECT VARIOUS SATELLITES AND EACH SATELLITE MAY CARRY ONE OR MORE OF THE TYPES OF SERVICES.

- A) Consider use of the following transmission architectures:

- Satellite switched TDMA

- TDMA up, TDM down

- Scanning (hopping) beam TDMA

- FDMA up, TDM down

- Satellite Switched MF/TDMA

- Switching Hub earth stations with double hop transmission.

- B) Select a candidate network architecture that:

- Comprises multiple access subnetworks optimized for each user.

- Interconnects the subnetworks by means of a baseband processor.

- Optimizes the marriage of interconnection and access techniques.

#### 1.2.2 TASK 2 - NETWORK CONTROL

Provide an overall network control architecture that will serve the needs of the baseband and satellite switched RF interconnected subnetworks. This architecture shall consider the provision of the following network control functions:

- Intelligent Onboard Baseband Processor

- Distributed Network Control

- Acquisition and Synchronization

- Demand Assignment

- Fade Compensation

- Traffic and BBP Scheduling Procedures

- Network Timing and Synchronization

- Onboard Clock Control

#### 1.2.3 TASK 3. - TECHNOLOGY CHALLENGES

The results of the studies shall be used to identify elements of network architecture and control that require the greatest degree of technology development to realize an operational system. This will be specified in terms of :

- Requirements of the Enabling Technology.

- Difference From the Current Available Technology.

- Estimate of the Development Requirements Needed to Achieve An Operational System

The results obtained for each of these tasks are presented sections 2, 3, and 4 of this report.

FIGURE 1.2 EXTENDED WORLD COVERAGE WITH INTERSATELLITE LINK

#### 2 NETWORK ARCHITECTURES

#### 2.1 SERVICES CARRIED

#### 2.1.1 IDENTIFICATION OF SERVICES

Various classes of telecommunications services can be expected to be supported by an advanced satellite communications system. These may be integrated into a common network on a single satellite or they may be carried as separate networks over different satellites individually designed to optimize each type of service.

Table 2.1 lists various telecommunications services that are expected to be carried on the satellites of the late 20th and early 21st century. Transmission attributes are identified for each service type in this table. The attributes and their definitions are listed below:

Speed Of Access - Refers to the speed with which the service must be established following the instant of a request.

FAST refers to response in tens of seconds and

SLOW in minutes to hours.

Traffic Load - Refers to traffic intensity on the channels provided. LOW refers to fractions of Erlangs,

MEDIUM to 1 to 20 Erlangs and HIGH to >20 Erlangs.

Channel Rate - Refers to the bit rate on the channel carrying the

service. LOW refers to rates less than 16 kbit/s, MEDIUM to rates between 16 Kbit/s and 20 Mbit/s, HIGH to rates between 20 and 140 Mbit/s and VERY

HIGH to rates > 140 Mbit/s.

Connectivity - PP is point-to-point, MP is multipoint-to-point,

PM is point-to-multipoint and MM is multipoint-to-multipoint or full mesh.

Assignment - Refers to either PA for preassigned or DA for

demand assigned.

BER - Refers to the bit error rate on the transmission

that can be tolerated to carry the service. LOW is

$<10^{-8}$ , MEDIUM is  $<10^{-6}$  and HIGH is  $<10^{-3}$

Error Control

Method

Refers to use of either Forward Error Correction (FEC) or Automatic Repeat Request (ARQ)

#### 2.1.2 CATEGORIES OF SERVICES

The various services can be organized into the following four categories that are based on discipline rather than attributes:

#### 1. MOBILE COMMUNICATIONS

Land Maritime Aeronautical Personal

#### 2. COMPUTER AND DATA COMMUNICATIONS

Packet Data Bulk File Transfer Data Collection Data Broadcast

#### 3. TELECOMMUNICATIONS

Trunk Telephone

ISDN

Business (Customer Premises Station)

Teleconference

Electronic Mail

#### 4. BROADCAST VIDEO

Network Video Distribution

Cable Video Distribution

Educational Video Distribution

The mobile group is characterized by fast access speed, low to medium traffic load per terminal, predominantly low channel transmission rate, mostly multipoint to point and point to multipoint connectivities, medium to high BER and strong dependence on FEC to overcome the vagaries of the transmission links.

TABLE 2.1 SATELLITE SERVICES AND ATTRIBUTES

| ERROR<br>CONTROL<br>METHOD | FEC         | FEC      | FEC/ARQ     | FEC/ARQ              | FEC       | FEC/ARQ     | FEC/ARQ          | FEC         | FEC         | FEC/ARQ     | FEC         | FEC          | FEC/ARQ      | FEC/ARQ  |

|----------------------------|-------------|----------|-------------|----------------------|-----------|-------------|------------------|-------------|-------------|-------------|-------------|--------------|--------------|----------|

| BER                        | HIGH        | MED      | MED         | MOT                  | MED       | MED         | LOW              | LOW         | LOW         | MED         | HIGH        | MED          | MED          | MOT      |

| ASSIGN                     | DA          | DA       | DA          | DA/PA                | DA/PA     | DA          | PA               | DA/PA       | PA          | DA/PA       | DA          | PA           | DA/PA        | DA/PA    |

| CONNECT                    | MP/PM       | MP/PM    | MP/PM       | PM/MP/MM             | PM        | PP/MP       | PP               | MM          | PM          | PP/PM       | MP/PP       | PM           | MP           | MM       |

| CHANNEL<br>RATE            | MOT         | MEDIUM   | TOW         | MED/HIGH             | MED/HIGH  | TOW         | HIGH             | MEDIUM      | VERY HIGH   | LOW/MED     | LOW.        | LOW/HIGH     | LOW/MED      | MED/HIGH |

| TRAFFIC<br>LOAD            | MEDIUM      | MEDIUM   | TOW         | HIGH                 | MEDIUM    | HIGH        | MEDIUM           | HIGH        | HIGH        | HIGH        | HIGH        | MEDIUM       | LOW          | HIGH     |

| SPEED<br>OF<br>ACCESS      | FAST        | FAST     | FAST        | FAST                 | SLOW      | FAST        | SLOW             | FAST        | SLOW        | SLOW        | FAST        | FAST         | SLOW         | FAST     |

| SERVICE                    | LAND MOBILE | MARITIME | AERONAUTIC. | <b>BUSINESS(CPS)</b> | TELECONF. | PACKET DATA | <b>BULK DATA</b> | TRUNK TELE. | VIDEO DIST. | ELECT. MAIL | PERS. COMM. | DATA BRDCAST | DATA COLLECT | ISDN     |

NOTE; ALL TRANSMISSIONS CONSIDERED TO BE DIGITAL.

The computer and data group has mixed characteristics. Access speed should be fast for packet and broadcast data but slow for bulk transmission and data collection. Channel transmission rate is high for bulk transmission, medium for broadcast and packet and low for data collection. Connectivity is point to point for bulk data, multipoint to point and point to point for packet data, point to multipoint for broadcast data and multipoint to point for data collection.

The telecommunications group also has mixed characteristics. Access speed is fast for trunk telephone, ISDN and business CPS telephone but slow for video teleconferencing and electronic mail. Traffic load is high for trunk telephone, ISDN, business CPS telephone and electronic mail (assuming concentration of traffic) and medium for teleconferencing. Channel rate is medium to high for all but the electronic mail which ranges from low to medium. Connectivity is full mesh, point to multipoint and point to point. Assignment is preassigned and demand assigned for all members in this group. BER is low for all except electronic mail which may be medium or high when ARQ is used. FEC is used for all of these services to meet the high quality standards that have come to be expected for telecommunications with the possible exception of electronic mail when protected by ARQ.

The broadcast video group comprise services that today are exclusively carried by analog means. However in the future, because of the research being performed in the laboratories on video source coding, it can be expected that digital transmission at rates as low as 20 Mbit/s for broadcast quality video equivalent to today's NTSC/PAL/SECAM quality and 80 Mbit/s for high definition 1050/1125 line broadcast video can be expected. The transmission of these signals over satellite links requires slow access, high traffic loads, high channel rates, point to multipoint preassigned connectivity, low BER and application of FEC.

#### 2.2 FUTURE COMMUNICATION SATELLITE PAYLOADS

Future satellite communications payloads will support all or some subset of the services identified above. A good place to begin is to review some of the types of payloads currently in use or anticipated and project their logical extrapolations. Todays international satellites are designed to support principally the telecommunications and video broadcast groups with the recent addition of the maritime mobile service. It can be expected that the mobile services will include aeronautical in the early 1990s.

### NAS3-24886 FINAL REPORT 2.2.1 International Services and Extrapolations

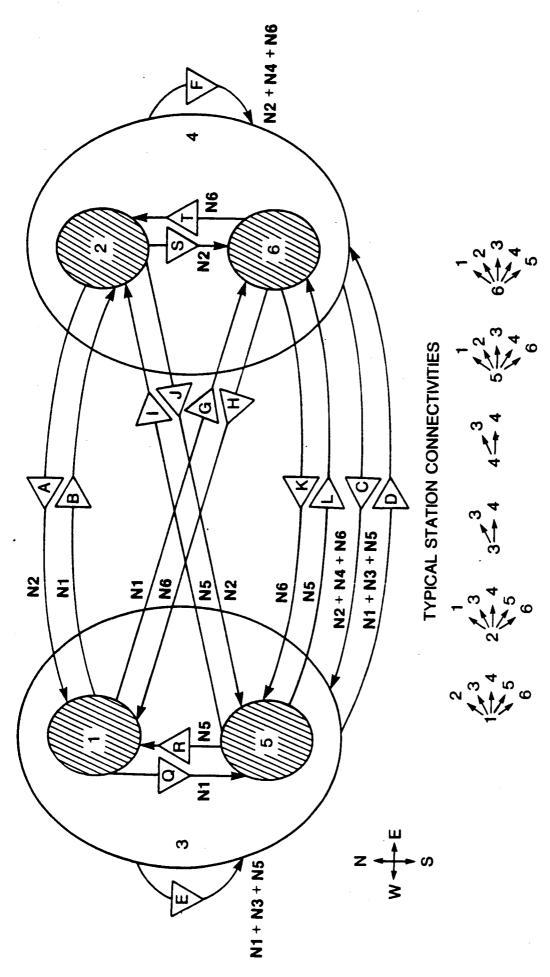

Telephone services in the INTELSAT V are supported by high capacity FM/FDMA carriers or 120 Mbit/s TDMA carried in bent pipe transponders of 72 MHz occupied bandwidth (spaced on 80 MHz centers) operating with point to multipoint connectivity. The INTELSAT V has four beams at C band, two hemibeams covering the east and west hemispheres of the earth and two zone beams covering the northeast and northwest quadrants such as those containing Europe and North America respectively. The network connectivity configuration is illustrated in Figure 2.1. The beams are interconnected by transponders of 72 MHz bandwidth that can be switched from time to time by means of a static switch to accommodate variations in the traffic load on the various routes. The INTELSAT V also has a global beam at C band equipped with transponders that are used principally for TV transmission. These international satellites also support thin route preassigned and DAMA telephony by use of single channel per carrier (SCPC) in the global and hemibeam transponders.

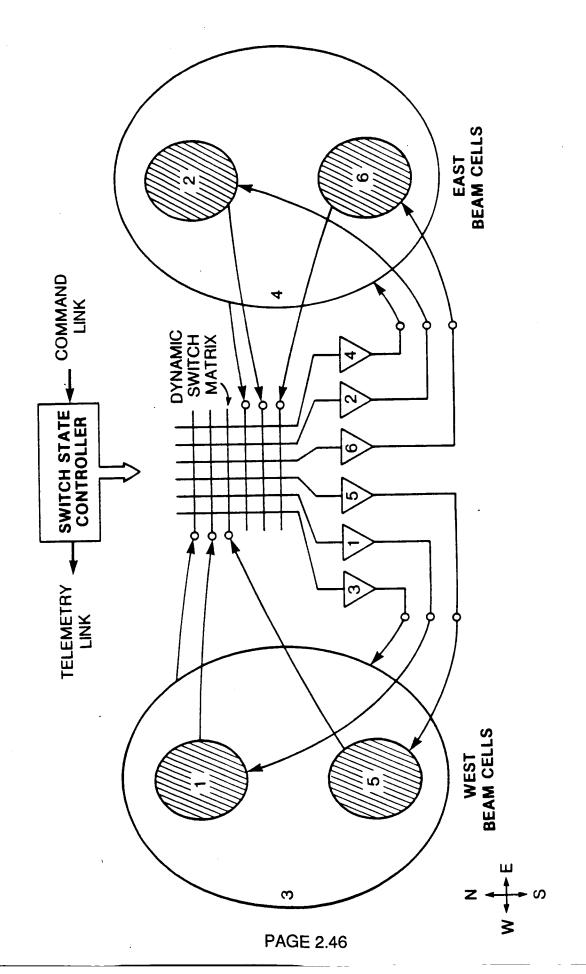

The INTELSAT VI adds two additional C band zone beams in the southeast and southwest quadrants resulting in six beams. The network connectivity configuration is shown in Figure 2.2. These are interconnected by means of 72 MHz bandwidth transponders that can be switched by a static switch. The INTELSAT VI also has two dynamic microwave switch matrices each interconnecting the six C band beams in a bank of six 72 MHz transponders resulting in an overall capacity of 2 x 6 x 120 Mbit/s = 1.44 Gbit/s. These operate with the same 120 Mbit/s TDMA terminals that are used for static operation in the INTELSAT V. The TDMA system has been designed for both the static and dynamic switched mode operation without modifications to the earth station TDMA terminal equipments.

Recent research and development work at COMSAT LABS using an advanced modulation technique that merges Octal Phase Shift Keying with FEC and maximum likelihood Viterbi decoding achieves transmission rates of 140 Mbit/s over the 72 MHz bandwidth transponders. These are intended for use in carrying the new international digital exchange rates of 140Mbit/s for supporting the ISDN. This is probably the highest rate that can be anticipated for satellite use in the foreseeable future and they will appear principally on the international transoceanic paths. The only possible exception is in the case of HDTV which if transmitted in its uncompressed form requires 240 Mbit/s. For the other types of telephone services, lower transmission rates on the uplinks are expected because they allow the use of smaller earth stations.

Both the INTELSAT V and VI are also equipped with fixed spot beams at Ku band pointed at North America and Europe respectively in the Atlantic Ocean Region to serve the international business services (IBS) and intermediate data rate (IDR) services which operate using terminals with antennas of 3.5 to 7.5 m diameter equipped with HPAs of several hundred watts. The IBS services are used by corporations to establish private, open architecture international business communications networks. The IDR services are used by telephone companies and PTTs to carry international PSTN ( Public Switched Telephone Network) services. The high EIRP (45 to 48 dBw) and G/T (0 to 3 dB/K) of the Ku band spot beams makes it possible to operate with small low power earth stations. This has created a high demand for use of the INTELSAT Ku band transponders.

#### 2.2.2 Domestic Services and Extrapolations

In the U.S. domestic arena, Ku band satellites with CONUS beams are used extensively for multipoint to point VSAT data services, full mesh DAMA SCPC telephony and point to multipoint preassigned telephony at T1 primary multiplex rates using FDMA and TDMA carriers in transponders having 36 MHz bandwidth (spaced on 40 MHz centers) at C band and 44 MHz bandwidth (spaced on 49 MHz centers) at Ku band. T1 rates (1.544 Mbit/s) are used for telephone and teleconferencing. Small antenna terminal operation at C-band is frequently impeded because of interference with terrestrial and other satellite services making Ku band operation more attractive. Typical U.S.domestic satellites include SATCOM, WESTAR, TELSTAR, GALAXY and COMSTAR at C-band, SBS at Ku-band and SPACENET and TRDS East operating at both C and Ku band.

Much of the medium and high capacity domestic public switched and private business telephone service has been removed from the domestic satellites as a result of the move on the part of a number of the domestic carriers to install long distance terrestrial lightguides. It will be difficult to regain the high capacity traffic that runs between major metropolitan districts; however, the traffic that lies outside these major routes and the bypass traffic between business locations can be retained and made to grow if carried by small, very low cost, customer premises earth stations. For example, VSAT node/hub services and small earth station full mesh SCPC DAMA telephone (such as SKY SWITCH) are expanding.

There is also extensive use of CONUS beams at C band to distribute

television for private, religious and commercial broadcast networks in the point to multipoint TVRO and point-to-point and point-to-multipoint broadcast network TV distribution applications. This is also occurring at Ku band. Such TV distribution service occupies the greatest fraction of CONUS satellite usage today.

#### 2.3 NETWORK OPTIONS

#### 2.3.1 SIMPLE GLOBAL BEAM NETWORKS.

Satellite networks had their birth in the full earth coverage beams of the early satellites used in the international services. In such a network all stations in the beam coverage, which includes everything that can see the satellite at an elevation angle of 10° or greater, can easily communicate with each other no matter their location provided the antennas are capable of receiving the signal and developing a good signal to noise ratio. Because these first satellites had very low G/T (-25dB/K) and low e.i.r.p. (11 dBw) the earth stations tended to be large and expensive. None the less, since virtually no other means for establishing long distance communications existed, they proliferated into a world wide international satellite communications network.

Although the global beam configuration is very simple, it fully exploits the multiple access, DAMA attributes that are uniquely the hallmark of satellites. Improvements in performance came by virtue of controlling the beam coverage so that virtually all of the satellite's power was directed to the surface of the earth with little lost to space and by reducing the noise temperature of the receivers. Theoretically, this leads to limiting values of G ≈ 22 dB yielding G/T ≈ -10 dB/K and e.i.r.p. ≈ 28 dBw for a satellite with a 1500 K receiver and 4 watts of power delivered to a global beam antenna in a transponder bandwidth of 36MHz. These values supported links to earth stations with antennas as small as 15m at C band and somewhat smaller if bandwidth was sacrificed; however, the dominant antenna was the gigantic 30m INTELSAT Standard A. Multichannel FDMA, SCPC digital and analog channels and TDMA networks evolved using these transponders and antennas. DAMA made its advent with the digital SCPC which was intended for links to the developing nations. TV distribution also achieved important and highly advertised usage even though it constituted only a small fraction of total usage. Efficient support of smaller terminals was not possible without further increase in both satellite G/T and e.i.r.p. These eventually came about by

the introduction narrower regional beams in later generations of INTELSATS and in domestic satellites of CANADA, the U.S. and EUROPE.

#### 2.3.2 REGIONAL BEAM NETWORKS

Regional beams are those that have a coverage confined to a specific region of the earth smaller than earth coverage. CONUS is a good example of such a regional coverage and numerous privately owned satellite networks are supported over the U.S. carrying all the categories of services identified previously. Typical examples are the COMSTARS that carry analog telephone, TI digital for telephone and teleconferencing and broadcast TV distribution at C Band. The SBS satellites carry the 48 Mbit/s burst rate TDMA which is used for CPS business services for voice data and teleconferencing and is also used for broadcast network TV distribution and TVRO distribution to cable TV heads. Typical antenna diameters used in the SBS network are 5.5m powered by 300 w high power amplifers. Even though the SBS stations are small compared to INTELSAT standards, they still proved to be too expensive for competitive business services in the U.S. The average installed cost of an SBS earth station is \$750,000.

There are numerous similar satellite systems serving the U.S. and many other regions of the world. New systems are under development, particularly in EUROPE and JAPAN, to introduce direct broadcast TV and high fidelity stereo programs to the home and to serve CPS users. The big advantage enjoyed by the regional satellite systems is the higher satellite antenna gain inherent in the smaller earth coverage. For example, the CONUS beam has an antenna gain of approximately 31 dB which is 9 dB greater than that of the global beam resulting in corresponding reductions in the e.i.r.p. and G/T needed by the earth station. When used to provide either low bit rate SCPC or TDMA services in small-node/large-hub network configurations with bandwidth limited transponder operation, small, low cost earth stations equipped with 1.8m antennas and 2w HPAs can provide random access data services. Accomplishing full mesh connectivity for similar links requires 3.5 m antennas equipped with 25w HPAs.

INTELSAT has introduced regional beams in the INTELSAT V and VI as illustrated previously in Figures 2.1 and 2.2 The hemi beams are essentially half earth coverage resulting in a nominal 3dB increase in beam gain (total ≈25 dB) and the zone beams are quarter earth coverage resulting in a nominal 6dB increase in beam gain (total ≈28 dB). Also

INTELSATS V and VI have Ku band narrow beams that achieve satellite antenna gains of approximately 31 to 34 dB covering EUROPE and NORTH AMERICA. The C band beams have permitted the introduction of the new INTELSAT Std. A earth station antenna, which has a nominal 15m diameter, for wideband telephone services and the Std. F antennas that range in size from 4.5 to 10m for IBS and IDR services. The Ku band beams have permitted the introduction of Std E antennas that range in size from 3.5 to 7.5 m that are also intended for use by the IBS and IDR services.

#### 2.3.3 SPOT BEAM NETWORKS

#### 2.3.3.1 Spot Beam Advantages

The availability of the high eirp and high G/T transponders at K band has stimulated the use of satellite communications in the domestic and international arenas. These have made it possible to operate various satellite services with small, low power earth terminals. The present systems using CONUS type coverage have come to a limit resulting from practical limits on satellite uplink G/T and downlink e.i.r.p. Further improvement requires the use of narrower satellite beams. A spot beam of 200 mile diameter augments the antenna gain by 24 dB compared to a typical CONUS beam. This yields a corresponding increase in the uplink G/T and the downlink e.i.r.p. diminished to a small extent by increased losses due to more complex antenna feed and switching arrangements. Spot beam satellites are a powerful means to reduce the size and power of the earth terminals; however, they reduce the coverage area of the beam and to restore the coverage some form of beam to beam connectivity must be introduced on the satellite.

#### 2.3.3.2 Spot Beam Connectivity

Beam to beam connectivity can be implemented by means of a dynamic microwave switch matrix (MSM) switching in synchronization with TDMA traffic bursts sent at appropriate times in a TDMA frame from earth stations to be routed from their upbeam to a designated downbeam during the epoch of their passage through the satellite. This method is already used in the 120 Mbit/s TDMA system operating on the INTELSAT VI to interconnect its hemi and zone beams as shown in Figure 2.3. An immediately obvious variation is to convert the signals to their digital baseband form by means of a demodulator, perform the upbeam to downbeam routing by a baseband switch and convert the signal once again to the modulated RF signal for the downbeam frequency. Neither of these switch methods, RF matrix or baseband switch matrix, involves storage

onboard the satellite except for short alignment buffers needed in the case of the baseband switch. Rather the storage is done on the ground at the earth stations in the TDMA terminal time compression and expansion buffers used to format the TDMA burst transmission and reception. The principal advantage of conversion to baseband is to achieve signal regeneration and to support the possibility of rate conversion from low and possibly differing uplink rates on multiple FDM carriers to high downlink rates on a single high rate carrier.

#### 2.3.3.3 Hopping Spot Beams

Either of the above methods, dynamic microwave switch matrix (MSM) or baseband switching matrix (BBSM) without further embellishment, can be married to hopping up and down beams. The hopping beam notion derives from the observation that in a multiple beam system (say with beams of 200 mile diameter) there will be several hundred beam coverage areas in a region such as CONUS as shown in Figure 2.4. Even if, due to beam isolation considerations, only one fourth of these beams could be used the amount of transmission capacity they provide would far exceed the capacity that could be processed by a practical spacecraft. It therefore becomes apparent that some means to time division multiplex among the several hundred beams so that for example only ten are active at any given instant is needed. Thus the need for beam hopping is created. Some of the beams which point to regions of intense traffic may not need to hop while others that cover wide expanses of thinly distributed traffic will hop extensively.

#### 2.3.4 ONBOARD SWITCHING AND STORAGE

#### 2.3.4.1 Operating Without Onboard Storage

A multiple hopping beam system can operate in either the MSM or BBSM mode without onboard storage of the traffic. All that needs to be done is to store the bits of each earth station's traffic in a memory and exhaust the contents of the memory as a TDMA burst at the appropriate time to pass through the satellite once each TDMA frame during the connection epoch onboard between the desired upbeam and downbeam. This is nothing more than standard TDMA operation using the method of TDMA synchronization between the earth and space segments as practiced in the INTELSAT SS/TDMA for multiple fixed beam operation or the ACTS system for multiple hopping beam operation. The problem of synchronizing the earth station transmissions to the switching and beam hopping in the

#### 2.3.4.2 Operating With Onboard Storage

Since, as explained above, it is possible to accomplish beam hopping operation without onboard storage, then what advantage is offered by adding onboard storage? The principal advantage of onboard storage lies in the fact that a station's traffic can be grouped into a single burst that is transmitted once each TDMA frame. Similarly, a station can receive its traffic in a contiguous group that is time division multiplexed as a burst in the downlink. If a station's traffic is all destined to one downbeam, then there is no real advantage to storing the station's traffic onboard. However if the traffic goes to destinations in different down beams then there is a very significant advantage because without onboard storage the station would have to transmit as many different bursts as there are destination beam dwells. In a hopping beam system with many destination dwell regions to be visited this can constitute a huge burden in terms of the number of uplink and/or downlink beam dwells needed during each TDMA frame. This not only creates a severe and perhaps impossible problem to implement a beam dwell schedule that adapts from frame to frame to accommodate rapidly changing traffic patterns, but it also decreases the system traffic efficiency. This is because the traffic is broken up into many short duration bursts each of which carries a preamble and guardtime overhead. To this must be added the guard times of a large number of beam switchings needed to hop from dwell to dwell.

#### 2.3.4.3 Comparing Operation Without And With Onboard Storage

An estimate of the impact of operating without onboard storage is developed in the following. Assume that a system is operating with one up and one downbeam in an environment with N stations in a system having M beam dwell regions, K beams (each having an up and downbeam) and serving C channels. Thus the average number of channels carried per station is C/N, the number of stations per cell averages N/M and the number of cells served by each beam is M/K. In a full mesh connected network, each of the the stations is to communicate to all of the others. Thus there are at most N(N-1) bursts in the system. However, if the number of bursts exceeds the number of channels then full mesh connectivity is not possible in which case there are a maximum of C bursts in the system. Correspondingly, the average number of bursts per station is N-1 or C/N. Each of the K beams must on the average hop among

M/K dwells which for full mesh connectivity yields a maximum number of (M/K)<sup>2</sup> hops per beam except when the number of channels becomes limiting it is C/K hops per beam.

For a system equipped with onboard switching, the parameters involving the bursts in the system, bursts per station and hops per beam are all reduced. Since the onboard switch can disassemble and reassemble the traffic from and to any station, only one burst is needed per station yielding N bursts in the system. For similar reasons the beam needs to visit each dwell region once per frame and hence there are M/K hops per beam.

For convenience, the values of the key parameters described above are tabulated in TABLE 2.2.

# TABLE 2.2 COMPARISON OF BEAM HOPPING PARAMETERS WITH AND WITHOUT ONBOARD MEMORY

| PARAMETER            |           | ONBOARD<br>ORAGE          | WITH ONBOARD<br>STORAGE |  |  |

|----------------------|-----------|---------------------------|-------------------------|--|--|

| AVE. CHANNELS/STATIC | N         | C/N                       | · C/N                   |  |  |

| NUMBER OF STATIONS/0 | CELL      | N/M                       | N/M                     |  |  |

| NUMBER OF CELLS/BEAM | Л         | M/K                       | M/K                     |  |  |

| MAX HOPS/BEAM        | LESSOR OF | (M/K) <sup>2</sup> OR C/K | M/K                     |  |  |

| MAX BURSTS/SYSTEM    | LESSOR OF | N(N-1) OR C               | N                       |  |  |

| BURSTS/STATION       | LESSOR OF | N-1 OR C/N                | 1                       |  |  |

#### 2.3.4.4 Examples Of Operating Without And With Onboard Storage

To illustrate the difference between operation with and without onboard memory, three network examples are now considered.

The first is a network of single channel per burst users in which the total number of channels is C=10,000, the number of stations served is N=10,000, the number of beam dwells is M=200 and the number of beams is K=4. The results are given in TABLE 2.3. The results reveal that the maximum number of hops/beam is 2,500 without onboard memory and only 50 with the onboard memory.

## **TABLE 2.3**

# EXAMPLE 1 OF THE COMPARISON OF BEAM HOPPING PARAMETERS WITH AND WITHOUT ONBOARD MEMORY

# SINGLE CHANNEL PER BURST OPERATION

C = NUMBER OF CHANNELS =10,000 N = NUMBER OF STATIONS =10,000

M = NUMBER OF DWELLS = 200

K = NUMBER OF BEAMS =4

| PARAMETER               | NO ONBOARD<br>STORAGE | WITH ONBOARD<br>STORAGE |

|-------------------------|-----------------------|-------------------------|

| AVE. CHANNELS/STATION   | 1                     | . 1                     |

| NUMBER OF STATIONS/CELL | 50                    | 50                      |

| NUMBER OF CELLS/BEAM    | 50                    | 50                      |

| MAX HOPS/BEAM           | 2,500                 | 50                      |

| MAX BURSTS IN SYSTEM    | 10,000                | 10,000                  |

| MAX BURSTS/STATION      | 1                     | 1                       |

The second example represents a case having medium traffic intensity per station in which the number of channels is C=100,000 the number of stations is N=500 while the other parameters are the same as in the first example. The results given in TABLE 2.4 show maximums of 2,500 hops/beam, 100,000 bursts/system and 200 bursts/station without the onboard memory compared to 50, 500 and 1 in corresponding categories with onboard memory.

#### **TABLE 2.4**

# EXAMPLE 2 OF THE COMPARISON OF BEAM HOPPING PARAMETERS WITH AND WITHOUT ONBOARD MEMORY

### MEDIUM ROUTE INTENSITY

C = NUMBER OF CHANNELS =100,000

N = NUMBER OF STATIONS =500

M = NUMBER OF DWELLS = 200

K = NUMBER OF BEAMS =4

| PARAMETER               | NO ONBOARD<br>STORAGE | WITH ONBOARD<br>STORAGE |

|-------------------------|-----------------------|-------------------------|

| AVE. CHANNELS/STATION   | 200                   | 200                     |

| NUMBER OF STATIONS/CELL | 2.5                   | 2.5                     |

| NUMBER OF CELLS/BEAM    | 50                    | 50                      |

| MAX HOPS/BEAM           | 2,500                 | . 50                    |

| MAX BURSTS IN SYSTEM    | 100,000               | 500                     |

| MAX BURSTS/STATION      | 200                   | 1                       |

The third example represents a case having thin traffic intensity per station in which the number of channels is C=100,000 the number of stations is N=5,000 while the other parameters are the same as in the first example. The results given in TABLE 2.5 show maximums of 2,500 hops/beam, 100,000 bursts/system and 20 bursts/station without the onboard memory compared to 50, 500 and 1 in corresponding categories with onboard memory.

In all three examples the presence of onboard memory reduces the number of bursts carried in the system and the number of beam hops by orders of magnitude. It is clear that onboard storage has significant value in a beam hopping system.

#### **TABLE 2.5**

# EXAMPLE OF THE COMPARISON OF BEAM HOPPING PARAMETERS WITH AND WITHOUT ONBOARD MEMORY

#### THIN ROUTE INTENSITY

C = NUMBER OF CHANNELS =100,000

N = NUMBER OF STATIONS =5,000

M = NUMBER OF DWELLS = 200

K = NUMBER OF BEAMS =4

| PARAMETER               | NO ONBOARD<br>STORAGE | WITH ONBOARD<br>STORAGE |

|-------------------------|-----------------------|-------------------------|

| AVE. CHANNELS/STATION   | 20                    | 20                      |

| NUMBER OF STATIONS/CELL | 25                    | 25                      |

| NUMBER OF CELLS/BEAM    | 50                    | 50                      |

| MAX HOPS/BEAM           | 2,500                 | 50                      |

| MAX BURSTS IN SYSTEM    | 100,000               | 5,000                   |

| MAX BURSTS/STATION      | 20                    | 1                       |

#### 2.3.5 INTERSATELLITE LINKS

In application to commercial communications satellites, a principal use of the intersatellite link may be the interconnection of two or more gateway satellites. This concept has already been described in section 1 of this report. Another use that could evolve would be the interconnection of a cluster of satellites occupying nearly the same location (thus appearing as a single satellite to the earth stations) to interconnect services carried on the different satellites. This might occur if each of

the satellites carried a different type of service, such as for example public telephone on one and land, aero mobile on another, etc. The intersatellite link would serve to perform cross connects between services whose transmission modes and implementation architectures are so different that different satellites are the most economical means for implementing them. Implementation of an intersatellite link is discussed further in section 4.

#### 2.4 TRANSMISSION CONFIGURATIONS

In general, two basic transmission methods have dominated satellite communications, Frequency Division Multiplexing abbreviated as FDM and Time Division Multiplexing, abbreviated as TDM. In satellite communications to connote the fact that the uplinks to the satellite can be accessed by any number of earth stations and transmissions transponded from the satellite can be received by any number of stations the abbreviations are modified to FDMA and TDMA which refer to Frequency Division and Time Division Multiple Access respectively. This multiple accessing capability is uniquely the domain of the satellites and must be used to full advantage to compete with the terrestrial transmission options.

#### 2.4.1 FDMA

FDMA customarily designates division of the spectrum of a satellite transponder into a multiplicity of smaller frequency bands each occupied by a carrier. The carriers may have various bandwidths which are individually scaled to accommodate different levels of traffic or they may all be of the same bandwidth as in the case of Single Channel Per Carrier (SCPC) systems used in DAMA networks such as INTELSAT's SPADE, INMARSAT's maritime mobile system, SKY SWITCH and PALAPA. It is likely that the land mobile and aeronautical mobile systems will use this technique.

#### 2.4.2 TDMA

TDMA refers to the division of a high bit rate carrier, occupying the entire bandwidth of a transponder, into time division burst transmissions that eminate from numerous earth stations and are synchronized so that each arrives at the satellite in an epoch assigned uniquely to it. The simplest TDMA system uses a bent pipe transponder in which the uplink transmissions are simply repeated and returned to the earth on the

downlink. A multiplicity of transponders can be used in such a system and the up and down beams can be pointed to different regions to provide multiple beam connections such as those previously described for INTELSAT V. Stations can access destinations in different regions by frequency hopping their transmissions to fall in the band of the transponder with its downbeam pointed to the desired destination region.

TDMA is inherently suited for systems that perform onboard dynamic switching. By rule, each station's transmission must arrive and pass through the satellite in a prescribed time epoch. It is a relatively simple matter to coordinate these epochs with the switching of the onboard connections and to have them coincide with the proper switching epoch to be directed to the destination downbeam. As explained previously, this is what happens in the INTELSAT VI when it uses its MSM to operate in the SS-TDMA mode. This also is done for satellites that will perform memoryless onboard switching at baseband such as currently planned on the ITALSAT.

TDMA is also used on the ACTS satellite which incorporates an onboard baseband switch that stores the individual channel signals arriving on the uplinks from multiple uplink hopping beams in input memories and rearranges these into TDM downlink transmissions that contiguously group all of the traffic destinated to a dwell region into an epoch that coincides with the time that the downlink hopping beam points to the destination.

#### 2.4.3 MF/TDMA

There is another way to use TDMA that is referred to as MF/TDMA. It simply refers to the transmission of several TDMA carriers in a transponder rather than one. These carriers are used simultaneously by different stations to carrier their burst transmissions. The advantage is a reduction in the amount of transmit power needed by an earth station to access the network. The disadvantage is the reduction of the space segment's capacity because of the transponder output backoff allowance needed to reduce intermodulation distortion to an acceptable level. Typically, between 30 and 50% of the space segment capacity must be given up to achieve the MF/TDMA operation in a bentpipe transponder.

MF/TDMA can also operate in an satellite switched mode (SS-MF/TDMA) in which TDMA traffic bursts operating on multiple low burst rate carriers through the MSM.

MF/TDMA can also be used in baseband switched systems, most likely on the uplinks. For example, the bandwidth normally allocated to the highest bit rate (or symbol rate) TDMA carrier may be assigned to several lower bit rate (or symbol rate) TDMA carriers. This is done in the ACTS where the upbeams can carry either one 110 Msym/s or four 27.5 Msym/s TDMA carriers. In this case, because onboard demodulation and remodulation (regeneration ) is used, there is no space segment power backoff penalty.

#### 2.4.4 CDMA

Another transmission method that has been used principally by the military is Code Division Multiplexing which when used on the satellites can be termed as Code Division Multiple Access (CDMA). CDMA uses unique codes to distinguish the transmissions of the individual stations of the network. Each stations is assigned a unique orthogonal code that is decoded at its receive side. To call any particular station, a transmitter sends the message coded in the desired receiver's code. Many such transmissions can be sent simultaneously to serve a large number of stations. The system is limited in the number of coded transmissions that can be simultaneously supported by the noise background generated by the cumulative addition of all of the transmissions at the receivers. CDMA systems are thus said to be self noise limiting. CDMA also has an attending property that causes the transmitted signal to be spread over a spectrum that can be orders of magnitude greater than that which would be occupied if the signal were transmitted by ordinary means. This property is due to the fact that each symbol of the message is coded in terms of M symbols of a coding pseudo random bit sequence which causes the spectrum of the coded signal to be multiplied in width by M. The bits of the pseudo random code are frequently referred to as chips. This spreading action dilutes the spectral density of the transmitted signal M<sup>-1</sup> by and can reduce the signal spectrum level to a level less than the thermal noise background to hide the signal from unwanted listeners. This is called the spread spectrum action. Obviously, this same spread spectrum action can reduce a high power signal's spectral density to a level that is non interfering to other services sharing the same band.

CDMA has not been used to any significant extent in satellite systems mostly because greater transmission capacities can be achieved by FDMA and TDMA using the same facilities. However, there is an application of CDMA that has received considerable attention in the last few years as implemented by the Equatorial Radio Company. In this case the Coded transmission is used principally for its attending property to

spread the transmitted signal over a wide spectrum. In this way a high power signal can be transmitted from a small antenna with low spectral density and thereby avoid violating the spectral density limits set forth by the CCIR. This makes it possible to operate small earth stations at C band in environments where clearance could not otherwise be obtained. On the receive side, CDMA also has the advantage of permitting signals coded in the station's code to be picked out of an environment of interfering narrowband signals. This is the result of the correlation receive processing that literally converges the coded receive signal into a narrowband signal of bandwidth determined by the original uncoded signal while spreading the interfering signal's power over a wideband equal to or greater than that of the spectrum spread signal.

In this study, only FDMA, TDMA and MF/TDMA transmission methods are assumed. CDMA has its peculiar advantages which can be factored in on a case by case basis as the need dictates.

#### 2.4.5 TRANSMISSION CONFIGURATIONS

Various arrangements of FDMA, TDMA and MF/TDMA transmission can be used in a satellite system. Transmission schemes are the principal distinguishing hallmarks of the various classes of networks that will use future satellites which have multiple beams some of which are fixed and others hopping. Transmission methods applicable to Uplink and Downlink respectively are listed in the columns of TABLE 2.6. Each row identifies a particular combination of transmission methods for the up and down links respectively.

# 2.4.5.1 FDMA-FDMA Operation

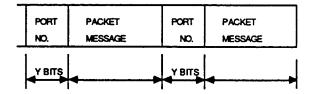

Arrangement 1 uses FDMA on both the up and down links. It is the principal method used for most satellite systems during their first two decades of existence. The method is the natural evolutionary product of the use of the global and regional beam bent pipe transponding repeater satellite. It is also used as the principal transmission method in the multibeam systems of INTELSATs V and VI. It's attractiveness resides in the freedom it offers in terms of the operating discipline that must be adhered to by the users of the system. This freedom has led to the growth of many different and novel network architectures (such as the node/hub star networks popular at this time for VSAT business communications) and for this reason it will continue to be a principal component of any satellite system in the immediate future. The recent Hughes Galaxy filing for a CONUS system uses a combination of four regional up beams