# **NASA Contractor Report 181767**

# **Advanced Information Processing System: Local System Services**

Laura Burkhardt Linda Alger Roy Whittredge Peter Stasiowski

THE CHARLES STARK DRAPER LABORATORY, INC. CAMBRIDGE, MA 02139

Contract NAS1-18061 April 1989

National Aeronautics and Space Administration

Langley Research Center Hampton. Virginia 23665-5225

(NASA-CR-181767) ADVINCED INFORMATION PROCESSING SYSTEM: LOCAL SYSTEM SERVICES (Diaper (Charles Stark) Lab.) 190 pcscl 09B

N89-21582

Unclas G3/62 0200059

## TABLE OF CONTENTS

| Secti | ion          |                       |             | 1                                                  | Page |  |

|-------|--------------|-----------------------|-------------|----------------------------------------------------|------|--|

|       | LIS          | r of IL               | LUSTRAT     | IONS                                               | vi   |  |

| 1.0   | INTRODUCTION |                       |             |                                                    |      |  |

|       | 1.1          | 1.1 AIPS Architecture |             |                                                    |      |  |

|       |              | 1.1.1                 | AIPS Fat    | ult Tolerant Processors: Overview                  | 4    |  |

|       |              | 1.1.2                 | Fault Tol   | erant Processor: Functional View                   | 6    |  |

|       | 1.2          | AIPS S                | System Soft | tware                                              | 10   |  |

|       |              | 1.2.1                 | AIPS Sof    | tware Design Approach                              | 10   |  |

|       |              | 1.2.2                 | AIPS Sys    | tem Software Overview                              | 13   |  |

|       |              |                       | 1.2.2.1     | Local System Services                              | 13   |  |

|       |              |                       | 1.2.2.2     | Inter-Computer System Services                     | 15   |  |

|       |              |                       | 1.2.2.3     | System Manager                                     | 16   |  |

|       |              |                       | 1.2.2.4     | I/O System Services                                | 17   |  |

| 2.0   | GPC          | CINITIA               | LIZATIO     | Y                                                  | 21   |  |

|       | 2.1          |                       |             | Functional Requirements and Design                 |      |  |

|       | 2.2          |                       |             | ion Software Specifications                        |      |  |

| 3.0   | REA          | AL TIMI               | E OPERAT    | TNG SYSTEM                                         | 25   |  |

|       |              |                       |             | ating System Functional Requirements               |      |  |

|       |              | 3.1.1                 |             | xecution Management                                |      |  |

|       |              | 3.1.2                 |             | Management                                         |      |  |

|       |              | 3.1.3                 |             | Communication                                      |      |  |

|       |              | 3.1.4                 |             | Exceptions                                         |      |  |

|       | 3.2          | Real T                |             | ting System Software Specifications                |      |  |

|       |              | 3.2.1                 |             | ecution Management Process Descriptions            |      |  |

|       |              | 3.2.2                 |             | Management Process Descriptions                    |      |  |

|       |              | 3.2.3                 |             | Communication Process Descriptions                 |      |  |

|       |              | 3.2.4                 | Software    | Exception Process Description                      | 43   |  |

| 4.0   | GPO          | C FAUL'               | Г ДЕТЕСТ    | TION, IDENTIFICATION AND RECONFIGURATION           | ٧45  |  |

|       | 4.1          | GPC F                 | ault Detect | ion, Identification and Reconfiguration Functional |      |  |

|       |              | Requir                | ements and  | d Design                                           | 45   |  |

|       |              | 4.1.1                 |             | etection and Identification                        |      |  |

|       |              |                       | 4.1.1.1     | Fast FDIR                                          | 48   |  |

|       |              |                       | 4.1.1.2     |                                                    |      |  |

|       |              |                       | 4.1.1.3     | 8                                                  |      |  |

|       |              |                       | 4.1.1.4     | _                                                  |      |  |

|       |              | 4.1.2                 | Channel 1   | Recovery                                           |      |  |

|     |     |                                                            | 4.1.2.1                                            | Transient          | FDIR                               | 52  |  |

|-----|-----|------------------------------------------------------------|----------------------------------------------------|--------------------|------------------------------------|-----|--|

|     |     |                                                            | 4.1.2.2                                            | <b>Lost Soul S</b> | ync                                | 55  |  |

|     |     |                                                            | 4.1.2.3                                            | System Rest        | art                                | 57  |  |

|     |     | 4.1.3                                                      | Reconfi                                            | guration           | •••••                              | 57  |  |

|     |     | 4.1.4                                                      | Loggin                                             | g                  | •••••                              | 57  |  |

|     | 4.2 | GPC F                                                      | ault Detect                                        | tion, Identific    | ation and Reconfiguration Software |     |  |

|     |     | Specific                                                   | cations                                            |                    |                                    | 58  |  |

|     |     | 4.2.1                                                      |                                                    |                    | entification Process Descriptions  |     |  |

|     |     |                                                            | 4.2.1.1                                            | Fast FD            | [                                  | 59  |  |

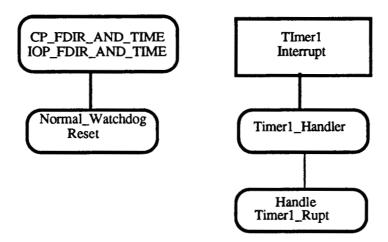

|     |     |                                                            | 4.2.1.2                                            | Watchdog T         | Timer Reset                        | 78  |  |

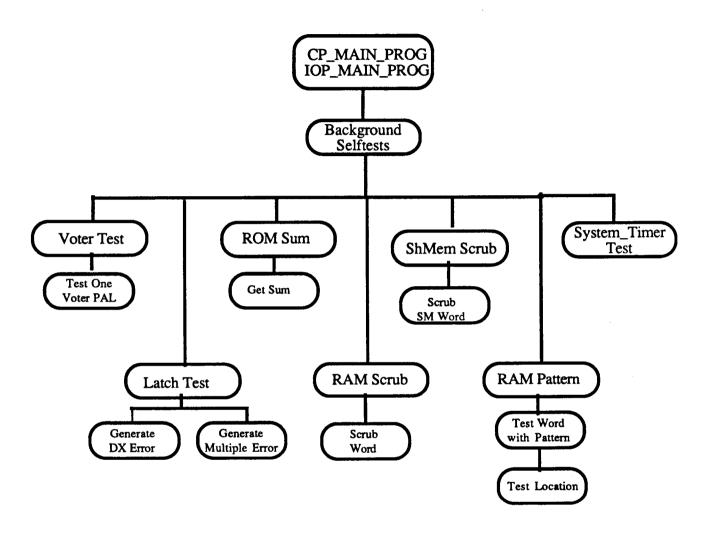

|     |     |                                                            | 4.2.1.3                                            | Background         | d Selftests                        | 81  |  |

|     |     |                                                            | 4.2.1.4                                            | -                  | ption Handler                      |     |  |

|     |     | 4.2.2                                                      | Channel                                            | Recovery Pro       | ocess Descriptions                 | 99  |  |

|     |     |                                                            | 4.2.2.1                                            |                    | FDIR                               |     |  |

|     |     |                                                            | 4.2.2.2                                            | Lost Soul S        | ync                                | 106 |  |

|     |     |                                                            | 4.2.2.3                                            |                    | tart Processes                     |     |  |

|     |     | 4.2.3                                                      | Reconfig                                           | uration Proce      | ess Descriptions                   | 124 |  |

|     |     | 4.2.4                                                      | _                                                  |                    | riptions                           |     |  |

|     |     |                                                            | 4.2.4.1                                            | User Erre          | or Logs                            | 128 |  |

|     |     |                                                            | 4.2.4.2                                            |                    | Logs                               |     |  |

|     |     |                                                            |                                                    |                    |                                    |     |  |

| 5.0 | GPO | C STA                                                      | TUS RE                                             | PORTER             | •••••                              | 133 |  |

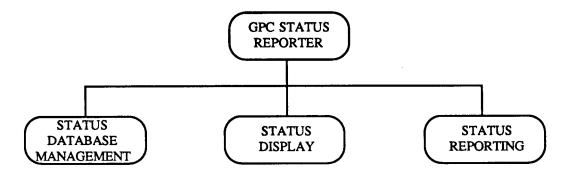

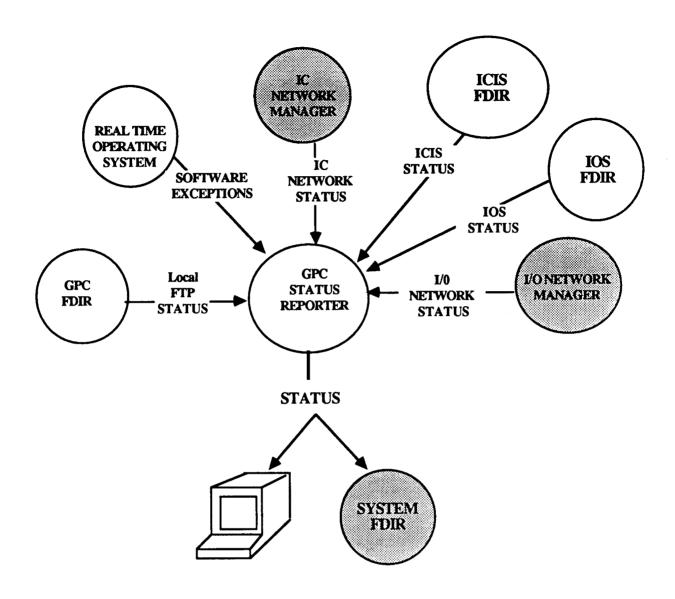

|     | 5.1 | 5.1 GPC Status Reporter Functional Requirements and Design |                                                    |                    |                                    |     |  |

|     |     | 5.1.1                                                      | Status Da                                          | tabase Manag       | gement                             | 134 |  |

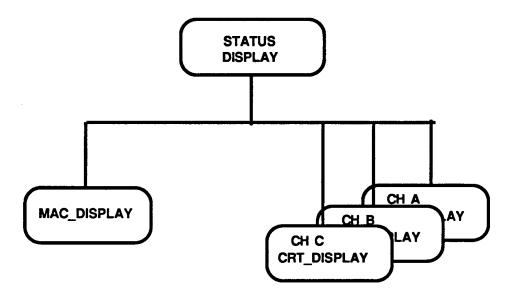

|     |     | 5.1.2                                                      | Status                                             | Display            |                                    | 135 |  |

|     |     | 5.1.3                                                      | Status Re                                          | porting            |                                    | 137 |  |

|     | 5.2 | GPC S                                                      | tatus Repo                                         | rter Software      | Specifications                     | 137 |  |

|     |     | 5.2.1                                                      | Status Da                                          | atabase Mana       | gement Process Descriptions        | 137 |  |

|     |     | 5.2.2                                                      | Site State                                         | ıs Display Pr      | ocess Descriptions                 | 139 |  |

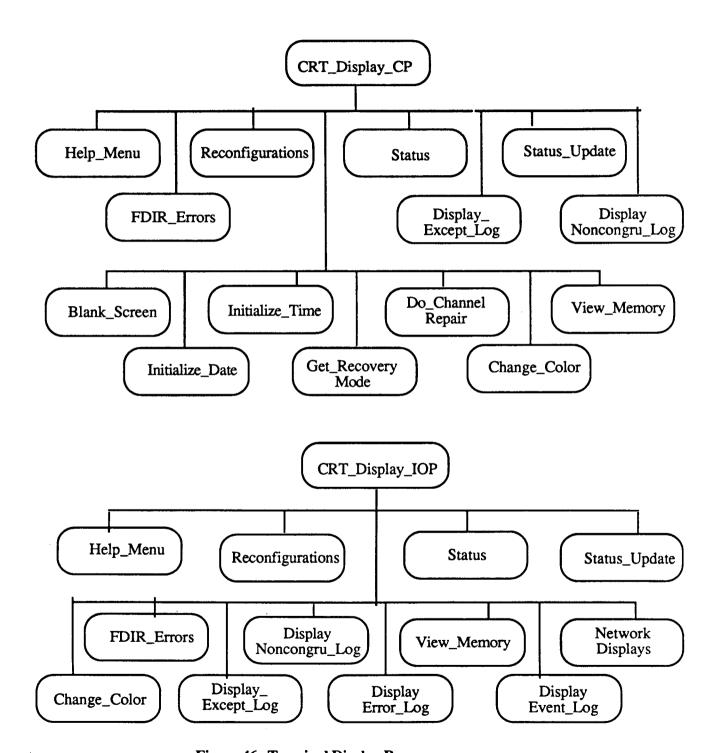

|     |     |                                                            | 5.2.2.1                                            | Terminal           | Displays                           | 139 |  |

|     |     |                                                            | 5.2.2.2                                            | Macintosh l        | Displays                           | 151 |  |

|     |     |                                                            |                                                    |                    |                                    |     |  |

| 6.0 |     |                                                            |                                                    |                    |                                    |     |  |

|     | 6.1 | Local T                                                    | al Time Manager Functional Requirements and Design |                    |                                    |     |  |

|     |     | 6.1.1                                                      |                                                    |                    |                                    |     |  |

|     |     |                                                            | 6.1.1.1                                            | Time Datab         | ase                                | 161 |  |

|     |     |                                                            | 6.1.1.2                                            | Time Datab         | ase Manager                        | 162 |  |

|     |     |                                                            |                                                    | 6.1.1.2.1          | Initialize Time                    | 163 |  |

|     |     |                                                            |                                                    | 6.1.1.2.2          | Immediate Local Time               | 163 |  |

|     | •,  |                                                            |                                                    | 6.1.1.2.3          | Update Local Time                  | 163 |  |

|     |     |                                                            |                                                    | 6.1.1.2.4          | Time Utilities                     | 164 |  |

|     |     |                                                            | 6.1.1.3                                            | Calendar Ex        | ktensions                          | 164 |  |

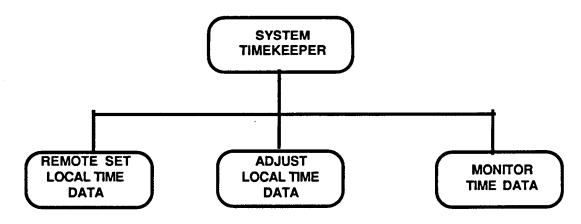

|     |     | 6.12                                                       | System T                                           |                    |                                    | 165 |  |

|            |                                             |       | 6.1.2.1                              | Remote Set Local Time Data                             | 166 |  |  |

|------------|---------------------------------------------|-------|--------------------------------------|--------------------------------------------------------|-----|--|--|

|            |                                             |       | 6.1.2.2                              | Adjust Local Time Data                                 | 167 |  |  |

|            |                                             |       | 6.1.2.3                              |                                                        |     |  |  |

|            | 6.2                                         | Local | Time Mai                             | nager Software Specifications                          |     |  |  |

|            | 6.2.1 Local Timekeeper Process Descriptions |       |                                      |                                                        |     |  |  |

|            |                                             |       | 6.2.1.1                              | Time Database Manager Process Descriptions             | 169 |  |  |

|            |                                             |       |                                      | <b>6.2.1.1.5</b> Time Utilities                        | 172 |  |  |

|            |                                             |       | 6.2.1.2                              | CALENDAR Extensions Process Descriptions               | 175 |  |  |

|            |                                             | 6.2.2 | System T                             | imekeeper Process Descriptions                         | 176 |  |  |

| <b>-</b> ^ | CONCLUSIONS AND RECOMMENDATIONS             |       |                                      |                                                        |     |  |  |

| 7.0        |                                             |       |                                      |                                                        |     |  |  |

|            | 7.1                                         |       | ng of Local System Services Software |                                                        |     |  |  |

|            | 7.2                                         |       |                                      |                                                        |     |  |  |

|            |                                             | 7.2.1 | Channel 1                            | Resynchronization                                      | 179 |  |  |

|            |                                             | 7.2.2 | Different                            | iation Between Transient and Intermittent Faults       | 179 |  |  |

|            |                                             | 7.2.3 | Additiona                            | al Monitor Interlock Functionality and Fault Detection | 180 |  |  |

|            |                                             | 7.2.4 | Duplex I                             | TTP Fault Isolation and Reconfiguration                | 181 |  |  |

|            |                                             | 7.2.5 |                                      | n Mode Fault Protection                                |     |  |  |

| 8.0        | RE                                          | FERE  | NCES                                 |                                                        | 183 |  |  |

| API        | END                                         | IX A: | FAULT-T(                             | DLERANT PROCESSOR DATA EXCHANGE                        | A-1 |  |  |

### LIST OF ILLUSTRATIONS

| Figu      | ire Title                                                              | Page   |

|-----------|------------------------------------------------------------------------|--------|

| 1.        | AIPS Distributed Configuration                                         | 3      |

| 2.        | Simplified Schematic of AIPS Fault Tolerant Processor                  | 4      |

| <b>3.</b> | Fault Tolerant Processor Architecture: Functional View (One Channel)   | 7      |

| 4.        | AIPS System Design Approach                                            | 11     |

| 5.        | Centralized AIPS Configuration                                         |        |

| 6.        | Top Level View of System Services                                      |        |

| 7.        | Local System Services                                                  | 14     |

| 8.        | Inter-Computer System Services                                         | 16     |

| 9.        | System Manager                                                         | 17     |

|           | I/O System Services                                                    |        |

| 11.       | GPC INIT Control Flow Diagram                                          | 24     |

| 12.       | AIPS Real Time Operating System                                        | 25     |

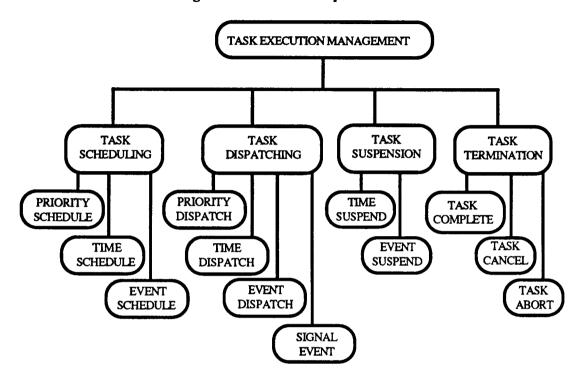

| 13.       | Task Execution Management                                              | 28     |

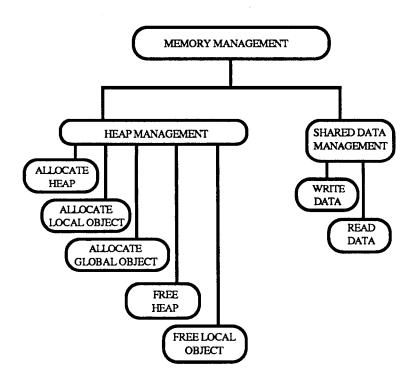

| 14.       | Memory Management                                                      | 35     |

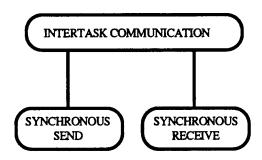

|           | Intertask Communication                                                |        |

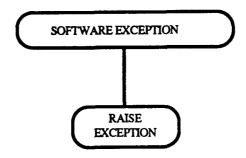

| 16.       | Software Exception                                                     | 43     |

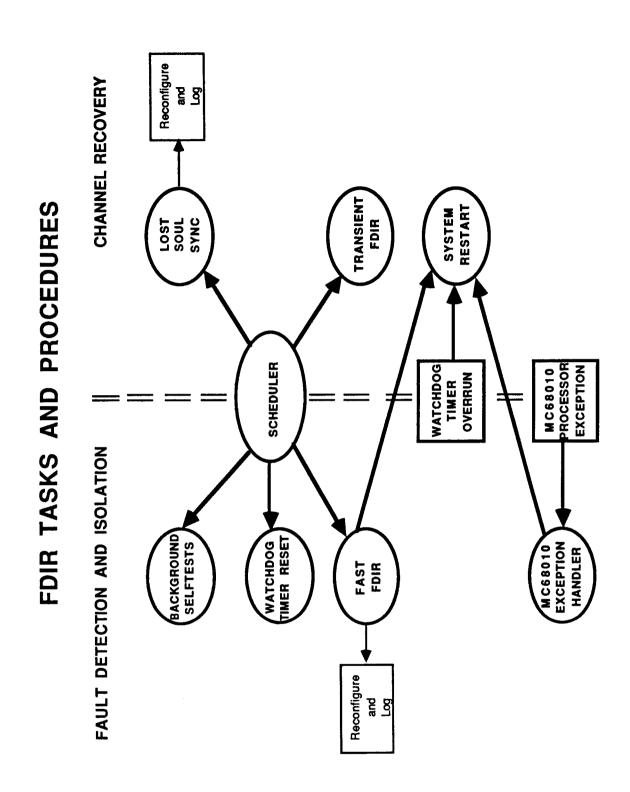

| 17.       | Summary of FDIR Tasks and Procedures                                   | 46     |

| 18.       | FDIR Tasks and Procedures                                              | 47     |

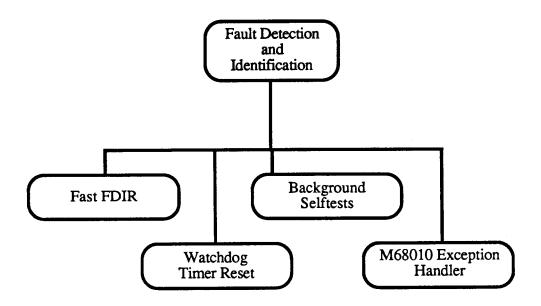

| 19.       | Fault Detection and Identification Functions                           | 58     |

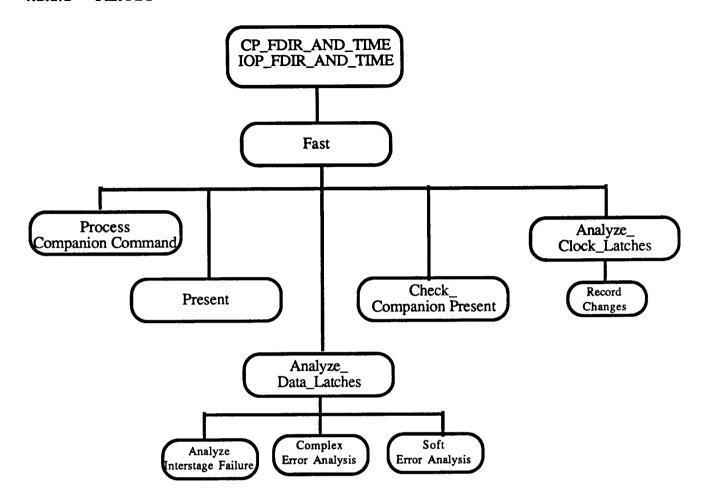

| 20.       | Fast FDI Processes                                                     | 59     |

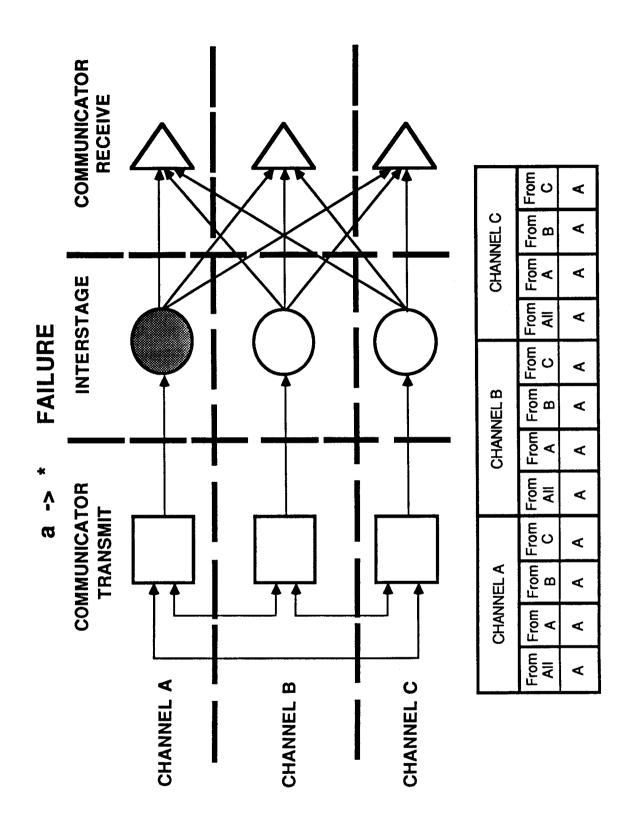

| 21.       | Data Exchange Error Latch Settings                                     | 65     |

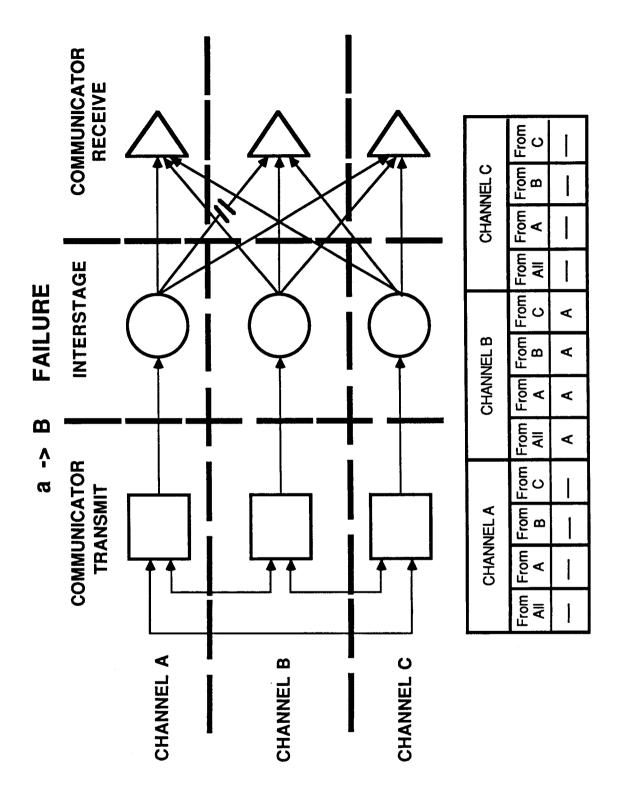

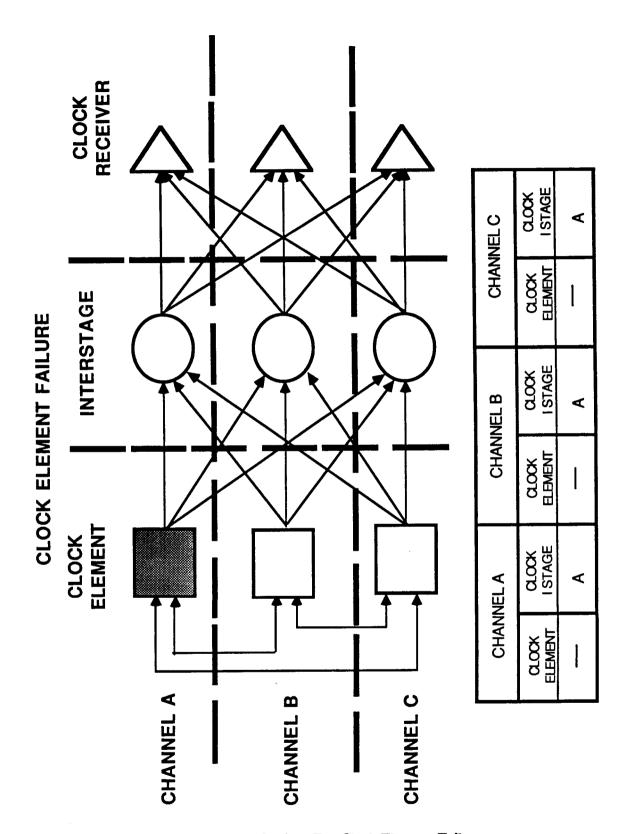

| 22.       | Latch Settings For Interstage Failure                                  | 67     |

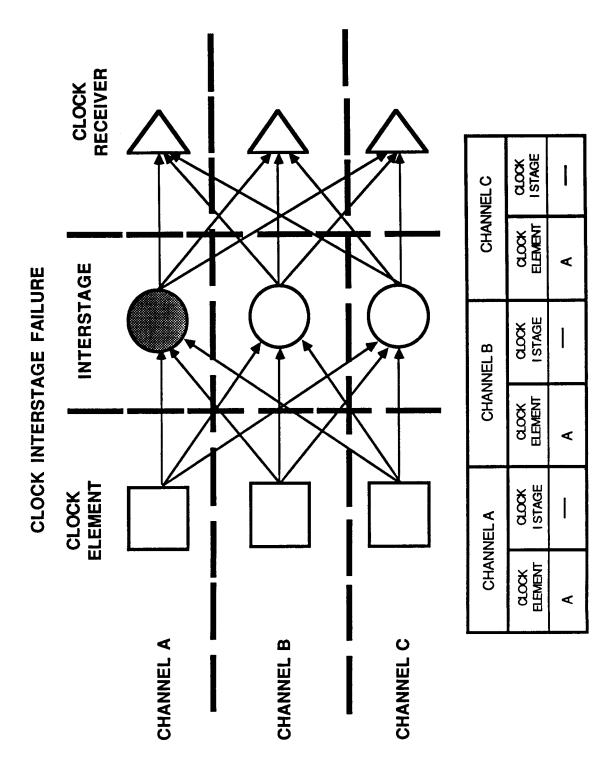

| 23.       | Latch Settings For Interstage - Receiver Link Failure                  | 69<br> |

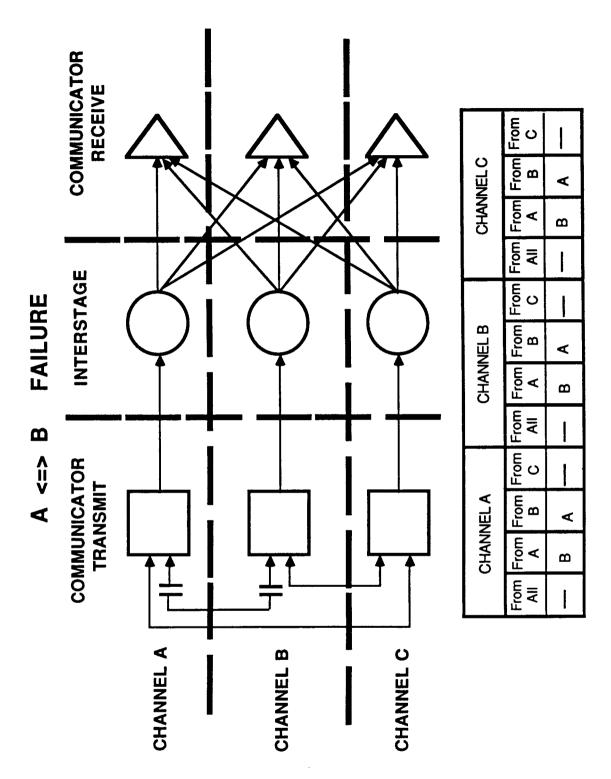

| 24.       | Latch Settings For Bidirectional Transmitter - Transmitter Failure     | 70     |

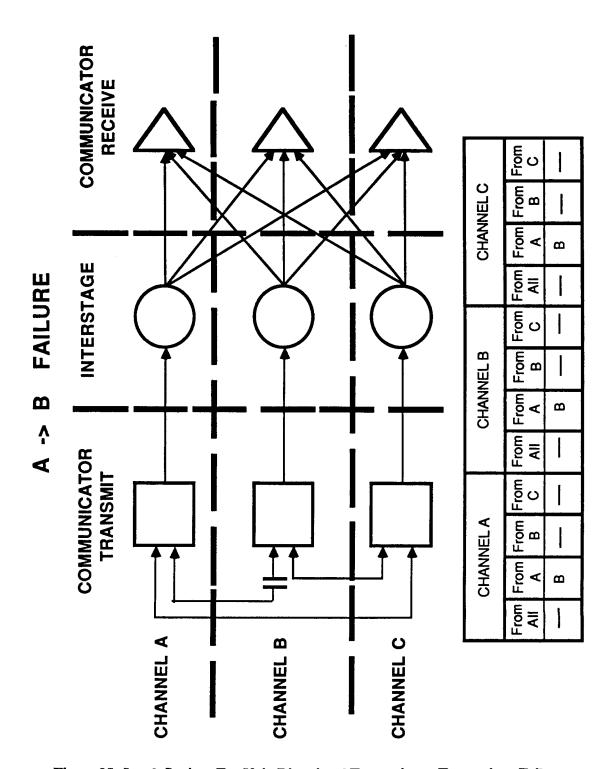

| 25.       | Latch Settings For Uni - Directional Transmitter - Transmitter Failure | 71     |

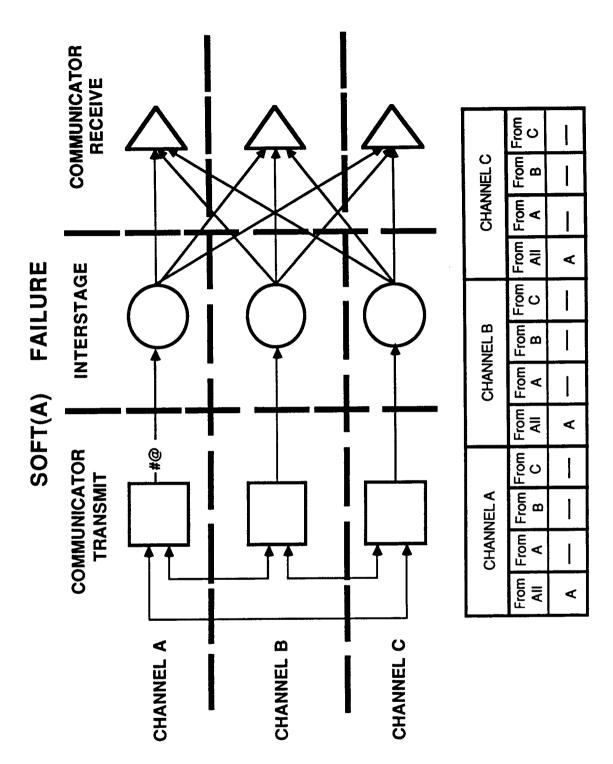

| 26.       | Latch Settings For "Soft" Failure                                      | 73     |

|           | Latch Settings For Clock Element Failure                               |        |

|           | Latch Settings For Clock Interstage Failure                            |        |

| 29.       | Watchdog Timer Reset Processes                                         | 78     |

| 30.       | Background Selftests Processes                                         | 18     |

|           | Test on a Two-Bit Unit                                                 |        |

| 32.       | Data Exchange Error Latch Tests and Expected Results                   |        |

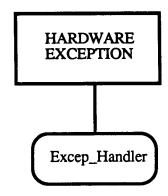

| 33.       | Exception Handler Processes                                            | 98     |

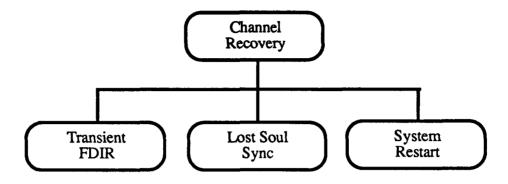

| 34.       | Channel Recovery Functions                                             | 99     |

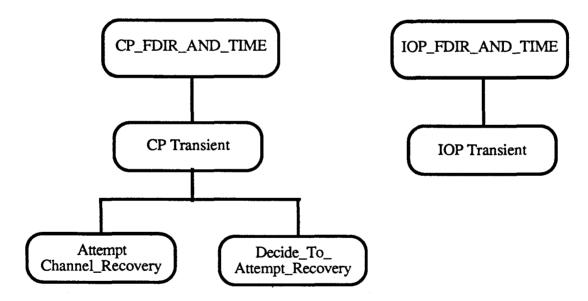

|           | Transient FDIR Processes                                               |        |

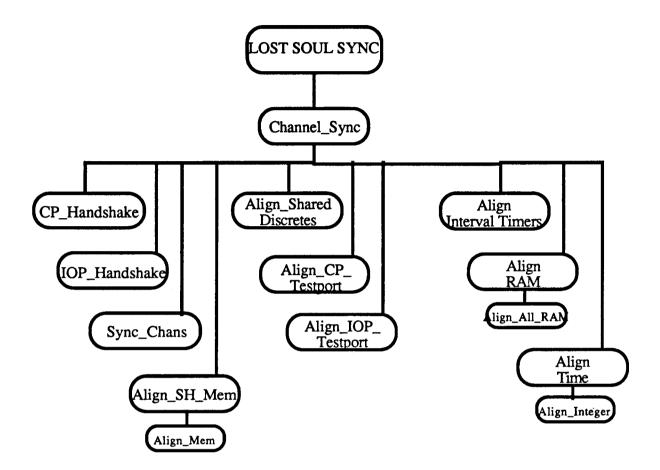

| 36.       | Lost Soul Sync                                                         | 106    |

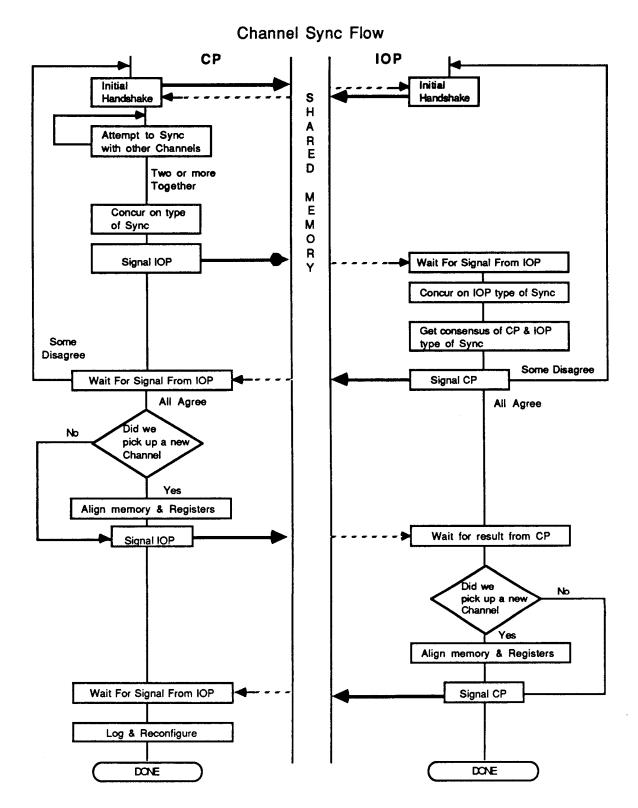

| 37.       | Channel Sync Flow Diagram                                              | 301    |

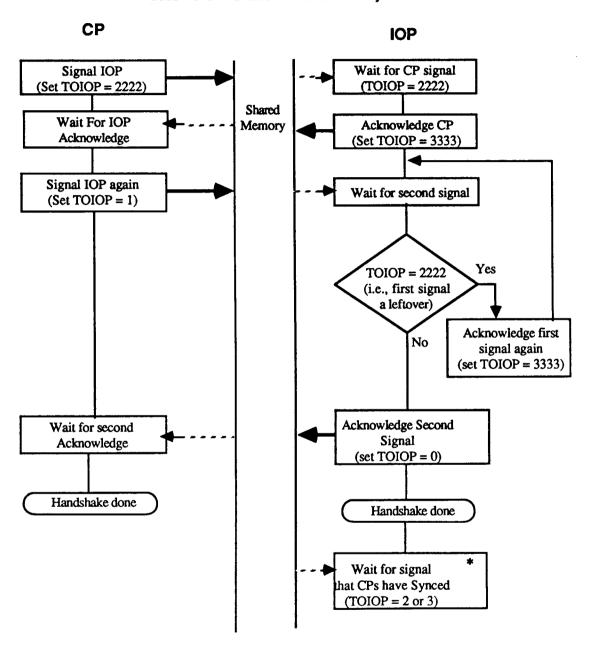

| 20        | CP and IOP Handshake Flow                                              |        |

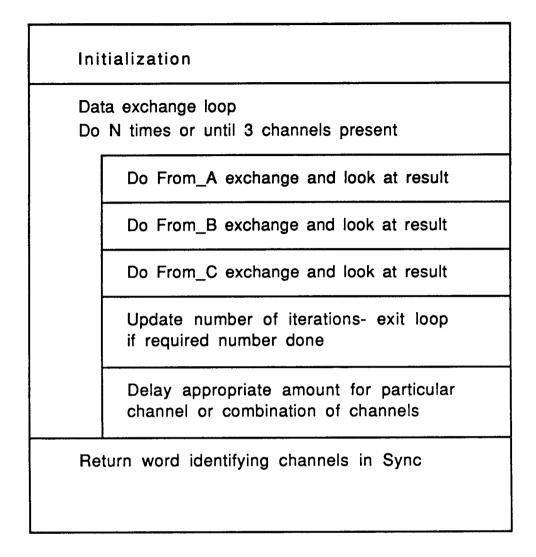

| 39. Sync Chans N-S Diagram                           | 116  |

|------------------------------------------------------|------|

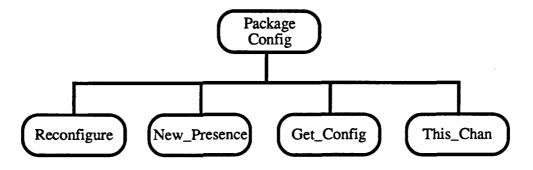

| 40. Reconfiguration Processes                        | 124  |

| 41. GPC Status Reporter Functions                    | 133  |

| 42. GPC Status Reporter Data Flow                    | 134  |

| 43. Status Database                                  | 135  |

| 44. Status Display                                   | 136  |

| 45. Database Management Process Descriptions         |      |

| 46. Terminal Display Processes                       |      |

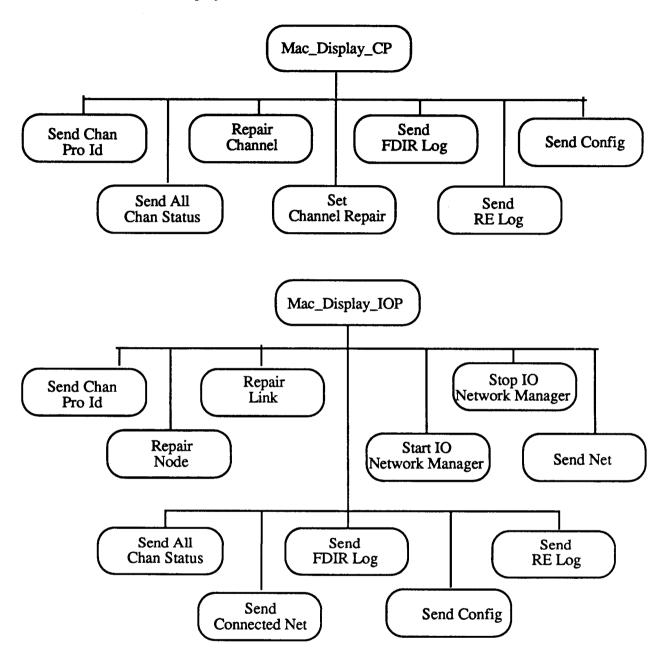

| 47. Macintosh Display Processes                      | 151  |

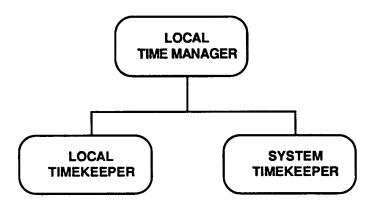

| 48. Local Time Manager                               |      |

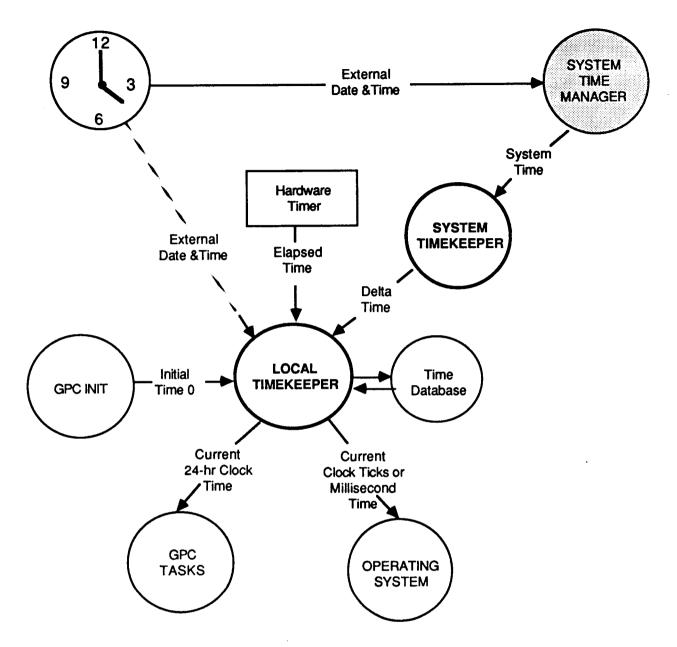

| 49. Information Flow through the Local Time Manager  | 160  |

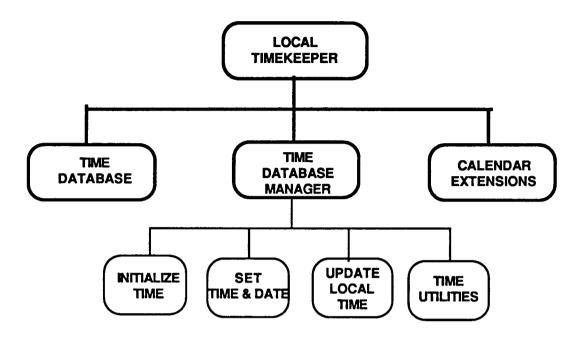

| 50. Local Timekeeper Components                      |      |

| 51. System Timekeeper                                |      |

| 52. FDIR and Operating System Overhead Measurements  |      |

| A-1 Overview of Data Exchange Hardware               | A-2  |

| A-2 Cross-Channel Communication and Voter/Selector   | A-5  |

| A-3 Addresses of Data Exchange Registers             | A-7  |

| A-4 Simplex Data Exchange From Channel B             | A-8  |

| A-5 Voted Data Exchange                              |      |

| A-6 Error Register Formats                           | A-11 |

| A-7 IC Network Interface For One FTP Channel         | A-12 |

| A-8 Data Flow Through LMN and Cross-Channel Hardware |      |

| A-9 Data Flow From CP to ICIS                        |      |

### 1.0 INTRODUCTION

The purpose of this report is to document the functional requirements and detailed specifications for the Local System Services of the Advanced Information Processing System (AIPS). This introductory section is provided to outline the overall architecture and functional requirements of the AIPS system. Section 1.1 gives a brief overview of the AIPS architecture as well as a detailed description of the AIPS Fault Tolerant Processor (FTP) architecture, while Section 1.2 provides an introduction to the AIPS system software. Sections 2 through 6 describe the Local System Services functional requirements and design and detailed specifications. Each of these sections describes one of the Local System Services functions. Section 7 concludes with a summary of results and suggestions for future work in this area.

### 1.1 AIPS Architecture

The Advanced Information Processing System is designed to provide a fault- and damage-tolerant data processing architecture which can serve as the core avionics system for a broad range of aerospace vehicles being researched and developed by NASA. These vehicles include manned and unmanned space vehicles and platforms, deep space probes, commercial transports, and tactical military aircraft.

AIPS is a multicomputer architecture composed of hardware and software 'building blocks' that can be configured to meet a broad range of application requirements. The hardware building blocks are fault-tolerant, general purpose computers (GPCs), fault- and damage-tolerant inter-computer (IC) and input/output (I/O) networks, and interfaces between the networks and the general purpose computers. The software building blocks are the major software functions: local system services, input/output system services, inter-computer system services and the system manager. This software provides the services necessary in a traditional real-time computer such as task scheduling and dispatching, communication with sensors and actuators, etc. The software also supplies the redundancy management services necessary in a redundant computer and the services necessary in a distributed system such as inter-function communication across processing sites, management of distributed redundancy, management of networks, and migration of functions between processing sites.

The AIPS hardware consists of a number of computers which may be physically dispersed throughout a vehicle. These dispersed computers are linked together by a reliable, damage-tolerant data communication pathway called the IC network, or IC bus. (Since the hardware implementation is a circuit-switched network which appears to the communication software and the receiving and transmitting devices as a conventional bus, the terms 'network' and 'bus' are used interchangeably throughout this document.) A computer at any particular processing site may also have access to varying numbers and types of I/O buses, which are separate from the IC bus. The I/O buses may be global,

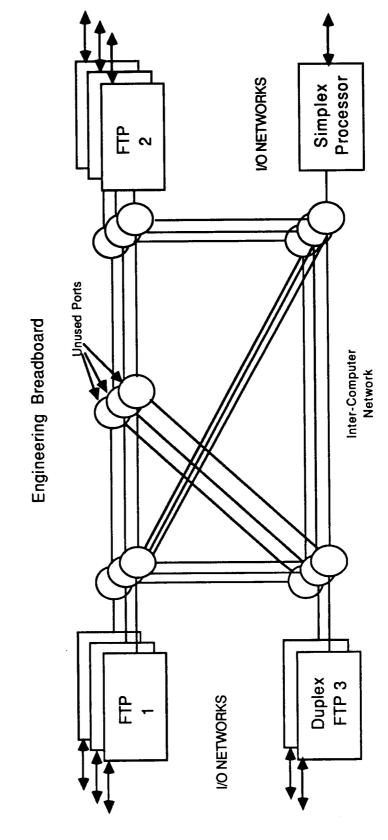

regional or local in nature. I/O devices on the global I/O bus are available to all, or at least a majority, of the AIPS computers. Regional buses connect I/O devices in a given region to the processing sites located in their vicinity. Local buses connect a computer to the I/O devices dedicated to that computer. Additionally, I/O devices may be connected directly to the internal bus of a processor and accessed as though the I/O devices reside in the computer memory (memory mapped I/O). Both the I/O buses and the IC bus are time-division multiple-access contention buses. Figure 1 shows the laboratory engineering model for a distributed AIPS configuration. This distributed AIPS configuration includes all the hardware and software building blocks mentioned earlier and was conceived to demonstrate the feasibility of the AIPS architecture.

The laboratory configuration of the distributed AIPS system shown in Figure 1 consists of four processing sites. Each processing site has a General Purpose Computer (GPC). GPCs may be simplex or they may be FTPs of varying redundancy levels. Of the four FTPs in the laboratory configuration, one is simplex, one is duplex, and two are triplex processors. An FTP may also be quadruply redundant but none was fabricated for the AIPS laboratory demonstration. The redundant FTPs are built such that they can be physically dispersed for damage tolerance; each of the redundant channels of a FTP can be as far as 5 meters from other channels of the same FTP. The FTP architecture is described in more detail in the following subsection.

The GPCs communicate with each other over the Inter-Computer Network, in which the circuit-switching nodes have been configured into redundant virtual buses. Each redundant bus is referred to as a layer; these layers are totally independent and are not cross-strapped to each other. Each layer contains a circuit-switched node for each processing site; thus every processing site is serviced by three nodes of the IC network. GPCs are designed to receive data on all three layers, but the capability of a GPC to transmit on the network depends on the GPC redundancy level. Triplex FTPs can transmit on all three layers, duplex FTPs on only two of the three layers, and simplex processors on only a single layer. In duplex and triplex FTPs, a given processor can transmit on only one network layer. Thus malicious behavior of a processor can disrupt only one layer.

The IC network and the GPC interfaces into the network are designed in strict accordance with fault-tolerant systems theory so that any arbitrary random hardware fault, even a Byzantine fault, can not disrupt communication between triplex FTPs. Thus the triplex IC network, in conjunction with the GPC interfaces into the network, provides error-masking capability for communication between two triplex computers.

The I/O network is demonstrated in the laboratory using a 15-node circuit-switched network that interfaces with each of the GPCs on 1 to 6 nodes, depending on the GPC redundancy level. The 15 I/O nodes can be configured in the laboratory as global, regional, and local I/O networks to demonstrate various dimensions of the AIPS I/O concept.

# Advanced Information Processing System (AIPS)

Figure 1. AIPS Distributed Configuration

### 1.1.1 AIPS Fault Tolerant Processors: Overview

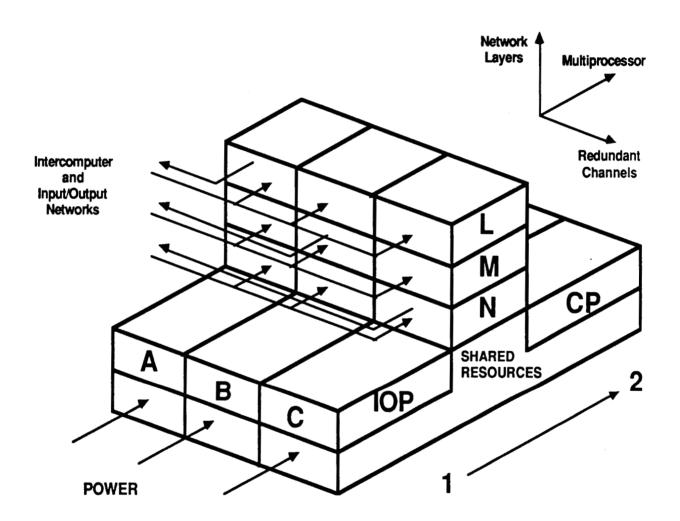

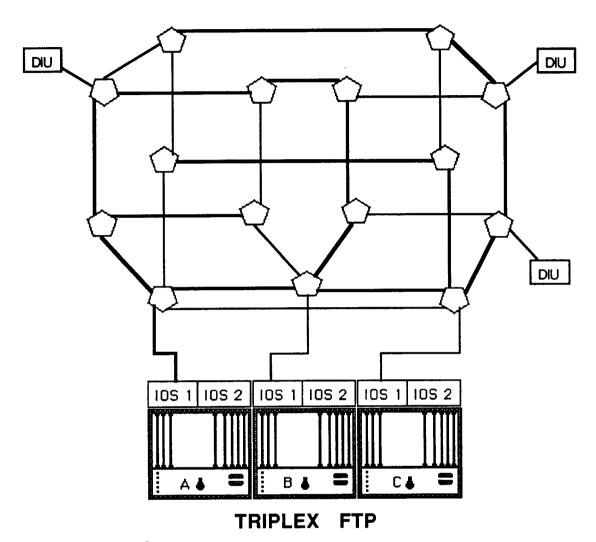

The AIPS Fault-Tolerant Processor (FTP) is a significant enhancement of the CSDL FTP [1,2] developed and used in many centralized real-time applications. The basic FTP architecture has been enhanced to work efficiently and reliably in the distributed information processing environment of AIPS. Figure 2 shows a simplified schematic of a triplex AIPS FTP.

### **AIPS FAULT TOLERANT PROCESSOR**

Figure 2. Simplified Schematic of AIPS Fault Tolerant Processor

The first enhancement was the addition of a second processor to each channel so that input/output operations can be performed in parallel with application function computations. The I/O processor (IOP) is used to perform the collection of sensor data and transmission of actuator commands that are typical in traditional real-time systems. It also

performs inter-computer communication, which is a significant burden in a distributed system. The IOP thereby leaves its counterpart, the computational processor (CP), free for calculation and decision-making tasks. This architecture has several important attributes.

First, the IOP and the CP share the data exchange and other hardware responsible for providing fault tolerance in the FTP. This results in increased throughput without additional hardware penalties for fault tolerance. Second, by performing all external communications the IOP can, with appropriate help from System Services Software, completely shield the CP and the applications programs running on it from the complexities of a distributed processing environment. Third, by making all the incoming data congruent before presenting it to the CP, the IOP also shields the applications programs from the redundant nature of the system. These last two attributes greatly simplify the process of developing applications software.

The second major enhancement to the basic FTP architecture was the addition of dedicated hardware interfaces between the FTP and the Input/Output and the Inter-Computer Networks. These are called the Input Output Sequencer (IOS) and the Inter-Computer Interface Sequencer (ICIS), respectively. These interfaces are shared by the CP and the IOP and are shown as blocks L, M, and N in Figure 2. L, M, and N refer to the three layers of the IC network. These interfaces take care of the low level bus protocol and formatting details (typically the physical layer and the data link layer), thus relieving the IOP from having to manage the I/O and IC networks at microsecond time intervals. The ICIS and IOS make it possible to interface the AIPS FTPs to very high speed buses. The possibility of Byzantine faults in the network nodes causing single point FTP failures is quite real, so the design of these interfaces adheres strictly to fault-tolerant systems theoretical principles.

The AIPS FTP architecture is both symmetric and modular. It is symmetric in that either processor can do the work of the other. Since both the CP and the IOP have access to all the external interfaces, the FTP can be operated with only one processor per channel, if desired. For AIPS applications that do not have intensive I/O and/or IC communication, one processor per channel may suffice. Or a combination of one-processor and two-processor GPCs may be used, where sites with little I/O and/or IC activity have only one processor per channel while other sites have two. The architecture is modular in that the number of I/O and IC interfaces per FTP can be varied to fit various processor and network redundancy levels and parallel and partitioned networks.

The AIPS FTP architecture, in combination with the networks, provides a system architecture that is extremely flexible and expandable. It has been designed from the outset to be a distributed architecture utilizing fault-tolerant computers. These qualities can only be appreciated fully if one has faced the task of mating various existing avionics computers,

such as flight control and engine control computers, in order to create an integrated fault-tolerant system.

### 1.1.2 Fault Tolerant Processor: Functional View

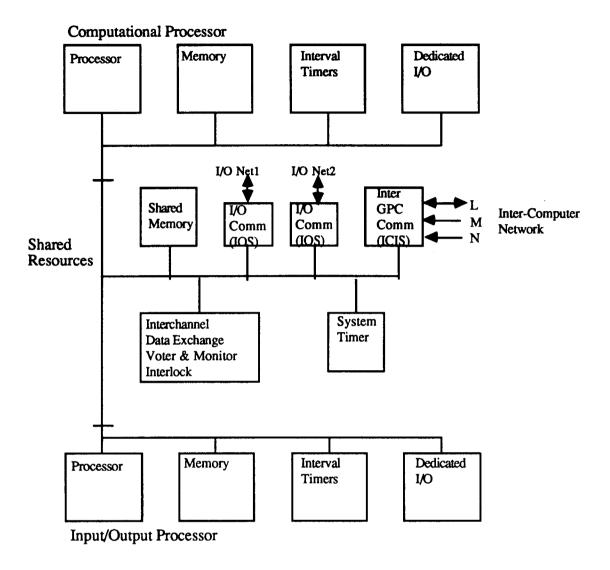

The Fault-Tolerant Processor (FTP) consists of a variable number of redundant processing channels depending on the reliability requirements of the application. The AIPS engineering breadboard FTP is intended to be operated primarily as a triplex, but it provides fail-safe capability when operated as a duplex. A single channel can also be used for non-critical operations as a simplex computer.

Each channel of an FTP consists of three sections: a computational section, an input/output section, and the resources shared between them. The first section contains a Computational Processor (CP), memory, timers and clocks. The second section contains an Input/Output Processor (IOP), memory, timers, and clocks. The shared resources include shared memory, data exchange hardware, timers, and external interface hardware. The redundant processors are tightly synchronized using a fault-tolerant clock. Data is exchanged among redundant channels on point-to-point links. The data exchange hardware also performs the bit-for-bit voting, fault detection and masking functions in a manner that satisfies all the requirements to protect the FTP from Byzantine failures, as described in Appendix A. Apart from redundancy, there are other features that provide hardware and software fault tolerance. These include watchdog timers, processor interlocks, a privileged operating mode, handlers for hardware and software exceptions, and self tests.

A functional view of one channel of an AIPS FTP is shown in Figure 3. The CP and IOP are identical, conventional processor architectures. Interval timers are used for scheduling tasks and maintaining time-out limits on applications tasks (task watchdog timers). A hardware watchdog timer is provided to increase fault coverage and to cause a processor to fail-safe in case of hardware or software malfunctions. This timer resets the processor and disables all of its outputs, if it is not reset periodically. The watchdog timer is implemented independently of the basic processor timing circuitry. A monitor and interlock circuit in each channel provides the capability to disable the outputs of faulty processors. Any two correctly operating processors in a triplex FTP can disable the outputs of the third failed processor through this interlock mechanism. A processor that is failed active is thus prevented from transmitting erroneous data or commands on I/O networks, IC networks, and local I/O devices.

The CP and IOP share resources through a bus that can be accessed by either processor. These shared resources include memory; a system timer; the interchannel data exchange and voting circuits; and interfaces to one or more I/O networks, memory mapped I/O devices, and the IC network.

Figure 3. Fault Tolerant Processor Architecture: Functional View (One Channel)

One very important aspect of the FTP architecture is the interconnection hardware between redundant channels. The interchannel data exchange and voting hardware serves three purposes: it provides a path for distributing data in one channel to all other channels; it provides a mechanism for comparing results of the redundant channels; and it provides a path for distributing and comparing timing and control signals such as the fault tolerant clock and external interrupts.

Two types of data exchanges are possible: a simplex exchange or a voted exchange. The simplex exchange is used to distribute copies of data from one channel to all other channels, for example, the value of a sensor that is available in only one channel. A voted exchange, on the other hand, is used to compare and vote results of the redundant channels, for example, an actuator command produced by all three channels which must be voted before the command is actually issued.

The interchannel data exchange and voting circuits appear on the shared bus as a set of registers which include the transmit register, the receive register, and error latches. Data is exchanged between redundant channels one word at a time by writing the word to the transmit register and then reading the result from the receive register. When an exchange is initiated, the transmitter in each channel sends to all channels either its own data (in the case of a voted exchange) or the data available from another channel (in the case of a simplex exchange). Each channel thus receives three copies of the data, which are voted on a bit-by-bit basis. The majority result, which will be the same in all channels even in the presence of an error, is placed in each processor's receive register. The type of exchange (voted or simplex) which will be performed is determined by the particular transmit register that is referenced when the exchange is initiated.

Either type of exchange takes on the order of 5 microseconds in the engineering breadboard version of the AIPS FTP. The hardware is designed to lock out access to the receive register while the exchange is in progress; a processor which tries to read the receive register before the transaction has completed is suspended. As soon as the data becomes available, the processor is released and the register read cycle completes normally. The processor wait is thus transparent to the software.

The same software executes on a redundant FTP as on a simplex channel and application code is written as if it were to operate on a simplex computer. All redundant processors have identical software and execute identical instructions at exactly the same time. This feature of the architecture is carried out in the data exchange hardware and software as well. The data exchange hardware is designed such that all redundant processors execute identical instructions when exchanging data whether it is redundant data to be voted or simplex data being transmitted from one channel to others. Thus, for example, if a simplex exchange is to be made from channel A, all three channels write to their FROM\_A register. While the contents of the FROM\_A register are transmitted from A, voted, and deposited in the receive registers of all three processors, the contents of the FROM\_A registers in channels B and C, which are meaningless, are ignored.

On a routine basis, the internally produced data that needs to be exchanged consists of error information and cross channel comparisons of results for fault detection. These operations can be easily confined to the program responsible for Fault Detection, Identification, and Reconfiguration (FDIR). Voting of the results of the redundant computational processors is performed in hardware by the input/output processors and the system software responsible for the I/O services. Therefore, the remaining pieces of the Operating System software and the applications programs need not be aware of the existence of the data exchange registers. The task scheduler and dispatcher, for example, can view the computational core as a single reliable processor.

Data from other processing sites is received by each IOP on the redundant IC buses,

hardware voted, and then deposited in their respective shared memories. Simplex source data such as that from I/O devices is received by the IOP in one channel to which the I/O device is physically connected. This data is then transmitted to the other two IOPs using the data exchange registers. The congruent data is then deposited in all three shared memories. Thus, the computational processor obtains all external data that has already been processed for errors and source congruency requirements by I/O System Services executing on the I/O processor.

The IOP and CP communicate through the shared memory. The IOP and CP have independent operating systems that cooperate to assure that the data from input devices is made available to the applications programs running in the CP in a timely and orderly fashion. Similarly, the two processors cooperate on the outgoing information so that the output devices receive commands at appropriate times. Hence the CP and IOP actions must be synchronized to some extent. To help achieve this synchronization in software, a hardware feature has been provided which enables one processor to interrupt the other. By writing to a reserved address in shared memory the CP can interrupt the IOP and by writing to another reserved location the IOP can interrupt the CP. Different meanings are assigned to this interrupt by leaving an event code in some other predefined part of the shared memory, before the inter-processor interrupt is asserted.

For routine flow of information in both directions, the shared memory is used without interrupts but with suitable locking semaphores to pass consistent data sets. The interrupts can be used to synchronize this activity as well as to pass time critical data that must meet tight response time requirements. In order to assure data consistency, it is necessary that while one side is updating a block of data the other side does not access that block of data. This has been implemented using software semaphores. Hardware support for semaphores is provided in the form of the test and set instruction.

The architectural approach described above provides several significant operational benefits. The most important of these is the decoupling of the computational and input/output streams of transactions. The computational processor is unburdened from having to do I/O transactions. To the CP, all I/O appears memory mapped including not only I/O devices but also all other computers in the system. That is, each sensor, actuator, switch, computer, etc., with which the FTP interfaces can be addressed simply by reading or writing words in the shared memory.

### 1.2 AIPS System Software

The AIPS system software, as well as the hardware, has been designed to provide a virtual machine architecture that hides hardware redundancy, hardware faults, multiplicity of resources, and distributed system characteristics from the applications programmer. Section 1.2.1 discusses the approach used for the AIPS system software design. Section 1.2.2 is a high level description of the system services that are provided for AIPS users.

### 1.2.1 AIPS Software Design Approach

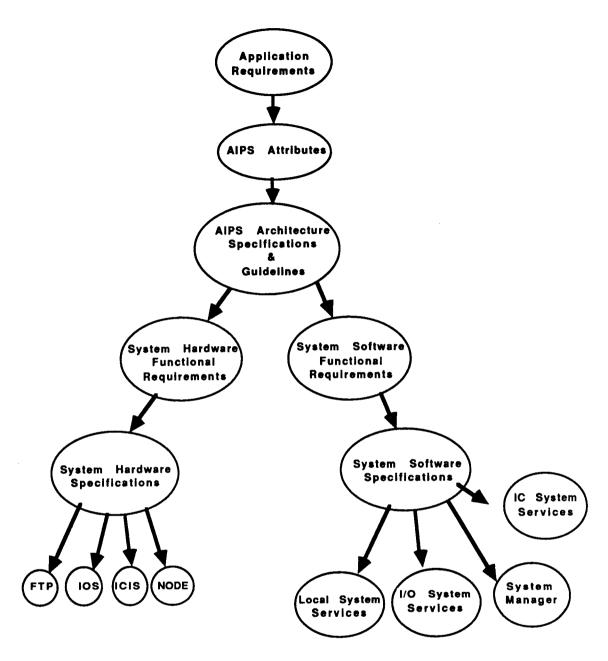

The approach used to design the AIPS system software is part of the overall AIPS system design methodology. An abbreviated form of this system design methodology is shown in Figure 4. This methodology began with the application requirements and eventually led to a set of architectural specifications. The architecture was then partitioned into hardware and software functional requirements. This report documents the design approach used for Local System Services software, beginning with the functional requirements and proceeding through detailed specifications.

Hardware and software for the AIPS architecture is being designed and implemented in two phases. The first phase is the centralized AIPS configuration. The centralized AIPS architecture, as shown in Figure 5, is configured as one triplex Fault Tolerant Processor (FTP), an Input/Output network and the interfaces between the FTP and the network, referred to as input/output sequencers (IOS). The laboratory demonstration of the input/output network consists of 15 circuit-switched nodes which can be configured as multiple local I/O networks connected to the triplex GPC. For example, the I/O network may be configured as one 15-node network, as shown in Figure 5, or as three 5-node networks. The software building blocks that have been designed and implemented for the AIPS centralized architecture include local system services and I/O system services. The following subsection 1.2.2 gives an overview of all the AIPS software building blocks. The remainder of the document, Sections 2 through 6, focuses on the functional design and detailed specification of the Local System Services.

Figure 4. AIPS System Design Approach

### 15-NODE I/O NETWORK

- Node

- Active Link

- Spare Link

- DIU Device Interface Unit

- IOS GPC/Network Interface (I/O Sequencer)

Figure 5. Centralized AIPS Configuration

### 1.2.2 AIPS System Software Overview

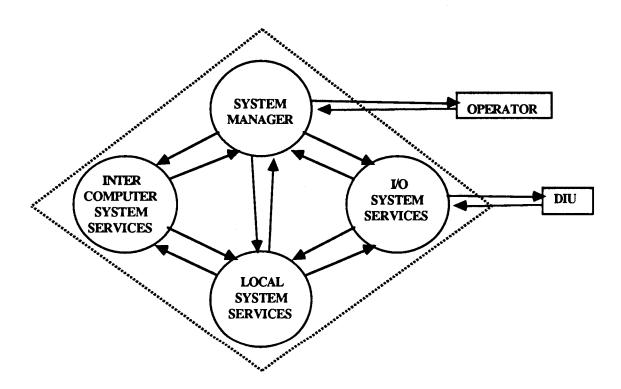

As shown in Figure 6, AIPS system software provides the following AIPS System Services: local system services, communication services, system management, and I/O system services. The system software is being developed in Ada. System services are modular and partitioned naturally according to hardware building blocks. The distributed AIPS configuration includes all the services. Versions of the system software for specific applications can be created by deleting unused services from this superset. The System Manager functions reside on only one GPC, but all functions of the System Manager are not necessarily on the same GPC. The other system services are replicated in each GPC. A brief description of each of the services follows.

Figure 6. Top Level View Of System Services

### 1.2.2.1 Local System Services

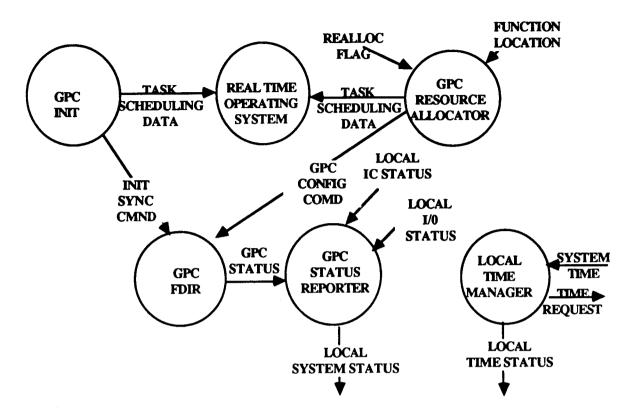

The local system services provided in each GPC are: GPC initialization, real-time operating system, local resource allocation, local GPC Fault Detection, Isolation, and Reconfiguration (FDIR), GPC status reporting, and local time management (see Figure 7).

Figure 7. Local System Services

The function of GPC initialization is to bring the GPC to a known and operational state from an unknown condition (cold start). GPC initialization synchronizes the CPs, synchronizes the IOPs and resets or initializes the GPC hardware and interfaces (interval timers, real time clock, interface sequencers, DUART, etc.) It makes the hardware state of the redundant channels congruent by alignment of memory and control registers. It then activates the system baseline software that is common to every GPC.

The AIPS real-time operating system supports task execution management, including scheduling according to priority, time and event occurrence, and is responsible for task dispatching, suspension and termination. It also supports memory management, software exception handling, and intertask communication between companion processors (IOP and CP). The AIPS operating system resides on every CP and IOP in the system. It uses the vendor-supplied Ada Run Time System (RTS), and includes additional features required for the AIPS real-time distributed operating system.

The GPC resource allocator coordinates and determines responsibility for any global or migratable functions from the system resource manager. It also monitors commands from the system resource manager to start or stop any function.

The GPC status reporter collects status information from the local functions, the local GPC FDIR, the IC system services and the I/O system services. It updates its local data base and disseminates this status information to the system manager.

GPC FDIR has the responsibility for detecting and isolating hardware faults in the CPs, IOPs, and shared hardware. It is responsible for synchronizing both groups of processors in the redundant channels of the FTP and for disabling outputs of failed channel(s) through interlock hardware. After synchronization, all CPs will be executing the same machine language instruction within a bounded skew, and all IOPs will be executing the same machine language instruction within a bounded skew. GPC FDIR logs all faults and reports status to the GPC status reporter. It is responsible for the CPU hardware exception handling and downmoding/upmoding hardware in response to configuration commands from the system manager. It is also responsible for transient hardware fault detection and for running low priority self tests to detect latent faults. This redundancy management function is transparent to the application programmer.

The local time manager works in cooperation with the system time manager to keep the local real time initialized and consistent with the universal time. It is also responsible for providing time services to all users.

Sections 2 through 6 describe the Local System Services functional requirements and design and detailed specifications. Each of these sections describes one of the Local System Services functions. Section 7 concludes with a summary of results and suggestions for future work in this area.

### 1.2.2.2 Inter-Computer System Services

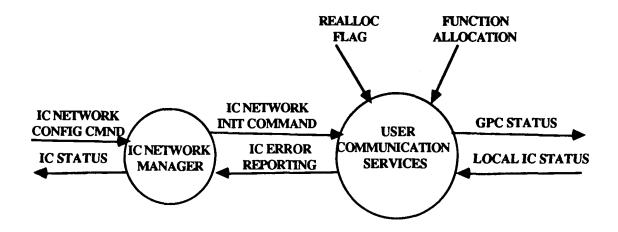

The inter-computer system services provide two functions: (1) inter-computer user communication services, that is, communication between functions not located in the same GPC, and (2) inter-computer network management (Figure 8).

The IC user communication service provides local and distributed inter-function communication which is transparent to the application user. It provides synchronous and asynchronous communication, performs error detection and source congruency on inputs, and records and reports IC communication errors to IC network managers. Inter-computer communication can be done in either point to point or broadcast mode and is implemented in each GPC.

The IC network manager is responsible for the fault detection, isolation and reconfiguration of the network. The AIPS distributed configuration consists of three identical, independent IC network layers which operate in parallel to dynamically mask faults in a single layer and provide reliable communication. There is one network manager for each network layer. However, the three network layer managers do not need to reside in the same GPC. They are responsible for detecting and isolating hardware faults in IC nodes and links and for

reconfiguring their respective network layer around any failed elements. The network manager function is transparent to all application users of the network.

Figure 8. Inter-Computer System Services

### 1.2.2.3 System Manager

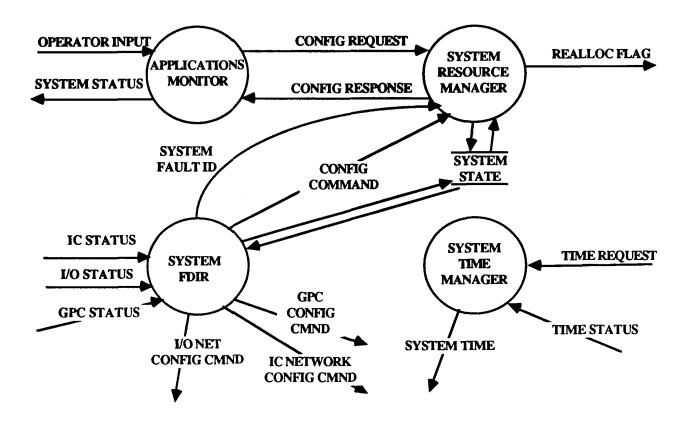

The system manager is a collection of system level services including the applications monitor, the system resource manager, the system fault detection, isolation and reconfiguration (FDIR), and the system time manager (Figure 9).

The applications monitor interfaces with the applications programs and the AIPS system operator. It accepts commands to migrate functions from one GPC to another, to display system status, to change the state of the system by requesting a hardware element state change, and to convey requests for desired hardware and software configurations to the system resource manager.

The system resource manager allocates migratable functions to GPCs. This involves the monitoring of the various triggers for function migration such as failure or repair of hardware components, mission phase or workload change, operator or crew requests and timed events. It reallocates functions in response to any of these events. It also designates managers for shared resources and sets up the task location data base in each GPC.

The system fault detection, isolation and reconfiguration (FDIR) is responsible for the collection of status from the inter-computer (IC) network managers, the I/O network managers, and the local GPC redundancy managers. It resolves conflicting local fault isolation decisions, isolates unresolved faults, correlates transient faults, and handles processing site failures.

Figure 9. System Manager

The system time manager, in conjunction with the local time manager on each GPC, has the job of maintaining a consistent time across all GPCs. The system time manager indicates to the local time manager when to set its value of time. It also sends a periodic signal to enable the local time manager to adjust its time to maintain consistency with an external time source such as the GPS Satellites or an internal source such as the real time clock in the GPC which hosts the system time manager software.

### 1.2.2.4 I/O System Services

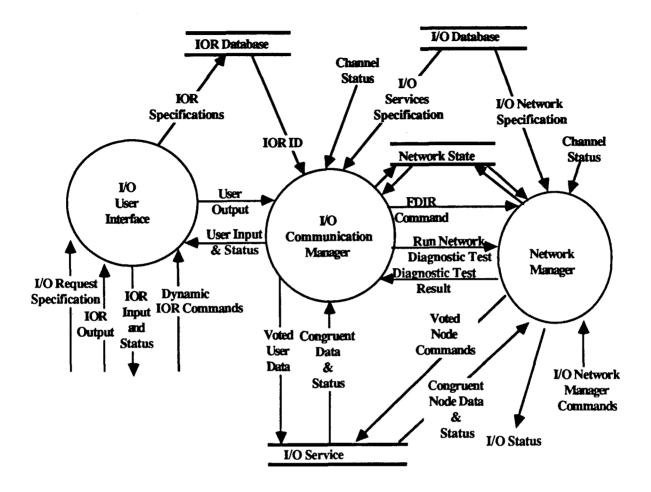

The I/O system services provide efficient and reliable communication between the user and external devices (sensors and actuators). The I/O system services software is also responsible for the fault detection, isolation and reconfiguration of the I/O network hardware and GPC/network interface hardware (input/output sequencers).

I/O system services is made up of three functional modules: I/O user interface, I/O communication management and the I/O network manager (Figure 10).

Figure 10. I/O System Services

The I/O user interface provides a user with read/write access to I/O devices or Device Interface Units (DIUs), such that the devices appear to be memory mapped. It also gives the user the ability to group I/O transactions into chains and I/O requests, and to schedule I/O requests either as periodic tasks or on demand tasks. A detailed description of the I/O user interface is provided in [3].

The I/O communication manager provides the functions necessary to control the flow of data between a GPC and the various I/O networks used by the GPC. It also performs source congruency and error detection on inputs, voting on all outputs, and reports communication errors to the I/O Network Manager. It is also responsible for the management of the I/O request queues. A detailed description of the I/O communication manager is provided in [3].

The I/O Network Manager is responsible for detecting and isolating hardware faults in I/O nodes, links, and interfaces and for reconfiguring the network around any failed elements. The network manager function is transparent to all application users of the network. A detailed description of the I/O Network Manager is provided in [4].

### 2.0 GPC INITIALIZATION

It is the responsibility of the GPC INIT module to bring the GPC to a known and operational state at startup and to initialize the system software tasks and the application procedures and/or tasks.

### 2.1 GPC Initialization Functional Requirements and Design

The function of GPC initialization is to bring the GPC to a known and operational state. If the GPC has a redundancy level greater than a simplex, the initialization software module is responsible for controlling the transition from an unknown, uninitialized state of the FTP hardware to a state such that all available channels are operating in an instruction-synchronous manner. Furthermore, the module will insure that the channels operating in such a synchronous manner will have "aligned", or "bit-for-bit identical", states of all redundant hardware elements (e.g., RAM and interval timers). Once this instruction-synchronous, hardware-aligned status is established for the FTP, it will continue to operate in a synchronous mode until a fault forces a channel out of synch. (This statement assumes all external data to the FTP is made congruent across channels by the appropriate I/O software.)

Upon reset, a processor will vector to the start-up entry point of the operating system. Standard initialization operations must be performed at this point:

- Initialization of standard hardware such as interval timers, real time clock, and DUARTs

- Exception vector initialization

- Interrupt handler initializations

- Software initialization (Ada "elaboration", including initialization and activation of tasks)

- Execution of power-on self tests

After the standard initialization functions are performed, the FTP specific initialization is performed. The redundant channels are synchronized to the instruction level. Since each channel has two processors, each processor is synchronized with the other processors of its type (i.e., CPs or IOPs). In addition, its companion must be synchronized with other processors of the companion's type, i.e., either both processors of a channel are good or they are both failed. Thus, processor activity within each channel must be coordinated before and during the synchronization process. The processors within each channel synchronize with one another to the extent that all of the intra-channel processors finish

their pre-synch initialization and signal their readiness to operate in synch with their corresponding inter-channel processors. After instruction-level synchronization, the hardware state of the redundant channels is made congruent by alignment of memory and control registers. The channel synchronization and alignment functions are performed within the SYNC software module which is described in Section 4.2.2.2.

After channel synchronization the power-on self tests are performed in order to check for any hardware faults in memory, error latches, voters, real-time clock and monitor interlock hardware. After the system is operational the self tests continue to run in background to check for any latent faults, but they are run in their entirety at system startup. (Execution of the self tests at power-on is optional in the laboratory engineering model.)

Next the operating system tasks are scheduled. These tasks include the redundancy management sequencer task, the GPC Status Reporter/CRT display tasks, and the I/O system services tasks. Finally, the application tasks are scheduled and the self test loop is entered. The self tests execute at the lowest priority when the system would otherwise be idle.

### 2.2 GPC Initialization Software Specifications

Process Name: Main Program

**Inputs:** DUART, interval timers, real time clock

Unsynchronized Processors, Channels

Non Aligned Volatile memory, control registers Uninitialized Task Control Blocks, Tasks Stacks Uninitialized interrupt handlers, exception handlers

Uninitialized IOS, ICIS Unscheduled Tasks

Outputs: An operational FTP in a known synchronous state

All Tasks scheduled.

Notes: This process calls the SYNC process, Section 4.2.2.2

### Description:

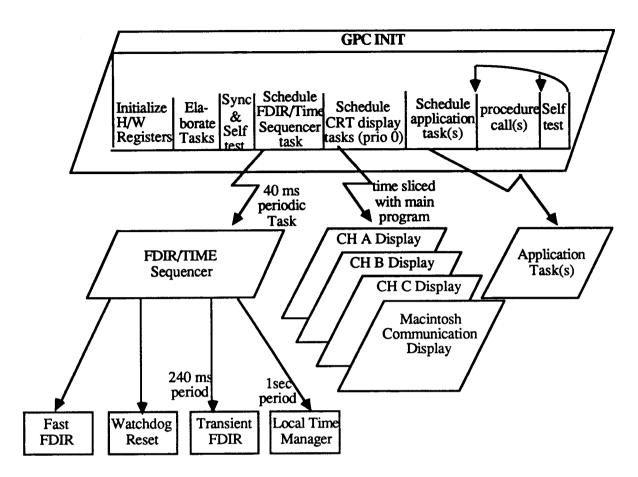

It is the responsibility of the GPC Init function to bring the FTP to an operational mode at startup and to initialize the application procedures and/or tasks. GPC Init resides on both the IOP and CP of each processing site. Since Ada requires that the process which initially executes be named 'Main Program', the GPC Init function is so named in the Ada source code. Figure 11 is a diagram of the control flow of the GPC Init function. First the

DUARTs, interval timers, real time clock and the interrupt and exception vectors are initialized. Then the elaboration of all system packages and tasks is completed. This includes initialization of every task control block and task stack area. Next the available channels of the FTP are synchronized and all volatile memory, control registers, interval timers, and real time clock are aligned in the synchronized channels. This is done by the SYNC process, Section 4.2.2.2, in both the CP and IOP processors.

Once the FTP is running synchronously, a complete iteration of the self tests is performed. These tests, which detect and identify faults in memory, error latches, voters, the real-time clock and the monitor interlock, are described in Section 4.2.1.3. The difference in the power-on self tests and the background self tests is that the power-on tests are not interrupted until an entire iteration has been completed.

Next the Local System Services sequencer task, the FDIR/Time Manager, is scheduled. This task is responsible for the execution of the periodic Local System Service functions: Fast FDIR, Transient FDIR and the Local Time Manager. The FDIR/Time Manager is a high priority, periodic task and presently executes every 40 milliseconds. The periodicity of this task is dependent on the particular application running on the GPC; it may be different for each GPC site. The FDIR/Time Manager and the three processes it controls are discussed in Sections 4.2.1, 4.2.2 and 6.1.1.2.3.

Finally, the GPC Status Reporter display tasks are scheduled. There are three tasks for CRT display and one task for Macintosh display. Like the main task, these tasks are of the lowest priority and are time-sliced with each other and the main program. The GPC Status Reporter/display tasks are described in Section 5.2.2. The time slice interval is equal to the period of the fastest periodic task in the system.

At this point all of the Local System Services tasks have been scheduled and the FTP is in a known and operational state. I/O System Services tasks and any application tasks may now be scheduled and/or application procedures called.

The main program finally enters the self test loop where it executes continually at the lowest priority the self tests in order to uncover latent faults. The self tests are described in Section 4.2.1.3. If needed, applications may call procedures within this loop also.

Figure 11. GPC INIT Control Flow Diagram

### 3.0 REAL TIME OPERATING SYSTEM

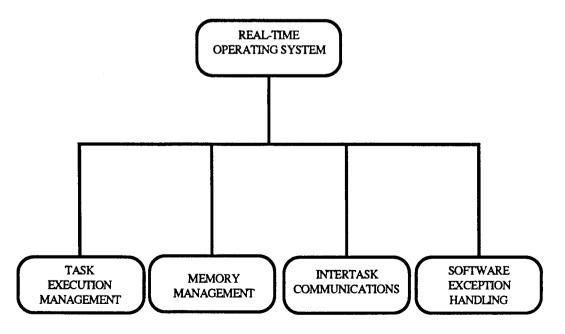

The foundation of the system software for AIPS is a real-time, multi-tasking operating system providing mechanisms for task scheduling, inter-task communication, memory management, and interrupt handling. The AIPS operating system consists of the vendor-supplied Ada Run Time System (RTS) along with those extensions needed to implement the functions given below. The extensions are written in Ada with time critical sections done in assembly language to reduce system overhead. The AIPS operating system resides on every IOP and CP.

### 3.1 Real Time Operating System Functional Requirements

The AIPS operating system provides the basic system services necessary to support the other application software tasks (see Figure 12). These services include:

- 1. Task execution management, including scheduling according to priority, time and event occurrence; dispatching (context switching); task suspension and termination.

- 2. Memory management, including global data allocation, local data allocation/deallocation and shared data access routines (protected read and write).

- 3. Intertask communication, including both synchronous and asynchronous (mailbox) communication.

- 4. Software exception handling.

Figure 12. AIPS Real Time Operating System

### 3.1.1 Task Execution Management

The basic execution unit is the Ada "task". The management of task execution includes scheduling according to priority, time and event occurrence, dispatching, task suspension and termination. A static priority is associated with each task. Task execution order is according to priority and proceeds in a run-until-blocked mode until one of the following conditions occurs:

- 1. task completion,

- 2. self suspension,

- 3. preemption by hardware interrupt,

- 4. explicit scheduling of higher priority task, or

- 5. time slicing of equal priority task.

A task is capable of scheduling itself or other tasks according to time (one-shot or periodic) or upon the occurrence of a software defined event. The option also exists to bracket the region of a task's periodicity by time or events; i.e. provide start/stop times or events.

The RTS requirements of Ada provide minimal user control of task scheduling with the Ada rendezvous and the "delay" statement. Scheduling by event is not an Ada requirement. So extensions to the Ada RTS are necessary in order for the task to schedule itself or another task cyclically, as the result of an event, at an absolute time, immediately, or to deschedule a task (remove all scheduling requirements).

AIPS requires two additional functions that are not provided by Ada RTS vendors: (1) preserving the data exchange receiver register for each task during a context switch, and (2) voting the program counter (PC) after every interrupt. Preserving the data exchange receiver register is necessary because a data exchange requires two instructions, a write to the transmitter followed by a read from the receiver, and an interrupt could occur after the write but before the read. When a task is suspended, therefore, the receiver value must be saved in the task control block; when a task is resumed, this value must be restored to the receiver. In the laboratory demonstration implementation, which uses a Motorola 68010 processor with an 8 MHz clock, restoring the receiver register takes approximately 5 μs.

Voting the PC after every interrupt is necessary because an interrupt could bring unsynchronized channels back into sync, thus masking the faulty condition. The state of each channel at the time of the interrupt can be determined by voting the PC; when a channel's PC is different from the majority value the operating system sets a flag for the FDIR task. This procedure ensures that a fault is detected as early as possible. In the laboratory demonstration implementation, which uses a Motorola 68010 processor with an 8 MHz clock, the PC check takes approximately  $43 \,\mu s$ , of which  $5 \,\mu s$  is used for the data exchange.

### 3.1.2 Memory Management

There are two types of memory in the FTP, local memory and shared memory. Local memory is memory on the private bus and can be accessed only by a single processor. Shared memory is memory on the shared bus and can be accessed by both processors in a channel.

Local memory is used for task execution. The operating system is responsible for allocating and deallocating all local memory space from heaps and stacks. The user must be able to specify the amount of local memory to be allocated for tasks and data objects. Also, routines are provided for the controlled access (protected read and writes) to data objects shared between multiple application tasks resident on the same processor.

Shared memory can be accessed by tasks resident on different processors and by several tasks resident on the same processor. Routines are provided for controlled access (protected read and writes) to data objects shared between multiple application tasks resident on different processors.

### 3.1.3 Intertask Communication

Local intertask communication is communication that takes place between tasks executing on the same processor. The operating system supports two methods of local inter-task communication: synchronous and asynchronous. Synchronous communication requires the communicating tasks to be at a specified synchronization point and is implemented in Ada by the "rendezvous". In local asynchronous inter-task communication, the communicating tasks are not required to be at a specified synchronization point; rather the communication is via data "mailboxes" using the local memory controlled access routines.

Remote inter-task communication is communication that takes place between tasks executing on different processors. The operating system supports two types of remote inter-task communication: remote task release and asynchronous "mailbox" communication. Remote task release means that a task running on one processor can start or release a task on the other processor. The remote inter-task mailbox communication is supported by using the shared memory controlled access routines.

### 3.1.4 Software Exceptions

Software exceptions not explicitly handled by the applications tasks are intercepted by the operating system and the task is purged.

### 3.2 Real Time Operating System Software Specifications

### 3.2.1 Task Execution Management Process Descriptions

Figure 13. Task Execution Management

### 3.2.1.1 Process Name: PRIORITY SCHEDULE

### **Inputs:**

GENERAL\_TASK\_ID

### **Outputs:**

GENERAL\_TASK\_ID.TASK\_NOT\_WAITING

### **Implementation Requirements:**

- Initiation:

- On demand

### **Process Description:**

If task to be scheduled is not waiting at a scheduling synchronization point, the TASK\_NOT\_WAITING indicator is set and an immediate return to the caller is performed.

Otherwise, if priority of task to be scheduled (GENERAL\_TASK\_ID.PRIORITY) is greater than the priority of the active task (ACTIVE\_TASK\_ID.PRIORITY), execution of the scheduled task is initiated via the PRIORITY\_DISPATCH process; otherwise, the task being scheduled is placed on the ready queue according to its priority and a return to the active task is performed.

### 3.2.1.2 Process Name: TIME\_SCHEDULE

### Inputs:

- GENERAL\_TASK\_ID

- GENERAL\_TASK\_ID.REPETITION\_TIME

- GENERAL\_TASK\_ID.COMPLETION\_TIME

- GENERAL\_TASK\_ID.COMPLETION\_EVENT

- INITIATION\_TIME

### **Outputs:**

None

### **Implementation Requirements:**

- Initiation:

- On demand

### **Process Description:**

Task to be scheduled (GENERAL\_TASK\_ID) is placed on the time queue according to the specified start time (INITIATION\_TIME).

If task is initial task on time queue, the time queue interval timer is updated.

### 3.2.1.3 Process Name: EVENT\_SCHEDULE

### Inputs:

- GENERAL\_TASK\_ID

- GENERAL\_TASK\_ID.COMPLETION\_TIME

- GENERAL\_TASK\_ID.COMPLETION\_EVENT

- EVENT

### **Outputs:**

None

### **Implementation Requirements:**

- Initiation:

- On demand

### **Process Description:**

Task to be scheduled (GENERAL\_TASK\_ID) is placed on the event queue indicated by the specified event(EVENT).

### 3.2.1.4 Process Name: PRIORITY\_DISPATCH

### **Inputs:**

• None

### **Outputs:**

None

### **Implementation Requirements:**

- Initiation:

- ready task priority > active task priority

- active task suspension

- active task termination

### **Process Description:**

If a task is active (ACTIVE\_TASK\_ID /=null), it is preempted and placed on the ready queue according to its priority (ACTIVE\_TASK\_ID.PRIORITY).

Execution of the highest priority task on the ready queue is initiated.

### 3.2.1.5 Process Name: TIME\_DISPATCH

### **Inputs:**

None

### **Outputs:**

TIME\_TASK\_ID.TASK\_NOT\_WAITING

### **Implementation Requirements:**

- Initiation:

- Time queue interval timer interrupt

### **Process Description:**

If task at the head of the time queue (TIME\_TASK\_ID) is not waiting at a scheduling synchronization point, the TASK\_NOT\_WAITING indicator is set and dispatching of the task is not performed.

Otherwise, if priority of time task (TIME\_TASK\_ID.PRIORITY) is greater than priority of active task (ACTIVE\_TASK\_ID.PRIORITY), the PRIORITY\_DISPATCH process is invoked; otherwise, the time task is placed on the ready queue according to its priority.

If the time task is periodic and the current time is less than TIME\_TASK\_ID.COMPLET-ION\_TIME or TIME\_TASK\_ID.COMPLETION\_EVENT has not occurred, then the time task is replaced on the time queue according to its period (TIME\_TASK\_ID.REPETITION\_TIME). Otherwise, the task is removed from the time queue.

The time queue interval timer is set to interrupt for the task now at the head of the time queue.

3.2.1.6 Process Name: SIGNAL\_EVENT

Inputs:

EVENT

**Outputs:**

GENERAL\_TASK\_ID

#### **Implementation Requirements:**

- Initiation:

- On occurrence of event

#### **Process Description:**

All tasks (GENERAL\_TASK\_ID) on event queue indicated by the specified event (EVENT) are dispatched via the EVENT\_DISPATCH process.

3.2.1.7 Process Name: EVENT DISPATCH

Inputs:

GENERAL\_TASK\_ID

**Outputs:**

GENERAL\_TASK\_ID.TASK\_NOT\_WAITING

# **Implementation Requirements:**

- Initiation:

- Invoked by SIGNAL\_EVENT process

#### **Process Description:**

If event task (GENERAL\_TASK\_ID) is not waiting at a scheduling synchronization point, the TASK\_NOT\_WAITING indicator is set and dispatch of the task is not performed.

Otherwise, if priority of event task (GENERAL\_TASK\_ID.PRIORITY) is greater than priority of active task (ACTIVE\_TASK\_ID.PRIORITY), the PRIORITY\_DISPATCH process is invoked; otherwise, the event task is placed on the ready queue according to its priority.

If current time is greater than GENERAL\_TASK\_ID.COMPLETION\_TIME or GENERAL\_TASK\_ID.COMPLETION\_EVENT has occurred, the event task is removed from the specified event queue. Otherwise, the task is left on the queue.

# 3.2.1.8 Process Name: TIME SUSPEND

# **Inputs:**

DELAY\_TIME

#### **Outputs:**

None

# **Implementation Requirements:**

- Initiation:

- On demand

- This process is implemented in Ada by the "delay" statement.

# **Process Description:**

The active task (ACTIVE\_TASK\_ID) is preempted and the TIME\_SCHEDULE process is invoked to place task on the time queue for the specified delay time (DELAY\_TIME).

Ready task execution is initiated by invoking the PRIORITY\_DISPATCH process.

# 3.2.1.9 Process Name: EVENT\_SUSPEND

# **Inputs:**

EVENT

# **Outputs:**

• None

# **Implementation Requirements:**

- Initiation:

- On demand

# **Process Description:**

The active task (ACTIVE\_TASK\_ID) is preempted and the EVENT\_SCHEDULE process is invoked to place task on the event queue indicated by the specified event (EVENT).

Ready task execution is initiated by invoking the PRIORITY\_DISPATCH process.

3.2.1.10 Process Name: TASK\_COMPLETE

# **Inputs:**

• None

# **Outputs:**

• None

# **Implementation Requirements:**

- Initiation:

- On demand

- This process is implemented in Ada by the normal task completion processing of the run time system.

# **Process Description:**

The active task (ACTIVE\_TASK\_ID) is deactivated. The ready task (READY\_TASK\_ID) is initiated by invoking the PRIORITY\_DISPATCH process.

3.2.1.11 Process Name: TASK\_CANCEL

# Inputs:

• GENERAL\_TASK\_ID

# **Outputs:**

None

# **Implementation Requirements:**

- Initiation:

- On demand

# **Process Description:**

The specified task (GENERAL\_TASK\_ID) is removed from the time queue and any applicable event queues. If the task has been preempted (i.e. is on the run queue), it is allowed to run to completion.

# 3.2.1.12 Process Name: TASK\_ABORT

# **Inputs:**

GERNERAL\_TASK\_ID

# **Outputs:**

• None

# **Implementation Requirements:**

- Initiation:

- On demand

- This process is implemented in Ada by the "abort" statement.

# **Process Description:**

The specified task (GENERAL\_TASK\_ID) and any dependent tasks are immediately removed from all queues (ready, time and event) in a manner least disruptive to the system as a whole. If the aborted task is the active task (GENERAL\_TASK\_ID = ACTIVE\_TASK\_ID), the PRIORITY\_DISPATCH process is invoked.

# 3.2.2 Memory Management Process Descriptions

Figure 14. Memory Management

3.2.2.1 Process Name: ALLOCATE\_HEAP

# **Inputs:**

- GENERAL\_TASK\_ID

- GENERAL\_TASK\_ID.HEAP\_SIZE

# **Outputs:**

GENERAL\_TASK\_ID.HEAP\_BASE

# **Implementation Requirements:**

- Initiation:

- Task elaboration

- A STORAGE exception shall be raised if the requested amount of memory is not available.

- This process is implemented by the vendor supplied run time system at task elaboration.

# **Process Description:**

The specified amount (GENERAL\_TASK\_ID.HEAP\_SIZE) of consecutive heap memory is allocated to the requesting task for local stack space and for allocating local data objects.

The base location address (GENERAL\_TASK\_ID.HEAP\_BASE) of memory allocated is returned to the process user.

# 3.2.2.2 Process Name: ALLOCATE\_LOCAL\_OBJECT

#### **Inputs:**

LOCAL\_OBJECT\_SIZE

# **Outputs:**

LOCAL\_OBJECT\_LOCATION

# **Implementation Requirements:**

- Initiation:

- On demand

- A STORAGE exception shall be raised if the requested amount of memory is not available.

- This process is implemented in Ada by the "new" allocator.

# **Process Description:**

The specified amount (LOCAL\_OBJECT\_SIZE) of the requesting task's local heap space is allocated for use by the requesting task as a data object.

The object location address (LOCAL\_OBJECT\_LOCATION) is returned to the process caller.

# 3.2.2.3 Process Name: ALLOCATE GLOBAL OBJECT

#### Inputs:

GLOBAL\_OBJECT\_SIZE

# **Outputs:**

GLOBAL\_OBJECT\_LOCATION

# **Implementation Requirements:**

- Initiation:

- On demand

- A STORAGE exception shall be raised if the requested amount of memory is not available.

# **Process Description:**

The specified amount (GLOBAL\_OBJECT\_SIZE) of the global memory is allocated for use by all tasks as a data object.

The object location address (GLOBAL\_OBJECT\_LOCATION) is returned to the process caller.

3.2.2.4 Process Name: FREE\_HEAP

# Inputs:

- GENERAL\_TASK\_ID

- GENERAL\_TASK\_ID.HEAP\_SIZE

- GENERAL\_TASK\_ID.HEAP\_BASE

# **Outputs:**

None

# **Implementation Requirements:**

- Initiation:

- Task Completion

# **Process Description:**