Proceedings

#### The 2nd Symposium on the

# Frontiers of Massively Parallel Computation

October 10–12, 1988 George Mason University Fairfax, Virginia

IEEE Computer Society Order Number 892 Library of Congress Number 88–82088 IEEE Catalog Number 88CH2649–2 ISBN 0–8186–0892–7 SAN 264–620X

EEE

George Mason University

63/62

0252

Uncl a

N90-

T HA

NACA-TM-101913) THE 2ND SYMPUSIUM 3N THE BUNIERS OF MASSIVELY PARALLEL COMPUTATIONS (NACA) 721 P CSCL 099

#### **COVER PHOTOS:**

1

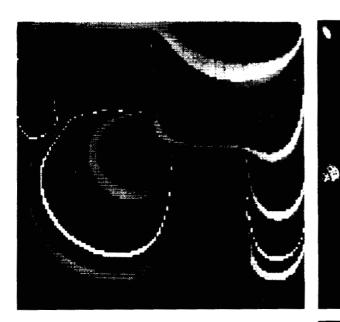

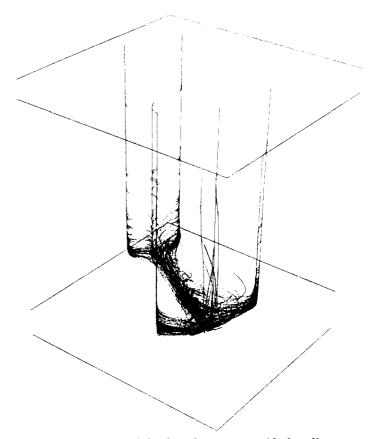

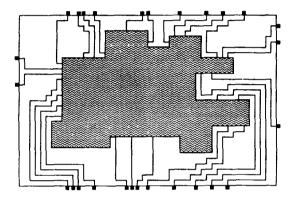

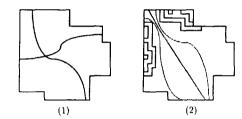

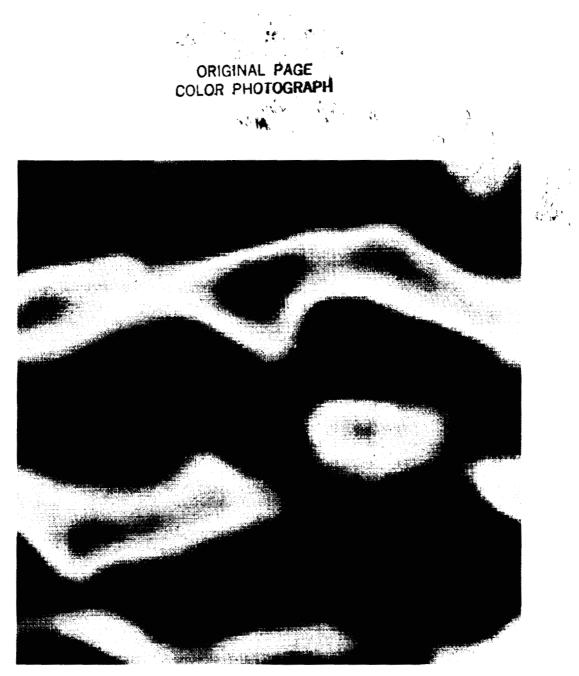

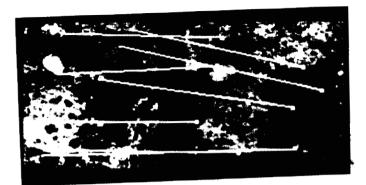

TOP LEFT: **Fluid Flow.** This picture shows the flow of water around rectangular objects in an open tank. Flow patterns are calculated using the Navier-Stokes equations on a 1,024-processor DAP 510.

TOP RIGHT: **Graphics.** "Mercury<sup>2</sup>" by H. C. Delany, M.I.T. Media Laboratory. This picture shows reflective spheres over an alien sunset. It was computed at 1024 x 1024 pixel resolution with 5 orders of reflection in 6 minutes using a 16,384-processor Connection Machine-2.

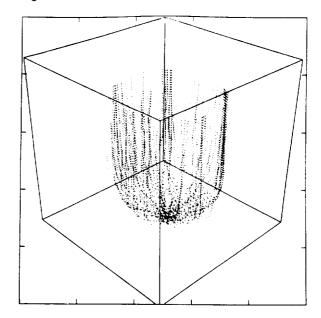

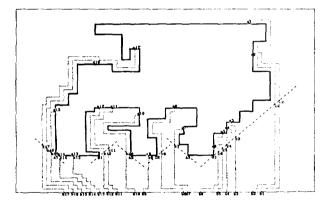

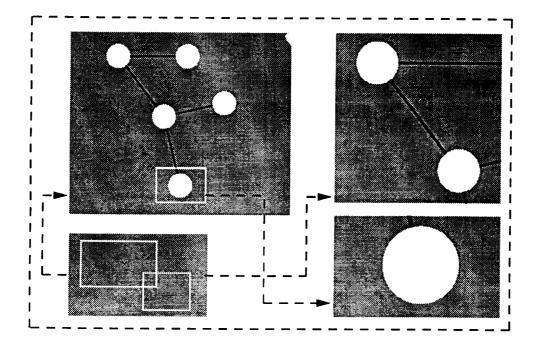

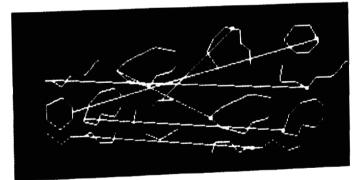

BOTTOM RIGHT: Stereo Image Matching by J. P. Strong and J. E. Dorband, NASA/ Goddard Space Flight Center. A three-dimensional perspective view of terrain in northeast India created by automatically fusing a pair of 512 x 512 stereo images in 50 seconds using NASA's 16,384-processor Massively Parallel Processor.

Cover design by ST Systems Corporation (STX) Graphics—Joan Sargies, Jane Foltz, and Barbara Gogan-Marinaro.

Proceedings

The 2nd Symposium on the

# **Frontiers of Massively Parallel Computations**

# The 2nd Symposium on the Frontiers of Massively Parallel Computation

Ronnie Mills, Editor ST Systems Corporation Lanham, Maryland

Proceedings of the second symposium sponsored by the Computer Society of the IEEE, NASA/Goddard Space Fight Center, IEEE National Capital Area Council, and George Mason University, and held at George Mason University Fairfax, Virginia October 10–12, 1988

> Supported by grants from Active Memory Technology, Digital Equipment Corporation, LORAL Defense Systems-Akron, Martin Marietta Aerospace, Science Applications Research, ST Systems Corporation, and Thinking Machines Corporation

Proceedings

The 2nd Symposium on the

## **Frontiers of Massively Parallel Computations**

Washington • Los Alamitos • Brussels • Tokyo

EEE Computer Society

The Institute of Electrical and Electronics Engineers, Inc.

The papers in this book comprise the proceedings of the meeting mentioned on the cover and title page. They reflect the authors' opinions and are published as presented and without change, in the interests of timely dissemination. Their inclusion in this publication does not necessarily constitute endorsement by the editors, the IEEE Computer Society Press, or The Institute of Electrical and Electronics Engineers, Inc.

Published by

IEEE Computer Society Press 1730 Massachusetts Avenue, N.W. Washington, D.C. 20036-1903

Copyright © 1988 by The Institute of Electrical and Electronics Engineers, Inc.

Copyright and Reprint Permissions: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limits of U.S. copyright law for private use of patrons those articles in this volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through the Copyright Clearance Center, 29 Congress Street, Salem, MA 01970. Instructors are permitted to photocopy isolated articles for noncommercial classroom use without fee. For other copying, reprint or republication permission, write to Director, Publishing Services, IEEE, 345 East 47th Street, New York, NY 10017. All rights reserved.

IEEE Computer Society Order Number 892 Library of Congress Number 88-82088 IEEE Catalog Number 88CH2649-2 ISBN 0-8186-0892-7 (paper) ISBN 0-8186-5892-4 (microfiche) ISBN 0-8186-8892-0 (case) SAN 264-620X

Additional copies may be ordered from:

IEEE Computer Society Order Department 10662 Los Vaqueros Circle Los Alamitos, CA 90728-2578

IEEE

IEEE Service Center 445 Hoes Lane P.O. Box 1331 Piscataway, NJ 08855-1331 IEEE Computer Society 13, Avenue de l'Aquilon B-1200 Brussels BELGIUM

IEEE Computer Society Ooshima Building 2-19-1 Minami Aoyama Minato-ku, Tokyo 107, JAPAN

THE INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS, INC.

#### PREFACE

Individuals interested in developing, using, and selling massively parallel computers converged on George Mason University in Fairfax, Virginia, on October 10 for Frontiers '88: The Second Symposium on the Frontiers of Massively Parallel Computation. Four-hundred-forty-five registrants (including five from foreign countries) attended the 3-day conference. Seventy-six universities, 81 corporations, and 37 Government organizations were represented.

There were 52 oral presentations and more than 60 poster presentations. There were also exhibits, a tutorial (attended by 129 registrants), and a panel discussion. The wide attendance and scope of the papers indicates that the field of massively parallel computing is attaining ever greater importance.

The sponsors and grantors look forward to continuing this series of symposia every other year at university sites in the greater Washington, DC, area. We hope these *Proceedings* give you some feel of the excitement that Frontiers '88 generated.

James R. Fischer NASA/Goddard Space Flight Center Conference Chairman David H. Schaefer George Mason University Program Chairman

#### A note about the exhibits:

Nine organizations mounted exhibits at the symposium. Four of these exhibits featured operational massively parallel systems:

Active Memory Technology had both their 1024 processor DAP 510 and their 4096 processor DAP 610 performing demonstrations.

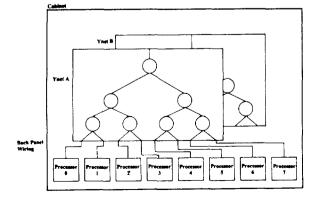

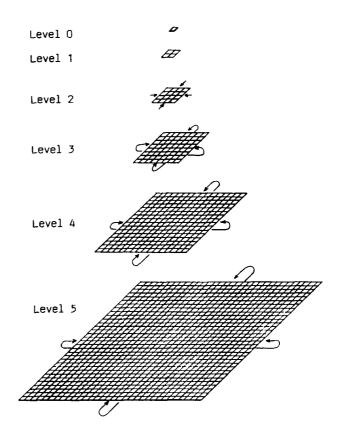

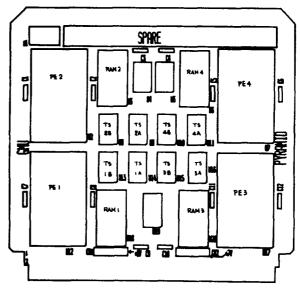

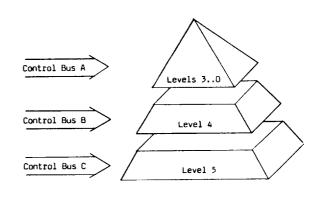

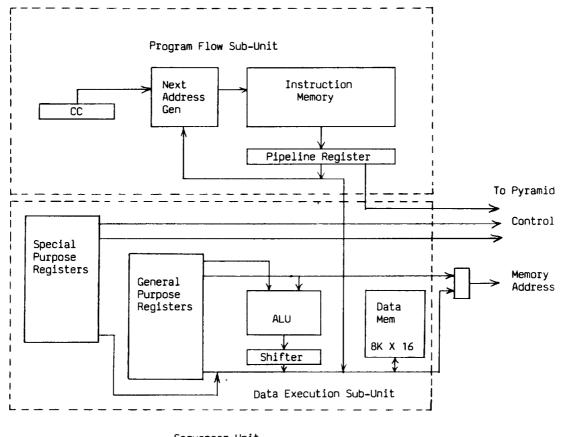

George Mason University demonstrated the student-built GAM 2 pyramid structure, containing 1365 processing elements on six levels, in their Advanced Computer Architecture Laboratory.

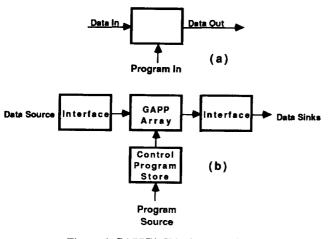

Martin Marietta Aerospace had a 40,000 processor Geometric Arithmetic Parallel Processor (GAPP) system in operation.

Thinking Machines Corporation had a 32,768 processor Connection Machine-2 running and demonstrating a variety of applications.

Other exhibitors were the Space Data and Computing Division at NASA/ Goddard Space Flight Center with an exhibit of Massively Parallel Processor (MPP) applications, LORAL Defense Systems-Akron with an exhibit on the MPP and the Associative Parallel Processor (ASPRO) computer, and the Cornell Theory Center with an exhibit of their Trollius Operating System. Two publisher exhibitors were John Wiley & Sons, Ltd., who advertised their new journal Concurrency: Practice and Experience, and the publishers of Supercomputing Review.

#### FOREWORD

This section was transcribed from welcoming remarks presented at the symposium.

#### Dr. George W. Johnson, President of George Mason University

George Mason University, in order to move quickly, has had to make certain bets. Two of those bets are represented by this conference. One bet was that we had always to anticipate what the cutting edge of developments in the fields that we chose to embark on would be. We decided that we would have to build a new engineering school, but that it would not be one built on the base of the physical sciences, but on the base of the information sciences. That was the first bet that we made.

The 2nd bet was that as a new university, we could not afford to be aloof and remote from our community, that we had to be what we call "interactive." We had to break down the walls between town and gown, the walls between marketplace and academy, and we have embarked aggressively on doing exactly that. You can see that the two come together in our School of Information Technology and Engineering, where the demarcation between business, government, and academy really is successfully blurred. And so this conference coming here at this particular time is really a signal event for George Mason University, and for that reason, among many others, you're very very welcome to the institution, and I'm glad to see you here. Thank you.

#### Dr. Lee Holcomb Director, Information Sciences and Human Factors Division NASA Headquarters

On behalf of NASA, I would like to welcome you all to this symposium—The 2nd Symposium on the Frontiers of Massively Parallel Computation. The NASA Office of Aeronautics and Space Technology has had a long history in parallel processing technology. Beginning in the early 1970's with the evaluation of the ILLIAC IV, we gained valuable knowledge on how to apply parallel processing power to aerospace computational requirements. In the late 1970's NASA was at the forefront of this important computing technology by funding the development of the world's first massively parallel processor, the MPP, which was originally intended for image processing applications. The MPP was designed, fabricated, and delivered to NASA in 1983, and an Applications Working Group was formed to encourage researchers from widely varied disciplines to conduct research on the MPP. That early investment is now bearing fruit, and is certainly evident, in part, by this symposium.

In the 1982 and 1983 time frame, the White House Office of Science and Technology Policy (OSTP) Federal Coordinating Committee on Science Engineering and Technology (FCCSET) established a subcommittee on supercomputing to coordinate the activities of the various federal government agencies. The early FCCSET committee focused on the concept of the federal government as a friendly buyer of supercomputers and on the concept of providing researchers access to supercomputers. Some of the programs that came out of this early activity were the Numerical Aerodynamic Simulation program at NASA/Ames, the NSF supercomputer centers that have been established throughout this country, and the Supercomputing Research Center in Maryland. More recently, the FCCSET committee has focused on the government being more than a friendly buyer. A recent OSTP report titled "A Research and Development Strategy for High Performance Computing," which was issued in November 1987, calls for government sponsorship of research in high performance computers, software technology and algorithms, networking, and basic research, and resources. Each government agency that is participating in FCCSET is preparing a response to this report. NASA has developed a high-performance computing initiative which includes 3 parallel computing testbeds, one for computational aerosciences, one for Earth & space sciences, and one for spaceborne applications. We intend to support algorithm and architecture research and advances in software for massively parallel systems, both operating systems and languages.

To date, this initiative has been worked primarily within the government through planning activities of the FCCSET committee. NASA now wants to solicit stronger involvement from industry and universities in this program. Dr. Paul Smith of my staff, who is here today, will be formulating an approach for forming a government, industry, and university planning team to advance this country's massively parallel computational capability. Dr. Smith will be present throughout this conference, and we solicit your views on how best to form this partnership. At the hearings on the National Supercomputer Network in September 1988, Senator Albert Gore, challenged the government to strengthen its ties with academia and industry. This conference provides one forum to begin forming a partnership of federal, academic and industrial researchers in this important frontier. I'm happy to welcome you to this symposium and hope that you will find it stimulating and productive.

#### ACKNOWLEDGEMENTS

#### Frontiers '88 could not have taken place without the contributions of many people including:

#### **Technical Meeting Committee** -

James Fischer (Conference Chair) NASA/Goddard Space Flight Center

James Tilton (Finance Chair) NASA/Goddard Space Flight Center

David Schaefer (Program Chair) George Mason University

Ronnie Mills (*Publications Chair*) S.T. Systems Corporation Pearl Wang (Tutorials Chair) George Mason University

Mark Stevens (*Publicity Chair*) S.T. Systems Corporation

Samuel Earp (Exhibition Chair) George Mason University

Barbara Framer (Local Arrangements Chair) George Mason University

#### **Representatives of Cosponsors and Grantors**

Ai C. Fang NASA Headquarters

Anne Marie Kelly Magdelene Johnson Denise Felix IEEE Computer Society

Thomas Doeppner IEEE National Capital Area Council

Lydia Walls Nancy Joyner George Mason University

Bruce Alper Kevin Linck Active Memory Technology, Inc. Jonathan Harris Digital Equipment Corporation

Alan Hinkle LORAL Defense Systems—Akron

Wade Pemberton Eugene Cloud Ron Sartain Martin Marietta Aerospace

Ron Estes S.T. Systems Corporation

Marvin Denicoff Carol Bee-Latty Thinking Machines Corporation

#### Working Program Committee -

Prof. David Schaefer George Mason University

Prof. Marvin Denicoff Thinking Machines Corporation

Dr. John Dorband NASA/Goddard Space Flight Center

Prof. Michael Rice George Mason University Dr. James Strong NASA/Goddard Space Flight Center

Dr. James Tilton NASA/Goddard Space Flight Center

Prof. Pearl Wang George Mason University

#### Steering Committee \_

Carol Bee-Latty Thinking Machines Corporation

James Fischer NASA/Goddard Space Flight Center

Chester Grosch Old Dominion University R. Michael Hord MRJ, Inc.

Michael Rice George Mason University

#### Program Committee \_\_\_\_

Prof. David Schaefer George Mason University

Dr. Ray Arnold NASA Headquarters

Dr. Ken Batcher LORAL Defense Systems-Akron

Dr. Jack Dongarra Argonne National Laboratory

Prof. Michael Duff University College, London

Dr. Milton Halem NASA/Goddard Space Flight Center

Dr. James Hardy Whitney/Demos Productions

Prof. Dennis Parkinson Active Memory Technology Massachusetts Institute of Technology

Prof. John Reif Duke University

Prof. Tomaso Poggio

Prof. Anthony Reeves University of Illinois

Prof. Azriel Rosenfeld University of Maryland

Dr. Paul Schneck Supercomputing Research Center

Dr. Steven Squires DARPA

Dr. Guy Steele Thinking Machines Corporation

Prof. Leonard Uhr University of Wisconsin

#### **Tutorial Lecturers**

Prof. Dennis Parkinson Active Memory Technology, Inc. Queen Mary College

Prof. David Schaefer George Mason University Prof. Pearl Wang George Mason University

Dr. John Dorband NASA/Goddard Space Flight Center

#### Invited Speakers \_\_\_\_\_

Dr. Kenneth Wilson Ohio State University

Gary Demos Whitney/Demos Productions Prof. Azriel Rosenfeld University of Maryland

Dr. Guy Steele Thinking Machines Corporation

#### **Session Chairs**

R. Michael Hord MRJ, Inc.

Dr. James Tilton NASA/Goddard Space Flight Center

Dr. James Strong NASA/Goddard Space Flight Center

Dr. Samuel Earp George Mason University

Dr. Michael Rice George Mason University

Jonathan Harris Digital Equipment Corporation Prof. Pearl Wang George Mason University

Prof. Joseph 'Ja 'Ja University of Maryland

Prof. H.J. Siegel Purdue University

Prof. Chester Grosch Old Dominion University

Dr. John Dorband NASA/Goddard Space Flight Center

Prof. Marvin Denicoff Thinking Machines Corporation

Special thanks to Maxine Schaefer for developing the database of abstract submissions, Millie Brice and Towanda Plater at NASA/Goddard for handling the numerous large mailings, Michele Braithwaite at George Mason University and Jim Elliott at NASA/Goddard for supporting publicity efforts, and the George Mason University student chapter of the IEEE for supporting the exhibition and audio visual needs of the conference.

### **CONTENTS**

| Preface<br>Foreword<br>Acknowledgements                                                                                                                                                                                         | v<br>vii<br>ix |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| PANEL DISCUSSION                                                                                                                                                                                                                | XXV            |

| INVITED PRESENTATIONS                                                                                                                                                                                                           |                |

| Languages for Massively Parallel Computers<br>Guy L. Steele, Jr., Thinking Machines Corporation                                                                                                                                 | 3              |

| Generating Movie-Quality Animated Graphics With Massively Parallel Computers<br>Gary Demos, Whitney–Demos Productions                                                                                                           | 15             |

| The Impact of Massively Parallel Computers on Image Processing<br>Azriel Rosenfeld, University of Maryland                                                                                                                      | 21             |

| SECTION I: ALGORITHMS<br>Part 1: Oral Presentations                                                                                                                                                                             |                |

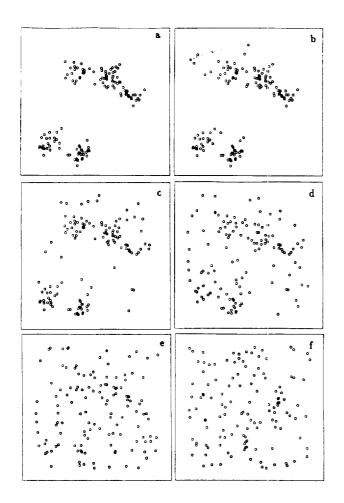

| How To Cluster in Parallel With Neural Networks<br>Behzad Kamgar-Parsi, University of Maryland<br>J. A. Gualtieri, NASA GSFC<br>Judy E. Devaney, Science Applications Research<br>Behrooz Kamgar-Parsi, George Mason University | 31             |

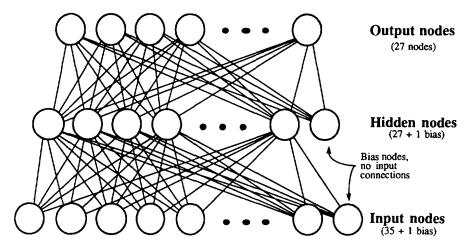

| Modeling Neural Networks on the MPP<br>Joe Hicklin and<br>Howard Demuth, University of Idaho                                                                                                                                    | 39             |

| Artificial Neural Network on a SIMD Architecture<br>Joe R. Brown,<br>Melissa M. Garber, and<br>Steven F. Venable, Martin Marietta Electronic Systems                                                                            | 43             |

| Characterizing the Error Function of a Neural Network<br>Barbara Moore and<br>Marcelo Fogaca, MIT<br>Alan Kramer, University of California, Berkeley                                                                            | 49             |

| The Impact of Rent's Rule on Massive Parallelism<br>P. J. Koopman and<br>D. P. Siewiorek, Carnegie Mellon University                                                                                                            | 59             |

| xiii BAGE X II INTENTIONALL                                                                                                                                                                                                     | t BLANK        |

| Overview and Extensions of a System for Routing Directed Graphs on SIMD Architectures<br>Sherryl Tomboulian, NASA Langley Research Center | 63  |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| An Analysis of Disjoint Path Properties in Data Manipulator Networks                                                                      | 69  |

| Wayne G. Nation and                                                                                                                       |     |

| Howard Jay Siegel, Purdue University                                                                                                      |     |

| Data Structures for Associative Supercomputers                                                                                            | 77  |

| J. L. Potter, Kent State University                                                                                                       |     |

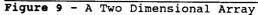

| Parallel Implementations of the Simplex Algorithm                                                                                         | 85  |

| Richard Marciano and                                                                                                                      |     |

| Teodor Rus, University of Iowa                                                                                                            |     |

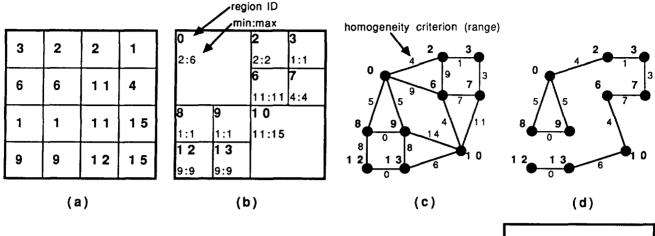

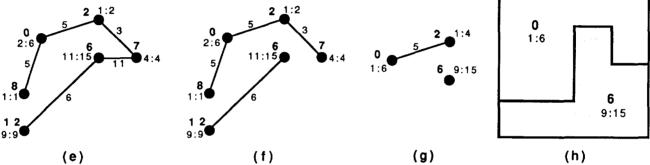

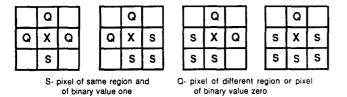

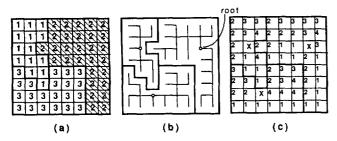

| Region Growing on a Highly Parallel Mesh-Connected SIMD Computer                                                                          | 93  |

| Marc Willebeek-LeMair, Cornell University                                                                                                 |     |

| Anthony P. Reeves, University of Illinois at Urbana-Champaign                                                                             |     |

| Hypercube Algorithms Suitable for Image Understanding in Uncertain Environments                                                           | 101 |

| T. L. Huntsberger and                                                                                                                     |     |

| A. Sengupta, University of South Carolina                                                                                                 |     |

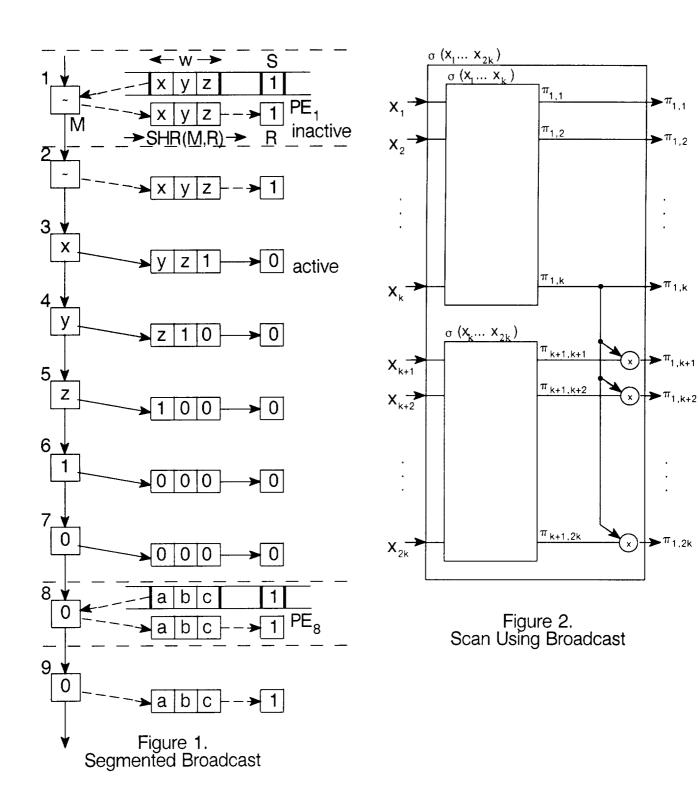

| Efficient Scan Operators for Bit-Serial Processor Arrays                                                                                  | 105 |

| C. M. Fiduccia and                                                                                                                        |     |

| R. M. Mattheyses, General Electric R & D Center                                                                                           |     |

| R. E. Stearns, SUNY at Albany                                                                                                             |     |

| SECTION I: ALGORITHMS                                                                                                                     |     |

| Part 2: Poster Presentations                                                                                                              |     |

|                                                                                                                                           |     |

| An Efficient Method for the Representation and Transmission of Message Patterns   | 115 |

|-----------------------------------------------------------------------------------|-----|

| P. J. Bernhard, Clemson University                                                |     |

| D. J. Rosenkrantz, SUNY at Albany                                                 |     |

| Minimum Spanning Tree on the HMESH Architecture                                   | 121 |

| R. V. Boppana and                                                                 |     |

| C. S. Raghavendra, University of Southern California                              |     |

| Optimal Mesh Algorithms for VLSI Routing                                          | 125 |

| Shing-Chong Chang and                                                             |     |

| Joseph JáJá, University of Maryland                                               |     |

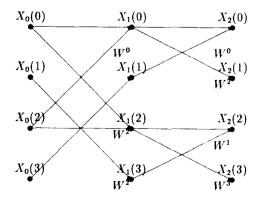

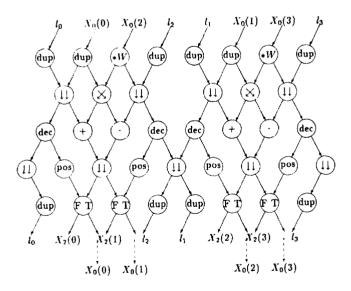

| A Uniform and Reconfigurable Framework for the Multidimensional Fourier Transform | 129 |

| Ron Coleman and                                                                   |     |

| Michael Post, Polytechnic University                                              |     |

| Alan Waksman, Plex Systems Research, Inc.                                         |     |

|                                                                                   |     |

xiv

| <b>d ( )</b> , ; |  |

|------------------|--|

|------------------|--|

٠

----

| Parallel Algorithms for Interactive Manipulation of Digital Terrain Models<br>E. W. Davis,<br>D. F. McAllister, and<br>V. Nagaraj, North Carolina State University                                          | 133 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

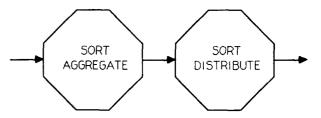

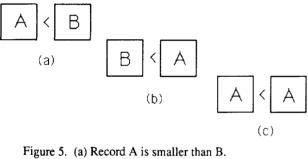

| Sort Computation<br>John E. Dorband, NASA GSFC                                                                                                                                                              | 137 |

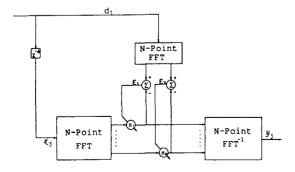

| Parallel Frequency Domain Adaptive Line Enhancer<br>Mohamed El-Sharkawy, Bucknell University<br>Maurice Aburdene, Naval Research Laboratory                                                                 | 143 |

| Optimal Geometric Algorithms for Digitized Pictures on an Optical Mesh<br>Mehrnoosh Mary Eshaghian and<br>V. K. Prasanna Kumar, University of Southern California                                           | 147 |

| An SIMD Parallel ε-Approximation Scheme for 0/1 Knapsack<br>Thomas E. Gerasch, SPARTA, Inc.                                                                                                                 | 151 |

| Fault Tolerant Message Routing on Large Parallel Systems<br>Jesse M. Gordon and<br>Quentin F. Stout, University of Michigan                                                                                 | 155 |

| Load Balancing for Massively-Parallel Soft-Real-Time Systems<br>Max Hailperin, Stanford University                                                                                                          | 159 |

| Efficient Algorithms for Massively Parallel Computers<br>I. Design of Stable Computational Systems Using Linear Systems Models<br>Harold M. Hastings, Hofstra University<br>Ivan Kadar, Grumman Corporation | 165 |

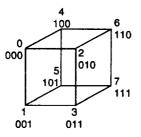

| Applied Geometric Algorithms on Boolean N_Cube Computers<br>Wen-Jing Hsu and<br>Xiaola Lin, Michigan State University<br>Kuan-Tsae Huang, IBM Corporation                                                   | 169 |

| A Fast Algorithm for Voronoi Diagram Calculation Based on Distance Doubling<br>David Izraelevitz, The Analytic Sciences Corporation                                                                         | 173 |

| Provably Good Parallel Algorithms for Channel Routing of Multiterminal Nets<br>Sridhar Krishnamurthy and<br>Joseph JáJá, University of Maryland                                                             | 177 |

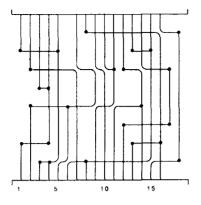

| Sparse Matrix Vector Multiplication on Polymorphic-Torus<br>Hungwen Li, Almaden Research Center<br>Ming-Cheng Sheng, IBM Corporation                                                                        | 181 |

----

| Almost Linear Speed-Up of Distributed Discrete Event Simulations<br>Boris D. Lubachevsky, Bell Laboratories                     | 187 |

|---------------------------------------------------------------------------------------------------------------------------------|-----|

| Dynamically Allocating Sets of Fine-Grained Processors to Running Computations<br>David Middleton, NASA Langley Research Center | 191 |

| Portable Parallel Algorithms for Geometric Problems                                                                             | 195 |

| Russ Miller, SUNY at Buffalo                                                                                                    |     |

| Quentin F. Stout, University of Michigan                                                                                        |     |

| Algorithms for Long Fast Fourier Transforms on a Connection Machine                                                             | 199 |

| J. P. Norris,                                                                                                                   |     |

| P. Hertz, and                                                                                                                   |     |

| K. S. Wood, Naval Research Laboratory                                                                                           |     |

| Paul Anderson, Planning Research Corporation                                                                                    |     |

| Simulating Neural Networks Using C*                                                                                             | 203 |

| Mark J. Norton, GE Aerospace Advanced Technology Laboratories                                                                   |     |

| ${\mathcal{D}}	ext{-}{	ext{Trees:}}$ A Class of Dense Regular Interconnection Topologies                                        | 207 |

| B. Ramkumar and                                                                                                                 |     |

| L. V. Kalé, University of Illinois at Urbana-Champaign                                                                          |     |

| A Model of Task Migration in Partitionable Parallel Processing Systems                                                          | 211 |

| Thomas Schwederski,                                                                                                             |     |

| Howard J. Siegel, and                                                                                                           |     |

| Thomas L. Casavant, Purdue University                                                                                           |     |

| Sparse Matrix Computations on an FFP Machine                                                                                    | 215 |

| B. T. Smith,                                                                                                                    |     |

| R. K. Singh, and                                                                                                                |     |

| G. A. Magó, University of North Carolina                                                                                        |     |

| A Parallel Algorithm for Finite Element Computation                                                                             | 219 |

| P. Subramaniam, Picker International                                                                                            |     |

| N. Ida, University of Akron                                                                                                     |     |

| The Fast Fourier Transform as a Test Case for a Systolic Data Flow Machine                                                      | 223 |

| Doron Tal,                                                                                                                      |     |

| John Comfort, and                                                                                                               |     |

| Maria Martinez, Florida International University                                                                                |     |

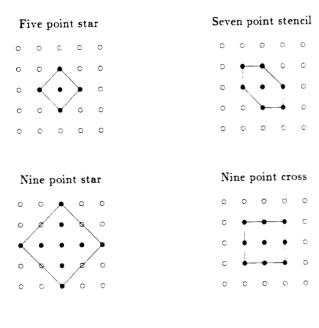

| Optimal Tilings for Iterative PDE Solvers                                                                                       | 227 |

| Anthony E. Terrano, Rutgers University                                                                                          |     |

| Parallel Algorithms for Direct Solution of Large Systems of Equations                                                           | 231 |

| Jian-She Wang and                                                                                                               |     |

| Nathan Ida, University of Akron                                                                                                 |     |

------

#### SECTION II: APPLICATIONS Part 1: Oral Presentations

| Stochastic Simulation of Charged Particle Transport on the Massively Parallel Processor<br>James A. Earl, University of Maryland                                                                                                                           | 237 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Suitability of Simulation of a Population of Chemical Polymers on the Massively Parallel<br>Processor                                                                                                                                                      | 241 |

| David Marshall Cohen, University of Iowa                                                                                                                                                                                                                   |     |

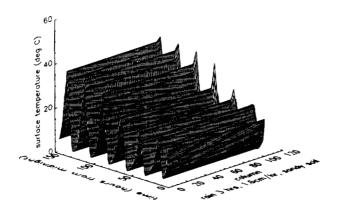

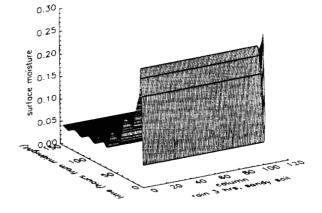

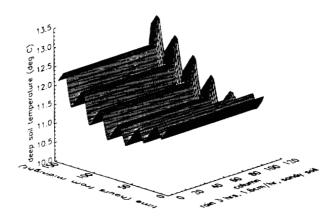

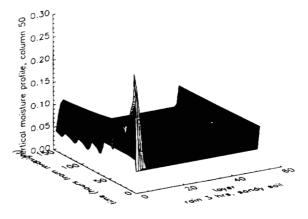

| Estimating Water Flow Through a Hillslope Using the Massively Parallel Processor<br>J. E. Devaney, Science Applications Research<br>P. J. Camillo and<br>B. J. Curray, NASA CSEC                                                                           | 249 |

| R. J. Gurney, NASA GSFC                                                                                                                                                                                                                                    |     |

| <ul> <li>Implementation of a 3D Thermal Analysis Code on the CM-2 Connection Machine Computer</li> <li>R. E. Cline, Jr., Sandia National Laboratories</li> <li>B. M. Boghosian and</li> <li>B. Nemnich, Thinking Machines Corporation</li> </ul>           | 257 |

| Fractal Graphics and Image Compression on a SIMD Processor<br>S. F. Reddaway and<br>A. Wilson, Active Memory Technology<br>A. Horn, Oxford University                                                                                                      | 265 |

| Application of Massively Parallel Machines to Molecular Dynamics Simulation of<br>Free Clusters<br>L. L. Boyer and<br>P. J. Edwardson, Naval Research Laboratory                                                                                           | 275 |

| An Overview of Current Connection Machine Applications at MRJ<br>R. Michael Hord, MRJ, Inc.                                                                                                                                                                | 279 |

| A High Performance Parallel Approach to Medical Imaging<br>G. Frieder, Syracuse University<br>O. Frieder, Bell Communications Research<br>M. R. Stytz, Air Force Institute of Technology                                                                   | 282 |

| Parallel Algorithm for the Solution of Nonlinear Poisson Equation of Semiconductor<br>Device Theory and Its Implementation on the MPP<br>J. P. Darling, The Johns Hopkins University Applied Physics Laboratory<br>I. D. Mayergoyz, University of Maryland | 289 |

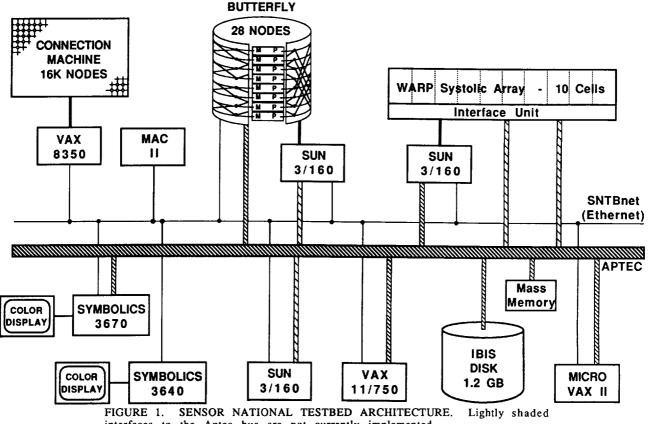

| DARPA Sensor National Testbed: Hardware and Software Architecture                                                                     | 295 |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| D. R. Guarino,                                                                                                                        |     |

| R. P. Kruger,                                                                                                                         |     |

| S. Sayre,                                                                                                                             |     |

| T. Sos,                                                                                                                               |     |

| C. J. Turner, and                                                                                                                     |     |

| C. L. Winter, Science Applications International Corporation                                                                          |     |

| Efficient Management of Sensory Data for an Autonomous Submersible Utilizing a                                                        |     |

| Parallel Processing Architecture                                                                                                      | 303 |

| Alhad Chande,                                                                                                                         |     |

| Sondra Shapiro, and                                                                                                                   |     |

| Art Acampora, Martin Marietta Aero & Naval Systems                                                                                    |     |

| SECTION II: APPLICATIONS<br>Part 2: Poster Presentations                                                                              |     |

| Simulations of Conposit, a Supra-Connectionist Architecture for Commonsense Reasoning<br>John A. Barnden, New Mexico State University | 311 |

| Massively Parallel Computing Applied to the One-Dimensional Bin Packing Problem<br>Judith O. Berkey, George Mason University          | 317 |

| C. C. M. J. B. Alexantelian Con Demonstration to the structure                                                                        | 321 |

| Surface Modeling Algorithm for Pyramid Architectures                                                                                  | 321 |

| D. Britton, George Mason University and Trident Systems, Inc.                                                                         |     |

| A Homogeneous Computational Model for Spatial Inference on Massively-Parallel                                                         |     |

| Architectures                                                                                                                         | 323 |

| Mark J. Carlotto, The Analytic Sciences Corporation                                                                                   |     |

| Scan Line Graphics Generation on the Massively Parallel Processor                                                                     | 327 |

| John E. Dorband, NASA CSFC                                                                                                            |     |

|                                                                                                                                       | 001 |

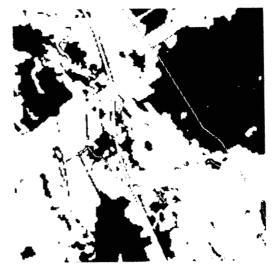

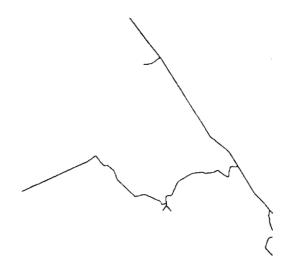

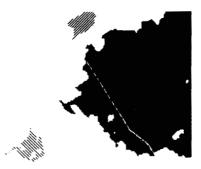

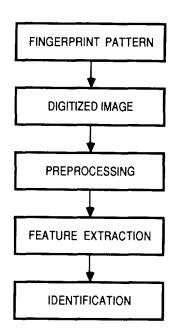

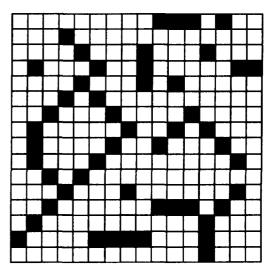

| Fingerprint Identification on a Massively Parallel Architecture                                                                       | 331 |

| T. R. Gowrishankar, George Mason University                                                                                           |     |

| Gray Scale Adjustment Algorithms on SIMD Architectures                                                                                | 335 |

|                                                                                                                                       |     |

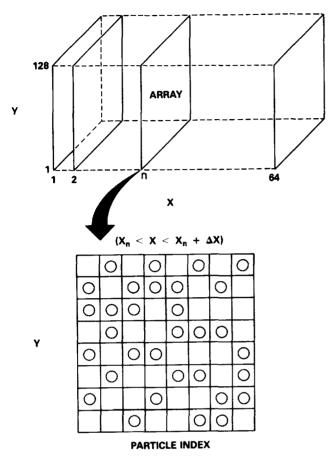

A Parallel Particle-In-Cell Model for the Massively Parallel Processor 339 C. S. Lin, A. L. Thring, and J. Koga, Southwest Research Institute

Christopher Lee Kuszmaul, MRJ, Inc.

| Parallel Algorithm for Determining Motion Vectors in Ice Floe Images by Matching<br>Edge Features<br>M. Manohar,    | 343 |

|---------------------------------------------------------------------------------------------------------------------|-----|

| H. K. Ramapriyan, and<br>J. P. Strong, NASA GSFC                                                                    |     |

| Symbolic Solution of Simultaneous Linear Algebraic Equations via Parallel                                           |     |

| Numerical Computing                                                                                                 | 349 |

| I. D. Mayergoyz and<br>F. P. Emad, University of Maryland                                                           |     |

| Parallel Implementation Considerations for a Class of Signal Processing Algorithms<br>Nidal M. Sammur and           | 353 |

| Martin T. Hagan, Oklahoma State University                                                                          |     |

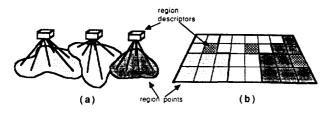

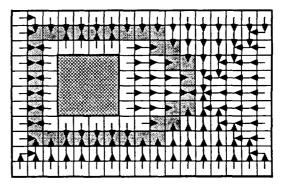

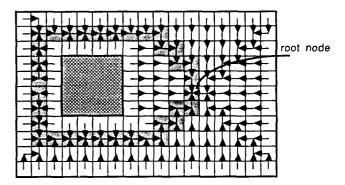

| Image Segmentation by Iterative Parallel Region Growing With Applications to Data<br>Compression and Image Analysis | 357 |

| James C. Tilton, NASA GSFC                                                                                          |     |

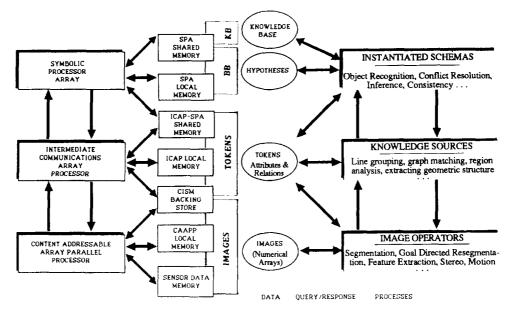

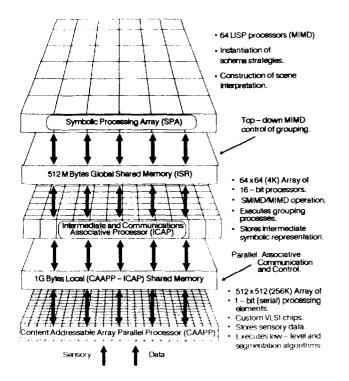

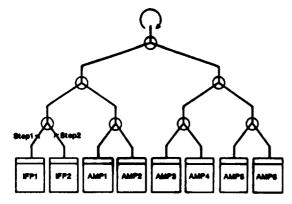

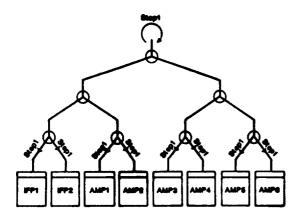

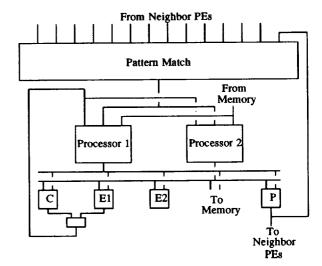

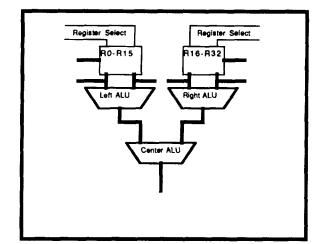

| The Performance of the Image Understanding Architecture on the DARPA Integrated<br>Image Understanding Benchmark    | 361 |

| Charles C. Weems, University of Massachusetts                                                                       |     |

| SECTION III: ARCHITECTURES<br>Part 1: Oral Presentations                                                            |     |

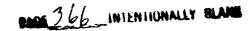

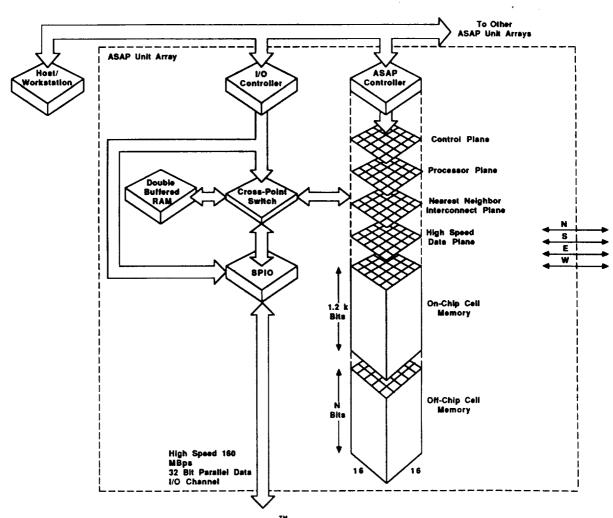

| The Martin Marietta Advanced Systolic Array Processor<br>A. Haug and                                                | 367 |

| R. Graybill, Martin Marietta Aero & Naval Systems                                                                   |     |

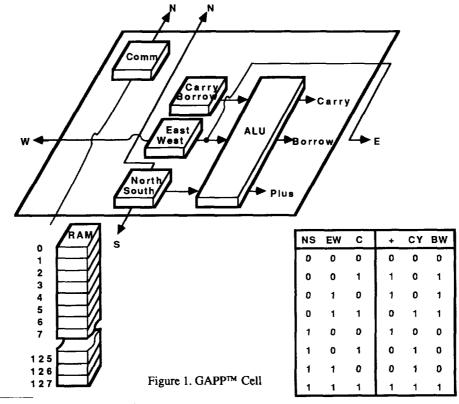

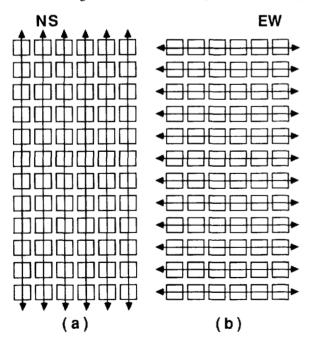

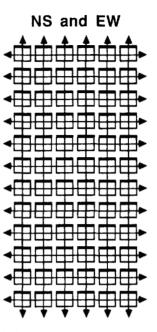

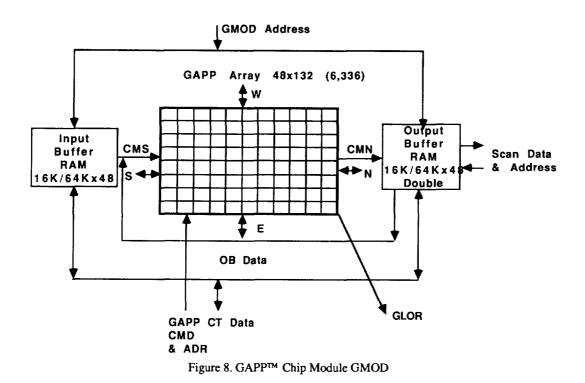

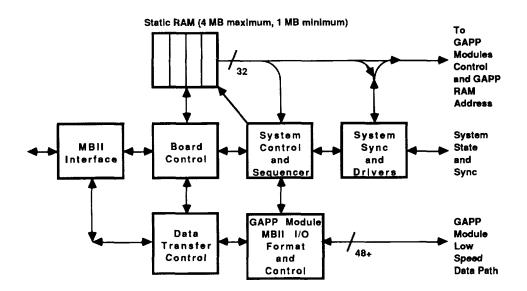

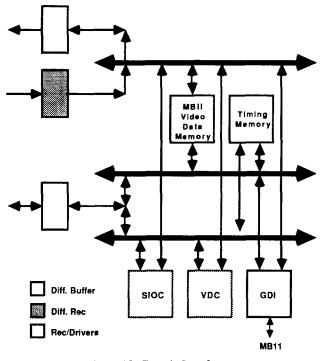

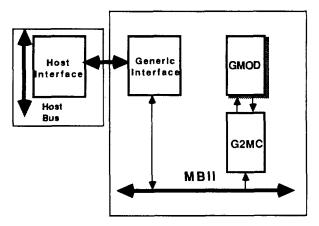

| The Geometric Arithmetic Parallel Processor                                                                         | 373 |

| Eugene L. Cloud, Martin Marietta Electronic Systems                                                                 |     |

| NAD (N. ALLI Dressen) The Crust Communication                                                                       | 000 |

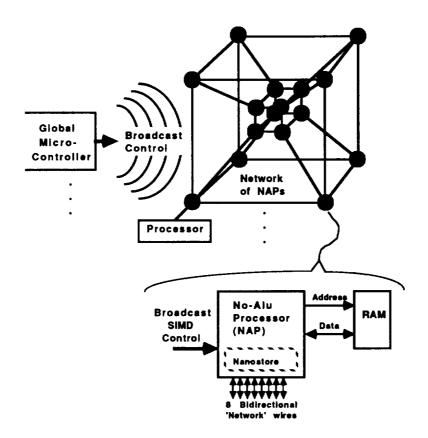

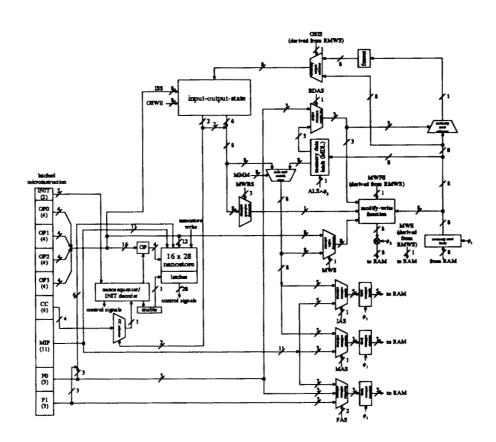

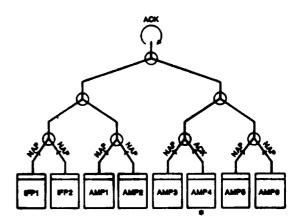

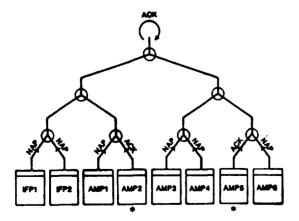

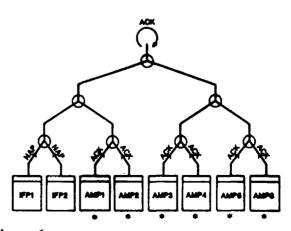

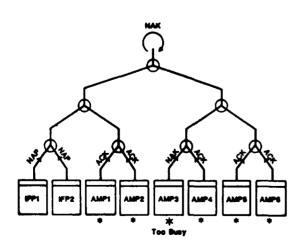

NAP (No ALU Processor): The Great Communicator

383

Jeff Fried, MIT and GTE Laboratories

383

Bradley C. Kuszmaul, MIT and Thinking Machines Corporation

391

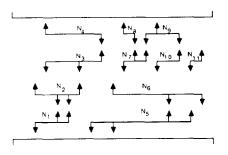

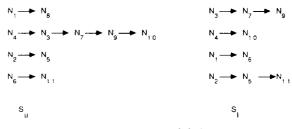

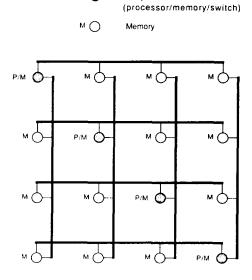

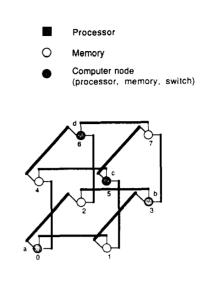

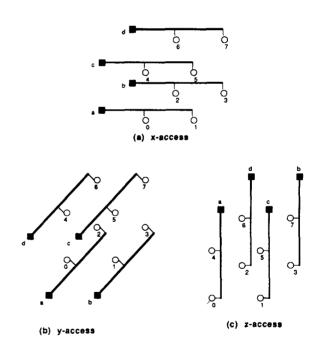

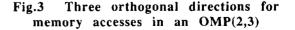

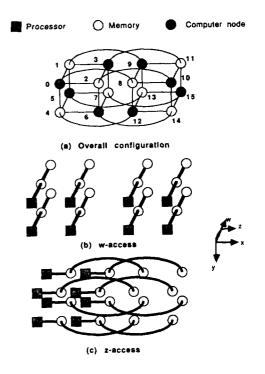

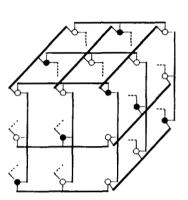

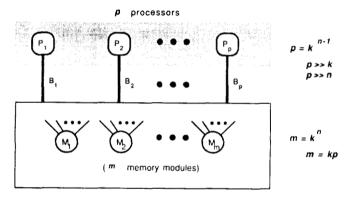

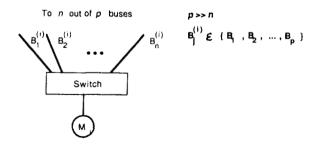

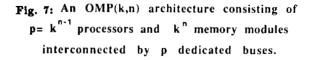

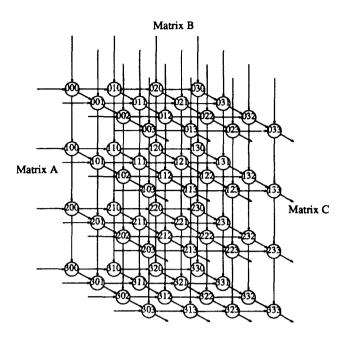

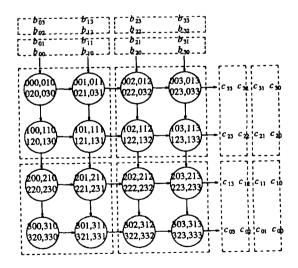

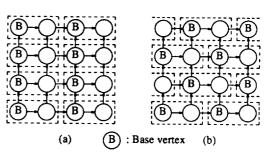

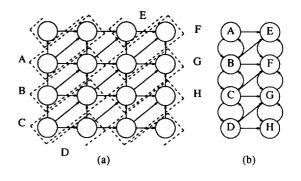

Generalization of Orthogonal Multiprocessor for Massively Parallel Computation

391

Kai Hwang and

391

Dongseung Kim, Uriversity of Southern California

| BLITZEN: A Highly Integrated Massively Parallel Machine                                                                                            | 399 |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| D. W. Blevins, The Microelectronics Center of North Carolina                                                                                       |     |

| E. W. Davis, North Carolina State University                                                                                                       |     |

| R. A. Heaton, The Microelectronics Center of North Carolina                                                                                        |     |

| J. H. Reif, Duke University                                                                                                                        |     |

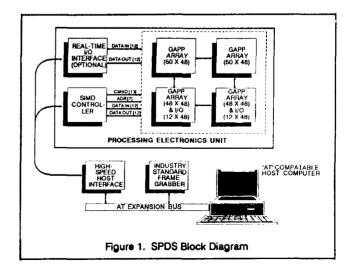

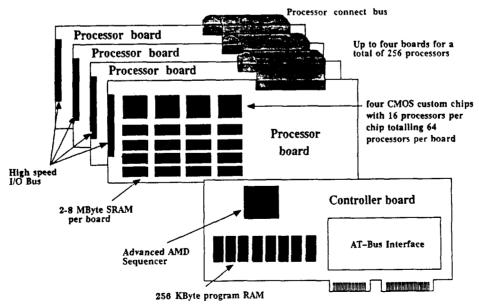

| Massively Parallel Computing System for Research and Development Applications                                                                      | 407 |

| W. Keith Johnson, Amber Engineering, Inc.                                                                                                          |     |

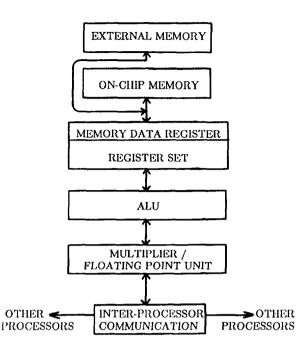

| The APx Accelerator                                                                                                                                | 413 |

| E. Abreu,                                                                                                                                          |     |

| D. Jenkins,                                                                                                                                        |     |

| M. Hervin, and                                                                                                                                     |     |

| D. Evans, Visionary Systems, Inc.                                                                                                                  |     |

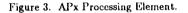

| The Design of a Bit-Serial Coprocessor to Perform Multiplication and Division on a Massively                                                       |     |

| Parallel Architecture                                                                                                                              | 419 |

| Robert E. Morley, Jr.,                                                                                                                             |     |

| Gary E. Christensen,                                                                                                                               |     |

| Thomas J. Sullivan, and                                                                                                                            |     |

| Orly Kamin, Washington University                                                                                                                  |     |

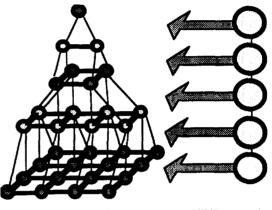

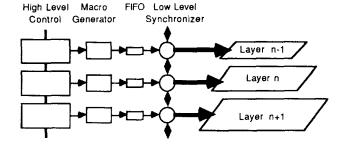

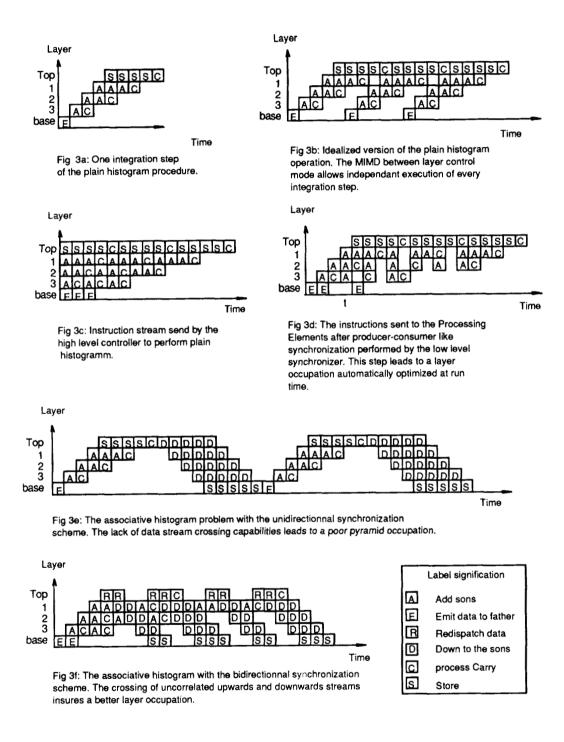

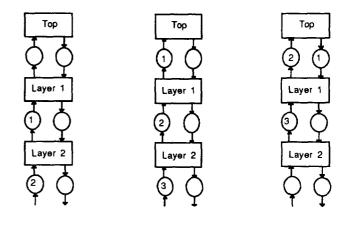

| Controlling and Programming the Sphinx Multi-SIMD Pyramid Machine<br>J. Méhat, Université Paris VIII                                               | 423 |

| A. Mérigot, Institut d'Electronique Fondamentale, Université Paris Sud                                                                             |     |

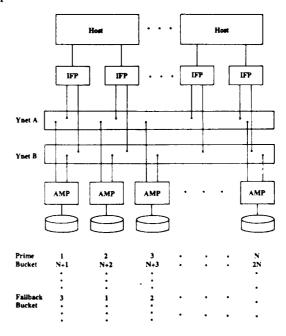

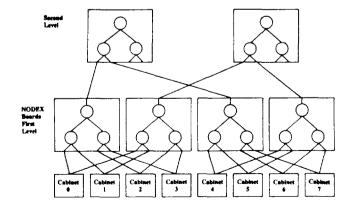

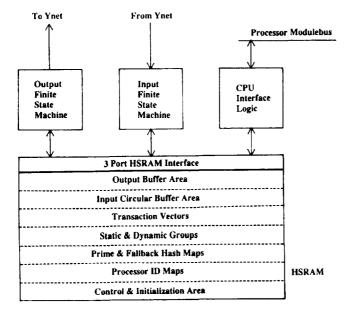

| The Ynet: An Interconnect Structure for a Highly Concurrent Data Base Computer System                                                              | 429 |

| Philip M. Neches, Teradata Corporation                                                                                                             |     |

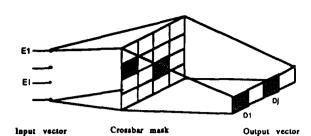

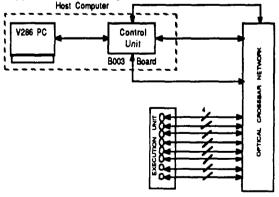

| A Reconfigurable Optical Interconnection Network for Highly Parallel Architecture<br>X. Thibault,                                                  | 437 |

| D. Comte, and                                                                                                                                      |     |

| P. Siron, O.N.E.R.A. /C.E.R.T.                                                                                                                     |     |

| The GAM II Pyramid                                                                                                                                 | 443 |

| Zahi Abuhamdeh, George Mason University                                                                                                            |     |

| SECTION III: ARCHITECTURES                                                                                                                         |     |

| Part 2: Poster Presentations                                                                                                                       |     |

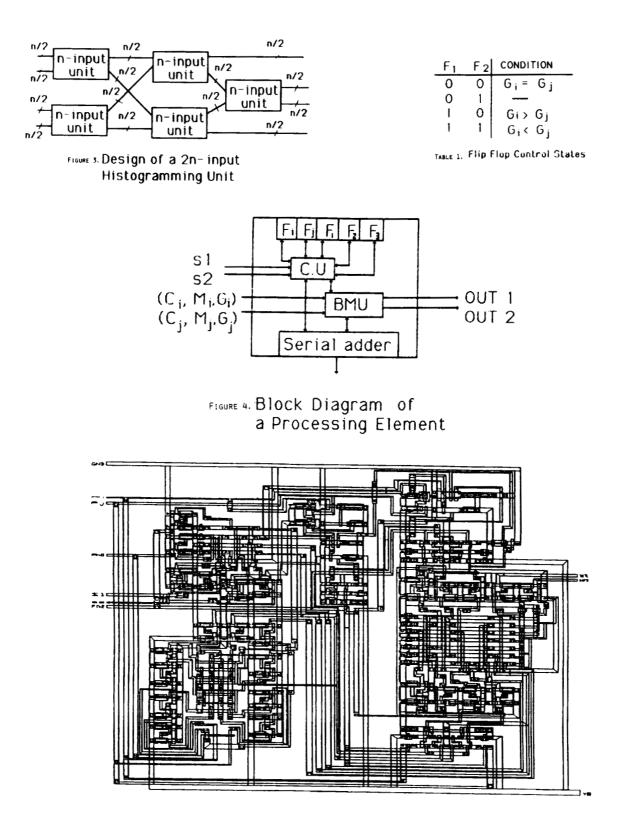

| Parallel and Pipelined VLSI Design for the Histogramming Operation<br>M. Abdelguerfi, University of Detroit<br>A. K. Sood, George Mason University | 451 |

S. Khalaf, Wayne State University

· \_\_\_\_\_

-

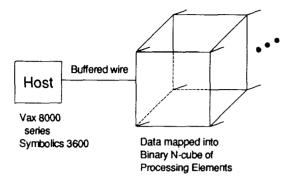

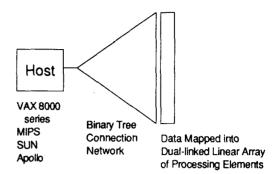

| The Function of a Connection Network Between Host and Processing Elements in<br>Massively Parallel Computer Systems | 455 |

|---------------------------------------------------------------------------------------------------------------------|-----|

| Timothy Bridges, Indiana University and Massively Parallel Arch. Corp.                                              |     |

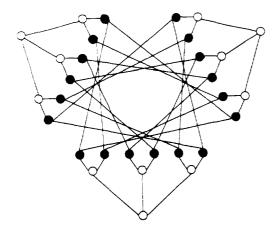

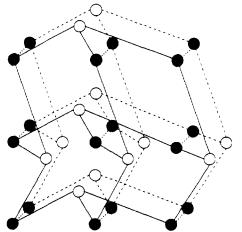

| Dense Symmetric Networks From Linear Groups                                                                         | 459 |

| L. Campbell and                                                                                                     |     |

| M. Fellows, University of Idaho                                                                                     |     |

| G. Carlsson, Princeton University                                                                                   |     |

| V. Faber and                                                                                                        |     |

| J. Moore, Los Alamos National Laboratories                                                                          |     |

| M. Langston, Washington State University                                                                            |     |

| A. Mullhaupt, University of New Mexico                                                                              |     |

| H. Sexton, Lucid, Inc.                                                                                              |     |

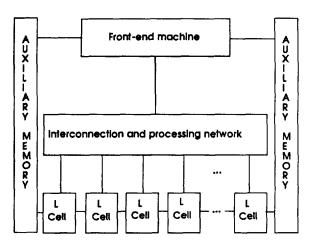

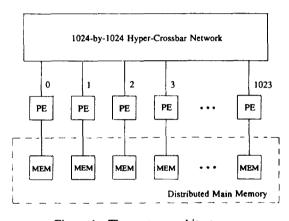

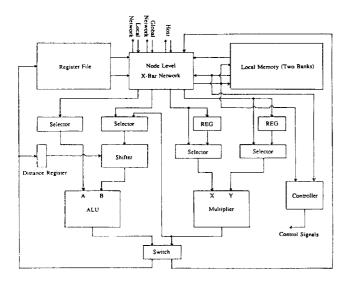

| A Massively Parallel Processing System Based on a Hyper-Crossbar Network                                            | 463 |

| C. Chin and                                                                                                         |     |

| W. Lin, General Electric Company                                                                                    |     |

| Hypercomputers: Design and Architecture                                                                             | 467 |

| Ron Coleman and                                                                                                     |     |

| Michael Post, Polytechnic University                                                                                |     |

| Alan Waksman, Plex Systems Research, Inc.                                                                           |     |

| A Reduced Diameter Interconnection Network                                                                          | 471 |

| K. Efe, University of Southwestern Louisiana                                                                        |     |

| P. Blackwell,                                                                                                       |     |

| T. Shiau, and                                                                                                       |     |

| W. Slough, University of Missouri–Columbia                                                                          |     |

| The PSMH: A Pyramid of Fractional Dimension                                                                         | 475 |

| Jean Hecquard and                                                                                                   |     |

| Raj Acharya, SUNY at Buffalo                                                                                        |     |

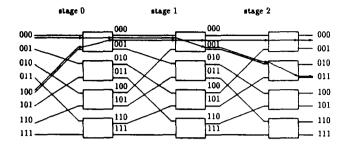

| Routing Linear Permutations Through the Omega Network in Two Passes                                                 | 479 |

| John Keohane and                                                                                                    |     |

| Richard E. Stearns, SUNY at Albany                                                                                  |     |

| Performance of the ASP on the DARPA Architecture Benchmark                                                          | 483 |

| A. Krikelis and                                                                                                     |     |

| R. M. Lea, Aspex Microsystems Ltd.                                                                                  |     |

| Simulation and Analysis of Enhanced Switch Architectures for Interconnection Networks                               |     |

| in Massively Parallel Shared Memory Machines                                                                        | 487 |

| Yue-sheng Liu and                                                                                                   |     |

| Susan Dickey, New York University                                                                                   |     |

| Fault Tolerance of Allocation Schemes in Massively Parallel Computers                                               | 491 |

| Marilynn Livingston, Southern Illinois University                                                                   |     |

| Quentin F. Stout, University of Michigan                                                                            |     |

----

| R. K. Mahadewa and       C. C. Carroll, University of Alabama         Regular Processor Arrays       499         Allen D. Malony, University of Illinois at Urbana-Champaign       503         Interconnection Networks for Fifth-Generation Computers       503         Bernard L. Meneze, University of Maryland       507         Reliability Considerations in Large-Scale Computing Systems       507         W. Najjar, Information Sciences Institute       3.1. Gaudiat, University of Southern California         Design Considerations for a Pyramidal Cellular Logic Processor       511         Joseph J. Pfeiffer, Jr., New Mexico State University       515         Microcode Generation for the Control of a Massively Parallel Computer       515         Tom Philips,       Bret Michael, and       2ahi Abuhamdeh, George Mason University         A Multi-Layered G-Network for Massively Parallel Computation       519       519         Terest Hayner Rice, East Tennesse State University       514       314         A Sequenced Hypercube Topology for a Massively-Parallel Database Computer       521       325         Moral Li, Florida International University       525       337       337         An Architecture for the Implementation of a Parallel Marker Propagation System       525       525         Howard Schneider, Cité de la Santé de Laval Hospital       537       537                                                                                                                                                          | Computer Architecture for Intelligent, Real-Time, Numeric and Symbolic Processing | 495 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|

| Regular Processor Arrays       499         Alten D. Malony, University of Illinois at Urbana-Champaign       503         Interconnection Networks for Fifth-Generation Computers       503         Bernard L. Menezes, University of Maryland       507         Reliability Considerations in Large-Scale Computing Systems       507         W. Najar, Information Sciences Institute       JL. Gaudiot, University of Southern California       501         Design Considerations for a Pyramidal Cellular Logic Processor       511         Joseph J. Pfeiffer, Jr., New Mexico State University       515         Microcode Generation for the Control of a Massively Parallel Computer       515         Tom Phillips,       Ber Michael, and       Zahi Abuhamdeh, George Mason University         A Multi-Layered G-Network for Massively Parallel Computation       519         Teresa Haynes Rice, East Tennessee State University       521         A Sequenced Hypercube Topology for a Massively-Parallel Database Computer       521         Naphtali Rishe,       507       531         Dorn Tal, and       Qiang Li, Florida International University       525         An Architecture for the Implementation of a Parallel Marker Propagation System       525         Howard Schneider, Cité de la Santé de Laval Hospital       531         LIN-Tree: A Fault-Tolerant Tree Architecture       537                                                                                                                                                             | R. K. Mahadevan and                                                               |     |

| Allen D. Malony, University of Illinois at Urbana–Champaign         Interconnection Networks for Fifth-Generation Computers       503         Bernard L. Menezes, University of Maryland       507         Reliability Considerations in Large-Scale Computing Systems       507         W. Najjar, Information Sciences Institute       511         J.L. Gaudiot, University of Southern California       501         Design Considerations for a Pyramidal Cellular Logic Processor       511         Joseph J. Pfeiffer, Jr., New Mexico State University       515         Microcode Generation for the Control of a Massively Parallel Computer       515         Tom Phillips,       Bere Michael, and         Zaki Abuhamdeh, George Mason University       514         A Multi-Layered G-Network for Massively Parallel Computation       519         Tereso Haynes Rice, East Tennessee State University       521         Ratan K. Guha, University of Central Florida       521         Naphtali Rishe,       525         Doron Tal, and       526         Qiang Li, Florida International University       525         Howard Schneider, Cité de la Santé de Laval Hospital       525         LN-Tree: A Fault-Tolerant Tree Architecture       531         K. Y. Srinivasan, University of Toledo       537         M. H. Sunwoo and       J. K. Aggar                                                                                                                                                                                                               | C. C. Carroll, University of Alabama                                              |     |

| Interconnection Networks for Fifth-Generation Computers<br>Bernard L. Meneze, University of Maryland       503         Reliability Considerations in Large-Scale Computing Systems       507         W. Najier, Information Sciences Institute       5.1. Gaudiot, University of Southern California         Design Considerations for a Pyramidal Cellular Logic Processor<br>Joseph J. Pfeiffer, Jr., New Mexico State University       511         Microcode Generation for the Control of a Massively Parallel Computer<br>Tom Phillips,<br>Bret Michael, and<br>Zahi Abuhamdeh, George Mason University       519         A Multi-Layered G-Network for Massively Parallel Computation<br>Teresa Haynes Rice, East Tennesses State University<br>Ratan K. Guha, University of Central Florida       519         A Sequenced Hypercube Topology for a Massively-Parallel Database Computer<br>Naphtali Rishe,<br>Doron Tal, and<br>Qiang Li, Florida International University       521         An Architecture for the Implementation of a Parallel Marker Propagation System<br>Howard Schneider, Cité de la Sonté de Laval Hompital       525         LIN-Tree: A Fault-Tolerant Tree Architecture<br>X: Y. Srinivasan, University of Tokado<br>A. K. Sond, George Mason University       537         A Sliding Memory Plane Array Processor<br>M. H. Sunwoo and<br>J. K. Aggarwal, University of Colorado<br>C. Wu and<br>Wictor P. Nelson, Auburn University       545         Neurocomputing With Optical Pilepline Networks<br>Zhiwai Xu, Rutgers University       545 | Regular Processor Arrays                                                          | 499 |

| Bernard L. Mencese, University of Maryland       507         Bernard L. Mencese, University of Southern California       507         W. Najjar, Information Sciences Institute       51.L. Gaudiot, University of Southern California       507         Design Considerations for a Pyramidal Cellular Logic Processor       511         Joseph J. Pfeiffer, Jr., New Mexico State University       511         Microcode Generation for the Control of a Massively Parallel Computer       515         Tom Phillips,       Bert Michael, and         Zahi Abuhamdeh, George Mason University       519         A Multi-Layered G-Network for Massively Parallel Computation       519         Teresa Haynes Rice, East Tennessee State University       521         A Sequenced Hypercube Topology for a Massively-Parallel Database Computer       521         Naphtali Rishe,       Doron Tal, and         Qiang Li, Florida International University       525         An Architecture for the Implementation of a Parallel Marker Propagation System       525         Howard Schneider, Cité de la Santé de Laval Hospital       531         LIN-Tree: A Fault-Tolerant Tree Architecture       531         K. Y. Srinicasan, University of Tokao       537         M. H. Sunwoo and       J. K. Aggarwal, University of Colorado         J. K. Aggarwal, University of Colorado       C. Wu and                                                                                                                                                                            | Allen D. Malony, University of Illinois at Urbana–Champaign                       |     |

| Bernard L. Menezes, University of Maryland         Reliability Considerations in Large-Scale Computing Systems       507         W. Najar, Information Sciences Institute       JL. Gaudiot, University of Southern California         Design Considerations for a Pyramidal Cellular Logic Processor       511         Joseph J. Pfeiffer, Jr., New Mexico State University       515         Microcode Generation for the Control of a Massively Parallel Computer       515         Tom Phillips,       Bret Michael, and         Zahi Abuhamdeh, George Mason University       519         A Multi-Layered G-Network for Massively Parallel Computation       519         Teresa Haynes Rice, East Tennesses State University       521         A Sequenced Hypercube Topology for a Massively-Parallel Database Computer       521         Naphtali Rishe,       Doron Tal, and         Qiang Li, Florida International University       525         An Architecture for the Implementation of a Parallel Marker Propagation System       525         Howard Schneider, Cité de la Sonté de Laval Hospital       531         LN-Tree: A Fault-Tolerant Tree Architecture       531         K. Y. Siniveasan, University of Texas at Austin       537         M. H. Sunwoo and       J. K. Aggarwal, University of Colorado       543         C. Wu and       Vniversity of Colorado       544                                                                                                                                                                                | Interconnection Networks for Fifth-Generation Computers                           | 503 |

| W. Najjar, Information Sciences Institute       J. L. Gaudiot, University of Southern California         Design Considerations for a Pyramidal Cellular Logic Processor       511         Joseph J. Pfeiffer, Jr., New Mexico State University       515         Microcode Generation for the Control of a Massively Parallel Computer       515         Tom Phillips,       Bret Michael, and         Zahi Abuhamdeh, George Mason University       519         A Multi-Layered G-Network for Massively Parallel Computation       519         Teresa Haynes Rice, East Tennessee State University       514         A Sequenced Hypercube Topology for a Massively-Parallel Database Computer       521         Naphtait Rishe,       Doron Tal, and       Giang Li, Florida International University         An Architecture for the Implementation of a Parallel Marker Propagation System       525         Howard Schneider, Cité de la Santé de Laval Hospital       531         LN-Tree: A Fault-Tolerant Tree Architecture       531         K. Y. Srinivasan, University of Toledo       A. K. Sood, George Mason University         A Sliding Memory Plane Array Processor       537         M. H. Sunuco and       J. K. Aggarwal, University of Colorado         C. Wu and       Victor P. Nelson, Auburn University         Neurocomputing With Optical Pipeline Networks       545         Zhiuei Xu, Rutgers Uni                                                                                                                                                  |                                                                                   |     |

| W. Najjar, Information Sciences Institute       J. L. Gaudiot, University of Southern California         Design Considerations for a Pyramidal Cellular Logic Processor       511         Joseph J. Pfeiffer, Jr., New Mexico State University       515         Microcode Generation for the Control of a Massively Parallel Computer       515         Tom Phillips,       Bret Michael, and         Zahi Abuhamdeh, George Mason University       519         A Multi-Layered G-Network for Massively Parallel Computation       519         Teresa Haynes Rice, East Tennessee State University       514         A Sequenced Hypercube Topology for a Massively-Parallel Database Computer       521         Naphtait Rishe,       Doron Tal, and       Giang Li, Florida International University         An Architecture for the Implementation of a Parallel Marker Propagation System       525         Howard Schneider, Cité de la Santé de Laval Hospital       531         LN-Tree: A Fault-Tolerant Tree Architecture       531         K. Y. Srinivasan, University of Toledo       A. K. Sood, George Mason University         A Sliding Memory Plane Array Processor       537         M. H. Sunuco and       J. K. Aggarwal, University of Colorado         C. Wu and       Victor P. Nelson, Auburn University         Neurocomputing With Optical Pipeline Networks       545         Zhiuei Xu, Rutgers Uni                                                                                                                                                  | Reliability Considerations in Large-Scale Computing Systems                       | 507 |

| JL. Gaudiat, University of Southern California         Design Considerations for a Pyramidal Cellular Logic Processor       511         Joseph J. Pfeiffer, Jr., New Mexico State University       515         Microcode Generation for the Control of a Massively Parallel Computer       515         Tom Phillips,       Bret Michael, and         Zahi Abuhamdeh, George Mason University       519         A Multi-Layered G-Network for Massively Parallel Computation       519         Teresa Haynes Rice, East Tennessee State University       810         Ratan K. Guha, University of Central Florida       521         A Sequenced Hypercube Topology for a Massively-Parallel Database Computer       521         Naphtali Rishe,       Doron Tal, and         Qiang Li, Florida International University       525         An Architecture for the Implementation of a Parallel Marker Propagation System       525         Howard Schneider, Cité de la Santé de Laval Hospital       531         LN-Tree: A Fault-Tolerant Tree Architecture       531         K. Y. Srinioasan, University of Toledo       A. K. Sood, George Mason University         A Sliding Memory Plane Array Processor       537         M. H. Sunwoo and       J. K. Aggarwal, University of Texas at Austin         Study of the Generalized Multiple Bus-Connected Parallel Computer       541         Chia Jiu Wa                                                                                                                                                                     | -                                                                                 |     |

| Joseph J. Pfeiffer, Jr., New Mexico State University       515         Microcode Generation for the Control of a Massively Parallel Computer<br>Tom Phillips,<br>Bret Michael, and<br>Zahi Abuhamdeh, George Mason University       515         A Multi-Layered G-Network for Massively Parallel Computation<br>Teresa Haynes Rice, East Tennessee State University<br>Ratan K. Guha, University of Central Florida       519         A Sequenced Hypercube Topology for a Massively-Parallel Database Computer<br>Naphtali Rishe,<br>Doron Tal, and<br>Qiang Li, Florida International University       521         An Architecture for the Implementation of a Parallel Marker Propagation System<br>Howard Schneider, Cité de la Santé de Laval Hospital       525         LN-Tree: A Fault-Tolerant Tree Architecture<br>K. Y. Srinivasan, University of Toledo<br>A. K. Sood, George Mason University       531         A Sliding Memory Plane Array Processor<br>M. H. Sunwoo and<br>J. K. Aggarual, University of Texas at Austin       537         Study of the Generalized Multiple Bus-Connected Parallel Computer<br>Chia-Jiu Wang, University of Colorado<br>C. Wu and<br>Victor P. Nelson, Auburn University       541         Neurocomputing With Optical Pipeline Networks<br>Zhiwei Xu, Rugers University       545                                                                                                                                                                                                                                               |                                                                                   |     |

| Joseph J. Pfeiffer, Jr., New Mexico State University       515         Microcode Generation for the Control of a Massively Parallel Computer<br>Tom Phillips,<br>Bret Michael, and<br>Zahi Abuhamdeh, George Mason University       515         A Multi-Layered G-Network for Massively Parallel Computation<br>Teresa Haynes Rice, East Tennessee State University<br>Ratan K. Guha, University of Central Florida       519         A Sequenced Hypercube Topology for a Massively-Parallel Database Computer<br>Naphtali Rishe,<br>Doron Tal, and<br>Qiang Li, Florida International University       521         An Architecture for the Implementation of a Parallel Marker Propagation System<br>Howard Schneider, Cité de la Santé de Laval Hospital       525         LN-Tree: A Fault-Tolerant Tree Architecture<br>K. Y. Srinivasan, University of Toledo<br>A. K. Sood, George Mason University       531         A Sliding Memory Plane Array Processor<br>M. H. Sunwoo and<br>J. K. Aggarual, University of Texas at Austin       537         Study of the Generalized Multiple Bus-Connected Parallel Computer<br>Chia-Jiu Wang, University of Colorado<br>C. Wu and<br>Victor P. Nelson, Auburn University       541         Neurocomputing With Optical Pipeline Networks<br>Zhiwei Xu, Rugers University       545                                                                                                                                                                                                                                               | Design Considerations for a Pyramidal Cellular Logic Processor                    | 511 |

| Microcode Generation for the Control of a Massively Parallel Computer       515         Tom Phillips,       Bret Michael, and         Zahi Abuhamdeh, George Mason University       A Multi-Layered G-Network for Massively Parallel Computation       519         Teresa Haynes Rice, East Tennessee State University       Ratan K. Guha, University of Central Florida       519         A Sequenced Hypercube Topology for a Massively-Parallel Database Computer       521         Naphtali Rishe,       Doron Tal, and       200         Qiang Li, Florida International University       525         An Architecture for the Implementation of a Parallel Marker Propagation System       525         Howard Schneider, Cité de la Santé de Laval Hospital       531         LN-Tree: A Fault-Tolerant Tree Architecture       531         K. Y. Srinivasan, University of Toledo       A K. Sood, George Mason University         A Sliding Memory Plane Array Processor       537         M. H. Sunwoo and       J. K. Aggarual, University of Colorado         C. Wu and       Victor P. Nelson, Auburn University         Neurocomputing With Optical Pipeline Networks       545                                                                                                                                                                                                                                                                                                                                                                                      | •                                                                                 | •   |

| Tom Phillips,       Bret Michael, and         Zahi Abuhamdeh, George Mason University       A         A Multi-Layered G-Network for Massively Parallel Computation       519         Teresa Haynes Rice, East Tennessee State University       State University         Ratan K. Guha, University of Central Florida       Sequenced Hypercube Topology for a Massively-Parallel Database Computer       521         Naphtali Rishe,       Doron Tal, and       Qiang Li, Florida International University       State Laval Hospital         An Architecture for the Implementation of a Parallel Marker Propagation System       525         Howard Schneider, Cité de la Santé de Laval Hospital       State State University of Toledo         LN-Tree: A Fault-Tolerant Tree Architecture       531         K.Y. Srinivasan, University of Toledo       A K. Sood, George Mason University         A Sliding Memory Plane Array Processor       537         M. H. Sunwoo and       J. K. Aggarwal, University of Texas at Austin         Study of the Generalized Multiple Bus-Connected Parallel Computer       541         Chia-Jiu Wang, University of Colorado       C. Wu and         Victor P. Nelson, Auburn University       545         Neurocomputing With Optical Pipeline Networks       545                                                                                                                                                                                                                                                                     |                                                                                   |     |

| Bret Michael, and       Zaki Abuhamdeh, George Mason University         A Multi-Layered G-Network for Massively Parallel Computation       519         Teresa Haynes Rice, East Tennessee State University       819         Ratan K. Guha, University of Central Florida       521         A Sequenced Hypercube Topology for a Massively-Parallel Database Computer       521         Naphtali Rishe,       Doron Tal, and         Qiang Li, Florida International University       525         An Architecture for the Implementation of a Parallel Marker Propagation System       525         Howard Schneider, Cité de la Santé de Laval Hospital       531         LN-Tree: A Fault-Tolerant Tree Architecture       531         K. Y. Srinivasan, University of Toledo       A. K. Sood, George Mason University         A Sliding Memory Plane Array Processor       537         M. H. Sunwoo and       J. K. Aggarwal, University of Colorado         C. Wu and       Victor P. Nelson, Auburn University         Neurocomputing With Optical Pipeline Networks       545         Zhiwei Xu, Rutgers University       545                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                 | 515 |

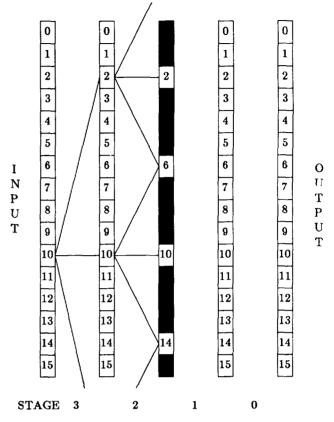

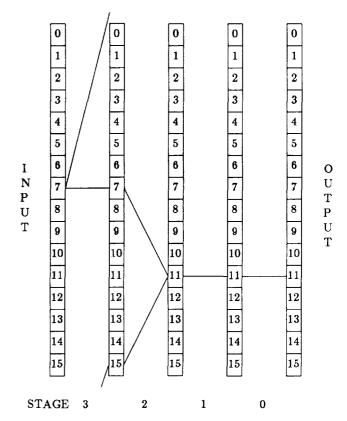

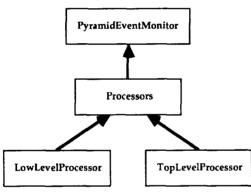

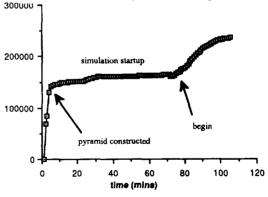

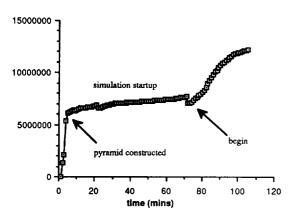

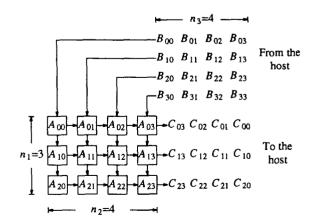

| Zahi Abuhamdeh, George Mason University       519         A Multi-Layered G-Network for Massively Parallel Computation       519         Teresa Haynes Rice, East Tennessee State University       519         Ratan K. Guha, University of Central Florida       521         A Sequenced Hypercube Topology for a Massively-Parallel Database Computer       521         Naphtali Rishe,       Doron Tal, and         Qiang Li, Florida International University       525         An Architecture for the Implementation of a Parallel Marker Propagation System       525         Howard Schneider, Cité de la Santé de Laval Hospital       531         K. Y. Srinivasan, University of Toledo       537         A. K. Sood, George Mason University       537         M. H. Sunuco and       J. K. Aggarwal, University of Texas at Austin         Study of the Generalized Multiple Bus-Connected Parallel Computer       541         Chia-Jiu Wang, University of Colorado       C. Wu and         Victor P. Nelson, Auburn University       545         Neurocomputing With Optical Pipeline Networks       545                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                                                                 |     |