77.73 P 354

## DESIGN AND ANALYSIS TECHNIQUES FOR CONCURRENT BLACKBOARD SYSTEMS

#### A Dissertation

Presented to

The Faculty of the Department of Computer Science

The College of William and Mary in Virginia

In Partial Fulfillment

of the Requirements for the Degree of

Doctor of Philosophy

by

John William McManus

(NASA-CR-190300) DESIGN AND ANALYSIS TECHNIQUES FOR CONCURRENT BLACKBOARD SYSTEMS Ph.D. Thesis (College of William and Mary) 354 p CSCL 09B N92-25257

Unclas 63/61 0087548

## APPROVAL SHEET

# This dissertation is submitted in partial fulfillment of the requirements for the degree of

|                   | Doctor of Philosophy                         |     |

|-------------------|----------------------------------------------|-----|

|                   | John William McManus, Author                 |     |

| pproved, April 19 | 992.                                         |     |

|                   | William L. Bynum, Dissertation Advisor       |     |

|                   | Stefan Feyock                                |     |

|                   | Rex K. Kincaid                               |     |

|                   | David M. Nicol                               |     |

|                   | P. Douglas Arbuckle, NASA Langley Research ( | Cer |

## Dedication

This thesis is dedicated to my parents, Vincent Joseph and Maryelaine McManus; my grandparents Joseph and Margaret McManus, and John William and Mary Ramey; and Dr. William Shelton Gray, Jr. I thank each of your support and for the love and encouragement that you have given me.

O Attic Shape! Fair Attitude! with brede

Of marble men and maidens overwrought.

With forest branches and the trodden weed;

Thou, silent form, dost tease us out of thought

As dost eternity: Cold Pastoral!

When old age shall this generation waste,

Thou shall remain, in midst of other woe

Than ours, a friend to man, to whom thou say'st,

'Beauty is truth, truth beauty'—that is all

Ye know on earth, and all ye need to

know.

Ode on a Grecian Urn John Keats 1819

## Table of Contents

| Introduction                                               | 2             |

|------------------------------------------------------------|---------------|

| 1.1 Statement of the Problem                               | 2             |

| 1.2 Unified Design and Analysis Methodology for Concurrent | •             |

| Blackboard Systems                                         | 3             |

| 1.3 The Concurrent Object-Oriented Blackboard System       | 7             |

| 1.4 Paladin and Concurrent-Claws                           |               |

| 1.5 Thesis Outline                                         | 9             |

| The Blackboard Problem-solving model                       | 13            |

| 2.1 The Blackboard Model                                   | 13            |

| 2.2 Description of the Blackboard Model                    | 15            |

| 2.3 Concurrent Blackboard Systems                          | 16            |

| 2.4 Types of Concurrent Blackboard Systems                 | 19            |

| 2.5 Distributed Blackboard Systems                         | 24            |

| 2.6 Conclusions                                            | 32            |

| A Formal Model for Blackboard Systems                      | 35            |

| 3.1 Formal Definition of a Blackboard System               | 35            |

| 3.2 Knowledge Source Activation Graph                      | 41            |

| 3.3 Examples                                               | 42            |

| 3.4 Multiple Instances of a Knowledge Source               | 49            |

| Blackboard System Design and Analysis Techniques           | 52            |

| 4.1 Unified Approach to System Design and Analysis         | 53            |

| 4.2 Knowledge Source Connectivity Analysis                 | 54            |

| 4.3 Examples of Connectivity Analysis                      | 59            |

| 4.4 Conclusions                                            | 70            |

| A Simulation Model for Blackboard Systems                  | 73            |

| 5.1 Blackboard System Simulation Model                     | 73            |

| 5.2 Description of the Simulation Model                    | 79            |

| 5.3 Conclusions                                            | 81            |

| The Concurrent Object-Oriented Blackboard System.          | 83            |

| 6.1 Description of The COBS Architecture                   | 83            |

| 6.2 Description of The COBS Design and Analysis Tools      | 88            |

| 6.3 Description of The COBS Simulation Model               | 91            |

| 6.4 Description of The COBS Code Generator                 | 94            |

|                                                            |               |

| The Paladin Tactical Decision Generation System            | 97            |

| 7.1 The Tactical Guidance Research and Evaluation System   | 97            |

| 7.2 TiGRES Components                                      | ጋ0<br>ያይ      |

| 7.4 KBS Modules of Paladin                                 | ۰۰۰۰۰۶۵<br>۱۸ |

| 7.4 RBS Modules of Paradin                                 | 10<br>10      |

| 7.5 Paradin Testing Procedures                             | 10            |

| 7.7 Evaluation of Cube_CLAWS Performance                   | 10            |

| 7.7 Evaluation of Cube_CLA ws 1 chormance                  | 11            |

|                                                            |               |

| Table of Contents |     |

|-------------------|-----|

| 7.9 Conclusions   | 114 |

## Table of Contents

| Validation of the COBS Simulation Model                                 | 117 |

|-------------------------------------------------------------------------|-----|

| 8.1 Simulation of Cube_CLAWS                                            | 117 |

| 8.2 Validating Cube_CLAWS Simulation Results                            | 118 |

| 8.3 Simulation of Paladin                                               | 122 |

| 8.4 Validating the Paladin Simulation Results                           | 123 |

| 8.5 Conclusions                                                         | 125 |

| 0.5 Constantinum                                                        |     |

| Utilizing the Concurrent Object-Oriented Blackboard System              | 127 |

| 9.1 Analysis of the Cube_CLAWS Design Specifications                    | 127 |

| 9.2 Analysis of the Cube Simulation Results                             | 130 |

| 9.3 Analysis of the Paladin Design Specifications                       | 134 |

| 9.4 Evaluation of Paladin Simulation Results                            | 135 |

| 9.5 Evaluation of Alternative Hardware Configurations                   | 136 |

| 9.6 Conclusions                                                         | 142 |

|                                                                         |     |

| Summary                                                                 | 144 |

| 10.1 The Formal Model for Blackboard Systems                            | 144 |

| 10.2 Future Research                                                    |     |

|                                                                         |     |

| Glossary                                                                | 148 |

|                                                                         |     |

| Appendix A Example Blackboard System Specifications                     | 152 |

| A.1 Blackboard System Specifications                                    | 152 |

| A.2 Blackboard System Execution Traces                                  | 155 |

|                                                                         |     |

| Appendix B Example Connectivity Analysis Results                        | 161 |

| B.1 Examples of Connectivity Analysis                                   | 161 |

| B.2 Example of a Simulation Run                                         | 176 |

|                                                                         |     |

| Appendix C                                                              | 189 |

| ••                                                                      |     |

| Appendix D Concurrent Blackboard Simulation System Verification Results |     |

| and COBS Simulation System Software                                     | 214 |

| D.1 Simulation Software and Results for B1                              | 214 |

| D.2 Simulation Software and Results for B2                              | 223 |

| D.3 Simulation Software and Results for B3                              | 235 |

| D.4 Simulation Software and Results for B4                              | 246 |

| D.5 Simulation Support Software                                         | 256 |

| D.6 COBS Simulation System Software                                     | 264 |

|                                                                         |     |

| Appendix E The COBS Code Generator                                      | 279 |

| E.1 Listing of the COBS Code Generator                                  | 279 |

| E.2 COBS Generated B2 Code                                              | 293 |

|                                                                         |     |

| Appendix F COBS Verification and Validation Results                     | 300 |

| F.1 Cube Design Analysis Results                                        | 300 |

| F.2 Cube2 Design Analysis Results                                       | 300 |

| F.3 Cube4 Design Analysis Results                                       | 301 |

| F4 Cubes Design Analysis Results                                        | 303 |

##

## Acknowledgments

The author would like to thank Dr. William Lee Bynum for all of the time, support, and ideas that he has provided. Thanks are given to the additional committee members for their willingness to serve on my committee: P. Douglas Arbuckle, Stefan Feyock, Rex K. Kincaid, and David M. Nicol. Special thanks go to David Nicol for reviewing the preliminary drafts of the Formal Model and the Simulation Model, his comments and ideas were invaluable to my research. Special thanks also go to P. Douglas Arbuckle for providing a safe haven in which to perform my research.

Gratitude is owed to the NASA Langley Research Center, and the Flight Systems Directorate for allowing me the opportunity to continue my education while working in the Aircraft Guidance and Control Branch. Appreciation is given to the Aircraft Guidance and Control Branch, which provided access to the computer facilities used for this research.

A special debt is owed to my wife, Mary Loving McManus, for being understanding and supportive while I have earned this degree.

## List of Tables

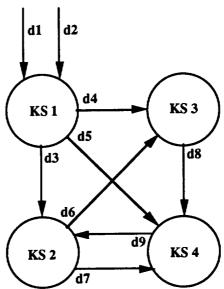

| Table 4.1 B1 Connectivity Analysis Results   | 60 |

|----------------------------------------------|----|

| Table 4.2 B1 Output Overlaps Γ               | 60 |

| Table 4.3 B1 Specialization Values Ω         | 60 |

| Table 4.4 B1 Output to Input Connectivity Λ  | 61 |

| Table 4.5 B1 Interdependence Values Π        | 61 |

| Table 4.6 B1 Serialization Values Σ          | 61 |

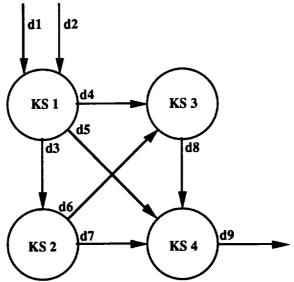

| Table 4.7 B2 Connectivity Analysis Results   | 62 |

| Table 4.8 B2 Output Overlaps Γ               | 63 |

| Table 4.9 B2 Specialization Values Ω         | 63 |

| Table 4.10 B2 Output to Input Connectivity Λ | 63 |

| Table 4.11 B2 Interdependence Values Π       | 64 |

| Table 4.12 B2 Serialization Values Σ         | 64 |

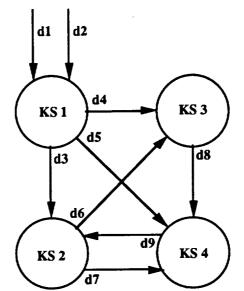

| Table 4.13 B3 Connectivity Analysis Results  | 65 |

| Table 4.14 B3 Output Overlaps Γ              | 66 |

| Table 4.15 B3 Specialization Values Ω        | 66 |

| Table 4.16 B3 Output to Input Connectivity Λ | 66 |

| Table 4.17 B3 Interdependence Values Π       | 67 |

| Table 4.18 B3 Serialization Values Σ         | 67 |

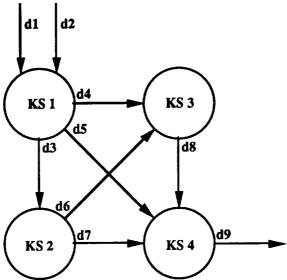

| Table 4.19 B4 Connectivity Analysis Results  | 68 |

| Table 4.20 B4 Output Overlap Γ               | 68 |

| Table 4.21 B4 Specialization Values Ω        | 69 |

| Table 4.22 B4 Output to Input Connectivity Λ | 69 |

| Table 4.23 B4 Interdependence Values Π       | 69 |

| Table 4.24 B4 Serialization Values Σ         | 70 |

| List of Tables                                                |     |

|---------------------------------------------------------------|-----|

| Table 7.1. Modes of Operation                                 | 102 |

| Table 7.2. Software Test Configuration Processor Assignments  | 110 |

| Table 8.1 Cube_CLAWS Knowledge Source Execution Times (msec.) | 118 |

| Table 8.2 Cube_CLAWS System Execution Times (msec.)           | 122 |

| Table 8.3 Paladin Knowledge Source Execution Times (msec.)    | 124 |

| Table 8.4 Paladin System Execution Times (msec.)              | 124 |

| Table 9.1 Processor Evaluation (msec.)                        | 137 |

| Table 9.2 Dynamics Knowledge Source Execution Times (msec.)   | 139 |

## List of Figures

| Figure 1.1. Blackboard System Design Process                                         | 6   |

|--------------------------------------------------------------------------------------|-----|

| Figure 1.2. Concurrent Object-Oriented Blackboard System Schematic                   | 8   |

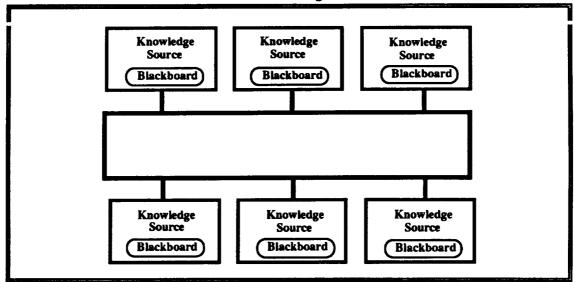

| Figure 2.1. Parallel Blackboard System Schematic                                     | 20  |

| Figure 2.2. Distributed Blackboard System with Centralized Blackboard Data Structure | 25  |

| Figure 2.3. Distributed Blackboard System with Distributed Blackboard Data Structure | 26  |

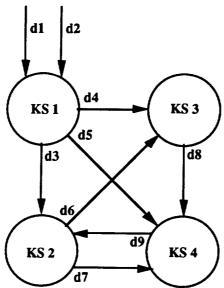

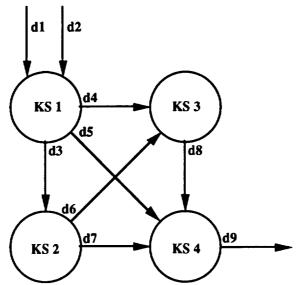

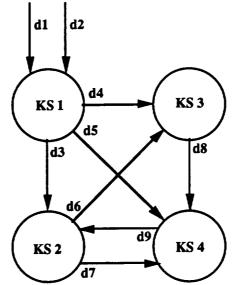

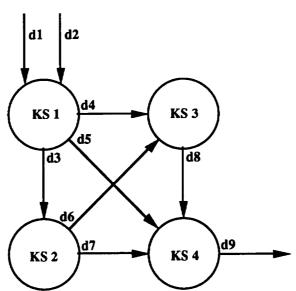

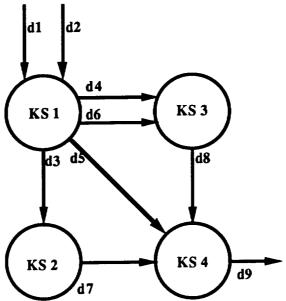

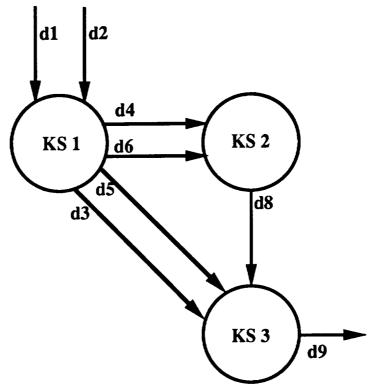

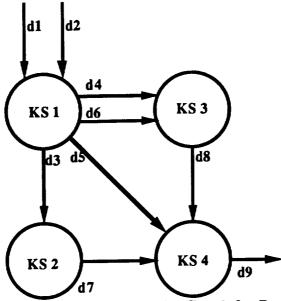

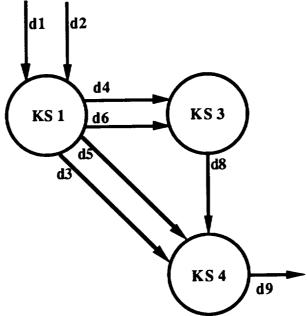

| Figure 3.1 Unsafe Knowledge Source Activation Graph                                  | 45  |

| Figure 3.2 Safe Knowledge Source Activation Graph                                    | 47  |

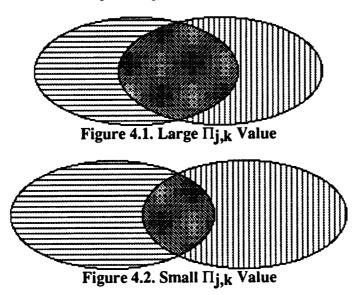

| Figure 4.1. Large P <sub>j,k</sub> Value                                             | 57  |

| Figure 4.2. Small P <sub>j,k</sub> Value                                             | 57  |

| Figure 4.3 Connectivity Graph for B1                                                 | 62  |

| Figure 4.4 Connectivity Graph for B2                                                 | 64  |

| Figure 4.5 Connectivity Graph for B3                                                 | 68  |

| Figure 4.6 Connectivity Graph for B4                                                 | 70  |

| Figure 5.2 Simulation Execution Structure                                            | 80  |

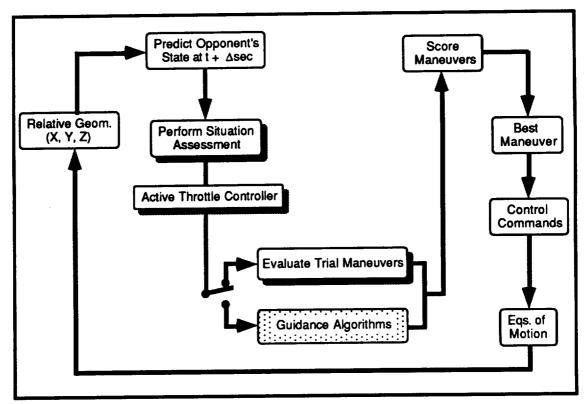

| Figure 7.1. Schematic Of Paladin                                                     | 102 |

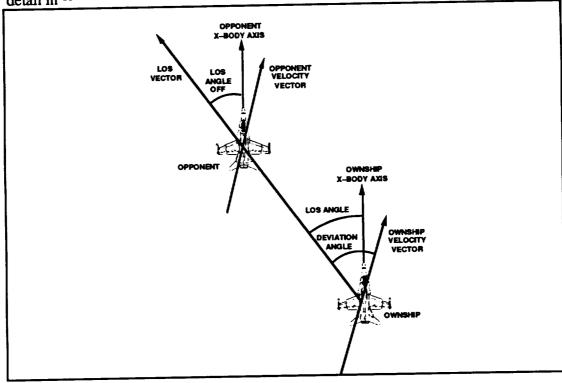

| Figure 7.2. Angle Definitions                                                        | 103 |

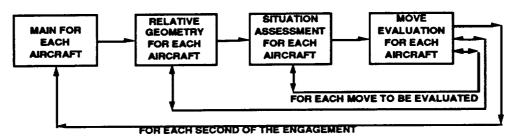

| Figure 7.3. CLAWS Schematic                                                          | 108 |

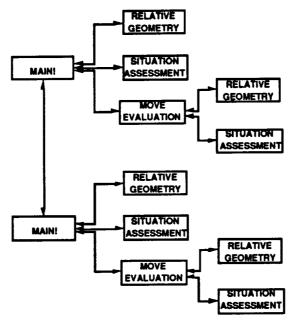

| Figure 7.4. Cube_CLAWS Schematic                                                     | 109 |

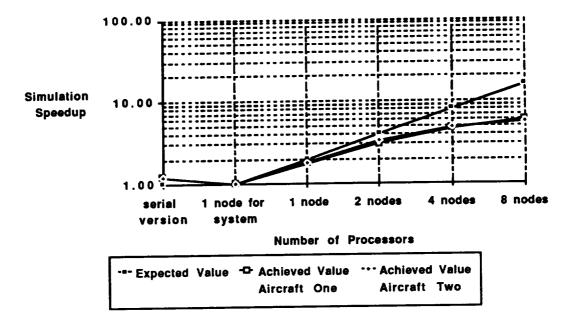

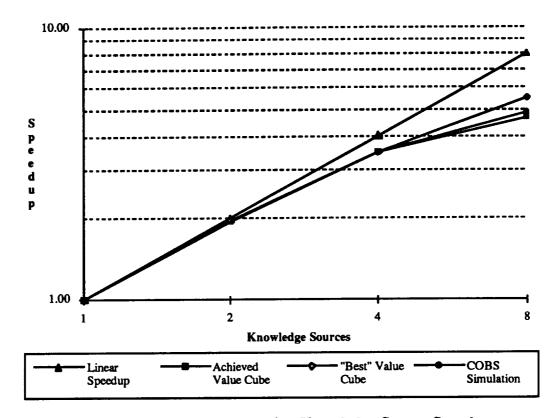

| Figure 7.5. Simulation Speedup                                                       | 112 |

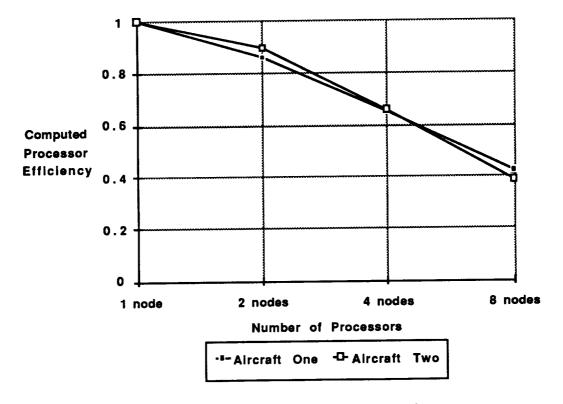

| Figure 7.6. Processor Efficiency for Simulation.                                     | 112 |

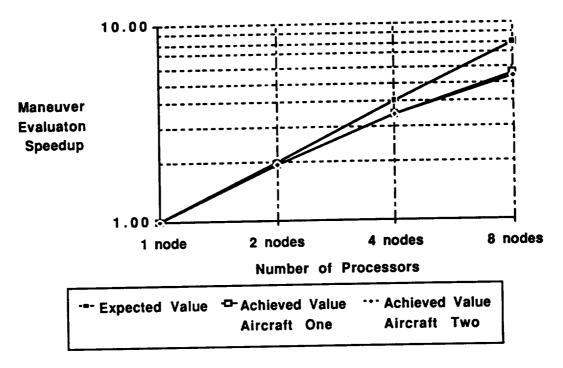

| Figure 7.7. Maneuver Evaluation Speedup                                              | 113 |

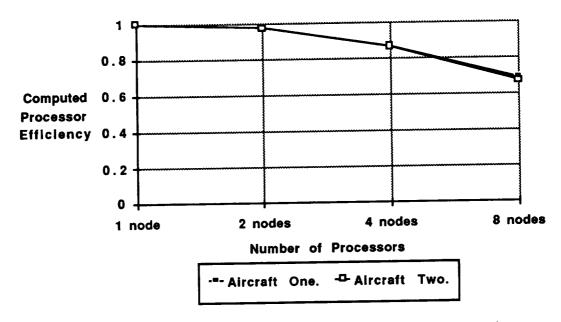

| Figure 7.8. Processor Efficiency for Maneuver Evaluation Subroutine                  | 113 |

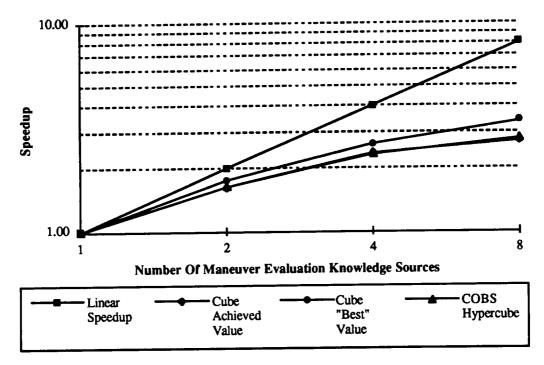

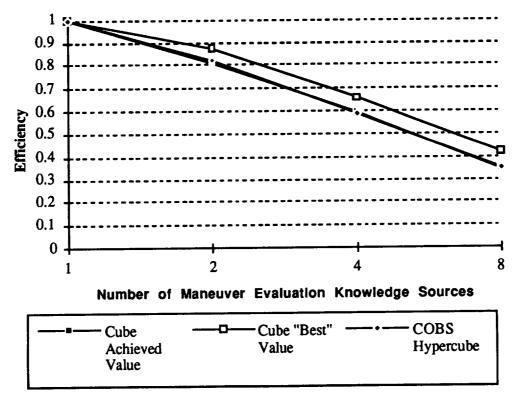

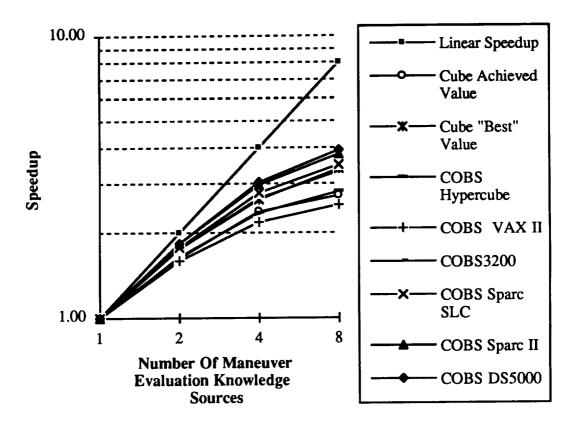

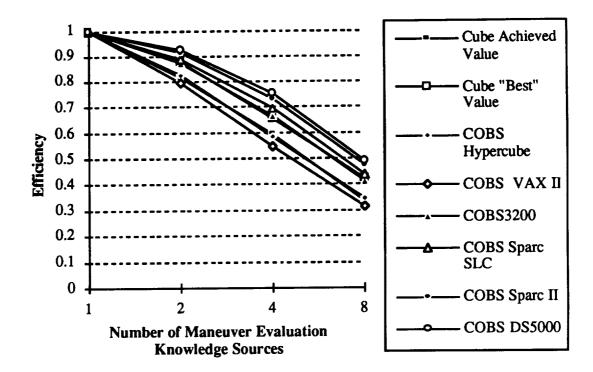

| Figure 8.1. Maneuver Evaluation Knowledge Source Speedup                             | 120 |

| List of Figures                                          |     |

|----------------------------------------------------------|-----|

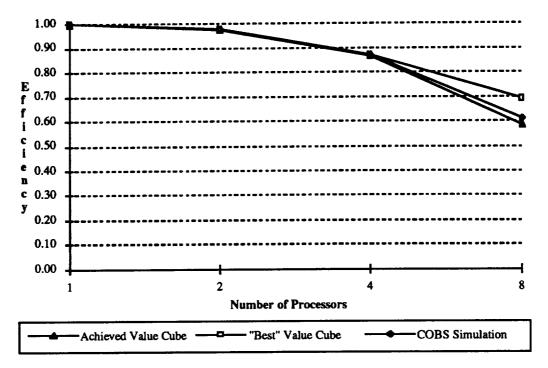

| Figure 8.2. Knowledge Source Processor Efficiency        | 121 |

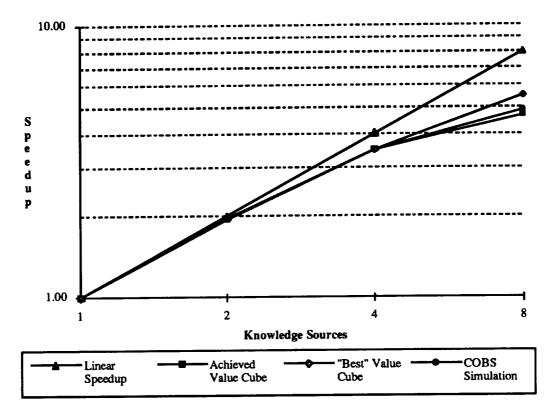

| Figure 9.1. Maneuver Evaluation Knowledge Source Speedup | 131 |

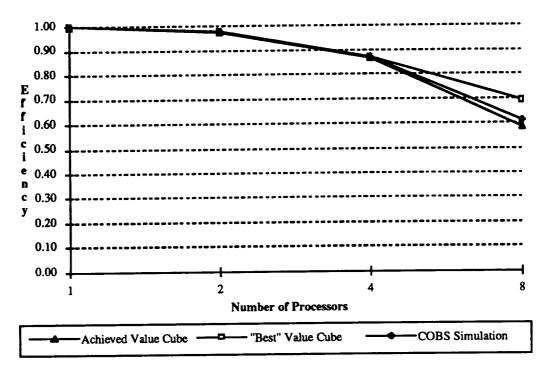

| Figure 9.2. Knowledge Source Processor Efficiency        | 132 |

| Figure 9.3. Cube Design Speedup                          | 133 |

| Figure 9.4. Cube Knowledge Source Efficiency             | 133 |

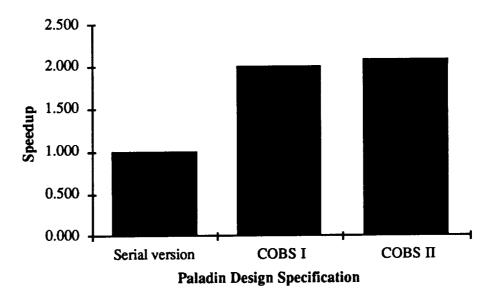

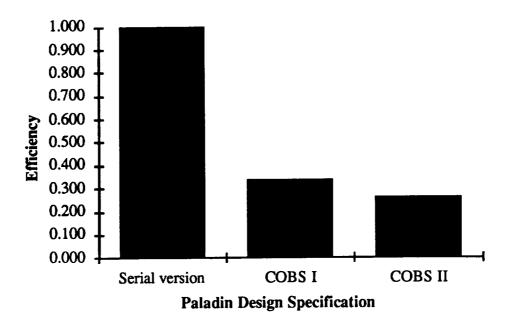

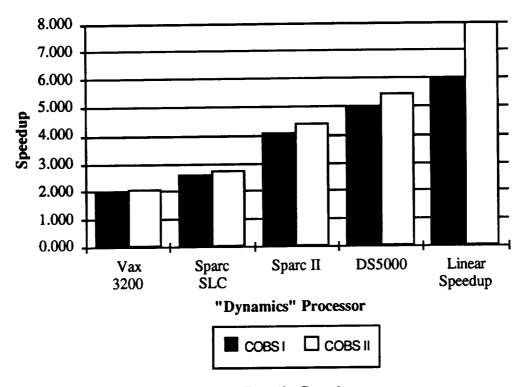

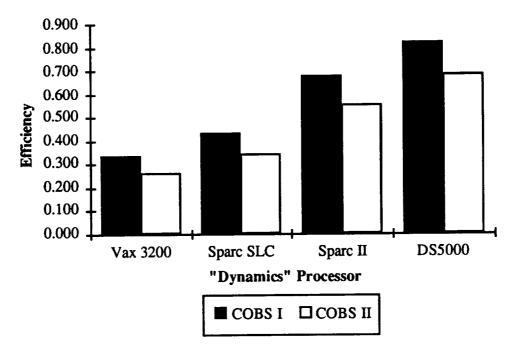

| Figure 9.5 Paladin Speedup                               | 135 |

| Figure 9.6 Processor Efficiency                          | 136 |

| Figure 9.7. System Speedup                               | 138 |

| Figure 9.8. Processor Efficiency                         | 139 |

| Figure 9.9 Paladin Speedup                               | 140 |

| Figure 9.10 Processor Efficiency                         | 141 |

| Figure A.1 Unsafe Knowledge Source Activation Graph      | 153 |

| Figure A.2 Safe Knowledge Source Activation Graph        | 155 |

| Figure B.1 Connectivity Graph for B1                     | 165 |

| Figure B.2 Connectivity Graph for B2                     | 169 |

| Figure B.3 Connectivity Graph for B3                     | 173 |

| Figure B.4 Connectivity Graph for B4                     | 176 |

#### Abstract

Blackboard systems are a natural progression of knowledge-based systems into a more powerful problem solving technique. They provide a way for several highly specialized knowledge sources to cooperate to solve large, complex problems. Blackboard systems incorporate the concepts developed by rule-based and expert systems programmers and include the ability to add conventionally coded knowledge sources. The small and specialized knowledge sources are easier to develop and test and can be hosted on hardware specifically suited to the task that they are solving.

The lack of a coherent set of design tools and guidelines results in blackboard systems being developed in an ad hoc fashion. Designers have been forced to make design choices in a void. Often the designer is stuck with a poorly designed system simply because revisions are too difficult once the system has been implemented. The lack of design and analysis tools is one of the reasons why incorporating concurrency into the blackboard problem-solving model has not been successful. The use of a centralized control mechanism, and contention in accessing the blackboard have also restricted the success of previous systems.

The Formal Model for Blackboard Systems was developed to provide a consistent method for describing a blackboard system. The Formal Model outlines the basic components of a blackboard system, and how the components interact. A set of blackboard system design tools has been developed and validated for implementing systems that are expressed using the Formal Model. The tools are used to test and refine a proposed blackboard system design before the design is implemented. The set of blackboard system design tools consists of a Knowledge Source Organizer, a Knowledge Source Input/Output Connectivity Analyzer, and a validated Blackboard System Simulation Model. My research has shown that the level of independence and specialization of the knowledge sources directly affects the performance of blackboard systems. Using the design, simulation, and analysis tools, I developed a concurrent object-oriented blackboard system that is faster, more efficient, and more powerful than existing systems. The use of the design and analysis tools provided the highly specialized and highly independent knowledge sources required for my concurrent blackboard system to achieve its design goals.

## Chapter 1

## Introduction

Blackboard systems are a natural progression of Knowledge-Based systems into a more powerful problem-solving technique. They provide a way for several highly specialized knowledge sources to cooperate to solve large and complex problems. Blackboard systems incorporate the concepts developed by rule-based and expert systems programmers and include the ability to add conventionally coded software to cooperate in solving problems. The smaller, specialized knowledge sources are easy to develop and test, and can be hosted on hardware specifically suited to their.

### 1.1 Statement of the Problem

Designing and developing blackboard systems is a difficult process. The designer is trying to balance several conflicting goals and achieve a high degree of concurrent knowledge source execution while maintaining both knowledge and semantic consistency on the blackboard. Blackboard systems have not attained their apparent potential because no established tools or methods exist to guide in their construction or analyze their performance.

"At present (1989), intuition is the primary criterion for making an appropriate set of design choices. Application characteristics, hardware and communication characteristics, and how the application is implemented are all likely to strongly affect the performance of a parallel or distributed blackboard application.

What is needed are system engineering guidelines for making appropriate design choices and improved languages and tools for constructing parallel and distributed blackboard applications. Such engineering guidelines require empirical measurements of pioneering applications. A few data points are beginning to emerge, but direct measurement of applications designed and executed on real parallel or distributed hardware remains to be performed."

My assessment of the current state—of—the—art in blackboard systems (Chapter 2) is that the techniques used to design, analyze, and develop blackboard systems are not sufficient. Successful blackboard systems application requires the development of a unified design and analysis methodology. This assessment is supported by the discussions at the AAAI Workshops on Blackboard Systems and other related research. In "A Survey of the Eighth National Conference on Artificial Intelligence:

Pulling Together or Pulling Apart?" Paul Cohen presents some interesting hypotheses on the state of AI research. His research shows that common methodological problems—from poor system evaluation to absurd assumption—arise because the methodologies applied by most current AI researchers are not sufficient.<sup>2</sup>

"I offer evidence for four hypotheses: First, AI research is dominated by two methodologies. Second, with respect to the goal of developing science and technology to support the design and analysis of AI systems, neither methodology is sufficient alone. Third, the bulk of AI research consequently suffers from familiar methodological problems, such as a lack of evaluation, a lack of hypothesis and predictions, irrelevant models, and weak analytic tools. Fourth, a methodology exists that merges the current "big two" and eliminates the conditions that give rise to methodological problems."<sup>3</sup>

Cohen's results show that most AI research applies one of two existing methodologies: model-centered research, or system-centered research. Model-centered research involves defining, extending, differentiating, and generalizing models. System-centered research involves designing and implementing systems to perform tasks that are too large and complex to be accomplished by a single algorithm.<sup>4</sup> The results are clear: No single existing blackboard system design and analysis methodology is sufficient.

## 1.2 Unified Design and Analysis Methodology for Concurrent Blackboard Systems

To address these problems, I have developed a methodology and a set of unified techniques for the design, simulation, analysis, and implementation of concurrent blackboard systems. The techniques include: a formal model for blackboard systems, a set of design and analysis techniques, a simulation model, and an automatic code generator for blackboard systems. This methodology provides for automatic generation of the blackboard system software based on the formal blackboard system design specifications.

The lack of a coherent set of design techniques and methodologies for blackboard systems has resulted in blackboard systems being developed in an ad hoc fashion. Some shells for building blackboard systems exist, such as Cage, Poligon, and GBB. These shells have no design aids or analysis tools and are insufficient. The shells do not provide the system designer with the tools or information required to successfully implement a system. As a result, many system designers have been stuck with poorly

designed systems because revisions are too difficult once the system has been implemented. The lack of design and analysis techniques is a major reason why incorporating concurrency into the blackboard problem-solving model has not been successful.

### 1.2.1 A Formal Model for Blackboard Systems

The need for a formal model for blackboard systems was highlighted at The First Workshop on Blackboard Systems<sup>5</sup> and has been repeated at the subsequent workshops<sup>6</sup>.

"As more and more systems appear claiming to use the blackboard paradigm, it is increasingly necessary to determine a set of criteria that define the essential elements of blackboard systems."

As interest in blackboard systems has grown, a formal description of the blackboard problem solving paradigm and the components of a blackboard system have become crucial. A formal model is required to define the basic components of a blackboard system. The formal model should specify what is, and what is not, a blackboard system. The Blackboard Architecture and Organization Panel at the workshop was concerned with identifying the basic attributes of a blackboard system, and with how far a system can deviate from the defined architecture and still be classified as a blackboard system.

I have developed a formal model for blackboard systems to address these issues. The Formal Model for Blackboard Systems is presented in detail in Chapter Three. The formal model outlines the basic components of a blackboard system, and how the components interact. Systems that cannot be expressed using the formal model are not valid blackboard systems. The formal model is consistent with the description of a blackboard system presented by H. Penny Nii<sup>8</sup>, and the formal description presented at the blackboard systems workshops.

#### 1.2.2 Blackboard System Design and Analysis Techniques

The set of blackboard system design techniques consists of a Knowledge Source Organizer, and a Knowledge Source Connectivity Analyzer. These generic techniques are used to test and refine a proposed blackboard system design before implementing the system. My preliminary research 9,10,11,12 has shown that the level of

independence and specialization of the knowledge sources directly affects the performance of blackboard systems.

This dissertation describes the first use of specialized blackboard system design and analysis techniques to design and predict the performance of concurrent blackboard systems. These techniques can be applied to many distributed system design problems and other parallelization problems. The design techniques measure knowledge source output/input connectivity across a shared blackboard data structure. This information is used to determine knowledge source independence and point out potential hotspots on the blackboard data structure.

The first technique, Knowledge Source Organization, decomposes the problem into component parts and aids in the initial selection of knowledge sources and the formation of the blackboard structure. Knowledge Source Organization develops the basic specification of the blackboard data objects and the knowledge sources.

The second technique, Knowledge Source Connectivity Analysis, completes the formal specification of a blackboard system, and computes a knowledge source connectivity graph showing blackboard data object connectivity between knowledge sources. The blackboard data object connectivity information is used to determine the interdependencies between knowledge sources and locate hotspots on the blackboard. The information is also used to predict the overall system performance and blackboard overhead for individual blackboard components. Knowledge sources that are tightly coupled may be combined into a single knowledge source to decrease the traffic on the blackboard and to increase system performance. Knowledge sources that have a high overhead and small execution times may be combined to reduce the overhead costs. This technique can be applied to many generic parallelization problems to analyze data connectivity in the system.

## 1.2.3 Blackboard System Simulation Model

The Blackboard System Simulation Model is a serial discrete event simulation. Verification of the simulation model and the implementation of the simulation system was performed using example blackboard system specifications. The performance of the simulation system was validated by comparing the performance predicted by the simulation model to the performance of known blackboard systems. Any discrepancies between the predicted and the actual performance of the system were

used to refine the blackboard simulation model, or possibly the blackboard system implementation. This refinement process was iterated at each stage of development until the predicted and actual performance values converged. The verification and validation of the simulation model is discussed in detail in Chapter Eight.

This dissertation describes the first use of simulation to predict the performance of blackboard systems. The knowledge source distribution information and the blackboard data connectivity generated by the knowledge source connectivity analysis is used to build the simulation model of the system. The execution of the knowledge sources and their interaction with the blackboard data objects are modeled.

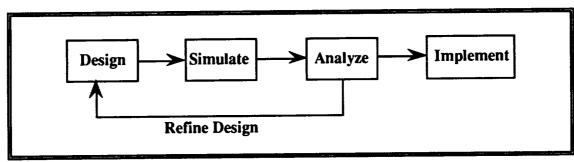

Once validated, a blackboard simulation model allows tradeoff and performance analysis to be completed before systems are implemented. The simulation model may also be used to determine the effect of different hardware and software configurations on system performance. The data generated by the model can be used to predict the performance of a single blackboard system implemented using several hardware/software configurations. The designer can develop an initial design using the blackboard system design tools and then use the blackboard system simulation model and blackboard system analysis tools to refine the design. (Figure 1.1) When the design goals have been met, and the systems performance validated by the blackboard system simulation model, the design can be implemented. The use of a design—>simulate—>refine process makes it easier for designers to meet design and performance goals, resulting in more efficient concurrent blackboard systems.

Figure 1.1. Blackboard System Design Process

## 1.2.3 Blackboard System Code Generator

The Blackboard System Code Generator generates all of the software required to implement a blackboard system based on a valid system specification. The code generator does not generate the software for the knowledge sources. The system

generates the Blackboard Data Structure and all required support software. This includes all required blackboard data object locks and synchronization primitives. The system generated software is implemented using the Concurrent Object-Oriented Blackboard System.

## 1.3 The Concurrent Object-Oriented Blackboard System

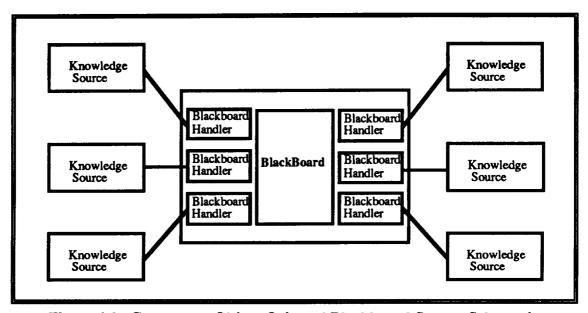

The Concurrent Object-Oriented Blackboard System (COBS) is an implementation of the formal model for blackboard systems, the design and analysis techniques, and the simulation model. The basic premise of COBS is that a concurrent blackboard system consisting of a set of highly independent, highly specialized knowledge sources cooperating using a shared object-oriented blackboard with no centralized blackboard controller will achieve the potential of the blackboard model of problem solving and outperform a conventionally designed blackboard system.

To date, most concurrent blackboard systems have centered on solving the memory contention problem or on reducing centralized control. Three generic concepts combine to form a synergistic solution to both of these problems.

- 1) A Daemon Driven Control Structure

- 2) The use of Blackboard Handlers

- 3) Highly Specialized, Highly Independent Knowledge Sources

COBS uses a associative memory-based control structure and blackboard handlers to implement a distributed control structure. The associative memory is implemented using an object-oriented data structure and daemon functions. This type of control structure models the associative memory concept of how the human brain functions and allows concurrent processing. The distributed control structure and the use of highly specialized, highly independent knowledge sources reduce memory contention on the blackboard and remove centralized control.

Blackboard control and knowledge source selection is achieved using daemons attached to the blackboard data objects. The daemons activate blackboard handlers when the data elements on the blackboard are updated. This daemon-driven control structure removes the need for a centralized blackboard control mechanism and allows concurrent knowledge source execution. The blackboard handlers control knowledge

source activation and provide the knowledge sources read/write access to the blackboard.

COBS was used to develop several applications. The applications, presented in detail in Chapter Seven, were used to validate the blackboard system simulation model. A preliminary blackboard simulation model was used in conjunction with the blackboard system design tools to fine tune the performance of the blackboard system before the design was implemented.

Figure 1.2. Concurrent Object-Oriented Blackboard System Schematic

## 1.4 Paladin and Concurrent-Claws

A Tactical Decision Generator for Air-to-Air combat was developed to evaluate COBS. Past research <sup>13,14,15,16</sup> has shown that this application requires a set of highly specialized knowledge sources cooperating in a dynamic environment. This application should effectively test all features of COBS. A concurrent blackboard system, Paladin, is used as an "Iron Pilot" for evaluating super-agile aircraft performance at NASA Langley Research Center. An "Iron Pilot" is a deterministic autopilot that acts as a challenging opponent in a simulated air combat engagement.

Paladin consists of multiple cooperating knowledge-based systems developed to study within-visual-range air combat engagements. This system incorporates modern airplane simulation techniques, sensors, and weapon systems. A concurrent message-passing version of the application, Concurrent-CLAWS, was developed and tested on

a 16 processor Intel Hyper Cube<sup>17</sup>. The concurrent version highlighted the gains that could be made by using a concurrent blackboard system and outlined many of the problems associated with designing concurrent blackboard systems. The experience gained in designing and developing these preliminary systems has affected the basic structure of COBS and highlighted the need for design and analysis tools for blackboard systems.

#### 1.5 Thesis Outline

This thesis is organized in the following manner:

- Chapter 2: The Blackboard Problem-solving model. This chapter restates the standard definitions of the blackboard problem-solving model and presents the development of serial implementations of the blackboard model. Concurrent blackboard systems are presented. Several problems associated with current implementations of parallel and distributed blackboard systems are discussed.

- Chapter 3: A Formal Model For Blackboard Systems. This chapter presents a formal specification of the blackboard problem-solving model and the components of a blackboard system.

- Chapter 4: Blackboard System Design and Analysis Techniques. This chapter describes a set of design and analysis techniques for blackboard systems.

Knowledge Source Connectivity is defined, and its effect on the performance of a blackboard system design is presented. Four examples are given, and the results of the design analyses are presented.

- Chapter 5: A Simulation Model for Blackboard Systems. This chapter discusses a serial simulation model for blackboard systems that is used to model the performance of proposed blackboard system designs. A set of blackboard system performance metrics is developed to measure blackboard system performance.

- Chapter 6: The Concurrent Object-Oriented Blackboard System. This chapter describes the Concurrent Object-Oriented Blackboard System model. and how it implements the formal model for blackboard systems. The four examples defined in Chapter Four are analyzed, and the results of the design analyses are used to verify the performance of the COBS design and analysis tools

- Chapter 7: Paladin. The application that will be developed to evaluate the Concurrent Object—Oriented Blackboard System, the set of design and analysis tools, and the blackboard simulation model is presented in this chapter.

- Chapter 8: Validation of the Concurrent Object—Oriented Blackboard System Simulation Model. This chapter describes the validation of the COBS simulation system using the two applications described in Chapter Seven and the blackboard system simulation model. The results of the analysis and simulation of the two examples and the systems actual performance data is used to validate the performance of the COBS simulation system.

- Chapter 9: Utilizing the Concurrent Object-Oriented Blackboard System

Simulation Model. This chapter describes the design and development of two applications using the set of design and analysis tools for concurrent blackboard systems and the blackboard system simulation model.

- Chapter 10: Conclusions This chapter presents the summary of the Formal Design and Analysis Techniques, and outlines future work.

### **Endnotes for Chapter One**

- <sup>1</sup> Daniel D. Corkill: "Advanced Architectures: Concurrency and Parallelism." In *Blackboard Architectures and Applications*, ed. V. Jagannathan et al., Academic Press, Inc 1989.

- Paul R. Cohen: "A Survey of the Eighth National Conference on Artificial Intelligence: Pulling Together or Pulling Apart?" AI Magazine, Spring 1991. pp 16-41

- 3 Ibid.

- 4 Ibid.

- 5 Rajendra Dodhiawala et al: "The First Workshop on Blackboard Systems." AI Magazine, Spring 1989. pp 77-80

- 6 Keith Decker, "Blackboard Systems." IEEE Expert, October 1991. pp 71-72

- <sup>7</sup> Dodhiawala

- <sup>8</sup> H. Penny Nii, "Blackboard Systems: The Blackboard Model of Problem Solving and the Evolution of Blackboard Architectures." *AI Magazine*, 7 (2), 1986, pp. 38 53.

- 9 Richard M. Hueschen and John W. McManus. "Application of AI Methods to Aircraft Guidance and Control." In *Proceedings 1988 American Control Conference*, June 15-17, 1988. pp. 195 - 201.

- 10 John W. McManus and Kenneth H. Goodrich. "Application of Artificial Intelligence (AI) Programming Techniques to Tactical Guidance For Fighter Aircraft." In *Proceedings AIAA Guidance*, Navigation, and Control Conference, 1989. AIAA Paper #89-3525, pp. 851-858.

- 11 John W. McManus and Kenneth H. Goodrich. "Artificial Intelligence (AI) Based Tactical Guidance For Fighter Aircraft." In *Proceedings AIAA Guidance*, Navigation, and Control Conference, 1990. AIAA Paper # 90-3435.

- 12 John W. McManus "A Parallel Distributed System for Aircraft Tactical Decision Generation." In *Proceedings of the 9th Digital Avionics Systems Conference*, 1990, pp.505 512.

- 13 Richard M. Hueschen and John W. McManus, 1988

- <sup>14</sup> John W. McManus and Kenneth H. Goodrich, 1989

- 15 John W. McManus and Kenneth H. Goodrich, 1990

- <sup>16</sup> McManus, 1990

<sup>17</sup> Ibid.

## Chapter 2

## The Blackboard Problem-solving model

This chapter presents a historical overview of the development of the blackboard model, an overview of concurrent blackboard systems, and some of the issues involved in designing and implementing a parallel or distributed blackboard systems.

### 2.1 The Blackboard Model

The basic concepts of the blackboard problem-solving model were first presented in 1962 by Allen Newell. Newell describes the following model of problem solving:

"Metaphorically we can think of a set of workers, all looking at the same blackboard: each is able to read everything that is on it, and to judge when he has something worthwhile to add to it. This conception is just that of Selfridge's Pandemonium<sup>1</sup>: a set of daemons, each independently looking at the total situation and shrieking in proportion to what they see that fits their natures..."<sup>2</sup>

The problem solving technique outlined by Newell, and in Simon's paper on information processing theory<sup>3</sup> are the basis of the blackboard problem-solving model.<sup>4</sup> The concepts presented by Newell led to the development of the production system problem-solving approach, and were later used in the development of the OPS 5 system.

A blackboard system consists of a set of knowledge sources, a blackboard data structure, and an opportunistic control strategy used to activate the knowledge sources. The control strategy is termed "opportunistic" due to the self-activating nature of the knowledge sources. Each knowledge source monitors the blackboard and activates itself based on the state of the blackboard. The blackboard model of problem solving is best described by H. Penny Nii.

"A Blackboard System can be viewed as a collection of intelligent agents who are gathered around a blackboard, looking at pieces of information written on it, thinking about the current state of the solution, and writing their conclusions on the blackboard as they generate them." 5

The blackboard is a centralized global data structure, often partitioned in a hierarchical manner, used to represent the problem domain. The blackboard is also used to allow inter-knowledge source communication and acts as a shared memory

visible to all of the knowledge sources. This design allows for opportunistic problem solving and allows a knowledge source to contribute towards the solution of the current problem without knowing which of the other knowledge sources will use the information. The use of opportunistic problem solving allows the data transfers on the blackboard to determine which processes are active at a given time. The use of an opportunistic data—driven control structure, and highly specialized knowledge sources allows a set of knowledge sources to cooperate to solve large, complex problems.

The blackboard problem-solving model is an evolution of the rule-based/expert system model of problem solving that seeks to build on the inherent strengths of those systems.

- Knowledge sources should be highly specialized and highly

independent. This allows several rule-based/expert systems to

cooperate to solve problems that are larger than can be managed by a

single expert system. Specialization and independence provide modular

protection, restricting the effect of a rule firing to the knowledge source

it fires in.

- The control of rule application in a blackboard system is distributed

across the set of knowledge sources. Conflict resolution is carried out at

the blackboard level instead of being centralized in one rule base.

- A different inference engine and knowledge representation scheme can

be selected for each knowledge source. This allows each knowledge

source to use the knowledge representation scheme and

problem-solving strategy best suited to solve its subset of the problem.

- Blackboard systems provide for parallel execution of the knowledge sources. This parallel execution of the separate knowledge sources cannot be modeled in a rule—based system using a single rule base without having a set of rules in the rule base whose only purpose is to order the firing of other rules. The addition of the "sequencing" rules violates the basic principle that the rules in a rule-based system are not serialized and can fire in any order.

## 2.2 Description of the Blackboard Model

Due to the hierarchical structure of the blackboard, each data object on the blackboard will usually have only one knowledge source that can update it. It is important to note that although knowledge sources are often referred to as "experts", knowledge sources are not restricted to Expert Systems or other AI systems. Many knowledge sources are numeric or algorithmic in nature. The use of multiple, independent knowledge sources allows each knowledge source to use the data representation scheme and problem-solving strategy that best suit the specific purpose of the knowledge source. The use of independent knowledge sources also provides for modular protection between knowledge sources. A change in the functionality of one knowledge source cannot effect the function of another knowledge source.

Penny Nii and others<sup>6,7,8</sup> have delineated three properties that the knowledge sources of a blackboard system should possess:

- Knowledge sources can see everything on the blackboard at all times, and what they see represents the current state of the solution. This implies the ability to do concurrent atomic reads.

- 2) Knowledge sources can write their conclusions on the blackboard at any time without getting in the way of any other knowledge sources. This implies the ability to do concurrent writes to the blackboard.

- 3) The act of writing on the blackboard will not confuse any other knowledge sources. This implies that serializability is maintained and that write operations are atomic.

The implication of these properties is that a single problem is being solved asynchronously, in parallel, with no memory contention. This is not the case in serial implementations of blackboard systems. Most serial blackboard systems, including the early versions of Paladin<sup>9</sup>, modify the blackboard system problem-solving model in such a way that it cannot be executed in parallel. Knowledge sources are treated as schedulable entities that are queued for execution, with only one knowledge source executing at a time. This modification to the blackboard model requires the additional overhead of adding a centralized control mechanism to handle the scheduling and execution of the knowledge source.

Serial blackboard systems implement the blackboard data structure as an interconnected data structure that is not globally visible to all of the knowledge sources at all times. These systems make the assumption that the knowledge source execution sequence selected by the control module preserves the consistency of the blackboard. Although serial blackboard systems remove the concurrency described in the model by allowing only one knowledge source to execute at a time, the use of the shared blackboard data structure still allows opportunistic problem solving.

These constraints and modifications to the blackboard model must be removed for the promise of the model to be fully realized. Current research in the area of blackboard systems centers on the development of concurrent blackboard systems that allow the knowledge sources to execute concurrently.

## 2.3 Concurrent Blackboard Systems

The development of concurrent blackboard systems requires a combination of expertise and tools from the AI field and from the Operating Systems/Concurrency Control fields. Past research on concurrent blackboard systems has lacked this global approach and has not realized the full potential of concurrent blackboard systems.

There are two major motivations for developing concurrent blackboard systems. The first, and most obvious motivation, is that properly implemented concurrent blackboard systems will outperform existing rule-based systems, expert systems, and serial blackboard systems. Concurrent blackboards also deliver more processing power than can be obtained in a uniprocessing environment. This increase in processing power allows the solution of larger and more complex problems. The second motivation is to allow the system designers to integrate a network of computers, each best suited to execute a specific type of knowledge source, into a single problem solving approach. An example of such a system is a heterogeneous network consisting of conventional architecture machines (VAX 3200<sup>TM</sup>, Sun SPARC<sup>TM</sup>) for numeric processing, specialized AI hardware for symbolic processing, and a shared memory parallel processing machine to host the blackboard. This type of network allows each knowledge source to be implemented in a computationally favorable environment and programming language.

#### 2.3.1 Performance Issues

There are several factors that can affect the performance of concurrent blackboard systems. The four most common are listed below. This list will be used as a reference when discussing the performance of existing blackboard systems later in this chapter.

- Contention for shared data and shared resources.

- The cost of communications in a multiprocessor system. Several

current blackboard systems, including Concurrent-CLAWS<sup>10</sup>, have

demonstrated that message-passing costs, including message creation

and receipt costs, and the finite bandwidth of the communication

network, can become a significant portion of the system's execution

time.

- Maintaining semantic consistency. Semantic consistency requires that

the inputs to a knowledge source do not change during the time in

which the knowledge source performs its problem-solving activities and

places its results onto the blackboard.

- Process creation and management costs. These costs are significant only for systems that dynamically create and delete processes. Corkill¹¹¹ outlines the problems with this type of approach and with the use of time-sliced multiplexing of knowledge sources. The major problem with time-slicing is blackboard consistency. Changes can be made to the blackboard while a knowledge source is paused that affect the computation of the paused knowledge source. Corkill presents two "simple" approaches to overcoming this problem. Both are computationally expensive and can lead to systems where little progress is made due to the overhead of blackboard consistency recovery. Corkill states that "dealing with multiplexed knowledge source executions in a uniprocessor environment has not been worth the effort."¹²

## 2.3.2 Opportunities for Concurrent Execution

There are many levels in blackboard systems at which concurrency can be exploited. Concurrency is found at the application level, where the designer must

recognize and exploit the inherently concurrent features of the problem being solved. It is important to consider the grain size of the tasks being executed concurrently to insure that the performance gains outweigh the cost of implementing concurrent knowledge source execution.

Concurrency can also be exploited at a lower level if a language with built-in parallel-processing constructs, such as vector operations, can be applied to the problem. In the case of blackboard systems, it is also important to find a language that supports frame-based or object-oriented programming features to ease implementation of the blackboard data structure. One of the driving factors in designing a blackboard system is the type or types of hardware the system will be implemented on. This decision lays the architectural framework for the system and may constrain other features such as programming language selection.

Current research has outlined many options for exploiting parallelism in blackboard systems. The following list is presented as a introduction to some of these options. More detailed descriptions of how an option is implemented follow in the sections describing parallel and distributed implementations of blackboard systems.

- 1) Knowledge Parallelism: This exploits the ability to run multiple instances of a knowledge source in parallel.

- 2) Pipeline Parallelism: Data flow through levels in the blackboard is used to create execution pipelines.

- 3) Data Parallelism: Create partitions in the blackboard and distribute them so that different knowledge sources can concurrently access the blackboard data structure partitions and execute in parallel.

- 4) Control Concurrency: Allow the control element to execute concurrently with the knowledge sources.

- 5) Rule Execution: This allows several (or all) rules in an active knowledge source to be executed concurrently.

- 6) Blackboard Internals: Allowing concurrent object creation, deletion, retrieval, and modification.

## 2.3.3 Multiple Instances of a Knowledge Source

Several systems <sup>13,14</sup> have proposed the use of multiple instances of a knowledge source. The use of multiple instances of a knowledge source may lead to significant data coherence problems on the blackboard data structure. There are two commonly used ways to implement multiple instances of a knowledge source.

Instances of knowledge sources can be partitioned into parallel execution pipelines.

Pipelining knowledge sources requires data parallelism on the blackboard. Pipelining is implemented by developing knowledge source pipelines and having each pipeline execute on a unique set of input data. The use of unique sets of inputs and outputs for each knowledge source pipeline protects the system from data coherence problems.

Individual instances of the knowledge source can run in parallel.

Several systems claim to allow multiple instances of a single knowledge source to execute concurrently. These systems all use a serial control component to activate knowledge sources. The serial control structure allows a single knowledge source to execute at any given time, protecting the system from memory coherence problems. If the knowledge sources are not pipelined and they are allowed to execute concurrently severe data coherence problems can result. Without pipelines it is difficult to insure that a knowledge source does not interfere with another activation of that knowledge source, and that instances of a knowledge source do not attempt to update the same blackboard data object. The effect of allowing multiple instances of a knowledge source in the blackboard model of problem solving is discussed in detail in Chapter Three.

## 2.4 Types of Concurrent Blackboard Systems

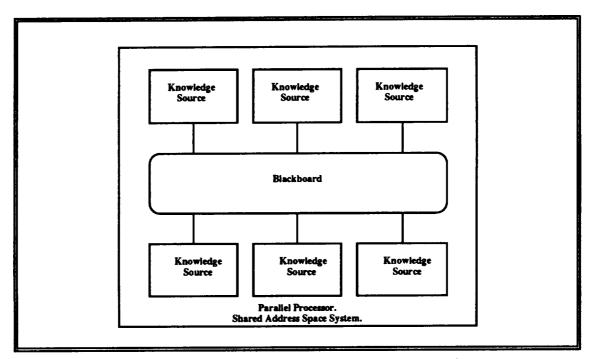

Concurrent blackboard systems can be partitioned into two classes: parallel blackboard systems and distributed blackboard systems. Parallel blackboard systems are developed for multiprocessor shared memory architectures and distributed blackboard systems are developed for distributed memory, message-passing architectures.

### 2.4.1 Parallel Blackboard Systems

Parallel blackboard systems(Figure 2.1) stress the concurrent execution of knowledge sources and the blackboard control components in a shared address space. As outlined by Corkill<sup>15</sup>, the major point of concern in parallel blackboard systems is the potential for asynchronous modifications to the blackboard by concurrently executing knowledge sources. These modifications may invalidate the results of other executing knowledge sources. Concurrency in parallel blackboard systems is also restricted by the use of a single, centralized control module. Nii states

"A centralized controller drastically limits speedup, and knowledge source invocation should be distributed without synchronization." <sup>16</sup>

Figure 2.1. Parallel Blackboard System Schematic

## 2.4.1.1 The Cage Architecture

Rice, Aiello, and Nii<sup>17</sup> developed the Cage system. Cage extends the serial Attempt to GEneralize (AGE) system allowing for parallel execution of its applications components. The system allows for concurrent knowledge source execution, concurrent rule execution, and concurrent rule clause execution.

Two types of knowledge source concurrency exist in Cage. Multiple knowledge sources can execute on different levels of the blackboard data structure, or multiple

instances of a knowledge source can execute on different data objects on the same level of the blackboard. Multiple instances of a knowledge source executing concurrently are used to form execution pipelines that flow data up the blackboard data structure. Cage supports synchronized knowledge source execution. The synchronization is managed by the blackboard control structure. If synchronization is used, knowledge sources are held at a barrier until all previously selected knowledge sources complete execution. When no synchronization is used, knowledge sources execute when they are triggered.

The researchers investigated the use of concurrency at the rule execution level using a simulated parallel hardware environment. The condition clauses for all of the rules in the active knowledge sources were evaluated in parallel and the appropriate action clauses were executed in parallel. This sequence can be executed with or without synchronization between the evaluation of the condition clauses. When synchronization is used, it is implemented using barrier synchronization primitives.

Concurrent rule execution did not achieve the expected execution speedups. The cost of the barrier synchronization, the memory contention caused by the parallel execution of the condition clauses, the lack of a regular or "normal" rule form, and the lack of hardware support introduced overhead that outweighed the speedup gains possible with concurrent rule execution. This concept does not show promise for achieving speedup unless hardware support for concurrent rule execution is developed, and a normalized rule form is used to express knowledge in the knowledge sources.

Cage knowledge sources use atomic read and write operations to insure data coherence. The researchers discovered that a detailed specification of a knowledge source's activation conditions is required for concurrent blackboard systems. This is caused by the asynchronous operation of the knowledge sources. Cage uses complex preconditions to ensure that it is appropriate to activate a knowledge source and implements "conditional actions" to protect the system from race conditions. A conditional action tests the value of a data object before the data object is updated.

#### 2.4.1.2 Shared Memory Blackboard Approach

Daniel Corkill<sup>18</sup> discusses several approaches to executing knowledge sources concurrently on a shared memory architecture and then proposes a Shared Memory Blackboard Approach. The first approach Corkill presents executes each knowledge source as an uninterruptable task. This approach can result in both memory contention

and resource allocation bottlenecks. The second approach Corkill discusses is time slicing the execution of the knowledge sources. Each knowledge source creates a "local" copy of all blackboard elements required for execution. This approach has several faults, including the introduction of context switching costs and other operating system overhead into the system execution time. The final approach discussed is to treat an entire knowledge source activation as an atomic operation. This approach requires the ability to treat blackboard objects, and even whole regions of the blackboard, as "allocatable resources" that can be locked for either exclusive access or for read-only access. This system places the responsibility for deadlock prevention on the programmer. Locking blackboard objects and regions is computationally expensive and can cause knowledge source blocking due to memory contention.

Corkill's shared memory blackboard approach allows each processor to directly access the shared blackboard data structure. Corkill proposes two ways to map the knowledge sources of a blackboard system to the available processors. He presents a functional mapping and a computational server mapping.

In the functional mapping approach each type of knowledge source is assigned to a specific processor. If multiple instances of a knowledge source are required the additional instances are queued for execution on the processor. This approach is suited for heterogeneous computer networks where different knowledge sources execute on specialized processors. The main problem with this approach is that processing demands may not be uniform. This will result in some processors being overloaded, with several instances of a knowledge source queued for execution, while other processors may be setting idle.

The computational server model is suited for a homogeneous computer network. Knowledge source activations are queued for execution. When a processor completes execution of a knowledge source it selects the highest rated knowledge source activation from the activation queue. This approach results in better load balancing across the network, but requires that all knowledge sources can be executed by all processors. Corkill outlines a way to extend the computational server model to heterogeneous networks. An activation queue is created for each type of processor in the network and knowledge sources are queued according to their processing requirements.

The implementation of Corkill's shared memory blackboard approach supports both object and region locking. Locks are ordered before they are acquired. If a lock cannot be acquired the process blocks waiting for that lock. Integrating blackboard monitoring and control requires determining which processes are responsible for which activities. The control shells define event handlers that are used by the processes to handle the initialization tasks associated with an event. The event handlers must be defined to interact correctly with the multiprocessing control shell. No performance data for the shared memory blackboard approach was presented.

### 2.4.1.3 The Agora System

Roberto Bisiani<sup>19</sup> developed the Agora system to support the ANGEL speech recognition system. ANGEL consists of four loosely connected blackboard subsystems communicating through a centralized blackboard data structure. A pipelining control structure is used to activate the blackboard subsystems. Bisiani stresses that each blackboard subsystem has different performance and hardware requirements. The use of a blackboard problem solving structure provides software engineering support by decoupling the system integration mechanisms from the behavior of the knowledge sources.

The Agora system supports the concept of Shared Data Types (SDT). The knowledge sources in Agora communicate via shared access to the blackboard data objects. The data objects are strongly typed and can only be accessed by used defined accessor functions. Data objects can be created dynamically, and modifications to the object are reported to all interested knowledge sources. Data object sharing is used to insure that data objects are consistent and accessible across processor boundaries.

SDT's are abstract data types consisting of two elements. Data definitions specify the structure of the data elements, and accessor functions specify the available operations for instances of the data type. An instance of an SDT is referred to as a Shared Data Structure (SDS). Agora provides a set of basic accessor functions for managing SDS's. Knowledge sources are activated when they receive an activation request posted from another knowledge source. When an SDS is modified the knowledge source updating the SDS sends an activation message to all knowledge sources that "have declared an interest" in the SDS. The activation operations are managed by the Agora system, not by the applications programmer.

Bisiani presents a unique memory management scheme to reduce hotspots in memory. Agora uses a write-once memory management system. The use of a write-once memory management system removes the need for blackboard data element read locking. This allows read operations to return stale data. The programmer is required to implement any protocols required to prevent stale data from being read by a knowledge source.

The write once memory management system implemented by Agora is extraordinarily memory expensive. Additional system overhead is required to support either "stop and wait" or "background" garbage collection. Memory coherence problems can occur if the user does not implement the memory coherence protocols correctly, or if no protocols are implemented. The cost of the background garbage collection and the memory coherence protocols may outweigh any performance gains achieved by Agora. Only minimal performance data was presented for the Agora system.

#### 2.4.2 Conclusions

The systems discussed above approach the problems presented by shared memory parallel blackboard systems from many different perspectives. The Cage system and Corkill's Shared Memory Blackboard face bottlenecks at the shared blackboard data structure. The lack of two-phase locking protocols cause knowledge source serializability problems. The Agora systems uses its write-once memory management scheme to avoid memory contention problems, but allows access to stale data and adds the overhead of the garbage collection system. A successful blackboard system implementation must support knowledge source pipelining and two-phase locking protocols, and reduce memory contention on the blackboard data structure.

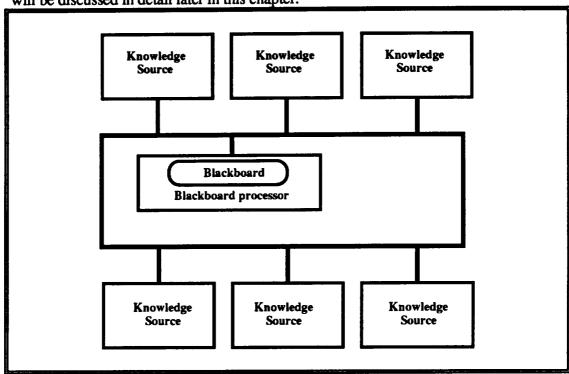

# 2.5 Distributed Blackboard Systems

Distributed blackboard systems are designed to use a distributed, message-passing architecture. This design allows blackboard data to be communicated among autonomous blackboard subsystems or knowledge sources. The major issue in designing a distributed blackboard system is deciding what information to communicate, where to store it, and when and where to send it.

The are two types of distributed blackboard systems. The first type of distributed blackboard system, shown in figure 2.2, uses a centralized blackboard data structure

that is accessed by a set of distributed knowledge sources. The second type, shown in figure 2.3, distributes the blackboard data structure, allowing each knowledge source direct access to some part of the blackboard data structure. Systems that distribute the blackboard data structure have additional data coherence problems not found in centralized blackboard based systems, and in many cases violate the fundamental requirement that all knowledge sources can see and access all of the blackboard data objects at all times. Several systems that use a distributed blackboard data structure

will be discussed in detail later in this chapter.

Figure 2.2. Distributed Blackboard System with Centralized Blackboard Data Structure

Figure 2.3. Distributed Blackboard System with Distributed Blackboard Data Structure

#### 2.5.1 Centralized Blackboard Data Structure

How a problem is distributed across the available hardware platforms and how tightly the knowledge sources are coupled has a significant impact on the system's performance. Currently, no techniques exist to aid the designer in decomposing a problem into a set of knowledge sources and in evaluating the preliminary design. If the knowledge sources are tightly coupled, a large number of messages will be passed and blackboard consistency becomes a major concern. If the knowledge sources are highly independent but share large amounts of data, communication delays will limit concurrency as nodes are forced to wait for information.

#### 2.5.1.1 Poligon

Rice, Aiello and Nii<sup>20</sup> present several options for gaining speedups in a distributed blackboard system.

- 1) Eliminate the centralized scheduling mechanism

- 2) Optimize system design for a distributed memory, message-passing hardware

- 3) Distribute the data across the blackboard to reduce hotspots

Items one and three are directly applicable to both parallel blackboard systems and distributed blackboard systems. Item two is not a trivial task due to the lack of existing algorithms or tools to perform the optimization. In many cases, the execution of the system's knowledge sources is so irregular, due in part to the use of opportunistic problem solving techniques, that a complete optimization is not possible.

Poligon<sup>21</sup> is based on a distributed memory hardware model when each processor is viewed as a blackboard node. They define a blackboard node as follows:

"a blackboard node is a process on a processor, surrounded by a collection of processors able to service its requests to execute rules."22

The implicit assumption in this definition is that all knowledge sources are rule—based systems. This assumption may severely limit the performance of systems implemented using Poligon, and limits the types of problems it is suited to address. Poligon provides no user accessible data locks, nodes are automatically locked during read and write operations. The blackboard architecture is designed to prevent deadlock from occuring, but livelock can still occur. Processing nodes are capable of evaluating their own performance. The nodes assess each request to modify their local state. The node determines if it should perform the update or take other action based on its progress towards solving the current problem.

Rice, Aiello and Nii draw several conclusions from their experiments using Poligon. Their first conclusion is:

"The difficulty of implementation of applications is due largely to the divergence of implementations of serial blackboard systems from the pure blackboard model in order to make implementation and programming more manageable."<sup>23</sup>

They state that the applications they tested did not have enough data parallelism to support pipeline parallelism so the effect of pipeline parallelism could not be fully evaluated. Data communication costs were not viewed as being excessive, as long as data flowed through the pipelines. Hardware supporting a non-blocking message passing protocol was used for communication. This type of protocol supports high speed data transfers but may result in data inconsistencies. The final point presented may be the most important:

#### CHAPTER 2. The Blackboard Problem Solving Model

"The use of a central controller to determine which knowledge sources to run in parallel drastically limited the speedup possible, no matter how many knowledge sources were executed in parallel."24

#### 2.5.1.2 The Blackboard Server Approach

Daniel Corkill<sup>25</sup> also describes a blackboard server approach to developing a distributed blackboard system. The blackboard server approach implements a centralized shared blackboard. The approach does not allow multiple access paths to the blackboard and maintains a single version of each blackboard data object. The blackboard is divided into non-overlapping blackboard responsibility areas and a unique blackboard server is allocated to each area. The knowledge sources send all blackboard interaction requests to the appropriate server, which then queues the request for processing. This implementation requires that all knowledge sources know which blackboard server handles which specific data elements on the blackboard. Corkill discusses two blackboard partitioning extremes. In one case a single node can act as a server for the whole blackboard. In the other extreme a node can be assigned to act as a server for a disjoint section of the blackboard. The correct balance between these two extremes for each unique application may be difficult to determine. If the required message routing information is not made available to all of the knowledge sources, then all of the data is not visible to all of the knowledge sources and opportunistic problem solving performance will degrade.

The blackboard server approach may also suffer from several performance problems. If hotspots in memory occur, some blackboard servers may become overloaded while others are idle. Queuing the memory requests adds a serialized component to the memory access system and additional system overhead. The blackboard server approach outlined by Corkill is based on some partitioning of blackboard data structure. It may be more efficient to assign a unique knowledge source server to each knowledge source. Assigning a unique knowledge source server does not require message routing information and should reduces hotspots on the blackboard. This does not require queuing of blackboard data requests and the associated system overhead.

#### 2.5.2 Distributed Blackboard Data Structure

To incorporate message-passing into a distributed blackboard system the central blackboard controller must handle all incoming data requests. This requirement is

nontrivial and may reduce the use of opportunistic problem solving by forcing serialized message handling, creating a bottleneck at the blackboard. Several methods of distributing the blackboard data structure have been proposed to address this problem.

Distributing the blackboard data structure introduces several subtle changes in the way knowledge sources function. One added requirement is that some entity, either the blackboard controller or the knowledge sources themselves, must know where all of the data a knowledge source requires can be found, and who the knowledge source must notify when it completes execution. Without the use of specialized knowledge source organization and knowledge source connectivity analysis techniques, the affect of this requirement cannot be assessed during the system design phase. This requirement is nontrivial and may reduce the use of opportunistic problem solving by forcing lockstep execution of knowledge sources.

## 2.5.2.1 Functionally Accurate, Cooperative Communication

. .

To address problems caused by having a distributed blackboard data structure Lesser and Corkill<sup>26</sup> have proposed a Functionally Accurate, Cooperative (FA/C) communication system for building distributed blackboard systems. The system utilizes cooperating instances of a blackboard system running concurrently and communicating using a global blackboard. Each knowledge source, or processing node, can be viewed as an instance of a blackboard system. "Functionally accurate" refers to the ability of the system to generate "acceptably accurate" solutions without requiring that all of the intermediate results shared by the knowledge sources (processing nodes) are correct and consistent. "Cooperative" refers to the iterative style of knowledge source interaction. Each knowledge source produces tentative results that may be incorrect, incomplete, or inconsistent with the tentative results produced by other knowledge sources. Consistencies between the tentative results can be seen as reinforcing the results produced by the other knowledge sources. The hope of this approach is that significantly less communication is required to exchange tentative results instead of passing all of the raw data and processing the results. Blocking and synchronization overhead can be reduced or eliminated. This should increase parallelism and opportunistic problem solving. FA/C was developed to address the problem of maintaining semantic consistency on the blackboard data structure. No test results were presented that measured the effectiveness and cost of implementing this

type of system, but FA/C communication does show some potential for reducing message-passing costs and "lockstep" style system execution.

#### 2.5.2.2 The Distributed Blackboard Approach

In the distributed blackboard approach Corkill<sup>27</sup> describes a system where each processing node has a separate local blackboard that contains the local data objects and copies of all data objects received from other nodes. The distribution of the blackboard data objects is an important design consideration for this type of system. The user must decide if local blackboard data structures will "overlap" and on the level blackboard data object consistency that will be implemented. Blackboard data structures "overlap" if two or more blackboard data structures have a copy of a blackboard data object.

There is a direct relationship between the degree of overlap of the blackboard data structures and the communications costs required to maintain blackboard data object consistency. Allowing blackboard data objects to overlap increases the cost of maintaining blackboard data structure consistency. An update message must be sent to each node that "shares" a blackboard data object. Blackboard overlap also increases the chance that nodes will process inconsistent data, resulting in an incorrect conclusion.

The benefit of not allowing backboard data structures to overlap is that a single copy of each blackboard data object exists making blackboard consistency easier to maintain. This data-object sharing approach results in increased communication costs if a large number of nodes share data objects. Each node has to generate a request for a data object stored on a non-local node every time the data object is needed. These communications costs can become a significant part on a node's execution time. It is clear that the amount of blackboard overlap and the required level of blackboard consistency directly affect a systems communications costs and overall performance. Design, simulation, and analysis techniques are required to balance these costs before a system is implemented. Inter-node communications costs and the cost of blackboard consistency are a function of the implementation of a distributed blackboard data structure, and are not inherent in the blackboard system problem solving paradigm.

#### 2.5.2.3 "Virtual" Blackboard Systems

V. Jagannathan<sup>28</sup> proposes a "Virtual Blackboard" for reducing communication costs when using a distributed blackboard data structure. In this model, all of the