11-22 Bern Barrow

Abstract for submission to MRS 1998 Spring Meeting, April 13-17, San Francisco, CA Symposium F: Wide-Bandgap Semiconductors for High Power, High Frequency and High Temperature

1 **4 4** 4

## NON-MICROPIPE DISLOCATIONS IN 4H-SIC DEVICES: ELECTRICAL PROPERTIES AND DEVICE TECHNOLOGY IMPLICATIONS

# Philip G. Neudeck, NASA Lewis Research Center, Cleveland, OH; Wei Huang, Michael Dudley, State University of New York at Stony Brook, NY; Christian Fazi, U.S. Army Research Laboratory, Adelphi, MD.

It is well-known that SiC wafer quality deficiencies are delaying the realization of outstandingly superior 4H-SiC power electronics. While efforts to date have centered on eradicating micropipes (i.e., hollow core super-screw dislocations with Burgers vectors  $\geq 2c$ ), 4H-SiC wafers and epilayers also contain elementary screw dislocations (i.e., Burgers vector = 1c with no hollow core) in densities on the order of thousands per cm<sup>2</sup>, nearly 100-fold micropipe densities. While not nearly as detrimental to SiC device performance as micropipes, it has recently been demonstrated that elementary screw dislocations somewhat degrade the reverse leakage and breakdown properties of 4H-SiC p<sup>+</sup>n diodes. Diodes containing elementary screw dislocations exhibited a 5% to 35% reduction in breakdown voltage, higher pre-breakdown reverse leakage current, softer reverse breakdown I-V knee, and microplasmic breakdown current filaments that were non-catastrophic as measured under high series resistance biasing. This paper details continuing experimental and theoretical investigations into the electrical properties of 4H-SiC elementary screw dislocations. The nonuniform breakdown behavior of 4H-SiC p<sup>+</sup>n junctions containing elementary screw dislocations exhibits interesting physical parallels with nonuniform breakdown phenomena previously observed in other semiconductor materials. Based upon experimentally observed dislocation-assisted breakdown, a re-assessment of wellknown physical models relating power device reliability to junction breakdown has been undertaken for 4H-SiC. The potential impact of these elementary screw dislocation defects on the performance and reliability of various 4H-SiC device technologies being developed for high-power applications will be discussed.

## NON-MICROPIPE DISLOCATIONS IN 4H-Si( DEVICES: ELECTRICAL PROPERTIES AND DEVICE TECHNOLOGY IMPLICATIONS

P. G. NEUDECK\*, W. HUANG\*\*, M. DUDLEY\*\*, AND C. FAZI\*\*\* \*NASA Lewis Research Center, M.S. 77-1, 21000 Brookpark Rd., Cleveland, OH 44135 \*\*Dept. of Materials Science & Engineering, SUNY, Stony Brook, NY 11794 \*\*\*U.S. Army Research Laboratory, Adelphi, MD 20783

#### ABSTRACT

It is well-known that SiC wafer quality deficiencies are delaying the realization of outstandingly superior 4H-SiC power electronics. While efforts to date have centered on eradicating micropipes (i.e., hollow core super-screw dislocations with Burgers vectors > 2c), 4H-SiC wafers and epilayers also contain elementary screw dislocations (i.e., Burgers vector = 1c with no hollow core) in densities on the order of thousands per cm<sup>2</sup>, nearly 100-fold micropipe densities. While not nearly as detrimental to SiC device performance as micropipes, it has been previously shown that diodes containing elementary screw dislocations exhibit a 5% to 35% reduction in breakdown voltage, higher pre-breakdown reverse leakage current, softer reverse breakdown I-V knee, and concentrated microplasmic breakdown current filaments when measured under DC testing conditions. This paper details the impact of elementary screw dislocations on the experimentally observed reverse-breakdown pulse-failure characteristics of low-voltage (< 250 V) small-area (< 5 x 10<sup>-4</sup> cm<sup>2</sup>) 4H-SiC p<sup>+</sup>n diodes. The presence of elementary screw dislocations did not significantly affect the failure properties of these diodes when subjected to non-adiabatic breakdown-bias pulsewidths ranging from 0.1 µs to 20 µs in duration. Diodes with and without elementary screw dislocations exhibited positive temperature coefficient of breakdown voltage and high junction failure power densities well above the failure power densities exhibited by highly reliable silicon power rectifiers. This preliminary result, based on measurements from one wafer of SiC diodes, suggests that highly reliable low-voltage SiC rectifiers may be attainable despite the presence of elementary screw dislocations.

### INTRODUCTION

It is widely recognized that material quality deficiencies are the primary reason why SiC highpower devices cannot be realized at present. While small-current, small-area high-voltage (1-5 kV) SiC devices are being prototyped and tested, the high densities of crystallographic defects in SiC wafers prohibits the attainment of SiC devices with very high operating currents (> 50 A) that are commonly obtainable in silicon-based high-power electronics [1, 2]. Micropipe defects are clearly very detrimental to electrical device performance, as these defects cause premature breakdown point-failures in SiC high-field devices fabricated in 4H- and 6H-SiC c-axis crystals with and without epilayers [2]. Commercial 4H- and 6H-SiC wafers and epilayers also contain elementary screw dislocations (i.e., Burgers vector = 1c with no hollow core) in densities on the order of thousands per cm<sup>2</sup>, nearly 100-fold micropipe densities [3-6]. Because of the non-terminating behavior of screw dislocations, both hollow-core (micropipes) and non-hollow-core (elementary) screw dislocations and associated crystal lattice stresses are replicated in subsequently grown SiC epilayers [7, 8].

The electrical impact of elementary screw dislocation defects on SiC device performance has largely been overlooked while attention has focused on eradicating SiC micropipes. However, as SiC micropipe densities fall below 1 per cm<sup>2</sup> in the best reported wafers [9], the operational effects of elementary screw dislocations must now be considered. While not nearly as detrimental to SiC device performance as micropipes, it has recently been demonstrated that elementary screw dislocations somewhat degrade the reverse leakage and breakdown properties of 4H-SiC p<sup>+</sup>n diodes [10]. Diodes containing elementary screw dislocations exhibited a 5% to 35% reduction in breakdown voltage, higher pre-breakdown reverse leakage current, softer reverse breakdown I-V knee, and highly localized microplasmic breakdown current filaments.

Localized breakdowns and high-current filaments at junction hotspots are undesirable in silicon-based solid-state power devices. In operational practice, silicon power devices that

uniformly distribute breakdown current over the entire junction area exhibit much greater reliability than silicon devices that manifest localized breakdown behavior. This is because silicon devices that avoid localized junction breakdown exhibit larger Safe Operating Areas (SOA's) and can much better withstand repeated fast-switching stresses and transient overvoltage glitches that arise in high-power systems [11-14]. Positive temperature coefficient of breakdown voltage (PTCBV), a standard behavior in silicon power devices free of crystal dislocation defects, helps insure that current flow is distributed uniformly throughout a device, instead of concentrated at high-current filaments. This enables silicon power rectifiers to exhibit a high energy to thermal junction failure when subjected to transient breakdown or switching bias conditions in which voltage and current are simultaneously large in the device. It is generally accepted that power rectifier SOA and reliability increases with increasing semiconductor junction energy to fail. Silicon junctions that suffer localized breakdown due to the presence of crystal dislocation defects do not generally exhibit sufficient energy to fail characteristics to be considered reliable for use in high-power

Before SiC can become feasible for widespread incorporation into high-power systems, SiC power devices must demonstrate at least equal, if not superior, reliability characteristics as presentday dislocation-free silicon power devices. Therefore, SiC power devices must demonstrate at least equal, if not superior, SOA's and immunity to switching and overvoltage stresses as silicon power devices. Since all appreciable current (> 1 A) SiC power devices are virtually guaranteed to contain elementary screw dislocations, it is important to ascertain the junction breakdown and energy-tofail characteristics of SiC diodes with elementary screw dislocations. The study reported in this paper quantitatively compares (to first order) theoretical and experimentally measured energy-to-fail characteristics of 4H-SiC p<sup>+</sup>n junction diodes, with and without screw dislocations, to the well-

## SILICON AND SILICON CARBIDE JUNCTION FAILURE THEORY

One method of measuring diode junction failure characteristics is to subject the device to highvoltage pulses that momentarily bias the device beyond its reverse breakdown voltage. As high breakdown current is drawn at high applied voltage, a large breakdown power is dissipated at the junction which quickly heats up the device. Pulses of increasing amplitude or duration are applied until a critical junction failure temperature  $T_m$  is reached, at which point the device is unrecoverably damaged. For short pulse durations between 0.1  $\mu$ s and 20  $\mu$ s in length, heat flow occurs almost exclusively from the active device junction into bulk semiconductor wafer substrate; heat flow from the substrate to the package is essentially negligible on this timescale. Wunsch and Bell [15] derived a general first-order approximation for the junction power density  $P_D$  (kW/cm<sup>2</sup>) applied over time t ( $\mu$ s) necessary for a device to reach a critical failure temperature T<sub>m</sub> from an initial starting temperature of Ti:

$$P_{\rm D} = \sqrt{\pi \,\kappa \,\rho \,C_{\rm p}} \left[ T_{\rm m} - T_{\rm i} \right] t^{-1/2} \, \rm kW/cm^2$$

where  $\kappa$  is the thermal conductivity (W/cm-K),  $\rho$  is the density (g/cm<sup>3</sup>), and C<sub>p</sub> is the specific heat of the semiconductor (J/gm-K). One choice for T<sub>m</sub> is the temperature at which intrinsic carriers exceed the junction doping leading to second breakdown [11]. Metal-semiconductor contact dependention can also limit the neak temperature a device can withstand without demage. For more degradation can also limit the peak temperature a device can withstand without damage. For more general first-order calculations that are independent of the junction doping and contact metallization,  $T_m$  is often set to the semiconductor Debye temperature  $T_D$ . The theoretical  $P_D$  vs. t curve calculated by Wunsch and Bell [15] for silicon using  $\rho = 2.33$  g/cm<sup>3</sup>,  $C_p = 0.7566$  J/gm-K,  $\kappa = 0.526$  W/cm-K,  $T_i = 298$  K,  $T_m = T_D = 948$  K is:

$$f_D = 1109 [t (\mu s)]^{-1/2} \text{ kW/cm}^2$$

## {Silicon Theoretical}

Wunsch and Bell found that (1) reasonably approximates the general junction failure behavior of a wide variety of experimental silicon rectifiers. However, the experimentally observed best fit to the  $P_D$  vs. t curve they observed for silicon rectifier diodes actually followed the relation [15]:

## $P_{\rm D} = 560 \ [t \ (\mu s)]^{-1/2} \ kW/cm^2$

4

which lies somewhat below the theoretical calculation (2). Silicon experimental studies also indicate that pulse shape does not significantly change experimental device failure power densities, so that average power density may be used as a good approximation when diode voltage and/or

current waveforms are non-constant over the pulse duration [14]. If current flow is focused through junction hotspots or defects, the effective power density, which is normalized to the total junction area instead of the hotspot junction area, will decrease

accordingly. For example, if current flow is focused through hotspots so that most of the current flows through only 10 % of the total junction area, the theoretical silicon  $P_D$  vs. t approximation (2) shifts downward to [15]: (4)

$$P = 110.9 [t (us)]^{-1/2} kW/cm^2$$

{Silicon 10 % Hotspot Theoretical}

Similar to the above first-order calculations for silicon rectifiers, theoretical  $P_D$  vs. t failure characteristics of 4H-SiC rectifiers can be estimated using basic SiC material properties. While specific heat and thermal conductivity are both functions of temperature, their temperature dependence has not been taken into account in these first-order calculations. Furthermore, there is inconsistency between the few SiC thermal properties that have been reported in the scientific literature. Nevertheless, basic "best-case" and "worst-case" combinations of thermal conductivity and specific heat can be calculated to roughly estimate upper and lower theoretical limits on the junction failure power densities that might be observed in defect-free 4H-SiC junctions. For both punction range power densities that might be observed in delect-nee 4ft-SiC junctions. For both calculations,  $\rho = 3.2 \text{ gm/cm}^3$ ,  $T_i = 298 \text{ K}$ , and  $T_m = T_D = 1120 \text{ K}$  [16] were used. The worst-case specific heat  $C_p = 0.3 \text{ J/gm-K}$  at 300 K is calculated using the simple Debye model described by Kittel [17]. A worst-case 4H-SiC thermal conductivity  $\kappa = 2 \text{ W/cm-K}$  is chosen based on Kittel [17]. A worst-case 4H-SiC thermal conductivity  $\kappa = 100 \text{ K}$  matrix meantly monoted in [0]. Combined into matrix (1) there was a matrix for the matrix for the matrix meantly monoted in [0]. measurements recently reported in [9]. Combined into relation (1) these worst-case material constants yield  $P_D$  vs. t relationship for 4H-SiC of:

$P_{\rm D} = 2014 [t (\mu s)]^{-1/2} \text{ kW/cm}^2$

(5) {SiC Worst Case Theoretical}

The best-case thermal conductivity  $\kappa = 4.9$  W/cm-K was chosen from Slack's measurements of 6H-SiC at 300 K [18]. The work of Zyweitz et. al. [16] suggests that the specific heat of 4H-SiC does not increase much beyond  $C_p = 1.0$  J/gm-K at temperatures above 600 K. Using these thermal parameters, the best-case first-order estimation of P us theorem. thermal parameters, the best-case first-order estimation of  $P_D$  vs. t becomes: (6)

$P_{\rm D} = 5755 [t (\mu s)]^{-1/2} \text{ kW/cm}^2$

{SiC Best Case Theoretical}

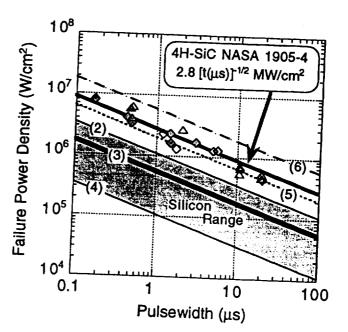

Theoretical relations (2) through (6) are plotted in Figure 2 for reference to experimental data presented in the following section.

## EXPERIMENT

Epitaxial mesa-isolated 4H-SiC  $p^*n$  junction diodes (n-doping between 2.5 x 10<sup>17</sup> to 1.5 x 10<sup>18</sup> cm<sup>-3</sup>) were fabricated on commercial 4H-SiC substrates as previously described in [10]. Nickel annealed at 1000 °C for 5 minutes in an argon tube furnace served as a backside contact, while an unannealed 300 Å Al / 1000 Å Ti / 2000 Å Al sandwich patterned by liftoff provided good ohmic

The presence or absence of screw dislocations in individual devices was conclusively contact to the degenerately doped  $p^+$  cap epilayer.

determined by examination of reverse I-V properties as demonstrated in [10]. A total of 17 circular diodes varying in size from 100  $\mu$ m in diameter to 250  $\mu$ m in diameter were pulse-tested to failure in this work, 6 of which contained no elementary screw dislocations. Devices were pulse tested on-wafer in near-dark conditions on a probing station equipped with coaxial probes. For pulse durations of less than 0.5 µs, the charge-line circuit described in [19] was employed to apply pulses and measure device voltage  $V_D(t)$  and current  $I_D(t)$  transient response. Longer bias pulses were supplied by a Velonex Model 350 pulse generator. Devices were subjected to manually triggered single-shot pulses of increasing pulse amplitudes and/or widths until device failure occurred. Between pulses, device I-V was checked for degradation using a standard 60 Hz curvetracer. Device failure was observed by sudden changes in the  $I_D(t)$  and  $V_D(t)$  response, degradation in the curve-tracer measured I-V, and physical changes in device appearance observed with the probe station microscope. Devices were sometimes tested immersed in Fluorinert FC-77 [20] to reduce the possibility of edge-related surface flashover [21], while others were tested in air.

Post-failure optical microscopic examination was carefully conducted on each damaged device. A few devices exhibited clear evidence of surface flashover failure near the mesa periphery. A few devices were totally obliterated similar to what is depicted in [22]. However, strong evidence of damage was confined to near-central regions of the device mesa away from the mesa edge and often away from where the probe tip contacted the diode.

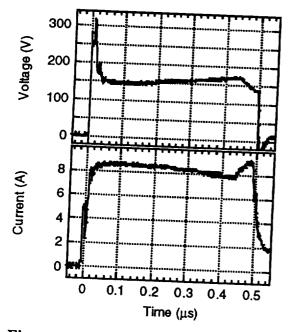

Figure 1 shows  $V_D(t)$  and  $I_D(t)$  traces of a typically observed device failure on a 200  $\mu$ m diameter device that contained screw dislocations and was tested immersed in Fluorinert. For the first 0.05  $\mu$ s of the pulse, the device exhibits negative temperature coefficient of breakdown voltage (NTCBV) behavior, as  $I_D(t)$  shows an initial increase while  $V_D(t)$  shows an initial decrease. However, the trend reverses to PTCBV behavior, as  $I_D(t)$  decreases and  $V_D(t)$  increases as the that 4H-SiC p<sup>+</sup>n junction diodes containing elementary screw dislocations can exhibit PTCBV

At t = 0.44  $\mu$ s, the device fails as evidenced by the onset of a sharp current increase coupled with voltage collapse prior to the falling edge of the 0.5  $\mu$ s bias pulse. Curve-tracer characterization immediately following the pulse confirmed the device failed to a resistive short-circuit during the Figure 1 pulse. An average device power density P<sub>D</sub> was calculated by averaging P(t) = V<sub>D</sub>(t) I<sub>D</sub>(t) over the pulse prior to failure and dividing by the total junction area. Thus the device withstood an average power density P<sub>D</sub> of 4.17 MW/cm<sup>2</sup> over a period of 0.44  $\mu$ s in Figure 1, which is one of the experimental data points plotted in Figure 2. Post-failure analysis of this device indicated physical damage in the near-central device region, with no evidence of edge-related breakdown failure.

Figure 1: Diode voltage  $V_D(t)$  and current  $I_D(t)$  transients recording the failure of a 200 µm diameter 4H-SiC p<sup>+</sup>n diode under pulse-breakdown testing. The diode fails at 0.44 µs, prior to the falling edge of the 0.5 µs bias pulse.

Figure 2: Average power density  $P_p$  vs. pulse bias duration t for device reverse breakdown failure. Experimental data points for NASA 4H-SiC p<sup>+</sup>n diode sample 1905-4 are plotted along with calculated approximations (2), (3), & (4) for silicon and (5) & (6) for 4H-SiC discussed in the main text.

Figure 2 shows all experimentally  $P_D$  vs. t failure data points collected in this study on devices whose DC-measured breakdown voltages ranged from 70 V to 220 V due to n-layer doping variation across the wafer. Diamond symbols on the plot represent devices that clearly exhibited bulk failure where exact failure times and power densities could be directly inferred from the  $V_D(t)$ and  $I_D(t)$  traces. Triangles represent data points that were collected from pulses in which a diode did not fail (failure occurred during a subsequent pulse), or from pulses where the diode failure occurred at the edge of a device mesa presumably due to surface flashover. Devices that contained no screw dislocations are denoted by open symbols, while filled symbols represent data collected from devices that contained at least one screw dislocation.

from devices that contained at least one screw dislocation. The experimentally observed failure data points plotted in Figure 2 are consistent with the t<sup>-12</sup> behavior predicted by Relation (1). The fit to the experimental data:

$P_{\rm p} = 2800 \,[t \,(\mu s)]^{-1/2} \,kW/cm^2$  {4H-SiC Experimental} (7)

falls between the theoretical 4H-SiC limits approximated in (5) and (6). Thus, these 4H-SiC parts can withstand pulse breakdown power densities approximately 5 times the power density that silicon diodes typically withstand before junction failure is reached. It is important to note that this preliminary data indicates that the presence or absence of elementary screw dislocations from a diode had no significant impact on the reverse failure energy of these low-voltage 4H-SiC diodes. Devices with and without screw dislocations exhibited comparable failure power densities to within the range of experimental scatter shown in Figure 2.

### CONCLUSION

The presence of elementary screw dislocations did not significantly affect the failure properties of low-voltage (< 250 V) 4H-SiC p<sup>+</sup>n junction diodes when subjected to non-adiabatic breakdownbias pulses. Diodes with and without elementary screw dislocations exhibited positive temperature coefficient of breakdown voltage and high junction failure power densities well above the failure power densities exhibited by highly reliable silicon power rectifiers. This preliminary result, based on measurements from one wafer of 4H-SiC p<sup>+</sup>n diodes, suggests that highly reliable low-voltage SiC rectifiers may be attainable in diodes that contain elementary screw dislocations. However, further studies are needed to ascertain the impact of screw dislocations on the failure properties of 4H- and 6H-SiC Schottky rectifiers, high-voltage (> 1 kV) p<sup>+</sup>n rectifiers, and other SiC device structures with significant bipolar gain such as thyristors and IGBT's.

## ACKNOWLEDGMENTS

The authors would like to gratefully acknowledge the assistance of D.J. Larkin, J. A. Powell, C. Salupo, G. Beheim, L. Keys, A. Trunek, J. Heisler of NASA Lewis Research Center. Work at NASA Lewis was carried out under joint funding from NASA Lewis Research Center and Defense Advanced Research Projects Agency (DARPA) Order #D149 (monitored by J. Alexander) and Order #E111/3 (monitored by E. Brown).

#### REFERENCES

- 1. P. G. Neudeck, J. Electron. Mater. 24 (4), 283-288 (1995).

- 2. P. G. Neudeck and J. A. Powell, IEEE Electron Device Lett. 15 (2), 63-65 (1994).

- 3. M. Dudley, S. Wang, W. Huang, C. H. Carter, Jr., and C. Fazi, J. Phys. D 28 A63-A68 (1995).

- S. Wang, M. Dudley, C. H. Carter, Jr., V. F. Tsvetkov, and C. Fazi in <u>Applications of Synchrotron Radiation Techniques to Materials Science</u>, edited by L. Terminello, N. Shinn, G. Ice, K. D'Amico, and D. Perry (Mater. Res. Soc. Proc. 375, Pittsburgh, PA 1995), pp. 281-286.

- 5. W. Si, M. Dudley, R. Glass, V. Tsvetkov, and C. H. Carter, Jr., J. Electron. Mater. 26 (3), 128-133 (1997).

- W. Si and M. Dudley in <u>Silicon Carbide. III-Nitrides. and Related Materials</u>, edited by G. Pensl, H. Morkoc, B. Monemar, and E. Janzen (Materials Science Forum 264-268, Trans Tech Publications, Switzerland 1998), pp. 429-432.

- 7. S. Wang, M. Dudley, C. H. Carter, Jr., and H. S. Kong in <u>Diamond. SiC and Nitride Wide</u> <u>Bandgap Semiconductors.</u> edited by C. H. Carter, Jr., G. Gildenblat, S. Nakamura, and R. J. Nemanich (Mater. Res. Soc. Proc. 339, Pittsburgh, PA 1994), pp. 735-740.

- J. A. Powell, D. J. Larkin, P. G. Neudeck, J. W. Yang, and P. Pirouz in <u>Silicon Carbide and Related Materials</u>, edited by M. G. Spencer, R. P. Devaty, J. A. Edmond, M. A. Kahn, R. Kaplan, and M. Rahman (Institute of Physics Conference Series 137, Bristol, UK 1994), pp. 161-164.

- V. F. Tsvetkov, R. C. Glass, D. Henshall, D. A. Asbury, and C. H. Carter, Jr. in <u>Silicon Carbide. III-Nitrides. and Related Materials</u>, edited by G. Pensl, H. Morkoc, B. Monemar, and E. Janzen (Materials Science Forum 264-268, Trans Tech Publications, Switzerland 1998), pp. 3-8.

- P. G. Neudeck, W. Huang, and M. Dudley to appear in <u>Power Semiconductor Materials and Devices</u>, edited by S. J. Pearton, R. J. Shul, E. Wolfgang, F. Ren, and S. Tenconi (Mater. Res. Soc. Proc. 483, Warrandale, PA, 1998).

- 11. S. M. Sze, <u>Physics of Semiconductor Devices</u>, 2nd ed., Wiley-Interscience, New York, 1981, pp. 169-175.

- 12. B. J. Baliga, Modern Power Devices, Wiley-Interscience, New York, 1987, pp. 314-318.

- 13. L. W. Ricketts, J. E. Bridges, and J. Miletta, <u>EMP Radiation and Protective Techniques</u>, Wiley, New York, 1976.

- 14. R. N. Ghose, <u>EMP Environment and System Hardness Design</u>, D. White Consultants, Gainesville, VA, 1984, pp. 4.1-4.31.

- 15. D. C. Wunsch and R. R. Bell, IEEE Trans. Nucl. Sci. 15 (6), 244-259 (1968).

- 16. A. Zywietz, K. Karch, and F. Bechstedt, Physical Review B 54 (3), 1791-1798 (1996).

- 17. C. Kittel, Introduction to Solid State Physics, 6th ed., Wiley, New York, 1986, pp. 99-122.

- 18. G. A. Slack, J. Appl. Phys. 35 (12), 3460 (1964).

x : · ·

- 19. P. G. Neudeck and C. Fazi, J. Appl. Phys. 80 (2), 1219-1225 (1996).

- 20. Fluorinert<sup>™</sup>, 3M Company, St. Paul, MN 55144.

- 21. G. Gradinaru, V. P. Madangarli, and T. S. Sudarshan, IEEE Trans. Electron Devices 41 (7), 1233-1238 (1994).

- 22. P. G. Neudeck, D. J. Larkin, J. A. Powell, L. G. Matus, and C. S. Salupo, Appl. Phys. Lett. 64 (11), 1386-1388 (1994).