E11895

## RF TRANSMISSION LINES ON SILICON SUBSTRATES

George E. Ponchak

NASA Glenn Research Center, 21000 Brookpark Rd., Cleveland, OH 44135 USA george.ponchak@grc.nasa.gov

420831

Abstract- A review of RF transmission lines on silicon substrates is presented. Through measurements and calculated results, it is shown that attenuation is dominated by conductor loss if silicon substrates with a resistivity greater than 2500  $\Omega$ -cm are used. Si passivation layers affect the transmission line attenuation; however, measured results demonstrate that passivation layers do not necessarily increase attenuation. If standard, low resistivity Si wafers must be used, alternative transmission lines such as thin film microstrip and CPW on thick polyimide layers must be used. Measured results presented here show that low loss per unit length is achievable with these transmission lines.

#### I. INTRODUCTION

The market for mobile voice and pager communication systems, especially at 2 GHz, has grown tremendously over the past several years. Now, demand is growing for higher frequency systems at 20 and 30 GHz for high data rate video and digital communications. Since these are commercial markets, it is imperative that system designers achieve the required performance at the lowest cost.

For the RF circuit designer, there are several methods that can be used to lower the cost. First, the Radio Frequency Integrated Circuits (RFICs) or Monolithic Microwave Integrated Circuits (MMICs) that perform RF amplification and frequency translation may be made using the lowest cost technology. Second, more functions can be incorporated onto a single circuit to minimize interconnect and wire bonding expenses while improving reliability. Third, thermal management and wafer breakage expenses can be reduced.

To meet these challenges, Si RFICs have emerged as a strong challenger to the traditional GaAs MMIC [1-5]. This has been made possible by the development of SiGe heterojunction bipolar transistors (HBTs) by IBM [5] and DaimlerChrysler [6]. In fact, by using aggressive bandgap engineering, HBTs with a maximum frequency of oscillation,  $f_{max}$ , of 160 GHz have been demonstrated. While commercial circuits based on this HBT are not available; Si RFICs operating into the millimeter-wave spectrum are currently available. Since Si wafers cost less than GaAs wafers and there is a larger worldwide Si processing infrastructure, it may be expected that Si RFICs will cost less than GaAs MMICs will. Because these circuits may be monolithically integrated with BJT and CMOS data processing and memory circuits, it is possible to build single chip communication systems. Furthermore, since sensors and MEMs devices are usually built on Si substrates, single chip systems are possible. Thus, the packaging and interconnect costs are significantly lowered.

However, the development of millimeter-wave HBTs only solves half of the problem with Si as a microwave substrate. Unlike digital ICs, interconnects in RFICs are required for impedance matching, filtering, and signal distribution. In fact, most of the circuit area in RFICs is comprised of transmission lines. Microwave transmission lines are characterized by their propagation constant  $\gamma=\alpha+j\beta$  where  $\beta$  is the phase constant and  $\alpha$  is the attenuation constant. Attenuation may be separated into the attenuation due to losses in the dielectric,  $\alpha_d$ , and the conductor,  $\alpha_c$ . While  $\alpha_c$  is primarily dependent on the conductivity and geometry of the metal lines,  $\alpha_d$  is primarily dependent on the substrate and determined by [7]:

$$\alpha_d = \frac{\pi}{\lambda_0} \frac{\varepsilon_r}{\varepsilon_r - 1} \frac{\varepsilon_{eff}(f) - 1}{\sqrt{\varepsilon_{eff}(f)}} \tan \delta \quad (\text{Np/cm})$$

(1)

where  $\varepsilon_r$  is the relative dielectric constant ( $\varepsilon_r$ =11.68 for Si [8]),  $\lambda_0$  is the free space wavelength, and  $\varepsilon_{eff}$  (f) is the effective permittivity of the transmission line. The loss tangent,

$$\tan \delta = \frac{\varepsilon''}{\varepsilon'} + \frac{1}{\omega \varepsilon' \rho} \tag{2}$$

is dependent on the complex permittivity,  $\varepsilon=\varepsilon'$ -j $\varepsilon''$  (where  $\varepsilon''/\varepsilon'=0.0018$  for Si [8]), and the resistivity of the substrate,

After inserting the associated values for Si into Equ. 1, the dielectric attenuation is given by:

$$\alpha_d = \frac{\varepsilon_{eff}(f) - 1}{\sqrt{\varepsilon_{eff}(f)}} \left\{ 1.7905 \cdot 10^{-3} f + \frac{153.09}{\rho} \right\} (dB/cm) \quad (3)$$

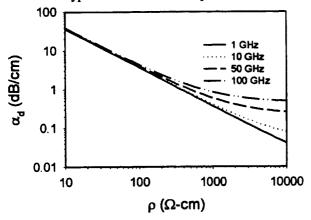

where f is the frequency in GHz and  $\rho$  is in  $\Omega$ -cm. Ideally,  $\rho$  is infinite and  $\alpha_d$  is only dependent on losses associated with the polarization of the atoms in the material. In practice, the second term may be neglected if ρ>8.55\*10<sup>5</sup>/f. Traditionally, digital Si ICs are fabricated on wafers with a bulk substrate resistivity of 1 to 10  $\Omega$ -cm. Thus, the second term dominates and  $\alpha_d \approx 32$  dB/cm over the entire microwave and millimeter-wave frequency spectrum for microstrip and coplanar waveguide (CPW) as shown in Fig. 1. Obviously, this is a prohibitively high attenuation. Even if Si substrates with a resistivity of 10000  $\Omega$ -cm, which is the highest resistivity wafers commonly available, are used, the second term dominates  $\alpha_d$  through 50 GHz; however, the dielectric loss is less than 0.1 dB/cm at 1 GHz for microstrip lines on 10000  $\Omega$ cm Si which is a very acceptable attenuation.

While it may seem obvious to use Si wafers with the highest resistivity available and ignore the dielectric losses, this decision is not always up to the circuit designer. The two foundries offering SiGe HBT processing, IBM in the US and Temic Semiconductor in

Germany, use CMOS grade Si. Therefore, RF circuit designers must be able to layout circuits on either type of substrate. In the rest of this paper, low loss transmission lines on both types of Si wafer will be presented.

Fig. 1: Calculated dielectric attenuation of 50  $\Omega$  microstrip line on 100  $\mu m$  thick Si and a line width of 80  $\mu m$ .

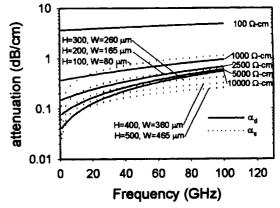

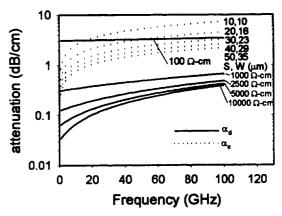

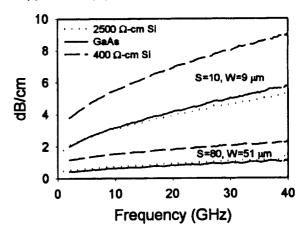

# II. TRANSMISSION LINES ON HIGH RESISTIVITY SILICON

While Equ. 3 clearly shows that dielectric attenuation decreases as the substrate resistivity increases, it is reasonable to ask how high the resistivity should be before the incremental benefit of lower ad is too small to affect circuit performance. This question arises because substrate cost increases as the resistivity increases. Fig. 2 shows the calculated conductor and dielectric loss of 50 Ω microstrip lines as a function of the Si resistivity and thickness, and Fig. 3 shows the calculated conductor and dielectric loss of 50  $\Omega$  CPW lines as a function of the CPW geometry and Si resistivity. As shown in Fig. 2, the dielectric attenuation for microstrip lines may not be neglected even when the resistivity is 10000  $\Omega$ -cm. For CPW lines of the commonly used center strip and slot widths, S and W respectively, a resistivity of 2000  $\Omega$ -cm is required for  $\alpha > 10\alpha_d$ . These results are due to slightly higher  $\alpha_d$  for microstrip lines and significantly higher ae for narrow CPW lines. Fig. 4 shows measured attenuation of narrow and wide CPW lines on 400 and 2500 Ω-cm Si and GaAs. As predicted by Fig. 3, the attenuation of CPW on HRS and GaAs is similar; while on 400 Ω-cm Si, CPW has significantly higher loss. Note that lower conductor loss is achievable with CPW lines by increasing S and W, which would increase the influence of a<sub>d</sub>. However, for commonly used CPW and microstrip dimensions, a resistivity of 2500  $\Omega$ -cm and 10000  $\Omega$ -cm is required respectively if at is to be ignored.

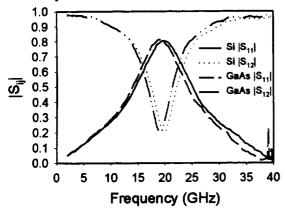

Besides low loss, HRS offers another major advantage to Si circuit designers. Most circuit element models developed over the past twenty years are based on measurements and modeling of GaAs circuits. Since  $\varepsilon_r$  of Si and GaAs differ by only 9 percent, Si circuit designers may use the same models. Fig. 5 shows the measured characteristics of a CPW short circuit terminated series stub on HRS and GaAs. Except for a frequency shift due

to the lower dielectric constant of Si, the characteristics are the same. Other components behave similarly.

Fig. 2: Calculated attenuation of 50  $\Omega$  microstrip line as a function of Si thickness (H), strip width (W), and Si resistivity (metal thickness = 2  $\mu$ m).

Fig. 3: Calculated attenuation of 50  $\Omega$  CPW as a function of strip width (S), slot width (W), and Si resistivity (metal thickness = 2  $\mu$ m).

Fig. 4: Measured attenuation of CPW on Si and GaAs as a function of frequency and line geometry, metal thickness =1.5  $\mu m$ .

There are potential difficulties with HRS though. CPW placed directly on HRS, as was done for Figs. 4 and 5, has bias dependent propagation characteristics, and even worse, leakage current between the center conductor and ground planes is large enough to alter the bias of diodes and other active components [9]. To mitigate this problem, HRS must be passivated with SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>. However, several authors have noted a substantial increase in attenuation when a passivation layer is used and have

recommended removing the insulator from the exposed surface: only leave the insulator under the metal lines [10].

Fig. 5: Measured CPW short circuit series stub on GaAs and HRS, S=W=50  $\mu m.$

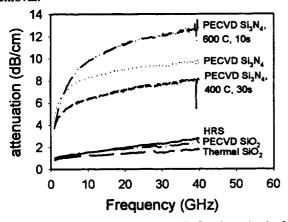

The increased attenuation is believed to be due to trapped charges in the passivation material that induces image charges at the insulator/HRS interface. These charges short the center conductor to the ground planes. Removal of the insulator from the slots of CPW eliminates the induced charges and restores the low attenuation of the line. However, this observation is not universal. Fig. 6 shows the attenuation of CPW lines on HRS with SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> passivation without etching the slot regions. It is noted that CPW on Si<sub>3</sub>N<sub>4</sub> has significantly higher loss, even after densification bakes, while CPW on SiO2 has lower loss than CPW directly on HRS. Analysis indicates that the Si<sub>3</sub>N<sub>4</sub> has approximately 2% Si ions in the film, but the SiO<sub>2</sub> has no impurities. Thus, impurity free passivation layers eliminates the need for passivation removal.

Fig. 6: Measured attenuation of CPW on HRS with passivation layer, S and W equal 50 and 35  $\mu m$  respectively.

# III. TRANSMISSION LINES ON LOW RESISTIVITY SILICON

Because low resistivity Si introduces significant attenuation as shown in Fig. 1, microstrip, CPW, and other transmission lines cannot be placed directly on it. Instead, methods must be used that either shield or minimize the electromagnetic field interaction with the Si. This is usually accomplished by using the polyimide that Si IC manufactures use for wafer planarization.

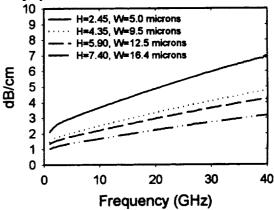

Thin film microstrip (TFMS) is formed by depositing a metal ground plane on the top surface of the Si, depositing polyimide on top of that, and then the microstrip on top of the polyimide. Thus, the polyimide, which is typically between 2 and 10  $\mu$ m, forms the microstrip substrate [11]. Fig. 7 shows the measured attenuation of 50  $\Omega$  TFMS as a function of the polyimide thickness, H, and strip width, W. Note that attenuation decreases as the polyimide thickness increases, but that low loss is achievable with less than 10  $\mu$ m of polyimide.

Figure 7: Measured attenuation of 50  $\Omega$  TFMS as a function of polyimide thickness.

With CPW, ground planes either above or below the substrate are not desired since they introduce the potential for exciting parasitic microstrip or parallel plate waveguide modes. This possibility increases when the polyimide is less than three times S+2W. Since a very thick polyimide would be required to maintain a good CPW TEM mode, it is not possible to shield the Si from the CPW with a ground plane as was done for the TFMS.

Figure 8: Measured attenuation of CPW lines on 14.59  $\mu m$  polyimide on 2-10  $\Omega\text{-cm}$  Si.

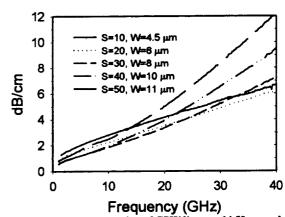

Instead, polyimide is used to elevate the CPW above the Si to minimize the field interaction with the Si [12]. Polyimide is deposited directly on the Si wafer and the CPW is then defined on top of the polyimide. Fig. 8 shows the measured attenuation of five CPW lines on 14.59  $\mu$ m thick polyimide, which is on low resistivity Si. When S+2W is small, the attenuation is conductor loss dominated (varies as  $f^{0.5}$ ); however, the frequency dependence and attenuation increases as S+2W increases. This is the opposite of CPW lines on HRS or other insulators. Furthermore,  $\epsilon_{eff}$  and the characteristic

impedance are also dependent on S+2W relative to the polyimide thickness. Thus, while each of the CPW lines in Fig. 8 is 35  $\Omega$  on HRS, their impedance varies from 42 to 52  $\Omega$  on polyimide.

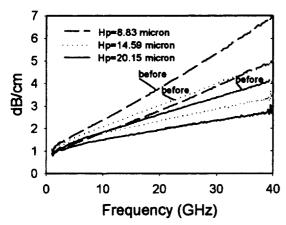

Micromachining CPW on HRS to remove the substrate from the slots has been shown to reduce attenuation. This may be done with CPW on polyimide also as is shown in Fig. 9. Fig. 10 shows measured loss of micromachined CPW on low resistivity Si. There is a 28 percent reduction in attenuation after etching for the CPW line on thinner polyimide and a 35 percent reduction in attenuation on the thickest polyimide at 40 GHz. Etching the polyimide from the slots also lowers  $\epsilon_{\rm eff}$ :  $\epsilon_{\rm eff}$  for a CPW line with S and W of 10 and 9  $\mu$ m respectively and a polyimide thickness of 20.15  $\mu$ m is only 1.3.

Figure 9: CPW on low resistivity Si with a polyimide interface layer that has been removed from the slots.

Figure 10: Measured attenuation of CPW lines on polyimide before and after etching polyimide from slots, S=10,  $W=9~\mu m$ .

### IV. CONCLUSIONS

A review of transmission lines suitable for Si RFICs has been presented. It has been shown that CPW lines on Si with a resistivity greater than 2500  $\Omega$ -cm have approximately the same attenuation as CPW on GaAs. Furthermore, passivation layers on HRS do not necessarily increases attenuation if they are grown with low impurity

concentrations. When low resistivity Si must be used, thin film microstrip with a polyimide thickness of only 7.4  $\mu$ m yields the same attenuation as similarly sized CPW lines on HRS. CPW lines on polyimide have higher attenuation or require thicker polyimide than TFMS, but if the polyimide is etched from the slots, the attenuation is comparable to that of TFMS and CPW on HRS. Transmission lines on polyimide have a significantly lower  $\epsilon_{\rm eff}$  than CPW or microstrip on HRS, which increases circuit speed.

#### V. REFERENCES

- [1] J.-F. Luy, K. M. Strohm, H.-E. Sasse, A. Schuppen, J. Buechler, M. Wollitzer, A. Gruhle, F. Schaffler, U. Guettich, and A. Klaaben, "Si/SiGe MMIC's," *IEEE Trans. Micro. Theory Tech.*, Vol. 43, No. 4, pp. 705-714, 1995.

- [2] C. Rheinfelder, K. Strohm, F. Beiβwanger, J. Gerdes, F. J. Schmuckle, J. F. Luy, and W. Heinrich, "26 GHz coplanar SiGe MMICs," *IEEE 1996 Micro. and Millimeter-Wave Circuits Symp. Dig.*, San Francisco, CA, June 16-18, 1996, pp. 205-208.

- [3] J.-S. Rieh, L.-H. Lu, L. B. P. Katehi, P. Bhattacharya, E. T. Croke, G. E. Ponchak, and S. A. Alterovitz, "X- and Kuband amplifiers based on Si/SiGe HBTs and micromachined lumped components," *IEEE Trans. Micro. Theory Tech.*, Vol. 46, No. 5, pp. 685-694, 1998.

- [4] N. Suematsu, M. Ono, S. Kubo, Y. Iyama, and O. Ishida, "L-band internally matched Si-MMIC front-end," *IEEE Trans. Micro. Theory Tech.*, Vol. 44, No. 12, pp. 2375-2378, 1996.

- [5] M. Case, S. A. Maas, L. Larson, D. Rensch, D. Harame, and B. Meyerson, "An X-band monolithic active mixer in SiGe HBT technology," 1996 IEEE MTT-S Int. Micro. Symp. Dig., San Francisco, CA, June 17-21, 1996, pp. 655-658.

- [6] A. Gruhle and A. Schuppen, "Recent advances with SiGe heterojunction bipolar transistors," *Thin Solid Films*, Vol. 294, pp. 246-249, 1997.

- [7] R. E. Collin, Foundations for Microwave Engineering, New York: McGraw-Hill, 1992, pp. 153-164.

- [8] M. N. Afsar and K. J. Button, "Precise millimeter-wave measurements of complex refractive index, complex dielectric permittivity and loss tangent of GaAs, Si, SiO2, A12O3, BeO, Macor, and glass," *IEEE Trans. Microwave Theory Tech.*, Vol. 31, No. 2, pp. 217-223, 1983.

- [9] Y. Wu, S. Yang, H. S. Gamble, B. M. Armstrong, V. F. Fusco, and J. A. C. Stewart, "The effect of a SiO<sub>2</sub> interface layer on CPW lines and schottky barrier diodes on HRS substrates," 1998 Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems Digest, Ann Arbor, MI, Sept. 17-18, 1998, pp. 178-180.

- [10] Y. Wu, H. S. Gamble, B. M. Armstrong, V. F. Fusco, and J. A. C. Stewart, "SiO<sub>2</sub> interface layer effects on microwave loss of high-resistivity CPW line," *IEEE Microwave and Guided Wave Lett.*, Vol. 9, No. 1, pp. 1012, 1999.

- [11] G. E. Ponchak and A. N. Downey, "Characterization of thin film microstrip lines on polyimide," *IEEE Trans.* Components, Packaging, and Manufacturing Tech. -Part B, Vol. 21, No. 2, pp. 171-176, May 1998.

- [12] G. E. Ponchak and L. P. B. Katehi, "Measured attenuation of coplanar waveguide on CMOS grade silicon substrates with a polyimide interface layer," *IEE Electronics Letters*, Vol. 34, No. 13, pp. 1327-1329, June 25, 1998.

This report is a preprint of an article submitted to a journal for publication. Because of changes that may be made before formal publication, this preprint is made available with the understanding that it will not be cited or reproduced without the permission of the author.