NASA/TM-2001-210876

# A Practical Tutorial on Modified Condition/ Decision Coverage

Kelly J. Hayhurst Langley Research Center, Hampton, Virginia

Dan S. Veerhusen Rockwell Collins, Inc., Cedar Rapids, Iowa

John J. Chilenski The Boeing Company, Seattle, Washington

Leanna K. Rierson Federal Aviation Administration, Washington, D.C.

# The NASA STI Program Office ... in Profile

Since its founding, NASA has been dedicated to the advancement of aeronautics and space science. The NASA Scientific and Technical Information (STI) Program Office plays a key part in helping NASA maintain this important role.

The NASA STI Program Office is operated by Langley Research Center, the lead center for NASA's scientific and technical information. The NASA STI Program Office provides access to the NASA STI Database, the largest collection of aeronautical and space science STI in the world. The Program Office is also NASA's institutional mechanism for disseminating the results of its research and development activities. These results are published by NASA in the NASA STI Report Series, which includes the following report types:

- TECHNICAL PUBLICATION. Reports of completed research or a major significant phase of research that present the results of NASA programs and include extensive data or theoretical analysis. Includes compilations of significant scientific and technical data and information deemed to be of continuing reference value. NASA counterpart of peer-reviewed formal professional papers, but having less stringent limitations on manuscript length and extent of graphic presentations.

- TECHNICAL MEMORANDUM. Scientific and technical findings that are preliminary or of specialized interest, e.g., quick release reports, working papers, and bibliographies that contain minimal annotation. Does not contain extensive analysis.

- CONTRACTOR REPORT. Scientific and technical findings by NASA-sponsored contractors and grantees.

- CONFERENCE PUBLICATION. Collected papers from scientific and technical conferences, symposia, seminars, or other meetings sponsored or co-sponsored by NASA.

- SPECIAL PUBLICATION. Scientific, technical, or historical information from NASA programs, projects, and missions, often concerned with subjects having substantial public interest.

- TECHNICAL TRANSLATION. Englishlanguage translations of foreign scientific and technical material pertinent to NASA's mission.

Specialized services that complement the STI Program Office's diverse offerings include creating custom thesauri, building customized databases, organizing and publishing research results ... even providing videos.

For more information about the NASA STI Program Office, see the following:

- Access the NASA STI Program Home Page at *http://www.sti.nasa.gov*

- E-mail your question via the Internet to help@sti.nasa.gov

- Fax your question to the NASA STI Help Desk at (301) 621-0134

- Phone the NASA STI Help Desk at (301) 621-0390

- Write to: NASA STI Help Desk NASA Center for AeroSpace Information 7121 Standard Drive Hanover, MD 21076-1320

NASA/TM-2001-210876

# A Practical Tutorial on Modified Condition/ Decision Coverage

Kelly J. Hayhurst Langley Research Center, Hampton, Virginia

Dan S. Veerhusen Rockwell Collins, Inc., Cedar Rapids, Iowa

John J. Chilenski The Boeing Company, Seattle, Washington

Leanna K. Rierson Federal Aviation Administration, Washington, D. C.

National Aeronautics and Space Administration

Langley Research Center Hampton, Virginia 23681-2199

Available from:

NASA Center for AeroSpace Information (CASI) 7121 Standard Drive Hanover, MD 21076-1320 (301) 621-0390 National Technical Information Service (NTIS) 5285 Port Royal Road Springfield, VA 22161-2171 (703) 605-6000

# **Table of Contents**

| 1 | BACKGROUND AND PURPOSE                                      | 1  |

|---|-------------------------------------------------------------|----|

|   | 1.1 Scope of the Tutorial                                   | 1  |

|   | 1.2 NOTES ON DEFINITIONS AND NOTATION                       |    |

| ~ |                                                             |    |

| 2 | MC/DC APOLOGIA                                              |    |

|   | 2.1 The Verification Process                                |    |

|   | 2.2 DEFINITION AND ROLE OF COVERAGE                         |    |

|   | 2.2.1 Requirements Coverage Analysis                        |    |

|   | 2.2.2 Structural Coverage Analysis                          |    |

|   | 2.3 TYPES OF STRUCTURAL COVERAGE                            |    |

|   | 2.3.1 Statement Coverage                                    |    |

|   | 2.3.2 Decision Coverage                                     |    |

|   | 2.3.3 Condition Coverage                                    |    |

|   | 2.3.4 Condition/Decision Coverage                           |    |

|   | 2.3.5 Modified Condition/Decision Coverage                  |    |

|   | 2.3.6 Multiple Condition Coverage                           |    |

|   | 2.4 STRUCTURAL COVERAGE VERSUS STRUCTURAL TESTING           |    |

|   | 2.5 MORE DETAILS ABOUT MODIFIED CONDITION/DECISION COVERAGE |    |

|   | 2.5.1 A Note on Source versus Object Code Coverage          |    |

|   | 2.6 CONFOUNDING ISSUES                                      | 12 |

| 3 | MC/DC APPROACH                                              | 14 |

|   | 3.1 MC/DC BUILDING BLOCKS ("HOW DO I TEST A?")              |    |

|   | 3.1.1 and Gate                                              | 13 |

|   | 3.1.2 or Gate                                               |    |

|   | 3.1.3 xor Gate                                              |    |

|   | 3.1.4 not Gate                                              |    |

|   | 3.1.5 Comparator                                            |    |

|   | 3.1.6 If-then-else Statement                                |    |

|   | 3.1.7 Loop Statements                                       |    |

|   | 3.2 EVALUATION METHOD                                       |    |

|   | 3.2.1 Source Code Representation                            |    |

|   | 3.2.2 Identification of Test Inputs                         |    |

|   | 3.2.3 Elimination of Masked Tests                           |    |

|   | 3.2.4 Determination of MC/DC.                               |    |

|   | 3.2.5 Output Confirmation                                   |    |

|   | 3.3 FOLLOWING THE FIVE-STEP EVALUATION PROCESS              | 29 |

|   | 3.4 GROUPED FUNCTIONALITY.                                  |    |

|   | 3.5 DEVELOPING COMPLEX CONSTRUCTS                           |    |

|   | 3.6 MC/DC WITH SHORT CIRCUIT LOGIC                          |    |

|   | 3.7 MC/DC WITH BIT-WISE OPERATIONS.                         |    |

|   | 3.7.1 Examples with Bit-Wise Operations                     |    |

|   | 3.7.2 Alternate Treatments of Bit-wise Operations           |    |

|   | 3.8 ANALYSIS RESOLUTION                                     |    |

| A | MC/DC ADMONITIONS                                           |    |

| 4 |                                                             |    |

|   | 4.1 AUTOMATION PROBLEMS                                     |    |

|   | 4.1.1 How Coverage Analysis Tools Work                      |    |

|   | 4.1.2 Factors to Consider in Selecting or Qualifying a Tool |    |

|   | 4.2 PROCESS PROBLEMS                                        |    |

|   | 4.2.1 Inadequate Planning for MC/DC                         |    |

|   | 4.2.2 Misunderstanding the MC/DC Objective                  |    |

|   | 4.2.3 Inefficient Testing Strategies                        |    |

|   | 4.2.4 Poor Management of Verification Resources             | 55 |

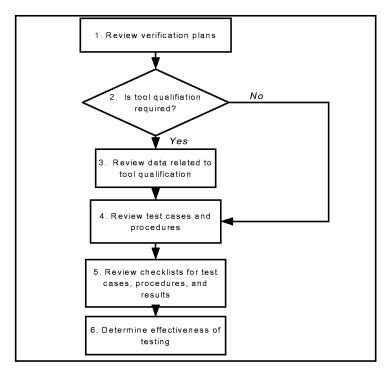

| 5 ASSESSMENT PROCESS                                             | 56             |

|------------------------------------------------------------------|----------------|

| STEP 1—REVIEW VERIFICATION PLANS                                 |                |

| STEP 2—DETERMINE NEED FOR TOOL QUALIFICATION                     |                |

| STEP 3—REVIEW DATA RELATED TO QUALIFICATION OF MC/DC TOOLS       |                |

| STEP 4—REVIEW TEST CASES AND PROCEDURES                          |                |

| STEP 5—REVIEW CHECKLISTS FOR TEST CASES, PROCEDURES, AND RESULTS | 60             |

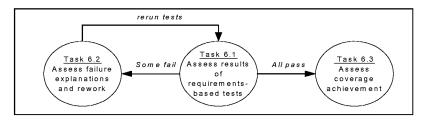

| STEP 6—DETERMINE EFFECTIVENESS OF TEST PROGRAM                   | 60             |

| Task 6.1—Assess results of requirements-based tests              |                |

| Task 6.2—Assess failure explanations and rework                  |                |

| Task 6.3—Assess coverage achievement                             |                |

| 6 SUMMARY                                                        | 62             |

| 7 REFERENCES                                                     | 63             |

| APPENDIX A                                                       | 65             |

| SOLUTIONS TO EXERCISES                                           | 65             |

| Solution 2.5a                                                    |                |

| Solution 2.5b                                                    |                |

| Solution 3.3a, OR/XOR Exercise                                   |                |

| Solution 3.3b, Ground Test Exercise                              |                |

| Solution 3.3c, Weight on Wheels Exercise                         |                |

| Solution 3.3d, Gain Exercise                                     |                |

| Solution 3.5, Reset-Overides-Set Latch Exercise                  |                |

| APPENDIX B                                                       | 72             |

| CERTIFICATION AUTHORITIES SOFTWARE TEAM POSITION PAPER ON MA     | ASKING MC/DC72 |

| APPENDIX C                                                       | 78             |

| BACKGROUND ON TUTORIAL AUTHORS                                   |                |

# Abstract

This tutorial provides a practical approach to assessing modified condition/decision coverage (MC/DC) for aviation software products that must comply with regulatory guidance for DO-178B level A software. The tutorial's approach to MC/DC is a 5-step process that allows a certification authority or verification analyst to evaluate MC/DC claims without the aid of a coverage tool. In addition to the MC/DC approach, the tutorial addresses factors to consider in selecting and qualifying a structural coverage analysis tool, tips for reviewing life cycle data related to MC/DC, and pitfalls common to structural coverage analysis.

# **1** Background and Purpose

The RTCA/DO-178B document *Software Considerations in Airborne Systems and Equipment Certification* is the primary means used by aviation software developers to obtain Federal Aviation Administration (FAA) approval<sup>1</sup> of airborne computer software (ref. 1, 2). DO-178B describes software life cycle activities and design considerations, and enumerates sets of objectives for the software life cycle processes. The objectives applicable to a given piece of software are based on the software level determined by a system safety assessment. The objectives serve as a focal point for approval of the software.

This tutorial concerns one particular objective in DO-178B: objective 5 in Table A-7 of Annex A. This objective, which is applicable to level A software only, requires that tests achieve modified condition/decision coverage (MC/DC) of the software structure. The purpose of the tutorial is to provide sufficient information upon which a diligent person may build a strong working knowledge of how to meet the MC/DC objective, and provide a means to assess whether the objective has been met<sup>2</sup>.

# **1.1 Scope of the Tutorial**

This tutorial provides a broad view of MC/DC, concentrating on practical information for software engineers. Topics include the role of MC/DC within the verification process described in DO-178B, the rationale for the MC/DC objective, a pragmatic approach for manually evaluating MC/DC, and an aid for assessing an applicant's MC/DC program. Although understanding the rationale for MC/DC is not strictly necessary for developing a working knowledge of its use, information is included to help reduce current well-documented misunderstandings about the topic (ref. 3).

The tutorial is a self-study course designed for individuals who either develop and verify aviation software products that must comply with the DO-178B objectives for level A, or who provide oversight and assurance of such products. Readers are assumed to have a basic knowledge of Boolean algebra and DO-178B. Specific references to DO-178B and other supporting materials are cited throughout. Also included throughout are exercises designed to give readers structured opportunities to assess their understanding of the concepts presented; solutions for the exercises are given in Appendix A. Readers

<sup>&</sup>lt;sup>1</sup> ED-12B, the European equivalent of DO-178B, is recognized by the Joint Aviation Authorities (JAA) via JAA temporary guidance leaflet #4 as the primary means for obtaining approval of airborne computer software.

<sup>&</sup>lt;sup>2</sup> This work was supported by the FAA William J. Hughes Technical Center, Atlantic City International Airport, New Jersey.

are encouraged to complete the exercises as they are encountered in the text to obtain maximum benefit from the tutorial.

After successful completion of this tutorial, readers should be able to:

- Explain the rationale for MC/DC

- Assess whether specific test cases meet the MC/DC criteria

- Ask informed questions about structural coverage analysis tools

- Determine if the integral processes support compliance with the MC/DC objective

- Avoid common problems associated with MC/DC

Lest anyone think otherwise, please recognize that this tutorial does not constitute regulatory software policy or guidance. Furthermore, the approach to MC/DC presented in this tutorial is just one possible approach to assessing compliance with the MC/DC objective and, as such, should not be considered the *only* means of complying with the objective. We have tried to clearly identify all places where the provided information goes beyond what is explicitly stated in DO-178B.

Chapter 2 provides the rationale for MC/DC. A manual approach to evaluating MC/DC is presented in chapter 3. Chapter 4 provides a collection of ways to help mitigate problems associated with MC/DC, including problems in selecting and qualifying a structural coverage analysis tool and process problems. Finally, chapter 5 provides information on determining an applicant's compliance with the MC/DC objective. For further information on relevant research and theoretical aspects of MC/DC see *An Investigation of Three Forms of the Modified Condition Decision Coverage (MCDC) Criterion* (ref. 4).

# 1.2 Notes on definitions and notation

The definitions and descriptions of terms used in this tutorial are consistent with those given in the Glossary of DO-178B, unless noted otherwise. The following notational conventions are used throughout the tutorial:

Boolean operators are denoted by bolded italics: and, or, xor, not

Boolean conditions are denoted by bolded capital letters: A, B, C, ...

Non-Boolean variables are denoted in plain lower case letters: x, y, z, ...

Boolean outcomes are written as either *false* or *true*, or *F* or *T*

A test case for a Boolean function with *n* inputs is denoted by  $C = (C_1 C_2 \dots C_n)$ , where  $C_i = F$  or T

Where graphical representations are introduced in the text, the relevant symbols are defined when they are introduced. Code segments used as examples are written in Ada unless noted otherwise.

# 2 MC/DC Apologia

This chapter explains the context in which the MC/DC objective exists, and presents a rationale for the objective. Readers whose sole interest is in learning how to achieve or assess compliance may wish to skim this chapter.

# 2.1 The Verification Process

"No product of human intellect comes out right the first time. We rewrite sentences, rip out knitting stitches, replant gardens, remodel houses, and repair bridges. Why should software be any different?" (ref. 5)

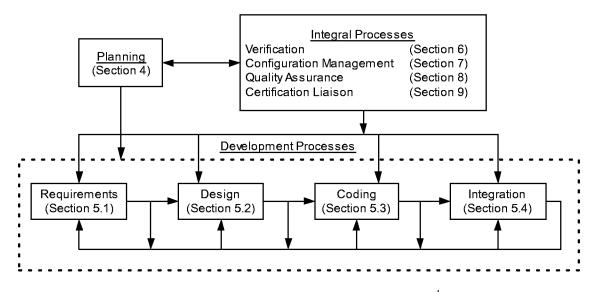

According to DO-178B<sup>3</sup>, the purpose of the verification process is to detect and report errors that have been introduced in the development processes. The verification process does not produce software; its responsibility is to ensure that the produced software implements intended function completely and correctly, while avoiding unintended function. Because each development process may introduce errors, verification is an integral process (see Figure 1), which is coupled with every development process. Including verification activities with each development activity is intended to help "build in" quality at each step, because "testing or analyzing in" quality at the end of the life cycle is impractical.

Figure 1. DO-178B software life cycle processes.<sup>4</sup>

Verification examines the relationship between the software product and the requirements. At an abstract level, the software verification process exists to constantly ask the question: are we building the system right?

Verification can be expensive and time consuming, even for software that is not safety critical. To date, no one has been able to define objective test measures of software quality. That is, typical statistical approaches to quality assurance, which work well for physical devices, do not apply to software. Consequently, drawing conclusions about software quality short of testing every possible input to the program is fraught with danger. This fact contributes to the current reliance on structural coverage as one measure of the completeness of testing.

<sup>&</sup>lt;sup>3</sup> This is the last time the phrase "According to DO-178B" or its variants will appear in this document. The reader should simply assume its presence everywhere.

<sup>&</sup>lt;sup>4</sup> This figure is based on a similar Life Cycle Diagram in RTCA/DO-254 Design Assurance Guidance for Airborne Electronic Hardware (ref. 6).

#### **2.2 Definition and Role of Coverage**

"Our goal, then, should be to provide enough testing to ensure that the probability of failure due to hibernating bugs is low enough to accept. 'Enough' implies judgement." (ref. 7)

*Coverage* refers to the extent to which a given verification activity has satisfied its objectives. Coverage measures can be applied to any verification activity, although they are most frequently applied to testing activities. Appropriate coverage measures give the people doing, managing, and auditing verification activities a sense of the adequacy of the verification accomplished; in essence, providing an exit criteria for when to stop. That is, what is "enough" is defined in terms of coverage.

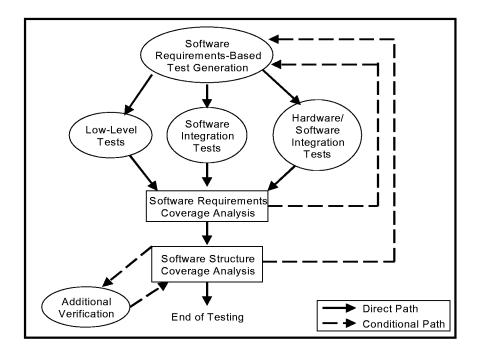

Coverage is a measure, not a method or a test. Thus, phrases such as "MC/DC testing" can do more harm than good<sup>5</sup>. As a measure, coverage is usually expressed as the percentage of an activity that is accomplished. Two specific measures of test coverage are shown in Figure 2 (ref. 2): requirements coverage and software structure coverage (to be consistent with common usage, we will use the phrase *structural coverage* hereafter). Requirements coverage analysis determines how well the requirements-based testing verified the implementation of the software requirements (DO-178B, section 6.4.4.1), and establishes traceability between the software requirements and the test cases (DO-178B, section 6.2). Structural coverage analysis determines how much of the code structure was executed by the requirements-based tests (DO-178B, section 6.4.4.2), and establishes traceability between the code structure and the test cases (DO-178B, section 6.2). Please note that requirements coverage analysis precedes structural coverage analysis.

Figure 2. DO-178B software testing activities.

<sup>&</sup>lt;sup>5</sup> The terms "black-box testing" and "white-box testing", which are used extensively in software engineering literature, also may be misleading. These terms (especially "white-box testing") tend to obscure the necessary connection to requirements. These terms do not appear in DO-178B; neither do they appear in this tutorial. The distinction between *coverage* and *testing* will be further discussed in section 2.4.

#### 2.2.1 Requirements Coverage Analysis

According to software engineering theory, software requirements should contain a finite list of behaviors and features, and each requirement should be written to be verifiable. Testing based on requirements is appealing because it is done from the perspective of the user (thus providing a demonstration of intended function), and allows for development of test plans and cases concurrently with development of the requirements. Given a finite list of requirements and a set of completion criteria, requirements-based testing becomes a feasible process, unlike exhaustive testing (ref. 5).

The Annex A objectives for requirements-based test coverage are stated with respect to both high- and low-level requirements. Objective 3 in Table A-7 requires test coverage of high-level requirements for software levels A-D; and objective 4 in Table A-7 requires test coverage of low-level requirements for software levels A-C. The corresponding guidance in section 6.4.4.1 states that the test coverage analysis should show that test cases exist for each software requirement, and that the test cases satisfy the criteria for normal and robustness testing.

Unfortunately, a test set that meets requirements coverage is not necessarily a thorough test of the software, for several reasons:

- the software requirements and the design description (used as the basis for the test set) may not contain a complete and accurate specification of all the behavior represented in the executable code;

- the software requirements may not be written with sufficient granularity to assure that all the functional behaviors implemented in the source code are tested; and,

- requirements-based testing *alone* cannot confirm that the code does not include unintended functionality.

"[D]uring the development of any non-trivial program, software structure is almost always created that cannot be determined from top-level software specifications" (ref. 8). Derived requirements, as described in DO-178B, were instituted for this reason, and should be tested as part of requirements-based testing. If the derived requirements are not documented appropriately, however, there will likely be no requirements-based tests for them; and, consequently, requirements coverage analysis has no documentation basis from which to say that the requirements-based tests are insufficient. The software structure or implementation detail, which is ideally documented as derived requirements, demands structural coverage analysis.

Different engineers may generate different, yet functionally equivalent, low-level requirements from the same set of high-level requirements. Likewise, different engineers may generate different, yet functionally equivalent, source code from the same set of low-level requirements. For example, a low-level requirement to assign to x twice the input value y may be coded as x := 2 \* y; x := y + y; or x := y / 0.5. Logical low-level requirements may likewise be implemented in a different yet equivalent manner. For example, a low-level requirement to monitor a stop light could be implemented as **Red\_On** := **Red\_Light**; or as **Red\_On** := **not Green\_Light and not Yellow\_Light**. The designer of the low-level requirements and the person testing the low-level requirements do not necessarily know the source code implemented code structure has been adequately tested and does not contain any unintended functionality. For a detailed example of the impact of code structure on coverage, see Chilenski's analysis of various

implementations of the type-of-triangle problem<sup>6</sup> in *An Investigation of Three Forms of the Modified Condition Decision Coverage (MCDC) Criterion* (ref. 4).

# 2.2.2 Structural Coverage Analysis

Structural coverage analysis provides a means to confirm that "the requirements-based test procedures exercised the code structure" (DO-178B, section 6.4.4). Recall that in the flow of testing activities, requirements coverage will have been accomplished and reviewed before structural coverage analysis begins. The subsequent structural coverage analysis reveals what source code structure has been executed with the requirements-based test cases. The RTCA/DO-248A<sup>7</sup> document *Second Annual Report for Clarification of DO-178B "Software Considerations in Airborne Systems and Equipment Certification"* (ref. 9) explains the intent of structural coverage analysis in the response to the Frequently Asked Question (FAQ #43) "What is the intent of structural coverage analysis?":

Sections 6.4.4.2 and 6.4.4.3 of DO-178B/ED-12B define the purpose of structural coverage analysis and the possible resolution for code structure that was not exercised during requirements-based testing.

The purpose of structural coverage analysis with the associated structural coverage analysis resolution is to complement requirements-based testing as follows:

- 1. Provide evidence that the code structure was verified to the degree required for the applicable software level;

- 2. Provide a means to support demonstration of absence of unintended functions;

- 3. Establish the thoroughness of requirements-based testing.

With respect to intended function, evidence that testing was rigorous and complete is provided by the combination of requirements-based testing (both normal range testing and robustness testing) and requirements-based test coverage analysis.

When drafting DO-178B/ED-12B, it was realized that requirements-based testing cannot completely provide this kind of evidence with respect to unintended functions. Code that is implemented without being linked to requirements may not be exercised by requirements-based tests. Such code could result in unintended functions. Therefore, something additional should be done since unintended functions could affect safety. A technically feasible solution was found in structural coverage analysis.

The rationale is that if requirements-based testing proves that all intended functions are properly implemented, and if structural coverage analysis demonstrates that all existing code is reachable and adequately tested, these two together provide a greater level of confidence that there are no unintended functions. Structural coverage analysis will:

- Indicate to what extent the requirements-based test procedures exercise the code structure; and

- Reveal code structure that was not exercised during testing.

<u>Note 1</u>: In the above text, the term "exercised during requirements-based testing" does not only mean that the specific code was exercised. It also means that the behavior of the code has been compared with the requirements to which it traces.

<sup>&</sup>lt;sup>6</sup> The type-of triangle problem is taken from Glenford Myers' (ref. 10) classic example of requirements for determining whether a triangle is scalene, equilateral, or isosceles based on the lengths of the sides of the triangle.

<sup>&</sup>lt;sup>7</sup> Information from RTCA/DO-248A is quoted throughout the tutorial with permission from the RTCA.

<u>Note 2</u>: Other papers on structural coverage analysis and the link between DO-178B/ED-12B and the FAR/JAR's may be found by using keyword index in Appendix C [of DO-248A].

The amount of code structure that has been exercised can be measured by different criteria. Several of these structural coverage criteria are discussed briefly in the next section.

# 2.3 Types of Structural Coverage

Typically structural coverage criteria are divided into two types: data flow and control flow. Data flow criteria measure the flow of data between variable assignments and references to the variables. Data flow metrics, such as all-definitions and all-uses (ref. 7), involve analysis of the paths (or subpaths) between the definition of a variable and its subsequent use. Because the DO-178B objectives for test coverage of software structure do not include explicit data flow criteria, the following discussion focuses on control flow.

Control flow criteria measure the flow of control between statements and sequences of statements. The structural coverage criteria in many standards, including DO-178B, are often control flow criteria. For control flow criteria, the degree of structural coverage achieved is measured in terms of statement invocations, Boolean expressions evaluated, and control constructs exercised. Table 1 gives the definitions of some common structural coverage measures based on control flow. A dot (•) indicates the criteria that applies to each type of coverage.

|                                                                                                    |                       |                      |                       | -                                  |       | 1                                 |

|----------------------------------------------------------------------------------------------------|-----------------------|----------------------|-----------------------|------------------------------------|-------|-----------------------------------|

| Coverage Criteria                                                                                  | Statement<br>Coverage | Decision<br>Coverage | Condition<br>Coverage | Condition/<br>Decision<br>Coverage | MC/DC | Multiple<br>Condition<br>Coverage |

| Every point of entry and exit in the program has been invoked at least once                        |                       | •                    | •                     | •                                  | •     | •                                 |

| Every statement in the program has been invoked at least once                                      | •                     |                      |                       |                                    |       |                                   |

| Every decision in the program has taken all possible outcomes at least once                        |                       | •                    |                       | •                                  | ٠     | •                                 |

| Every condition in a decision in the<br>program has taken all possible<br>outcomes at least once   |                       |                      | •                     | •                                  | •     | •                                 |

| Every condition in a decision has<br>been shown to independently affect<br>that decision's outcome |                       |                      |                       |                                    | ٠     | • <sup>8</sup>                    |

| Every combination of condition<br>outcomes within a decision has<br>been invoked at least once     |                       |                      |                       |                                    |       | •                                 |

Table 1. Types of Structural Coverage

<sup>&</sup>lt;sup>8</sup> Multiple condition coverage does not explicitly require showing the independent effect of each condition. This will be done, in most cases, by showing that every combination of decision inputs has been invoked. Note, however, that logical expressions exist wherein every condition cannot have an independent effect.

Three of the measures in Table 1 are found in objectives for test coverage given in DO-178B Table A-7 of Annex A<sup>9</sup>:

- objective 7 requires statement coverage for software levels A-C

- objective 6 requires decision coverage for software levels A-B

- objective 5 requires MC/DC for software level A

The structural coverage measures in Table 1 range in order from the weakest, statement coverage, to the strongest, multiple condition coverage. A brief description of each of the structural coverage measures in Table 1 is given in the following sections. For a more detailed description of each of these measures, see *The Art of Software Testing* (ref. 10).

#### 2.3.1 Statement Coverage

To achieve statement coverage, every executable statement in the program is invoked at least once during software testing. Achieving statement coverage shows that all code statements are reachable (in the context of DO-178B, reachable based on test cases developed from the requirements). Statement coverage is considered a weak criterion because it is insensitive to some control structures (ref. 11). Consider the following code segment (ref. 12):

- if (x > 1) and (y = 0) then z := z / x; end if;

- if (z = 2) or (y > 1) then z := z + 1; end if;

By choosing x = 2, y = 0, and z = 4 as input to this code segment, every statement is executed at least once. However, if an *or* is coded by mistake in the first statement instead of an *and*, the test case will not detect a problem. This makes sense because analysis of logic expressions is not part of the statement coverage criterion. According to Myers (ref. 10), "statement-coverage criterion is so weak that it is generally considered useless." At best, statement coverage should be considered a minimal requirement.

The remaining measures in Table 1 consider various aspects of decision logic as part of their criteria. To highlight differences between these measures, we will refer to the decision (A or B), where A and B are both conditions.

#### 2.3.2 Decision Coverage

Decision coverage requires two test cases: one for a *true* outcome and another for a *false* outcome. For simple decisions (i.e., decisions with a single condition), decision coverage ensures complete testing of control constructs. But, not all decisions are simple. For the decision (**A** or **B**), test cases (*TF*) and (*FF*) will toggle the decision outcome between *true* and *false*. However, the effect of **B** is not tested; that is, those test cases cannot distinguish between the decision (**A** or **B**) and the decision **A**.

#### 2.3.3 Condition Coverage

Condition coverage requires that each condition in a decision take on all possible outcomes at least once (to overcome the problem in the previous example), but does not require that the decision take on all

<sup>&</sup>lt;sup>9</sup> There are actually four objectives in Table A-7 for test coverage of software structure. Objective 8, requiring data coupling and control coupling for software levels A-C, is not addressed in this tutorial; but, is mentioned here for completeness.

possible outcomes at least once. In this case, for the decision (**A** or **B**) test cases (*TF*) and (*FT*) meet the coverage criterion, but do not cause the decision to take on all possible outcomes. As with decision coverage, a minimum of two tests cases is required for each decision.

### 2.3.4 Condition/Decision Coverage

Condition/decision coverage combines the requirements for decision coverage with those for condition coverage. That is, there must be sufficient test cases to toggle the decision outcome between *true* and *false* and to toggle each condition value between *true* and *false*. Hence, a minimum of two test cases are necessary for each decision. Using the example (**A** or **B**), test cases (*TT*) and (*FF*) would meet the coverage requirement. However, these two tests do not distinguish the correct expression (**A** or **B**) from the expression **A** or from the expression **B** or from the expression (**A** and **B**).

#### 2.3.5 Modified Condition/Decision Coverage

The MC/DC criterion enhances the condition/decision coverage criterion by requiring that each condition be shown to independently affect the outcome of the decision. The independence requirement ensures that the effect of each condition is tested relative to the other conditions. However, achieving MC/DC requires more thoughtful selection of the test cases, as will be discussed further in chapter 3, and, in general, a minimum of n+1 test cases for a decision with n inputs. For the example (**A** or **B**), test cases (*TF*), (*FT*), and (*FF*) provide MC/DC. For decisions with a large number of inputs, MC/DC requires considerably more test cases than any of the coverage measures discussed above.

#### 2.3.6 Multiple Condition Coverage

Finally, multiple condition coverage requires test cases that ensure each possible combination of inputs to a decision is executed at least once; that is, multiple condition coverage requires exhaustive testing of the input combinations to a decision. In theory, multiple condition coverage is the most desirable structural coverage measure; but, it is impractical for many cases. For a decision with n inputs, multiple condition coverage requires  $2^n$  tests.<sup>10</sup>

# 2.4 Structural Coverage versus Structural Testing

The distinction between structural coverage analysis and structural (or structure-based) testing is often misunderstood. Some of the confusion stems from the misguided notion that coverage is a testing method. But, the confusion is undoubtedly fueled by language in DO-178A<sup>11</sup> specifically referring to structure-based testing. According to DO-248A Discussion Paper #3 (ref. 9), "Basically, DO-178A/ED-12A requires that structural testing is carried out but does not define explicitly what type of structural testing is acceptable, nor does it define the scope of structural testing required for the different levels of software." Neither structural testing nor structure-based testing is mentioned in DO-178B.

To clarify the difference between structural coverage analysis and structural testing, DO-248A contains the following FAQ in response to the question "Why is structural testing not a DO-178B/ED-12B requirement?" (ref. 9, FAQ #44):

<sup>&</sup>lt;sup>10</sup> In the context of DO-178B, the number of inputs and the number of conditions in an expression can be different. For example, the expression (**A** and **B**) or (**A** and **C**) has three inputs, but four conditions, because each occurrence of **A** is considered a unique condition. The maximum number of possible test cases is always  $2^n$ , where *n* is the number of inputs, not the number of conditions.

<sup>&</sup>lt;sup>11</sup> DO-178A/ED-12A was the predecessor to DO-178B/ED-12B.

There is a distinction between structural coverage analysis and structural testing. The purpose of structural coverage analysis is to "determine which code structure was not exercised by the requirements-based test procedures" (reference DO-178B/ED-12B Section 6.4.4.2). Structural testing is the process of exercising software with test scenarios written from the source code, not from the requirements. Structural testing does not meet the DO-178B/ED-12B objective that all code structure is exercised by the requirements-based test procedures. The correct approach when structural coverage analysis identifies untested code is to consider the possible causes in accordance with DO-178B/ED-12B Section 6.4.4.3. If any additional testing is required, it should be requirements-based testing, using high-level, low-level, or derived requirements, as appropriate.

Structured<sup>12</sup> testing cannot find errors such as the non-implementation of some of the requirements. Since the starting point for developing structural test cases is the code itself, there is no way of finding requirements (high-level, low-level, or derived) not implemented in the code through structural tests. It is a natural tendency to consider outputs of the actual code (which is de facto the reference for structural testing) as the expected results. This bias cannot occur when expected outputs of a tested piece of code are determined by analysis of the requirements.

Since the code itself is used as the basis of the test cases, structural testing may fail to find simple coding errors.

Structural testing provides no information about whether the code is doing what it is *supposed* to be doing as specified in the requirements. With respect to control flow, structural testing does not provide any information as to whether the right decisions are being made for the right reasons. Finally, structural testing fails to assure that there are no unintended functions. In the best case, structural testing confirms that the object code and processor properly implement the source code.

# 2.5 More Details about Modified Condition/Decision Coverage

According to legend, there were once folks who advocated requiring 100% multiple condition coverage (that is, exhaustive testing) for level A software. The motivation was simple: testing all possible combinations of inputs for each decision ensures that the correct decision outcome is reached in all cases. The problem with such testing, however, is that for a decision with n inputs,  $2^n$  tests are required. In cases where n is small, running  $2^n$  tests may be reasonable; running  $2^n$  tests for large n is impracticable.

In avionics systems, complex Boolean expressions are common. Table 2 shows the number of Boolean expressions with n conditions for all of the logic expressions taken from the airborne software (written in Ada) of five different Line Replaceable Units (LRUs) from level A systems (ref. 4). The five LRUs came from five different airborne systems from two different airplane models in 1995 (two from one model and three from the other). As Chilenski's data shows, actual code has been written with more than 36 conditions.

|                                                              |       | Number of Conditions, <i>n</i> |     |     |     |     |    |       |       |       |  |  |

|--------------------------------------------------------------|-------|--------------------------------|-----|-----|-----|-----|----|-------|-------|-------|--|--|

| 1 2 3 4 5 6-10                                               |       |                                |     |     |     |     |    | 16-20 | 21-35 | 36-76 |  |  |

| Number of Boolean<br>expressions with <i>n</i><br>conditions | 16491 | 2262                           | 685 | 391 | 131 | 219 | 35 | 36    | 4     | 2     |  |  |

Table 2. Boolean Expression Profile for 5 Line Replaceable Units

<sup>&</sup>lt;sup>12</sup> Although the text of FAQ #44 that appears in DO-248A uses "Structured", the correct word for the FAQ (and the word intended by the subgroup that wrote the FAQ) is "Structural".

Clearly, multiple condition coverage is impractical for systems such as these. MC/DC attempts to provide a practical alternative. "The modified condition/decision coverage criterion was developed to achieve many of the benefits of multiple-condition testing while retaining the linear growth in required test cases of condition/decision testing. The essence of the modified condition/decision coverage criterion is that each condition must be shown to independently affect the outcome of this decision, i.e., one must demonstrate that the outcome of a decision changes as a result of changing a single condition." (ref. 13) MC/DC is intended to assure, with a high degree of confidence, that the verification process has shown that each condition in each decision in the source code has the proper effect.

*Exercise 2.5a*: Consider an expression with 36 inputs. How much time would it take to execute all of the test cases required for multiple condition coverage (exhaustive testing) of this expression if you could run 100 test cases per second?

*Exercise 2.5b*: If your test artifacts include a single line for the test results of each test case, how tall would the report be for test results for achieving multiple condition coverage for an expression with 36 inputs? (Assume 64 lines per sheet of paper, and 250 sheets of paper per inch height.)

# 2.5.1 A Note on Source versus Object Code Coverage

Structural coverage achieved at the source code level can differ from that achieved at the object code level. Depending on language and compiler features used, multiple object code statements can be generated from a single source code statement (ref. 8). According to Beizer, a test suite that provides 100% statement coverage at the source code level for a "good piece of logic-intensive modern code" might cover 75% or less of the statements at the object code level (ref. 7). Consequently, achieving MC/DC at the source code level does not guarantee MC/DC at the object code level, and vice versa.

For software levels A-C, structural coverage analysis may be performed on the source code (DO-178B, section 6.4.4.2b). For level A software, however, additional verification should be performed if the compiler generates object code not directly traceable to the source code statements. A common misconception exists that MC/DC must be performed on the object code if the compiler generates code that is not directly traceable to the source code. The additional verification should establish the correctness of the code sequences that are not directly traceable; that is, the requirement for additional analysis applies only to those object code segments that are not traceable. Issues related to source code to object code traceability are addressed in FAQ #41 and FAQ #42 in DO-248A and are being documented in FAA policy.

There has been debate as to whether structural coverage, MC/DC in particular, can be demonstrated by analyzing the object code in lieu of the source code. According to FAQ #42 in DO-248A (ref. 9), structural coverage, including MC/DC, can be demonstrated at the object code level...

as long as analysis can be provided which demonstrates that the coverage analysis conducted at the object code will be equivalent to the same coverage analysis at the source code level. In fact, for Level A software coverage, DO-178B/ED-12B Section 6.4.4.2b states that if "...*the compiler generates object code that is not directly traceable to Source Code statements. Then, additional verification should be performed on the object code..."* This is often satisfied by analyzing the object code to ensure that it is directly traceable to the source code. Hence, DO-178B/ED-12B determines the conditions for analysis of the source code for structural coverage, and it does not prevent one from performing analysis directly on the object code.

The analysis necessary to establish that coverage achieved at the object code level is equivalent to achieving the same level of coverage at the source code is *not* trivial in the general case. In some cases, however, showing equivalence may be simplified by using short-circuit control forms. According to FAQ #42 (ref. 9), compiler features such as short-circuit evaluation of Boolean expressions can be used to simplify the analysis.

"When utilizing compiler features to simplify analysis, one relies on the compiler to behave as expected. Therefore, one may need to qualify the compiler features being used as a verification tool. (See Section 12.2.2)."

Further information on source to object traceability is not included in this tutorial due to forthcoming policy from the FAA. However, further information on short-circuit control forms is presented in section 3.6.

# 2.6 Confounding Issues

The requirement to show the *independent* effect of each condition within a decision makes MC/DC unique among coverage criteria. Without any constraining definitions, determining whether a condition has independent effect might seem rather simple: a condition has independent effect when that condition *alone* determines the outcome of the decision. At first glance, this simple definition seems to be consistent with the intent of MC/DC. Whether the simple notion is truly consistent with DO-178B, however, requires knowing the full DO-178B definition<sup>13</sup> of MC/DC plus the definitions for *condition* and *decision* (ref. 2).

<u>Condition</u>-A Boolean expression containing no Boolean operators.

<u>Decision</u>–A Boolean expression composed of conditions and zero or more Boolean operators. A decision without a Boolean operator is a condition. If a condition appears more than once in a decision, each occurrence is a distinct condition.

<u>Modified Condition/Decision Coverage</u>-Every point of entry and exit in the program has been invoked at least once, every condition in a decision in the program has taken all possible outcomes at least once, every decision in the program has taken all possible outcomes at least once, and each condition in a decision has been shown to independently affect that decision's outcome. A condition is shown to independently affect a decision's outcome by varying just that condition while holding fixed all other possible conditions.

These definitions raise a number of confounding issues when determining whether a set of test cases provides MC/DC.

The first issue involves the meaning of "condition". Without the last sentence in the definition of decision, most people would probably say that the decision (**A** and **B**) or (**A** and **C**), where **A**, **B**, and **C** are conditions set by the software, contains three conditions—**A**, **B**, and **C**. According to the last sentence of the definition, however, this decision contains four conditions: the first **A**, **B**, **C**, and the second **A**. The first occurrence of **A** is said to be *coupled* with the second occurrence of **A** because a change to one condition affects the other. According to the definition of MC/DC above, showing independent effect in this example requires, among other things, showing what happens when the value of the first **A** is held constant, while the value of the second **A** is toggled between *false* and *true*. This typically cannot be accomplished in any meaningful way.

<sup>&</sup>lt;sup>13</sup> We are using the word "definition" loosely. A strong case can be made that the Glossary entries provide, at best, descriptions rather than definitions. Because the distinction between "definition" and "description" is probably not important to most readers of this tutorial, we ignore it everywhere except this footnote.

The next issue involves the scope of "within a decision". For example, consider the following code statements:

| A:=B  or  C;     | (statement 1) |

|------------------|---------------|

| E := A and $D$ ; | (statement 2) |

These two statements are logically equivalent to:

E:=(B or C) and D; (statement 3)

Statements 1, 2, and 3 all contain decisions, even though none of the statements are branch points such as an *if* statement. That is, a decision is not synonymous with a branch point. MC/DC applies to all decisions—not just those within a branch point.

Further, a test set that provides MC/DC for statements 1 and 2 individually will not necessarily provide MC/DC for statement 3. That is, if a complex decision statement is decomposed into a set of less complex (but logically equivalent) decision statements, providing MC/DC for the parts is not always equivalent to providing MC/DC for the whole. For the example above, tests (*TFT*), (*FTF*), and (*FFT*) for (**B**,**C**,**D**) provide MC/DC for statements 1 and 2 individually, but do not provide MC/DC for statement 3.

The final issue involves the concept of independent effect. Showing that a condition independently affects a decision's outcome by varying just that condition while holding all others fixed is commonly referred to as the unique-cause approach to MC/DC. This approach ensures that the effect of each condition is tested relative to the other conditions without requiring analysis of the logic of each decision (that is, if changing the value of a single condition causes the value of the decision outcome to change, then the single condition is assumed to be the cause for the change—no further analysis is needed). Historically, the unique-cause approach has often been the only acceptable means of showing the independent effect of a condition. The unique-cause approach cannot be applied, however, to decisions where there are repeated or strongly coupled conditions; e.g., (A and B) or (A and C).

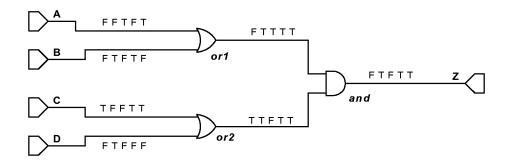

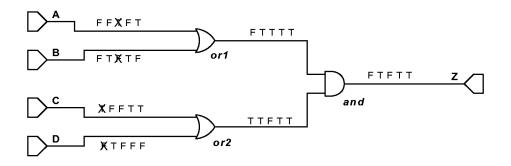

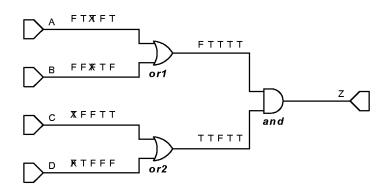

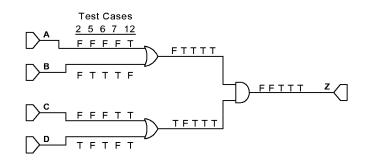

The unique-cause approach commonly is taught by presenting a truth table for an expression; for example, the decision  $\mathbf{Z}:=(\mathbf{A} \text{ or } \mathbf{B}) \text{ and } (\mathbf{C} \text{ or } \mathbf{D})$  shown in Table 3. In the truth table approach, test cases that provide MC/DC are selected by identifying pairs of rows where only one condition and the decision outcome change values between the two rows. In Table 3, the columns shaded in gray indicate the independence pairs for each condition. For example, test case 2 coupled with test case 10 together demonstrate the independent effect of  $\mathbf{A}$ , because  $\mathbf{A}$  is the only condition that has changed value along with the change in value of the outcome  $\mathbf{Z}$ . Although the truth table is a simple approach to showing the independent effect of a condition, the truth table approach suffers from a number of limitations: (a) the truth table is unwieldy for large logical expressions; and, for a logical expression at a time; and, (c) the truth table does not connect the inputs and outputs from the requirements-based tests with the source code structure.

The approach to MC/DC given in this tutorial differs from the traditional approach and mitigates many of the difficulties described above. The approach, presented in the next chapter, requires analysis of the logic of a decision to confirm independent effect of the conditions. This analysis (which goes beyond that required for the unique-cause approach) has the advantages of (a) allowing more test cases to meet the MC/DC criteria than unique cause (which may make confirming MC/DC easier), (b) applying to decisions with coupled conditions that frequently occur in avionics applications, and (c) having capability equivalent to the unique-cause approach to detect errors (see Appendix B).

|    | 11 |   |   |   |  |   |  |    |   |    |    |

|----|----|---|---|---|--|---|--|----|---|----|----|

|    | Α  | В | C | D |  | Z |  | A  | B | С  | D  |

| 1  | F  | F | F | F |  | F |  |    |   |    |    |

| 2  | F  | F | F | Т |  | F |  | 10 | 6 |    |    |

| 3  | F  | F | Τ | F |  | F |  | 11 | 7 |    |    |

| 4  | F  | F | Τ | T |  | F |  | 12 | 8 |    |    |

| 5  | F  | Т | F | F |  | F |  |    |   | 7  | 6  |

| 6  | F  | Τ | F | Т |  | Т |  |    | 2 |    | 5  |

| 7  | F  | Т | Τ | F |  | Т |  |    | 3 | 5  |    |

| 8  | F  | Т | Т | T |  | Т |  |    | 4 |    |    |

| 9  | Т  | F | F | F |  | F |  |    |   | 11 | 10 |

| 10 | Т  | F | F | Т |  | Τ |  | 2  |   |    | 9  |

| 11 | Т  | F | Т | F |  | Т |  | 3  |   | 9  |    |

| 12 | T  | F | Τ | T |  | Τ |  | 4  |   |    |    |

| 13 | T  | Τ | F | F |  | F |  |    |   | 15 | 14 |

| 14 | T  | Τ | F | T |  | T |  |    |   |    | 13 |

| 15 | Т  | Τ | Т | F |  | Т |  |    |   | 13 |    |

| 16 | T  | Τ | Τ | T |  | T |  |    |   |    |    |

Table 3. Truth Table Approach to MC/DC

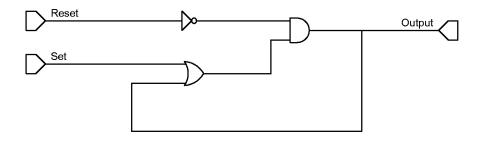

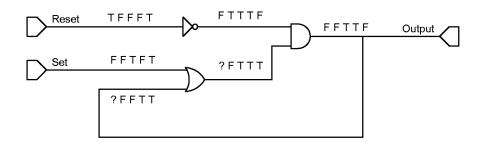

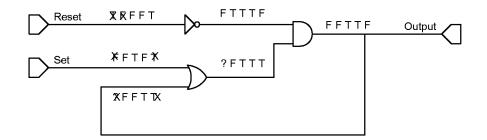

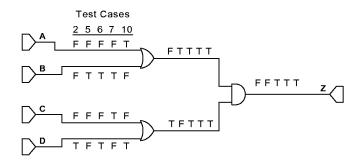

# 3 MC/DC Approach

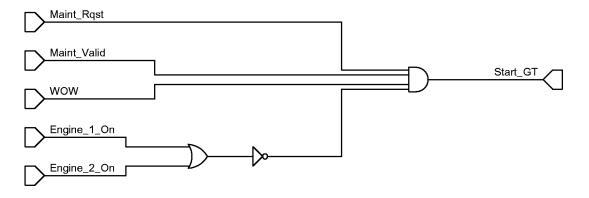

This chapter presents a practical approach based on gate-level representations of logic constructs for evaluating whether a given set of requirements-based test cases conforms with three of the four requirements for  $MC/DC^{14}$ :

- every decision in the program has taken all possible outcomes at least once

- every condition in a decision in the program has taken all possible outcomes at least once

- every condition in a decision has been shown to independently affect that decision's outcome

The MC/DC approach for the tutorial was selected because it requires an explicit mapping of the requirements-based tests to the source code structure. This approach applies to any source code written regardless of whether it is in a high-level language such as Ada or in assembly language. Mapping requirements-based test cases to source code structure reinforces the notion that structural coverage analysis is a check on the adequacy of requirements-based tests for a given source code implementation. The approach also capitalizes on several concepts familiar to engineers, including a schematic representation of the source code (which allows you to see everything needed for assessing MC/DC on one page), and the hardware testing concepts of controllability and observability.

The MC/DC approach provides simple steps that allow a certification authority or verification analyst to evaluate MC/DC claims without the aid of a coverage tool. The steps can also be used to help confirm that a tool properly assesses MC/DC. The MC/DC approach in this chapter does not evaluate the correctness of existing requirements-based tests—it is assumed that these tests have been reviewed adequately for correctness and coverage of the requirements. The purpose of the approach, however, is to determine if existing requirements-based test cases provide the level of rigor required to achieve MC/DC

<sup>&</sup>lt;sup>14</sup> The fourth requirement for meeting MC/DC, testing of entry and exit points, is common to all structural coverage measures, except for statement coverage, and, as such, is not critical to a discussion of MC/DC.

# of the source code. This approach is *not* intended to be the only method for determining compliance with the MC/DC objective, but rather a method to be added to your array of review techniques.

This chapter is divided into eight sections. Section 3.1 discusses basic building blocks that are fundamental to the MC/DC approach. Section 3.2 presents the steps of the approach. Sections 3.3-3.7 address how to apply the approach to different scenarios, such as grouped functionality, short-circuit control forms, and bit-wise operations. Finally, resolving errors or shortcomings identified through the structural coverage analysis is discussed in section 3.8.

# 3.1 MC/DC Building Blocks ("how do I test a ...?")

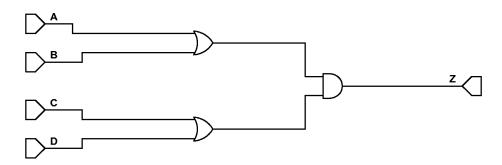

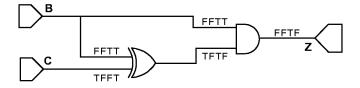

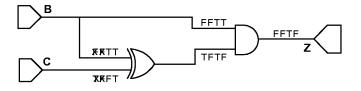

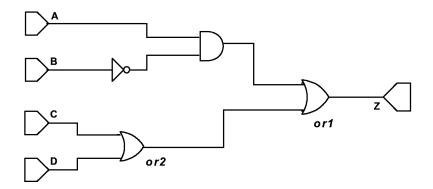

Understanding how to test individual logical operators, such as a logical expression with a single *and* operator, is essential to understanding MC/DC. In this tutorial, logical operators are shown schematically as logical gates; and, the terms "logical operator" and "gate" are used interchangeably. Table 4 shows the schematic representation of the elementary logical operators: *and*, *or*, *xor*, and *not*.

| Name     | Schematic Representation | Code example         | Truth Table                                  |

|----------|--------------------------|----------------------|----------------------------------------------|

| Input    |                          |                      |                                              |

| Output   | <u>د</u>                 |                      |                                              |

| and Gate |                          | C := A and B;        | <mark>АВС</mark><br>ТТТТ<br>FF<br>FTF<br>FFF |

| or Gate  |                          | C := A <i>or</i> B;  | <u>АВС</u><br>ТТТТ<br>ГГТТ<br>FТТ<br>FFF     |

| xor Gate |                          | C := A <i>xor</i> B; | <u>АВС</u><br>ТТF<br>ТFТ<br>FT<br>FFF        |

| not Gate |                          | B := not A;          | <u>А В</u><br>Т F<br>F T                     |

Table 4. Representations for Elementary Logical Expressions

According to Chilenski and Miller, showing that each logical condition independently affects a decision's outcome requires specific minimal test sets for each logical operator (ref. 13). Knowing the minimal test sets for each logical operator provides the basis for determining compliance with the MC/DC objective. Here, the *and* gate, *or* gate, *xor* gate, and the *not* gate are considered to be basic constructs. Given the test requirements for these basic constructs, more complex constructs containing Boolean expressions can be examined, including a comparator, *if* statement, and *loop* statements. Minimum testing requirements and a tabular example for each of these constructs are described below.

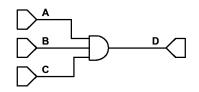

## 3.1.1 and Gate

Minimum testing to achieve MC/DC for an *and* gate requires the following:

- (1) All inputs are set *true* with the output observed to be *true*. This requires one test case for each *n*-input *and* gate.

- (2) Each and every input is set exclusively *false* with the output observed to be *false*. This requires *n* test cases for each *n*-input *and* gate.

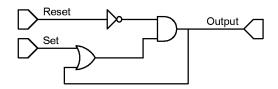

The requirements make sense when considering how an *and* gate works. Changing a single condition starting from a state where all inputs are *true* will change the outcome; that is, an *and* gate is sensitive to any *false* input. Hence, a specific set of n+1 test cases is needed for an *n*-input *and* gate. These specific n+1 test cases meet the intent of MC/DC by demonstrating that the *and* gate is correctly implemented.

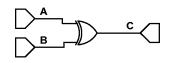

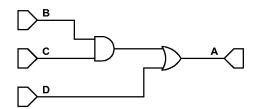

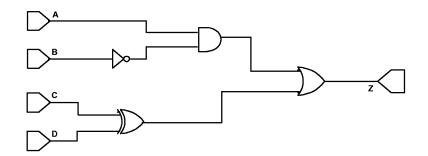

An example of the minimum testing required for a three-input *and* gate (shown in Figure 3) is given in Table 5. In this example, test case 1 in Table 5 provides the coverage for (1) above, and test cases 2-4 provide coverage for (2).

Figure 3. Three-input and gate.

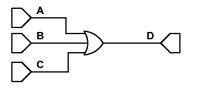

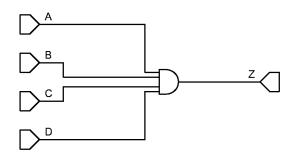

#### 3.1.2 or Gate

Minimum testing to achieve MC/DC for an *or* gate requires the following:

- (1) All inputs are set *false* with the output observed to be *false*. This requires one test case for each *n*-input *or* gate.

- (2) Each and every input is set exclusively *true* with the output observed to be *true*. This requires *n* test cases for each *n*-input *or* gate.

These requirements are based on an *or* gate's sensitivity to a *true* input. Here again, n+1 specific test cases are needed to test an *n*-input *or* gate. These specific n+1 test cases meet the intent of MC/DC by demonstrating that the *or* gate is correctly implemented.

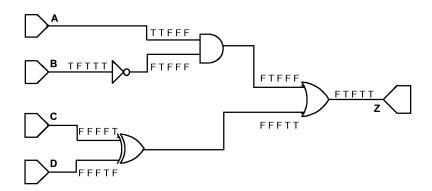

An example of the minimum testing required for a three-input or gate (shown in Figure 4) is given in Table 6. In this example, test case 1 provides the coverage for (1) while test cases 2-4 provide the coverage for (2).

Table 5. Minimum Tests for Three-input and Gate

| Test Case Number | 1 | 2 | 3 | 4 |

|------------------|---|---|---|---|

| Input <b>A</b>   | Т | F | Т | Т |

| Input B          | Т | Т | F | Т |

| Input <b>C</b>   | Т | Т | Т | F |

| Output D         | Т | F | F | F |

Figure 4. Three-input or gate.

#### 3.1.3 xor Gate

Table 6. Minimum Tests for a Three-input or Gate

| Test Case Number | 1 | 2 | 3 | 4 |

|------------------|---|---|---|---|

| Input <b>A</b>   | F | Т | F | F |

| Input <b>B</b>   | F | F | Т | F |

| Input <b>C</b>   | F | F | F | Т |

| Output <b>D</b>  | F | Т | Т | Т |

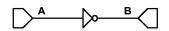

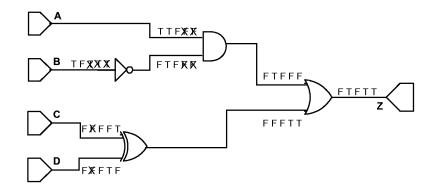

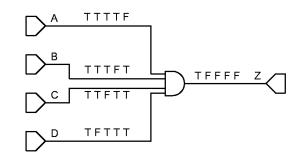

The *xor* gate differs from both the *and* and the *or* gates with respect to MC/DC in that there are multiple minimum test sets for an *xor*. Consider the two-input *xor* gate shown in Figure 5. All of the possible test cases for this *xor* gate are shown in Table 7. For a two-input *xor* gate, any combination of three test cases will provide MC/DC.

Figure 5. Two-input *xor* gate.

Table 7. Test Cases for a Two-input xor Gate

| Test Case Number | 1 | 2 | 3 | 4 |

|------------------|---|---|---|---|

| Input <b>A</b>   | T | Т | F | F |

| Input <b>B</b>   | T | F | Т | F |

| Output <b>C</b>  | F | Т | Т | F |

Hence, minimum testing to meet the definition of MC/DC for a two-input *xor* gate requires one of the following sets of test cases from Table 7:

- (1) test cases 1, 2, and 3

- (2) test cases 1, 2, and 4

- (3) test cases 1, 3, and 4

- (4) test cases 2, 3, and 4

Note that for a test set to distinguish between an *or* and an *xor* gate it must contain test case 1 in Table 7. Hence, test sets 1, 2, and 3 above can detect when an *or* is coded incorrectly for an *xor*, and vice versa. While not explicitly required by MC/DC, elimination of test set 4 as a valid test set is worth considering.

Note also that minimum tests to achieve MC/DC for an *xor* gate with more than two inputs are implementation dependent. Hence, no single set of rules applies universally to an *xor* gate with more than two inputs.

## 3.1.4 not Gate

The logical *not* works differently from the previous gates: the *not* works only on a single operand. That operand may be a single condition or a logical expression. But, with respect to a gate level representation, there is a single input to the *not* gate as shown in Figure 6.

Figure 6. not gate.

Minimum testing to achieve MC/DC for a logical *not* requires the following:

- (1) The input is set *false* with the output observed to be *true*.

- (2) The input is set *true* with the output observed to be *false*.

#### 3.1.5 Comparator

A comparator evaluates two numerical inputs and returns a Boolean based on the comparison criteria. Within the context of DO-178B, a comparator is a condition and also a simple decision. The following comparison criteria are considered in this tutorial:

- less than

- greater than

- less than or equal to

- greater than or equal to

- equal to

- not equal to

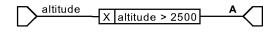

In general, the comparison point can be a constant or another variable (see Figure 7).

Figure 7. Two types of comparators.

In either case, two test cases will confirm MC/DC for a comparator—one test case with a *true* outcome, and one test case with a *false* outcome. Hence, minimum testing for a comparator requires the following:

- (1) Input x set at a value above the comparison point (or y)

- (2) Input x set at a value below the comparison point (or y)

However, the numerical aspects of a comparator must also be considered in determining reasonable tests. For example, given a software requirement to test ( $x \le 5000$ ), one test case with a *true* outcome (e.g., x = -30000), and one test case with a *false* outcome (e.g., x = 30000) provide MC/DC. However, these cases do not confirm that the design is accurately implemented in the source code. Specifically in this example, the test cases do not confirm that 5000 is the correct comparison point or less-than-or-equal-to is the appropriate relational operator. The source code could have been implemented as x < -5000 or as  $x \le 500$  and still pass the test cases.

Selecting two test cases closer to the comparison point is better, but does not cover certain coding errors. For example, test cases with x = 5000 and x = 5001 are better, but they will not detect a coding error of x = 5000.

In general, three test cases are needed to assure that simple coding errors have not been made; that is,

that the correct relational operator and comparison point are used in the code. So, while MC/DC only requires two tests, minimum *good* requirements-based testing for a comparator requires:

- (1) Input x set at a value slightly above the comparison point

- (2) Input x set at a value slightly below the comparison point

- (3) Input x set at a value equal to the comparison point

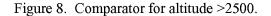

The definition of "slightly" is determined by engineering judgement based on the numerical resolution of the target computer, the test equipment driving the inputs, and the resolution of the output device. Consider for example, the following set of test cases for a design that sets the output **A** *true* when altitude is greater than 2500 (see Figure 8 and Table 8).

| Test Case Number | 1  | 2     | 3    | 4    | 5    |

|------------------|----|-------|------|------|------|

| Input altitude   | 25 | 32000 | 2500 | 2499 | 2501 |

| Output <b>A</b>  | F  | Т     | F    | F    | Т    |

Test cases 1 and 2 give the desired MC/DC output. However, those test cases do not confirm that the toggle occurred at 2500, and not elsewhere. Even adding test case 3 does not improve the test suite much. The design could have been implemented with a comparison point anywhere between 2501 and 32000, and give the same result for test cases 1, 2, and 3. Test cases 3, 4, and 5 are a better set, because this set confirms that the transition occurs at 2500.

#### 3.1.6 If-then-else Statement

The *if-then-else* statement is a switch that controls the execution of the software. Consider the following example where x, y, and z are integers and C is a Boolean:

if C then z := x else z := y;

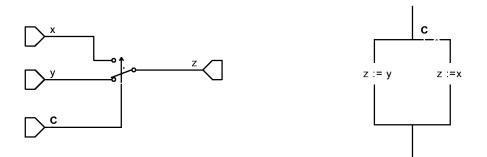

Two different schematic representations of this code are shown in Figure 9.

Figure 9. Two *if-then-else* constructs.

Minimum testing for the *if-then-else* statement requires the following:

- (1) Inputs that force the execution of the *then* path (that is, the decision evaluates to *true*)

- (2) Inputs that force the execution of the *else* path (that is, the decision evaluates to *false*). Note that the decision must evaluate to *false* with confirmation that the *then* path did not execute, even if there is no *else* path.

- (3) Inputs to exercise any logical gates in the decision as required by sections 3.1.1-3.1.5

For example, for a single condition Z, the statement *if* Z *then...else...* requires only two test cases to achieve MC/DC. The decision in *if* X or Y or Z *then... else...* requires four test cases to achieve MC/DC. A minimal test set for the statement *if* Z *then* a := x *else* a := y is shown in Table 9.

| Test Case Number |                               |                               |  |  |

|------------------|-------------------------------|-------------------------------|--|--|

|                  | Traverse the <i>then</i> path | Traverse the <i>else</i> path |  |  |

| Input x          | 12                            | 18                            |  |  |

| Input y          | 50                            | 34                            |  |  |

| Input <b>Z</b>   | Т                             | F                             |  |  |

| Output a         | 12                            | 34                            |  |  |

Table 9. Minimum tests for *if Z* then a := x else a := y

Note that a *case* statement may be handled similarly to the *if-then-else* statement.

## 3.1.7 Loop Statements

Loop statements are constructs that cause a sequence of statements to be executed zero or more times. Constructs such as the *while loop* and the *for loop* are switches to control the execution of the software similar to an *if-then-else* construct. In the context of MC/DC, the challenge is to confirm that loops have been traversed appropriately.

## While Loop

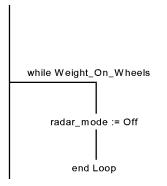

Consider the following example where **Weight\_On\_Wheels** is a Boolean:

```

while Weight_On_Wheels loop

radar_mode := Off;

end loop;

```

A schematic representation of this code is shown in Figure 10. In this case, **Weight\_On\_Wheels** is the decision for the *while loop* construct.

Figure 10. while loop construct.

Minimum testing for the *while loop* requires the following:

(1) Inputs to force the execution of the statements in the loop (that is, the decision evaluates to *true*)

- (2) Inputs to force the exit of the loop (that is, the decision evaluates to *false*)

- (3) Inputs to exercise any logical gates in the decision as required by sections 3.1.1-3.1.5

In Figure 10, two test cases may be used to achieve MC/DC. One test case confirms that radar\_mode remains off as long as **Weight\_On\_Wheels** is *true*. The second test case confirms that radar\_mode could be set to something other than off when **Weight\_On\_Wheels** is *false*. In the case where **Weight\_On\_Wheels** is replaced by a Boolean expression, the Boolean expression would also need to be evaluated, and the setting of radar\_mode to off confirmed, by the methods previously described in sections 3.1.1-3.1.5.

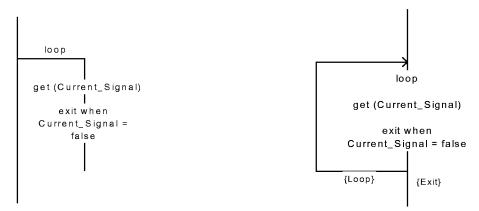

# <u>Exit when</u>

Not all decisions must appear at the start of a loop. The *exit when* statement can be used anywhere within a *loop* construct or a *for loop* to terminate the execution of the loop.<sup>15</sup> Consider the following example of a *loop* statement with an *exit when* condition. In this example, **Current\_Signal** = *false* is the decision (see Figure 11).

loop

get (Current\_Signal); exit when Current\_Signal = false; end loop;

Minimum testing for the *exit when* statement requires the following:

(1) Inputs to force the repeated execution of the statements in the loop when the decision for the *exit when* evaluates to *false*

<sup>&</sup>lt;sup>15</sup> The Ada language permits multiple *exit when* statements within a loop. Because this may be interpreted as violating the single exit principle in software engineering, some developers may restrict the use of *exit when* statements.

- (2) Inputs to force the immediate exit of the loop when the decision for the *exit when* evaluates to *true*

- (3) Inputs to exercise any logical gates in the decision as required by sections 3.1.1-3.1.5

Figure 11. Two types of exit when statements.

# 3.2 Evaluation Method

The minimum test requirements in section 3.1 establish the inputs and expected output for individual logical operators necessary to confirm that:

- the decision has taken all possible outcomes at least once,

- every condition in the decision has taken all possible outcomes at least once, and

- every condition in the decision independently affects the decision's outcome.

Only one minimum test set will provide MC/DC when the only operator in the decision is an *and*, and only one minimum test set will provide MC/DC when the only operator in the decision is an *or*; however, a number of different test sets will meet the minimum test requirements when the operator is an *xor*.

Confirming MC/DC for a decision with mixed logical operators, such as (**A** or **B**) and (**C** or **D**), is complicated by the fact that the output from one logical operator may mask the output of another logical operator. For example, any *false* input to an *and* gate masks all other inputs; that is, the output of the *and* gate will be *false* regardless of the other inputs. Similarly, any *true* input to an *or* gate masks all other inputs; a *true* input will cause the output to be *true* regardless of the other inputs.

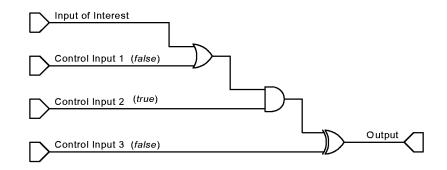

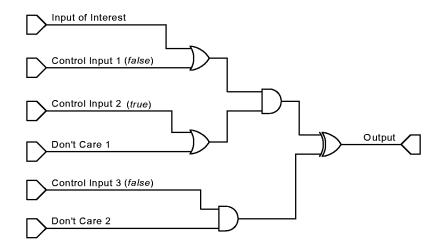

Two concepts taken from testing logic circuits are helpful in understanding MC/DC for complex logical expressions: controllability and observability (ref. 14). For software, controllability can be described loosely as the ability to test each logical operator of an expression by setting the values of the expression's inputs (this corresponds to meeting the minimum test requirements in section 3.1). Observability refers to the ability to propagate the output of a logical operator under test to an observable point.

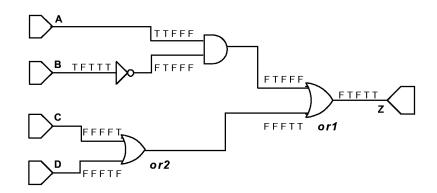

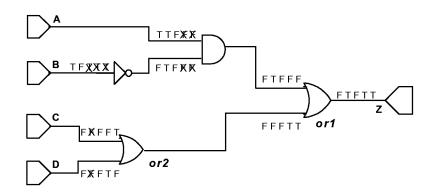

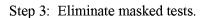

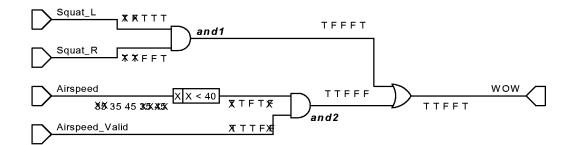

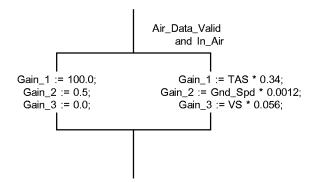

To evaluate MC/DC using the gate-level approach, each logical operator in a decision in the source code is examined to determine whether the requirements-based tests have observably exercised the operator using the minimum tests from section 3.1. This approach, which applies to both decisions with

common logical operators and decisions with mixed logical operators, involves the following five steps:

- (1) Create a schematic representation of the source code.

- (2) Identify the test inputs used. Test inputs are obtained from the requirements-based tests of the software product.

- (3) Eliminate masked test cases. A masked test case is one whose results for a specific gate are hidden from the observed outcome.

- (4) Determine MC/DC based on the building blocks discussed in section 3.1.

- (5) Finally, examine the outputs of the tests to confirm correct operation of the software. This step may seem redundant because this confirmation is accomplished in the comparison of the requirements-based test cases and results with the requirements. However, if the expected result in the test case does not match the output expected based on the gate representation of the code, an error is indicated, either in the source code or in its schematic representation.

Each of these steps is described below.

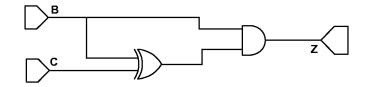

# 3.2.1 Source Code Representation

In the first step of the process, a schematic representation of the software is generated. The symbols used to represent the source code are not important, so long as they are consistent. For this tutorial, the symbols shown in Table 4 and Table 10 are used.

The following example is used to illustrate the steps of the evaluation method, starting with the source code representation.

**Example 1.** Consider the following line of source code:

A := (B and C) or D;

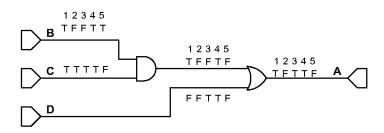

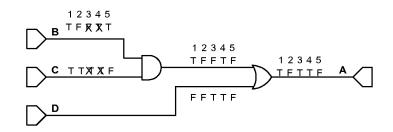

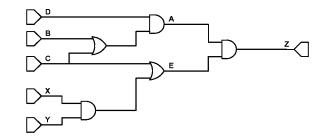

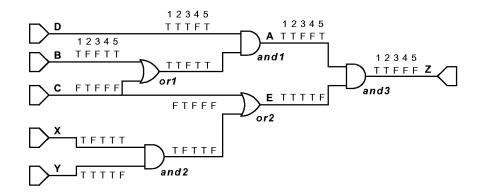

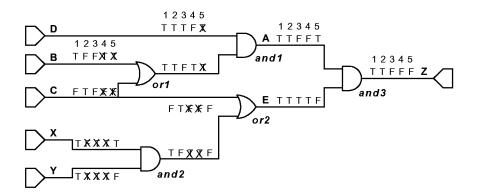

This source code is shown schematically in Figure 12.

Figure 12. Schematic representation of example 1 source code.

| Name                                                   | Schematic Representation                         | Code example                                                                    |

|--------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|

| Comparator<br>(x with constant)                        | X X x > constant                                 | A := x > constant;                                                              |

| Comparator<br>(x with y)                               |                                                  | <b>A</b> := x > y;                                                              |

| Summer<br>(addition or<br>subtraction may be<br>shown) |                                                  | z := x + y;                                                                     |

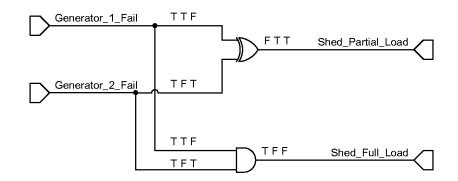

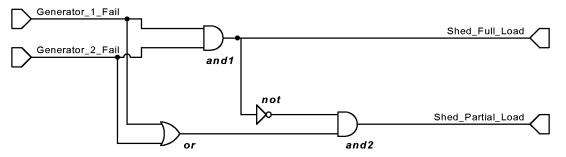

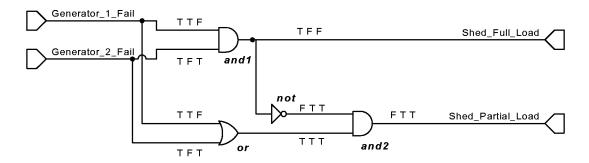

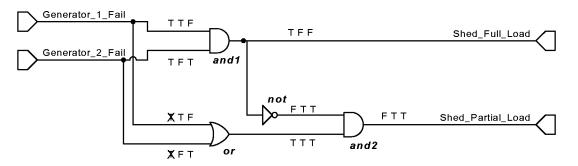

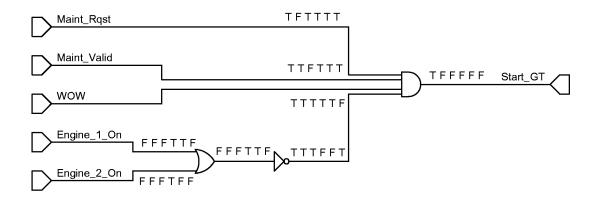

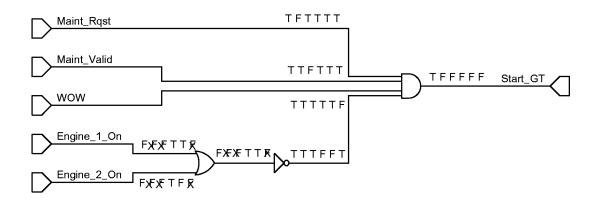

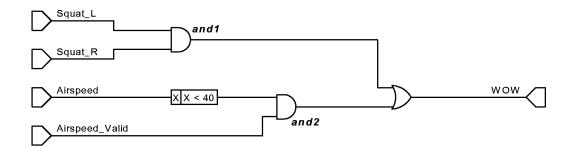

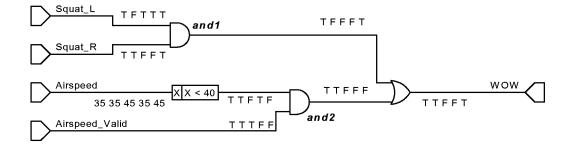

| Multiplier                                             |                                                  | z := x * y;                                                                     |