NASA/CR-2003-212161

# A Comparison of Bus Architectures for Safety-Critical Embedded Systems

John Rushby SRI International, Menlo Park, California

March 2003

Since its founding, NASA has been dedicated to the advancement of aeronautics and space science. The NASA Scientific and Technical Information (STI) Program Office plays a key part in helping NASA maintain this important role.

The NASA STI Program Office is operated by Langley Research Center, the lead center for NASA's scientific and technical information. The NASA STI Program Office provides access to the NASA STI Database, the largest collection of aeronautical and space science STI in the world. The Program Office is also NASA's institutional mechanism for disseminating the results of its research and development activities. These results are published by NASA in the NASA STI Report Series, which includes the following report types:

- TECHNICAL PUBLICATION. Reports of completed research or a major significant phase of research that present the results of NASA programs and include extensive data or theoretical analysis. Includes compilations of significant scientific and technical data and information deemed to be of continuing reference value. NASA counterpart of peer-reviewed formal professional papers, but having less stringent limitations on manuscript length and extent of graphic presentations.

- TECHNICAL MEMORANDUM. Scientific and technical findings that are preliminary or of specialized interest, e.g., quick release reports, working papers, and bibliographies that contain minimal annotation. Does not contain extensive analysis.

- CONTRACTOR REPORT. Scientific and technical findings by NASA-sponsored contractors and grantees.

- CONFERENCE PUBLICATION. Collected papers from scientific and technical conferences, symposia, seminars, or other meetings sponsored or co-sponsored by NASA.

- SPECIAL PUBLICATION. Scientific, technical, or historical information from NASA programs, projects, and missions, often concerned with subjects having substantial public interest.

- TECHNICAL TRANSLATION. Englishlanguage translations of foreign scientific and technical material pertinent to NASA's mission.

Specialized services that complement the STI Program Office's diverse offerings include creating custom thesauri, building customized databases, organizing and publishing research results ... even providing videos.

For more information about the NASA STI Program Office, see the following:

- Access the NASA STI Program Home Page at http://www.sti.nasa.gov

- E-mail your question via the Internet to help@sti.nasa.gov

- Fax your question to the NASA STI Help Desk at (301) 621–0134

- Phone the NASA STI Help Desk at (301) 621–0390

- Write to: NASA STI Help Desk NASA Center for AeroSpace Information 7121 Standard Drive Hanover, MD 21076–1320

NASA/CR-2003-212161

## A Comparison of Bus Architectures for Safety-Critical Embedded Systems

John Rushby SRI International, Menlo Park, California

National Aeronautics and Space Administration

Langley Research Center Hampton, Virginia 23681–2199 Prepared for Langley Research Center under Cooperative Agreement NCC1-377

#### Acknowledgments

I am grateful for helpful comments received from Bruno Dutertre, Kurt Liebel, Paul Miner, Ginger Shao, and Christian Tanzer.

The use of trademarks or names of manufacturers in this report is for accurate reporting and does not constitute an official endorsement, either expressed or implied, of such products or manufacturers by the National Aeronautics and Space Administration

Available from:

ĺ

NASA Center for AeroSpace Information (CASI) 7121 Standard Drive Hanover, MD 21076–1320 (301) 621–0390 National Technical Information Service (NTIS) 5285 Port Royal Road Springfield, VA 22161–2171 (703) 605–6000

#### Abstract

Avionics and control systems for aircraft use distributed, fault-tolerant computer systems to provide safety-critical functions such as flight and engine control. These systems are becoming *modular*, meaning that they are based on standardized architectures and components, and *integrated*, meaning that some of the components are shared by different functions—of possibly different criticality levels.

The modular architectures that support these functions must provide mechanisms for coordinating the distributed components that provide a single function (e.g., distributing sensor readings and actuator commands appropriately, and assisting replicated components to perform the function in a fault-tolerant manner), while protecting functions from faults in each other. Such an architecture must tolerate hardware faults in its own components and must provide very strong guarantees on the correctness and reliability of its own mechanisms and services.

One of the essential services provided by this kind of modular architecture is communication of information from one distributed component to another, so a (physical or logical) communication bus is one of its principal components, and the protocols used for control and communication on the bus are among its principal mechanisms. Consequently, these architectures are often referred to as *buses* (or *databuses*), although this term understates their complexity, sophistication, and criticality.

The capabilities once found in aircraft buses are becoming available in buses aimed at the automobile market, where the economies of scale ensure low prices. The low price of the automobile buses then renders them attractive to certain aircraft applications—provided they can achieve the safety required.

In this report, I describe and compare the architectures of two avionics and two automobile buses in the interest of deducing principles common to all of them, the main differences in their design choices, and the tradeoffs made. The avionics buses considered are the Honeywell SAFEbus (the backplane data bus used in the Boeing 777 Airplane Information Management System) and the NASA SPIDER (an architecture being developed as a demonstrator for certification under the new DO-254 guidelines); the automobile buses considered are the TTTech Time-Triggered Architecture (TTA), recently adopted by Audi for automobile applications, and by Honeywell for avionics and aircraft control functions, and FlexRay, which is being developed by a consortium of BMW, DaimlerChrysler, Motorola, and Philips.

I consider these buses from the perspective of their fault hypotheses, mechanisms, services, and assurance.

## Contents

| 1 | Intro | oductio     | n                                      | 1    |  |  |  |

|---|-------|-------------|----------------------------------------|------|--|--|--|

| 2 | Com   | nparison 11 |                                        |      |  |  |  |

|   | 2.1   | The Fo      | our Buses                              | . 11 |  |  |  |

|   |       | 2.1.1       | SAFEbus                                | . 11 |  |  |  |

|   |       | 2.1.2       | ΤΤΑ                                    | . 12 |  |  |  |

|   |       | 2.1.3       | SPIDER                                 | . 12 |  |  |  |

|   |       | 2.1.4       | FlexRay                                | . 13 |  |  |  |

|   | 2.2   | Fault H     | Typothesis and Fault Containment Units | . 13 |  |  |  |

|   |       | 2.2.1       | SAFEbus                                |      |  |  |  |

|   |       | 2.2.2       | ΤΤΑ                                    | . 18 |  |  |  |

|   |       | 2.2.3       | SPIDER                                 | . 19 |  |  |  |

|   |       | 2.2.4       | FlexRay                                | . 20 |  |  |  |

|   | 2.3   | Clock       | Synchronization                        |      |  |  |  |

|   |       | 2.3.1       | SAFEbus                                | . 21 |  |  |  |

|   |       | 2.3.2       | ΤΤΑ                                    | . 22 |  |  |  |

|   |       | 2.3.3       | SPIDER                                 | . 23 |  |  |  |

|   |       | 2.3.4       | FlexRay                                | . 23 |  |  |  |

|   | 2.4   | Bus Gu      | uardians                               | . 23 |  |  |  |

|   |       | 2.4.1       | SAFEbus                                | . 24 |  |  |  |

|   |       | 2.4.2       | TTA                                    | . 24 |  |  |  |

|   |       | 2.4.3       | SPIDER                                 | . 25 |  |  |  |

|   |       | 2.4.4       | FlexRay                                | . 25 |  |  |  |

|   | 2.5   | Startup     | and Restart                            | . 25 |  |  |  |

|   |       | 2.5.1       | SAFEbus                                | . 26 |  |  |  |

|   |       | 2.5.2       | ΤΤΑ                                    | . 27 |  |  |  |

|   |       | 2.5.3       | SPIDER                                 | . 28 |  |  |  |

|   |       | 2.5.4       | FlexRay                                | . 28 |  |  |  |

|   |       |             | 28                                     | . 28 |  |  |  |

|   |       | 2.6.1       | SAFEbus                                | . 32 |  |  |  |

|     | 2.6.2<br>2.6.3 | TTA     | 34 |

|-----|----------------|---------|----|

|     | 2.6.4          | FlexRay |    |

| 2.7 | Flexibi        | ility   | 35 |

|     | 2.7.1          | SAFEbus | 36 |

|     | 2.7.2          | ΤΤΑ     | 36 |

|     | 2.7.3          | SPIDER  | 37 |

|     | 2.7.4          | FlexRay | 37 |

| 2.8 | Assura         | ance    | 38 |

|     | 2.8.1          | SAFEbus | 38 |

|     | 2.8.2          | ΤΤΑ     | 39 |

|     | 2.8.3          | SPIDER  | 39 |

|     | 2.8.4          | FlexRay | 40 |

| 3 Conclusion | n |

|--------------|---|

|--------------|---|

41

# **List of Figures**

------

| 1.1 | Generic Bus Configuration | 5 |

|-----|---------------------------|---|

| 1.2 | Bus Interconnect          | 6 |

| 1.3 | Star Interconnect         | 7 |

| 1.4 | SPIDER Interconnect       | 8 |

-

### Chapter 1

### Introduction

Embedded systems generally operate as closed-loop control systems: they repeatedly sample sensors, calculate appropriate control responses, and send those responses to actuators. In safety-critical applications, such as fly- and drive-by-wire (where there are no direct connections between the pilot and the aircraft control surfaces, nor between the driver and the car steering and brakes), requirements for ultra-high reliability demand fault tolerance and extensive redundancy. The embedded system then becomes a distributed one, and the basic control loop is complicated by mechanisms for synchronization, voting, and redundancy management.

Systems used in safety-critical applications have traditionally been *federated*, meaning that each "function" (e.g., autopilot or autothrottle in an aircraft, and brakes or suspension in a car) has its own fault-tolerant embedded control system with only minor interconnections to the systems of other functions. This provides a strong barrier to fault propagation: because the systems supporting different functions do not share resources, the failure of one function has little effect on the continued operation of others. The federated approach is expensive, however (because each function has its own replicated system), so recent applications are moving toward more integrated solutions in which some resources are shared across different functions. The new danger here is that faults may propagate from one function to another; *partitioning* is the problem of restoring to integrated systems. A dual issue is that of *strong composability*: here we would like to take separately developed functions and have them run without interference on an integrated system platform with negligible integration effort.

The problems of fault tolerance, partitioning, and strong composability are challenging ones. If handled in an ad-hoc manner, their mechanisms can become the primary sources of faults and of *un*reliability in the resulting architecture [Mac88]. Fortunately, most aspects of these problems are independent of the particular functions concerned, and they can be handled in a principled and correct manner by generic mechanisms implemented as an architecture for distributed embedded systems. One of the essential services provided by this kind of architecture is communication of information from one distributed component to another, so a (physical or logical) communication bus is one of its principal components, and the protocols used for control and communication on the bus are among its principal mechanisms. Consequently, these architectures are often referred to as *buses* (or *databuses*), although this term understates their complexity, sophistication, and criticality. In truth, these architectures are the safety-critical core of the applications built above them, and the choice of services to provide to those applications, and the mechanisms of their implementation, are issues of major importance in the construction and certification of safety-critical embedded systems.

Capabilities and considerations once encountered only in buses for civil aircraft are now found in buses aimed at the automobile market, where the economies of scale ensure low prices. The low price of the automobile buses then renders them attractive to certain aircraft applications—provided they can achieve the safety required.

In this report, I describe and compare the architectures of two avionics and two automobile buses in the interest of deducing principles common to all of them, the main differences in their design choices, and the tradeoffs made. The avionics buses considered are the Honeywell SAFEbus [ARI93, HD92] (the backplane data bus used in the Boeing 777 Airplane Information Management System) and the NASA SPIDER [MMTP02] (an architecture being developed as a demonstrator for certification under the new DO-254 guidelines); the automobile buses considered are the TTTech Time-Triggered Architecture (TTA) [TTT02, KG94], recently adopted by Audi for automobile applications, and by Honeywell for avionics and aircraft controls functions, and FlexRay [B<sup>+</sup>01], which is being developed by a consortium of BMW, DaimlerChrysler, Motorola, and Philips.

All four of the buses considered here are primarily *time triggered*; this is a fundamental design choice that influences many aspects of their architectures and mechanisms, and sets them apart from fundamentally *event-triggered* buses such as Controller Area Network (CAN), Byteflight, and LonWorks.

"Time triggered" means that all activities involving the bus, and often those involving components attached to the bus, are driven by the passage of time ("if it's 20 ms since the start of the frame, then read the sensor and broadcast its value"); this is distinguished from "event triggered," which means that activities are driven by the occurrence of events ("if the sensor reading changes, then broadcast its new value"). A time-triggered system interacts with the world according to an internal schedule, whereas an event-triggered system responds to stimuli that are outside its control.

The time-triggered and event-triggered approaches to systems design find favor in different application areas, and each has strong advocates. For integrated, safety-critical systems, however, the time-triggered approach is generally preferred. The reason is that an integrated system brings different applications ("functions" in avionics terms) together whereas in a safety-critical system we usually prefer them to be kept apart! This is so that a failure in one application cannot propagate and cause failures in other applications; such protection against fault propagation is called *partitioning*, and it is most rigorously

achieved (for reasons to be explained shortly) in time-triggered systems. Partitioning is a necessity in integrated safety-critical systems, but once achieved it also creates new opportunities. First, it simplifies the construction of fault-tolerant applications: such applications must be replicated across separate components with independent failure characteristics and no propagation of failures between them. Traditional "federated" architectures are typically hand-crafted to achieve these properties, but partitioning provides them automatically (indeed, they are the same as partitioning, reinterpreted to apply to the redundant components of a single application, rather than across different applications). Second, partitioning allows single applications to be "deconstructed" into smaller components that can be developed to different assurance levels: this can reduce costs and can also allow provision of new, safety-related capabilities. For example, an autopilot has to be developed to DO-178B assurance Level A [RTC92]; this is onerous and expensive, and a disincentive to introduction of desirable additional capabilities, such as extensive built-in self test (BIST). If the BIST could run in a separate partition, however, its assurance might be reduced to Level C, with corresponding reduction in its cost of development. Third, although the purpose of partitioning is to exclude fault propagation, it has the concomitant benefit that it promotes composability. A *composable* design is one in which individual applications are unaffected by the choice of the other applications with which they are integrated: an autothrottle, for example, could be developed, tested, and (in principle) certified, in isolation-in full confidence that it will perform identically when integrated into the same system as an autolander and a coffee maker.

Partitioning and composability concern the *predictability* of the resources and services perceived by the clients (i.e., applications and their subfunctions) of an architecture; predictability has two dimensions: *value* (i.e., logically correct behavior) and *time* (i.e., services are delivered at a predictable rate, and with predictable latency and jitter). It is temporal (time) predictability—especially in the presence of faults—that is difficult to achieve in event-triggered architectures, and thereby leaves time triggering as the only choice for safety-critical systems. The problem in event-driven buses is that events arriving at different nodes may cause them to contend for access to the bus, so some form of media access control (i.e., a distributed mutual exclusion algorithm) is needed to ensure that each node eventually is able to transmit without interruption. The important issue is how predictable is the access achieved by each node, and how strong is the assurance that the predictable is the predictable.

Buses such as Ethernet resolve contention probabilistically and therefore can provide only probabilistic guarantees of timely access, and no assurance at all in the presence of faults. Buses for embedded systems such as CAN [ISO93], LonWorks [Ech99], or Profibus (Process Field Bus) [Deu95] use various priority, preassigned slot, or token schemes to resolve contention deterministically. In CAN, for example, the message with the lowest number always wins the arbitration and may therefore have to wait only for the current message to finish (though that message may be retransmitted in the case of transmission failure), while other messages also have to wait for any lower-numbered messages. Thus, although contention is resolved deterministically, latency increases with load and can be bounded with only probabilistic guarantees—and these can be quite weak in the presence of faults that cause some nodes to make excessive demands, thereby reducing the service available to others. Event-triggered buses for safety-critical applications add various mechanisms to limit such demands. ARINC 629 [ARI56] (an avionics data bus used in the Boeing 777), for example, uses a technique sometimes referred to as "minislotting" that requires each node to wait a certain period after sending a message before it can contend to send another. Even here, however, latency is a function of load, so the Byteflight protocol [Byt] developed by BMW extends this mechanism with guaranteed, preallocated slots for critical messages. At this point, however, we are close to a time-triggered bus, and if we were to add mechanisms to provide fault tolerance and to contain the effects of node failures, then we would arrive at a design similar to one of the time-triggered buses that is the focus of this comparison.

In a time-triggered bus, there is a static preallocation of communication bandwidth in the form of a global schedule: each node knows the schedule and knows the time, and therefore knows when it is allowed to send messages, and when it should expect to receive them. Thus, contention is resolved at design time (as the schedule is constructed), when all its consequences can be examined, rather than at runtime. Because all communication is time triggered by the global schedule, there is no need to attach source or destination addresses to messages sent over the bus: each node knows the sender and intended recipients of each message by virtue of the time at which it was sent. Elimination of the address fields not only reduces the size of each message, thereby greatly increasing the message bandwidth of the bus (messages are typically short in embedded control applications), but it also eliminates a potential source of serious faults: the possibility that a faulty node may send messages to the wrong recipients or, worse, may masquerade as a sender other than itself.

Time-triggered operation provides efficiency, determinism, and partitioning, but at the price of flexibility. To reduce this limitation, most time-triggered buses are able to switch among several schedules. The different schedules may be optimized for different missions, or phases of a mission (e.g., startup vs. cruise), for operating in a degraded mode (e.g., when some major function has failed), or for optional equipment (e.g., for cars with and without traction control). In addition, some make provision for event-triggered services, either "piggybacked" on time-triggered mechanisms, or "timesharing" between time- and event-triggered operation. Flexibility of operation is considered in more detail in Section 2.7.

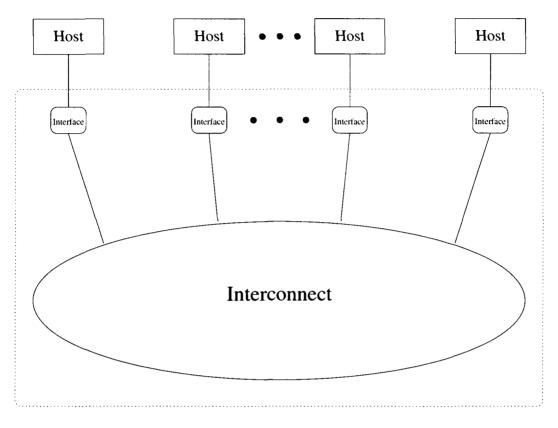

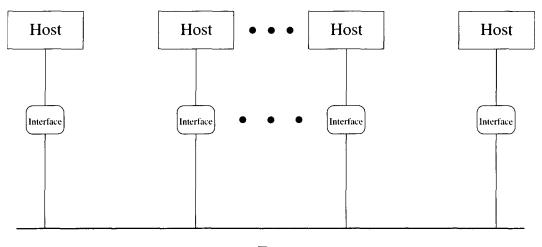

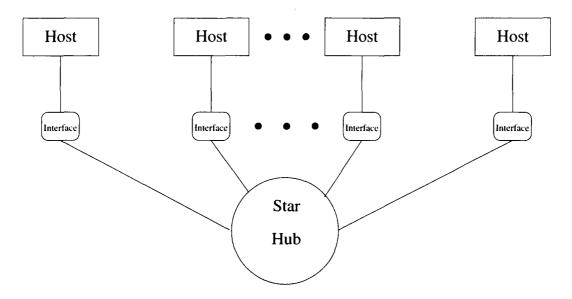

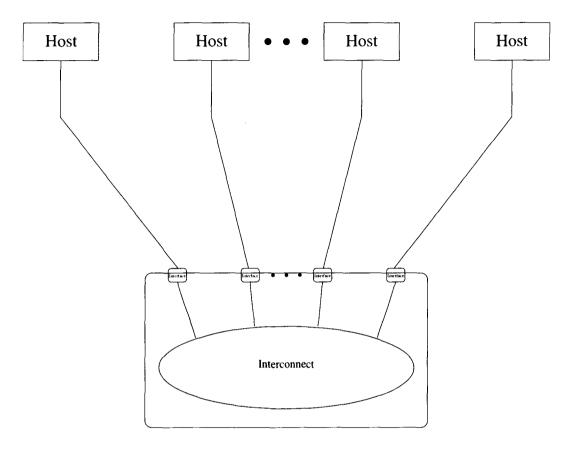

Figure 1.1 portrays a generic bus architecture: application programs run in the *host* computers, while the *interconnect* medium provides broadcast communications; *interface* devices connect the hosts to the interconnect. All components inside the dashed box are considered part of the bus. Realizations of the interconnect may be a physical bus, as shown in Figure 1.2, or a centralized hub, as shown in Figure 1.3. The interfaces may be physically proximate to the hosts, or they may form part of a more complex central hub, as shown in Figure 1.4.

Figure 1.1: Generic Bus Configuration

Safety-critical aerospace functions (those at Level A of DO-178B) are generally required to have failure rates less than  $10^{-9}$  per hour, and an architecture that is intended to support several such functions should provide assurance of failure rates better than  $10^{-10}$ per hour.<sup>1</sup> Consumer-grade electronics devices have failure rates many orders of magnitude worse than this, so redundancy and fault tolerance are essential elements of a bus architecture. Redundancy may include replication of the entire bus, of the interconnect and/or the interfaces, or decomposition of those elements into smaller subcomponents that are then replicated. These topics are considered in more detail in Section 2.1.

Fault tolerance takes two forms in these architectures: first is that which ensures that the bus itself does not fail, second is that which eases the construction of fault-tolerant ap-

<sup>&</sup>lt;sup>1</sup>An explanation for this figure can be derived by considering a fleet of 100 aircraft, each flying 3,000 hours per year over a lifetime of 33 years (thereby accumulating about  $10^7$  flight-hours). The requirement is that no fault should lead to loss of an aircraft in the lifetime of the fleet [FAA88]. If hazard analysis reveals ten potentially catastrophic failure conditions in each of ten systems, then the "budget" for each is about  $10^{-9}$ [LT82, page 37]. Similar calculations can be performed for cars—higher rates of loss are accepted, but there are vastly more of them. See the MISRA guidelines [MIS94]. Also note that failure includes malfunction as well as loss of function.

#### Bus

Figure 1.2: Bus Interconnect

plications. Each of these mechanisms must be constructed and validated against an explicit *fault hypothesis*, and must deliver specified *services* (that may be specified to degrade in acceptable ways in the presence of faults). The fault hypothesis must describe the *kinds* (or *modes*) of faults that are to be tolerated, and their maximum *number* and *arrival rate*. These topics are considered in more detail in Section 2.2.

Although the bus *as whole* must not fail, it may be acceptable for service to some specified number of hosts to fail in some specified manner (typically "fail silent," meaning no messages are transmitted to or from the host); also, some host computers may themselves fail. In these circumstances (when a host has failed, or when the bus is unable to provide service to a host), applications software in other hosts must tolerate the failure and continue to provide the function concerned. For example, three hosts might provide an autopilot function in a triple modularly redundant (TMR) fashion, or two might operate in a master/shadow manner. To coordinate their fault-tolerant operation, redundant hosts may need to maintain identical copies of relevant state data, or may need to be notified when one of their members becomes unavailable. The bus can assist this coordination by providing application-independent services such as interactively consistent message reception and group membership. These topics are considered in more detail in Section 2.6.

The global schedule of a time-triggered system determines when each node (i.e., host and corresponding interface) can access the interconnect medium. A global schedule requires a global clock and, for the reasons noted above, this clock must have a reliability of about  $10^{-10}$ . It might seem feasible to locate a single hardware clock somewhere in the bus, then distribute it to the interfaces, and to achieve the required reliability by replicating the whole bus. The difficulty with this approach is that the clocks will inevitably drift apart over time, to the point where the two buses will be working on different parts of the

Figure 1.3: Star Interconnect

schedule. This would present an unacceptable interface to the hosts, so it is clear that the clocks need to be synchronized. Two clocks do not suffice for fault-tolerant clock synchronization (we cannot tell which is wrong): at least four are required for the most demanding fault models [LMS85] (although three may be enough in certain circumstances [Rus94]). Rather than synchronize multiple buses, each with a single clock, it is better to replicate clocks within a single bus. Now, the hosts are full computers-equipped with clocks-so it might seem that they could undertake the clock synchronization. The difficulty with this approach is that bus bandwidth is dependent on the quality of clock synchronization (message "frames" must be separated by a gap at least as long as the maximum clock skew), and clock synchronization is, in turn, dependent on the accuracy with which participants can estimate the differences between their clocks, or (for a different class of algorithms) on how quickly the participants can respond to events initiated by another clock. Specialized hardware is needed to achieve either of these with adequate performance, and this rules out synchronization by the hosts. Instead, the clocks and their synchronization mechanisms are made part of the bus; some designs locate the clocks within the interconnect, while others locate them within the interfaces. The topic of clock synchronization is considered in more detail in Section 2.3.

A fault-tolerant global clock is a key mechanism for coordinating multiple components according to a global schedule. The next point to be considered is where the global schedule should be stored, and how the time trigger should operate. In principle, the schedule could be held in the host computers, which would then determine when to send messages to their interfaces for transmission: in this case, the interfaces would perform only low-level (physical layer) protocol services. However, effective bus bandwidth depends on the global

Figure 1.4: SPIDER Interconnect

schedule being tight, with little slack for protocol processing delays or interrupt latency. As with clock synchronization, this argues for hardware assistance in message timing and transmission. Hence, most of the buses considered here hold the schedule in the interface units, which then take on responsibility for most of the protocol services associated with the bus.

Although buses differ in respect to the fault hypotheses they consider, all those that place responsibility for scheduling in the interface units must consider the possibility that some of these may fail in a way that causes them to transmit on the interconnect at the wrong time, thereby excluding or damaging properly timed transmissions from other interfaces. The worst manifestation of this failure is the so-called "babbling idiot" failure where a faulty interface transmits constantly, thereby compromising the operation of the entire bus. To control this failure, it is necessary to introduce another component, called a *guardian* that restricts the ability of an interface to transmit on the interconnect. A guardian should fail independently of the interfaces, and have independent access to the schedule and to the global time. There are many ways to implement the guardian functionality. For example,

we could duplicate each interface and arrange it so that the second instance acts as a check on the primary one (essentially, they are wired in series). The problem with this approach is the cost of providing a second duplicate for each interface. A lower-cost alternative reduces the functionality of the guardian at the expense of making it somewhat dependent on the primary interface. A third alternative locates the guardian functionality in the interconnect (specifically, in the hub of a star configuration) where its cost can be amortized over many interfaces, albeit at the cost of introducing a single point of failure (which is overcome by duplicating the entire hub). These topics are considered in more detail in Section 2.4.

It is nontrivial to start up a bus architecture that provides sophisticated services, especially if this must be performed in the presence of faults. Furthermore, it may be necessary to restart the system if faults outside its hypothesis cause it to fail: this must be done very quickly (within about 10 ms) or the overall system may go out of control. And it is necessary to allow individual hosts or interfaces that detect faults in their own operation to drop off the bus and later rejoin when they are restored to health. The topics of startup, restart, and rejoin are consider in Section 2.5.

Any bus architecture that is intended to support safety-critical applications, with its attendant requirement for a failure rate below  $10^{-10}$ , must come with strong assurance that it is fit for the purpose. Assurance will include massive testing and fault injection of the actual implementation, and extensive reviews and analysis of its design and assumptions. Some of the analysis may employ formal methods, supported by mechanized tools such as model checkers and theorem provers [Rus95]. Industry or government guidelines for certification may apply in certain fields (e.g., [RTC92, RTC00] for airborne software and hardware, respectively, and [MIS94] for cars). These topics are considered in more detail in Section 2.8.

The comparison between the four bus architectures is described in the next chapter; conclusions are presented in Chapter 3.

### **Chapter 2**

### Comparison

We begin with a brief description of the topology and operation of each of the four bus architectures, and then consider each of them with respect to the issues introduced in the previous chapter. Within each section, the buses are considered in the order of their date of first publication: SAFEbus, TTA, SPIDER, FlexRay. Certain paragraphs are labeled in the margin by keywords that are intended to aid navigation.

#### 2.1 The Four Buses

We describe the general characteristics of each of the bus architectures considered.

#### 2.1.1 SAFEbus

SAFEbus<sup>™</sup> was developed by Honeywell (the principal designers are Kevin Driscoll and Ken Hoyme [HDHR91, HD92, HD93]) to serve as the core of the Boeing 777 Airplane Information Management System (AIMS) [SD95], which supports several critical functions, such as cockpit displays and airplane data gateways. The bus has been standardized as ARINC 659 [ARI93], and variations on Honeywell's implementation are being used or considered for other avionics and space applications.

SAFEbus uses a bus interconnect topology similar to that shown in Figure 1.2; the interfaces (called Bus Interface Units, or BIUs) are duplicated, and the interconnect bus is quad-redundant; in addition, the whole AIMS is duplicated. Most of the functionality of SAFEbus is implemented in the BIUs, which perform clock synchronization and message scheduling and transmission functions. Each BIU acts as its partner's bus guardian by controlling its access to the interconnect. Each BIU of a pair drives a different pair of interconnect buses but is able to read all four; the interconnect buses themselves each comprise two data lines and one clock line. The bus lines and their drivers have the electrical characteristics of OR gates (i.e., if several different BIUs drive the same line at the same

time, the resulting signal is the OR of the separate inputs). Some of the protocols exploit this property.

Of the architectures considered here, SAFEbus is the most mature—it has been keeping Boeing 777s in the air for nearly a decade—but it is also the most expensive: the BIUs provide rich functionality and are fully duplicated at each node.

#### 2.1.2 TTA

The Time-Triggered Architecture (TTA) was developed by Hermann Kopetz and colleagues at the Technical University of Vienna [KG93, KG94, MBSP02]. Commercial development of the architecture is undertaken by TTTech and it is being deployed for safety-critical applications in cars by Audi and Volkswagen, and for flight-critical functions in aircraft and aircraft engines by Honeywell (specifically, the FADECs of Honeywell's F124 engine for the Aermacchi M-346 fighter/trainer, and of General Electric's F110 engine for the F16 fighter) and Hamilton Sunstrand/Nord Micro (specifically, the cabin pressure control of the Airbus A380).

Current implementations of TTA use a bus interconnect topology similar to that shown in Figure 1.2; we will refer to this version as TTA-bus. The next generation of TTA implementations will use a star interconnect topology similar to that shown in Figure 1.3; we will refer to this version as TTA-star. The interfaces are essentially the same in both designs; they are called *controllers* and implement the TTP/C protocol [TTT02] that is at the heart of TTA, providing clock synchronization, and message sequencing and transmission functions. The interconnect is duplicated and each controller drives both copies. In TTA-bus, each controller drives the buses through a bus guardian; in TTA-star, the guardian functionality is implemented in the central hub. TTA-star can also be arranged in distributed configurations in which subsystems are connected by hub-to-hub links.

Of the architectures considered here, TTA is unique in being used for both automobile applications, where volume manufacture leads to very low prices, and aircraft, where a mature tradition of design and certification for flight-critical electronics provides strong scrutiny of arguments for safety.

#### 2.1.3 SPIDER

A Scalable Processor-Independent Design for Electromagnetic Resilience (SPIDER) is being developed by Paul Miner and colleagues at the NASA Langley Research Center [MMTP02] as a research platform to explore recovery strategies for radiation-induced high-intensity radiated fields/electromagnetic interference (HIRF/EMI) faults, and to serve as a case study to exercise the recent design assurance guidelines for airborne electronic hardware (DO-254) [RTC00].

The SPIDER interconnect is composed of active elements called Redundancy Management Units, or RMUs. Its topology can be organized either as shown in Figure 1.4, where the RMUs and interfaces (the BIUs) form part of a centralized hub, or as in Figure 1.3, where the RMUs form the hub, or similar to Figure 1.1, where the RMUs provide a distributed interconnect. The lines connecting hosts to their interfaces are optical fiber, and the whole system beyond the hosts (i.e., optical fibers and the RMUs and BIUs) is called the Reliable Optical Bus (ROBUS).

Clock synchronization and other services of SPIDER are achieved by distributed algorithms executed among the BIUs and RMUs [MMTP02]. The scheduling aspects of SPIDER are not well documented as yet, but the bus guardian functionality is handled in the RMUs following an approach due to Palumbo [Pal96].

SPIDER is an interesting design that uses a different topology and a different class of algorithms from the other buses considered here. However, its design and implementation are still in progress, and so it is omitted from some comparisons. I hope to increase coverage of SPIDER as more details become available.

#### 2.1.4 FlexRay

FlexRay, which is being developed by a consortium including BMW, DaimlerChrysler, Motorola, and Philips, is intended for powertrain and chassis control in cars. It differs from the other buses considered here in that its operation is divided between time-triggered and event-triggered activities.

FlexRay can use either an "active" star topology similar to that shown in Figure 1.3, or a "passive" bus topology similar to that shown in Figure 1.2. In both cases, duplication of the interconnect is optional. Each interface (it is called a communication controller) drives the lines to its interconnects through separate bus guardians located with the interface. As with TTA-star, FlexRay can also be deployed in distributed configurations in which subsystems are connected by hub-to-hub links. Published descriptions of the FlexRay protocols and implementation are sketchy at present  $[B^+01, BMF02]$  (see also the Web site www.flexray-group.com).

FlexRay is interesting because of its mixture of time- and event-triggered operation, and potentially important because of the industrial clout of its developers. However, full details of its design are not available to the general public, so comparisons are based on the informal descriptions that have been published.

#### 2.2 Fault Hypothesis and Fault Containment Units

Any fault-tolerant system must be designed and evaluated against an explicit *fault hypothe*sis that describes the number, type, and arrival rate of the faults it is intended to tolerate. The fault hypothesis must also identify the different *fault containment units* (FCUs) in the design: these are the components that can *independently* be afflicted by faults. The division of an architecture into separate FCUs needs careful justification: there must be no propagation of faults from one FCU to another, and no "common mode failures" where a single physical event produces faults in multiple FCUs. We consider only physical faults (those caused by damage to, defects in, or aging of the devices employed, or by external disturbances such as cosmic rays, and electromagnetic interference): design faults must be excluded, and must be shown to be excluded by stringent assurance and certification processes.

It is a key assumption of all reliability calculations that failures of separate FCUs are statistically independent. Knowing the failure rate of each FCU, we can then use Markov or other stochastic modeling techniques [But92] to calculate the reliability of the overall architecture. Of course these calculations depend on claimed properties of the architecture (e.g., "this architecture can tolerate failures of any two FCUs"), and design assurance methods (e.g., formal verification) must be employed to justify these claims. The division of labor is that design assurance must justify a "theorem" of the form

#### enough nonfaulty components implies correct operation

and stochastic analysis must justify the antecedent to this theorem.

The assumption that failures of separate FCUs are independent must be ensured by careful design and assured by stringent analysis. True independence generally requires that different FCUs are served by different power supplies, and are physically and electrically isolated from each other. Providing this level of independence is expensive and it is generally undertaken only in aircraft applications. In cars, it is common to make some small compromises on independence: for example, the guardians may be fabricated on the same chip as the interface (but with their own clock oscillators), or the interface may be fabricated on the same chip as the host processor. It is necessary to examine these compromises carefully to ensure that the loss in independence applies only to fault modes that are benign, extremely rare, or tolerated by other mechanisms.

The fault *mode* mentioned above is one aspect of a fault hypothesis; the others are the total *number* of faults, and their *rate* of arrival. A fault mode describes the kind of behavior that a faulty FCU may exhibit. The same fault may exhibit different modes at different levels of a protocol hierarchy: for example, at the electrical level, the fault mode of a faulty line driver may be that it sends an intermediate voltage (one that is neither a digital 0 nor a digital 1), while at the message level the mode of the same fault may be "Byzantine," meaning that different receivers interpret the same message in different ways (because some see the intermediate voltage as a 0, and others as a 1). Some protocols can tolerate Byzantine faults, others cannot; for those that cannot, we must show that the fault mode is controlled at the underlying electrical level.

The basic dimensions that a fault can affect are value, time, and space. A *value* fault is one that causes an incorrect value to be computed, transmitted, or received (whether as a physical voltage, a logical message, or some other representation); a *timing* fault is one that causes a value to be computed, transmitted, or received at the wrong time (whether too early, too late, or not at all); a *spatial proximity* fault is one where all matter in some specified volume is destroyed (potentially afflicting multiple FCUs). Bus-based interconnects of the kind shown in Figure 1.2 are vulnerable to spatial proximity faults: all redundant

Spatial proximity fault buses necessarily come into close proximity at each node, and general destruction in that space could sever or disrupt them all. Interconnect topologies with a central hub are far more resilient in this regard: a spatial proximity fault that destroys one or more nodes does not disrupt communication among the others (the hub may need to isolate the lines to the destroyed nodes in case these are shorted), and destruction of a hub can be tolerated if there is a duplicate in another location.

There are many ways to classify the effects of faults in any of the basic dimensions. One classification that has proved particularly effective in analysis of the types of algorithms that underlie the architectures considered here is the *hybrid* fault model of Thambidurai and Park [TP88]. In this classification, the effect of a fault may be *manifest*, meaning that it is reliably detected (e.g., a fault that causes an FCU to cease transmitting messages), *symmetric*, meaning that whatever the effect, it is the same for all observers (e.g., an off-by-1 error), or *arbitrary*, meaning that it is entirely unconstrained. In particular, an arbitrary fault may be *asymmetric* or *Byzantine*, meaning that its effect is perceived differently by different observers (as in the intermediate voltage example).

The great advantage to designs that can tolerate arbitrary fault modes is that we do not have to justify assumptions about specific fault modes: a system is shown to tolerate (say) two arbitrary faults by proving that it works in the presence of two faulty FCUs with no assumptions whatsoever on the behavior of the faulty components. A system that can tolerate only specific fault modes may fail if confronted by a different fault mode, so it is necessary to provide assurance that such modes cannot occur. It is this *absence* of assumptions that is so attractive in safety-critical contexts about systems that can tolerate arbitrary faults. This point is often misunderstood and such systems are often derided as being focused on asymmetric or Byzantine faults, "which never arise in practice." Byzantine faults are just one manifestation of arbitrary behavior, and they certainly cannot be asserted not to occur (in fact, they have been observed in several systems that have been monitored sufficiently closely). One situation that is likely to provoke asymmetric manifestations is a *slightly out* of specification (SOS) fault, such as the intermediate electrical voltage mentioned earlier. SOS faults in the timing dimension include those that put a signal edge very close to a clock edge, or that have signals with very slow rise and fall times (i.e., weak edges). Depending on the timing of their own clock edges, some receivers may recognize and latch such a signal, others may not, resulting in asymmetric or Byzantine behavior.

FCUs may be active (e.g., a processor) or passive (e.g., a bus); while an arbitraryfaulty active component can do anything, a passive component may change, lose, or delay data, but it cannot spontaneously create a new datum. Keyed checksums or cryptographic signatures can sometimes be used to reduce the fault modes of an active FCU to those of a passive one. (An arbitrary-faulty active FCU can always create its own messages, but it cannot create messages purporting to come from another FCU if it does not know the key of that FCU; signatures need to be managed carefully for this reduction in fault mode to be credible [GLR95].)

Any fault-tolerant architecture will fail if subjected to too many faults; generally speak-

Hybrid fault model

Arbitrary faults

SOS faults

Active/Passive faults

> Maximum number of faults

ing, it requires more redundancy to tolerate an arbitrary fault than a symmetric one, which in turn requires more redundancy than a manifest fault. The most effective fault-tolerant algorithms make this tradeoff automatically between number and difficulty of faults tolerated. For example, the clock synchronization algorithm of [Rus94] can tolerate a arbitrary faults, s symmetric, and m manifest ones simultaneously provided n, the number of FCUs, satisfies n > 3a + 2s + m. It is provably impossible (i.e., it can be proven that no algorithm can exist) to tolerate a arbitrary faults in clock synchronization with fewer than 3a+1 FCUs and 2a+1 disjoint communication paths (or a+1 disjoint broadcast channels) [DHS86,FLM86] (unless digital signatures are employed—which is equivalent to reducing the severity of the arbitrary fault mode). Synchronization is approximate (i.e., the clocks of different FCUs need to be close together, not exactly the same); those problems that require exact agreement (e.g., group membership, consensus, diagnosis) cannot be solved in the presence of a arbitrary faults unless there are at least 3a + 1 FCUs, 2a + 1 disjoint communication paths (or a + 1 disjoint broadcast channels) between them, and a + 1 levels (or "rounds") of communication [Lyn96]. The number of FCUs and the number of disjoint paths required, but not the number of rounds, can be reduced by using digital signatures.

#### Self-checking

Fail silence

Reconfiguration

Reconfig rate

Because it is algorithmically much easier to tolerate simple failure modes, some architectures (e.g., SAFEbus) arrange FCUs (the BIUs in the case of SAFEbus) in self-checking pairs: if the members of a pair disagree, they go offline, ensuring that the effect of their failure is seen as a manifest fault (i.e., one that is easily tolerated). The controllers and bus guardians in TTA-bus operate in a similar way. Most architectures also employ substantial self-checking in each FCU; any FCU that detects a fault will shut down, thereby ensuring that its failure will be manifest. (This kind of operation is often called *fail silence*). Even with extensive self-checking and pairwise-checking, it may be possible for some fault modes to "escape," so it is generally necessary to show either that the mechanisms used have complete coverage (i.e., there will be no violation of fail silence), or to design the architecture so that it can tolerate the "escape" of at least one arbitrary fault.

Many architectures can tolerate only a single fault at a time, but can reconfigure to exclude faulty FCUs and are then able to tolerate additional faults. Prior to reconfiguration, it is necessary to identify the faulty component(s); algorithms to do this are based on distributed diagnosis and group membership. It is provably impossible to correctly identify an arbitrary-faulty FCU in some circumstances [WLS97], so there is tension between leaving a faulty FCU in the system and the risk of excluding a nonfaulty one (and still leaving the faulty one in operation). Most faults are *transient*, meaning they correct themselves given a little time, so there is also tension between the desire to exclude faulty FCUs quickly, and the hope that they may correct themselves if left in operation [Rus96]. A transient fault may contaminate state data in a way that leaves a permanent residue after the original fault has cleared, so mechanisms are needed to purge such effects [Rus93a].

Given decisions about the diagnosis and reconfiguration strategy, it is possible to calculate the time taken to perform these operations for given fault modes and, hence, to calculate the maximum rate at which diagnosis and reconfiguration can occur. The architectures considered here operate according to static schedules, which consist of "rounds" or "frames" that are executed repeatedly in a cyclic fashion. The *reconfiguration rate* is often then expressed in terms of faults per round (or the inverse). It is usually important that every node is scheduled to make at least one broadcast in every round, since this is how fault status is indicated (and hence how reconfiguration is triggered).

The reconfiguration rate determines how rapidly the architectures can recover from the effects of prior faults and so be ready to tolerate another. The *fault arrival rate* is the hypothesized rate at which faults (of different kinds) actually occur. Reliability modeling must analyse the fault arrival rate and mission time against the fault tolerance and reconfiguration rate of the architecture to determine if it can satisfy the mission goals.

An excluded FCU may perform a restart and self check. If successful, it may then apply to rejoin the system. This is a delicate operation for most architectures, because one FCU may be going faulty at the same time as another (nonfaulty) one is rejoining: this presents two simultaneous changes in the behavior of the system and may cause algorithms tolerant of only a single fault to fail.

Historical experience and analysis must be used to show that the hypothesized modes, numbers, and arrival rate are realistic, and that the architecture can indeed operate correctly under those hypotheses for its intended mission time. But sometimes things go wrong: the system may experience many simultaneous faults (e.g., from unanticipated HIRF), or other violations of its fault hypothesis. We cannot guarantee correct operation in such cases (otherwise our fault hypothesis was too conservative), but safety-critical systems generally are constructed to a "never give up" philosophy and will attempt to continue operation in a degraded mode. Although it is difficult to provide assurance of correct operation during these events (otherwise we could revise the fault hypothesis), it may be possible to provide assurance that the system returns to normal operation once the faults cease (assuming they were transients) using the ideas of self-stabilization [Sch93].

The usual method of operation in "never give up" mode is that each node reverts to local control of its own actuators using the best information available (e.g., each brake node applies braking force proportional to pedal pressure if it is still receiving that input, and removes all braking force if not), while at the same time attempting to regain coordination with its peers.

#### 2.2.1 SAFEbus

The FCUs of SAFEbus are the BIUs (two per node), the hosts, and the buses (there are two, each of which is a self-checking pair). In addition, two copies of the entire system are located in separate cabinets in different parts of the aircraft. ARINC 659 shows a single host attached to each pair of BIUs [ARI93, Attachment 2–1], but in the Honeywell implementation these are also paired: each host (called a Core Processing Module, or CPM) is attached to a single BIU, and forms a separate FCU.

The fault hypothesis of SAFEbus is the following.

Fault arrival rate

Rejoin

Never give up

#### **Fault modes:**

- Arbitrary active faults in BIUs and CPMs

- Arbitrary passive faults in the buses

- Spatial proximity faults that may take out an entire cabinet

**Maximum faults:** SAFEbus adopts a single-fault hypothesis: at most one component of any pair may fail. In more detail, the fault hypothesis of SAFEbus allows the following numbers of faults.

- At most one of the BIUs in any node (the entire node is then considered faulty)

- At most one of the CPMs in a node (the entire node is then considered faulty)

- At most one fault in either of the two buses

- Any number of nodes may fail, but for an application to be functional, at least one node that supports it must be nonfaulty

#### Fault arrival rate:

• Able to tolerate any rate

#### 2.2.2 TTA

The FCUs of TTA depend on how the system is fabricated. It is anticipated that in highvolume applications, TTP controllers will be integrated on the same chip as the host, so these should be considered to belong to a single FCU. Current implementations of TTPbus have the controller separate from the host, but the bus guardians are on the same chip as the controller. Guardians do, however, have their own clock oscillator, so they can be considered a separate FCU for time-partitioning purposes. TTA-star moves the guardians to the central hub, where they definitely form a separate FCU from the controllers. TTA-bus has two bus lines, which are separate FCUs; in TTA-star, the interconnect functionality is provided by the central hubs (so the bus guardian and interconnect are in the same FCU), which are duplicated.

The fault hypothesis of TTA is the following.

#### Fault modes:

- Arbitrary active faults in controllers and the hub of TTA-star

- Arbitrary passive faults in the guardians and buses of TTA-bus

- Spatial proximity faults that may take out nodes and a hub in TTA-star; spatialproximity faults are not part of the fault hypothesis for TTA-bus

**Maximum faults:** TTA adopts a single-fault hypothesis. In more detail, the fault hypothesis of TTA assumes the following numbers of faults.

- For TTA-bus: in each node either the controller or the bus guardian may fail (but not both). One of the buses may fail. To retain single fault tolerance, at least four controllers and their bus guardians must be nonfaulty, and both buses must be nonfaulty. Provided at least one bus is nonfaulty, the system may be able to continue operation with fewer nonfaulty components.

- For TTA-star: to retain single fault tolerance, at least four controllers and both hubs must be nonfaulty. Provided at least one hub is nonfaulty, the system may be able to continue operation with fewer nonfaulty components.

#### Fault arrival rate:

• At most one fault every two rounds

#### 2.2.3 SPIDER

The FCUs of SPIDER are the hosts, the BIUs, and the RMUs; a host and its BIU may form a single FCU in some implementations. The BIUs and RMUs may be distributed, or contained in the hub of the ROBUS.

The fault hypothesis of SPIDER is the following.

#### Fault modes:

- Arbitrary active faults in any FCU

- Spatial proximity faults that may take out nodes and RMUs (depending on the physical topology employed)

- **Maximum faults:** If there are  $n \ge 3$  BIUs and  $m \ge 3$  RMUs, then SPIDER can tolerate an arbitrary fault in any one of these FCUs. SPIDER's maximum faults hypothesis is actually specified with respect to the hybrid fault model, and its constraints are n > 2ba + 2bs + bm, m > 2ra + 2rs + rm, and either ba = 0 or ra = 0, where ba, bs, and bm are the numbers of arbitrary-, symmetric- and manifest-faulty BIUs, and ra, rs, and rm are the corresponding numbers for the RMUs.

- Fault arrival rate: Within the constraints presented above, SPIDER is able to tolerate multiple simultaneous faults. SPIDER's reconfiguration mechanism is graceful degradation: FCUs diagnosed as faulty may be ignored by nonfaulty FCUs. Its fault diagnosis algorithms, derived from those of [WLS97], satisfy strong properties: any FCU diagnosed as faulty is indeed faulty, and all maifest- and symmetric-faulty FCUs (and many abritrary-faulty ones) will be diagnosed [GM02, GM03]. The fault arrival rate hypothesis is a function of the amount of redundancy in the ROBUS, and can be adjusted within certain parameters by employing different numbers of BIUs and RMUs. Reliability modeling and analysis using the SURE program [But92] are described in [MMTP02].

#### 2.2.4 FlexRay

Published diagrams of FlexRay indicate that a node consisting of a microcontroller host, a communication controller, and two bus guardians will be fabricated on a single chip. It appears that all four components will use separate clock oscillators, so that the controller and guardians can be considered as separate FCUs for time-partitioning purposes. The interconnects, whether passive buses or active stars, are separate FCUs.

The fault hypothesis of FlexRay is not stated explicitly; the following are inferences based on available documents.

#### Fault modes:

- Asymmetric (and presumably, therefore, also arbitrary) faults in controllers *for the purposes of clock synchronization*

- Fault modes for other services and components are not described

- Spatial proximity faults may take out nodes and an entire hub

#### **Maximum faults:**

- It appears that a single-fault hypothesis is intended: in each node, at most one bus guardian, or the controller, may be faulty. At most one of the interconnects may be faulty.

- For clock synchronization, fewer than a third of the nodes may be faulty.

Fault arrival rate: The fault arrival rate hypothesis is not described.

#### 2.3 Clock Synchronization

Fault-tolerant clock synchronization is a fundamental requirement for a time-triggered bus architecture. Tightness of the bus schedule, and hence the throughput of the bus, is strongly related to the quality of global clock synchronization that can be achieved—and this is related to the quality of the clock oscillators local to each node, and to the algorithm used to synchronize them. There are two basic classes of algorithm for clock synchronization: those based on averaging and those based on events. Averaging works by each node measuring the skew between its clock and that of every other node, and then setting its clock to some "average" value. A simple average (e.g., the mean or median) over all clocks may be affected by wild readings from faulty clocks (which, under an arbitrary fault model, may provide different readings to different observers), so we need a "fault-tolerant average" that is largely insensitive to a certain number of readings from faulty clocks. Event-based algorithms rely on nodes being able to sense events directly on the interconnect: each node broadcasts a "ready" event when it is time to synchronize and sets its clock when it has

seen a certain number of events from other nodes. Depending on the fault model, additional waves of "echo" or "accept" events may be needed to make this fault tolerant.

Schneider [Sch87] gives a general description that applies to all averaging clock synchronization algorithms; these algorithms differ only in their choice of "fault-tolerant average." The Welch-Lynch algorithm [WL88] is a popular choice that is characterized by use of the "fault-tolerant midpoint" as its averaging function. We assume n clocks and the maximum number of simultaneous faults to be tolerated is t (3t < n); the fault-tolerant midpoint is the average of the t + 1'st and n - t'th clock reading, when these are arranged in order from smallest to largest. If there are at most t faulty clocks, then some reading from a nonfaulty clock must be at least as small as the t + 1'st reading, and the reading from another nonfaulty clock must be at least as great as the n - t'th; hence, the average of these two readings should be close to the middle of the spread of readings from good clocks.

The most important event-based algorithm is that of Srikanth and Toueg [ST87]; it is attractive because it achieves optimal accuracy. Both averaging and event-based algorithms require at least 3a + 1 nodes to tolerate a arbitrary faults.

#### 2.3.1 SAFEbus

The SAFEbus bus is quad-redundant (a pair of self-checking pairs) and each of its four components comprises two data lines and a separate clock line. SAFEbus uses the clock lines for an event-triggered clock synchronization algorithm. The schedule loaded in each interface (BIU in SAFEbus terminology) indicates when a synchronization event should be performed, and these must be sufficiently frequent to maintain the paired BIUs of each node within two bit-times of each other.

In a clock synchronization event, each BIU asserts the clock lines of the two buses that it can write for four bit-times. The electrical characteristics of the SAFEbus cause it to act as an OR gate with the BIUs as its inputs. Thus, the near-simultaneous assertion of each clock line by multiple BIUs generates a pulse on each line that is the OR of its individual pulses. Each BIU synchronizes to the trailing edge of this composite pulse.

A faulty BIU could attempt to assert its clock lines for far longer than the specified four bit-times, thereby delaying the trailing edge that is the global synchronization event. The guardian function of its partner BIU will cut it off once the transmit window closes, and all receiving BIUs will count it out after some number of bit-times greater than four, but the synchronization event will still be delayed. However, this fault affects only the two buses driven by the faulty BIU. Each BIU reads all four buses (although it can write only two of them), detects the trailing edge of the composite synchronization pulse on each of them, and then combines these in a fault-tolerant manner [ARI93, Attachment 4–10] to yield the event to which it actually synchronizes.

SAFEbus also applies several other error detection and masking techniques to minimize the impact of faulty clocks, BIUs, and buses: for example, "pulses" are ignored from buses that have not changed state since the previous synchronization (to overcome stuck-at faults or failed power supplies).

There are several variants to the clock synchronization performed by SAFEbus: a "Short Resync" operates essentially as described above; a "Long Resync" is similar but provides additional information on the data lines to allow an unsynchronized BIU to rejoin the system; an "Initial Sync" is used at startup or following a disruption that requires a restart.

#### 2.3.2 TTA

The TTA algorithm is basically the Welch-Lynch algorithm specialized for t = 1 (i.e., it tolerates a single fault): that is, clocks are set to the average of the 2nd and n - 1'st clock readings (i.e., the second-smallest and second-largest). This algorithm works and tolerates a single arbitrary fault whenever  $n \ge 4$ . TTA does not use dedicated wires or signaling to communicate clock readings among the nodes attached to the network; instead, it exploits the fact that communication is time triggered by a global schedule. When a node x receives a message from a node y, it notes the reading of its local clock and subtracts a fixed correction term to account for the network delay; the difference between this adjusted clock reading and the time for y's transmission that is indicated in the global schedule yields x's perception of the difference between clocks x and y.

Not all TTP nodes have accurate clock oscillators (because these are expensive); those that do have the SYF field set in the Message Descriptor List (MEDL—the global schedule known to all nodes) and the clocks used for synchronization are selected from those that have the SYF flag set.

For scalability, implementation of the Welch-Lynch algorithm should use data structures that are independent of the value of n—that is, it should not be necessary for each node to store the clock difference readings for all n clocks. Clearly, the t'th smallest clock difference reading can be determined with just t registers, and the t'th largest can be determined similarly, for a total of 2t registers per node. In TTA, with t = 1, this requires four registers. TTA does indeed use four registers, but not in quite this way. Each node maintains a queue of four clock-difference readings; whenever a message is received from a node that is in the current membership and that has the SYF field set, the clock difference reading is pushed on to the receiving node's queue (ejecting the oldest reading in the queue). When the current slot has the synchronization field (CS) set in the MEDL, each node runs the synchronization algorithm using the four clock readings stored in its queue.

This algorithm is able to tolerate a single arbitrary fault among the four clocks used in synchronization, but TTA is able to tolerate more than a single fault by reconfiguring to exclude nodes with faulty clocks. This is accomplished by the group membership service: any node with a clock that skews significantly from the global time will mistime its broadcast so that it occurs partially outside its assigned slot. This will cause its message to be truncated by its guardian, which will cause it to fail checksum and to be rejected by all nonfaulty nodes. The membership algorithm will then exclude this node. Only the clocks of current

group members are eligible for use in synchronization, so the clock of the excluded node will not be placed in the clock-difference queue, and that of some other node having the SYF flag will be used instead.

#### 2.3.3 SPIDER

SPIDER uses an event-based algorithm similar to that of Srikanth and Toueg, and also influenced by Davies and Wakerly [DW78] (this remarkably prescient paper anticipated many of the issues and solutions in Byzantine fault tolerance by several years) and Palumbo [Pal96].

The basic design of SPIDER is similar to that of the Draper FTP [Lal86] in that its active components are divided into two classes (BIUs and RMUs) that play slightly different rôles in each of its algorithms. In SPIDER, the RMUs play the part of the "interstages" in FTP. Its clock synchronization algorithm operates in three phases as follows.

- 1. Each RMU broadcasts a "ready" event to all BIUs when its own clock reaches a specified value.

- 2. Each BIU broadcasts an "accept" event to all RMUs as soon as it has received events from t + 1 RMUs (where t is the number of faults to be tolerated).

- 3. Each RMU resets its clock as soon as it has received events from t + 1 BIUs.

This synchronizes the RMUs; the BIUs can be synchronized by one more wave of events from the RMUs.

#### 2.3.4 FlexRay

FlexRay uses the standard Welch-Lynch algorithm, with clock differences presumably determined in a manner similar to TTA. However, published descriptions of FlexRay indicate that it has no membership service and no mechanisms for detecting faulty nodes, nor for reconfiguring to exclude them. To tolerate two arbitrary faults (as claimed in published descriptions), FlexRay must therefore employ at least seven nodes with five disjoint communication paths or three broadcast channels (3t + 1, 2t + 1, and t + 1, respectively, for<math>t = 2), whereas TTA can do this with five nodes (providing the faults arrive sequentially) and with seven nodes it can tolerate four sequential faults.

#### 2.4 Bus Guardians

Some kind of bus guardian functionality is necessary to prevent faulty nodes usurping the scheduled time slots of other nodes or even—in the case of the "babbling idiot" fault mode—destroying all legitimate communication. Bus guardianship depends on message transmission by an interface to an interconnect being mediated by a separate FCU that has

an independent copy of the schedule, and independent knowledge of the global time. Such a fully independent guardian is likely to be expensive, however, and equivalent almost to a second interface (as it is in SAFEbus). Most architectures, therefore, seek to reduce the cost of bus guardianship; they do so in different ways, and incur different penalties.

#### 2.4.1 SAFEbus

SAFEbus makes no compromises: its BIUs are paired and each member of a pair acts as a guardian for the other. Each BIU performs its own clock synchronization and has its own copy of the schedule. As a result, SAFEbus is expensive: its nodes cost a few hundred dollars each.

#### 2.4.2 TTA

In TTA-bus, the guardians have their own clock oscillators and independent copy of the schedule, but they are not able to synchronize independently, and they share the same power supply and physical environment as their controllers. Most of the functionality of a bus guardian is shared across both bus lines.

TTA-bus guardians are synchronized by a start-of-round signal received from their controller. If this signal is given at the wrong time, then the guardian will open its window at the wrong time and will allow its (presumably faulty) controller to transmit at that wrong time. However, its transmission will either collide with a legitimate transmission, resulting in garbage, or will hit the slot of an already excluded node, or some other unused part of the frame. In neither case will it be acknowledged, so the errant controller will shut down if it is "not too faulty" to follow the TTP/C protocol; in any case, the other nodes of the system will exclude both the errant node (since it will have failed to broadcast in its own slot) and the node (if any) whose slot it usurped, and will thereafter proceed unhindered. The errant node will not be able to repeat its trick because a guardian places tight limits on how far the start-of-round signal can move (which is enough to reduce this scenario to extremely low probability in the first place).

In TTA-star, guardian functionality is moved to the central hub. Since there is now only one guardian per interconnect, rather than one per node, more resources can be expended in its construction. The guardian in a hub is able to perform independent clock synchronization and is therefore a fully independent FCU, and provides full coverage against clock synchronization faults and babbling fault modes in all controllers. The penalty is that a central hub is a single point of failure, and as an active entity, it is probably less reliable than a passive bus. This penalty is overcome by duplication, which has the concomitant benefit of providing tolerance for spatial proximity faults.

#### 2.4.3 SPIDER

The scheduling aspects of SPIDER are not well documented as yet, but the bus guardian functionality is handled in the RMUs following an approach due to Palumbo [Pal96].

#### 2.4.4 FlexRay

Operation of the bus guardians of FlexRay is not described in any detail in the available documents. Published diagrams show two guardians per node sharing the same chip and power supply as the controller. These guardians presumably operate in a manner similar to those of TTA-bus, with similar vulnerabilities, though at greater cost (since two guardians per node presumably require two oscillators).

#### 2.5 Startup and Restart

It obviously is necessary to be able to start up the bus and its associated components from cold—preferably with no outside assistance. Modern aircraft systems generally have enough redundancy to operate for several days with some components failed or faulty [Hop88]. This allows repairs to be deferred until the aircraft's schedule brings it to a major maintenance site. Car owners are notorious for deferring maintenance and for operating their vehicles with faults present. These characteristics make it necessary that startup can be performed correctly in the presence of faults.

Restart during operation may be necessary if HIRF or other environmental influences lead to violation of the fault hypothesis and thereby cause complete failure of the bus. Notice that this failure must be detected by the bus, and the restart must be automatic and very fast: most control systems can tolerate loss of control inputs (e.g., by reverting to some form of local control and either releasing the actuators, or freezing them in the previously commanded position) for only a few cycles: longer outages will lead to loss of control. For example, Heiner and Thurner of DaimlerChrysler estimate that the maximum transient outage time for a steer-by-wire automobile application is 50 ms [HT98]. Given that other (e.g., host-level) activities may need to be performed on restart, this suggests 10 ms as a reasonable goal for bus restart. The presence of faulty components could complicate, or even prevent restart (e.g., if multiple faults are present, but some of the algorithms can tolerate only single faults), so it is desirable that previous reconfigurations (e.g., that excluded those faulty components) should be recorded in a way that makes this information available during restart.

Restart is usually initiated when an interface detects no activity on any bus line for some interval; that interface will then transmit some "wake up" message on all lines. Of course, it is possible that the interface in question is faulty (and there was bus activity all along but that interface did not detect it), or that two interfaces decide simultaneously to send the "wake up" call. The first possibility must be avoided by careful checking, preferably by

independent units (e.g., both interfaces of a pair, or an interface and its guardian); the second requires some form of collision detection and resolution: this should be deterministic to guarantee an upper bound on the time to reach resolution (that will allow a single interface to send an uninterrupted "wake up" message) and, ideally, should not depend on reliable collision detection (because there is no such thing).

Components that detect faults in their own operation, or that are notified of their faulty operation by others (e.g., through failed comparison with a paired component, or by exclusion from the group in a system that employs group membership) may drop off the bus and undergo local restart and self-test. If the test is successful (i.e., the fault was transient), then the component will attempt to reintegrate itself into the ongoing operations of the bus. This is a delicate operation because the sudden arrival of a new participant in the bus traffic can present symptoms rather like a fault—and can be particularly challenging to handle if a real fault is manifested simultaneously, or if another component rejoins at the same time.

Restart of the whole bus, and reintegration of individual components, can be interpreted as self-stabilizing services: self-stabilizing algorithms are those that converge to a stable state from any initial state [Dij74, Sch93]. Such algorithms generally assume that no faults are present (or that transient faults have ceased) once stabilization begins; in the circumstances considered here, however, it is possible that some residual faults remain during stabilization. Thus, the algorithms employed for restart and reintegration in bus architectures do not make explicit reference to self-stabilization, although this may provide an attractive framework for their formal analysis. Frameworks that integrate self-stabilization with fault tolerance have been proposed [AG93, GP93] that may provide a useful foundation for this endeavor.

#### 2.5.1 SAFEbus

A SAFEbus node in the "out-of-sync" state listens on the bus for a Long Resync; if it finds one, it uses the information in that message to integrate itself into the ongoing activity of the bus. If a Long Resync is not detected for a certain length of time, the node transmits an Initial Sync message on all buses (note that both BIUs in the node must agree on this action). Due to the OR gate character of the SAFEbus lines, and the coding used for the Initial Sync message, it does no harm if several nodes attempt to send this message nearly simultaneously. After sending or receiving an Initial Sync message, a node waits a specified amount of time and then sends a Long Resync message; all nodes should be reintegrated and the bus restarted at this point.

SAFEbus uses the same mechanisms for cold start and restart; these are very fast, as nodes will send Initial Sync messages after a timeout that is little longer than a single round of the cyclic schedule, and the bus will be synchronized and operational in the round after that. Reintegration is even faster, as the reintegrating node need wait only for a Long Resync to be sent, and each node initiates at least one of these per round. The SAFEbus mechanisms are fully decentralized and very robust (e.g., they do not depend on collision detection).

#### 2.5.2 TTA