# NASA/TP-2003-XXXXXX

# PEM-INST-001: Instructions for Plastic Encapsulated Microcircuit (PEM) Selection, Screening, and Qualification

Prepared by:

Dr. Alexander Teverovsky and Dr. Kusum Sahu

Reviewed by:

Dr. Henning Leidecker

Approved by: Darryl Lakins

National Aeronautics and Space Administration

Goddard Space Flight Center Greenbelt, Maryland 20771

#### The NASA STI Program Office ... in Profile

Since its founding, NASA has been dedicated to the advancement of aeronautics and space science. The NASA Scientific and Technical Information (STI) Program Office plays a key part in helping NASA maintain this important role.

The NASA STI Program Office is operated by Langley Research Center, the lead center for NASA's scientific and technical inform ation. The NASA STI Program Office provides access to the NASA STI Database, the largest collection of aeronautical and space science ST I in the world. The Program Office is also NASA's institutional mechanism for disseminating the results of its research and development activities. These results are published by NASA in the NASA STI Report Series, which includes the following report types:

- TECHNICAL PUBLICATION. Reports of completed research or a major significant phase of research that present the results of NASA programs and include extensive data or theoretical analysis. Includes compilations of significant scientific and technical data and information deemed to be of continuing reference value. NASA's counterpart of peerreviewed formal professional papers but has less stringent limitations on manuscript length and extent of graphic presentations.

- TECHNICAL MEMORANDUM. Scientific and technical findings that are preliminary or of specialized interest, e.g., quick release reports, working papers, and bibliographies that contain minimal annotation. Does not contain extensive analysis.

- CONTRACTOR REPORT. Scientific and technical findings by NASA-sponsored contractors and grantees.

- CONFERENCE PUBLICATION. Collected papers from scientific and technical conferences, symposia, seminars, or other meetings sponsored or cosponsored by NASA.

- SPECIAL PUBLICATION. Scientific, technical, or historical information from NASA programs, projects, and mission, often concerned with subjects having substantial public interest.

- TECHNICAL TRANSLATION. Englishlanguage translations of foreign scientific and technical material pertinent to NASA's mission.

Specialized services that complement the STI Program Office's diverse offerings include creating custom thesauri, building customized databases, organizing and publishing research results, and even providing videos.

For more information about the NASA STI Program Office, see the following:

- Access the NASA STI Program Home Page at http://www.sti.nasa.gov/STI-homepage.html

- E-mail your question via the Internet to help@sti.nasa.gov

- Fax your question to the NASA Access Help Desk at (301) 621-0134

- Telephone the NASA Access Help Desk at (301) 621-0390

- Write to:

NASA Access Help Desk

NASA Center for AeroSpace Information

7121 Standard Drive

Hanover, MD 21076–1320

# NASA/TP-2003-XXXXXX

# PEM-INST-001: Instructions for Plastic Encapsulated Microcircuit (PEM) Selection, Screening, and Qualification

Prepared by:

Dr. Alexander Teverovsky and Dr. Kusum Sahu, Goddard Space Flight Center, Greenbelt, MD

Reviewed by:

Dr. Henning Leidecker, Goddard Space Flight Center, Greenbelt, MD

Approved by:

Darryl Lakins, Goddard Space Flight Center, Greenbelt, MD

National Aeronautics and Space Administration

**Goddard Space Flight Center** Greenbelt, Maryland 20771

#### Prepared by:

Dr. Alexander Teverovsky, Senior Component Failure Analyst, QSS( Quality Support Services),

Parts, Packaging, and Assembly Technologies Office Goddard Space Flight Center, Greenbelt, MD

Dr. Kusum Sahu, Principal Parts Engineer, Code 562 Parts, Packaging, and Assembly Technologies Office Goddard Space Flight Center, Greenbelt, MD

Reviewed by:

WSU m

Dr. Henning Leidecker, Chief Engineer, Code 562 Parts, Packaging, and Assembly Technologies Office Goddard Space Flight Center, Greenbelt, MD

Approved by:

Darryl Lakins, Head, Code 562

Parts, Packaging, and Assembly Technologies Office Goddard Space Flight Center, Greenbelt, MD

Available from:

NASA Center for AeroSpace Information 7121 Standard Drive Hanover, MD 21076-1320

Price Code: A17

National Technical Information Service 5285 Port Royal Road Springfield, VA 22161

Price Code: A10

# **TABLE OF CONTENTS**

| SECTION | •        |                                                                 | PAGE       |

|---------|----------|-----------------------------------------------------------------|------------|

|         | Table o  | of Contents                                                     | 1          |

|         | List of  | Tables                                                          | 2          |

|         | List of  | Figures                                                         | 2          |

|         | Preface  |                                                                 | 3          |

| 1.      | NASA     | GSFC PEMs Policy                                                | 4          |

| 2.      | Produc   | t Assurance System for PEMs                                     | 6          |

|         | 2.1      | Scope                                                           | 6          |

|         | 2.2      | Product Assurance System (Screening,<br>Qualification, and DPA) | 6          |

|         | 2.3      | Additional Evaluations                                          | 7          |

|         | 2.4      | Requirements for PEMs by Project Risk Levels                    | 8          |

| 3.      | Require  | ements for Screening                                            | 9          |

| 4.      | Require  | ements for Qualification                                        | 16         |

| 5.      | Destruc  | ctive Physical Analysis (DPA)                                   | 20         |

|         | 5.1      | Purposes of DPA for PEMs                                        | 20         |

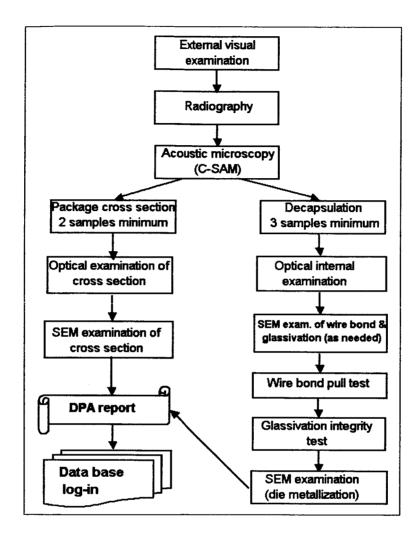

|         | 5.2      | DPA Test Flow                                                   | 20         |

|         | 5.3      | GSFC DPA Procedure                                              | 22         |

|         | 5.3.1    | External Visual Examination                                     | 22         |

|         | 5.3.2    | Radiography                                                     | 22         |

|         | 5.3.3    | Acoustic Microscopy (C-SAM)                                     | 22         |

|         | 5.3.4    | Package Level Cross-Sectioning                                  | 24         |

|         | 5.3.5    | Internal Visual Inspection                                      | 26         |

|         | 5.3.6    | Bond Pull Test                                                  | 27         |

|         | 5.3.7    | Glassivation Layer Integrity                                    | 28         |

|         | 5.3.8    | Assembly Examination Using Scanning Electron Microscope         | e (SEM) 28 |

|         | 5.3.9    | Die Metallization Examination Using SEM                         | 28         |

| 6.      | Evalua   | tion Analysis                                                   | 30         |

| 7.      | Deration | ng Requirements                                                 | 31         |

| 8.      | Handli   | ng and Storage Requirements                                     | 32         |

| 9.      | Inform   | nation From Manufacturers                                       | 33         |

| 10.     | Appen    | dix A: Basis for GSFC Policy on the Use of PEMs                 | 35         |

| 11.     | Appen    | dix B: Product Assurance Methodology                            | 43         |

# LIST OF TABLES

| <u>TABLE</u>  |                                                          | <u>PAGE</u> |

|---------------|----------------------------------------------------------|-------------|

| Table 1       | GSFC PEM Requirements                                    | 8           |

| Table 2       | GSFC Screening Requirements for PEMS                     | 10          |

| Table 2A      | Burn-in and Electrical Measurement Requirements for PEMs | 13          |

| Table 3       | GSFC Qualification Requirements for PEMS                 | 18          |

| Table 4       | Derating Requirements for PEMs                           | 31          |

| Table 5       | Manufacturer Information                                 | 33          |

| <u>FIGURE</u> | LIST OF FIGURES                                          | <u>PAGE</u> |

| Figure 1      | Product Assurance System for PEMs and Its Relationship   |             |

|               | With Reliability During the Part Lifespan                | 7           |

| Figure 2      | A Typical Test Flow for Screening of PEMs                | 9           |

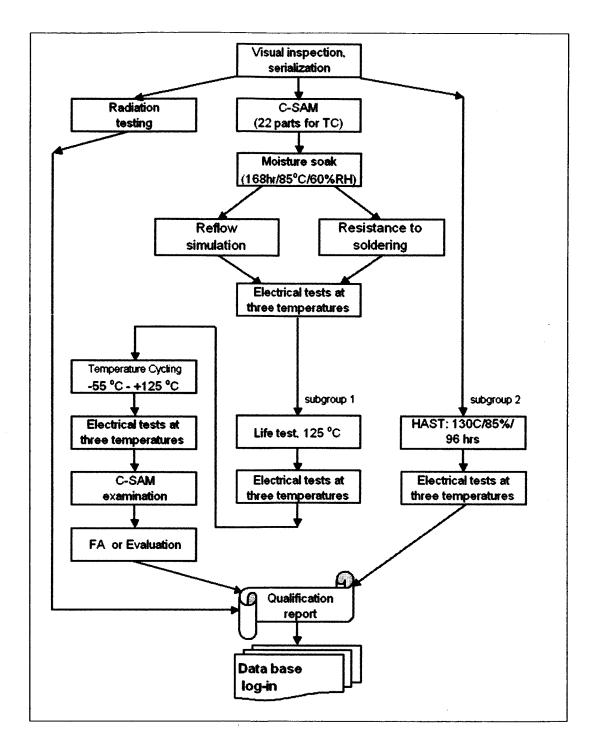

| Figure 3      | A Typical Qualification Test Flow for PEMs               | 17          |

| Figure 4      | A Typical DPA Test Flow for PEMs                         | 21          |

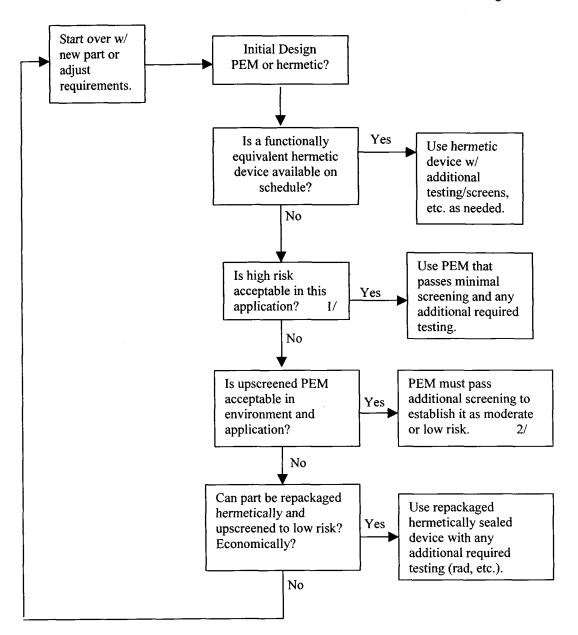

| Figure 5      | PEM Evaluation Process                                   | 42          |

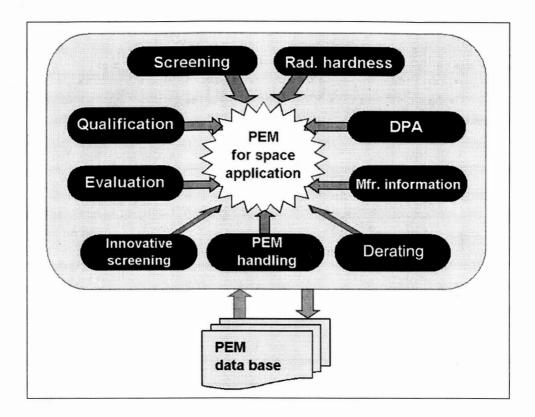

| Figure 6      | GSEC Product Assurance System for PEMs                   | 44          |

## **PREFACE**

Potential users of plastic encapsulated microcircuits (PEMs) need to be reminded that unlike the military system of producing robust high-reliability microcircuits that are designed to perform acceptably in a variety of harsh environments, **PEMs are primarily designed for use in benign environments where equipment is easily accessed for repair or replacement.** The methods of analysis applied to military products to demonstrate high reliability cannot always be applied to PEMs. This makes it difficult for users to characterize PEMs for two reasons:

- 1. Due to the major differences in design and construction, the standard test practices used to ensure that military devices are robust and have high reliability often cannot be applied to PEMs that have a smaller operating temperature range and are typically more frail and susceptible to moisture absorption. In contrast, high-reliability military microcircuits usually utilize large, robust, high-temperature packages that are hermetically sealed.

- 2. Unlike the military high-reliability system, users of PEMs have little visibility into commercial manufacturers' proprietary design, materials, die traceability, and production processes and procedures. There is no central authority that monitors PEM commercial product for quality, and there are no controls in place that can be imposed across all commercial manufacturers to provide confidence to high-reliability users that a common acceptable level of quality exists for all PEMs manufacturers. Consequently, there is no guaranteed control over the type of reliability that is built into commercial product, and there is no guarantee that different lots from the same manufacturer are equally acceptable. And regarding application, there is no guarantee that commercial products intended for use in benign environments will provide acceptable performance and reliability in harsh space environments.

The qualification and screening processes contained in this document are intended to detect poor-quality lots and screen out early random failures from use in space flight hardware. However, since it cannot be guaranteed that quality was designed and built into PEMs that are appropriate for space applications, users cannot screen in quality that may not exist. It must be understood that due to the variety of materials, processes, and technologies used to design and produce PEMs, this test process may not accelerate and detect all failure mechanisms. While the tests herein will increase user confidence that PEMs with otherwise unknown reliability can be used in space environments, such testing may not guarantee the same level of reliability offered by military microcircuits. PEMs should only be used where due to performance needs there are no alternatives in the military high-reliability market, and projects are willing to accept higher risk.

#### 1. NASA/GSFC PEMS POLICY

The use of plastic encapsulated microcircuits (PEMs) is permitted on NASA Goddard Space Flight Center (GSFC) space flight applications, provided each use is thoroughly evaluated for thermal, mechanical, and radiation implications of the specific application and found to meet mission requirements. PEMs shall be selected for their functional advantage and availability, not for cost savings; the steps necessary to ensure reliability usually negate any initial apparent cost advantage. A PEM shall not be substituted for a form, fit, and functional equivalent, high-reliability, hermetic device in space flight applications.

Due to the rapid change in wafer-level designs typical of commercial parts and the unknown traceability between packaging lots and wafer lots, lot-specific testing is required for PEMs, unless specifically excepted by the Mission Assurance Requirements (MAR) for the project. Lot-specific qualification, screening, and radiation hardness assurance analysis and/or testing shall be consistent with the required reliability level as defined in the MAR.

Developers proposing to use PEMs shall address the following items in their Performance Assurance Implementation Plan: source selection (manufacturers and distributors), storage conditions for all stages of use, packing, shipping and handling, electrostatic discharge (ESD), screening and qualification testing, derating, radiation hardness assurance, test house selection and control, and data collection and retention. Use of PEMs outside the manufacturer's rated temperature range requires written approval from GSFC. Specifically, PEMs must be:

- Stored under temperature-controlled, clean conditions, protected from ESD and humidity.

- Traceable to the branded manufacturer.

- Procured from the manufacturer or their approved distributor.

- Tested to verify compliance with the performance requirements of the application environment over the intended mission lifetime.

- Tested using practices and facilities with demonstrated capabilities sufficient to handle and test the technologies involved.

Testing in accordance with EEE-INST-002 shall be performed as necessary to qualify and screen the devices, in order to verify compliance with the application requirements and project risk level defined in the program MAR. Radiation evaluation shall address all threats appropriate for the technology, application, and environment, including Total Ionizing Dose (TID), Single Event Effects (SEE), and displacement damage. Existing radiation data can be used only with the review and approval of the project radiation specialist.

PEMs with manufacture dates older than 3 years before the time of installation shall not be used without GSFC approval. Derating of PEMs must be addressed with consideration of specific material, device construction, device characteristics, and application requirements.

Use of PEMs with pure tin-plated terminations requires special precautions to preclude failures caused by tin whiskers. GSFC approval of mitigation strategies is required.

PEM-INST-001 Section 1. NASA GSFC PEMs Policy Page 5 of 44

Exceptions to testing required by EEE-INST-002 may be permitted by GSFC on a case-by-case basis, where it can be demonstrated that either existing lot-specific test data show acceptable results, or the use of high-risk PEMs represents low risk of functional loss should the part fail. All rationale for such exceptions shall be documented.

NASA will use part performance data collected in accordance with this policy to evaluate the policy's effectiveness and to develop recommendations for future improvements and streamlining.

#### 2.0 PRODUCT ASSURANCE SYSTEM FOR PEMS

# 2.1 Scope

This document establishes a system of product assurance for PEMs in order to invoke the GSFC PEM policy. It is based partly on existing qualification system for military and aerospace components, experience accumulated by the parts engineering community, and practices or guidelines established by high-reliability electronics industry.

# 2.2 Product Assurance System (Screening, Qualification, and DPA)

<u>Purpose</u>. The purpose of this product assurance system is to mitigate the risk of PEM usage, evaluate long-term reliability of the parts, and prevent failures. Commercial PEMs are primarily designed for benign environments and are considered as high-risk parts when used in space applications. For this reason, no PEMs are considered acceptable in high-reliability applications "as is" without additional testing and analysis to assure adequate reliability and radiation tolerance.

Primary Elements of the Product Assurance System

<u>Screening</u>. The purpose of screening is to detect and remove defective parts and reduce infant mortality failures. The screening process proactively evaluates the reliability of the lot.

<u>Qualification</u>. The purpose of qualification testing is to ensure that no wear-out mechanisms would cause premature failures during the part storage, ground phase integration period, and spacecraft mission. The qualification process provides information regarding reliability of the design and the technology.

<u>Radiation Hardness</u>. Radiation effects on the parts (Total Ionization Dose [TID] and Single Event Effects [SEE]) must be assessed on a lot-specific basis according to the project requirements.

Destructive Physical Analysis (DPA). The purpose of DPA is to determine whether the lot has any design, material, workmanship, or process flaws that may not show up during screening and qualification tests and cause degradation or failures during the hardware integration period and spacecraft mission lifetime. When obvious gross defects are revealed during DPA, it is usually an indication that manufacturer's processes are out of control, and a replacement of the lot might be required. Therefore, it is recommended that DPA should be performed prior to screening and qualification of the lot. Anomalies revealed by DPA raise concerns regarding quality and reliability of the parts. These concerns may be further addressed by tailoring screening and qualification procedures or by performing additional design evaluation and testing of the parts (refer to Section 6).

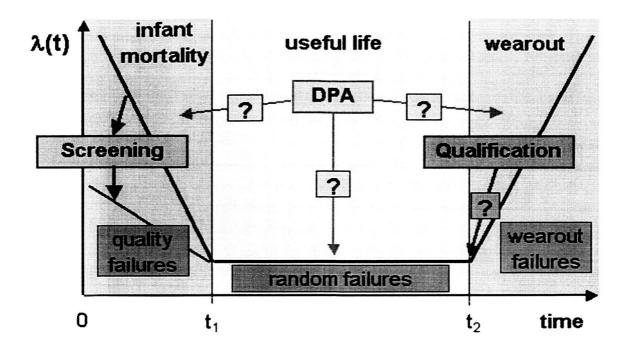

A relationship between the major elements of the product assurance system (screening, qualification, and DPA) and reliability of the parts can be illustrated using a classic bathtub-shaped curve of the lifespan failure rate shown in Figure 1. The three elements of the system discussed have been widely used for high-reliability parts and remain the major means to provide high-quality PEMs for space projects.

**Figure 1.** Product Assurance System for PEMs and Its Relationship With Reliability During the Part Lifespan

#### 2.3 Additional Evaluations

Additional evaluations might be necessary to further mitigate risks associated with the use of PEMs. These assessments shall include:

<u>Design Evaluation</u>. Additional part- and application-specific evaluations performed beyond standard screening, qualification, or DPA may be necessary. Refer to Section 6, which describes capabilities of this element of the product assurance system.

<u>Manufacturer History.</u> The manufacturer's history of ability to produce consistent reliability and quality should be reviewed (refer to Section 9).

<u>Distributor</u>. Use of reputable distributors is essential to avoid procurement of counterfeit parts. Use of brokers is not recommended. Distributor compliance to PEMs handling and storage requirements should be assessed.

Qualification by Flight History. For all PEMs, qualification by flight history or similarity is not acceptable. Commercial PEM manufacturers are known to produce the same part number with die sourced from different wafer lots having different die revisions. The same part number may also be made by multiple production plants, processed according to requirements that vary between wafer and assembly

plants. However, the history of parts' application is important and allows addressing specific problems of design and technology of the parts revealed previously.

# 2.4 Requirements for PEMs by Project Risk Levels

Requirements for use of PEMs in GSFC projects are shown in Table 1 for different project risk levels defined in EEE-INST-001.

Table 1. GSFC PEM Requirements 1/

| Selection Priority | Screening<br>(See Section 3) | Qualification<br>(See Section 4) | DPA<br>(See Section 5) |

|--------------------|------------------------------|----------------------------------|------------------------|

| Level 1            | X                            | X                                | Х                      |

| Level 2            | X                            | X                                | Х                      |

| Level 3            | Х                            | X                                | X                      |

#### Notes:

1/ PEMs qualified according to this document are intended for operation within the manufacturer's data sheet limits. Any uprating and use of PEMs outside the manufacturer's specified range, particularly the temperature limits, is not acceptable.

# 3.0 REQUIREMENTS FOR SCREENING

<u>General</u>. Screening is the only element of the product assurance system, which is applied to all flight parts by testing and inspecting every sample, and proactively affects reliability of the lot. Refer to Tables 2 and 2a for screening requirements of PEMs for projects of different risk levels.

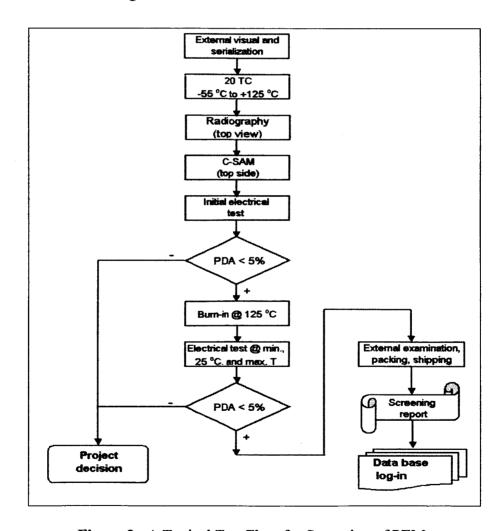

<u>Handling</u>. There are numerous data indicating that improper handling and testing of the parts can introduce more defects than are screened out. Therefore, extreme caution should be taken during handling, storage, and testing to reduce the possibility of electrostatic discharge (ESD), electrical overstress (EOS), contamination, and mechanical damage to the parts. This demands scrupulous attention to the practice and requirements of handling and storage of the flight parts. Guidelines and requirements for handling and storage of PEMs are described in Section 8 of this document. A typical test flow for screening of PEMs is shown in Figure 3.

**Figure 2.** A Typical Test Flow for Screening of PEMs (See Table 2 for details of GSFC screening requirements for PEMs.)

**Table 2.** Screening Requirements for PEMs 1/

| Screen                                                                                   | Test Method and Conditions                                                                                              | Level 1                                                                                          | Level 2                                                                                          | Level 3                                                                                          |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| External visual, and serialization 2/                                                    | Per paragraph 5.3.1.                                                                                                    | Х                                                                                                | Х                                                                                                | Х                                                                                                |

| 2. Temperature cycling                                                                   | MIL-STD-883, Method 1010,<br>Condition B (or to the manufacturer's<br>storage temperature range, whichever<br>is less). |                                                                                                  |                                                                                                  |                                                                                                  |

|                                                                                          | Temperature cycles, minimum.                                                                                            | 20                                                                                               | 20                                                                                               | 20                                                                                               |

| 3. Radiography 3/                                                                        | Per paragraph 5.3.2.                                                                                                    | X                                                                                                | X                                                                                                | X                                                                                                |

| 4. C-SAM inspection 4/                                                                   | Per paragraph 5.3.3.                                                                                                    | X                                                                                                | Х                                                                                                | X                                                                                                |

| 5. Initial (pre-burn-in)                                                                 | Per device specification, at 25 °C                                                                                      | х                                                                                                | X                                                                                                | х                                                                                                |

| electrical measurements (EM) 5/                                                          | At min. and max. rated operational temperatures.                                                                        | X                                                                                                | X                                                                                                | -                                                                                                |

| 6. Engineering review (steps 1 to 5) 6/                                                  |                                                                                                                         |                                                                                                  |                                                                                                  |                                                                                                  |

| 7. Static (steady-state) burn-in (BI) test at 125 °C or at max. operating temperature 7/ | MIL-STD-883, Method 1015, condition A or B.  Hours, minimum depending on the BI temperature.                            | 240 hrs. at<br>125 °C<br>445 hrs. at<br>105 °C<br>885 hrs. at 85<br>°C<br>1,560 hrs. at<br>70 °C | 160 hrs. at<br>125 °C<br>300 hrs. at<br>105 °C<br>590 hrs. at 85<br>°C<br>1,040 hrs. at<br>70 °C | 160 hrs. at<br>125 °C<br>300 hrs. at<br>105 °C<br>590 hrs. at 85<br>°C<br>1,040 hrs. at<br>70 °C |

| 7a. Post static BI electrical measurements at 25 °C                                      | Per device specification. Calculate Delta when applicable.                                                              | X                                                                                                | X                                                                                                | х                                                                                                |

| 9. Dynamic burn-in test at 125 °C or at max. operating temperature 7/                    | MIL-STD-883, Method 1015, Cond. D. Hours, minimum.                                                                      | Same as test step 7.                                                                             | Same as test step 7.                                                                             | Same as test step 7.                                                                             |

| 10. Final parametric and functional tests                                                | Per device specification (at 25 °C, maximum, and minimum rated operating temperatures).                                 | X                                                                                                | X                                                                                                | X                                                                                                |

| 11.Calculate percent<br>defective (steps 7 to 10)<br>6/                                  | Maximum acceptable PDA.                                                                                                 | 5%                                                                                               | 10%                                                                                              | 10%                                                                                              |

| 12. External visual/packing 2/                                                           | Per paragraph 5.3.1 and Section 8.                                                                                      | X                                                                                                | X                                                                                                | X                                                                                                |

Notes on next page.

#### Notes to Table 2. Screening Requirements for PEMs

#### 1/ General

- 1.1/ Screening is performed on 100% of flight parts.

- 1.2/ Historically, only parts with tight lot-specific controls imposed during manufacturing had been allowed for applications in level 1 projects. Such a control is impossible for PEMs, and the suggested screening procedures are not considered as a substitute for manufacturing control, but rather as risk mitigation measures.

- 1.3/ It is the responsibility of the project parts engineer to submit screening test results to Code 562 for logging into the Code 562 PEM database.

- It is recommended to combine the incoming/outgoing visual inspections with the serialization and packaging to reduce handling and possible damage to the parts. Serialization should be performed in such a way to allow a top side C-SAM inspection. Flight parts should be handled and stored in a manner to prevent mechanical and ESD damage, contamination, and moisture absorption (see Section 8).

- To minimize handling, only a top view X-ray inspection is required. Focus to inspect for wire sweeping and obvious defects in the part. Depending on the results of the top view X-ray and/or part construction, a side view may be required.

#### 4/ Acoustic Microscopy (C-SAM)

- 4.1/ General. Acoustic microscopy is performed to screen out defects at critical die surface and lead tip wire-bond areas of the parts and screening, except for power devices, is performed only at the top side.

- 4.2/ Coated Die. Top side of the internal portion of the leads is inspected in PEMs with polymer die coating. Inspection of the die area is not required, as the die coating has a low acoustic impedance that appears as a false delamination.

- 4.3/ Power Devices. For power parts, the bottom side inspection of die attachment might be replaced with the thermal impedance measurements.

- 4.4/ Rejection Criteria.

- Any measurable amount of delamination between molding compound and the die surface.

- Any delaminations on the leads at wire bond areas.

- Delaminations extending more than 2/3 the length of internal part of the leads.

#### 5/ Electrical Measurements

- 5.1/ Special Testing. In addition to parametric and functional measurements per data sheets, supplement and/or innovative testing techniques (e.g. IDDQ leakage currents, thermal impedance, output noise, etc.) can be used to select better quality parts from the lot (cherry pick) as flight candidates. These techniques should be certified and approved by Code 562.

- 5.2/ Failure modes (parametric or catastrophic) should be recorded for each failed part.

#### 6/ Engineering Review

- 6.1/ More than 10% C-SAM rejects might require additional evaluation of thermo-mechanical integrity of the lot or its replacement.

- 6.2/ Most established PEMs manufacturers guarantees 3-sigma level process minimum, which means that less than 0.27% of the parts can be out of specification. Excessive fallouts during initial electrical measurements at room temperature might be due to a poor quality of the lot or effect of temperature cycling performed before electrical measurements, or it might be an indication of problems with the testing lab. When excessive rejects are experienced, the project PE decides whether a lot replacement or additional evaluation is needed based on observed failure modes and results of failure analysis. Excessive rejects during initial electrical measurements might be a legitimate cause for lot replacement.

#### Notes to Table 2 (Continued). Screening Requirements for PEMs

#### 7/ Burn-in (BI)

- 7.1/ General. Burn-in is a complex, product-specific test and if possible should be conducted by the manufacturer of the part. If a user performs this test, special care should be taken not to exceed maximum current, voltage, and die temperature limits.

- 7.2/ Burn-in Temperature. The BI temperature is a "stress" temperature used to precipitate failure of defective parts and is typically much higher than the operational temperature of the part, where the characteristics are guaranteed to remain within the data sheet limits. Most PEM manufacturers use temperatures in the range from 125 °C to 150 °C to periodically perform BI to monitor quality of their product. However, if the parts engineer is unable to justify the suitability of burn-in at 125 °C, the burn-in ambient temperature shall be limited to the maximum operating temperature per the device specifications provided by the manufacturer.

- 7.3/ *Junction Temperature*. The junction temperature during BI testing should not exceed the absolute maximum rated junction temperature for the part.

- 7.4/ Molding Material Glass Transition Temperature. When the die temperature is close to or exceeds the glass transition temperature (Tg) of the molding compound (MC), electrical and mechanical properties of MC may change significantly and new degradation mechanisms may cause failures of the part. For most molding compounds, Tg values exceed 140 to 150 °C, which gives a necessary temperature margin for 125 °C BI. Reliability of the PEMs, which are manufactured with low-Tg molding compounds (Tg < 120 °C), is difficult to assess, and such parts are not recommended for space projects without additional extensive analysis and testing. Glass transition temperature measurements are recommended prior to BI if usage of low-Tg molding compound for the lot is suspected.

- 7.5/ Protection. In some parts the sensitivity of the input/output ESD protection circuits increases with temperature and these circuits can be turned on easily, at lower and/or shorter voltage spikes, than at room temperature. For this reason, special care should be taken to prevent possible power line transients during burn-in testing.

- 7.6/ Excessive proportion of functional BI failures, even when the total number of failures is within the PDA limits, might be an indication of serious lot reliability problems. In these cases additional testing and analysis of the parts might be required.

- 7.7/ Steady-state burn-in is performed on all linear and mixed-signal devices (see Table 2A for details on burn-in conditions). The duration of steady-state burn-in can be reduced 50% if the parts are to be subjected to dynamic burn-in testing.

- 7.8/ Dynamic burn-in is not required for parts operating under steady-state conditions, e.g. voltage references, temperature sensors, etc.

- 7.9/ Only one type of BI test, either static or dynamic, is required for level 2 and 3 parts.

- 7.10/ Under special circumstances, when it is technically and economically viable, and for components, which are difficult to assess at the piece part level, alternative testing in lieu of static and/or dynamic BI testing (for example, board-level burn-in) may be permitted. It is the responsibility of the project PE to document and submit a rationale for the technical feasibility and equivalency of the alternative testing to the project and GSFC Code 562 for approval. Board-level burn-in shall not be routinely substituted for piece part burn-in as a convenience.

Table 2A. Burn-in and Electrical Measurement Requirements for PEMs

|                                                              | Require                                                             | Required Burn-In 1/                                                                                                                               |                                                          | Electrical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IC Type                                                      | Static<br>(Condition C) 2/                                          | Dynamic<br>(Condition D) 2/                                                                                                                       | Delta                                                    | Measurements 3/, 4/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Digital Bipolar & Digital MOS/BiCMOS:                        | Not required for Digital Bipolar Technology.                        | Required for both technologies.  Vin = Square wave, 50% duty cycle to                                                                             | Δl <sub>cc</sub><br>or<br>Δl <sub>DD</sub>               | DC: V <sub>IC</sub> , V <sub>OH</sub> , V <sub>OL</sub> , I <sub>CC</sub> (I <sub>EE</sub> ), I <sub>IL</sub> , I <sub>IH</sub> , I <sub>DD</sub> , I <sub>OZL</sub> , I <sub>OZH</sub> , I <sub>OS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Flip-Flops, Multiplexers, Registers,                         | Required for Digital MOS  Technology.                               | input pins and control pins.  Frequency= 100 Hz to 1 Mhz.                                                                                         |                                                          | AC: Гріль, Гріль, Ттіль, Ттіль, Тріль, Тріль, Тріль, Тріль, ТА, Т. Тріль, Т. Тріль, Т. Тріль, Т. Тріль, Тр |

| RAMs FIFOs Microprocessors                                   | and Vss across the remaining inputs.                                | $V_{OUT} = V_{CC}/2$ or $V_{DD}/2$ through $R_{\rm L.}$ .                                                                                         |                                                          | runctional rests:  a) For simple logic devices, verify truth table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Interface Peripherals<br>ASICs                               | $V_{OUT}$ = 0.5 $V_{DD}$ through $R_L$                              |                                                                                                                                                   |                                                          | b) For complex logic devices such as ASIC, FPGA, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FPGA, PROM, PAL                                              |                                                                     |                                                                                                                                                   |                                                          | microprocessors, functional testing should include fault coverage calculations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                              |                                                                     |                                                                                                                                                   |                                                          | c) For PROMs, check fuse map; for RAMs, perform pattern sensitive tests such as March                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                              |                                                                     |                                                                                                                                                   |                                                          | Galpat, etc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Linear MOS, Bipolar,<br>and Bi-FET: 5/<br>Op-Amp, Instrument | $V_{\text{out}}\text{=}\text{Terminated to ground through}$ $R_{L}$ | V <sub>in</sub> = Square wave or sinewave<br>F= 10Hz to 100 KHz, 50% duty cycle<br>V <sub>out</sub> = Terminated to ground through R <sub>L</sub> | AI <sub>IB</sub><br>AI <sub>IO</sub><br>AV <sub>IO</sub> | DC: Icc, Iee, Io, Vo, Vopp, Av,<br>CMRR, PSRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Amplifiers, S/H, and<br>Comparator                           |                                                                     |                                                                                                                                                   |                                                          | AC: Slew rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Notes at end of Table 2A.

Table 2A (Continued). Burn-in and Electrical Measurement Requirements for PEMs

|                                     | Required                                                                    | Required Burn-In 1/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                       | Electrical                                                                                                           |

|-------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| IC Type                             | Static (Condition C) 2/                                                     | Dynamic<br>(Condition D) 2/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Delta                                 | Measurement 3/, 4/                                                                                                   |

| Linear MOS, Bipolar<br>and JFET: 5/ | $V_{in} = V_{DD}$ max across one-half input<br>pins and $V_{SS}$ across the | V <sub>in</sub> = Square wave at a specified<br>frequency and duty cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\Delta I_{ m CC}$ $\Delta I_{ m IH}$ | <b>DC:</b> V <sub>OH</sub> , V <sub>OL</sub> , I <sub>CC</sub> , I <sub>IL</sub> , I <sub>IH</sub> , I <sub>OS</sub> |

| Line Drivers and<br>Receivers       | remaining inputs.                                                           | $V_{out} = V_{CC} \text{ through } R_L$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                       | АС: Тран, Трна, Ттан, Ттна                                                                                           |

|                                     |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       | Functional Test: Verify truth table                                                                                  |