## Semiconductors & ICs

## MMIC Amplifiers for 90 to 130 GHz

Output power exceeds that of prior solid-state amplifiers operating above 110 GHz.

NASA's Jet Propulsion Laboratory, Pasadena, California

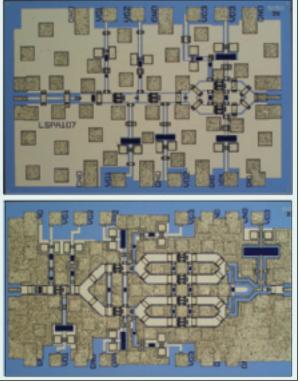

The figure shows two monolithic microwave integrated-circuit (MMIC) amplifier chips optimized to function in the frequency range of 90 to 130 GHz, covering nearly all of Fband (90 - 140 GHz). These amplifiers were designed specifically for local-oscillator units in astronomical radio telescopes such as the Atacama Large Millimeter Array (ALMA). They could also be readily adapted for use in electronic test equipment, automotive radar systems, and communications systems that operate between 90 and 130 GHz.

There have been many published articles about MMIC power-amplifier chips and modules that operate at lower frequencies in W-band (75–110 GHz). Such chips typically provide 50 to 300 mW of output power per 0.6 to 1.2 mm of gate periphery of the transistors on the chips, and contain either GaAs or InP high-electron-mobility transistors (HEMTs) or InP heterojunction bipolar transistors. The radio-frequency in-

terconnections on such chips have been primarily made with microstrip transmission lines, which are particularly convenient for large eight-way power-combining networks. For higher frequencies, it may be more beneficial to use grounded coplanar waveguide transmission lines to avoid the added source inductances required in microstrip circuits to provide grounds for the transistors. The present 90-130 GHz MMIC amplifiers are products of an effort to increase the operating frequency of power amplifiers beyond W-band utilizing co-planar waveguide circuitry, while also increasing the number of transistors to be power-combined on a chip (and hence, the maximum output power).

One of the challenges in designing MMIC power amplifiers to operate above W-band is the choice of transistor.

These **MMIC Amplifier Chips** operate in the frequency range of 90 to 130 GHz. The final stage of the chip shown at the top contains a twoway power combiner; the final stage of the chip shown at the bottom contains a four-way power combiner.

InP HEMTs having gate lengths no larger than 0.12 µm are the most mature technology available, though InP double-heterojunction bipolar transistors are starting to gain ground. A second challenge is to power-combine as many large-periphery transistors as possible within the constraints of matching networks at the higher frequencies. The best W-band power amplifiers utilize eight-way power combiners for a total gate periphery of 1.2 mm. Since powercombining field-effect transistors (FETs) involves placing source vias between the FETs, the compactness of power-combining structures becomes more difficult as wavelength decreases. One result of the constraints imposed by design rules, fabrication processes, and current-carrying capacities of the transmission line circuit elements, is that the range of coplanarwaveguide impedances available for matching networks is restricted approximately to between 23 and 65  $\Omega$ .

The present two MMIC amplifier chips were designed with these challenges and constraints in mind. The transistors on these chips are 0.11-µm-gate-length AlInAs/GaInAs/InP HEMT devices grown by molecular-beam epitaxy at HRL Laboratories, LLC. These transistors exhibit typical DC transconductances of 1,050 mS/mm and breakdown voltages of 4 V. The transistors include four gate fingers, each 37 µm wide, making a total periphery of 148 µm. The circuitry is formed using a grounded coplanar-waveguide transmission lines on a 50um-thick InP substrate. Vias between the top ground planes and back-side metal are used to suppress unwanted substrate waveguide modes. The chip shown in the upper part of the figure incorporates three stages. The final stage contains two power-combined HEMTs, so that the total gate periphery of the output stage is about 300 µm. The chip

shown in the lower part of the figure incorporates three stages. The final stage on this chip contains a four-way power combiner at the output; hence, the total gate periphery of the output stage of this chip is about 600  $\mu$ m. The amplifier chips were mounted in waveguide modules. When tested, these amplifier modules exhibited gains of 15 to 20 dB and output powers from 20 to 45 mW — the highest output powers thus far obtained from any solid-state amplifier modules above 110 GHz.

This work was done by Lorene Samoska, David Pukala, and Alejandro Peralta of Caltech for NASA's Jet Propulsion Laboratory; Eric Bryerton, Matt Morgan, and T. Boyd of the National Radio Astronomy Observatory; and Ming Hu and Adele Schmitz of HRL Laboratories, LLC. Further information is contained in a TSP (see page 1). NPO-41481